## 3G, HD, SD SDI Receiver

### **Key Features**

- Operation at 2.970Gb/s, 2.970/1.001Gb/s, 1.485Gb/s, 1.485/1.001Gb/s, and 270Mb/s

- Supports SMPTE ST 425 (Level A and Level B), SMPTE ST 424, SMPTE 292, SMPTE ST 259-C, and DVB-ASI

- 2K and Multi-link UHD support

- Configurable Power-down modes

- Integrated Retimer

- Serial digital reclocked or non-reclocked loop-through output

- Integrated audio de-embedder for 8 channels of 48kHz audio and audio clock generation

- · Ancillary data extraction

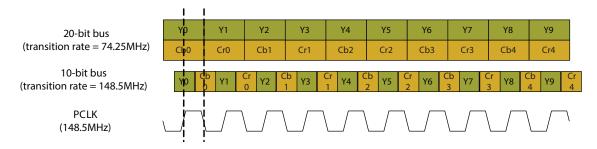

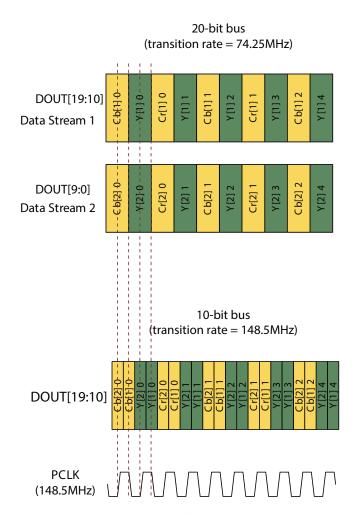

- Parallel data bus selectable as either 20-bit or 10-bit,

SDR or DDR rate

- Comprehensive error detection and correction features

- Dual serial digital input buffer with 2x2 MUX

- Serial Loopback independently configurable to select either input

- Performance optimized for 270Mb/s, 1.485Gb/s, and 2.97Gb/s.

- Dual/Quad Link 3G-SDI support with multiple GS3470 devices

- Output H, V, F, or CEA 861 timing signals

- GSPI host interface

- +1.2V digital core power supply, +1.2V and +1.8V analog power supplies, and selectable +1.8V or +2.5V I/O power supply

- -20°C to +85°C operating temperature range

- Low power operation typically 220mW

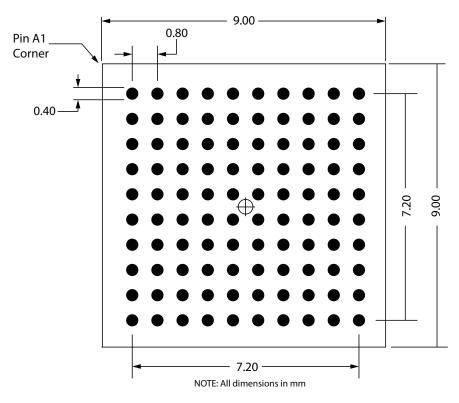

- Small 9mm x 9mm 100-ball BGA package (0.80mm Ball Pitch)

- Pb-free, Halogen-free, and RoHS/ WEEE-compliant package

### **Applications**

SDI Interfaces for:

- Monitors

- DVRs

- Video Switchers

- Editing Systems

- Cameras

- Medical Imaging

- Aviation, Military, and Vehicular video systems

- LED Wall and Digital Signage Applications

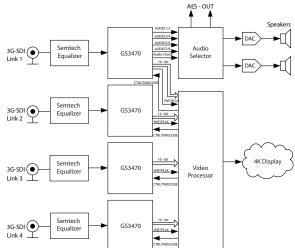

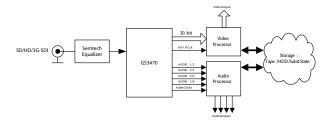

Application: 2160p50/60 (4K) Monitor

Application: Multi-format Video and Audio Processor

### **Description**

The GS3470 is a multi-rate SDI Receiver which includes complete SMPTE processing. The SMPTE processing features can be bypassed to support signals with other coding schemes. Multi-link UHD can be supported when multiple GS3470 devices are used.

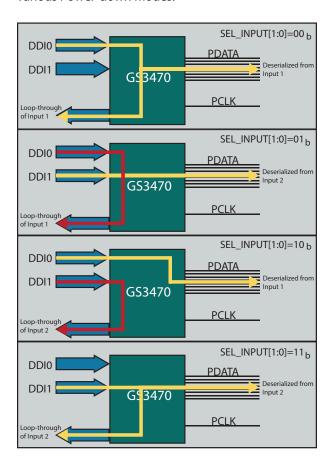

The device features a dual input buffer with a 2x2 MUX. The 2x2 MUX can select between either input for de-serialization and can route either of the two inputs to the serial loopback independently (reclocked or non-reclocked). In addition, the integrated Retimer with an internal VCO provides a wide Input Jitter Tolerance (IJT).

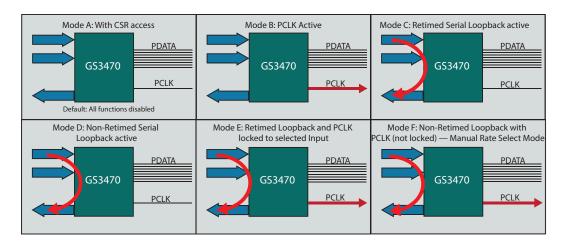

Configurable Power-down modes are available and allows for increased flexibility. Each Power-down mode enables power savings to a varying degree by selectively enabling or disabling key features. Some of the options available in Power-down mode are CSR access, PCLK, retimed DDO loop-through output, and non-retimed DDO loop-through output. Enabling or disabling each of these options will offer power consumption levels to suit the application's requirements.

The device has three other basic modes of operation which include:

- SMPTE mode

- DVB-ASI mode

- Data-Through mode

The GS3470 includes an audio de-embedder and audio clocks are internally generated. Up to eight channels (two audio groups) of serial digital audio may be extracted from the video data stream, in accordance with SMPTE ST 272-C and SMPTE ST 299.

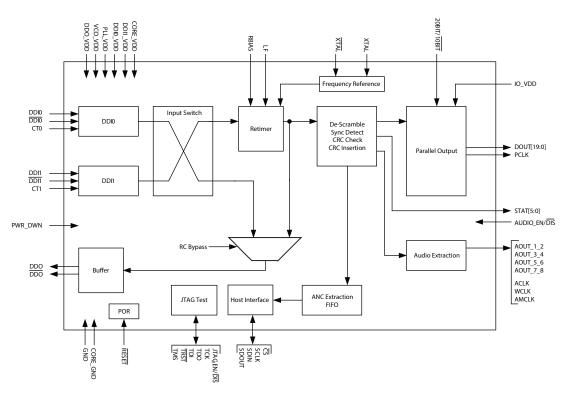

**GS3470 Functional Block Diagram**

# **Revision History**

| Version | ECO    | Date           | Changes and/or Modifications                                                                                                          |

|---------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 9       | 043185 | August 2018    | Updated Table 1-1, Table 2-3, and Section 4.<br>Added Table 5-12, and updated Section 5.                                              |

| 8       | 038819 | September 2017 | Updated to latest corporate template.                                                                                                 |

| 7       | 038315 | September 2017 | Updated several register and parameter names throughout Section 4. Updated Figure 4-1, Figure 6-1.                                    |

| 6       | 037007 | May 2017       | Updated Table 2-2, Table 2-3, Table 2-4,<br>Table 4-27, Table 5-8.<br>Changed all instances of DBUS to DOUT, and<br>VSS/VEE to A_GND. |

| 5       | 035144 | March 2017     | Added Figure 4-14 through Figure 4-19.<br>Updated Section 4.16.1.<br>Updated Table 2-2, Table 2-3, Table 2-4,<br>Table 4-27.          |

| 4       | 033598 | October 2016   | Updated data sheet to reflect GS3471 modifications.                                                                                   |

| 3       | 029850 | March 2016     | Updates to 1.1 Pin Assignment and 2.2 Recommended Operating Conditions.                                                               |

| 2       | 029341 | February 2016  | Initial release changes.                                                                                                              |

| 1       | 028179 | October 2015   | Initial release changes.                                                                                                              |

| 0       | 020778 | July 2014      | New document.                                                                                                                         |

## **Contents**

| 1. Pin Out                                                   | 6  |

|--------------------------------------------------------------|----|

| 1.1 Pin Assignment                                           | 6  |

| 1.2 Pin Descriptions                                         | 6  |

| 2. Electrical Characteristics                                | 10 |

| 2.1 Absolute Maximum Ratings                                 | 10 |

| 2.2 Recommended Operating Conditions                         | 10 |

| 2.3 DC Electrical Characteristics                            | 11 |

| 2.4 AC Electrical Characteristics                            | 13 |

| 3. Input/Output Circuits                                     | 17 |

| 4. Detailed Description                                      | 19 |

| 4.1 Functional Overview                                      | 19 |

| 4.2 Device Power-Up                                          | 21 |

| 4.2.1 Power-Down Mode                                        | 21 |

| 4.2.2 Device Reset                                           | 23 |

| 4.3 Modes of Operation                                       | 23 |

| 4.3.1 Auto and Manual Mode                                   | 23 |

| 4.3.2 Low Latency Video Path                                 | 24 |

| 4.3.3 SMPTE and SMPTE Bypass Mode                            | 24 |

| 4.3.4 DVB-ASI Mode                                           | 25 |

| 4.4 Digital Differential Input (DDI/DDI)                     | 25 |

| 4.5 Serial Digital Loop-Through Output                       | 25 |

| 4.6 Serial Digital Retimer                                   | 26 |

| 4.7 External Crystal/Reference Clock                         | 26 |

| 4.8 Lock Detect                                              | 26 |

| 4.9 Parallel Data Outputs                                    | 27 |

| 4.9.1 Parallel Data Bus Output Levels                        | 27 |

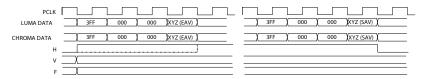

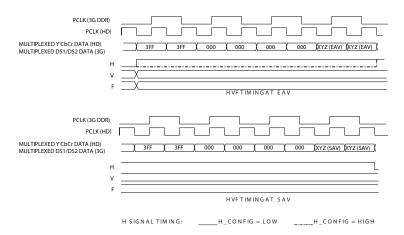

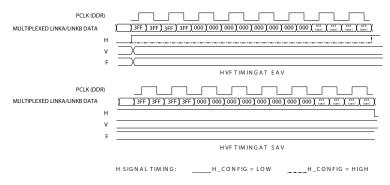

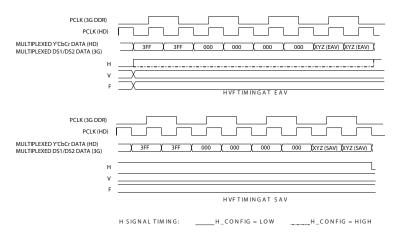

| 4.9.2 Parallel Output in SMPTE Mode                          | 27 |

| 4.9.3 Parallel Output in DVB-ASI Mode                        | 28 |

| 4.9.4 Parallel Output in Data-Through Mode                   | 28 |

| 4.9.5 Parallel Output Data Format Clock/PCLK Settings        | 28 |

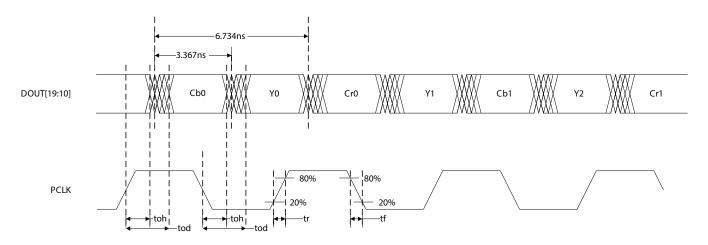

| 4.9.6 DDR Parallel Clock Timing                              | 30 |

| 4.10 Timing Signal Extraction                                | 32 |

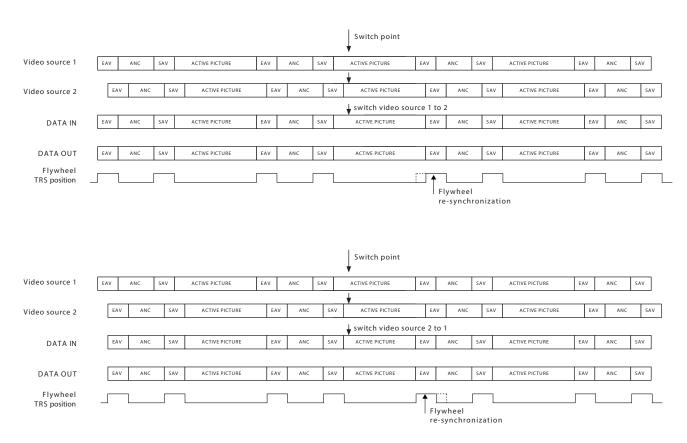

| 4.10.1 Automatic Switch Line Lock Handling                   | 32 |

| 4.10.2 Manual Switch Line Lock Handling                      | 33 |

| 4.11 Programmable Multifunction Outputs                      | 34 |

| 4.12 H:V:F Timing Signal Extraction                          | 35 |

| 4.12.1 CEA-861 Timing Generation                             | 37 |

| 4.13 Automatic Video Standards Detection                     | 42 |

| 4.14 Data Format Detection & Indication                      | 47 |

| 4.14.1 SMPTE ST 425 Mapping - 3G Level A and Level B Formats | 48 |

| 4.15 EDH Detection                                           | 49 |

| 4.15.1 EDH Packet Detection (SD Only)                        | 49 |

| 4.15.2 EDH Flag Detection                                    | 49 |

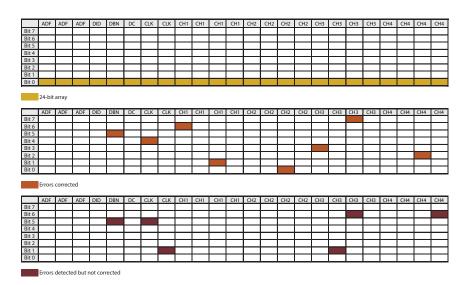

| 4.16 Video Signal Error Detection & Indication               | 50 |

| 4.16.1 TRS Error Detection                                   | 52 |

| 4.16.2 Line Based CRC Error Detection            | 52  |

|--------------------------------------------------|-----|

| 4.16.3 EDH CRC Error Detection                   | 53  |

| 4.16.4 HD & 3G Line Number Error Detection       | 53  |

| 4.17 Ancillary Data Detection & Indication       | 53  |

| 4.17.1 Programmable Ancillary Data Detection     | 55  |

| 4.17.2 SMPTE ST 352 Payload Identifier           | 56  |

| 4.17.3 Ancillary Data Checksum Error             | 57  |

| 4.18 Signal Processing                           | 58  |

| 4.18.1 Audio De-Embedding Mode                   | 59  |

| 4.18.2 TRS Insertion                             | 59  |

| 4.18.3 Line Based CRC Insertion                  | 59  |

| 4.18.4 Line Number Insertion                     | 60  |

| 4.18.5 ANC Data Checksum Insertion               | 60  |

| 4.18.6 EDH CRC Insertion                         | 61  |

| 4.18.7 Illegal Word Re-mapping                   | 61  |

| 4.18.8 TRS and Ancillary Data Preamble Remapping | 61  |

| 4.18.9 Ancillary Data Extraction                 | 61  |

| 4.19 Audio De-Embedder                           | 67  |

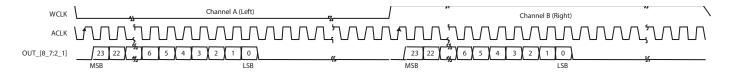

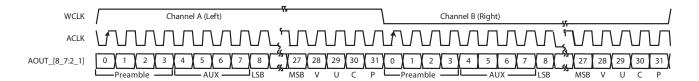

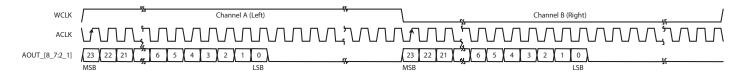

| 4.19.1 Serial Audio Data I/O Signals             | 68  |

| 4.19.2 Serial Audio Data Format Support          | 69  |

| 4.19.3 Audio Processing                          | 74  |

| 4.19.4 Error Reporting                           | 80  |

| 4.20 GSPI - HOST Interface                       | 81  |

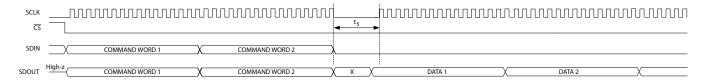

| 4.20.1 CS Pin                                    | 81  |

| 4.20.2 SDIN Pin                                  | 81  |

| 4.20.3 SDOUT Pin                                 | 82  |

| 4.20.4 SCLK Pin                                  | 83  |

| 4.20.5 Command Word 1 Description                |     |

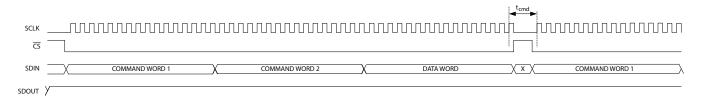

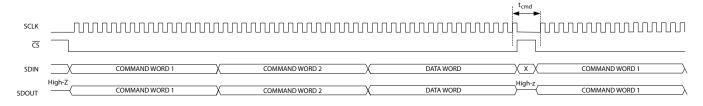

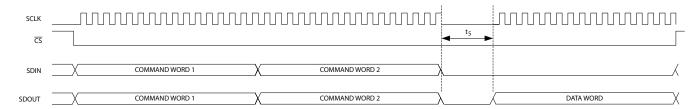

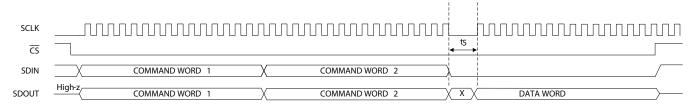

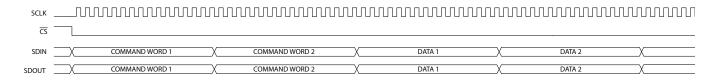

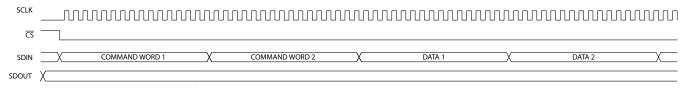

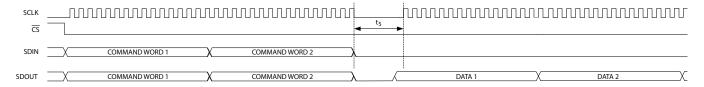

| 4.20.6 GSPI Transaction Timing                   | 86  |

| 4.20.7 Single Read/Write Access                  | 88  |

| 4.20.8 Auto-Increment Read/Write Access          |     |

| 4.20.9 Setting a Device Unit Address             |     |

| 4.20.10 Default GSPI Operation                   |     |

| 4.21 JTAG Test Operation                         |     |

| 5. Register Map                                  |     |

| 5.1 Control Registers                            |     |

| 6. Application Information                       |     |

| 6.1 Typical Application Circuit                  |     |

| 6.2 Layout Considerations                        |     |

| 7. References & Relevant Standards               |     |

| 8. Package & Ordering Information                |     |

| 8.1 Package Dimensions                           |     |

| 8.2 Recommended PCB Footprint                    |     |

| 8.3 Packaging Data                               |     |

| 8.4 Marking Diagram                              |     |

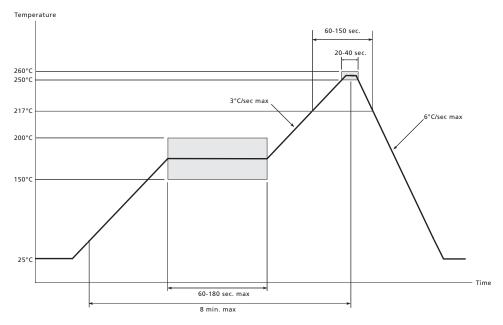

| 8.5 Solder Reflow Profiles                       |     |

| 8.6 Ordering Information                         | 158 |

# 1. Pin Out

# 1.1 Pin Assignment

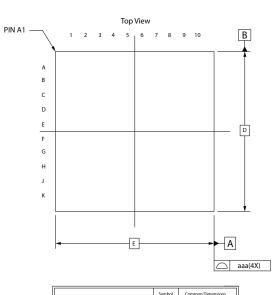

Figure 1-1: Pin Assignment

|   | 1        | 2        | 3                | 4        | 5        | 6           | 7        | 8        | 9        | 10     |

|---|----------|----------|------------------|----------|----------|-------------|----------|----------|----------|--------|

| Α | DDI0     | DDI0     | СТ0              | RBIAS    | XTAL     | XTAL        | RSVD     | PCLK     | DOUT18   | DOUT17 |

| В | DDI0_VDD | DDI0_VDD | RSVD             | RSVD     | STAT0    | STAT1       | IO_VDD   | DOUT19   | DOUT16   | DOUT15 |

| С | PLL_VDD  | PLL_VDD  | LF               | VCO_VDD  | STAT2    | STAT3       | CORE_GND | DOUT12   | DOUT14   | DOUT13 |

| D | DDI1_VDD | PLL_VDD  | A_GND            | VCO_VDD  | STAT4    | STAT5       | TRST     | TDI      | CORE_GND | IO_VDD |

| E | CT1      | DDI1_VDD | A_GND            | CORE_GND | CORE_VDD | CORE_VDD    | TDO      | TCK      | DOUT10   | DOUT11 |

| F | DDI1     | A_GND    | A_GND            | CORE_GND | CORE_GND | CORE_VDD    | TMS      | SDIN     | DOUT8    | DOUT9  |

| G | DDI1     | A_GND    | A_GND            | CORE_GND | CORE_GND | CORE_VDD    | SDOUT    | SCLK     | CORE_GND | IO_VDD |

| н | NC       | NC       | JTAG_<br>EN/DIS  | WCLK     | RESET    | BIT20/BIT10 | CS       | CORE_GND | DOUT6    | DOUT7  |

| J | DDO_VDD  | DDO_VDD  | PWR_DWN          | AOUT_1_2 | ACLK     | AOUT_5_6    | CORE_GND | DOUT1    | DOUT4    | DOUT5  |

| К | DDO      | DDO      | AUDIO_<br>EN/DIS | AOUT_3_4 | AMCLK    | AOUT_7_8    | IO_VDD   | DOUT0    | DOUT2    | DOUT3  |

# **1.2 Pin Descriptions**

**Table 1-1: Pin Descriptions**

| Pin Number       | Name                     | Туре         | Description                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2<br>G1, F1 | DDI0, DDI0<br>DDI1, DDI1 | SDI Input    | Serial digital differential input. It is possible to DC-couple to upstream Semtech devices supporting 1.2V outputs. Additionally, devices with 1.8 and 2.5V outputs are supported through a 4.7 $\mu$ F capacitor in series with the $\overline{DDI}/DDI$ input. Connect unused inputs to DDI_VDD through 1k $\Omega$ resistors. |

| A4               | RBIAS                    | Analog Input | External resistor for the bias circuit. Connect to ground through 777 $\!\Omega$ resistor.                                                                                                                                                                                                                                       |

| A5, A6           | XTAL, XTAL               | Analog Input | Input connection for 27MHz crystal. When a reference clock input is used on XTAL, do not connect XTAL.                                                                                                                                                                                                                           |

www.semtech.com

Table 1-1: Pin Descriptions (Continued)

| Pin Number                                                                                         | Name       | Type         | Description                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                          |  |  |  |

|----------------------------------------------------------------------------------------------------|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A8                                                                                                 | PCLK       | Output       | Parallel data bus clock.  Please refer to the Output Logic parameters in Table 2-3: DC  Electrical Characteristics for logic level threshold and compatibility.  Please refer to Table 4-5: GS3470 Output Data Formats for PCLK output rates.                                              |                                                                                                                                                                                                          |  |  |  |

| A7, B3, B4                                                                                         | RSVD       | _            | These pins are reserved, do not connect.                                                                                                                                                                                                                                                   |                                                                                                                                                                                                          |  |  |  |

| B7, D10, G10, K7                                                                                   | IO_VDD     | Power        | Power connection for di                                                                                                                                                                                                                                                                    | gital I/O. Connect to 1.8V or 2.5V DC digita                                                                                                                                                             |  |  |  |

|                                                                                                    |            |              |                                                                                                                                                                                                                                                                                            | ut Logic parameters in Table 2-3: DC<br>for logic level threshold and compatibility                                                                                                                      |  |  |  |

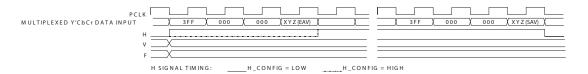

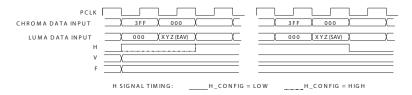

| B8, A9, A10, B9,<br>B10, C9, C10, C8,<br>E10, E9, F10, F9,<br>H10, H9, J10, J9,<br>K10, K9, J8, K8 |            |              | SMPTE mode  (SMPTE_BYPASS = HIGH and DVB_ASI = LOW):  DOUT[19:10] — Luma data output SD and HD data rates; Data Stream 3G data rate  DOUT[9:0] — Chroma data output SD and HD data rates; Data Stream 3G data rate  Data-Through mode  (SMPTE_BYPASS = LOW and DVB_ASI = LOW): Data output |                                                                                                                                                                                                          |  |  |  |

|                                                                                                    | DOUT[19:0] | Output       |                                                                                                                                                                                                                                                                                            | SMPTE mode (SMPTE_BYPASS = HIGH and DVB_ASI = LOW): Multiplexed Luma/Chroma data outpu for SD and HD data rates; Multiplexed Data Stream 1&2 for 3G data rate                                            |  |  |  |

|                                                                                                    |            |              | 10-bit mode<br>20BIT/10BIT = LOW<br>(DOUT[19:10])                                                                                                                                                                                                                                          | DVB-ASI mode (SMPTE_BYPASS = LOW and DVB_ASI = HIGH): 8/10bit decoded DVB-ASI data for SD data rates Data-Through mode (SMPTE_BYPASS = LOW and DVB_ASI = LOW): Data output  Note 1: When in 10-bit mode, |  |  |  |

|                                                                                                    |            |              |                                                                                                                                                                                                                                                                                            | DOUT[9:0] are set to 0.  Note 2: When in 10-bit mode, leave unused output pins unconnected.                                                                                                              |  |  |  |

| C1, C2, D2                                                                                         | PLL_VDD    | Power        | Power pins for the Retim                                                                                                                                                                                                                                                                   | ner PLL. Connect to 1.2V DC analog.                                                                                                                                                                      |  |  |  |

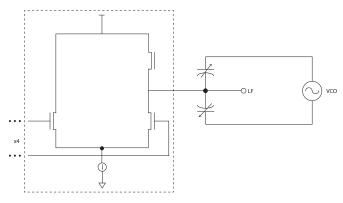

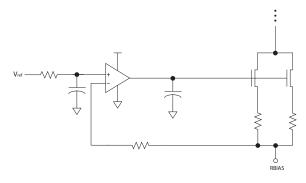

| C3                                                                                                 | LF         | Analog Input | Loop Filter component of Application Circuit.                                                                                                                                                                                                                                              | connection. Connect as per Typical                                                                                                                                                                       |  |  |  |

**Table 1-1: Pin Descriptions (Continued)**

| Pin Number                                | Name                 | Туре                                    | Description                                                                                                                                                                                                                         |

|-------------------------------------------|----------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C4, D4                                    | VCO_VDD              | Power                                   | Power pin for the VCO. Connect to RC filter as per Typical Application Circuit. Connect to a 1.2V $\pm 5\%$ analog supply through a 24.9 $\Omega$ resistor. Additionally, connect to ground through a 10 $\mu$ F capacitor.         |

| C7, D9, E4, F4, F5,<br>G4, G5, G9, J7, H8 | CORE_GND             | Power                                   | Ground pins for digital circuitry. Connect to digital ground.                                                                                                                                                                       |

| D3, E3, F2,<br>F3, G2, G3                 | A_GND                | Power                                   | Ground pins for analog circuitry. Connect to analog ground.                                                                                                                                                                         |

| D1, E2<br>B1, B2                          | DDI1_VDD<br>DDI0_VDD | Power                                   | Power pins for SDI buffer. Connect to 1.2V DC analog.                                                                                                                                                                               |

|                                           |                      |                                         | Multi-function status outputs. See Section 4.11 for more details on assigning signals to STAT pins.  Please refer to the Output Logic parameters in Table 2-3: DC                                                                   |

| D6, D5, C6,<br>C5, B6, B5                 | STAT[5:0]            | Digital Output                          | Electrical Characteristics for logic level threshold and compatibility.  Each of the STAT[5:0] pins can be configured individually to output one of the following signals.  See Table 4-7: Output Signals Available on Programmable |

|                                           |                      |                                         | Multifunction Pins for Status Signal Selection Codes and Default Output Pins.  JTAG interface reset. Digital active-low reset input. Used to reset the                                                                              |

| D7                                        | TRST                 | Digital Input,<br>Internal<br>Pull-down | JTAG test sequence.  When LOW, the JTAG test sequence is reset.  When HIGH, normal operation of the JTAG test sequence resumes.  When not in use, TRST can be left unconnected.                                                     |

| D8                                        | TDI                  | Digital Input,<br>Internal Pull-up      | JTAG interface Test Data Input. Serial instructions and data are received on this pin. When not in use, TDI can be left unconnected.                                                                                                |

| E1, A3                                    | CT[1:0]              | Analog Input                            | Decoupling for internal SDI termination resistors. Connect as per Typical Application Circuit. When an input is not used, its corresponding CT pin can be left unconnected.                                                         |

| E5, E6, F6, G6                            | CORE_VDD             | Power                                   | Power connection for device core. Connect to 1.2V DC digital.                                                                                                                                                                       |

| E7                                        | TDO                  | Digital Output                          | JTAG interface Test Data Output. TDO is the serial output for test instructions and data.                                                                                                                                           |

| E8                                        | TCK                  | Digital Input                           | JTAG interface Test Clock input. The test clock input provides the clock for the test logic of this device.                                                                                                                         |

| F7                                        | TMS                  | Digital Input,<br>Internal Pull-up      | JTAG interface Test Mode Select input. This signal is decoded by the internal TAP controller to control test operations.  When not in use, TMS can be left unconnected.                                                             |

| F8                                        | SDIN                 | Digital Input                           | Serial Digital Data Input for the Gennum Serial Peripheral Interface (GSPI) host control/status port. When GSPI is not used, SDIN should be tied HIGH or LOW to minimize noise.                                                     |

| G7                                        | SDOUT                | Digital Output                          | Serial Digital Data Output for the Gennum Serial Peripheral Interface (GSPI) host control/status port. Active-high output. When GSPI is not used, leave unconnected.                                                                |

Table 1-1: Pin Descriptions (Continued)

| Pin Number              | Name                                            | Туре                                    | Description                                                                                                                                                                                                                         |

|-------------------------|-------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G8                      | SCLK                                            | Digital Input                           | Serial Data Clock input. Burst-mode clock input for the Gennum<br>Serial Peripheral Interface (GSPI) host control/status port. When GSI<br>is not used, SCLK should be tied HIGH or LOW to minimize noise.                          |

| H1, H2                  | NC                                              | _                                       | No connect. Pins are not connected internally.                                                                                                                                                                                      |

| H3                      | JTAG_EN/ <del>DIS</del>                         | Digital Input,<br>Internal<br>Pull-down | JTAG enable. Digital active-high to enable JTAG communications.<br>When HIGH, JTAG operational mode is enabled.<br>When LOW, JTAG operational mode is disabled.                                                                     |

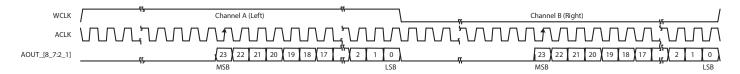

| H4                      | WCLK                                            | Output                                  | 48kHz word clock for audio. When not used, leave unconnected.                                                                                                                                                                       |

| H5                      | RESET                                           | Digital Input,<br>Internal Pull-up      | Device reset signal.  When LOW, the device will be set to default conditions.                                                                                                                                                       |

| H6                      | BIT20/ <del>BIT10</del>                         | Digital Input,<br>Internal Pull-up      | Control signal input.  Used to select the output bus width.  HIGH = 20-bit, LOW = 10-bit.  Please refer to the Input Logic parameters in Table 2-3: DC Electric Characteristics for logic level threshold and compatibility.        |

| H7                      | <u>cs</u>                                       | Digital Input                           | Chip Select input for the Gennum Serial Peripheral Interface (GSPI) host control/status port. Active-low input. When GSPI is not used, connect CS to IO_VDD.                                                                        |

| J1, J2                  | DDO_VDD                                         | Power                                   | Power pin for the serial digital output $50\Omega$ buffer. Connect to 1.2V 1.8V DC analog.                                                                                                                                          |

| J3                      | PWR_DWN                                         | Digital Input,<br>Internal<br>Pull-down | When HIGH, places the device in a power-down state.                                                                                                                                                                                 |

| J4,<br>K4,<br>J6,<br>K6 | AOUT_1_2,<br>AOUT_3_4,<br>AOUT_5_6,<br>AOUT_7_8 | Output                                  | Serial Audio Outputs. When not in use, leave unconnected.                                                                                                                                                                           |

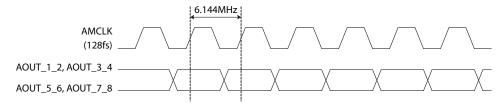

| J5                      | ACLK                                            | Output                                  | 64fs sample clock for audio. When not in use, leave unconnected.                                                                                                                                                                    |

| K1, K2                  | DDO, DDO                                        | Digital Output                          | Differential serial digital outputs. When not in use, leave unconnected.                                                                                                                                                            |

| КЗ                      | AUDIO_EN/ <del>DIS</del>                        | Digital Input,<br>Internal Pull-up      | Control signal input.  When HIGH, enables audio extraction. When LOW, disables audio extraction.  Please refer to the Input Logic parameters in Table 2-3: DC Electric Characteristics for logic level threshold and compatibility. |

| K5                      | AMCLK                                           | Output                                  | Oversampled master clock for audio (128fs, 256fs, 512fs selectable When not in use, leave unconnected.                                                                                                                              |

Rev.9

August 2018

## 2. Electrical Characteristics

# 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                                               | Value                  |

|---------------------------------------------------------|------------------------|

| Supply Voltage, Digital Core (CORE_VDD)                 | -0.3V to +1.5V         |

| Supply Voltage, Digital I/O (IO_VDD)                    | -0.3V to +2.8V         |

| Supply Voltage, Analog 1.2V (PLL_VDD, VCO_VDD, DDI_VDD) | -0.3V to +1.5V         |

| Supply Voltage, Analog 1.8V (DDO_VDD)                   | -0.3V to +2.0V         |

| Input Voltage Range (Digital Inputs)                    | -0.3V to IO_VDD + 0.3V |

| Ambient Operating Temperature (T <sub>A</sub> )         | -20°C to +85°C         |

| Storage Temperature (T <sub>STG</sub> )                 | -50°C to +125°C        |

| Peak Reflow Temperature (JEDEC J-STD-020C)              | 260°C                  |

| ESD Sensitivity, HBM (JESD22-A114)                      | 3kV                    |

**Note:** Absolute Maximum Ratings are those values beyond which damage may occur. Functional operation under these conditions or at any other condition beyond those indicated in the AC/DC Electrical Characteristics sections is not implied.

# 2.2 Recommended Operating Conditions

**Table 2-2: Recommended Operating Conditions**

| Parameter                               | Symbol                | Conditions | Min  | Тур                                                                                                         | Max  | Units |

|-----------------------------------------|-----------------------|------------|------|-------------------------------------------------------------------------------------------------------------|------|-------|

| Operating Temperature Range,<br>Ambient | T <sub>A</sub>        | _          | -20  | _                                                                                                           | +85  | °C    |

| Supply Voltage, Digital Core            | CORE_VDD              | _          | 1.14 | 1.2                                                                                                         | 1.26 | V     |

| Supply Voltage, Digital I/O             | IO VDD                | 1.8V mode  | 1.71 | 1.8                                                                                                         | 1.89 | V     |

| Supply Voltage, Digital I/O             | 10_400                | 2.5V mode  | 2.38 | 2.5                                                                                                         | 2.63 | V     |

| Supply Voltage, PLL                     | PLL_VDD               | _          | 1.14 | 1.2                                                                                                         | 1.26 | V     |

| Supply Voltage, VCO                     | VCO_VDD               | _          | 1.14 | 1.2                                                                                                         | 1.26 | V     |

| Supply Voltage, Serial Digital Input    | DDI0_VDD,<br>DDI1_VDD | _          | 1.14 | 1.2                                                                                                         | 1.26 | V     |

| Supply Voltage, CD Buffer               | DDO VDD               | 1.2V mode  | 1.14 | 1.2                                                                                                         | 1.26 | V     |

| Supply voltage, CD bullet               | DDO_VDD               | 1.8V mode  | 1.71 | 2.5     2.63       1.2     1.26       1.2     1.26       1.2     1.26       1.2     1.26       1.8     1.89 | V    |       |

| Serial Input Data Rate                  |                       | _          | 270  | _                                                                                                           | 2970 | Mb/s  |

# 2.3 DC Electrical Characteristics

**Table 2-3: DC Electrical Characteristics**

$Guaranteed\ over\ recommended\ operating\ conditions\ unless\ otherwise\ noted.$

| Parameter                                                                                                       | Symbol            | Conditions               | Min  | Тур   | Max   | Units                                                                                                                                                                                       | Notes |

|-----------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| System                                                                                                          |                   |                          |      |       |       |                                                                                                                                                                                             |       |

| DDI0_VDD,<br>DDI1_VDD Supply<br>Current                                                                         | I <sub>DDI</sub>  | 1.2V                     | 0.02 | 0.07  | 0.12  | mA                                                                                                                                                                                          | _     |

| IO_VDD Supply                                                                                                   | l <sub>io</sub>   | 1.8V                     | 2.52 | 10.31 | 21.53 | mA                                                                                                                                                                                          | _     |

| Current                                                                                                         | I <sub>IO</sub>   | 2.5V                     | 6.62 | 21.7  | 44.86 | mA                                                                                                                                                                                          | _     |

| DDO_VDD Supply                                                                                                  | I <sub>DDO</sub>  | 1.2V                     | 8.21 | 8.92  | 9.71  | mA                                                                                                                                                                                          | _     |

| Current                                                                                                         | סטטי              | 1.8V                     | 8.30 | 9.05  | 9.85  | mA                                                                                                                                                                                          | _     |

| PLL_VDD Supply<br>Current                                                                                       | I <sub>PLL</sub>  | 1.2V                     | 59.8 | 67.8  | 74.4  | mA                                                                                                                                                                                          | _     |

| CORE_VDD Supply<br>Current                                                                                      | I <sub>CORE</sub> | 1.2V                     | 17.7 | 20.3  | 22.2  | mA                                                                                                                                                                                          | _     |

|                                                                                                                 |                   | 10-bit 3GA               | 160  | 191   | 227   | mW                                                                                                                                                                                          | _     |

|                                                                                                                 | P                 | 10-bit 3GB               | 135  | 158   | 192   | mW                                                                                                                                                                                          | _     |

|                                                                                                                 |                   | 20-bit 3GA               | 137  | 161   | 193   | mW                                                                                                                                                                                          | _     |

| Total Device Power                                                                                              |                   | 20-bit 3GB               | 154  | 184   | 230   | mW                                                                                                                                                                                          | _     |

| DDO_VDD = 1.2V                                                                                                  |                   | 10-bit HD                | 125  | 148   | 179   | mW                                                                                                                                                                                          | _     |

| IO_VDD = 1.8V                                                                                                   | r                 | 20-bit HD                | 109  | 129   | 170   | mA  mA  mA  mA  mA  mA  mA  mA  mW  mW                                                                                                                                                      | _     |

| (Audio Enabled)                                                                                                 |                   | 10/20-bit SD             | 97   | 109   | 141   | mW                                                                                                                                                                                          | _     |

|                                                                                                                 |                   | DVB-ASI                  | _    | 103   | _     | 21.53 mA  44.86 mA  9.71 mA  9.85 mA  74.4 mA  22.2 mA  227 mW  192 mW  193 mW  230 mW  179 mW  170 mW  141 mW  — mW  11.3 mW  121 mW  300 mW  237 mW  241 mW  325 mW  209 mW  164 mW  — mW | _     |

| PLL_VDD Supply Current  CORE_VDD Supply Current  Fotal Device Power DDO_VDD = 1.2V O_VDD = 1.8V  Audio Enabled) |                   | Sleep                    | 3.3  | 5     | 11.3  | mW                                                                                                                                                                                          | _     |

|                                                                                                                 |                   | Standby with DDO Retimed | 82   | 105   | 121   | mA mA mA mA mA mA mA mA mA mW                                                                                                                           | _     |

|                                                                                                                 |                   | 10-bit 3GA               | 275  | 287   | 300   | mW                                                                                                                                                                                          | _     |

|                                                                                                                 |                   | 10-bit 3GB               | 224  | 230   | 237   | mW                                                                                                                                                                                          | _     |

|                                                                                                                 |                   | 20-bit 3GA               | 219  | 228   | 241   | mW                                                                                                                                                                                          | _     |

| Total Device Power                                                                                              |                   | 20-bit 3GB               | 276  | 286   | 325   | mW                                                                                                                                                                                          | _     |

| DDO_VDD = 1.8V                                                                                                  | Р                 | 10-bit HD                | 211  | 218   | 221   | mW                                                                                                                                                                                          | _     |

| IO_VDD = 2.5V                                                                                                   | r                 | 20-bit HD                | 165  | 174   | 209   | mA mA mA mA mA mA mA mA mW                                                                                                                              | _     |

| (Audio Enabled)                                                                                                 |                   | 10/20-bit SD             | 125  | 132   | 164   | mW                                                                                                                                                                                          | _     |

|                                                                                                                 |                   | DVB-ASI                  | _    | 121   | _     | mW                                                                                                                                                                                          | _     |

|                                                                                                                 |                   | Sleep                    | 7.1  | 10.1  | 16.9  | mA mA mA mA mA mA mA mA mW                                                                                                                              | _     |

|                                                                                                                 |                   | Standby with DDO Retimed | 108  | 127   | 163   | mW                                                                                                                                                                                          | _     |

### **Table 2-3: DC Electrical Characteristics (Continued)**

Guaranteed over recommended operating conditions unless otherwise noted.

| Parameter                               | Symbol          | Conditions                            | Min             | Тур                                | Max             | Units | Notes |

|-----------------------------------------|-----------------|---------------------------------------|-----------------|------------------------------------|-----------------|-------|-------|

| Digital I/O                             |                 |                                       |                 |                                    |                 |       |       |

| Input Logic LOW                         | V <sub>IL</sub> | 2.5V or 1.8V operation                | _               | _                                  | 0.3 x<br>IO_VDD | V     | _     |

| Input Logic HIGH                        | V <sub>IH</sub> | 2.5V or 1.8V operation                | 0.7 x<br>IO_VDD | _                                  | _               | V     | _     |

| Output Logic LOW V                      | V <sub>OL</sub> | $I_{OL} = 8mA, 1.8V$ operation        | _               | _                                  | 0.41            | V     | _     |

|                                         | *OL             | I <sub>OL</sub> = 8mA, 2.5V operation | _               | _                                  | 0.29            | V     | _     |

| Output Logic HIGH                       | V <sub>OH</sub> | I <sub>OL</sub> = 8mA,1.8V operation  | 1.49            | _                                  | _               | V     | _     |

| Output Logic High                       |                 | I <sub>OL</sub> = 8mA, 2.5V operation | 2.27            | _                                  | _               | V     | _     |

| Serial Input                            |                 |                                       |                 |                                    |                 |       |       |

| Serial Input Common<br>Mode Voltage     | _               | AC or DC-coupled                      | 0.90            | 0.96                               | 1.06            | V     | _     |

| Serial Output                           |                 |                                       |                 |                                    |                 |       |       |

| Serial Output<br>Common Mode<br>Voltage | _               | 50Ω load                              | _               | DDO_VDD<br>- V <sub>swing</sub> /2 | _               | V     | 1     |

#### Note:

<sup>1.</sup> Serial output swing limited when using DDO\_VDD = 1.2V.

# 2.4 AC Electrical Characteristics

**Table 2-4: AC Electrical Characteristics**

$Guaranteed\ over\ recommended\ operating\ conditions\ unless\ otherwise\ noted.$

| Parameter                | Symbol             | Conditions              | Min | Тур                            | Max | Units | Notes |

|--------------------------|--------------------|-------------------------|-----|--------------------------------|-----|-------|-------|

| System                   |                    |                         |     |                                |     |       |       |

| Device Latency:          |                    | 3G (Level A)            | 65  | 67                             | 69  | PCLK  | _     |

| AUDIO_EN = 1,            |                    | 3G (Level B)            | 141 | 144                            | 147 | PCLK  | _     |

| SMPTE mode,              | _                  | HD                      | 65  | 67                             | 69  | PCLK  | _     |

| IOPROC_EN = 1            |                    | SD                      | 37  | 39                             | 41  | PCLK  | _     |

| Device Latency:          |                    | 3G (Level A)            | 28  | 30                             | 32  | PCLK  | _     |

| AUDIO_EN = 0,            |                    | 3G (Level B)            | 63  | 65                             | 67  | PCLK  | _     |

| SMPTE mode,              | _                  | HD                      | 25  | 27                             | 29  | PCLK  | _     |

| IOPROC_EN = 1            |                    | SD                      | 25  | 27                             | 29  | PCLK  | _     |

| Device Latency:          |                    | 3G (Level A)            | 20  | 22                             | 24  | PCLK  | _     |

| AUDIO_EN = 0,            |                    | 3G (Level B)            | 47  | 50                             | 53  | PCLK  | _     |

| SMPTE mode,              | _                  | HD                      | 21  | 23                             | 25  | PCLK  | _     |

| IOPROC_EN = 0            |                    | SD                      | 19  | 21                             | 23  | PCLK  | _     |

| Device Latency:          |                    | 3G (Level A)            | 11  | 13                             | 15  | PCLK  | _     |

| AUDIO_EN = 0,            |                    | 3G (Level B)            | 11  | 13                             | 15  | PCLK  | _     |

| SMPTE bypass,            | _                  | HD                      | 11  | 13                             | 15  | PCLK  | _     |

| IOPROC_EN = 0            |                    | SD                      | 11  | 13                             | 15  | PCLK  | _     |

| Device Latency: DVB-ASI  | _                  | _                       | 12  | 14                             | 16  | PCLK  | _     |

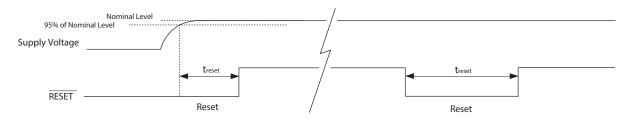

| Reset Time               | t <sub>reset</sub> | _                       | 1   | _                              | _   | ms    | _     |

| Parallel Output          |                    |                         |     |                                |     |       |       |

| Parallel Clock Frequency |                    | 3G/HD (10-bit)          | _   | 148.5<br>or<br>148.5/<br>1.001 | _   | MHz   | _     |

|                          | f <sub>PCLK</sub>  | HD (20-bit), 10-bit DDR | _   | 74.25<br>or<br>74.25/<br>1.001 | _   | MHz   | _     |

|                          |                    | SD (20-bit), 10-bit DDR | _   | 13.5                           | _   | MHz   | _     |

|                          |                    | SD (10-bit)             |     | 27                             |     | MHz   |       |

Rev.9

August 2018

### **Table 2-4: AC Electrical Characteristics (Continued)**

Guaranteed over recommended operating conditions unless otherwise noted.

| Parameter                        | Symbol             | bol Conditions                     |       | Min  | Тур | Max | Units | Notes |

|----------------------------------|--------------------|------------------------------------|-------|------|-----|-----|-------|-------|

| Parallel Clock Duty Cycle        | DC <sub>PCLK</sub> | _                                  |       | _    | 50  | _   | %     | _     |

|                                  |                    | 6pF C                              | SPI   | 1.5  | _   | _   | ns    | _     |

|                                  |                    | 6pF C <sub>load</sub>              | AUDIO | 1.5  | _   | _   | ns    | _     |

|                                  | •                  | 3G 10-bit                          | DOUT  | 0.3  | _   | _   | ns    | _     |

|                                  |                    | 6pF C <sub>load</sub>              | STAT  | 0.3  | _   | _   | ns    | _     |

|                                  | •                  | 3G 20-bit                          | DOUT  | 0.5  | _   | _   | ns    | _     |

|                                  |                    | 6pF C <sub>load</sub>              | STAT  | 0.5  | _   | _   | ns    | _     |

| Outrout Data Hald Time a (1.0)() | <b>.</b>           | HD 10-bit                          | DOUT  | 1.5  | _   | _   | ns    | _     |

| Output Data Hold Time (1.8V)     | t <sub>oh</sub>    | 6pF C <sub>load</sub>              | STAT  | 1.5  | _   | _   | ns    | _     |

|                                  | •                  | HD 20-bit                          | DOUT  | 5.0  | _   | _   | ns    | _     |

|                                  |                    | 6pF C <sub>load</sub>              | STAT  | 5.0  | _   | _   | ns    | _     |

|                                  |                    | SD 10-bit<br>6pF C <sub>load</sub> | DOUT  | 15.0 | _   | _   | ns    | _     |

|                                  |                    |                                    | STAT  | 15.0 | _   | _   | ns    | _     |

|                                  |                    | SD 20-bit<br>6pF C <sub>load</sub> | DOUT  | 30.0 | _   | _   | ns    | _     |

|                                  |                    |                                    | STAT  | 30.0 | _   | _   | ns    | _     |

|                                  |                    | 6nE C                              | SPI   | 1.5  | _   | _   | ns    | _     |

|                                  |                    | 6pF C <sub>load</sub>              | AUDIO | 1.5  | _   | _   | ns    | _     |

|                                  |                    | 3G 10-bit<br>6pF C <sub>load</sub> | DOUT  | 0.3  | _   | _   | ns    | _     |

|                                  |                    |                                    | STAT  | 0.3  | _   | _   | ns    | _     |

|                                  | •                  | 3G 20-bit                          | DOUT  | 0.5  | _   | _   | ns    | _     |

|                                  |                    | 6pF C <sub>load</sub>              | STAT  | 0.5  | _   | _   | ns    | _     |

| Out Details                      |                    | HD 10-bit                          | DOUT  | 1.5  | _   | _   | ns    | _     |

| Output Data Hold Time (2.5V)     | t <sub>oh</sub>    | 6pF C <sub>load</sub>              | STAT  | 1.5  | _   | _   | ns    | _     |

|                                  |                    | HD 20-bit                          | DOUT  | 4.0  | _   | _   | ns    | _     |

|                                  |                    | 6pF C <sub>load</sub>              | STAT  | 4.0  | _   | _   | ns    | _     |

|                                  |                    | SD 10-bit                          | DOUT  | 15.0 | _   | _   | ns    | _     |

|                                  |                    | 6pF C <sub>load</sub>              | STAT  | 15.0 | _   | _   | ns    | _     |

|                                  | -                  | SD 20-bit                          | DOUT  | 30.0 | _   | _   | ns    | _     |

|                                  |                    | 6pF C <sub>load</sub>              | STAT  | 30.0 | _   | _   | ns    | _     |

### **Table 2-4: AC Electrical Characteristics (Continued)**

Guaranteed over recommended operating conditions unless otherwise noted.

| Parameter                         | Symbol Conditions              |                                     | ions  | Min | Тур | Max  | Units | Notes |

|-----------------------------------|--------------------------------|-------------------------------------|-------|-----|-----|------|-------|-------|

|                                   |                                | 15 F.C                              | SPI   | _   | _   | 28.0 | ns    | _     |

|                                   |                                | 15pF C <sub>load</sub> -            | AUDIO | _   | _   | 10.0 | ns    | _     |

|                                   |                                | 3G 10-bit                           | DOUT  | _   | _   | 2.4  | ns    | _     |

|                                   |                                | 15pF C <sub>load</sub>              | STAT  | _   | _   | 2.8  | ns    | _     |

|                                   | •                              | 3G 20-bit                           | DOUT  | _   | _   | 6.0  | ns    | _     |

|                                   |                                | 15pF C <sub>load</sub>              | STAT  | _   | _   | 6.3  | ns    | _     |

| Output Data Dolay Time (1.9V)     | <b>+</b> .                     | HD 10-bit                           | DOUT  | _   | _   | 4.0  | ns    | _     |

| Output Data Delay Time (1.8V)     | t <sub>od</sub>                | 15pF C <sub>load</sub>              | STAT  | _   | _   | 4.2  | ns    | _     |

|                                   | •                              | HD 20-bit                           | DOUT  | _   | _   | 14.2 | ns    | _     |

|                                   |                                | 15pF C <sub>load</sub>              | STAT  | _   | _   | 14.4 | ns    | _     |

|                                   | •                              | SD 10-bit                           | DOUT  | _   | _   | 21.0 | ns    | _     |

|                                   |                                | 15pF C <sub>load</sub>              | STAT  | _   | _   | 21.0 | ns    | _     |

|                                   |                                | SD 20-bit<br>15pF C <sub>load</sub> | DOUT  | _   | _   | 40.0 | ns    | _     |

|                                   |                                |                                     | STAT  | _   | _   | 40.0 | ns    | _     |

|                                   |                                | 15pF C <sub>load</sub>              | SPI   | _   | _   | 28.0 | ns    | _     |

|                                   |                                |                                     | AUDIO | _   | _   | 10.0 | ns    | _     |

|                                   |                                | 3G 10-bit<br>15pF C <sub>load</sub> | DOUT  | _   | _   | 2.3  | ns    | _     |

|                                   |                                |                                     | STAT  | _   | _   | 2.8  | ns    | _     |

|                                   |                                | 3G 20-bit<br>15pF C <sub>load</sub> | DOUT  | _   | _   | 6.0  | ns    | _     |

|                                   |                                |                                     | STAT  | _   | _   | 6.3  | ns    | _     |

| Output Data Delay Time (2.5V)     | + .                            | HD 10-bit                           | DOUT  | _   | _   | 3.8  | ns    | _     |

| Output Data Delay Time (2.5v)     | t <sub>od</sub>                | 15pF C <sub>load</sub>              | STAT  | _   | _   | 4.2  | ns    | _     |

|                                   |                                | HD 20-bit                           | DOUT  | _   | _   | 13.0 | ns    | _     |

|                                   |                                | 15pF C <sub>load</sub>              | STAT  | _   | _   | 13.5 | ns    | _     |

|                                   | •                              | SD 10-bit                           | DOUT  | _   |     | 21.0 | ns    |       |

|                                   |                                | 15pF C <sub>load</sub>              | STAT  | _   | _   | 21.0 | ns    | _     |

|                                   |                                | SD 20-bit                           | DOUT  | _   | _   | 40.0 | ns    | _     |

|                                   |                                | 15pF C <sub>load</sub>              | STAT  | _   |     | 40.0 | ns    |       |

|                                   |                                |                                     | STAT  | _   | _   | 3.1  | ns    |       |

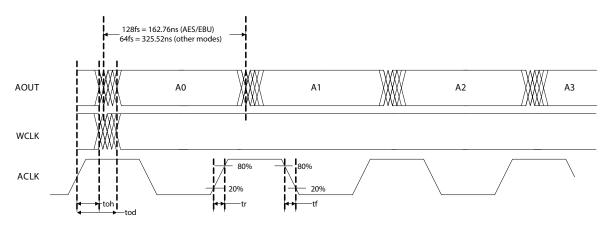

| Output Data Rise/Fall Time (1.8V) | t <sub>r</sub> /t <sub>f</sub> | 6pF C <sub>load</sub>               | DOUT  | _   |     | 3.1  | ns    |       |

|                                   |                                |                                     | AUDIO | _   | _   | 3.3  | ns    | _     |

### **Table 2-4: AC Electrical Characteristics (Continued)**

Guaranteed over recommended operating conditions unless otherwise noted.

| Parameter                            | Symbol                             | Conditions                   |       | Min  | Тур  | Max  | Units            | Notes |

|--------------------------------------|------------------------------------|------------------------------|-------|------|------|------|------------------|-------|

|                                      |                                    |                              | STAT  | _    | _    | 2.1  | ns               | _     |

| Output Data Rise/Fall Time (2.5V)    | t <sub>r</sub> /t <sub>f</sub> 6pl | 6pF C <sub>load</sub>        | DOUT  | _    | _    | 2.1  | ns               | _     |

|                                      |                                    |                              | AUDIO | _    | _    | 2.2  | ns               | _     |

| Serial Digital Input                 |                                    |                              |       |      |      |      |                  |       |

| Serial Input Data Rate               | DR <sub>SDI</sub>                  | _                            |       | 0.27 | _    | 2.97 | Gb/s             | _     |

| Serial Input Swing                   | ΔV <sub>DDI</sub>                  | Differenti<br>100Ω l         |       | 200  | 400  | 1000 | $mV_{ppd}$       | _     |

| Serial Input Jitter Tolerance        | SIJT                               | Nomina<br>bandw<br>Square wa | idth  | 0.8  | _    | _    | UI               | _     |

| Serial Digital Output                |                                    |                              |       |      |      |      |                  |       |

| Serial Output Data Rate              | DR <sub>DDO</sub>                  | _                            |       | 0.27 | _    | 2.97 | Gb/s             | _     |

| Serial Output Swing                  | $\Delta V_{DDO}$                   | Differenti<br>100Ω l         |       | _    | 400  | _    | ${\rm mV_{ppd}}$ | 2,4   |

| Serial Output Rise Time<br>20% ~ 80% | tr <sub>DDO</sub>                  | _                            |       | _    | 112  | 135  | ps               | _     |

| Serial Output Fall Time<br>20% ~ 80% | tf <sub>DDO</sub>                  | _                            |       | _    | 114  | 135  | ps               | _     |

| Rise/ Fall Mismatch                  |                                    | _                            |       | _    | 2    | 8    | ps               | _     |

|                                      |                                    | 3G PR                        | BS    | 0.05 | 0.06 | 0.08 | UI               | 3     |

| Serial Output Intrinsic Jitter       | t <sub>OJ</sub>                    | HD PF                        | RBS   | 0.03 | 0.04 | 0.05 | UI               | 3     |

|                                      | •                                  | SD PR                        | BS    | 0.01 | 0.02 | 0.03 | UI               | 3     |

|                                      |                                    | 3G                           |       | 3    | 5    | 10   | ps               | _     |

| Serial Output Duty Cycle Distortion  | DCD <sub>SDD</sub>                 | HD                           | l     | 1    | 5    | 7    | ps               | _     |

|                                      | •                                  | SD                           |       | 1    | 2    | 5    | ps               | _     |

| Asynchronous Lock Time               | _                                  | _                            |       | _    | _    | 750  | μs               | _     |

| Lock Time from Power-up              | _                                  | After 20 m<br>at -20         |       | _    | 725  | _    | ms               | _     |

#### Notes:

- 1. Serial output swing limited when using DDO\_VDD = 1.2V

- 2. Serial output swing can be adjusted through GSPI.

- 3. Retiming enabled.

- 4. Default setting and typical condition.

Rev.9

August 2018

# 3. Input/Output Circuits

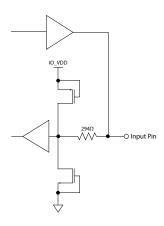

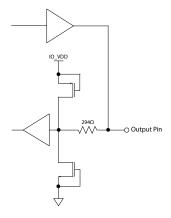

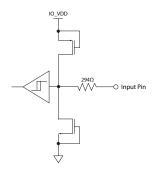

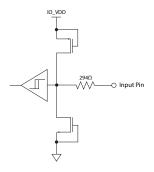

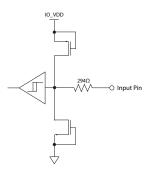

Figure 3-1: Bidirectional Digital Input/Output Pin Configured as an Input (SDIN, CS, SCLK)

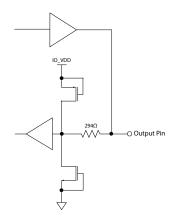

Figure 3-3: Bidirectional Digital Input/Output Pin Configured as an Output with Programmable Drive Strength (DOUT[19:0], PCLK, STAT[5:0])

Figure 3-5: Digital Input with Schmitt Trigger and  $100k\Omega$  Internal Pull-Down (TRST, JTAG\_EN/DIS, PWR\_DWN)

Figure 3-2: Bidirectional Digital Input/Output Pin Configured as an Output (AMCLK, TDO, SDOUT, WCLK, AOUT\_1\_2, AOUT\_3\_4, AOUT\_5\_6, AOUT\_7\_8, ACLK)

Figure 3-4: Digital Input with Schmitt Trigger and  $100k\Omega$  Internal Pull-Up (AUDIO\_EN/DIS, TDI, TMS, RESET, BIT20/BIT10)

Figure 3-6: Digital Input with Schmitt Trigger (TCK)

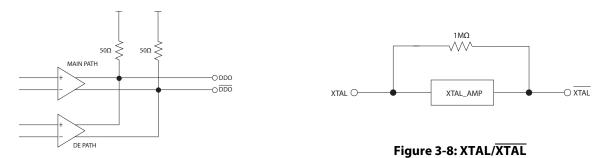

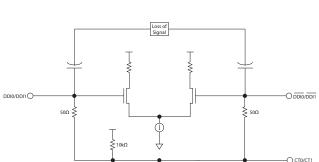

Figure 3-7: DDO/DDO

Figure 3-9: DDI0/DDI0, DDI1/DDI1, CT[1:0]

Figure 3-10: LF

Figure 3-11: RBIAS

# 4. Detailed Description

### **4.1 Functional Overview**

The GS3470 includes a dual serial digital input buffer with 2x2 MUX, an integrated retimer, serial data loop through output, robust serial-to-parallel conversion, integrated SMPTE video processing, and additional processing functions such as audio extraction, ancillary data extraction, EDH support, and DVB-ASI decoding.

The serial digital input buffer with 2x2 MUX offers a lot of flexibility for use in default and various Power-down modes.

Figure 4-1: Flexible Input Loopback

Expanded and configurable Power-down modes offer increased flexibility by selectively enabling or disabling key features (such as CSR access, PCLK, retimed DDO loop-through output, and non-retimed DDO loop-through output). Figure 4-2 show the various Power-down modes.

Figure 4-2: Flexible Power Down Modes

The device has three other primary modes of operation which include SMPTE mode, DVB-ASI mode, and Data-Through mode. In SMPTE mode, when receiving a SMPTE compliant SDI input, the GS3470 performs full SMPTE processing, and features a number of data integrity checks and measurement capabilities. The device also supports ancillary data extraction, and can provide up to 1024 x 16-bit ancillary data words through host-accessible registers. Packet detection and error handling features are also offered. All processing features are optional, and may be individually enabled or disabled through register programming. In DVB-ASI mode, sync word detection, alignment, and 8/10bit decoding is applied to the received data stream. While in Data-Through mode, all forms of SMPTE and DVB-ASI processing are disabled, and the device can be used as a simple serial to parallel converter.

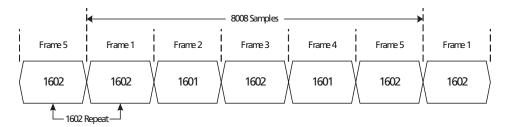

The GS3470 includes an audio de-embedder and audio clocks are internally generated. Up to eight channels (two audio groups) of serial digital audio may be extracted from the video data stream, in accordance with SMPTE ST 272-C and SMPTE ST 299. The output audio formats supported by the device include AES/EBU and I<sup>2</sup>S. A variety of audio processing features are provided to ease implementation.

Rev.9

August 2018

# 4.2 Device Power-Up

The GS3470 is designed to operate in a multi-voltage environment which allows any power-up sequence to be used. Supply pins can all be powered up in any order.

#### 4.2.1 Power-Down Mode

The *PWR\_DWN* pin reduces power to a minimum by disabling various device features. When the *PWR\_DWN* pin is de-asserted, the device returns to its previous operating condition within 1 second, without requiring input from the host interface. There are several power-down options which can be configured through GSPI prior to the device going into power-down. Table 4-1 provides a summary of the supported power-down options by accessing the **POWER\_DOWN** register.

**Table 4-1: Power-down Mode**

| Power-down Mode                                                                                    | CSR<br>Access | DDO<br>Loop-through<br>Mode | PCLK Mode        |

|----------------------------------------------------------------------------------------------------|---------------|-----------------------------|------------------|

| Power-down  PD_PCLK_ENABLE = 0  SERIAL_LOOPBACK_EN = 0  PD_CSR_ACCESS = 0  RC_BYP = X              | No            | DDO Disabled                | PCLK<br>Disabled |

| Power-down with CSR Access PD_PCLK_ENABLE = 0 SERIAL_LOOPBACK_EN = 0 PD_CSR_ACCESS = 1 RC_BYP = X  | Yes           | DDO Disabled                | PCLK<br>Disabled |

| Power-down with PCLK  PD_PCLK_ENABLE = 1  SERIAL_LOOPBACK_EN = 0  PD_CSR_ACCESS = X  RC_BYP = X    | Yes           | DDO Disabled                | PCLK Enabled     |

| Power-down with DDO  PD_PCLK_ENABLE = 0  SERIAL_LOOPBACK_EN = 1  PD_CSR_ACCESS = X  RC_BYP = 1     | No            | DDO Enabled<br>Non-retimed  | PCLK<br>Disabled |

| Power-down with DDO retimed PD_PCLK_ENABLE = 0 SERIAL_LOOPBACK_EN = 1 PD_CSR_ACCESS = X RC_BYP = 0 | Yes           | DDO Enabled<br>Retimed      | PCLK<br>Disabled |

**Table 4-1: Power-down Mode (Continued)**

| Power-down Mode                                                                                             | CSR<br>Access | DDO<br>Loop-through<br>Mode | PCLK Mode    |

|-------------------------------------------------------------------------------------------------------------|---------------|-----------------------------|--------------|

| Power-down with DDO/PCLK PD_PCLK_ENABLE = 1 SERIAL_LOOPBACK_EN = 1 PD_CSR_ACCESS = X RC_BYP = 1             | Yes           | DDO Enabled<br>Non-retimed  | PCLK Enabled |

| Power-down with DDO/PCLK retimed  PD_PCLK_ENABLE = 1  SERIAL_LOOPBACK_EN = 1  PD_CSR_ACCESS = X  RC_BYP = 0 | Yes           | DDO Enabled<br>Retimed      | PCLK Enabled |

**Table 4-2: Status Output Support in Power Down Modes**

| Mode                             | Rate Detect                                              | Carrier Detect     | Lock                                       | All Other Status<br>Outputs |

|----------------------------------|----------------------------------------------------------|--------------------|--------------------------------------------|-----------------------------|

| Power-down                       | N/A                                                      | N/A                | N/A                                        | N/A                         |

| Power-down with DDO              | N/A                                                      | N/A                | N/A                                        | N/A                         |

| Power-down with DDO retimed      | Available in<br>automatic or<br>manual modes             | Analog detect only | Locked status available<br>on STAT outputs | N/A                         |

| Power-down with PCLK             | Available in<br>manual mode<br>only, rate must<br>be set | Analog detect only | N/A                                        | N/A                         |

| Power-down with DDO/PCLK retimed | Available in<br>automatic or<br>manual modes             | Analog detect only | Locked status available<br>on STAT outputs | N/A                         |

| Power-down with DDO/PCLK         | Available in<br>manual mode<br>only, rate must<br>be set | Analog detect only | N/A                                        | N/A                         |

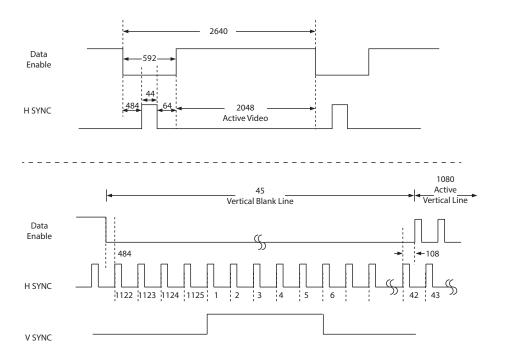

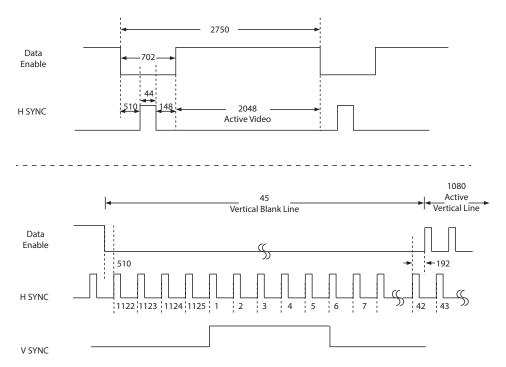

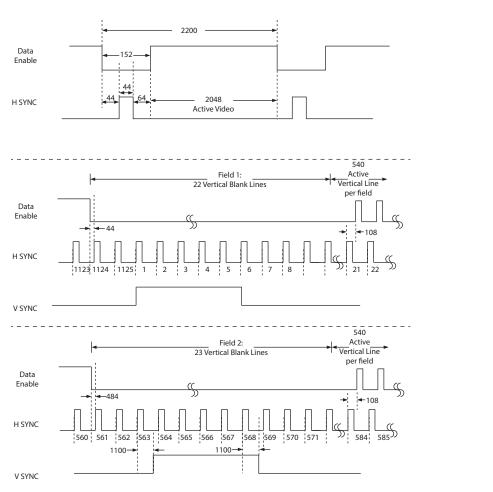

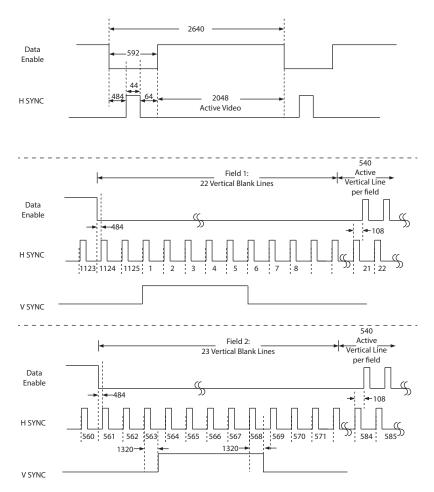

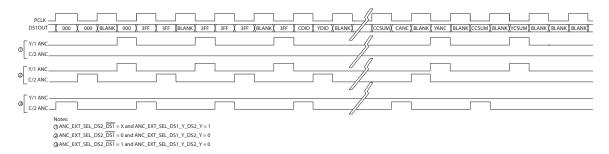

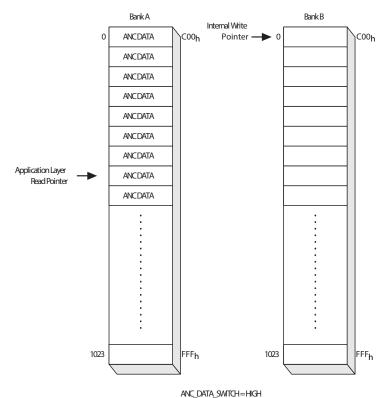

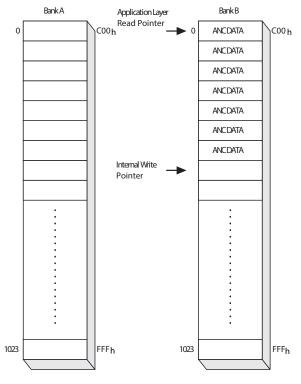

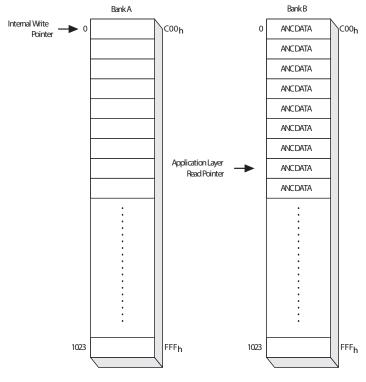

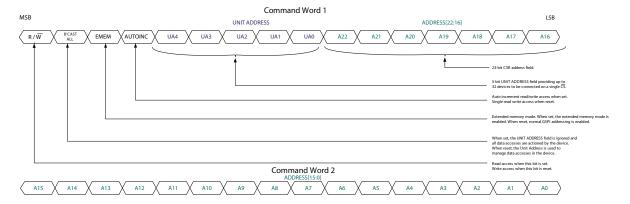

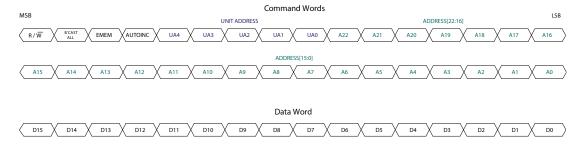

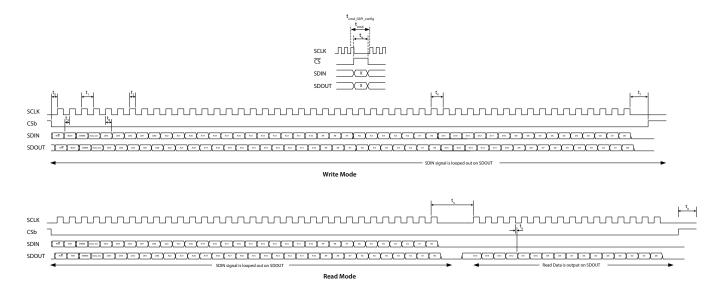

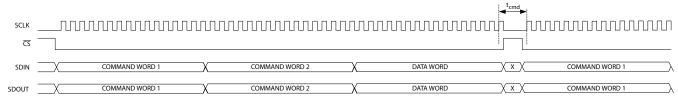

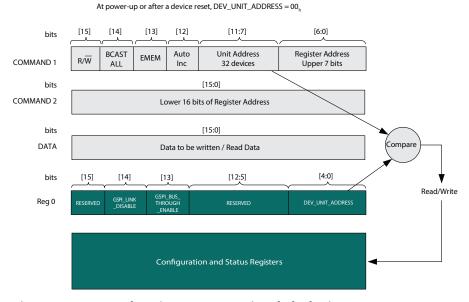

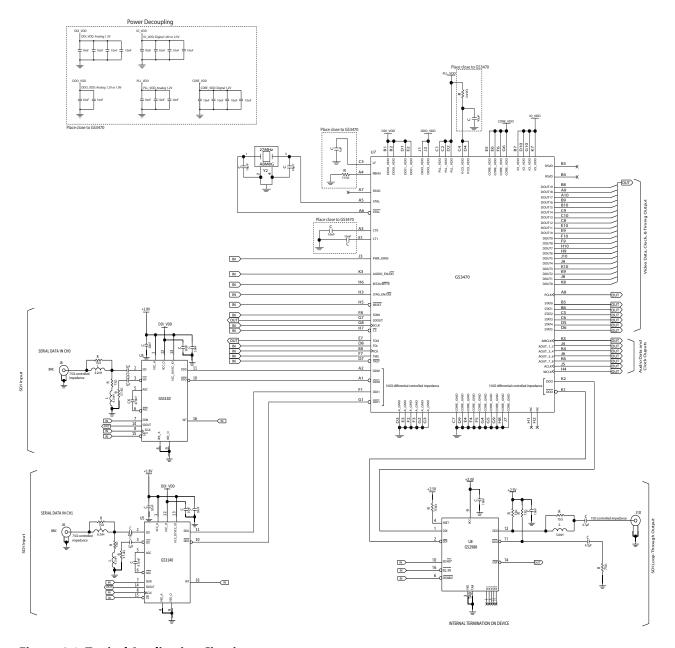

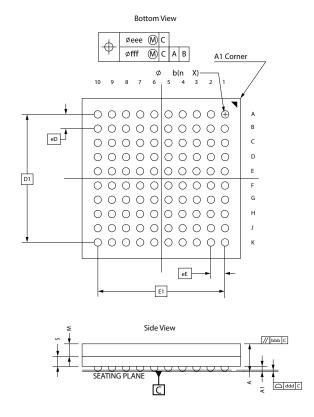

| Power-down with CSR access       | N/A                                                      | Analog detect only | N/A                                        | N/A                         |