# PD82000 Datasheet RPF DPU Controller

Power Matters.\*

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com

www.microsemi.com

© 2015–2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

# **Contents**

| 1 |        | ion History                                                      |     |

|---|--------|------------------------------------------------------------------|-----|

|   | 1.1    | Revision 1.1                                                     |     |

|   | 1.2    | Revision 1.0                                                     |     |

|   | 1.3    | Revision 0.3                                                     |     |

|   | 1.4    | Revision 0.1                                                     | 1   |

| 2 | Overv  | riew                                                             | . 2 |

|   | 2.1    | Features and Benefits                                            | 2   |

| 3 | Functi | ional Descriptions                                               | . 3 |

|   | 3.1    | Signaling                                                        |     |

|   | 3.2    | Interrupt Outputs                                                |     |

|   |        | 3.2.1 IRQ_OUT_PSE                                                | 3   |

|   |        | 3.2.2 IRQ_OUT_DPL                                                |     |

|   | 3.3    | Port Status Indications                                          |     |

|   |        | 3.3.1 Power-Good Status (PGS) <address 0x62=""></address>        |     |

|   |        | 3.3.3 Battery Operation Status (BTS) <address 0x66=""></address> |     |

|   |        | 3.3.4 LPM Status (LPS) <address 0x6e=""></address>               |     |

|   | 3.4    | Power Sharing                                                    |     |

|   | 3.5    | I <sup>2</sup> C Communication                                   | 5   |

| 4 | Electr | ical Specifications                                              | . 6 |

|   | 4.1    | Absolute Maximum Ratings                                         | 6   |

|   | 4.2    | PD82000 Electrical Characteristics                               | 6   |

| 5 | Pin De | escriptions                                                      | . 8 |

|   | 5.1    | Pin Diagram                                                      | 8   |

|   | 5.2    | Pins by Function                                                 |     |

| 6 | Packa  | age Information                                                  | 14  |

|   | 6.1    | Package Drawing                                                  |     |

|   | 6.2    | Thermal Specifications                                           |     |

| 7 | Order  | ing Information                                                  | 18  |

# **Figures**

| Figure 1 | PD82000 Pin Diagram                                  | . 8 |

|----------|------------------------------------------------------|-----|

|          | Package Drawing                                      |     |

|          | Recommended PCB Layout for 64-Pin LQFP 10 mm × 10 mm |     |

| Figure 4 | Classification Reflow Profile                        | 16  |

|          | PD82000 Label                                        |     |

# **Tables**

| Table 1  | Signaling Definition                                        | . 3 |

|----------|-------------------------------------------------------------|-----|

| Table 2  | PD82000 status events (IRQ Outputs)                         |     |

| Table 3  | PD82000 Status Events (registers)                           |     |

| Table 4  | I <sup>2</sup> C Address Selection                          |     |

| Table 5  | Limiting Values                                             |     |

| Table 6  | PD82000 Electrical Characteristics                          |     |

| Table 7  | PD82000 Pin Descriptions                                    | . 8 |

| Table 8  | Dimensions (mm are the original dimensions)                 |     |

| Table 9  | Thermal Characteristics                                     | 15  |

| Table 10 | Classification Reflow Profiles                              | 15  |

| Table 11 | SnPb Eutectic Process: Classification Temperature           | 16  |

| Table 12 | Pb-Free Process: Package Classification Reflow Temperatures | 16  |

| Table 13 | Ordering Information                                        | 18  |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

#### 1.1 **Revision 1.1**

LPS address corrected from 0x40 to 0x6E. Status events table changed to IRQ pins and registers tables. Pin 51 name updated from ADC5 IN to I2C ADDR. Additional information added to pin descriptions.

#### 1.2 **Revision 1.0**

Application information section added. Pin description, absolute maximum rating, electrical characteristics, and PD82000 labels updated.

#### 1.3 **Revision 0.3**

PCB layout recommendation, supply current, and pin description table/pin configuration updated.

#### 1.4 Revision 0.1

Revision 0.1 was the first publication of this document.

## 2 Overview

Microsemi's Reverse Power Feeding (RPF) chip set is used to allow Customer Premises Equipment (CPE) devices and Distribution Point Unit (DPU) to share and deliver power and data over the same cable.

Microsemi's RPF DPU Controller, PD82000, is a cost-effective, pre-programmed MCU designed to support monitoring and control of the RPF functions, and implement the RPF macros as defined in ETSI TS 101 548. The RPF DPU Controller in conjunction with Microsemi's PD ICs (PD70x01/PD81x0), supports safe power feeding, port disconnection in case of an error condition, DPU host communication for line status telemetry, multi-line FairPower™ sharing with battery backup support, and monitor and report of error fault conditions.

PD82000 utilizes an NXP microcontroller with Microsemi's Intellectual Property (IP) firmware, which provides features flexibility and scalability to support multi-lines DPU applications.

PD82000 is available in a 64-pin, 10 mm x 10 mm LQFP package.

#### 2.1 Features and Benefits

- I<sup>2</sup>C communication with DPU host up to 400 kHz

- Up to 16 lines FairPower sharing

- · Per line current measurement

- Output voltage monitoring

- Supports Power Good Status (PGS) and DPU Dying Gasp (DDG) IRQ signals to host

- Supports ACM/BAT/DGL signaling detection from PSE and indication to host DPU

- Per line cable disconnect detection

- Supports Low Power Mode (LPM) to save PSE battery power

- Internal power on reset

- Internal Flash

- Software download by I<sup>2</sup>C

- Programmable non-volatile parameters

- Wide ambient temperature range:

–40 °C to 85 °C

- MSL1, RoHS-compliant

# 3 Functional Descriptions

The following sections describe the functional aspects of the PD82000 device.

### 3.1 Signaling

Microsemi's RPF-DPU reference design supports detection of signaling generated by PSE and indications to the DPU host using I2C communication. The signaling pulses represents specific indications as defined by the ETSI TS 101 548 standard and summarized in the following table.

Table 1 • Signaling Definition

| Signal Name | Full Name       | Description                                                             |

|-------------|-----------------|-------------------------------------------------------------------------|

| DGL         | Dying Gasp Loss | PSE lost power dying gasp indication                                    |

| BAT         | Battery         | Operation on battery indication                                         |

| ACM         | AC Mains        | Operation on mains power and no PSE battery backup available indication |

Signaling is performed by modulation of the RPF voltage and detection by PD82000 through PGn inputs pins.

## 3.2 Interrupt Outputs

The PD82000 supports two interrupt signals to the DPU host, IRQ\_OUT\_PSE and IRQ\_OUT\_DPL.

#### 3.2.1 IRQ OUT PSE

PD82000 asserts this interrupt when it detects a PSE port status event from one or more DPU PD ports.

PD82000 supports detection and indication of the following port status events.

- PD Power Good—PD powered-up successfully by the PSE and receives power

- Port Disconnection—the port lost power as a result of a disconnection event (port cable unplugged or PSE port disabled) between the PSE port (U-R2P) and DPU input port (U-O)

- PSE Dying Gasp Loss (DGL)—the PSE lost both AC mains power and battery power (if available)

- PSE AC mains operation (ACM)—the PSE operates on mains power

- PSE Battery operation (BAT)— the PSE operates on backup battery

The indications of the port(s) that caused the interrupt are indicated in the IRQ\_OUT register (address 0x00). Once the host received IRQ\_OUT\_PSE, it can access the status registers to get the IRQ cause. The IRQ is cleared once the host reads IRQ\_OUT register.

## 3.2.2 IRQ\_OUT\_DPL

PD82000 asserts this interrupt when the DPU has no RPF source available (for instance, when the last DPU port lost power) so the DPU will shut-down after its energy-bank has run out.

## 3.3 Port Status Indications

PD82000's port status indication registers consist of 16 bits per port, and are utilized to indicate each port status independently. PD82000 asserts the IRQ\_OUT\_PSE interrupt to the host right after an update of one or more port status registers.

## 3.3.1 Power-Good Status (PGS) <address 0x62>

Power-Good bit indication is per port (16 bits total). PD82000 asserts bit "n" (PGS[n]) high when it gets a high signal level on PGn input pin.

PSE signaling pulses (ACM/BAT/DGL) over the power-good signal do not affect the PGS register during transmission. PD82000 de-asserts PGS[n] after receiving one of the following indications on PGn input pin.

- DGL signal—after receiving DGL signal, the PGn pin input may remain high until PSE energy bank is discharged. However, PD82000 de-asserts PGS[n] right after receiving the DGL indication and does not wait for complete discharge of the PSE energy bank.

- Port disconnection—port cable unplug event or PSE port disable leads to immediate loss of powergood signal at PGn input pin so that PGS[n] bit is de-asserted.

PD82000 updates counter registers to provide statistics of the power-loss reasons previously described.

#### 3.3.2 Dying-Gasp status (DGS) <address 0x02>

Dying gasp indication per port (16 bits total).

PD82000 asserts DGS[n] after receiving DGL (Dying-Gasp loss) signalling pulse from port n's PSE unit.

#### 3.3.3 Battery Operation Status (BTS) <address 0x66>

Battery operation status indication is per port (16 bits total). This status register indicates whether or not PSE operates from backup battery. PD82000 asserts the BTS[n] bit after BAT signaling is received from PSE or a command from the DPU host is received through I2C communication.

#### 3.3.4 LPM Status (LPS) <address 0x6E>

The PD82000 supports PSE battery power-saving by excluding ports that operate on backup-battery from power sharing, when it possible (i.e. when the ports operates from AC mains has enough accumulated power budget to provides DPU power demand)

Ports that excluded from power sharing, referred to be operated in Low Power Mode (LPM). These ports should keep minimum power signature to holds PSE power on state.

When ports granted a LPM operation, PD82000 sends control signal ("FB\_DOWN") through Latch\_data pins to disable the corresponding DC/DC modules.

The following tables summarize PD82000 status event previously described where H is VDD, L is GND, 1 is bit H and 0 is bit L, X is "don't care" and X|Y is X or Y.

Table 2 • PD82000 status events (IRQ Outputs)

|                 | IRQ_OUT_PSE (pin 62) |      | IRQ_OUT_DPL | (pin 36)         |

|-----------------|----------------------|------|-------------|------------------|

| Event           | Previous             | Next | Previous    | Next             |

| PD power good   | X                    | L    | Н           | Н                |

| Port disconnect | Х                    | L    | Н           | HJL <sup>1</sup> |

| DGL             | X                    | L    | Н           | HJL <sup>1</sup> |

| BAT             | X                    | L    | Н           | Н                |

| ACM             | Х                    | L    | Н           | Н                |

<sup>1.</sup> IRQ\_OUT\_DPL is low if the last port disconnected.

Table 3 • PD82000 Status Events (registers)

|                 | IRQ_OUT<br>(Reg 0x00) |      | PGS<br>(Reg 0x62) |      | DGS<br>(Reg 0x02) |      | BTS<br>(Reg 0x66) |      | LPS<br>(0x6E) |                  |

|-----------------|-----------------------|------|-------------------|------|-------------------|------|-------------------|------|---------------|------------------|

| Event           | Previous              | Next | Previous          | Next | Previous          | Next | Previous          | Next | Previous      | Next             |

| PD power good   | Χ                     | 1    | 0                 | 1    | 0                 | 0    | Х                 | 0    | 0             | 0                |

| Port disconnect | Х                     | 1    | 1                 | 0    | 0                 | 0    | Х                 | 0    | Х             | 0                |

| DGL             | Х                     | 1    | 1                 | 0    | 0                 | 1    | Х                 | 0    | Х             | 0                |

| BAT             | Х                     | 1    | 1                 | 1    | 0                 | 0    | Х                 | 1    | Х             | 1 0 <sup>1</sup> |

| ACM             | Х                     | 1    | 1                 | 1    | 0                 | 0    | Х                 | 0    | Х             | 0                |

1. LPM status equals 1 if the ports operating from AC mains are able to provide DPU power while all ports operate from battery in LPM mode.

## 3.4 Power Sharing

The PD82000 supports FairPower sharing up to 16 ports. For more details about current sharing implementation with PD82000, refer to application note PD82000\_AN\_221.

# 3.5 I<sup>2</sup>C Communication

I<sup>2</sup>C interface between Host CPU and PD82000 controller requires setting PD82000 address. this is done by applying a specific voltage level to pin I2C\_ADDR (#51) as shown in Table 8. PD82000 supports clock stretching. I<sup>2</sup>C bus rate range 100k- 400kHz. For more information refer to PD82000 user guide.

Table 4 • I<sup>2</sup>C Address Selection

| I <sup>2</sup> C Address (hex) | Valid Voltage Range (V <sub>DC</sub> ) | Pull-Down to DGND (KΩ) | Pull-Up to 3.3 V (KΩ) |

|--------------------------------|----------------------------------------|------------------------|-----------------------|

| 0x02                           | 0.00 to 0.21                           | 10                     | N.C                   |

| 0x04                           | 0.21 to 0.41                           | 10                     | 97.6                  |

| 0x08                           | 0.41 to 0.62                           | 10                     | 53.6                  |

| 0x0c                           | 0.62 to 0.83                           | 10                     | 35.7                  |

| 0x10                           | 0.83 to 1.03                           | 10                     | 25.5                  |

| 0x14                           | 1.03 to 1.24                           | 10                     | 19.1                  |

| 0x18                           | 1.24 to 1.44                           | 10                     | 14.7                  |

| 0x1c                           | 1.44 to 1.65                           | 10                     | 11.3                  |

| 0x20                           | 1.65 to 1.86                           | 10                     | 8.87                  |

| 0x24                           | 1.86 to 2.06                           | 10                     | 6.81                  |

| 0x28                           | 2.06 to 2.27                           | 10                     | 5.23                  |

| 0x2c                           | 2.27 to 2.48                           | 10                     | 3.92                  |

| 0x30                           | 2.48 to 2.68                           | 10                     | 2.8                   |

| 0x34                           | 2.68 to 2.89                           | 10                     | 1.87                  |

| 0x38                           | 2.89 to 3.09                           | 10                     | 1.02                  |

| 0x3c                           | 3.09 to 3.30                           | 10                     | 0.324                 |

# 4 Electrical Specifications

This section provides the electrical specifications for the PD82000 device.

## 4.1 Absolute Maximum Ratings

This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to GND unless otherwise noted.

Table 5 • Limiting Values

| PIN                                        | Min  | Max | Units |

|--------------------------------------------|------|-----|-------|

| VDD, VDD (I/O)                             | -0.5 | 3.6 | V     |

| VI (on all digital pins)                   | -0.5 | 3.6 | V     |

| I <sup>2</sup> C_SCL, I <sup>2</sup> C_SDA | 0    | 5.5 | V     |

| Junction temperature (TJ)                  |      | 150 | °C    |

| Lead soldering temperature (40 s, reflow)  |      | 260 | °C    |

| Storage temperature (TS)                   | -65  | 150 | °C    |

| ESD rating—HBM (all pins)                  | -8   | 8   | kV    |

### 4.2 PD82000 Electrical Characteristics

Unless otherwise specified under conditions, the minimum and maxim um ratings stated below apply over the entire specified operating ratings of the device.

Table 6 • PD82000 Electrical Characteristics

| Symbol                                 | Parameter                 | Conditions                             | Min                        | Тур | Max                      | Units |

|----------------------------------------|---------------------------|----------------------------------------|----------------------------|-----|--------------------------|-------|

| V <sub>DD</sub> , V <sub>DD(I/O)</sub> | Supply<br>voltage         |                                        | 3                          |     | 3.6                      | V     |

| I <sub>DD</sub>                        | Supply current            |                                        |                            | 25  |                          | mA    |

| V <sub>I</sub>                         | Input voltage             | Digital pin                            | 0                          |     | V <sub>DD(I/O)</sub>     |       |

| V <sub>IL</sub>                        | Low-level input voltage   | Digital pin/I <sup>2</sup> C bus       |                            |     | 0.3 V <sub>DD(I/O)</sub> | V     |

| V <sub>IH</sub>                        | High-level input voltage  | Digital pin/ I <sup>2</sup> C Bus      | 0.7 V <sub>DD(I/O)</sub>   |     |                          | V     |

| V <sub>OL</sub>                        | Low-level output voltage  | I <sub>OL</sub> = 2 mA                 |                            |     | 0.4                      | V     |

| V <sub>OH</sub>                        | High-level output voltage | I <sub>OH</sub> = 2 mA                 | V <sub>DD(I/O)</sub> – 0.4 |     |                          | V     |

| I <sub>OL</sub>                        | Low-level output current  | V <sub>OL</sub> = 0.4 V                | 2                          |     |                          | mA    |

| I <sub>OH</sub>                        | High-level output current | $V_{OH} = V_{DD(I/O)} - 0.4 \text{ V}$ | -2                         |     |                          | mA    |

Table 6 • PD82000 Electrical Characteristics (continued)

| Symbol               | Parameter                                     | Conditions            | Min | Тур | Max            | Units |

|----------------------|-----------------------------------------------|-----------------------|-----|-----|----------------|-------|

| I <sub>OLS</sub>     | Low-level<br>short-circuit<br>output current  | $V_{OL} = V_{DD}$     |     |     | 50             | mA    |

| I <sub>OHS</sub>     | High-level<br>short-circuit<br>output current | V <sub>OH</sub> = 0 V |     |     | <del></del> 45 | mA    |

| I <sub>PULL-UP</sub> | Pull-up current                               | V <sub>I</sub> = 0 V  | -50 | -80 | -100           | μΑ    |

| F <sub>CLK</sub>     | Internal clock frequency                      |                       |     | 48  |                | MHz   |

# **5** Pin Descriptions

The PD82000 device has 64 pins, which are described in this section.

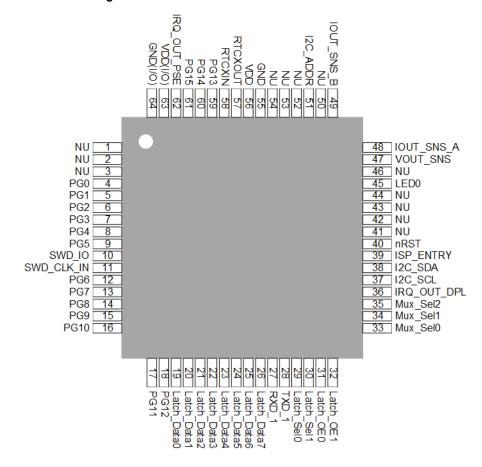

# 5.1 Pin Diagram

The following illustration is a representation of the PD82000 device, as seen from the top view.

Figure 1 • PD82000 Pin Diagram

# 5.2 Pins by Function

The following table shows the functional pin descriptions for the PD82000 device.

Table 7 • PD82000 Pin Descriptions

| Pin Number | Pin Designator | Pin Type | Pin Description          |

|------------|----------------|----------|--------------------------|

| 1          | NU             |          | Not used. Do not connect |

| 2          | NU             |          | externally.              |

| 3          | NU             |          |                          |

Table 7 • PD82000 Pin Descriptions (continued)

| Pin Number | Pin Designator | Pin Type | Pin Description                                                                                                                                                                                                                                                      |

|------------|----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4          | PG0            | IRQ_IN   | Positive-logic power good input                                                                                                                                                                                                                                      |

| 5          | PG1            | IRQ_IN   | signal. PG input capacitance (external) should be lower than                                                                                                                                                                                                         |

| 6          | PG2            | IRQ_IN   | 220 pF.                                                                                                                                                                                                                                                              |

| 7          | PG3            | IRQ_IN   |                                                                                                                                                                                                                                                                      |

| 8          | PG4            | IRQ_IN   |                                                                                                                                                                                                                                                                      |

| 9          | PG5            | IRQ_IN   |                                                                                                                                                                                                                                                                      |

| 10         | SWD_IO         | DEBUG    | Serial wire debug I/O—not used. Connect to 10k $\Omega$ pull-up resistor externally.                                                                                                                                                                                 |

| 11         | SWD_CLK_IN     | DEBUG    | Serial wire clock—not used. Connect to 10k $\Omega$ pull-down resistor externally.                                                                                                                                                                                   |

| 12         | PG6            | IRQ_IN   | Positive-logic power good input                                                                                                                                                                                                                                      |

| 13         | PG7            | IRQ_IN   | signal. PG input capacitance (external) should be lower than                                                                                                                                                                                                         |

| 14         | PG8            | IRQ_IN   | 220 pF.                                                                                                                                                                                                                                                              |

| 15         | PG9            | IRQ_IN   |                                                                                                                                                                                                                                                                      |

| 16         | PG10           | IRQ_IN   |                                                                                                                                                                                                                                                                      |

| 17         | PG11           | IRQ_IN   |                                                                                                                                                                                                                                                                      |

| 18         | PG12           | IRQ_IN   |                                                                                                                                                                                                                                                                      |

| 19         | Latch_Data0    | OUT      | On/off control signal (per channel,                                                                                                                                                                                                                                  |

| 20         | Latch_Data1    | OUT      | internal pull-up) to disable DC/DC PWM switching when channel is                                                                                                                                                                                                     |

| 21         | Latch_Data2    | OUT      | operated in Low Power Mode                                                                                                                                                                                                                                           |

| 22         | Latch_Data3    | OUT      | (LPM)In a multi-port DPU system (up to 8                                                                                                                                                                                                                             |

| 23         | Latch_Data4    | OUT      | ports) these pins should connect to                                                                                                                                                                                                                                  |

| 24         | Latch_Data5    | OUT      | the data inputs of a single octal D                                                                                                                                                                                                                                  |

| 25         | Latch_Data6    | OUT      | ——— flip-flop latch. In a 16-port DPU system, these                                                                                                                                                                                                                  |

| 26         | Latch_Data7    | OUT      | pins should connect to data inputs of two octal D flip-flop latches. The first latch (Latch 0) is used to control ports 0–7, and second latch (Latch 1) is used to control ports 8–15.  In a 1-port DPU system, these pins are not used (do not connect externally). |

| 27         | RXD_1          | IN       | Reserved. Do not connect externally.                                                                                                                                                                                                                                 |

| 28         | TXD_1          | OUT      | Reserved. Do not connect externally.                                                                                                                                                                                                                                 |

| 29         | Latch_Sel0     | OUT      | Latch CLK signal (internal pull-up). Latch_Sel0 should be connected to clock pulse input of ports 0–7 latch (Latch 0). Used to control ports 0–7.                                                                                                                    |

Table 7 • PD82000 Pin Descriptions (continued)

| Pin Number | Pin Designator       | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|----------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30         | Latch_Sel1           | OUT      | Latch CLK signal (internal pull-up). Latch_Sel1 should be connected to clock pulse input of ports 8–15 latch (Latch 1). Used to control ports 8– 15 in a16-port DPU application. In a DPU system with 8 ports or less, this pin is not used and should not be connected externally.                                                                                                                                                                                                                                                                                                                       |

| 31         | Latch_OE0            | OUT      | Output-enable signal to latch0 (internal pull-up). Latch_OE0 should be connected to negative-logic latch output-enable input. Used to control ports 0–7.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 32         | Latch_OE1            | OUT      | Output-enable signal to latch1 (internal pull-up). Latch_OE1 should be connected to negative- logic latch output-enable input. Used to control ports 8–15 in a16- port DPU application. In a DPU system with 8 ports or less, this pin is not used and should not be connected externally.                                                                                                                                                                                                                                                                                                                |

| 33         | Mux_Sel0             | OUT      | Channel selection for current sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 34 35      | Mux_Sel1  Mux_Sel2   | OUT      | MUX (internal pull-up). Should be connected to 3 digital select input of 8-channel analog MUX(s). In a 16-port DPU application, use two analog multiplexers (8 channels each). The first MUX (MUX_A) is used to sense current of ports 0–7. MUX_A common output should be connected to IOUT_SNS_A input (pin 48). The second MUX (MUX_B) used to sense current of ports 8–15. MUX_B common output should be connected to IOUT_SNS_B input (pin 49). In a multiport DPU with 8 ports or less, use only MUX_A. In a 1-port DPU application, these pins are not used and should not be connected externally. |

| 36         | IRQ_OUT_DPL          | OUT      | DPU power loss interrupt output (active low with internal pull-up). DPL IRQ asserted when the last PD channel disconnected to indicate DPU system has no available RPF source left.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 37         | I <sup>2</sup> C_SCL | IN       | Host I <sup>2</sup> C clock. Connect external pull-up resistor between this pin and VDD (10k $\Omega$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 7 • PD82000 Pin Descriptions (continued)

| Pin Number | Pin Designator       | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|----------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38         | I <sup>2</sup> C_SDA | IN/OUT   | Host $I^2C$ data.Connect external pull-up resistor between this pin and VDD (10k $\Omega$ ).                                                                                                                                                                                                                                                                                                                                                                                                         |

| 39         | ISP_ENTRY            | IN       | Not used. Connect to 100k $\Omega$ pullup resistor externally.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 40         | nRST                 | IN       | External reset (active low, internal weak pull-up). Minimum reset pulse width is 200 ns.  The reset pin can be connected to open-drain or push-pull driver output.  If the reset source is from opendrain output, then external pull-up resistor (10k) is recommended.  If the reset source is from a push-pull driver output, then a serial resistor between driver output and xRESET pin is optional.  Adding a capacitor (10 nF or higher) between this pin and GND(I/O) (pin 64) is recommended. |

| 41         | NU                   |          | Not used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 42         | NU                   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 43         | NU                   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 44         | NU                   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 45         | LED0                 | OUT      | Debug LED. LED Blinks (1 Hz) during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 46         | NU                   | IN       | Not used. Connect 10k $\Omega$ –100k $\Omega$ pull-down resistor externally.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 47         | VOUT_SNS             | IN       | Output voltage measurement. Connect to 12 V rail through voltage divider as follows: Connect 240k $\Omega$ pull-up resistor from the pin to 12 V (shared DC/DCs output). Connect 20k $\Omega$ pull-down resistor from the pin to ADC analog ground (pin 55), with 100 nF capacitor in parallel.                                                                                                                                                                                                      |

Table 7 • PD82000 Pin Descriptions (continued)

| Pin Number | Pin Designator | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                   |

|------------|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48         | IOUT_SNS_A     | IN       | Channels 0–7 current measure. In multiport DPU application, connect to common output of analog multiplexer while the analog multiplexer independent inputs are connected to current sense amplifiers output from isolated DC/DC outputs, and the multiplexer select input connected to Mux_Sel0-2 (pins 33–35).  Add 1 nF capacitor between this pin and ADC analog GND (pin 55). |

| 49         | IOUT_SNS_B     | IN       | Channels 8–15 current measure. In a 16-port DPU application, connect to common output of analog multiplexer (MUX_B) while the analog multiplexer independent inputs are connected to current sense amplifiers output from isolated DC/DC outputs, and the multiplexer select input connected to Mux_Sel0-2 (pins 33–35).                                                          |

|            |                |          | Add 1 nF capacitor between this pin and ADC analog GND (pin 55). If IOUT_SNS_B not used, (8-port or less DPU application), connect 20k $\Omega$ pull-down resistor from this pin to ADC analog GND.                                                                                                                                                                               |

| 50         | NU             |          | Not used. Connect 1k $\Omega$ pull-up resistor to VDD(3V3) pin 56.                                                                                                                                                                                                                                                                                                                |

| 51         | I2C_ADDR       | IN       | Analog input to program PD81000 I2C address. In order to set default address (0x20), connect pull-up resistor 8.87k $\Omega$ from this pin to VDD (3.3 V), and connect pull-down resistor 10k $\Omega$ from this pin to ground (GND).                                                                                                                                             |

| 52         | NU             | OUT      | Reserved                                                                                                                                                                                                                                                                                                                                                                          |

| 53         | NU             |          | Not used                                                                                                                                                                                                                                                                                                                                                                          |

| 54         | NU             |          |                                                                                                                                                                                                                                                                                                                                                                                   |

| 55         | GND            | PWR      | Ground                                                                                                                                                                                                                                                                                                                                                                            |

| 56         | VDD            | PWR      | 3.3 V supply voltage to the internal regulator and the ADC. Also used as the ADC reference voltage.                                                                                                                                                                                                                                                                               |

| 57         | RTCXOUT        | OUT      | Reserved                                                                                                                                                                                                                                                                                                                                                                          |

| 58         | RTCXIN         | IN       | Reserved                                                                                                                                                                                                                                                                                                                                                                          |

|            |                |          |                                                                                                                                                                                                                                                                                                                                                                                   |

Table 7 • PD82000 Pin Descriptions (continued)

| Pin Number | Pin Designator | Pin Type | Pin Description                                                                                                                                                                                                        |

|------------|----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 59         | PG13           | IRQ_IN   | Power good interrupt input. PG                                                                                                                                                                                         |

| 60         | PG14           | IRQ_IN   | Input capacitance (external) should not be higher than 220 pF.                                                                                                                                                         |

| 61         | PG15           | IRQ_IN   |                                                                                                                                                                                                                        |

| 62         | IRQ_OUT_PSE    | IRQ_OUT  | PSE port status event interrupt output (active low with internal pullup). IRQ is asserted when PD82000 detects a port status events from one or more ports. PD82000 indicates the IRQ reason through status resisters. |

| 63         | VDD(I/O)       | PWR      | I/O supply voltage                                                                                                                                                                                                     |

| 64         | GND(I/O)       | PWR      | I/O supply RTN                                                                                                                                                                                                         |

# **6** Package Information

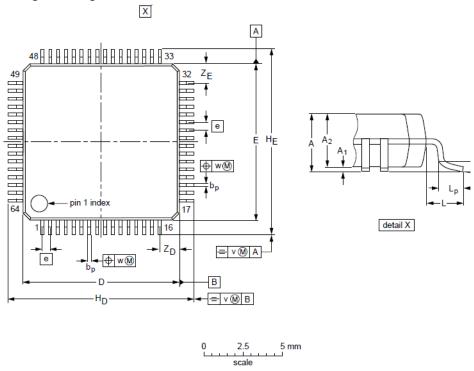

The PD82000 package is a 10 mm x 10 mm LQFP package, as described in the following section.

# 6.1 Package Drawing

The following illustration shows the package drawing for the PD82000 device.

Figure 2 • Package Drawing

Table 8 • Dimensions (mm are the original dimensions)

| Unit | A<br>max. | <b>A</b> <sub>1</sub> | A <sub>2</sub> | <b>A</b> <sub>3</sub> | b <sub>p</sub> | С | D <sup>(1)</sup> | E <sup>(1)</sup> | е | H <sub>D</sub> | HE | L | L <sub>P</sub> | v   | w    | у   | <b>Z</b> <sub>D</sub> <sup>(1)</sup> | Z <sub>E</sub> <sup>(1</sup> | Θ |

|------|-----------|-----------------------|----------------|-----------------------|----------------|---|------------------|------------------|---|----------------|----|---|----------------|-----|------|-----|--------------------------------------|------------------------------|---|

| mm   | 1.6       |                       |                |                       | 0.27<br>0.17   |   |                  |                  |   | 12.15<br>11.85 |    |   | 0.75<br>0.45   | 0.2 | 0.12 | 0.1 |                                      | 1.45<br>1.05                 |   |

Figure 3 • Recommended PCB Layout for 64-Pin LQFP 10 mm × 10 mm

# 6.2 Thermal Specifications

Thermal specifications for this device are based on the JEDEC JESD51 family of documents. These documents are available on the JEDEC Web site at www.jedec.org. The thermal specifications are modeled using a four-layer test board with two signal layers, a power plane, and a ground plane (2s2p PCB). For more information about the thermal measurement method used for this device, see the JESD51-1 standard.

12,5

Table 9 • Thermal Characteristics

| Thermal Resi  | istance PD82000 | Units | Notes                          |

|---------------|-----------------|-------|--------------------------------|

| $\Theta_{JA}$ | 61              | °C/W  | Mount on PCB of 76 mm × 114 mm |

| $\Theta_{JC}$ | 19              | °C/W  | Junction to top case           |

**Note:**  $\Theta_{JA}$  numbers assume no forced airflow. Junction temperature is calculated using  $T_J = T_A + (P_D \times \Theta_{JA})$ . In particular,  $\Theta_{JA}$  is a function of PCB construction.

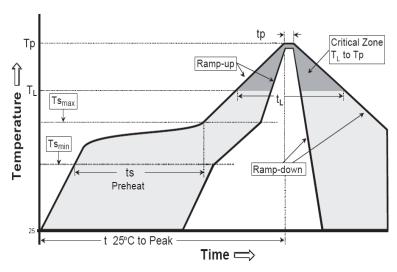

The following table describes the classification reflow profiles for the device. All temperatures refer to topside of the package, measured on the package body surface.

Table 10 • Classification Reflow Profiles

| Profile Feature                                | Sn-Pb Eutectic Assembly | PB-Free Assembly       |

|------------------------------------------------|-------------------------|------------------------|

| Average ramp-up rate (TS <sub>max</sub> to Tp) | 3 °C/second max.        | 3 °C/second max.       |

| Preheat                                        |                         |                        |

| Temperature Min (Ts <sub>min</sub> )           | 100 °C                  | 150 °C                 |

| Temperature Max (Ts <sub>max</sub> )           | 150 °C                  | 200 °C                 |

| Time (ts <sub>min</sub> to ts <sub>max</sub> ) | 60 seconds-120 seconds  | 60 seconds–150 seconds |

Table 10 • Classification Reflow Profiles

| Profile Feature                                         | Sn-Pb Eutectic Assembly          | PB-Free Assembly                 |

|---------------------------------------------------------|----------------------------------|----------------------------------|

| Time maintained above: Temperature $(T_L)$ Time $(t_L)$ | 183 °C<br>60 seconds–150 seconds | 217 °C<br>60 seconds–150 seconds |

| Time within 5 °C of actual peak temperature (tp)        | 10 seconds-30 seconds            | 20 seconds-40 seconds            |

| Ramp-down rate                                          | 6 °C/second max.                 | 6 °C/second max.                 |

| Time 25 °C to peak temperature                          | 6 minutes max.                   | 8 minutes max.                   |

The following illustration shows the classification reflow profile.

Figure 4 • Classification Reflow Profile

The device manufacturer/supplier shall assure process compatibility up to and including the stated classification temperature (this means peak reflow temperature 0  $^{\circ}$ C— for example, 260  $^{\circ}$ C + 0  $^{\circ}$ C) at the rated MSL level.

Table 11 • SnPb Eutectic Process: Classification Temperature

| Package Thickness   | Volume mm <sup>3</sup> <350 | Volume mm <sup>3</sup> ≥350 |

|---------------------|-----------------------------|-----------------------------|

| <2.5 mm             | 235 + 0/–5 °C               | 225 + 0/–5 °C               |

| 2.5 mm <sup>1</sup> | 225 + 0/–5 °C               | 225 + 0/–5 °C               |

Package volume excludes external terminals (balls, bumps, lands, leads) and/or non-integral heat sinks.

Table 12 • Pb-Free Process: Package Classification Reflow Temperatures

| Package Thickness | Volume mm <sup>3</sup> <350 | Volume mm <sup>3</sup><br>350–2000 | Volume mm <sup>3</sup> >2000 |

|-------------------|-----------------------------|------------------------------------|------------------------------|

| <1.6 mm           | 260 +0 °C*                  | 260 +0 °C*                         | 260 +0 °C*                   |

| 1.6 mm-2.5 mm     | 260 +0 °C*                  | 250 +0 °C*                         | 245 +0 °C*                   |

| ≥2.5 mm           | 250 +0 °C*                  | 245 +0 °C*                         | 245 +0 °C*                   |

Note: Exceeding these ratings may cause damage to the device.

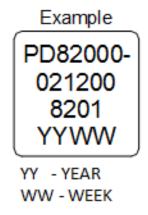

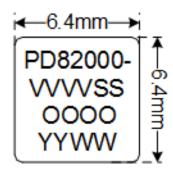

The following illustration shows the label for the PD82000 device.

Figure 5 • PD82000 Label

# 7 Ordering Information

The following table lists the ordering information for the PD82000 device.

Table 13 • Ordering Information

| Part Order Number | Description                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD82000-VVVVSS    | Lead-free, RoHS and MSL1-compliant 64-pin plastic LQFP package with a 10 mm × 10 mm body size. The operating temperature is – 40 °C ambient to 85 °C junction.  The tray marking is PD82000-VVVVSS PD-OOOOG3bb <sup>1</sup> YYWW |

<sup>1.</sup> MKTG Product Type/Version/SW Parameters/Operation P/N

For the latest firmware version available, refer to the Microsemi's website. Initial burning of controller's firmware is performed in factory. Firmware upgrades can be performed using the communication interface.