# PSoC™ 4 MCU: PSoC™ 4100S プラス

Arm® Cortex®-M0+ CPU をベース

## 概要

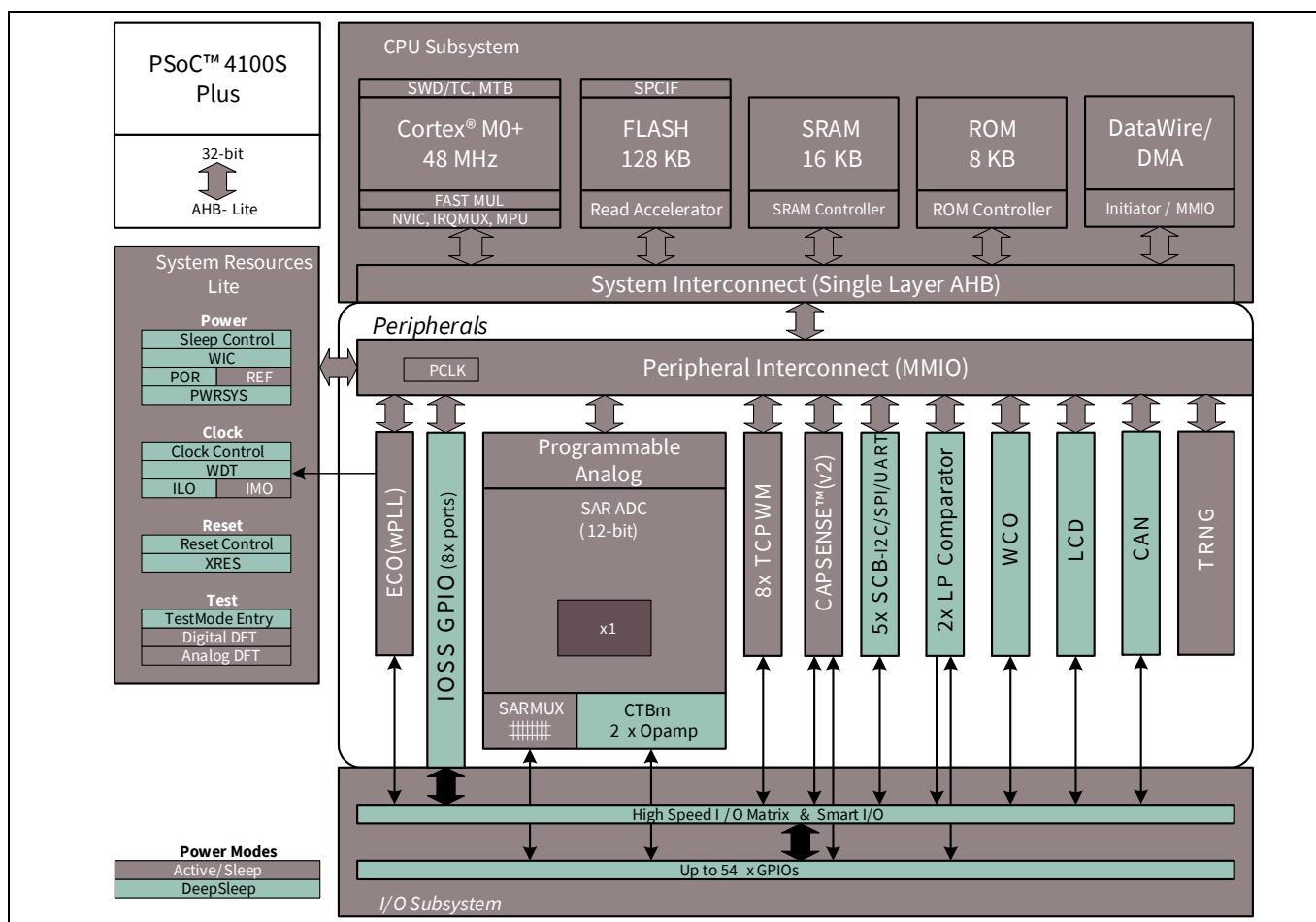

PSoC™ 4 は、Arm® Cortex®-M0+ CPU を内蔵したプログラマブル組込みシステムコントローラー ファミリ用の、拡張可能かつ再コンフィギュレーション可能なプラットフォーム アーキテクチャです。これはプログラム可能かつ再コンフィギュレーション可能なアナログ ブロックとデジタル ブロックを、柔軟な自動配線によって組み合わせたものです。PSoC™ 4100S プラスは PSoC™ 4 プラットフォーム アーキテクチャのメンバーです。標準的な通信機能とタイミング ペリフェラルを備えたマイクロコントローラー、クラス最高の性能を備えた静電容量タッチセンシング システム (CAPSENSE™)、プログラマブルな汎用の連続時間スイッチド キャパシタ アナログ ブロックおよびプログラマブルな内部接続で構成されます。新しいアプリケーションと設計ニーズのために、PSoC™ 4100S プラス製品は PSoC™ 4 プラットフォームのメンバーとの完全な上位互換性があります。

## 特長

- 32 ビット MCU サブシステム

- 48MHz Arm® Cortex®-M0+ CPU、シングル サイクルの乗算に対応

- 読み出しアクセラレータを備えた最大 128 KB のフラッシュ メモリ

- 最大 16 KB の SRAM

- 8 チャネル DMA エンジン

- プログラマブル アナログ

- 再設定可能な大電流外部ドライブと高帯域内部ドライブ、コンパレータ モード、ADC 入力バッファリング 能力に対応した 2 個のオペアンプ。ディープスリープ低消費電力モードで動作可能オペアンプはディープスリープ低消費電力モードで動作可能。

- 差動とシングルエンド モードおよび信号加算平均に対応したチャネル シーケンサを備えた 12 ビット 1Msps SAR ADC

- 静電容量センシング ブロックにより提供されるシングルスロープ 10 ビット ADC 機能

- 任意のピンに出力できる汎用または静電容量センシング用の 2 個の電流 DAC (IDAC)

- 2 個の低消費電力コンパレータ (低消費電力のディープスリープ モードで動作)

- プログラマブル デジタル

- 入出力ポートでブール演算の実行を可能にするプログラマブル論理 ブロック

- 低消費電力 (1.71V ~ 5.5V) 動作

- ディープスリープ モードで動作可能なアナログと 2.5µA のデジタル システム電流

- 静電容量センシング

- 静電容量シグマデルタ (CSD) により、クラス最高の信号対雑音比 (SNR) (>5:1) および耐水性を提供

- インフィニオンが提供するソフトウェア コンポーネントによる容易な静電容量センシングの設計

- ハードウェア自動チューニング (SmartSense)

- LCD 駆動

- GPIO ピンで LCD セグメントを駆動

- シリアル通信

- 5 個の独立した再コンフィギュレーション可能なシリアル通信 ブロック (SCB)、実行時に I<sup>2</sup>C, SPI、または UART 機能に再コンフィギュレーション可能

- タイミングおよびパルス幅変調

- 8 個の 16 ビット タイマー / カウンター / パルス幅変調器 (TCPWM) ブロック

- 中央揃え、エッジ、および疑似ランダム モード

- モーター駆動やその他の信頼性の高いデジタル ロジック アプリケーション用キル信号のコンパレータ ベースのトリガ

- 直交デコーダ

- クロック ソース

- 4MHz ~ 33MHz の外部水晶発振器 (ECO)

- 48MHz 周波数を生成する PLL

- 32kHz の時計用水晶発振器 (WCO)

- ±2% の内部主発振器 (IMO)

- 32kHz の内部低消費電力発振器 (ILO)

- 真性乱数発生器 (TRNG)

- TRNG は暗号アプリケーション用の安全な鍵の生成のために真性乱数を生成

- CAN ブロック

- タイムトリガ CAN (TTCAN) をサポートする CAN 2.0B ブロック

- 最大 54 本のプログラム可能な GPIO ピン

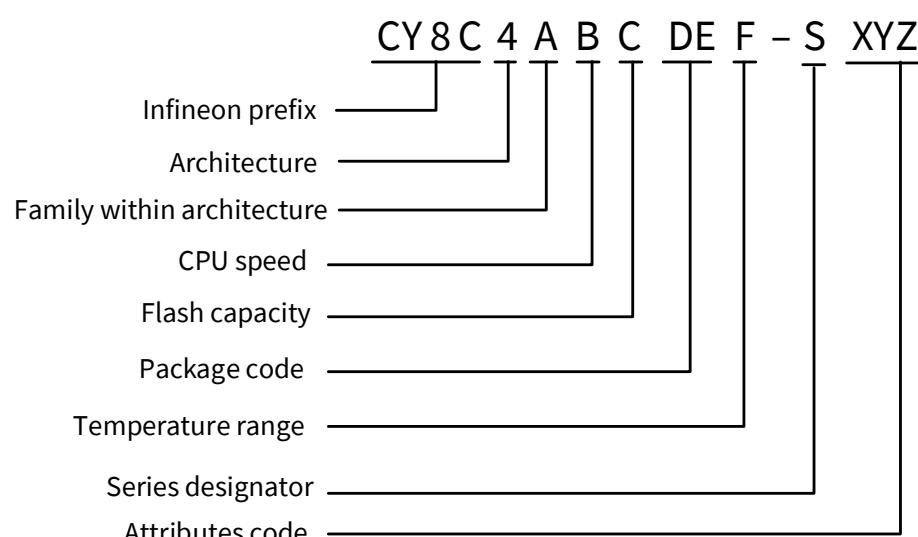

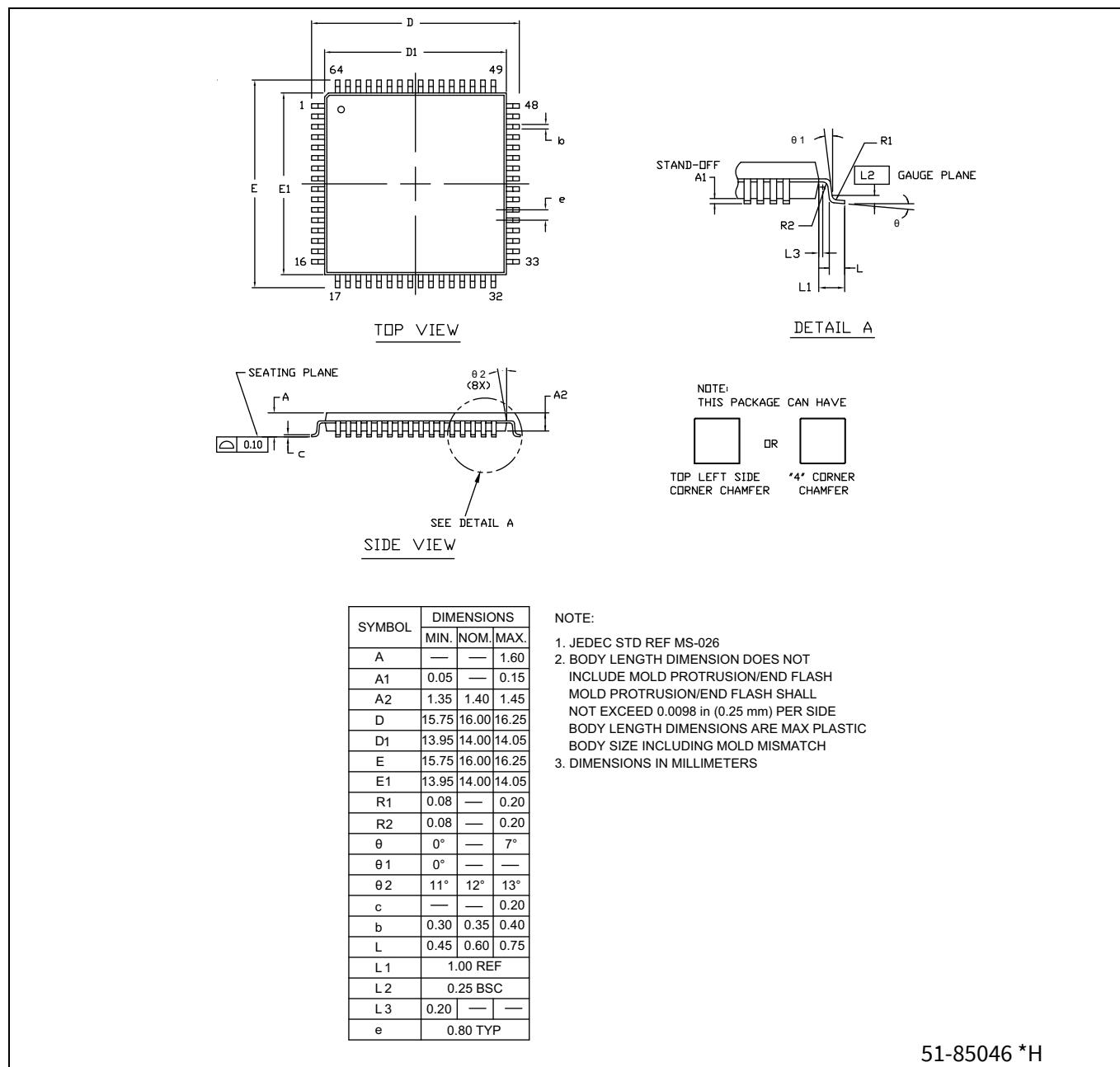

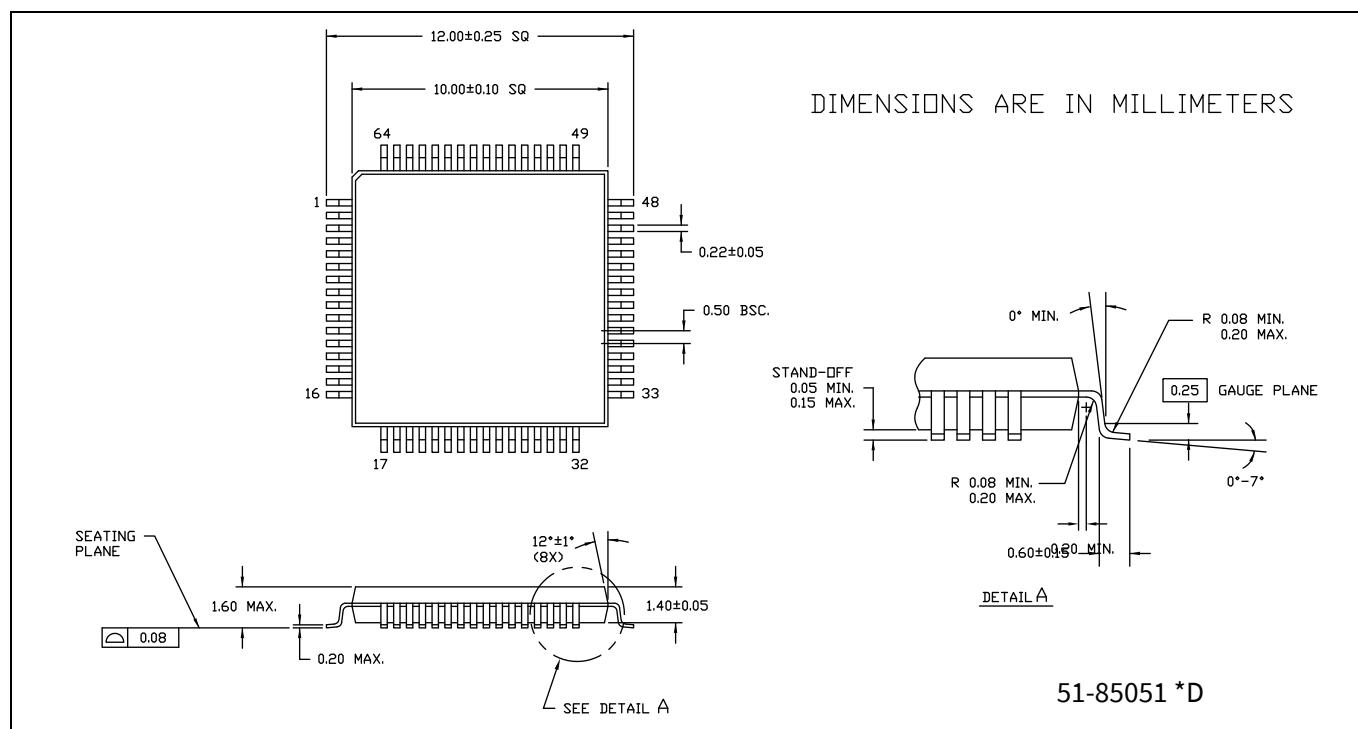

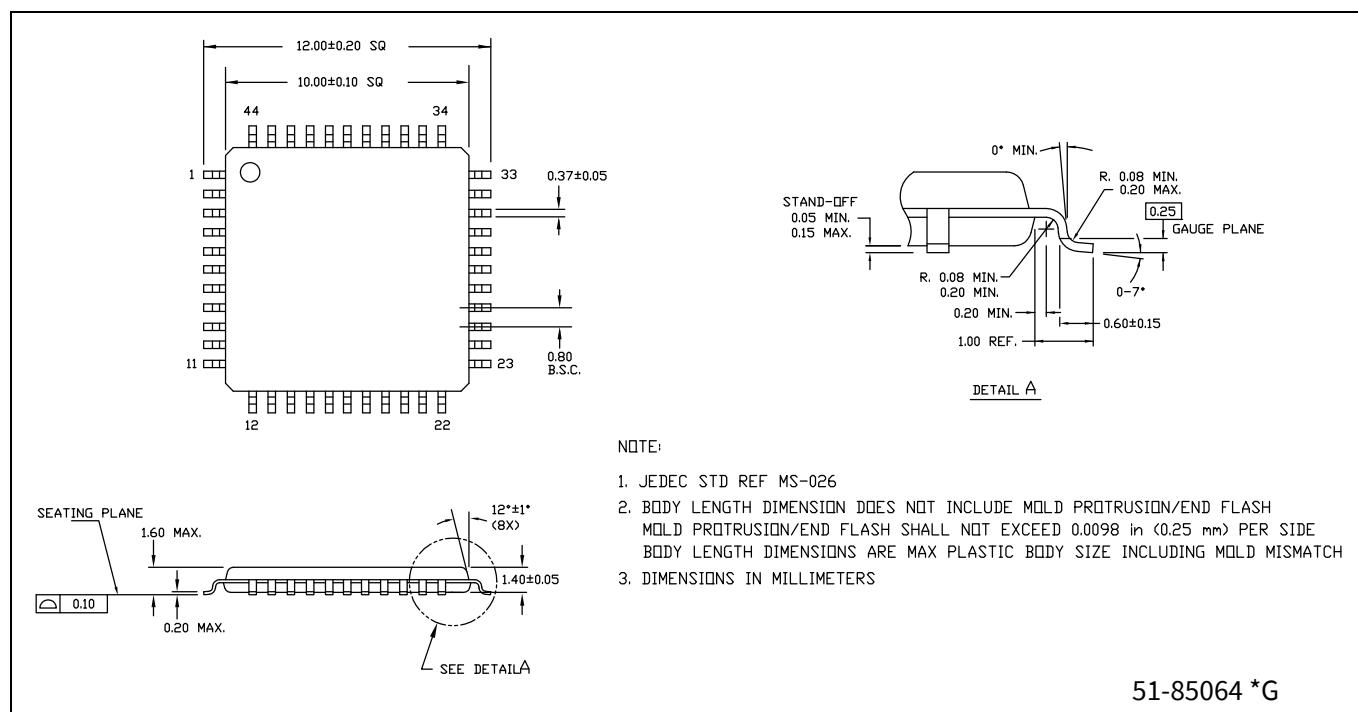

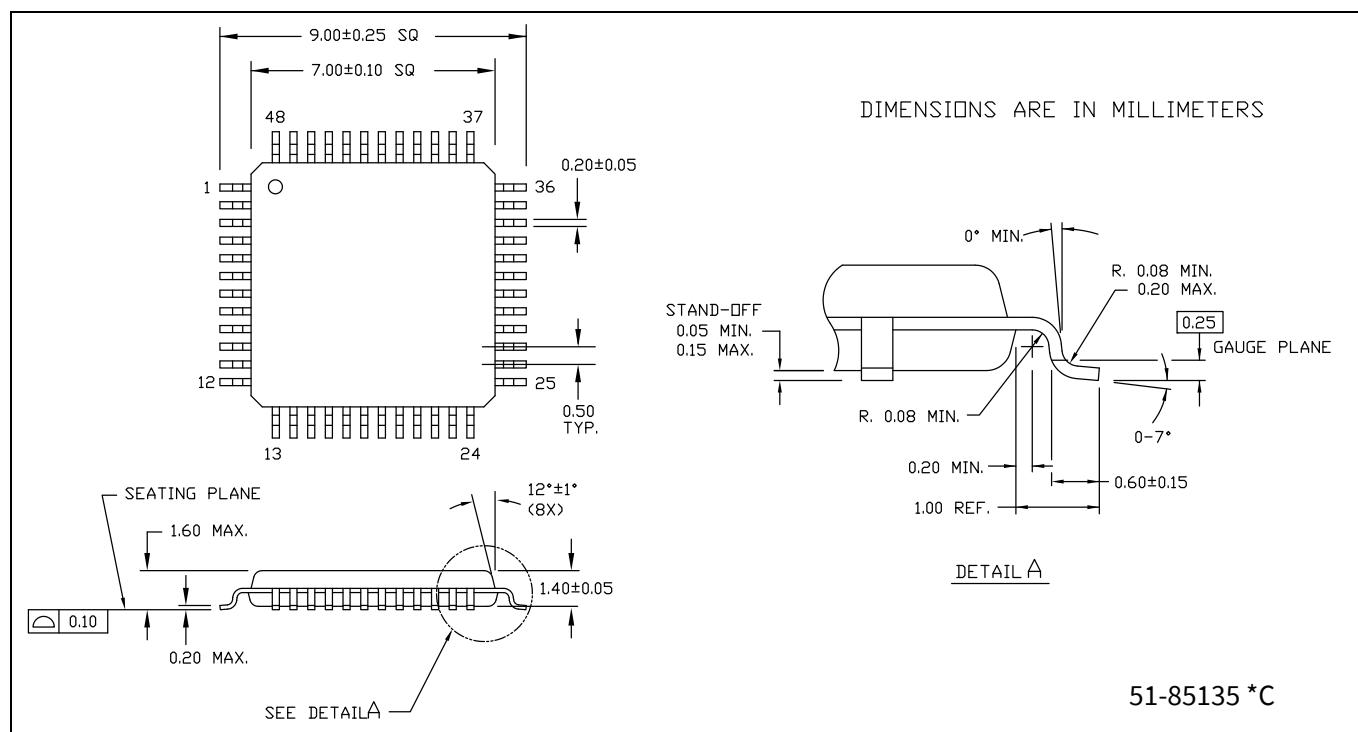

- パッケージ: 44 ピン TQFP (0.8mm ピッチ), 48 ピン TQFP (0.5mm ピッチ), 64 ピン TQFP 通常ピッチ (0.8mm) および微細ピッチ (0.5mm)

- すべての GPIO ピンは CAPSENSE™, アナログ, またはデジタルに対応

- 駆動モード, 駆動強度, およびスルーレートはプログラム可能

- ModusToolbox™ ソフトウェア

- マルチプラットフォームツールとソフトウェアライブラリの包括的なコレクション

- ボードサポートパッケージ (BSP), 周辺機器ドライバライブラリ (PDL), および CAPSENSE™ などのミドルウェアを含む

- PSoC™ Creator 設計環境

- 統合開発環境 (IDE) が回路図設計の入力からビルドまでを提供 (アナログとデジタルブロックの自動配線機能も備える)

- すべての固定機能およびプログラム可能なペリフェラル向けのアプリケーションプログラミングインターフェース (API) コンポーネント

- 業界標準ツールとの互換性

- 回路図の入力後、Arm® ベースの業界標準開発ツールで開発可能

## 目次

|                                      |    |

|--------------------------------------|----|

| <b>概要</b> .....                      | 1  |

| <b>特長</b> .....                      | 1  |

| <b>目次</b> .....                      | 3  |

| <b>1 Development ecosystem</b> ..... | 4  |

| 1.1 PSoC™ 4 MCU リソース .....           | 4  |

| 1.2 ModusToolbox™ software .....     | 5  |

| 1.3 PSoC™ Creator .....              | 6  |

| <b>ブロックダイヤグラム</b> .....              | 7  |

| <b>2 機能の説明</b> .....                 | 9  |

| 2.1 CPU およびメモリ サブシステム .....          | 9  |

| 2.2 システム リソース .....                  | 9  |

| 2.3 アナログ ブロック .....                  | 11 |

| 2.4 プログラマブル デジタル ブロック .....          | 12 |

| 2.5 固定機能デジタル ブロック .....              | 12 |

| 2.6 GPIO .....                       | 13 |

| 2.7 特殊機能ペリフェラル .....                 | 13 |

| <b>3 ピン配置</b> .....                  | 15 |

| 3.1 ピンの代替機能 .....                    | 18 |

| <b>4 電源</b> .....                    | 21 |

| 4.1 モード 1: 1.8 V ~ 5.5 V の外部電源 ..... | 21 |

| 4.2 モード 2: 1.8 V ±5% の外部電源 .....     | 21 |

| <b>5 電気的仕様</b> .....                 | 23 |

| 5.1 絶対最大定格 .....                     | 23 |

| 5.2 デバイス レベルの仕様 .....                | 23 |

| 5.3 アナログ ペリフェラル .....                | 27 |

| 5.4 デジタル ペリフェラル .....                | 36 |

| 5.5 メモリ .....                        | 38 |

| 5.6 システム リソース .....                  | 39 |

| <b>6 注文情報</b> .....                  | 43 |

| <b>7 パッケージ</b> .....                 | 46 |

| 7.1 パッケージ図 .....                     | 47 |

| <b>8 略語</b> .....                    | 50 |

| <b>9 本書の表記法</b> .....                | 54 |

| 9.1 測定単位 .....                       | 54 |

| <b>改訂履歴</b> .....                    | 55 |

| <b>免責事項</b> .....                    | 56 |

# 1 Development ecosystem

## 1.1 PSoC™ 4 MCU リソース

- インフィニオンは、[www.infineon.com](http://www.infineon.com) に大量のデータを掲載しており、ユーザーがデザインに適切な PSoC™ デバイスを選択し、迅速かつ効率的にデザインに統合する手助けをします。以下は、PSoC™ 4 MCU のリソースの要約とリンクです。

- **概要 : PSoC™ ポートフォリオ , PSoC™ ロードマップ**

- **製品セレクタ : PSoC™ 4 MCU**

- **アプリケーションノート** は、基本レベルから上級レベルまでの幅広いトピックを提供します。以下を含みます。

- [AN79953: Getting started With PSoC™ 4](#)

このアプリケーションノートには、使用する IDE ([ModusToolbox™ software](#) または [PSoC™ Creator](#)) を決定するために役立つ便利なフローチャートがあります。

- [AN91184: PSoC™ 4 Bluetooth® LE - Designing Bluetooth® LE applications](#)

- [AN88619: PSoC™ 4 hardware design considerations](#)

- [AN73854: Introduction to bootloaders](#)

- [AN89610: Arm® Cortex® code optimization](#)

- [AN86233: PSoC™ 4 MCU low-power modes and reduction techniques](#)

- [AN57821: PSoC™ 3, PSoC™ 4, and PSoC™ 5LP mixed-signal circuit board layout considerations](#)

- [AN85951: PSoC™ 4 and PSoC™ 6 CAPSENSE™ design guide](#)

- **サンプルコード** : 製品の機能と使用法を示します。[Infineon GitHub repositories](#) からも利用可能です。

- **テクニカルリファレンスマニュアル (TRM)**: PSoC™ 4 MCU アーキテクチャとレジスタの詳細な説明をします。

- **PSoC™ 4 MCU プログラミング仕様** : PSoC™ 4 MCU 不揮発性メモリのプログラムに必要な情報を提供します。

- **開発ツール**

- [ModusToolbox™ software](#) は、堅牢に一体化されたツールとソフトウェアライブラリによって、クロスプラットフォームコードの開発が可能です。

- [PSoC™ Creator](#) は、無料の Windows ベースの IDE です。これにより、PSoC™ 3, PSoC™ 4, PSoC™ 5LP、および PSoC™ 6 MCU ベースのシステムのハードウェアとファームウェアの同時設計が可能になります。アプリケーションは、回路図キャプチャと 150 を超える事前検証済みの本番環境対応の周辺機器コンポーネントを使用して作成されます。

- [CY8CKIT-149 PSoC™ 4100S Plus prototyping kit](#) は、使いやすく安価な評価プラットフォームです。このキットを使用すると、ブレッドボード互換形式ですべてのデバイス I/O に簡単にアクセスできます。

- [MiniProg4](#) および [MiniProg3](#) は、オールインワン開発プログラマーおよびデバッガーです。

- [PSoC™ 4 MCU CAD ライブラリ](#) は、一般的なツールに対応したフットプリントと回路図を提供します。IBIS モデルも使用できます。

- **トレーニングビデオ : PSoC™ 4 MCU 101 series** を含む、幅広いトピックを提供します。

- **Infineon developer community**: 世界中の PSoC™ 開発者と常時連絡 / 情報交換が可能です。[PSoC™ 4 MCU の専用コミュニティ](#) もあります。

## 1.2 ModusToolbox™ software

**ModusToolbox™ software** は、インフィニオンのマルチプラットフォームツールとソフトウェアライブラリの包括的なコレクションであり、統合された MCU とワイヤレスシステムを作成するための没入型開発エクスペリエンスを可能にします。以下のとおりです。

- 包括的 - 必要なリソースがあります

- 柔軟性 - 独自のワークフローでリソースを使用できます

- アトミック - 必要なリソースだけを取得できます

インフィニオンは、[GitHub でのコード リポジトリ](#)の大規模なコレクションを提供しています。これは以下を含みます。

- インフィニオンキットと連携したボードサポートパッケージ (BSP)

- ペリフェラルドライバーライブラリ (PDL) などの低レベルのリソース

- CAPSENSE™ などの業界をリードする機能を可能にするミドルウェア

- 徹底的にテストされた [サンプルコード](#) の広範なセット

ModusToolbox™ software は IDE に依存せず、ワークフロー や推奨される開発環境に簡単に適応できます。

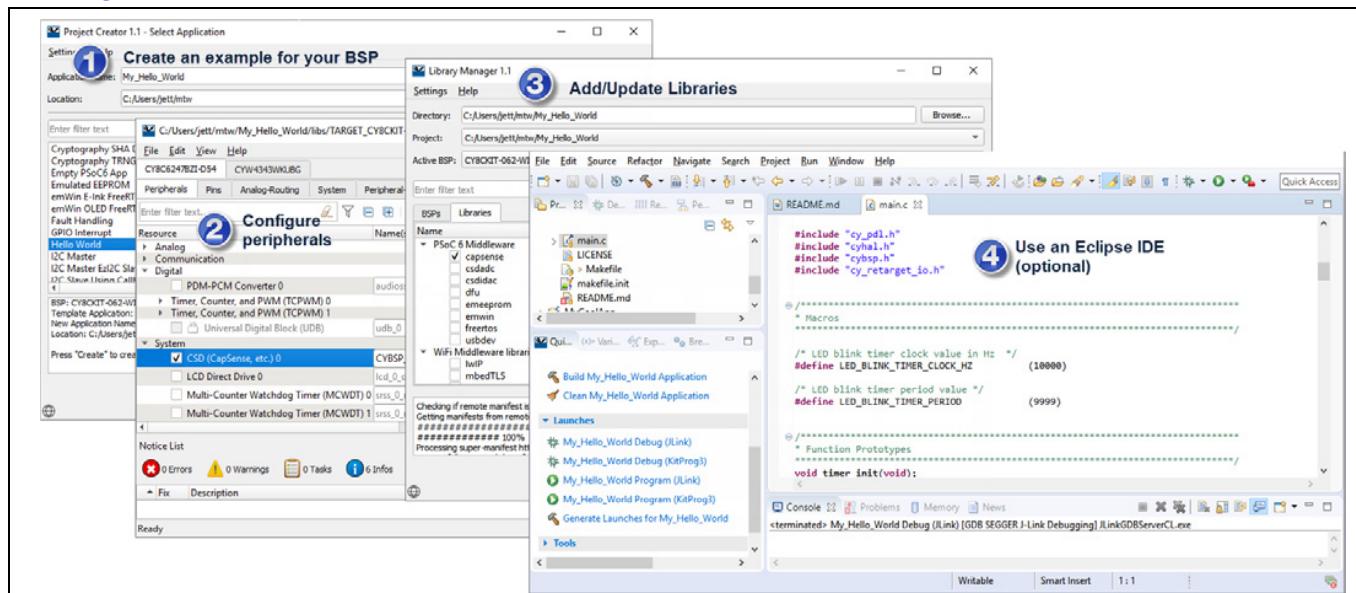

**Figure 1** に示すように、プロジェクトクリエーター、ペリフェラルおよびライブラリコンフィギュレーター、ライブラリマネージャー、および ModusToolbox™ 用のオプションの Eclipse IDE が含まれます。インフィニオンツールの使用については、ModusToolbox™ software に付属のドキュメントおよび [AN79953 -Getting started with PSoC™ 4](#) を参照してください。

**Figure 1** ModusToolbox™ software ツール

### 1.3 PSoC™ Creator

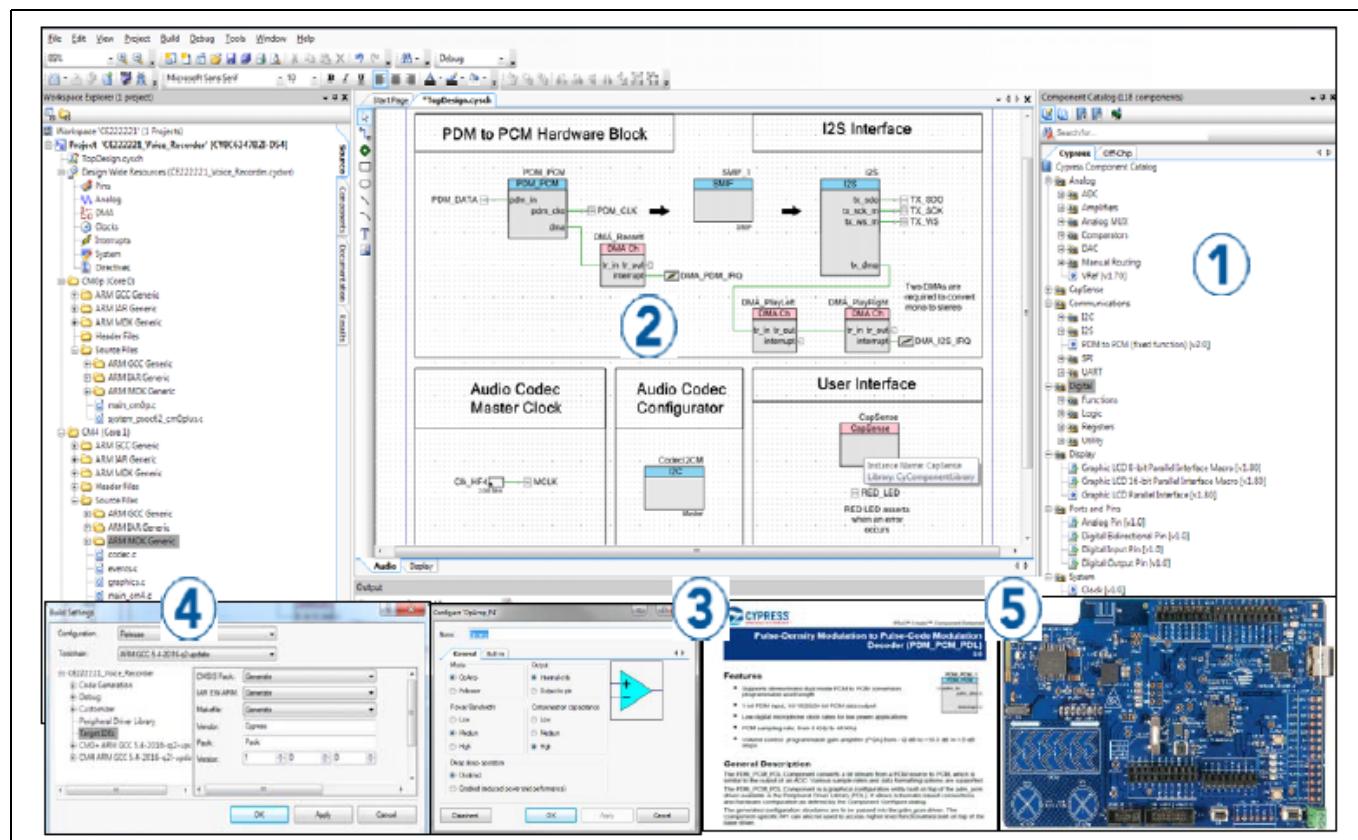

**PSoC™ Creator** は無料の Windows ベースの IDE です。このツールにより、お客様は PSoC™ 4 MCU のハードウェアとファームウェアシステムを同時に設計できます。Figure 2 に PSoC™ Creator でできることを示します。

1. 200 以上のコンポーネントのライブラリを探索

2. コンポーネントアイコンをドラッグ アンド ドロップして、メイン設計ワークスペースでハードウェアシステム設計を完成

3. コンポーネント構成ツールとコンポーネントデータシートを使用してコンポーネントを構成

4. PSoC™ Creator IDE でアプリケーションのファームウェアとハードウェアを相互設計またはサードパーティの IDE プロジェクトを構築

5. PSoC™ 4 Pioneer kit を使用してソリューションのプロトタイプを作成。設計変更が必要な場合、PSoC™ Creator および Components を使用すると、ハードウェアを改訂することなく、オンザフライで変更を加えることができます。

Figure 2 PSoC™ Creator の回路図入力とコンポーネント

## ブロックダイヤグラム

PSoC™ 4100S プラス デバイスは、ハードウェアとファームウェアの両方について、プログラミング、テスト、デバッグ、配線に幅広く対応します。

Arm® シリアルワイヤ デバッグ (SWD) インターフェースは、デバイスのプログラミングとデバッグ機能をすべてサポートします。

完全なデバッグ オンチップ (DoC) の機能により、標準の量産デバイスを使用した最終システムで、完全なデバイスのデバッグが可能です。専用のインターフェース、デバッグ ポッド、シミュレータ、またはエミュレータは不要です。デバッグをサポートするために必要なものは、通常のプログラミングに使う接続だけです。

PSoC™ Creator IDE は PSoC™ 4100S プラス デバイスのプログラミングおよびデバッグを完全にサポートします。SWD インターフェースは、業界標準のサードパーティ製ツールと完全互換です。PSoC™ 4100S プラスは、マルチチップ アプリケーション ソリューションまたはマイクロコントローラーの組合せでは適用不可能なセキュリティ レベルを提供します。このファミリは次の利点を持ちます。

- デバッグ機能を無効にできる

- 堅牢なフラッシュ保護

- お客様独自の機能をオンチップ プログラマブル ブロックに実装可能

デバッグ回路はデフォルトで有効にされており、ファームウェアで無効にできます。有効にされていない場合、一度デバイス全体を消去し、フラッシュ保護をクリアして、デバッグ機能を有効にする新しいファームウェアでデバイスをプログラムし直す以外に有効にする方法はありません。デバッグ機能のファームウェア制御は、ファームウェアを消去しなければオーバーライドされません。その結果セキュリティが向上します。

さらに、悪意を持ってデバイスを再プログラムすることに起因するフィッティング攻撃、またはフラッシュプログラミングシーケンスを開始して割り込むことでセキュリティシステムを突破しようという意図が懸念されるアプリケーションに対して、すべてのデバイスインターフェースを恒久的に無効できます。デバイスの最高レベルのセキュリティが有効になっている場合、すべてのプログラミング、デバッグ、およびテストインターフェースは無効にされます。そのため、デバイスセキュリティ機能を有効にした PSoC™ 4100S プラスは、故障解析ができない場合があります。これは PSoC™ 4100S プラスのトレードオフです。

## 2 機能の説明

### 2.1 CPU およびメモリ サブシステム

#### 2.1.1 CPU

PSoC™ 4100S プラスの Cortex®-M0+ CPU は、広範なクロックゲーティングに対応し低消費電力動作用に最適化された 32 ビット MCU サブシステムの一部です。ほとんどの命令の長さは 16 ビットです。CPU は Thumb-2 命令セットのサブセットを実行します。これは、8 つの割込み入力を備えたネスト型ベクタ割込みコントローラー (NVIC) ブロックと復帰割込みコントローラー (WIC) を含みます。WIC はディープスリープモードからプロセッサを復帰させることができます。これにより、チップがディープスリープモードにある時にメインプロセッサへの電源を切れます。

CPU サブシステムは 8 チャネル DMA エンジン、また JTAG の 2 線式のシリアルワイヤデバッグ (SWD) インターフェースも含みます。PSoC™ 4100S プラスに使用するデバッグコンフィギュレーションには、4 個のブレークポイント (アドレス) コンパレータと 2 個のウォッチポイント (データ) コンパレータがあります。

#### 2.1.2 フラッシュ

PSoC™ 4100S プラスデバイスは、フラッシュ ブロックからの平均アクセス時間を改善するために CPU と密結合された、フラッシュ アクセラレータ付きのフラッシュ モジュールを持っています。低消費電力のフラッシュ ブロックは 48MHz でゼロウェイクステート (WS) アクセス時間を達成するように設計されます。フラッシュ アクセラレータにより、アクセス性能は平均してシングルサイクル SRAM の 85% に達します。

#### 2.1.3 SRAM

48MHz でゼロウェイクステート (待ち状態なし) アクセスを備えた 16KB SRAM が提供されます。

#### 2.1.4 SROM

ブートおよびコンフィギュレーションルーチンを含む 8KB の監視 ROM が提供されます。

## 2.2 システムリソース

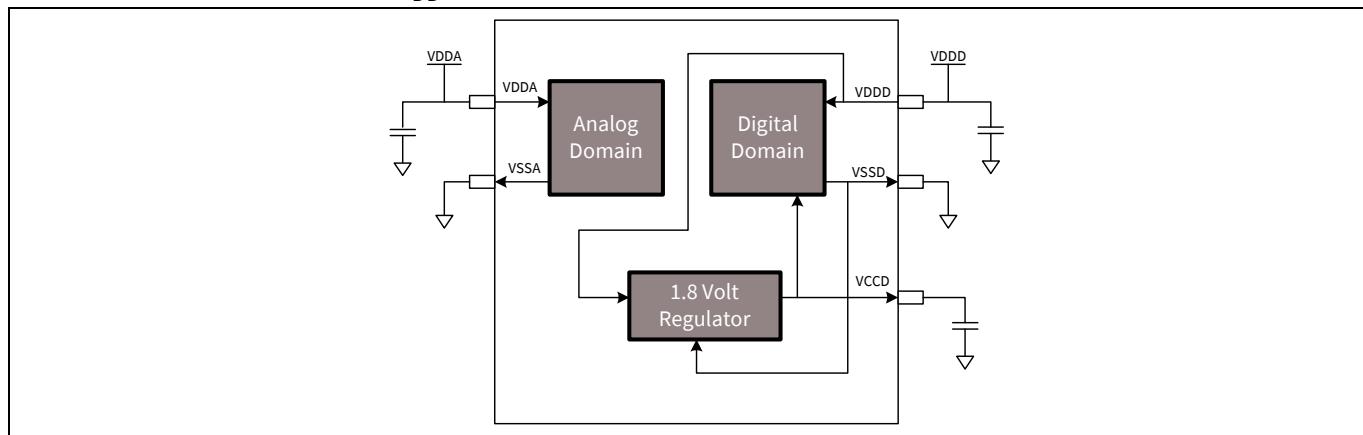

### 2.2.1 電源システム

電源システムの詳細は [電源](#) を参照してください。電圧レベルがそれぞれのモードに対して必要なものであることや、また電圧レベルによって、適切な機能に必要な状態になるまでモードへの移行が遅延されたり (例: パワーオンリセット (POR) 時)、あるいはリセットが生成されたりすること (例: 電圧低下検出時) を説明しています。PSoC™ 4100S プラスは、 $1.8V \pm 5\%$  (外部レギュレータ不使用時) または  $1.8V \sim 5.5V$  (内部レギュレータ使用時) の外部電源電圧で動作します。また PSoC™ 4100S プラスには 3 つの異なる電力モードがあります。これらのモード間の遷移は電源システムが管理します。PSoC™ 4100S プラスはアクティブモードおよびスリープとディープスリープの低消費電力モードに対応しています。

アクティブモードでは、すべてのサブシステムが動作できます。スリープモード中に CPU サブシステム (CPU、フラッシュ、SRAM) のクロックがゲートオフされます。このとき、ウェイクアップイベント中の瞬時ウェイクアップ機能により、すべてのペリフェラルと割込みがアクティブになります。ディープスリープモードでは、高速クロックおよび対応する回路がスイッチオフされます。このモードからの復帰には  $35\mu s$  を要します。オペアンプはディープスリープモードで動作し続けます。

## 2.2.2 クロックシステム

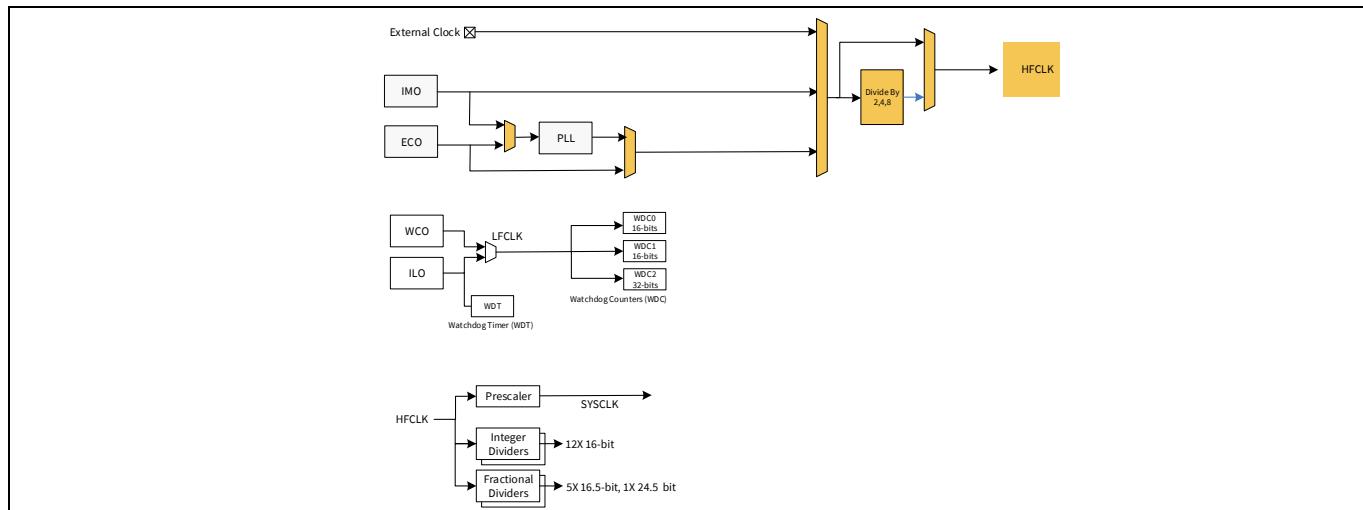

PSoC™ 4100S プラスクロックシステムは、クロックを必要とするすべてのサブシステムにクロックを供給し、グリッチなしに異なるクロックソース間で切り替えられます。さらに、クロックシステムはメタステーブル状態が発生しないことを保証します。

PSoC™ 4100S プラスのクロックシステムは、IMO, ILO, 32kHz 時計用水晶発振器 (WCO), MHz ECO と PLL および外部クロック入力から構成されます。WCO ブロックでは、IMO を 32kHz 発振器に固定できます。

**Figure 3 PSoC™ 4100S プラス MCU クロック アーキテクチャ**

HFCLK 信号は、アナログとデジタルペリフェラル用の同期クロックを生成するために分岐できます。PSoC™ 4100S プラスには 18 個の分周器があります (6 個の分数分周器、12 個の整数専用分周器)。12 個の 16 ビット整数分周器により、きめ細かな周波数を柔軟に生成できます。さらに、5 個の 16 ビット分数分周器と 1 個の 24 ビット分数分周器があります。

## 2.2.3 IMO クロックソース

IMO は PSoC™ 4100S プラスの内部クロック供給の主要なソースです。出荷試験中に仕様の精度を得るために調整されます。IMO のデフォルト周波数は 24MHz です。4MHz ステップで 24 ~ 48MHz に調整できます。インフィニオン提供の校正設定による IMO 許容誤差は、電圧と温度範囲全体で ±2% です。

## 2.2.4 ILO クロックソース

ILO は超低消費電力の 40kHz 発振器であり、主にディープスリープモードでウォッчドッグタイマー (WDT) とペリフェラルの動作用にクロックを生成するために使用されます。ILO 駆動のカウンターは、精度を改善するために IMO に対して校正できます。インフィニオンは校正を実行するソフトウェアコンポーネントを提供しています。

## 2.2.5 時計用水晶発振器 (WCO)

PSoC™ 4100S プラスのクロックサブシステムは、高精度タイミングアプリケーションに採用できる低周波数 (32kHz 時計用水晶振動子) 発振器も実装しています。

## 2.2.6 外部水晶発振器 (ECO)

PSoC™ 4100S プラスは 4MHz ~ 33MHz の水晶発振器も実装します。

## 2.2.7 ウォッчドッグタイマーおよびカウンター

ウォッчドッグタイマーは、ILO をクロックソースとして動作するクロックブロックに実装されます。ディープスリープ時のウォッчドッグ動作を可能にし、設定されたタイムアウトが発生する前に処理されなかった場合にウォッчドッグリセットを生成します。ウォッчドッグリセットは、ファームウェア読み出しが可能なリセット原因レジスタに記録されます。ウォッчドッグカウンターは 32kHz WCO を使用して、リアルタイムクロックを実装できます。

## 2.2.8 リセット

PSoC™ 4100S プラスは、ソフトウェアリセットを含む様々なソースからリセットできます。リセットイベントは非同期であり、デバイスを既知の状態に復帰させることが保証されています。リセットの原因はレジスタに記録されます。そのレジスタはリセット中も保存され、ソフトウェアがリセットの原因を判断できます。XRES ピンはアクティブ LOW の外部リセット用に予約されています。XRES ピンには、常に有効な内部プルアップ抵抗が接続されています。

## 2.3 アナログ ブロック

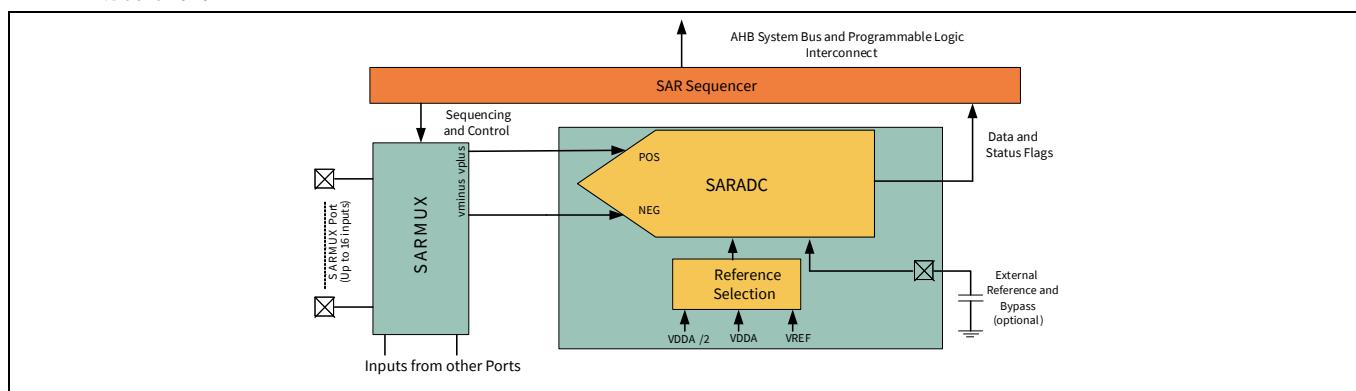

### 2.3.1 12 ビット SAR ADC

12 ビットの 1Msps SAR ADC は 18MHz の最大クロック レートで動作でき、12 ビット変換を行うためにその周波数で少なくとも 18 クロックを要します。

サンプルホールド (S/H) のアパートチャがプログラム可能であるため、SAR 入力を駆動するアンプの整定時間を規定する利得帯域幅要件を必要に応じて緩和できます。内部基準アンプ用に外部バイパス (固定したピン位置を介して) を提供できます。

SAR は 8 入力シーケンサを介して固定したピンに接続されます。シーケンサは、スイッチング オーバーヘッドの必要なく選択されたチャネルを自律的に巡回します (シーケンサ スキャン) (つまり、合計サンプリング帯域幅は、単一のチャネルか複数のチャネルであるかにかかわらず 1Msps です)。シーケンサの切り替えは、ステートマシンまたはファームウェア駆動の切り替えにより行われます。シーケンサの 1 つの機能は、CPU 割込みサービスの要件を軽減するための各チャネルのバッファリングです。信号を様々なソース インピーダンスと周波数に適合させるために、チャネルごとに異なるサンプリング時間をプログラムできます。また、デジタル化された値がプログラムされた範囲を超えた場合、レンジレジスタの一対 (低と高レンジ値) による信号範囲の指定は、対応する範囲外の割込みで実施されます。これにより、シーケンサ スキャンが完了し、CPU が値を読み出してソフトウェア内で範囲外の値の有無を確認するのを待たず、範囲外の値を早く検出できます。

SAR は高速クロック (最大 18MHz) を必要とするため、ディープスリープモードに対応していません。SAR の動作範囲は 1.71V ~ 5.5V です。

Figure 4 SAR ADC

### 2.3.2 2 個のオペアンプ (連続時間ブロック ; CTB)

PSoC™ 4100S プラスは、コンパレータモードのある 2 個のオペアンプを持つことにより、PGA, 電圧バッファ, フィルター, トランシスインピーダンスアンプなどほとんどの一般的なアナログ機能が外付け部品の必要なくオンチップで実行でき、消費電力, コスト, および空間を節約できます。ただし外部受動素子が必要になる場合もあります。内蔵オペアンプは、外部バッファを必要とせずに ADC のサンプルホールド回路を駆動するために十分な帯域幅を持つように設計されています。

### 2.3.3 低消費電力コンパレータ (LPC)

PSoC™ 4100S プラスはディープスリープモードで動作できる低消費電力コンパレータの一対を内蔵しています。これにより、低消費電力モード中に外部電圧レベルを監視する能力を維持しながらアナログシステムブロックを無効にできます。コンパレータ出力は、メタ stabilitiy を避けるために通常同期化

されます。ただし、システム復帰回路がコンパレータの切り替えイベントによりアクティブになるような、非同期電力モードで動作している場合を除きます。LPC の出力はピンに接続できます。

### 2.3.4 電流 DACs

PSoC™ 4100S プラスは、チップ上のすべてのピンを駆動できる 2 個の IDAC を備えています。IDAC はプログラマ可能な電流範囲があります。

### 2.3.5 アナログマルチプレクサバス

PSoC™ 4100S プラスは同心円状にチップの周辺を回る 2 本の独立したバスを備えています。これらのバス (amux バスと呼ばれる) はファームウェアでプログラマ可能なアナログスイッチに接続され、チップの内部リソース (IDAC、コンパレータ) を I/O ポートのいずれのピンにも接続できます。

## 2.4 プログラマブルデジタルブロック

### 2.4.1 Smart I/O ブロック

Smart I/O ブロックはスイッチと LUT の構造体であり、ブール関数を GPIO ポートのピンに配線される信号で実行できます。Smart I/O は論理演算をチップの入力ピン、および出力として出る信号で実行できます。

## 2.5 固定機能デジタルブロック

### 2.5.1 タイマー、カウンター、パルス幅変調器 (TCPWM) ブロック

TCPWM ブロックは、ユーザーが周期長をプログラム可能な 16 ビット カウンターからなります。キャプチャレジスタは、I/O イベントなどのイベントのときにカウント値を記録します。周期レジスタは、カウンターのカウントが周期レジスタのカウントに等しくなる時にカウントを停止し、または自動的にリロードします。比較レジスタは、PWM デューティ比出力として使用される比較値信号を生成します。このブロックはプログラム可能なオフセットをつけられる正出力とコンプリメンタリ出力も提供しており、デッドバンドをプログラム可能なコンプリメンタリ PWM 出力として使用できます。また、出力を事前に決定された状態に移行させるキル (Kill) 入力もあります。例えば、モーター駆動システムでは、過電流状態が示され、FET を駆動している PWM をソフトウェアの介入なしに直ちに止める必要がある時、キル入力が使用されます。各ブロックは直交デコーダも組み込んでいます。PSoC™ 4100S プラスは 8 個の TCPWM ブロックがあります。

### 2.5.2 シリアル通信ブロック (SCB)

PSoC™ 4100S プラスは 5 個のシリアル通信ブロックを備え、必要に応じて SPI, I<sup>2</sup>C, または UART 機能にプログラムできます。

**I<sup>2</sup>C モード**: ハードウェア I<sup>2</sup>C ブロックは、完全なマルチマスオーターとスレーブインターフェース (マルチマスターのアービトレイションが可能) を実装します。このブロックは、最大 1Mbps (ファストモードプラス) で動作可能で、CPU 用の割込みオーバヘッドとレイテンシを削減するためのフレキシブルなバッファリングオプションがあります。また、PSoC™ 4100S プラスのメモリでメールボックスアドレス範囲を作り、メモリアレイに対する読み書きの I<sup>2</sup>C 通信を効果的に削減する EZI2C にも対応しています。さらに、ブロックは送受信用に深さ 8 の FIFO にも対応しています。CPU がデータを読み出す一定の時間を増加することで、時間通りに CPU が読み出すデータがないことに起因したクロックストレッチの必要性を大幅に低減できます。

I<sup>2</sup>C ペリフェラルは、NXP I<sup>2</sup>C バス仕様とユーザー マニュアル (UM10204) で定義された通りに、I<sup>2</sup>C 標準モードとファストモードデバイスと互換性があります。I<sup>2</sup>C バス I/O は、オープンドレインモードの GPIO を使って実装されます。

PSoC™ 4100S プラスは、以下の点では I<sup>2</sup>C 仕様に完全に準拠しません。

- GPIO セルは過電圧耐性がないため、ホットスワップや I<sup>2</sup>C システムの残りの部分から独立して電源を投入できません。

**UART モード**: 最大 1Mbps で動作するフル機能の UART です。基本 UART プロトコルから少し変化したものである、車載向けシングルワイヤインターフェース (LIN), 赤外線インターフェース (IrDA), SmartCard

(ISO7816) プロトコルに対応しています。また、共通の RX と TX ラインを介して接続したペリフェラルのアドレス指定を可能にする 9 ビットマルチプロセッサ モードに対応しています。パリティ エラー、ブレーク検出、フレーム エラーなどの一般的な UART 機能に対応しています。深さ 8 の FIFO により、より大きい CPU サービス レイテンシが許容されます。

**SPI モード** : SPI モードは Motorola SPI, TI SSP (SPI コーデックを同期化するのに使用される開始パルスを追加), National Microwire (半二重の SPI) に完全に対応しています。SPI ブロックは FIFO を使用できます。

### 2.5.3 CAN

TT-CAN をサポートする CAN 2.0B ブロックがあります。

### 2.6 GPIO

PSoC™ 4100S プラスは最大 54 本の GPIO を持ちます。GPIO ブロックは以下を実装します。

- 8 種類の駆動モード

- アナログ入力モード (入力と出力バッファが無効)

- 入力のみ

- 弱プルアップ、強プルダウン

- 強プルアップ、弱プルダウン

- オープンドレイン、強プルダウン

- オープンドレイン、強プルアップ

- 強プルアップ、強プルダウン

- 弱プルアップ、弱プルダウン

- 入力閾値選択 (CMOS あるいは LVTTL)

- 駆動強度モードに加えて、入力と出力バッファの有効 / 無効の個別制御

- EMI を改善するための dV/dt 関連の雑音制御用の選択可能なスルーレート

ピンは、8 ビット幅のポートと呼ばれる論理エンティティに構成されます (ポート 5 とポート 6 はより少ないビット幅です)。電源投入とリセットの間、入力に過電流を与えず、過剰なターンオン電流を発生させないために、ブロックは無効状態にされます。高速 I/O マトリックスとして知られている多重化ネットワークが、1 本の I/O ピンに接続され得る複数の信号間を多重化するために使用されます。

データ出力とピンステートレジスタは、それぞれピン上で駆動される値とそれらのピンの状態を格納します。各 I/O ピンは有効になった場合に割込みを生成できます。各 I/O ポートには、それに対応する割込み要求 (IRQ) と割込みサービス ルーチン (ISR) ベクタがあります。

### 2.7 特殊機能ペリフェラル

#### 2.7.1 CAPSENSE™

CAPSENSE™ は、(アナログスイッチに接続された) アナログマルチプレクサバスを介してどのピンにも接続できる静電容量シグマ - デルタ (CSD) ブロックにより、PSoC™ 4100S プラスでサポートされています。CAPSENSE™ 機能はこのように、ソフトウェアで制御されるシステム内のいかなる使用可能なピンあるいはピングループに提供できます。扱い易くするために、CAPSENSE™ ブロック用の PSoC™ Creator コンポーネントが提供されています。

シールド電圧は、耐水機能を実現するために、他のマルチプレクサバス上で駆動できます。耐水性は、シールド電極を検知電極と同位相で駆動して提供されます。その検知電極はシールド静電容量が検知された入力を減衰させることを防ぐためのものです。近接センシングも実装できます。

CAPSENSE™ ブロックは、2 個の IDAC を備えています。CAPSENSE™ を使用しない (両方の IDAC とも使用可能) 場合、または CAPSENSE™ の耐水機能を利用しない場合 (どちらか一方の IDAC が使用可能)、一般用途に使用できます。

また、CAPSENSE™ ブロックは CAPSENSE™ 機能と併用できる 10 ビットのスロープ ADC 機能も提供しています。CAPSENSE™ ブロックは高性能で、低雑音のプログラマブル ブロックです。感度と柔軟性を向上させるために基準電圧と電流源の範囲をプログラム可能です。さらに、外部基準電圧も利用できます。VDDA およびグランドのセンシングを代替し、消費電力関連雑音をゼロにする全波 CSD モードがあります。

## 2.7.2 LCD セグメント駆動

PSoC™ 4100S プラスは最大 8 つのコモン信号と最大 30 のセグメント信号を駆動できる LCD コントローラーを内蔵しています。内部 LCD 電圧を生成する必要がないフル デジタル方式を使用して LCD セグメントを駆動します。2 つの方式は、デジタル相関と PWM と呼ばれています。デジタル相関は、コモンとセグメント信号の周波数と駆動レベルの変調に関連し、セグメントの全域で最高 RMS 電圧を生成してセグメントを点灯させるか、または RMS 信号を 0 に維持します。この方法は STN ディスプレイに適していますが、(より安い) TN ディスプレイに対してはコントラストが低くなることがあります。PWM は、PWM 信号を有するパネルの駆動に関連し、パネルの静電容量を効率的に使用して変調されたパルス幅の積分を提供し、所望の LCD 電圧を生成します。この方法は消費電力が増えますが、TN ディスプレイを駆動する際にはより良い結果を出します。

### 3 ピン配置

次の表は、PSoC™ 4100S プラスの 44 ピン TQFP, 48 ピン TQFP, および 64 ピン TQFP 通常ピッチと微細ピッチパッケージのピンリストです。

**Table 1** ピン配置

| 64-TQFP |      | 44-TQFP |      | 48-TQFP |      |

|---------|------|---------|------|---------|------|

| ピン      | 名称   | ピン      | 名称   | ピン      | 名称   |

| 39      | P0.0 | 24      | P0.0 | 28      | P0.0 |

| 40      | P0.1 | 25      | P0.1 | 29      | P0.1 |

| 41      | P0.2 | 26      | P0.2 | 30      | P0.2 |

| 42      | P0.3 | 27      | P0.3 | 31      | P0.3 |

| 43      | P0.4 | 28      | P0.4 | 32      | P0.4 |

| 44      | P0.5 | 29      | P0.5 | 33      | P0.5 |

| 45      | P0.6 | 30      | P0.6 | 34      | P0.6 |

| 46      | P0.7 | 31      | P0.7 | 35      | P0.7 |

| 47      | XRES | 32      | XRES | 36      | XRES |

| 48      | VCCD | 33      | VCCD | 37      | VCCD |

|         |      | 34      | VDDD |         |      |

| 49      | VSSD |         |      | 38      | VSSD |

| 50      | VDDD |         |      | 39      | VDDD |

| 51      | P5.0 |         |      |         |      |

| 52      | P5.1 |         |      |         |      |

| 53      | P5.2 |         |      |         |      |

| 54      | P5.3 |         |      |         |      |

| 55      | P5.5 |         |      |         |      |

| 56      | VDDA | 35      | VDDA | 40      | VDDA |

| 57      | VSSA | 36      | VSSA | 41      | VSSA |

| 58      | P1.0 | 37      | P1.0 | 42      | P1.0 |

| 59      | P1.1 | 38      | P1.1 | 43      | P1.1 |

| 60      | P1.2 | 39      | P1.2 | 44      | P1.2 |

| 61      | P1.3 | 40      | P1.3 | 45      | P1.3 |

| 62      | P1.4 | 41      | P1.4 | 46      | P1.4 |

| 63      | P1.5 | 42      | P1.5 | 47      | P1.5 |

| 64      | P1.6 | 43      | P1.6 | 48      | P1.6 |

| 1       | P1.7 | 44      | P1.7 | 1       | P1.7 |

|         |      | 1       | VSSD |         |      |

| 2       | P2.0 | 2       | P2.0 | 2       | P2.0 |

| 3       | P2.1 | 3       | P2.1 | 3       | P2.1 |

| 4       | P2.2 | 4       | P2.2 | 4       | P2.2 |

| 5       | P2.3 | 5       | P2.3 | 5       | P2.3 |

| 6       | P2.4 | 6       | P2.4 | 6       | P2.4 |

| 7       | P2.5 | 7       | P2.5 | 7       | P2.5 |

**Table 1** ピン配置 (*continued*)

| 64-TQFP |      | 44-TQFP |      | 48-TQFP |      |

|---------|------|---------|------|---------|------|

| ピン      | 名称   | ピン      | 名称   | ピン      | 名称   |

| 8       | P2.6 | 8       | P2.6 | 8       | P2.6 |

| 9       | P2.7 | 9       | P2.7 | 9       | P2.7 |

| 10      | VSSD |         |      |         |      |

| 11      | NC   |         |      |         |      |

| 12      | P6.0 | 10      | P6.0 |         |      |

| 13      | P6.1 |         |      |         |      |

| 14      | P6.2 |         |      |         |      |

| 15      | P6.4 |         |      |         |      |

| 16      | P6.5 |         |      |         |      |

| 17      | VSSD |         |      | 10      | VSSD |

|         |      |         |      | 11      | NC   |

| 18      | P3.0 | 11      | P3.0 | 12      | P3.0 |

| 19      | P3.1 | 12      | P3.1 | 13      | P3.1 |

| 20      | P3.2 | 13      | P3.2 | 14      | P3.2 |

|         |      |         |      | 15      | NC   |

| 21      | P3.3 | 14      | P3.3 | 16      | P3.3 |

| 22      | P3.4 | 15      | P3.4 | 17      | P3.4 |

| 23      | P3.5 | 16      | P3.5 | 18      | P3.5 |

| 24      | P3.6 | 17      | P3.6 | 19      | P3.6 |

| 25      | P3.7 | 18      | P3.7 | 20      | P3.7 |

| 26      | VDDD | 19      | VDDD | 21      | VDDD |

| 27      | P4.0 | 20      | P4.0 | 22      | P4.0 |

| 28      | P4.1 | 21      | P4.1 | 23      | P4.1 |

| 29      | P4.2 | 22      | P4.2 | 24      | P4.2 |

| 30      | P4.3 | 23      | P4.3 | 25      | P4.3 |

| 31      | P4.4 |         |      |         |      |

| 32      | P4.5 |         |      |         |      |

| 33      | P4.6 |         |      |         |      |

| 34      | P4.7 |         |      |         |      |

| 35      | P5.6 |         |      |         |      |

| 36      | P5.7 |         |      |         |      |

| 37      | P7.0 |         |      | 26      | P7.0 |

| 38      | P7.1 |         |      | 27      | P7.1 |

電源ピンの説明は以下のとおりです。

VDDD: デジタルセクション用の電源

VDDA: アナログセクション用の電源

VSSD, VSSA: それぞれデジタルとアナログセクション用のグランドピン

VCCD: 安定化デジタル電源 (1.8V±5%)

VDD: チップのすべてのセクション用の電源

VSS: チップのすべてのセクション用のグランド

下表はパッケージ別の GPIO 数です。

|        | 64 TQFP | 44 TQFP | 48 TQFP |

|--------|---------|---------|---------|

| GPIO 数 | 54      | 37      | 38      |

### 3.1 ピンの代替機能

それぞれのポートピンは多機能の1つに割り当てられます。例えば、アナログI/O, デジタルペリフェラル機能,LCDピン, またはCAPSENSE™ピンです。ピンの割当てを下表に示します。

**Table 2** ピンの代替機能

| ポート / ピン | アナログ           | Smart I/O        | ACT #0                | ACT #1            | ACT #3            | DS #2            | DS #3                |

|----------|----------------|------------------|-----------------------|-------------------|-------------------|------------------|----------------------|

| P0.0     | lpcomp.in_p[0] |                  |                       | tcpwm.tr_in[0]    | scb[2].uart_cts:0 | scb[2].i2c_scl:0 | scb[0].spi_select1:0 |

| P0.1     | lpcomp.in_n[0] |                  |                       | tcpwm.tr_in[1]    | scb[2].uart_rts:0 | scb[2].i2c_sda:0 | scb[0].spi_select2:0 |

| P0.2     | lpcomp.in_p[1] |                  |                       |                   |                   |                  | scb[0].spi_select3:0 |

| P0.3     | lpcomp.in_n[1] |                  |                       |                   |                   |                  | scb[2].spi_select0:1 |

| P0.4     | wco.wco_in     |                  |                       | scb[1].uart_rx:0  | scb[2].uart_rx:0  | scb[1].i2c_scl:0 | scb[1].spi_mosi:1    |

| P0.5     | wco.wco_out    |                  |                       | scb[1].uart_tx:0  | scb[2].uart_tx:0  | scb[1].i2c_sda:0 | scb[1].spi_miso:1    |

| P0.6     | exco.eco_in    |                  | srss.ext_clk:0        | scb[1].uart_cts:0 | scb[2].uart_tx:1  |                  | scb[1].spi_clk:1     |

| P0.7     | exco.eco_out   |                  | tcpwm.line[0]:3       | scb[1].uart_rts:0 |                   |                  | scb[1].spi_select0:1 |

| P5.0     |                |                  | tcpwm.line[4]:2       |                   | scb[2].uart_rx:1  | scb[2].i2c_scl:1 | scb[2].spi_mosi:0    |

| P5.1     |                |                  | tcpwm.line_compl[4]:2 |                   | scb[2].uart_tx:2  | scb[2].i2c_sda:1 | scb[2].spi_miso:0    |

| P5.2     |                |                  | tcpwm.line[5]:2       |                   | scb[2].uart_cts:1 | lpcomp.comp[0]:2 | scb[2].spi_clk:0     |

| P5.3     |                |                  | tcpwm.line_compl[5]:2 |                   | scb[2].uart_rts:1 | lpcomp.comp[1]:0 | scb[2].spi_select0:0 |

| P5.4     |                |                  | tcpwm.line[6]:2       |                   |                   |                  | scb[2].spi_select1:0 |

| P5.5     |                |                  | tcpwm.line_compl[6]:2 |                   |                   |                  | scb[2].spi_select2:0 |

| P1.0     | ctb0_oa0+      | SmartIo[2].io[0] | tcpwm.line[2]:1       | scb[0].uart_rx:1  |                   | scb[0].i2c_scl:0 | scb[0].spi_mosi:1    |

| P1.1     | ctb0_oa0-      | SmartIo[2].io[1] | tcpwm.line_compl[2]:1 | scb[0].uart_tx:1  |                   | scb[0].i2c_sda:0 | scb[0].spi_miso:1    |

| P1.2     | ctb0_oa0_out   | SmartIo[2].io[2] | tcpwm.line[3]:1       | scb[0].uart_cts:1 | tcpwm.tr_in[2]    | scb[2].i2c_scl:2 | scb[0].spi_clk:1     |

| P1.3     | ctb0_oa1_out   | SmartIo[2].io[3] | tcpwm.line_compl[3]:1 | scb[0].uart_rts:1 | tcpwm.tr_in[3]    | scb[2].i2c_sda:2 | scb[0].spi_select0:1 |

| P1.4     | ctb0_oa1-      | SmartIo[2].io[4] | tcpwm.line[6]:1       |                   |                   | scb[3].i2c_scl:0 | scb[0].spi_select1:1 |

Table 2 ピンの代替機能 (continued)

| ポート / ピン | アナログ                                        | Smart I/O        | ACT #0                | ACT #1            | ACT #3             | DS #2            | DS #3                |

|----------|---------------------------------------------|------------------|-----------------------|-------------------|--------------------|------------------|----------------------|

| P1.5     | ctb0_oa1+                                   | SmartIo[2].io[5] | tcpwm.line_compl[6]:1 |                   |                    | scb[3].i2c_sda:0 | scb[0].spi_select2:1 |

| P1.6     | ctb0_oa0+                                   | SmartIo[2].io[6] | tcpwm.line[7]:1       |                   |                    |                  | scb[0].spi_select3:1 |

| P1.7     | ctb0_oa1+<br>sar_ext_vref0<br>sar_ext_vref1 | SmartIo[2].io[7] | tcpwm.line_compl[7]:1 |                   |                    |                  | scb[2].spi_clk:1     |

| P2.0     | sarmux[0]                                   | SmartIo[0].io[0] | tcpwm.line[4]:0       | csd.comp          | tcpwm.tr_in[4]     | scb[1].i2c_scl:1 | scb[1].spi_mosi:2    |

| P2.1     | sarmux[1]                                   | SmartIo[0].io[1] | tcpwm.line_compl[4]:0 |                   | tcpwm.tr_in[5]     | scb[1].i2c_sda:1 | scb[1].spi_miso:2    |

| P2.2     | sarmux[2]                                   | SmartIo[0].io[2] | tcpwm.line[5]:1       |                   |                    |                  | scb[1].spi_clk:2     |

| P2.3     | sarmux[3]                                   | SmartIo[0].io[3] | tcpwm.line_compl[5]:1 |                   |                    |                  | scb[1].spi_select0:2 |

| P2.4     | sarmux[4]                                   | SmartIo[0].io[4] | tcpwm.line[0]:1       | scb[3].uart_rx:1  |                    |                  | scb[1].spi_select1:1 |

| P2.5     | sarmux[5]                                   | SmartIo[0].io[5] | tcpwm.line_compl[0]:1 | scb[3].uart_tx:1  |                    |                  | scb[1].spi_select2:1 |

| P2.6     | sarmux[6]                                   | SmartIo[0].io[6] | tcpwm.line[1]:1       | scb[3].uart_cts:1 |                    |                  | scb[1].spi_select3:1 |

| P2.7     | sarmux[7]                                   | SmartIo[0].io[7] | tcpwm.line_compl[1]:1 | scb[3].uart_rts:1 |                    | lpcomp.comp[0]:0 | scb[2].spi_mosi:1    |

| P6.0     |                                             |                  | tcpwm.line[4]:1       | scb[3].uart_rx:0  | can.can_tx_enb_n:0 | scb[3].i2c_scl:1 | scb[3].spi_mosi:0    |

| P6.1     |                                             |                  | tcpwm.line_compl[4]:1 | scb[3].uart_tx:0  | can.can_rx:0       | scb[3].i2c_sda:1 | scb[3].spi_miso:0    |

| P6.2     |                                             |                  | tcpwm.line[5]:0       | scb[3].uart_cts:0 | can.can_tx:0       |                  | scb[3].spi_clk:0     |

| P6.3     |                                             |                  | tcpwm.line_compl[5]:0 | scb[3].uart_rts:0 |                    |                  | scb[3].spi_select0:0 |

| P6.4     |                                             |                  | tcpwm.line[6]:0       |                   |                    | scb[4].i2c_scl   | scb[3].spi_select1:0 |

| P6.5     |                                             |                  | tcpwm.line_compl[6]:0 |                   |                    | scb[4].i2c_sda   | scb[3].spi_select2:0 |

| P3.0     |                                             | SmartIo[1].io[0] | tcpwm.line[0]:0       | scb[1].uart_rx:1  |                    | scb[1].i2c_scl:2 | scb[1].spi_mosi:0    |

Table 2 ピンの代替機能 (continued)

| ポート / ピン | アナログ         | Smart I/O        | ACT #0                | ACT #1            | ACT #3             | DS #2              | DS #3                |

|----------|--------------|------------------|-----------------------|-------------------|--------------------|--------------------|----------------------|

| P3.1     |              | SmartIo[1].io[1] | tcpwm.line_compl[0]:0 | scb[1].uart_tx:1  |                    | scb[1].i2c_sda:2   | scb[1].spi_miso:0    |

| P3.2     |              | SmartIo[1].io[2] | tcpwm.line[1]:0       | scb[1].uart_cts:1 |                    | cpuss.swd_data     | scb[1].spi_clk:0     |

| P3.3     |              | SmartIo[1].io[3] | tcpwm.line_compl[1]:0 | scb[1].uart_rts:1 |                    | cpuss.swd_clk      | scb[1].spi_select0:0 |

| P3.4     |              | SmartIo[1].io[4] | tcpwm.line[2]:0       |                   | tcpwm.tr_in[6]     |                    | scb[1].spi_select1:0 |

| P3.5     |              | SmartIo[1].io[5] | tcpwm.line_compl[2]:0 |                   |                    |                    | scb[1].spi_select2:0 |

| P3.6     |              | SmartIo[1].io[6] | tcpwm.line[3]:0       |                   |                    | scb[4].spi_select3 | scb[1].spi_select3:0 |

| P3.7     |              | SmartIo[1].io[7] | tcpwm.line_compl[3]:0 |                   |                    | lpcomp.comp[1]:1   | scb[2].spi_miso:1    |

| P4.0     | csd.vref_ext |                  |                       | scb[0].uart_rx:0  | can.can_rx:1       | scb[0].i2c_scl:1   | scb[0].spi_mosi:0    |

| P4.1     | csd.cshield  |                  |                       | scb[0].uart_tx:0  | can.can_tx:1       | scb[0].i2c_sda:1   | scb[0].spi_miso:0    |

| P4.2     | csd.cmod     |                  |                       | scb[0].uart_cts:0 | can.can_tx_enb_n:1 | lpcomp.comp[0]:1   | scb[0].spi_clk:0     |

| P4.3     | csd.csh_tank |                  |                       | scb[0].uart_rts:0 |                    | lpcomp.comp[1]:2   | scb[0].spi_select0:0 |

| P4.4     |              |                  |                       | scb[4].uart_rx    |                    | scb[4].spi_mosi    | scb[0].spi_select1:2 |

| P4.5     |              |                  |                       | scb[4].uart_tx    |                    | scb[4].spi_miso    | scb[0].spi_select2:2 |

| P4.6     |              |                  |                       | scb[4].uart_cts   |                    | scb[4].spi_clk     | scb[0].spi_select3:2 |

| P4.7     |              |                  |                       | scb[4].uart_rts   |                    | scb[4].spi_select0 |                      |

| P5.6     |              |                  | tcpwm.line[7]:0       |                   |                    | scb[4].spi_select1 | scb[2].spi_select3:0 |

| P5.7     |              |                  | tcpwm.line_compl[7]:0 |                   |                    | scb[4].spi_select2 |                      |

| P7.0     |              |                  | tcpwm.line[0]:2       | scb[3].uart_rx:2  |                    | scb[3].i2c_scl:2   | scb[3].spi_mosi:1    |

| P7.1     |              |                  | tcpwm.line_compl[0]:2 | scb[3].uart_tx:2  |                    | scb[3].i2c_sda:2   | scb[3].spi_miso:1    |

| P7.2     |              |                  | tcpwm.line[1]:2       | scb[3].uart_cts:2 |                    |                    | scb[3].spi_clk:1     |

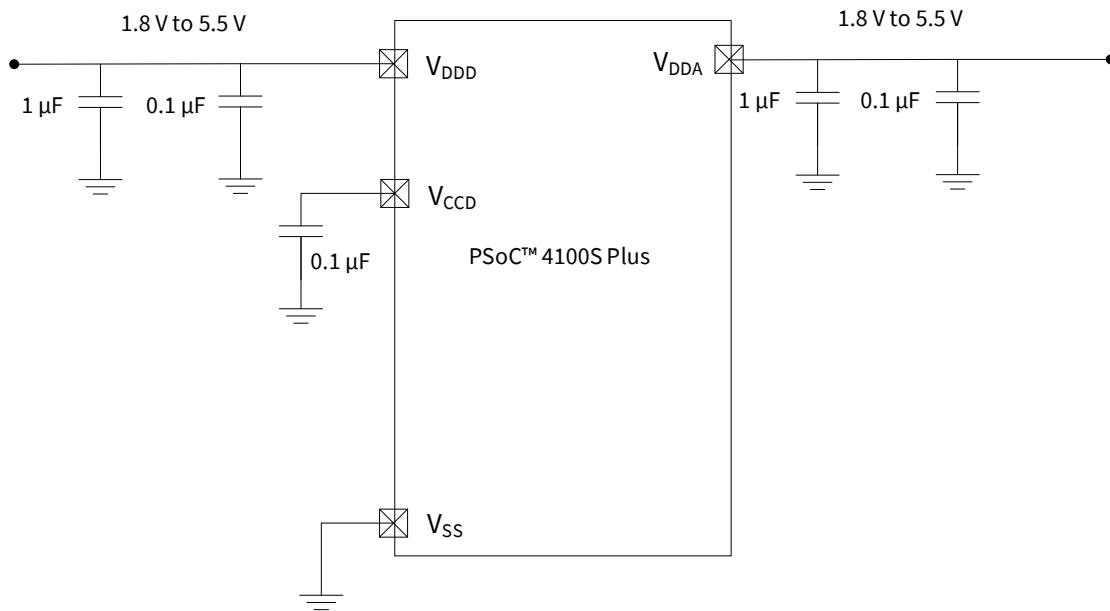

## 4 電源

以下の電源システム図に、PSoC™ 4100S プラス用に実装された電源ピンを示します。システムは、アクティブモードで動作するデジタル回路用のレギュレータが1つあります。アナログ用のレギュレータはありません。アナログ回路は  $V_{DD}$  入力から直接動作します。

**Figure 5** 電源接続

次の2つの異なる動作モードがあります。モード1では、供給電圧範囲は1.8V～5.5V(外部レギュレータ不使用、内部レギュレータは動作可能)です。モード2では、供給電圧範囲は1.8V±5%(外部レギュレータ使用、1.71～1.89V、内部レギュレータはバイパスされる)です。

### 4.1 モード1: 1.8V～5.5Vの外部電源

このモードでは、PSoC™ 4100S プラスは1.8V～5.5Vの電圧範囲の外部電源から電源供給されます。この範囲はバッテリー駆動動作にも対応します。例えばチップは、3.5Vから始まって1.8Vまで低下するバッテリーシステムから電源供給されます。このモードでは、PSoC™ 4100S プラスの内部レギュレータは内部ロジックに電源を供給し、その出力は  $V_{CCD}$  ピンに接続されます。 $V_{CCD}$  ピンは外部コンデンサ(0.1  $\mu$ F、X5Rセラミックかそれより良質なもの)を介してグランドにバイパスされ、他のどれにも接続してはいけません。

### 4.2 モード2: 1.8V±5%の外部電源

このモードでは、PSoC™ 4100S プラスは1.71V～1.89Vの外部電源から電源供給されます。この範囲には電源リップルが含まれていることに注意してください。このモードで、 $V_{DD}$  ピンと  $V_{CCD}$  ピンは互いに短絡され、バイパスされます。内部レギュレータはファームウェアで無効化できます。

バイパスコンデンサを  $V_{DDD}$  からグランドの間に接続する必要があります。この周波数範囲でのシステムの標準的な実践としては、1  $\mu$ Fレンジのコンデンサをより小さいコンデンサ(例えば、0.1  $\mu$ F)と並列で使用します。これらは単なる経験則です。しかし、重要なアプリケーションに対しては、設計に最適なバイパスを得るために、PCBレイアウト、リードインダクタンス、バイパスコンデンサ寄生容量をシミュレートする必要があることに留意してください。

バイパススキームの例を下図に示します。

Power supply bypass connections example

Figure 6 1.8 V ~ 5.5 V の外部電源 ( 内部レギュレータが有効 )

## 5 電気的仕様

### 5.1 絶対最大定格

Table 3 絶対最大定格<sup>[1]</sup>

| 仕様 ID# | パラメーター                | 説明                                                                 | Min  | Typ | Max          | 単位 | 詳細 / 条件   |

|--------|-----------------------|--------------------------------------------------------------------|------|-----|--------------|----|-----------|

| SID1   | $V_{DDD\_ABS}$        | $V_{SS}$ を基準としたデジタル電源電圧                                            | -0.5 | -   | 6            | V  | -         |

| SID2   | $V_{CCD\_ABS}$        | $V_{SS}$ を基準とした直接デジタルコア電圧入力                                        | -0.5 | -   | 1.95         |    | -         |

| SID3   | $V_{GPIO\_ABS}$       | GPIO 電圧                                                            | -0.5 | -   | $V_{DD}+0.5$ |    | -         |

| SID4   | $I_{GPIO\_ABS}$       | GPIO ごとの最大電流                                                       | -25  | -   | 25           | mA | -         |

| SID5   | $I_{GPIO\_injection}$ | GPIO 注入電流、 $V_{IH} > V_{DDD}$ の場合は Max、 $V_{IL} < V_{SS}$ の場合は Min | -0.5 | -   | 0.5          |    | ピンごとの注入電流 |

| BID44  | ESD_HBM               | 静電気放電(人体モデル)                                                       | 2200 | -   | -            | V  | -         |

| BID45  | ESD_CDM               | 静電気放電(デバイス帯電モデル)                                                   | 500  | -   | -            |    | -         |

| BID46  | LU                    | ラッチアップ時のピン電流                                                       | -140 | -   | 140          | mA | -         |

### 5.2 デバイスレベルの仕様

特記されていない限り、すべての仕様は  $-40^{\circ}\text{C} \leq T_A \leq 105^{\circ}\text{C}$  および  $T_J \leq 125^{\circ}\text{C}$  の条件で有効です。仕様は注記した場合を除いて 1.71V ~ 5.5V において有効です。

Table 4 DC 仕様

Typ 値は  $25^{\circ}\text{C}$ 、 $V_{DD} = 3.3\text{ V}$  で測定されます。

| 仕様 ID# | パラメーター    | 説明                                         | Min  | Typ | Max  | 単位            | 詳細 / 条件               |

|--------|-----------|--------------------------------------------|------|-----|------|---------------|-----------------------|

| SID53  | $V_{DD}$  | 電源ピン入力電圧                                   | 1.8  | -   | 5.5  | V             | 内部レギュレータ使用            |

| SID255 | $V_{DD}$  | 電源ピン入力電圧 ( $V_{CCD} = V_{DDD} = V_{DDA}$ ) | 1.71 | -   | 1.89 |               | 内部レギュレータ不使用           |

| SID54  | $V_{CCD}$ | 出力電圧(コアロジック用)                              | -    | 1.8 | -    |               | -                     |

| SID55  | $C_{EFC}$ | 外部レギュレータ電圧 ( $V_{CCD}$ ) バイパス              | -    | 0.1 | -    | $\mu\text{F}$ | X5R セラミックまたはこれより良質のもの |

| SID56  | $C_{EXC}$ | 電源バイパスコンデンサ                                | -    | 1   | -    |               | X5R セラミックまたはこれより良質のもの |

アクティブモード、 $V_{DD} = 1.8\text{ V} \sim 5.5\text{ V}$ 。Typ 値は  $25^{\circ}\text{C}$ 、 $V_{DD} = 3.3\text{ V}$  で測定。

|       |            |                           |   |     |     |    |  |

|-------|------------|---------------------------|---|-----|-----|----|--|

| SID10 | $I_{DD5}$  | フラッシュから実行。CPU 速度が 6 MHz。  | - | 1.8 | 2.4 | mA |  |

| SID16 | $I_{DD8}$  | フラッシュから実行。CPU 速度が 24 MHz。 | - | 3.0 | 4.6 |    |  |

| SID19 | $I_{DD11}$ | フラッシュから実行。CPU 速度が 48 MHz。 | - | 5.4 | 7.1 |    |  |

#### 注

- Table 3 に記載されている絶対最大条件を超えて使用すると、デバイスに恒久的なダメージを与える可能性があります。長時間にわたって絶対最大条件下に置くと、デバイスの信頼性に影響を与える可能性があります。最大保管温度は JEDEC 規格「JESD22-A103、High Temperature Storage Life」に準拠した  $150^{\circ}\text{C}$  です。絶対最大条件以内で使用している場合でも、標準的な動作条件を超えると、デバイスが仕様通りに動作しない可能性があります。

**Table 4 DC 仕様 (continued)**Typ 値は 25°C、 $V_{DD} = 3.3\text{ V}$  で測定されます。

| 仕様 ID#                                                                                               | パラメーター       | 説明                                                                     | Min | Typ | Max | 単位            | 詳細 / 条件                                       |

|------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------|-----|-----|-----|---------------|-----------------------------------------------|

| <b>スリープ モード、<math>V_{DD} = 1.8\text{ V} \sim 5.5\text{ V}</math> ( レギュレータが有効 )</b>                   |              |                                                                        |     |     |     |               |                                               |

| SID22                                                                                                | $I_{DD17}$   | $I^2C$ ウエイクアップ、WDT および コンパレータが有効                                       | -   | 1.1 | 1.8 | mA            | 6 MHz<br>12 MHz                               |

| SID25                                                                                                | $I_{DD20}$   | $I^2C$ ウエイクアップ、WDT および コンパレータが有効                                       | -   | 1.5 | 2.1 | mA            |                                               |

| <b>スリープ モード、<math>V_{DD} = 1.71\text{ V} \sim 1.89\text{ V}</math> ( レギュレータがバイパス )</b>               |              |                                                                        |     |     |     |               |                                               |

| SID28                                                                                                | $I_{DD23}$   | $I^2C$ ウエイクアップ、WDT、および コンパレータが有効                                       | -   | 1.1 | 1.8 | mA            | 6 MHz                                         |

| SID28A                                                                                               | $I_{DD23A}$  | $I^2C$ ウエイクアップ、WDT、および コンパレータが有効                                       | -   | 1.5 | 2.1 | mA            | 12 MHz                                        |

| <b>ディープスリープ モード、<math>V_{DD} = 1.8\text{ V} \sim 3.6\text{ V}</math> ( レギュレータが有効 )</b>               |              |                                                                        |     |     |     |               |                                               |

| SID30                                                                                                | $I_{DD25}$   | $I^2C$ ウエイクアップと WDT が有効。 $T = -40^\circ\text{C} \sim 60^\circ\text{C}$ | -   | 2.5 | 40  | $\mu\text{A}$ | $T = -40^\circ\text{C} \sim 60^\circ\text{C}$ |

| SID31                                                                                                | $I_{DD26}$   | $I^2C$ ウエイクアップと WDT が有効                                                | -   | 2.5 | 125 | $\mu\text{A}$ | Max は 3.6 V、85°C で測定                          |

| <b>ディープスリープ モード、<math>V_{DD} = 3.6\text{ V} \sim 5.5\text{ V}</math> ( レギュレータが有効 )</b>               |              |                                                                        |     |     |     |               |                                               |

| SID33                                                                                                | $I_{DD28}$   | $I^2C$ ウエイクアップと WDT が有効。 $T = -40^\circ\text{C} \sim 60^\circ\text{C}$ | -   | 2.5 | 40  | $\mu\text{A}$ | $T = -40^\circ\text{C} \sim 60^\circ\text{C}$ |

| SID34                                                                                                | $I_{DD29}$   | $I^2C$ ウエイクアップと WDT が有効                                                | -   | 2.5 | 125 | $\mu\text{A}$ | Max は 5.5 V、85°C で測定                          |

| <b>ディープスリープ モード、<math>V_{DD} = V_{CCD} = 1.71\text{ V} \sim 1.89\text{ V}</math> ( レギュレータがバイパス )</b> |              |                                                                        |     |     |     |               |                                               |

| SID36                                                                                                | $I_{DD31}$   | $I^2C$ ウエイクアップと WDT が有効。 $T = -40^\circ\text{C} \sim 60^\circ\text{C}$ | -   | 2.5 | 60  | $\mu\text{A}$ | $T = -40^\circ\text{C} \sim 60^\circ\text{C}$ |

| SID37                                                                                                | $I_{DD32}$   | $I^2C$ ウエイクアップと WDT が有効                                                | -   | 2.5 | 180 | $\mu\text{A}$ | Max は 1.89 V、85°C で測定                         |

| <b>XRES 電流</b>                                                                                       |              |                                                                        |     |     |     |               |                                               |

| SID307                                                                                               | $I_{DD\_XR}$ | XRES がアサート時の供給電流                                                       | -   | 2   | 5   | mA            | -                                             |

**Table 5 AC 仕様**

| 仕様 ID#               | パラメーター          | 説明                 | Min | Typ | Max | 単位            | 詳細 / 条件                     |

|----------------------|-----------------|--------------------|-----|-----|-----|---------------|-----------------------------|

| SID48                | $F_{CPU}$       | CPU 周波数            | DC  | -   | 48  | MHz           | $1.71 \leq V_{DD} \leq 5.5$ |

| SID49 <sup>[2]</sup> | $T_{SLEEP}$     | スリープモードからの復帰時間     | -   | 0   | -   | $\mu\text{s}$ |                             |

| SID50 <sup>[2]</sup> | $T_{DEEPSLEEP}$ | ディープスリープモードからの復帰時間 | -   | 35  | -   |               |                             |

**注**

2. 特性評価で保証されています。

### 5.2.1 GPIO

Table 6 GPIO の DC 仕様

| 仕様 ID#                | パラメーター           | 説明                                     | Min                   | Typ | Max                  | 単位 | 詳細 / 条件                                             |

|-----------------------|------------------|----------------------------------------|-----------------------|-----|----------------------|----|-----------------------------------------------------|

| SID57                 | $V_{IH}^{[3]}$   | 入力電圧 High 閾値                           | $0.7 \times V_{DDD}$  | -   | -                    | V  | CMOS 入力                                             |

| SID58                 | $V_{IL}$         | 入力電圧 Low 閾値                            | -                     | -   | $0.3 \times V_{DDD}$ |    | CMOS 入力                                             |

| SID241                | $V_{IH}^{[3]}$   | LVTTL 入力, $V_{DDD} < 2.7\text{ V}$     | $0.7 \times V_{DDD}$  | -   | -                    |    | -                                                   |

| SID242                | $V_{IL}$         | LVTTL 入力, $V_{DDD} < 2.7\text{ V}$     | -                     | -   | $0.3 \times V_{DDD}$ |    | -                                                   |

| SID243                | $V_{IH}^{[3]}$   | LVTTL 入力, $V_{DDD} \geq 2.7\text{ V}$  | 2.0                   | -   | -                    |    | -                                                   |

| SID244                | $V_{IL}$         | LVTTL 入力, $V_{DDD} \geq 2.7\text{ V}$  | -                     | -   | 0.8                  |    | -                                                   |

| SID59                 | $V_{OH}$         | 出力電圧 High レベル                          | $V_{DDD} - 0.6$       | -   | -                    |    | $V_{DDD}=3\text{ V}$ のとき、<br>$I_{OH}=4\text{ mA}$   |

| SID60                 | $V_{OH}$         | 出力電圧 High レベル                          | $V_{DDD} - 0.5$       | -   | -                    |    | $V_{DDD}=1.8\text{ V}$ のとき、<br>$I_{OH}=1\text{ mA}$ |

| SID61                 | $V_{OL}$         | 出力電圧 Low レベル                           | -                     | -   | 0.6                  |    | $V_{DDD}=1.8\text{ V}$ のとき、<br>$I_{OL}=4\text{ mA}$ |

| SID62                 | $V_{OL}$         | 出力電圧 Low レベル                           | -                     | -   | 0.6                  |    | $V_{DDD}=3\text{ V}$ のとき、<br>$I_{OL}=10\text{ mA}$  |

| SID62A                | $V_{OL}$         | 出力電圧 Low レベル                           | -                     | -   | 0.4                  |    | $V_{DDD}=3\text{ V}$ のとき、<br>$I_{OL}=3\text{ mA}$   |

| SID63                 | $R_{PULLUP}$     | プルアップ抵抗                                | 3.5                   | 5.6 | 8.5                  | kΩ | -                                                   |

| SID64                 | $R_{PULLDOWN}$   | プルダウン抵抗                                | 3.5                   | 5.6 | 8.5                  |    | -                                                   |

| SID65                 | $I_{IL}$         | 入力リーアク電流 (絶対値)                         | -                     | -   | 2                    | nA | $25^\circ\text{C}, V_{DDD} = 3.0\text{ V}$          |

| SID66                 | $C_{IN}$         | 入力静電容量                                 | -                     | -   | 7                    | pF | -                                                   |

| SID67 <sup>[4]</sup>  | $V_{HYSTTL}$     | 入力ヒステリシス LVTTL                         | 25                    | 40  | -                    | mV | $V_{DDD} \geq 2.7\text{ V}$                         |

| SID68 <sup>[4]</sup>  | $V_{HYSCMOS}$    | 入力ヒステリシス CMOS                          | $0.05 \times V_{DDD}$ | -   | -                    |    | $V_{DD} < 4.5\text{ V}$                             |

| SID68A <sup>[4]</sup> | $V_{HYSCMOS5V5}$ | 入力ヒステリシス CMOS                          | 200                   | -   | -                    |    | $V_{DD} > 4.5\text{ V}$                             |

| SID69 <sup>[4]</sup>  | $I_{DIODE}$      | 保護ダイオードをとおって<br>$V_{DD}/V_{SS}$ に流れる電流 | -                     | -   | 100                  | μA | -                                                   |

| SID69A <sup>[4]</sup> | $I_{TOT\_GPIO}$  | ソースおよびシンク電流を<br>チップ全体で合計した値の<br>最大値    | -                     | -   | 200                  | mA | -                                                   |

#### 注

- 3.  $V_{IH}$  は  $V_{DDD} + 0.2\text{ V}$  を越えてはいけません。

- 4. 特性評価で保証されています。

**Table 7** GPIO の AC 仕様

(特性評価で保証)

| 仕様 ID# | パラメーター         | 説明                                                              | Min | Typ | Max  | 単位  | 詳細 / 条件                                         |

|--------|----------------|-----------------------------------------------------------------|-----|-----|------|-----|-------------------------------------------------|

| SID70  | $T_{RISEF}$    | ストロング モードでの立ち上り時間                                               | 2   | -   | 12   | ns  | 3.3 V $V_{DDD}$ ,<br>$C_{load} = 25 \text{ pF}$ |

| SID71  | $T_{FALLF}$    | ストロング モードでの立ち下り時間                                               | 2   | -   | 12   |     | 3.3 V $V_{DDD}$ ,<br>$C_{load} = 25 \text{ pF}$ |

| SID72  | $T_{RISES}$    | 低速ストロング モードでの立ち上り時間                                             | 10  | -   | 60   | -   | 3.3 V $V_{DDD}$ ,<br>$C_{load} = 25 \text{ pF}$ |

| SID73  | $T_{FALLS}$    | 低速ストロング モードでの立ち下り時間                                             | 10  | -   | 60   | -   | 3.3 V $V_{DDD}$ ,<br>$C_{load} = 25 \text{ pF}$ |

| SID74  | $F_{GPIOOUT1}$ | GPIO $F_{OUT}$ 。3.3 V $\leq V_{DDD} \leq$ 5.5 V<br>高速ストロング モード  | -   | -   | 33   | MHz | 90/10%, 負荷 25 pF、<br>デューティ比 60/40               |

| SID75  | $F_{GPIOOUT2}$ | GPIO $F_{OUT}$ 。1.71 V $\leq V_{DDD} \leq$ 3.3 V<br>高速ストロング モード | -   | -   | 16.7 |     | 90/10%, 負荷 25 pF、<br>デューティ比 60/40               |

| SID76  | $F_{GPIOOUT3}$ | GPIO $F_{OUT}$ 。3.3 V $\leq V_{DDD} \leq$ 5.5 V<br>低速ストロング モード  | -   | -   | 7    |     | 90/10%, 負荷 25 pF、<br>デューティ比 60/40               |

| SID245 | $F_{GPIOOUT4}$ | GPIO $F_{OUT}$ 。1.71 V $\leq V_{DDD} \leq$ 3.3 V<br>低速ストロング モード | -   | -   | 3.5  |     | 90/10%, 負荷 25 pF、<br>デューティ比 60/40               |

| SID246 | $F_{GPIOIN}$   | GPIO 入力の動作周波数。<br>1.71 V $\leq V_{DDD} \leq$ 5.5 V              | -   | -   | 48   |     | $V_{IO}$ の 90/10%                               |

## 5.2.2 XRES

**Table 8** XRES の DC 仕様

| 仕様 ID#               | パラメーター        | 説明                                     | Min                  | Typ | Max                  | 単位 | 詳細 / 条件                                               |

|----------------------|---------------|----------------------------------------|----------------------|-----|----------------------|----|-------------------------------------------------------|

| SID77                | $V_{IH}$      | 入力電圧 High 閾値                           | $0.7 \times V_{DDD}$ | -   | -                    | V  | CMOS 入力                                               |

| SID78                | $V_{IL}$      | 入力電圧 Low 閾値                            | -                    | -   | $0.3 \times V_{DDD}$ |    |                                                       |

| SID79                | $R_{PULLUP}$  | プルアップ抵抗                                | -                    | 60  | -                    | kΩ | -                                                     |

| SID80                | $C_{IN}$      | 入力静電容量                                 | -                    | -   | 7                    | pF | -                                                     |

| SID81 <sup>[5]</sup> | $V_{HYSXRES}$ | 入力電圧ヒステリシス                             | -                    | 100 | -                    | mV | $V_{DD} > 4.5 \text{ V}$ 時の標準<br>ヒステリシス電圧<br>が 200 mV |

| SID82                | $I_{DIODE}$   | 保護ダイオードをとおって<br>$V_{DD}/V_{SS}$ に流れる電流 | -                    | -   | 100                  | μA |                                                       |

**Table 9** XRES の AC 仕様

| 仕様 ID#                | パラメーター           | 説明            | Min | Typ | Max | 単位 | 詳細 / 条件 |

|-----------------------|------------------|---------------|-----|-----|-----|----|---------|

| SID83 <sup>[5]</sup>  | $T_{RESETWIDTH}$ | リセット パルス幅     | 1   | -   | -   | μs | -       |

| BID194 <sup>[5]</sup> | $T_{RESETWAKE}$  | リセット解除からの復帰時間 | -   | -   | 2.7 | ms | -       |

## 注

5. 特性評価で保証されています。

## 5.3 アナログ ペリフェラル

### 5.3.1 CTBm オペアンプ

Table 10 CTBm オペアンプの仕様

| 仕様 ID#   | パラメーター              | 説明                                             | Min | Typ  | Max  | 単位  | 詳細 / 条件                           |

|----------|---------------------|------------------------------------------------|-----|------|------|-----|-----------------------------------|

|          | $I_{DD}$            | オペアンプ ブロック電流、外部負荷                              |     |      |      |     |                                   |

| SID269   | $I_{DD\_HI}$        | 電力 = 高                                         | -   | 1100 | 1850 | μA  | -                                 |

| SID270   | $I_{DD\_MED}$       | 電力 = 中                                         | -   | 550  | 950  |     | -                                 |

| SID271   | $I_{DD\_LOW}$       | 電力 = 低                                         | -   | 150  | 350  |     | -                                 |

|          | $G_{BW}$            | 負荷 = 20 pF, 0.1 mA<br>$V_{DDA} = 2.7\text{ V}$ |     |      |      |     |                                   |

| SID272   | $G_{BW\_HI}$        | 電力 = 高                                         | 6   | -    | -    | MHz | 入力および出力は 0.2 V ~ $V_{DDA}$ -0.2 V |

| SID273   | $G_{BW\_MED}$       | 電力 = 中                                         | 3   | -    | -    |     | 入力および出力は 0.2 V ~ $V_{DDA}$ -0.2 V |

| SID274   | $G_{BW\_LO}$        | 電力 = 低                                         | -   | 1    | -    |     | 入力および出力は 0.2 V ~ $V_{DDA}$ -0.2 V |

|          | $I_{OUT\_MAX}$      | $V_{DDA} = 2.7\text{ V}$ 、電源電圧より 500 mV 内側     |     |      |      |     |                                   |

| SID275   | $I_{OUT\_MAX\_HI}$  | 電力 = 高                                         | 10  | -    | -    | mA  | 出力は 0.5 V ~ $V_{DDA}$ -0.5 V      |

| SID276   | $I_{OUT\_MAX\_MID}$ | 電力 = 中                                         | 10  | -    | -    |     | 出力は 0.5 V ~ $V_{DDA}$ -0.5 V      |

| SID277   | $I_{OUT\_MAX\_LO}$  | 電力 = 低                                         | -   | 5    | -    |     | 出力は 0.5 V ~ $V_{DDA}$ -0.5 V      |

|          | $I_{OUT}$           | $V_{DDA} = 1.71\text{ V}$ 、電源電圧より 500 mV 内側    |     |      |      |     |                                   |

| SID278   | $I_{OUT\_MAX\_HI}$  | 電力 = 高                                         | 4   | -    | -    | mA  | 出力は 0.5 V ~ $V_{DDA}$ -0.5 V      |

| SID279   | $I_{OUT\_MAX\_MID}$ | 電力 = 中                                         | 4   | -    | -    |     | 出力は 0.5 V ~ $V_{DDA}$ -0.5 V      |

| SID280   | $I_{OUT\_MAX\_LO}$  | 電力 = 低                                         | -   | 2    | -    |     | 出力は 0.5 V ~ $V_{DDA}$ -0.5 V      |

|          | $I_{DD\_Int}$       | オペアンプ ブロック電流、内部負荷                              |     |      |      |     |                                   |

| SID269_I | $I_{DD\_HI\_Int}$   | 電力 = 高                                         | -   | 1500 | 1700 | μA  | -                                 |

| SID270_I | $I_{DD\_MED\_Int}$  | 電力 = 中                                         | -   | 700  | 900  |     | -                                 |

| SID271_I | $I_{DD\_LOW\_Int}$  | 電力 = 低                                         | -   | -    | -    |     | -                                 |

|          | $G_{BW}$            | $V_{DDA} = 2.7\text{ V}$                       | -   | -    | -    |     | -                                 |

| SID272_I | $G_{BW\_HI\_Int}$   | 電力 = 高                                         | 8   | -    | -    | MHz | 出力は 0.25 V ~ $V_{DDA}$ -0.25 V    |

|          |                     | 内部モード、外部モード両方のオペアンプの一般仕様                       |     |      |      |     |                                   |

**Table 10 CTBm オペアンプの仕様 (continued)**

| 仕様 ID#  | パラメーター                | 説明                                                        | Min   | Typ  | Max                   | 単位      | 詳細 / 条件                                                          |

|---------|-----------------------|-----------------------------------------------------------|-------|------|-----------------------|---------|------------------------------------------------------------------|

| SID281  | V <sub>IN</sub>       | チャージポンプが有効、V <sub>DDA</sub> = 2.7 V                       | -0.05 | -    | V <sub>DDA</sub> -0.2 | V       | -                                                                |

| SID282  | V <sub>CM</sub>       | チャージポンプが有効、V <sub>DDA</sub> = 2.7 V                       | -0.05 | -    | V <sub>DDA</sub> -0.2 |         | -                                                                |

|         | V <sub>OUT</sub>      | V <sub>DDA</sub> = 2.7 V                                  |       |      |                       |         |                                                                  |

| SID283  | V <sub>OUT_1</sub>    | 電力 = 高、I <sub>load</sub> =10 mA                           | 0.5   | -    | V <sub>DDA</sub> -0.5 | V       | -                                                                |

| SID284  | V <sub>OUT_2</sub>    | 電力 = 高、I <sub>load</sub> =1 mA                            | 0.2   | -    | V <sub>DDA</sub> -0.2 |         | -                                                                |

| SID285  | V <sub>OUT_3</sub>    | 電力 = 中、I <sub>load</sub> =1 mA                            | 0.2   | -    | V <sub>DDA</sub> -0.2 |         | -                                                                |

| SID286  | V <sub>OUT_4</sub>    | 電力 = 低、I <sub>load</sub> =0.1 mA                          | 0.2   | -    | V <sub>DDA</sub> -0.2 |         | -                                                                |

| SID288  | V <sub>OS_DR</sub>    | オフセット電圧(トリム後)                                             | -1.0  | ±0.5 | 1.0                   | mV      | 高電力モード、入力は0 V～V <sub>DDA</sub> -0.2 V                            |

| SID288A | V <sub>OS_DR</sub>    | オフセット電圧(トリム後)                                             | -     | ±1   | -                     |         | 中電力モード、入力は0 V～V <sub>DDA</sub> -0.2 V                            |

| SID288B | V <sub>OS_DR</sub>    | オフセット電圧(トリム後)                                             | -     | ±2   | -                     |         | 低電力モード、入力は0 V～V <sub>DDA</sub> -0.2 V                            |

| SID290  | V <sub>OS_DR_DR</sub> | オフセット電圧ドリフト(トリム後)                                         | -10   | ±3   | 10                    | μV/°C   | 高電力モード                                                           |

| SID290A | V <sub>OS_DR_DR</sub> | オフセット電圧ドリフト(トリム後)                                         | -     | ±10  | -                     | μV/°C   | 中電力モード                                                           |

| SID290B | V <sub>OS_DR_DR</sub> | オフセット電圧ドリフト(トリム後)                                         | -     | ±10  | -                     |         | 低電力モード                                                           |

| SID291  | CMRR                  | DC                                                        | 70    | 80   | -                     | dB      | 入力は0 V～V <sub>DDA</sub> -0.2 V、出力は0.2 V～V <sub>DDA</sub> -0.2 V  |

| SID292  | PSRR                  | 周波数 = 1 kHz、リップル = 10 mV                                  | 70    | 85   | -                     |         | V <sub>DDD</sub> = 3.6 V、高電力モード、入力は0.2 V～V <sub>DDA</sub> -0.2 V |

|         | 雑音                    |                                                           |       |      |                       |         |                                                                  |

| SID294  | VN2                   | 入力基準、1 kHz、電力 = 高                                         | -     | 72   | -                     | nV/rtHz | 入力と出力は0.2 V～V <sub>DDA</sub> -0.2 V                              |

| SID295  | VN3                   | 入力基準、10 kHz、電力 = 高                                        | -     | 28   | -                     |         | 入力と出力は0.2 V～V <sub>DDA</sub> -0.2 V                              |

| SID296  | VN4                   | 入力基準、100 kHz、電力 = 高                                       | -     | 15   | -                     |         | 入力と出力は0.2 V～V <sub>DDA</sub> -0.2 V                              |

| SID297  | C <sub>LOAD</sub>     | 最大負荷まで安定。50 pFで性能仕様を満たす                                   | -     | -    | 125                   | pF      | -                                                                |

| SID298  | SLEW_RATE             | C <sub>load</sub> = 50 pF、電力 = 高、V <sub>DDA</sub> = 2.7 V | 6     | -    | -                     | V/μs    | -                                                                |

**Table 10** CTBm オペアンプの仕様 (*continued*)

| 仕様 ID#    | パラメーター            | 説明                                                | Min | Typ  | Max | 単位  | 詳細 / 条件                                  |

|-----------|-------------------|---------------------------------------------------|-----|------|-----|-----|------------------------------------------|

| SID299    | T_OP_WAKE         | 無効から有効までの時間。<br>外付け RC 無し                         | -   | -    | 25  | μs  | -                                        |

| SID299A   | OL_GAIN           | オープンループゲイン                                        | -   | 90   | -   | dB  |                                          |

|           | COMP_MODE         | コンパレータモード、50 mV<br>駆動、 $T_{rise}=T_{fall}$ (おおよそ) |     |      |     |     |                                          |

| SID300    | TPD1              | 応答時間。電力 = 高                                       | -   | 150  | -   | ns  | 入力は<br>0.2 V ~ $V_{DDA}$ -0.2 V          |

| SID301    | TPD2              | 応答時間。電力 = 中                                       | -   | 500  | -   |     | 入力は<br>0.2 V ~ $V_{DDA}$ -0.2 V          |

| SID302    | TPD3              | 応答時間。電力 = 低                                       | -   | 2500 | -   |     | 入力は<br>0.2 V ~ $V_{DDA}$ -0.2 V          |

| SID303    | VHYST_OP          | ヒステリシス                                            | -   | 10   | -   | mV  | -                                        |

| SID304    | WUP_CTB           | イネーブル状態から使用可能までの所要時間                              | -   | -    | 25  | μs  | -                                        |

|           | ディープス<br>リープモード   | モード 2 は最低電流範囲。<br>モード 1 はより高い GBW を持つ。            |     |      |     |     |                                          |

| SID_DS_1  | $I_{DD\_HI\_M1}$  | モード 1、高電流                                         | -   | 1400 | -   | μA  | 25°C                                     |

| SID_DS_2  | $I_{DD\_MED\_M1}$ | モード 1、中電流                                         | -   | 700  | -   |     | 25°C                                     |

| SID_DS_3  | $I_{DD\_LOW\_M1}$ | モード 1、低電流                                         | -   | 200  | -   |     | 25°C                                     |

| SID_DS_4  | $I_{DD\_HI\_M2}$  | モード 2、高電流                                         | -   | 120  | -   |     | 25°C                                     |

| SID_DS_5  | $I_{DD\_MED\_M2}$ | モード 2、中電流                                         | -   | 60   | -   |     | 25°C                                     |

| SID_DS_6  | $I_{DD\_LOW\_M2}$ | モード 2、低電流                                         | -   | 15   | -   |     | 25°C                                     |

| SID_DS_7  | $G_{BW\_HI\_M1}$  | モード 1、高電流                                         | -   | 4    | -   | MHz | 20pF 負荷、DC 負荷なし、0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_8  | $G_{BW\_MED\_M1}$ | モード 1、中電流                                         | -   | 2    | -   |     | 20pF 負荷、DC 負荷なし、0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_9  | $G_{BW\_LOW\_M1}$ | モード 1、低電流                                         | -   | 0.5  | -   |     | 20pF 負荷、DC 負荷なし、0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_10 | $G_{BW\_HI\_M2}$  | モード 2、高電流                                         | -   | 0.5  | -   |     | 20pF 負荷、DC 負荷なし、0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_11 | $G_{BW\_MED\_M2}$ | モード 2、中電流                                         | -   | 0.2  | -   |     | 20pF 負荷、DC 負荷なし、0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_12 | $G_{BW\_Low\_M2}$ | モード 2、低電流                                         | -   | 0.1  | -   |     | 20pF 負荷、DC 負荷なし、0.2 V ~ $V_{DDA}$ -0.2 V |

**Table 10** CTBm オペアンプの仕様 (*continued*)

| 仕様 ID#    | パラメーター             | 説明        | Min | Typ | Max | 単位 | 詳細 / 条件                                |

|-----------|--------------------|-----------|-----|-----|-----|----|----------------------------------------|

| SID_DS_13 | $V_{OS\_HI\_M1}$   | モード 1、高電流 | -   | 5   | -   | mV | トリム後、25°C、<br>0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_14 | $V_{OS\_MED\_M1}$  | モード 1、中電流 | -   | 5   | -   |    | トリム後、25°C、<br>0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_15 | $V_{OS\_LOW\_M1}$  | モード 1、低電流 | -   | 5   | -   |    | トリム後、25°C、<br>0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_16 | $V_{OS\_HI\_M2}$   | モード 2、高電流 | -   | 5   | -   |    | トリム後、25°C、<br>0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_17 | $V_{OS\_MED\_M2}$  | モード 2、中電流 | -   | 5   | -   |    | トリム後、25°C、<br>0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_18 | $V_{OS\_LOW\_M2}$  | モード 2、低電流 | -   | 5   | -   |    | トリム後、25°C、<br>0.2 V ~ $V_{DDA}$ -0.2 V |

| SID_DS_19 | $I_{OUT\_HI\_M1}$  | モード 1、高電流 | -   | 10  | -   | mA | 出力は 0.5 V ~<br>$V_{DDA}$ -0.5 V        |

| SID_DS_20 | $I_{OUT\_MED\_M1}$ | モード 1、中電流 | -   | 10  | -   |    | 出力は 0.5 V ~<br>$V_{DDA}$ -0.5 V        |

| SID_DS_21 | $I_{OUT\_LOW\_M1}$ | モード 1、低電流 | -   | 4   | -   |    | 出力は 0.5 V ~<br>$V_{DDA}$ -0.5 V        |

| SID_DS_22 | $I_{OUT\_HI\_M2}$  | モード 2、高電流 | -   | 1   | -   |    |                                        |

| SID_DS_23 | $I_{OUT\_MED\_M2}$ | モード 2、中電流 | -   | 1   | -   |    |                                        |

| SID_DS_24 | $I_{OUT\_LOW\_M2}$ | モード 2、低電流 | -   | 0.5 | -   |    |                                        |

### 5.3.2 コンパレータ

**Table 11** コンパレータの DC 仕様

| 仕様 ID#  | パラメーター        | 説明                   | Min | Typ | Max            | 単位            | 詳細 / 条件                             |

|---------|---------------|----------------------|-----|-----|----------------|---------------|-------------------------------------|

| SID84   | $V_{OFFSET1}$ | 入力オフセット電圧 (工場出荷時トリム) | -   | -   | $\pm 10$       | mV            |                                     |

| SID85   | $V_{OFFSET2}$ | 入力オフセット電圧 (カスタムトリム)  | -   | -   | $\pm 4$        |               |                                     |

| SID86   | $V_{HYST}$    | 有効時のヒステリシス           | -   | 10  | 35             |               |                                     |

| SID87   | $V_{ICM1}$    | 通常モードでの入力同相電圧        | 0   | -   | $V_{DDD}-0.1$  | V             | モード 1 およびモード 2                      |

| SID247  | $V_{ICM2}$    | 低消費電力モードでの入力同相電圧     | 0   | -   | $V_{DDD}$      |               |                                     |

| SID247A | $V_{ICM3}$    | 超低消費電力モードでの入力同相電圧    | 0   | -   | $V_{DDD}-1.15$ |               | -40°C で $V_{DDD} \geq 2.2\text{ V}$ |

| SID88   | $C_{MRR}$     | 同相信号除去比              | 50  | -   | -              | dB            | $V_{DDD} \geq 2.7\text{ V}$         |

| SID88A  | $C_{MRR}$     | 同相信号除去比              | 42  | -   | -              |               | $V_{DDD} \leq 2.7\text{ V}$         |

| SID89   | $I_{CMP1}$    | 通常モードでのブロック電流        | -   | -   | 400            | $\mu\text{A}$ |                                     |

| SID248  | $I_{CMP2}$    | 低消費電力モードでのブロック電流     | -   | -   | 100            |               |                                     |

| SID259  | $I_{CMP3}$    | 超低消費電力モードでのブロック電流    | -   | -   | 6              |               | -40°C で $V_{DDD} \geq 2.2\text{ V}$ |

| SID90   | $Z_{CMP}$     | コンパレータの DC 入力インピーダンス | 35  | -   | -              | MΩ            |                                     |

**Table 12** コンパレータの AC 仕様

| 仕様 ID# | パラメーター | 説明                              | Min | Typ | Max | 単位 | 詳細 / 条件                             |

|--------|--------|---------------------------------|-----|-----|-----|----|-------------------------------------|

| SID91  | TRESP1 | 通常モードでの応答時間、50 mV オーバードライブ      | -   | 38  | 110 | ns |                                     |

| SID258 | TRESP2 | 低消費電力モードでの応答時間、50 mV オーバードライブ   | -   | 70  | 200 |    |                                     |

| SID92  | TRESP3 | 超低消費電力モードでの応答時間、200 mV オーバードライブ | -   | 2.3 | 15  | μs | -40°C で $V_{DDD} \geq 2.2\text{ V}$ |

### 5.3.3 温度センサー

**Table 13** 温度センサー仕様

| 仕様 ID# | パラメーター   | 説明       | Min | Typ     | Max | 単位 | 詳細 / 条件       |

|--------|----------|----------|-----|---------|-----|----|---------------|

| SID93  | TSENSACC | 温度センサー精度 | -5  | $\pm 1$ | 5   | °C | -40°C ~ +85°C |

#### 注

- 特性評価で保証されています。

### 5.3.4 SAR ADC

Table 14 SAR ADC の仕様

| 仕様 ID#                 | パラメーター    | 説明                | Min             | Typ | Max              | 単位  | 詳細 / 条件                |

|------------------------|-----------|-------------------|-----------------|-----|------------------|-----|------------------------|

| <b>SAR ADC の DC 仕様</b> |           |                   |                 |     |                  |     |                        |

| SID94                  | A_RES     | 分解能               | -               | -   | 12               | ビット |                        |

| SID95                  | A_CHNLS_S | チャネル数 - シングルエンド   | -               | -   | 16               |     |                        |

| SID96                  | A_CHNKS_D | チャネル数 - 差動        | -               | -   | 4                |     | 差動チャネルの入力は隣接する I/O を使用 |

| SID97                  | A-MONO    | 単調増加性             | -               | -   | -                |     | 有                      |

| SID98                  | A_GAINERR | ゲイン誤差             | -               | -   | ±0.1             | %   | 外部基準電圧あり               |

| SID99                  | A_OFFSET  | 入力オフセット電圧         | -               | -   | 2                | mV  | 1V 基準電圧で測定             |

| SID100                 | A_ISAR    | 消費電流              | -               | -   | 1                | mA  |                        |

| SID101                 | A_VINS    | 入力電圧範囲 - シングルエンド  | V <sub>SS</sub> | -   | V <sub>DDA</sub> | V   |                        |

| SID102                 | A_VIND    | 入力電圧範囲 - 差動       | V <sub>SS</sub> | -   | V <sub>DDA</sub> | V   |                        |

| SID103                 | A_INRES   | 入力抵抗              | -               | -   | 2.2              | kΩ  |                        |

| SID104                 | A_INCAP   | 入力静電容量            | -               | -   | 10               | pF  |                        |

| SID260                 | VREFSAR   | SAR 用の調整された内部基準電圧 | 1.188           | 1.2 | 1.212            | V   |                        |

### SAR ADC の AC 仕様

|         |            |                                               |      |   |          |      |                                           |

|---------|------------|-----------------------------------------------|------|---|----------|------|-------------------------------------------|

| SID106  | A_PSRR     | 電源電圧変動除去比                                     | 70   | - | -        | dB   |                                           |

| SID107  | A_CMRR     | 同相信号除去比                                       | 66   | - | -        | dB   | 1V で測定                                    |

| SID108  | A_SAMP     | サンプルレート                                       | -    | - | 1        | Msp  |                                           |

| SID109  | A_SNR      | 信号対雑音および歪み比 (SINAD)                           | 65   | - | -        | dB   | F <sub>IN</sub> = 10 kHz                  |

| SID110  | A_BW       | エイリアシングが発生しない入力帯域幅                            | -    | - | A_samp/2 | kHz  |                                           |

| SID111  | A_INL      | 積分非直線性 V <sub>DD</sub> = 1.71 ~ 5.5V、1 Msp    | -1.7 | - | 2        | LSB  | V <sub>REF</sub> = 1 ~ V <sub>DD</sub>    |

| SID111A | A_INL      | 積分非直線性 V <sub>DDD</sub> = 1.71 ~ 3.6V、1 Msp   | -1.5 | - | 1.7      | LSB  | V <sub>REF</sub> = 1.71 ~ V <sub>DD</sub> |

| SID111B | A_INL      | 積分非直線性 V <sub>DD</sub> = 1.71 ~ 5.5V、500 ksps | -1.5 | - | 1.7      | LSB  | V <sub>REF</sub> = 1 ~ V <sub>DD</sub>    |

| SID112  | A_DNL      | 微分非直線性 V <sub>DD</sub> = 1.71 ~ 5.5V、1 Msp    | -1   | - | 2.2      | LSB  | V <sub>REF</sub> = 1 ~ V <sub>DD</sub>    |

| SID112A | A_DNL      | 微分非直線性 V <sub>DD</sub> = 1.71 ~ 3.6V、1 Msp    | -1   | - | 2        | LSB  | V <sub>REF</sub> = 1.71 ~ V <sub>DD</sub> |

| SID112B | A_DNL      | 微分非直線性 V <sub>DD</sub> = 1.71 ~ 5.5V、500 ksps | -1   | - | 2.2      | LSB  | V <sub>REF</sub> = 1 ~ V <sub>DD</sub>    |

| SID113  | A_THD      | 全高調波歪み                                        | -    | - | -65      | dB   | F <sub>IN</sub> = 10 kHz                  |

| SID261  | FSARINTREF | SAR 動作速度 (外部基準バイパスコンデンサ無し)                    | -    | - | 100      | ksps | 12 ビット分解能                                 |

### 5.3.5 CSD および IDAC

Table 15 CSD および IDAC 仕様

| 仕様 ID#      | パラメーター         | 説明                            | Min  | Typ | Max             | 単位    | 詳細 / 条件                                                                                           |

|-------------|----------------|-------------------------------|------|-----|-----------------|-------|---------------------------------------------------------------------------------------------------|

| SYS.PER#3   | VDD_RIPPLE     | 電源の最大許容リップル (DC ~ 10MHz 帯域)   | -    | -   | ±50             | mV    | $V_{DD} > 2\text{ V}$ (リップルあり), $T_A = 25^\circ\text{C}$ , 感度 = 0.1 pF                            |

| SYS.PER#16  | VDD_RIPPLE_1.8 | 電源の最大許容リップル (DC ~ 10MHz 帯域)   | -    | -   | ±25             | mV    | $V_{DD} > 1.75\text{ V}$ (リップルあり), $T_A = 25^\circ\text{C}$ , 寄生容量 ( $C_P$ ) < 20 pF, 感度 ≥ 0.4 pF |

| SID.CSD.BLK | ICSD           | 最大ブロック電流                      | -    | -   | 4000            | μA    | コンパレータ, バッファ, および基準電圧生成器を含む動的(スイッチング)モードでの両 IDAC の最大ブロック電流                                        |

| SID.CSD#15  | $V_{REF}$      | CSD およびコンパレータ用の基準電圧           | 0.6  | 1.2 | $V_{DDA} - 0.6$ | V     | $V_{DDA} - 0.6$ または 4.4 (いずれか低い方)                                                                 |

| SID.CSD#15A | VREF_EXT       | CSD およびコンパレータ用の外部基準電圧         | 0.6  |     | $V_{DDA} - 0.6$ | V     | $V_{DDA} - 0.6$ or 4.4 (いずれか低い方)                                                                  |

| SID.CSD#16  | IDAC1IDD       | IDAC1(7 ビット)ブロック電流            | -    | -   | 1750            | μA    |                                                                                                   |

| SID.CSD#17  | IDAC2IDD       | IDAC2(7 ビット)ブロック電流            | -    | -   | 1750            | μA    |                                                                                                   |

| SID308      | VCSD           | 動作電圧範囲                        | 1.71 | -   | 5.5             | V     | $1.8\text{ V} \pm 5\%$ または $1.8\text{ V} \sim 5.5\text{ V}$                                       |

| SID308A     | VCOMPIDAC      | IDAC の最大電圧範囲                  | 0.6  | -   | $V_{DDA} - 0.6$ | V     | $V_{DDA} - 0.6$ または 4.4 (いずれか低い方)                                                                 |

| SID309      | IDAC1DNL       | DNL                           | -1   | -   | 1               | LSB   |                                                                                                   |

| SID310      | IDAC1INL       | INL                           | -2   | -   | 2               | LSB   | $V_{DDA} < 2\text{ V}$ の場合、INL が ±5.5 LSB                                                         |

| SID311      | IDAC2DNL       | DNL                           | -1   | -   | 1               | LSB   |                                                                                                   |

| SID312      | IDAC2INL       | INL                           | -2   | -   | 2               | LSB   | $V_{DDA} < 2\text{ V}$ の場合、INL が ±5.5 LSB                                                         |

| SID313      | SNR            | 指の信号と雑音のカウント比。<br>特性評価で保証     | 5    | -   | -               | Ratio | 静電容量範囲 = 5pF ~ 35pF, 感度 = 0.1pF。すべてのユースケース。<br>$V_{DDA} > 2\text{ V}$                             |

| SID314      | IDAC1CRT1      | 低域での IDAC1(7 ビット)の出力電流        | 4.2  | -   | 5.4             | μA    | LSB = 37.5nA (Typ)                                                                                |

| SID314A     | IDAC1CRT2      | 中域での IDAC1(7 ビット)の出力電流        | 34   | -   | 41              | μA    | LSB = 300nA (Typ)                                                                                 |

| SID314B     | IDAC1CRT3      | 高域での IDAC1(7 ビット)の出力電流        | 275  | -   | 330             | μA    | LSB = 2.4μA (Typ)                                                                                 |

| SID314C     | IDAC1CRT12     | 低域での IDAC1(7 ビット)の出力電流、2X モード | 8    | -   | 10.5            | μA    | LSB = 75nA (Typ)                                                                                  |