---

本ドキュメントは Cypress (サイプレス) 製品に関する情報が記載されております。本ドキュメントには、「MB」から始まるシリーズ名、品名およびオーダ型格が記載されておりますが、これらはすべて「CY」から始まるシリーズ名、品名およびオーダ型格として、新規および既存のお客様に引き続き提供してまいります。

#### オーダ型格の調べ方について

1. [www.cypress.com/pdn](http://www.cypress.com/pdn)にアクセスしてください。

2. SEARCH PCNS フィールドに、オーダ型格などのキーワードを入力し、「Apply」をクリックしてください。

3. 該当するタイトル>Title)をクリックしてください。

4. 「Affected Parts List」ファイルを開いてください。

当該ファイルに記載されている各種変更情報をご利用ください。

#### 詳しいお問い合わせ先

Cypress 製品およびそのソリューションの詳細につきましては、お近くの営業所へお問い合わせください。

#### サイプレスについて

サイプレスは、世界で最も革新的な車載や産業機器、スマート家電、民生機器および医療機器製品向けに、最先端の組み込みシステム ソリューションを提供するリーディング カンパニーです。サイプレスのマイクロコントローラーや、アナログ IC、ワイヤレスおよび USB ベースのコネクティビティ ソリューション、高い信頼性と高性能を提供するメモリ製品は、各種機器メーカーの差異化製品の開発と早期市場参入を支援します。サイプレスは、ベストクラスのサポートと開発リソースをグローバルに提供することで、彼らが従来市場を破壊しまったく新しい製品カテゴリを歴史的なスピードで市場投入できるよう支援します。詳細はサイプレスのウェブサイト ([japan.cypress.com](http://japan.cypress.com)) をご覧ください。

MB9AA40NB シリーズ

32ビット ARM® Cortex®-M3

FM3 マイクロコントローラ

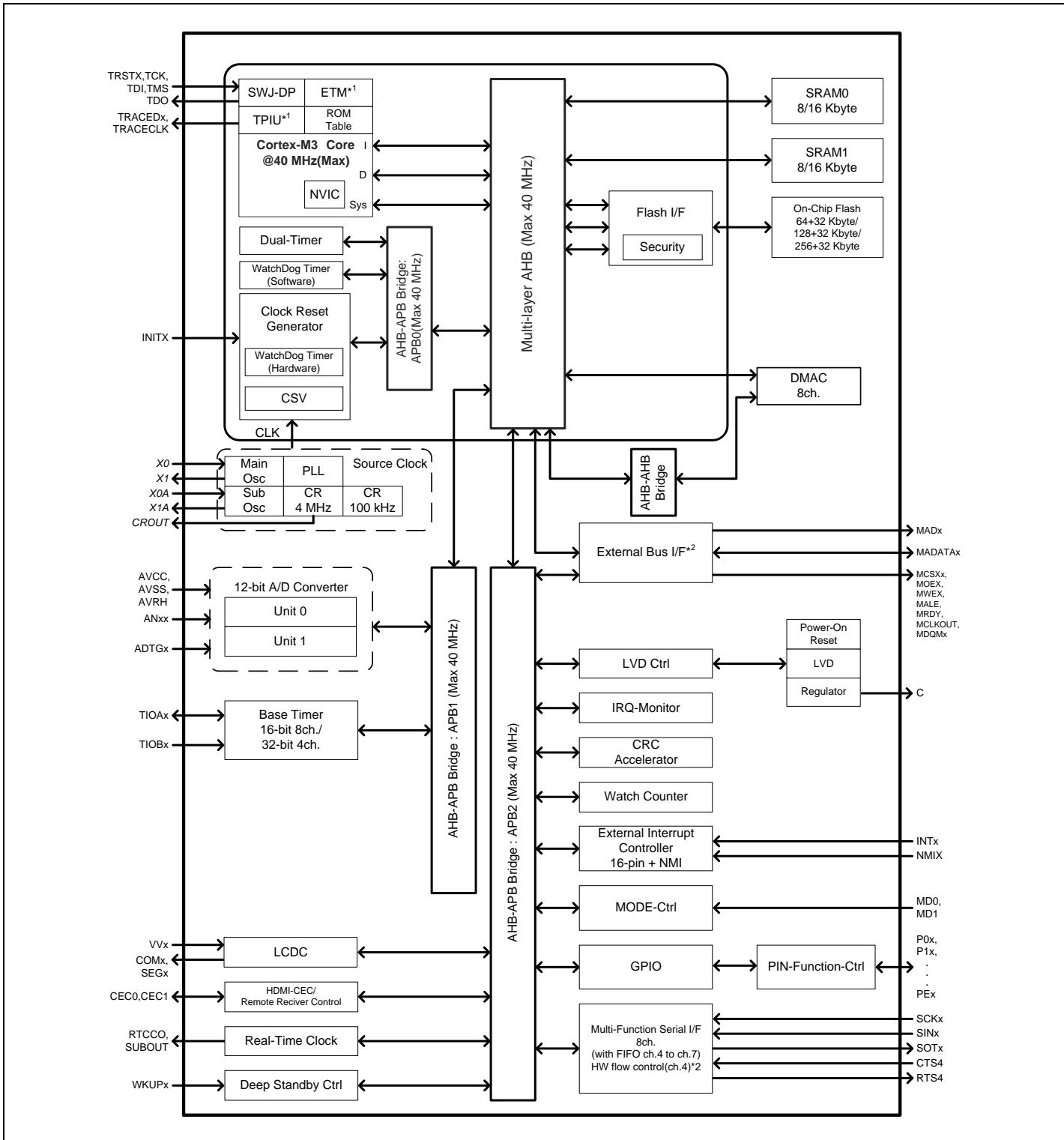

MB9AA40NB シリーズは、低消費電力と低コストを求める組込み制御用途向けに設計された、高集積 32 ビットマイクロコントローラです。本シリーズは、CPU に ARM Cortex-M3 プロセッサを搭載し、フラッシュメモリおよび SRAM のオンチップメモリとともに、周辺機能として、各種タイマ、A/D コンバータ、LCD、各種通信インターフェース(UART, CSIO, I<sup>2</sup>C)などにより構成されます。『FM3 ファミリ ペリフェラルマニュアル』において、このデータシートに記載されている製品は、TYPE6 製品に分類されます。

## 特長

### 32 ビット ARM Cortex-M3 コア

- プロセッサ版数: r2p1

- 最大動作周波数: 40 MHz

- ネスト型ベクタ割込みコントローラ(NVIC): 1 チャネルの NMI (ノンマスカブル割込み) と 48 チャネルの周辺割込みに対応。16 の割込み優先度レベルを設定できます。

- 24 ビットシステムタイマ(Sys Tick): OS タスク管理用のシステムタイマです。

### オンチップメモリ

#### [フラッシュメモリ]

- デュアルオペレーションフラッシュメモリ

- デュアルオペレーションフラッシュメモリは、上位バンクと下位バンクで構成されており、書込み/消去動作と読出しが同時実行します。

- メイン領域: 最大 256 K バイト (最大 240 K バイト上位バンク + 16 K バイト下位バンク)

- ワーク領域: 32 K バイト (下位バンク)

- リードサイクル: 0 ウェイトサイクル

- コード保護用セキュリティ機能

#### [SRAM]

本シリーズのオンチップ SRAM は、2 つの独立した SRAM (SRAM0, SRAM1) により構成されています。SRAM0 は、Cortex-M3 コアの I-Code バス、D-Code バスに接続されます。SRAM1 は、Cortex-M3 コアの System バスに接続されます。

- SRAM0: 最大 16 K バイト

- SRAM1: 最大 16 K バイト

### 外部バスインターフェース\*

- SRAM, NOR フラッシュメモリデバイスに対応

- 最大 8 チップセレクト

- 8/16 ビットデータ幅

- 最大 25 ビットのアドレスビット

- 最大アクセスサイズ: 256 M バイト

- アドレス/データマルチプレクスをサポート

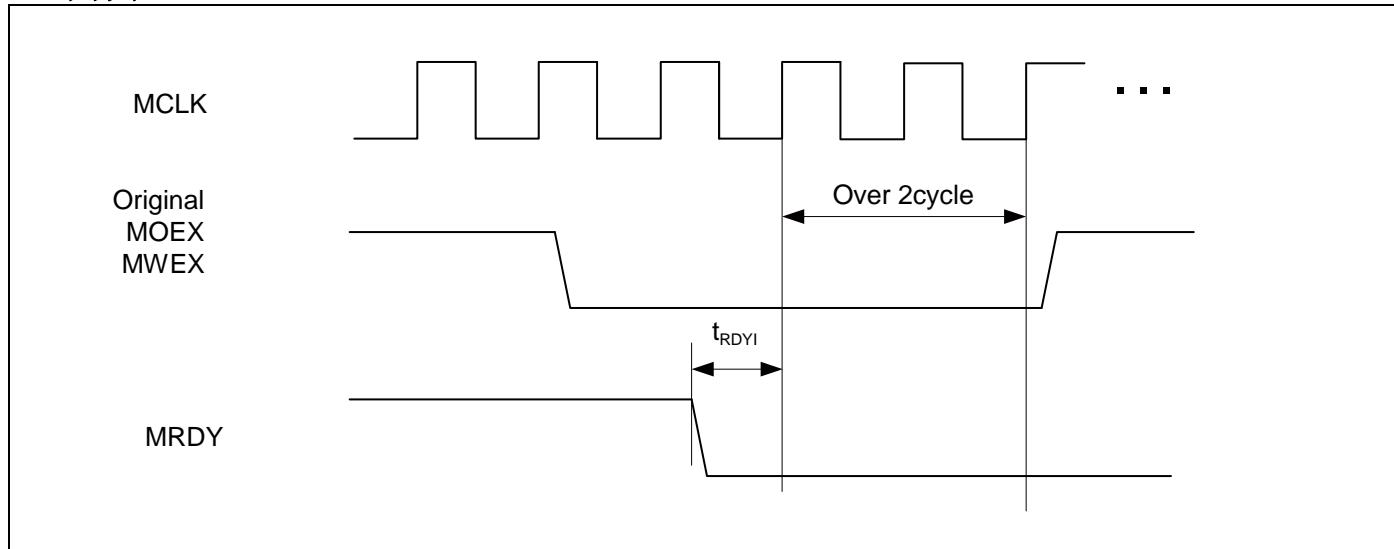

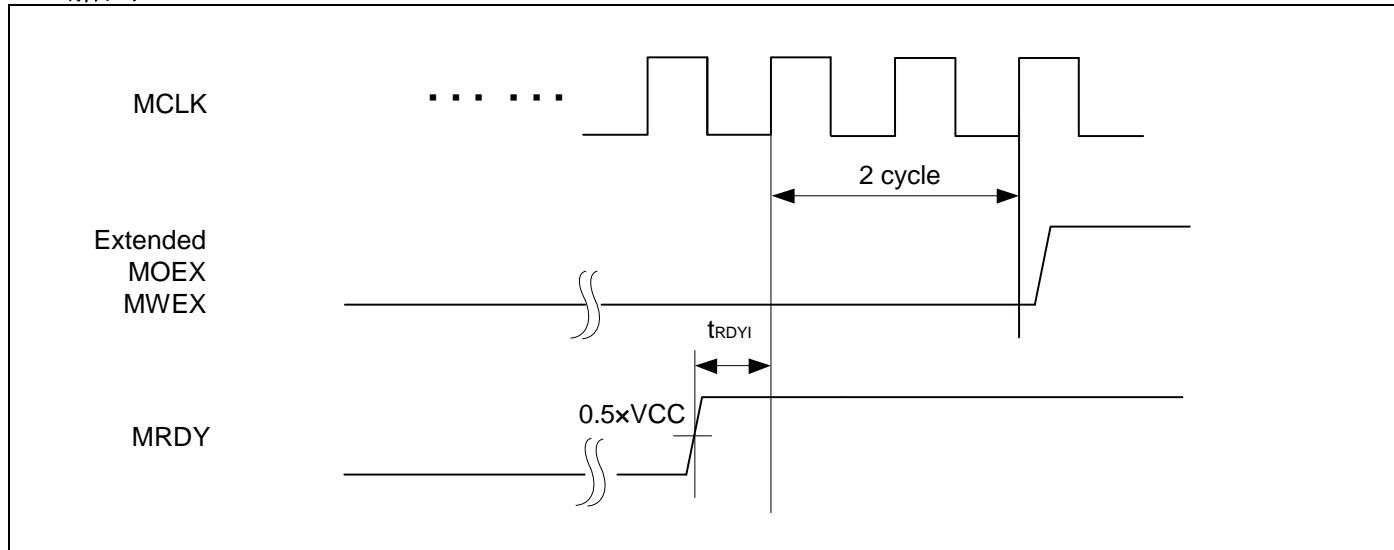

- 外部 RDY 機能をサポート

- \*: MB9AFA41LB, FA42LB, FA44LB は外部バスインターフェース非対応

### LCD コントローラ(LCDC)

- 40 SEG × 8COM (最大)

- 8COM/4COM モード選択可能

- 内部分割抵抗内蔵

- LCD 駆動電源 (バイアス) 端子(VV4~VV0)

- プリンギング機能あり

### マルチファンクションシリアルインターフェース(最大 8 チャネル)

- 16 段 × 9 ビット FIFO あり 4 チャネル(ch.4 ~ ch.7), FIFO なし 4 チャネル(ch.0 ~ ch.3)

- チャネルごとに動作モードを次の中から選択できます。

- UART

- CSIO

- I<sup>2</sup>C

### [UART]

- 全二重ダブルバッファ

- パリティあり/なし選択可能

- 専用ボーレートジェネレータ内蔵

- 外部クロックをシリアルクロックとして使用可能

- ハードウェアフロー・コントロール\*: CTS/RTS による送受信自動制御(ch.4のみ)

- 豊富なエラー検出機能(パリティエラー, フレーミングエラー, オーバランエラー)

- \*: MB9AFA41LB, FA42LB, FA44LB はハードウェアフロー・コントロール非対応

### [CSIO]

- 全二重ダブルバッファ

- 専用ボーレートジェネレータ内蔵

- オーバランエラー検出機能

### [I<sup>2</sup>C]

Standard-mode (最大 100 kbps)/ Fast-mode (最大 400 kbps)に対応

### DMA コントローラ(8 チャネル)

DMA コントローラは、CPU とは独立した DMA 専用バスを持ち、CPU と並列動作できます。

- 8 つを独自に構成かつ動作可能なチャネル

- ソフトウェア要求または内蔵周辺機能要求による転送開始可能

- 転送アドレス空間: 32 ビット(4G バイト)

- 転送モード: ブロック転送/ バースト転送/ デマンド転送

- 転送データタイプ: バイト/ ハーフワード/ ワード

- 転送ブロック数: 1 ~ 16

- 転送回数: 1 ~ 65536

### AD コンバータ(最大 24 チャネル)

#### [12 ビット A/D コンバータ]

- 逐次比較型

- 2 ユニット搭載

- 変換時間: 2.0  $\mu$ s @ 2.7 V ~ 3.6 V

- 優先変換可能(2 レベルの優先度)

- スキャン変換モード

- 変換データ格納用 FIFO 搭載(スキャン変換用: 16 段, 優先変換用: 4 段)

### ベースタイマ(最大 8 チャネル)

- チャネルごとに動作モードを次の中から選択できます。

- 16 ビット PWM タイマ

- 16 ビット PPG タイマ

- 16/32 ビットリロードタイマ

- 16/32 ビット PWC タイマ

### 汎用 I/O ポート

本シリーズは、端子が外部バスまたは周辺機能に使用されていない場合、汎用 I/O ポートとして使用できます。また、どの I/O ポートに周辺機能を割り当てるかを設定できるポートリロケート機能を搭載しています。

- 端子ごとにプルアップ制御可能

- 端子レベルを直接読出し可能

- ポートリロケート機能

- 最大 83 本の高速汎用 I/O ポート @100 pin Package

- 一部のポートは、5 V トレラントに対応

該当する端子については「端子機能一覧」を参照してください。

### デュアルタイマ(32/16 ビットダウンカウンタ)

デュアルタイマは、2 つのプログラム可能な 32/16 ビットダウンカウンタで構成されます。

各タイマチャネルの動作モードを次の中から選択できます。

- フリーランモード

- 周期モード(=リロードモード)

- ワンショットモード

### HDMI-CEC/リモコン受信(最大 2 チャネル)

- HDMI-CEC 送信

- シグナルフリーを判定してヘッダーブロックの自動送信

- アービトレーションロストを検出してステータス割込みを発生

- 1 バイトデータの設定により START, EOM, ACK を自動生成して CEC 送信出力

- 1 ブロック(1 バイトのデータと EOM, ACK)を送信したときに送信ステータス割込みを発生

- HDMI-CEC 受信

- 自動 ACK 応答機能

- ラインエラー検出機能

- リモコン受信

- 4 バイトの受信バッファ

- リピートコード検出機能

### リアルタイムクロック(RTC: Real Time Clock)

00年～99年までの年/月/日/時/分/秒/曜日のカウントを行います。

- 日時指定(年/月/日/時/分)での割込み機能、年/月/日/時/分だけの個別設定も可能

- 設定時間後/設定時間ごとのタイマ割込み機能

- カウントを継続して時刻書換え可能

- うるう年の自動カウント

### 時計カウンタ

時計カウンタはスリープ、タイマモードからのウェイクアップに使用します。インターバルタイマ: 最大 64s@サブクロック使用時(32.768 kHz)

### 外部割込み制御ユニット

- 外部割込み入力端子: 最大 16 本

- ノンマスカブル割込み(NMI)入力端子: 1 本

### ウォッチドッグタイマ(2 チャネル)

ウォッチドッグタイマは、タイムアウト値に達すると割込みまたはリセットを発生します。

本シリーズには、ハードウェアウォッチドッグとソフトウェアウォッチドッグの 2 つの異なるウォッチドッグがあります。ハードウェアウォッチドッグタイマは内蔵低速 CR 発振で動作するため、RTC モード、ストップモード、ディープスタンバイ RTC モード、ディープスタンバイストップモード以外のすべての低消費電力モードで動作します。

### CRC (Cyclic Redundancy Check) アクセラレータ

CRC アクセラレータは、ソフト処理負荷の高い CRC 計算を行い、受信データおよびストレージの整合性確認処理負荷の軽減を実現します。

CCITT CRC16 と IEEE-802.3 CRC32 をサポートします。

- CCITT CRC16 Generator Polynomial: 0x1021

- IEEE-802.3 CRC32 Generator Polynomial: 0x04C11DB7

### クロック/リセット

#### [クロック]

5 種類のクロックソース(2 種類の外部発振、2 種類の内蔵 CR 発振、メイン PLL)から選択できます。

- メインクロック: 4MHz ~ 48MHz

- サブクロック: 32.768kHz

- 内蔵高速 CR クロック: 4MHz

- 内蔵低速 CR クロック: 100kHz

- メイン PLL クロック

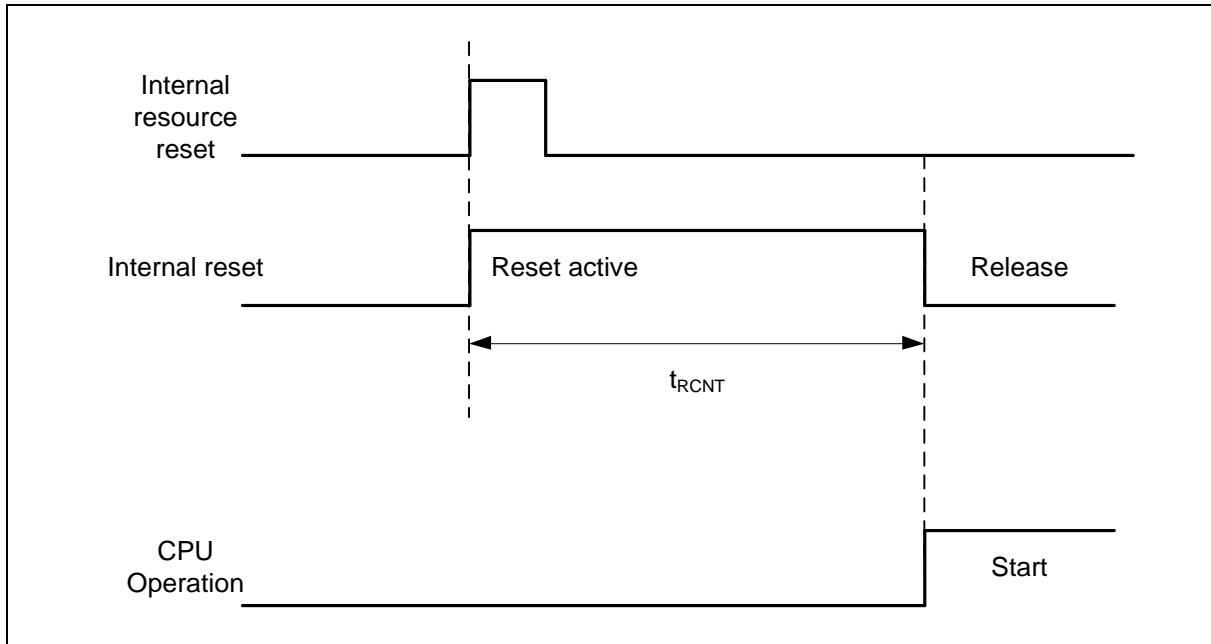

#### [リセット]

- INITX 端子からのリセット要求

- 電源投入リセット

- ソフトウェアリセット

- ウォッチドッグタイマリセット

- 低電圧検出リセット

- クロックスーパバイザリセット

### クロック監視機能(CSV : Clock Super Visor)

内蔵 CR 発振による生成クロックを用いて外部クロックの異常を監視します。

- 外部クロック異常(クロック停止)が検出されると、リセットがアサートされます。

- 外部周波数異常が検出されると、割込みまたはリセットがアサートされます。

### 低電圧検出機能(LVD : Low-Voltage Detect)

本シリーズは、2 段階で VCC 端子の電圧を監視します。設定した電圧より VCC 端子の電圧が下がった場合、低電圧検出機能により割込みまたはリセットが発生します。

- LVD1: 割込みによりエラーを報告

- LVD2: オートリセット動作

## 低消費電力モード

6種類の低消費電力モードに対応します。

- スリープ

- タイマ

- RTC

- ストップ

- ディープスタンバイ RTC(RAM 保持あり・なし選択可能)

- ディープスタンバイストップ(RAM 保持あり・なし選択可能)

## ユニーク ID

41ビットのデバイス固有の値を設定済み

## 電源

ワイドレンジ電圧対応: VCC = 1.65 V ~ 3.6 V

VCC = 2.2 V ~ 3.6 V (LCDC 使用時)

## デバッグ

- シリアル・ワイヤ JTAG デバッグ・ポート (SWJ-DP)

- エンベデッド・トレース・マクロセル(ETM)\*

- \*: MB9AFA41LB/MB, FA42LB/MB, FA44LB/MB は SWJ-DP のみ

対応

## Table of Contents

|                                                        |     |

|--------------------------------------------------------|-----|

| <b>特長</b>                                              | 1   |

| 1. 品種構成                                                | 7   |

| 2. パッケージと品種対応                                          | 8   |

| 3. 端子配列図                                               | 9   |

| 4. 端子機能一覧                                              | 16  |

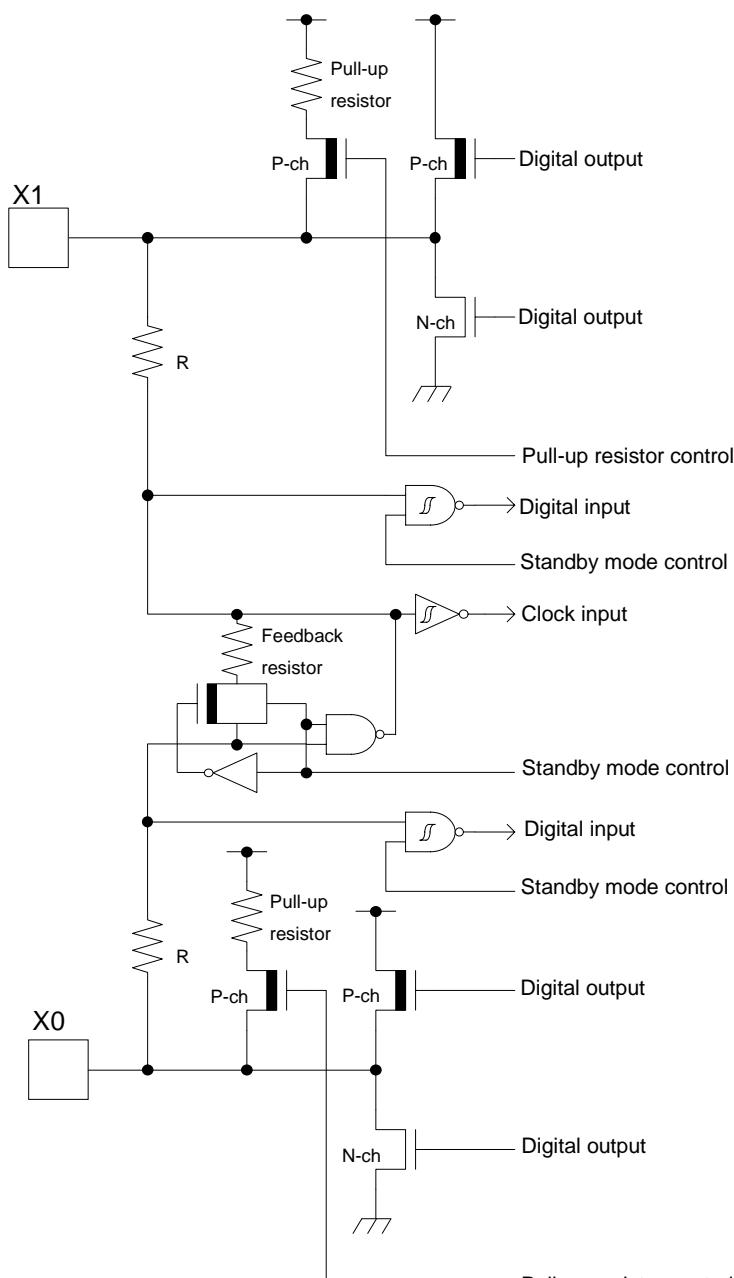

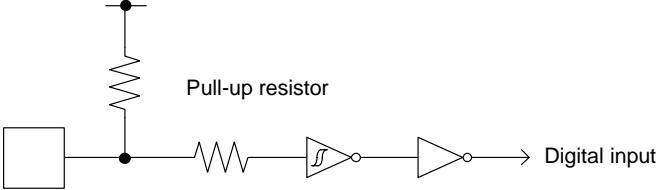

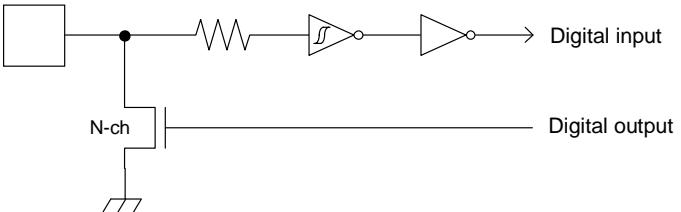

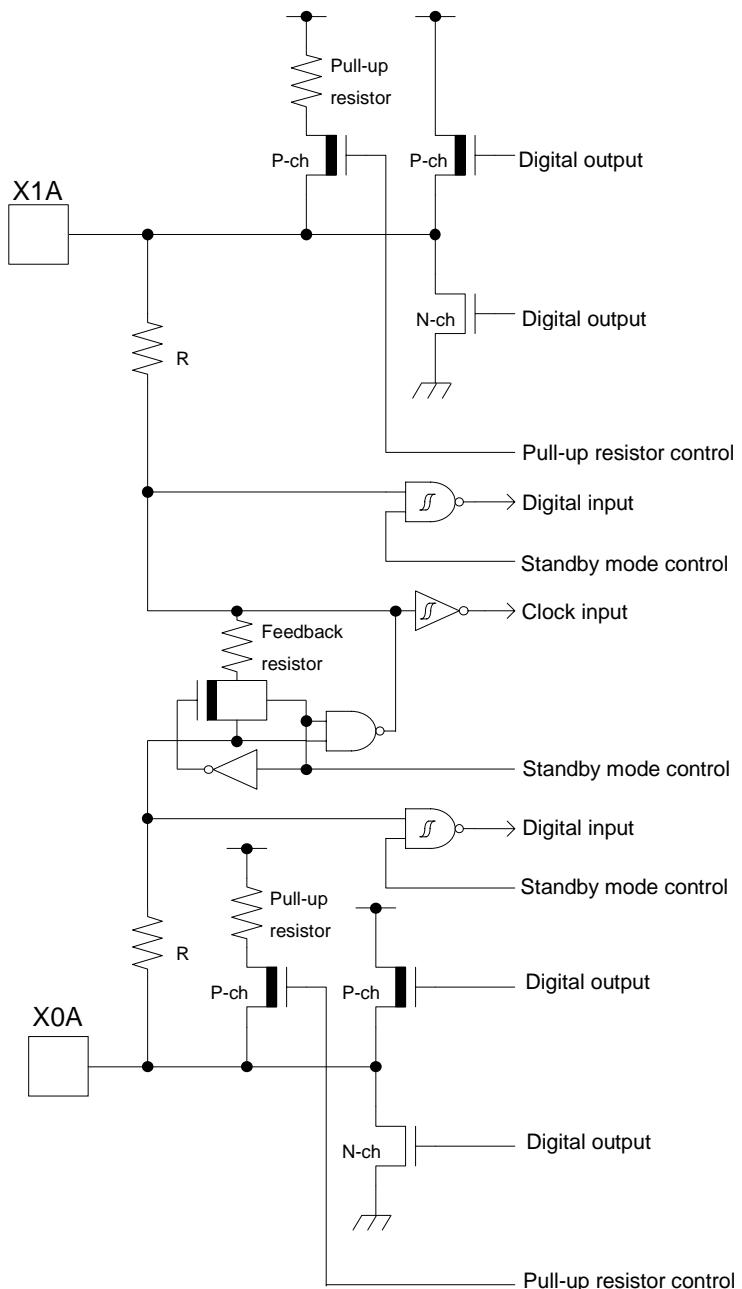

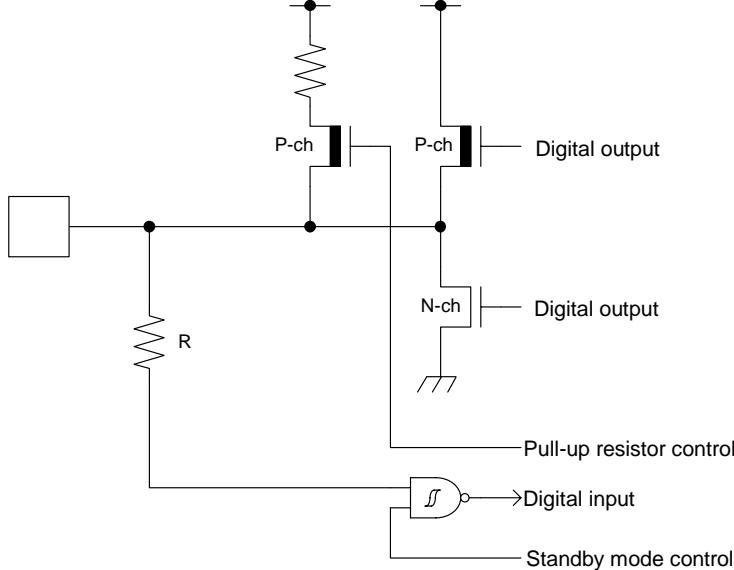

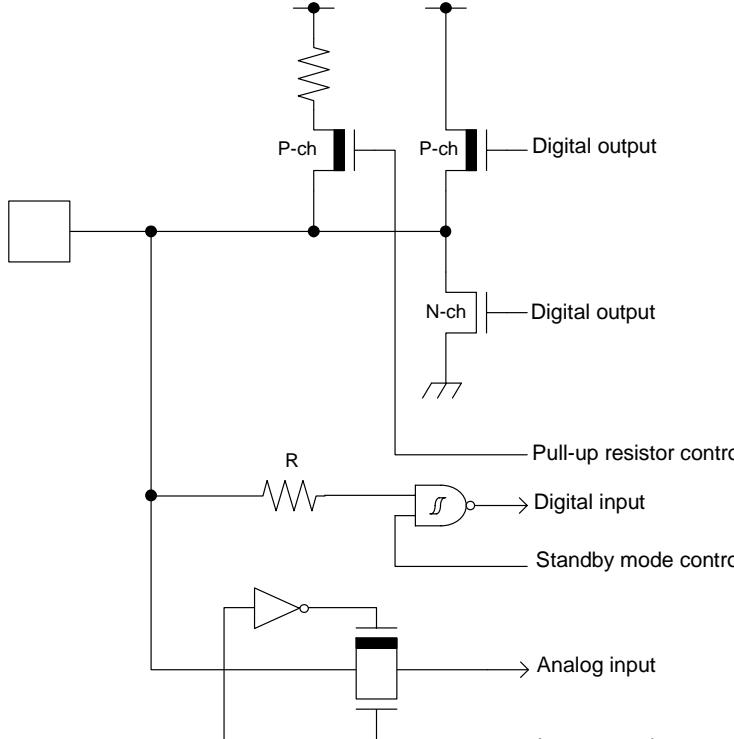

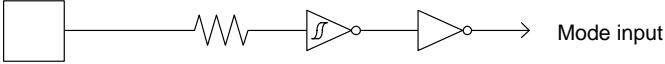

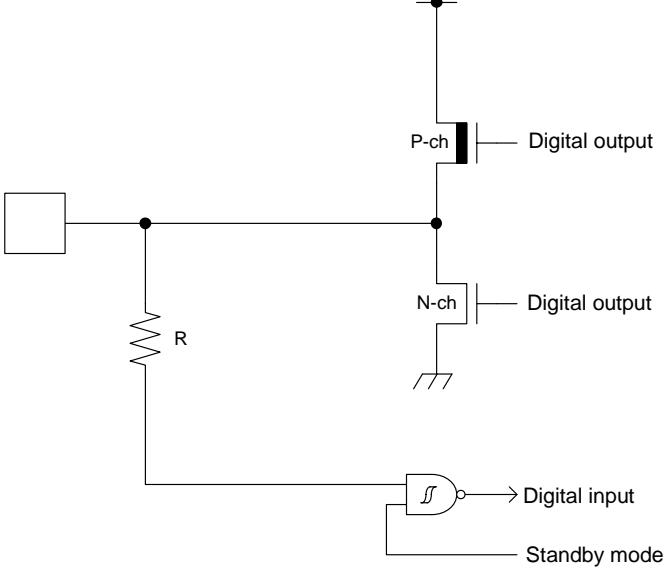

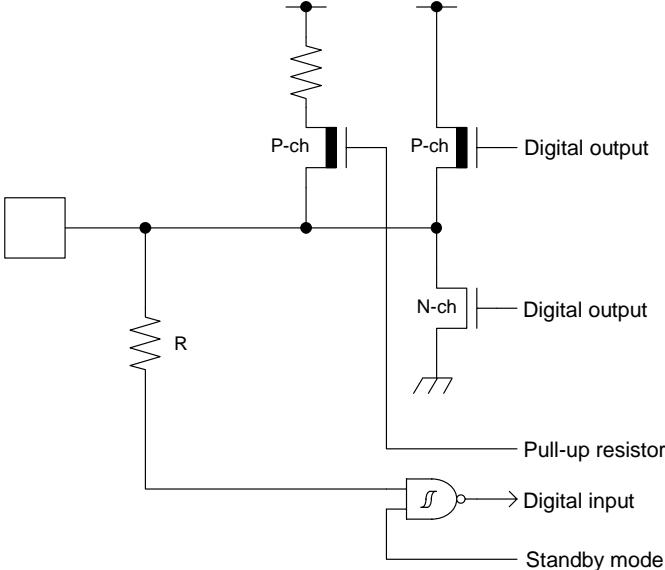

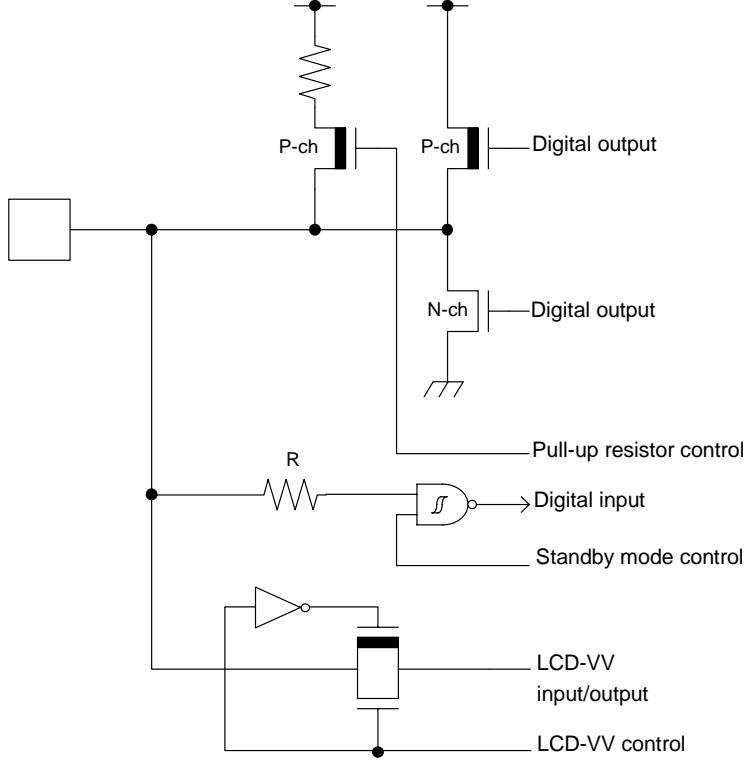

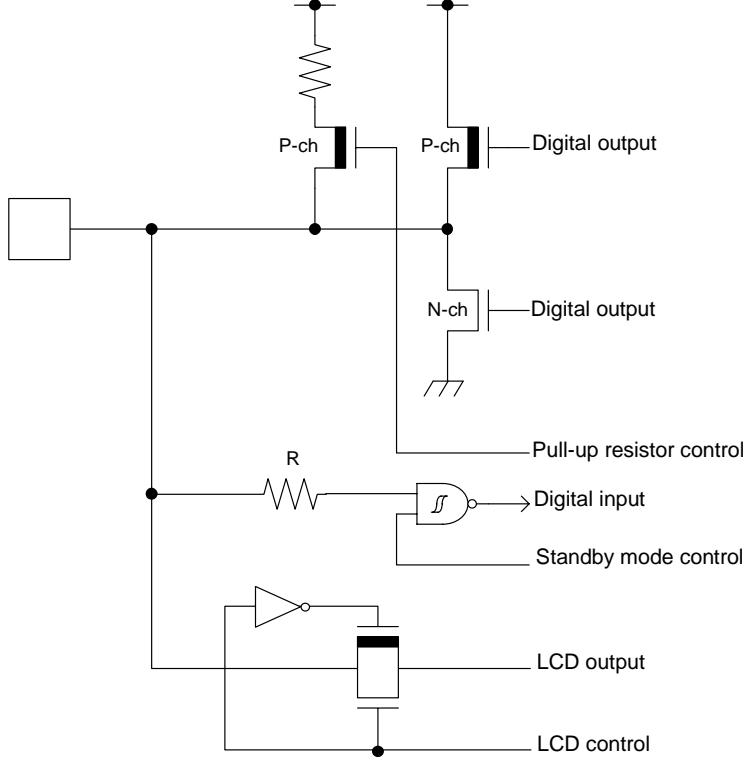

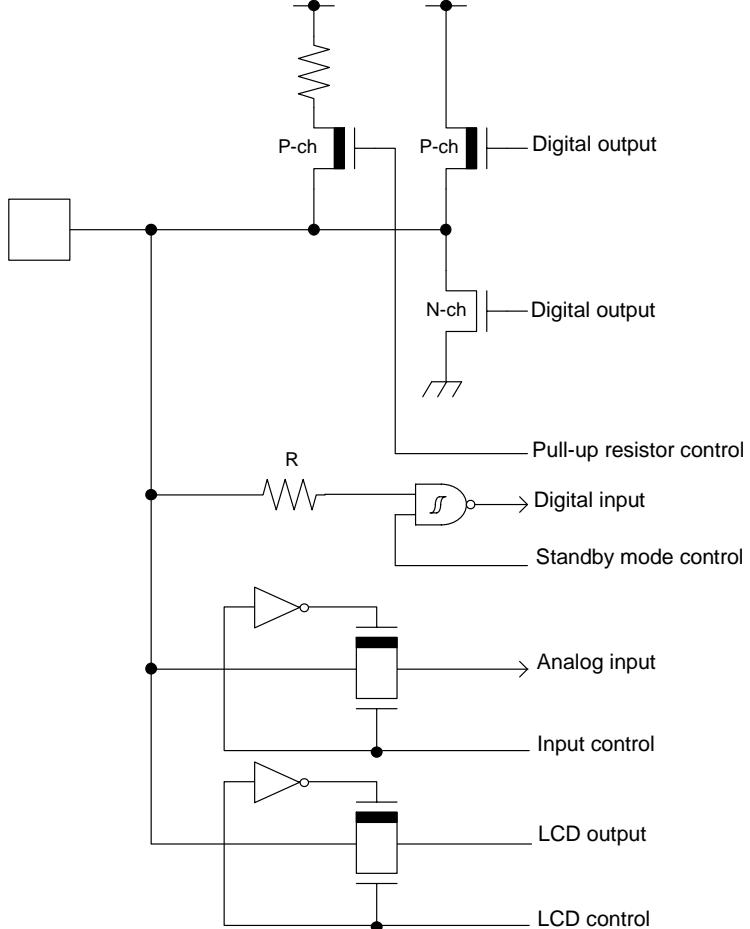

| 5. 入出力回路形式                                             | 42  |

| 6. 取扱上のご注意                                             | 49  |

| 6.1 設計上の注意事項                                           | 49  |

| 6.2 パッケージ実装上の注意事項                                      | 50  |

| 6.3 使用環境に関する注意事項                                       | 52  |

| 7. デバイス使用上の注意                                          | 53  |

| 8. ブロックダイヤグラム                                          | 56  |

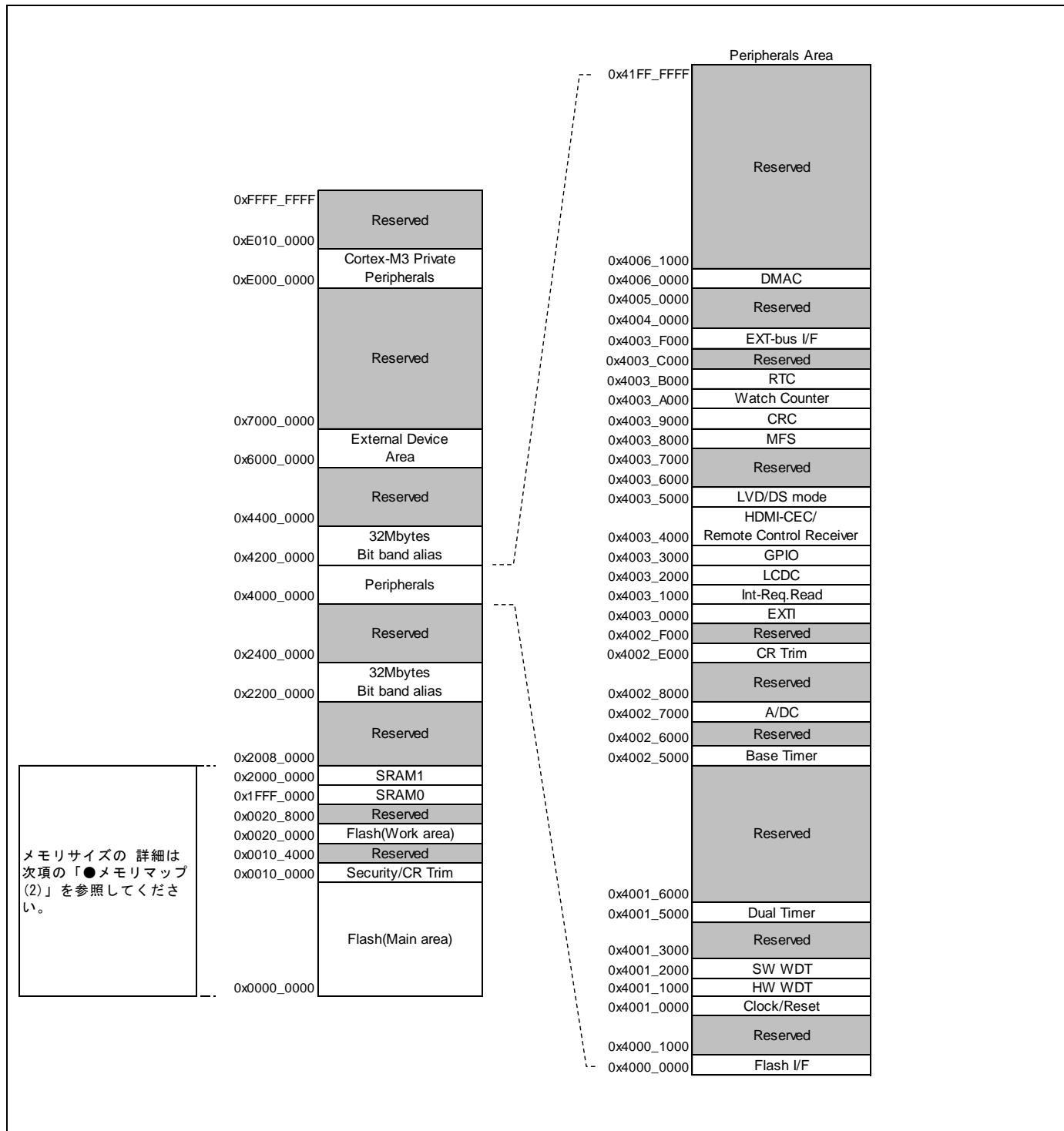

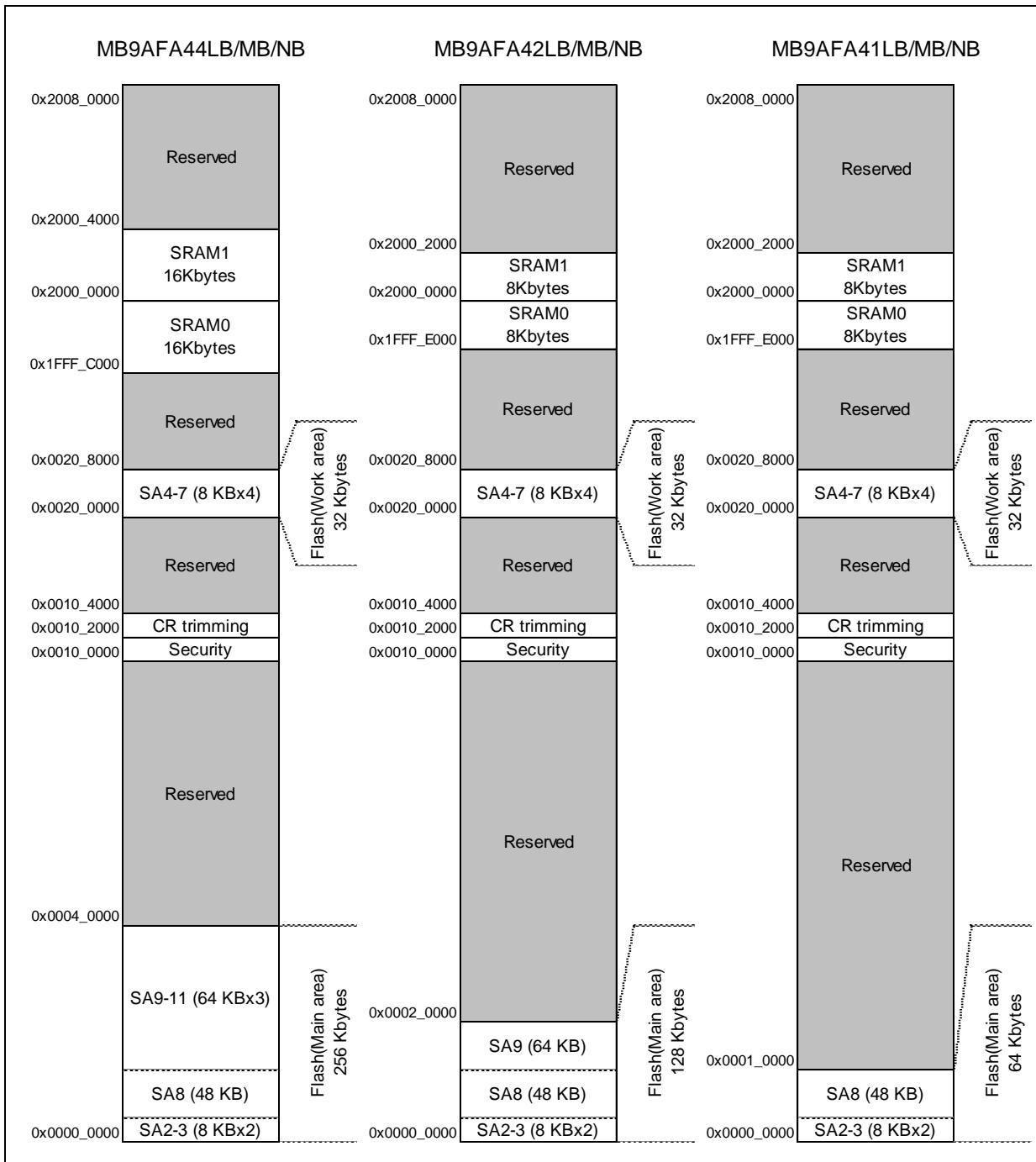

| 9. メモリサイズ                                              | 57  |

| 10. メモリマップ                                             | 57  |

| 11. 各 CPU ステートにおける端子状態                                 | 60  |

| <b>12. 電気的特性</b>                                       | 66  |

| 12.1 絶対最大定格                                            | 66  |

| 12.2 推奨動作条件                                            | 67  |

| 12.3 直流規格                                              | 68  |

| 12.3.1 電流規格                                            | 68  |

| 12.3.2 端子特性                                            | 71  |

| 12.4 LCD 特性                                            | 72  |

| 12.5 交流規格                                              | 73  |

| 12.5.1 メインクロック入力規格                                     | 73  |

| 12.5.2 サブクロック入力規格                                      | 74  |

| 12.5.3 内蔵 CR 発振規格                                      | 74  |

| 12.5.4 メイン PLL の使用条件 (PLL の入力クロックにメインクロックを選択した場合)      | 75  |

| 12.5.5 メイン PLL の使用条件 (メイン PLL の入力クロックに内蔵高速 CR を選択した場合) | 75  |

| 12.5.6 リセット入力規格                                        | 76  |

| 12.5.7 パワーオンリセットタイミング                                  | 76  |

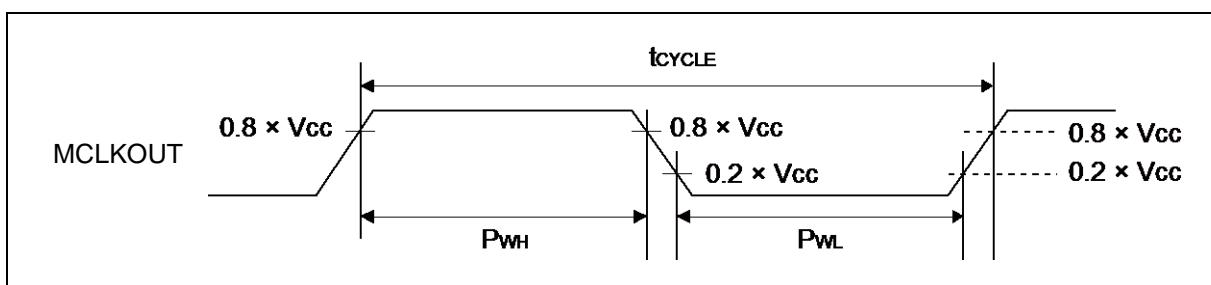

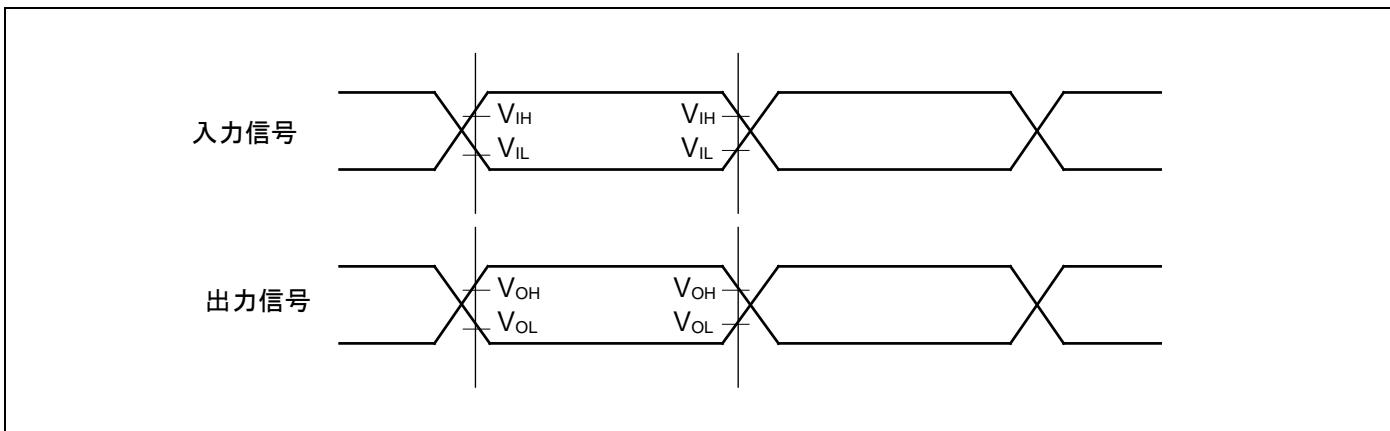

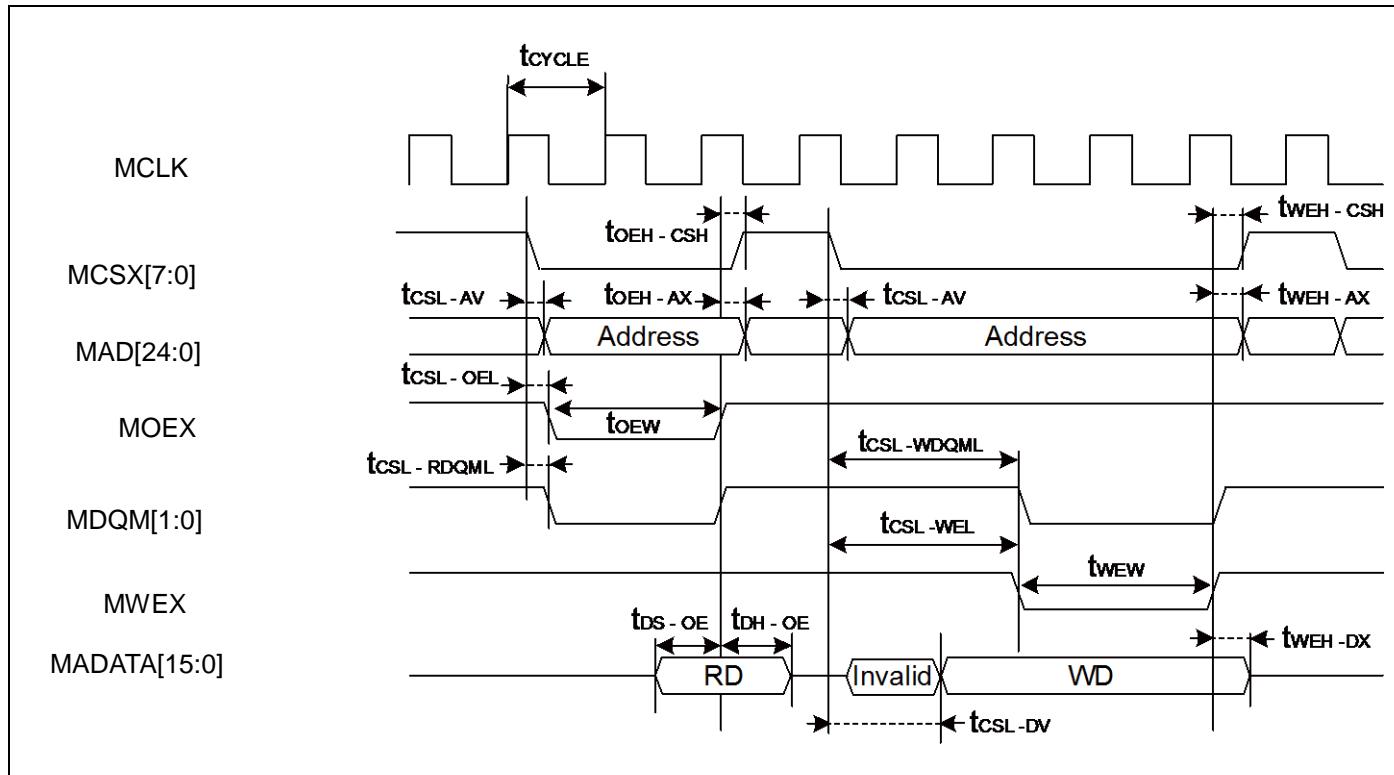

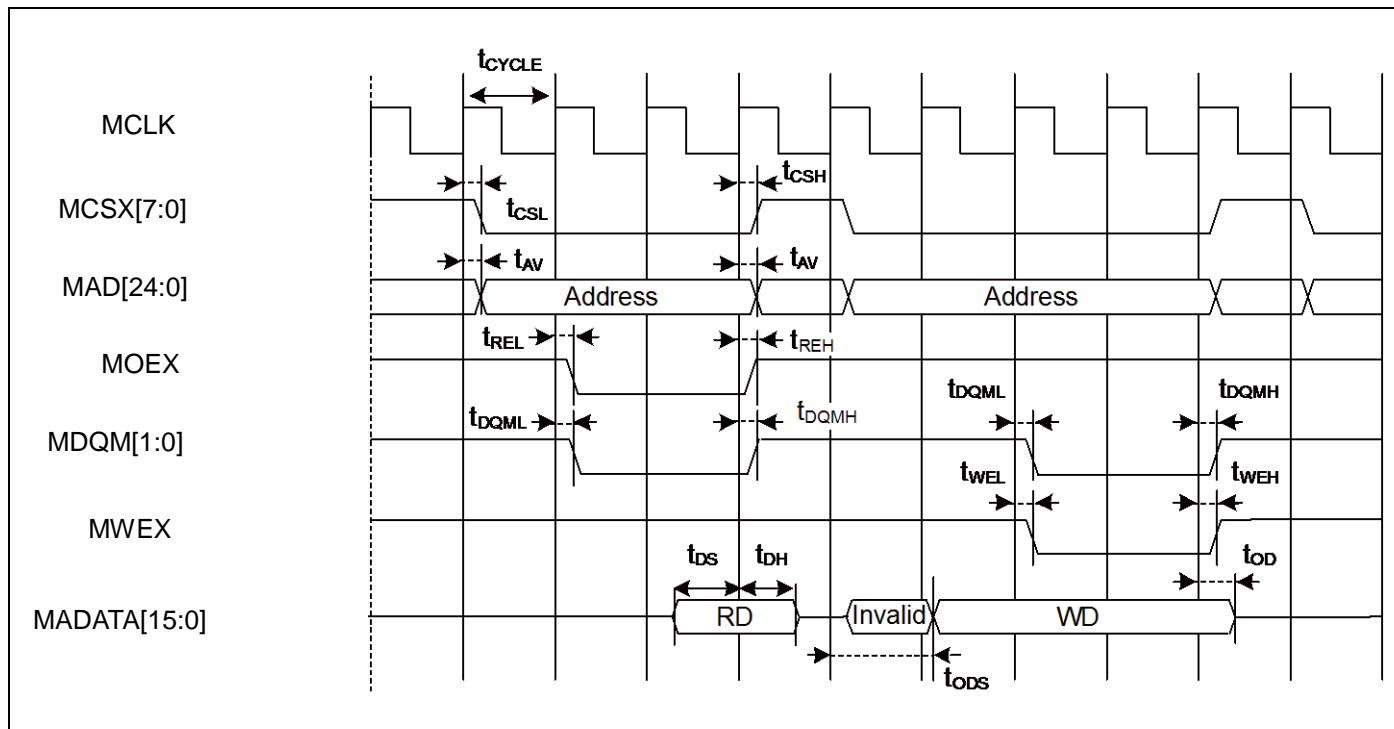

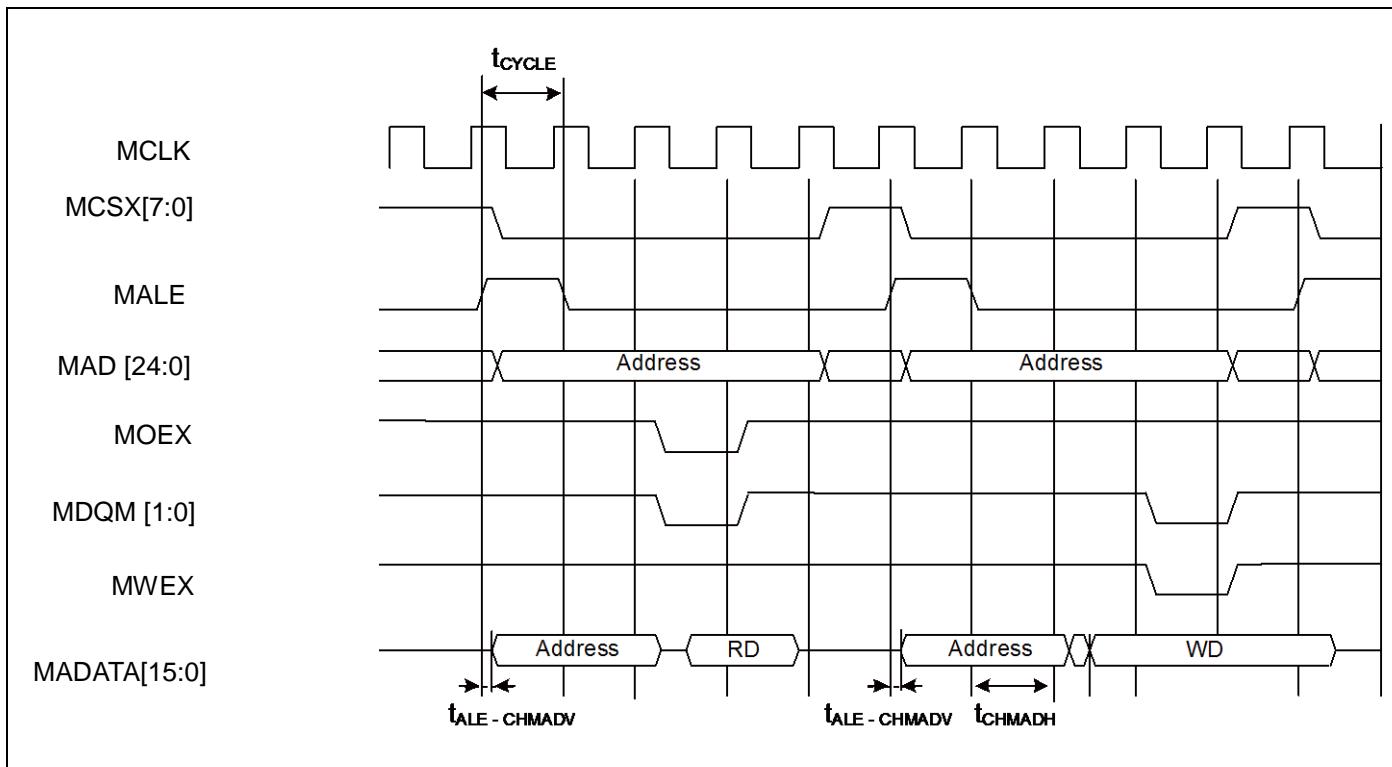

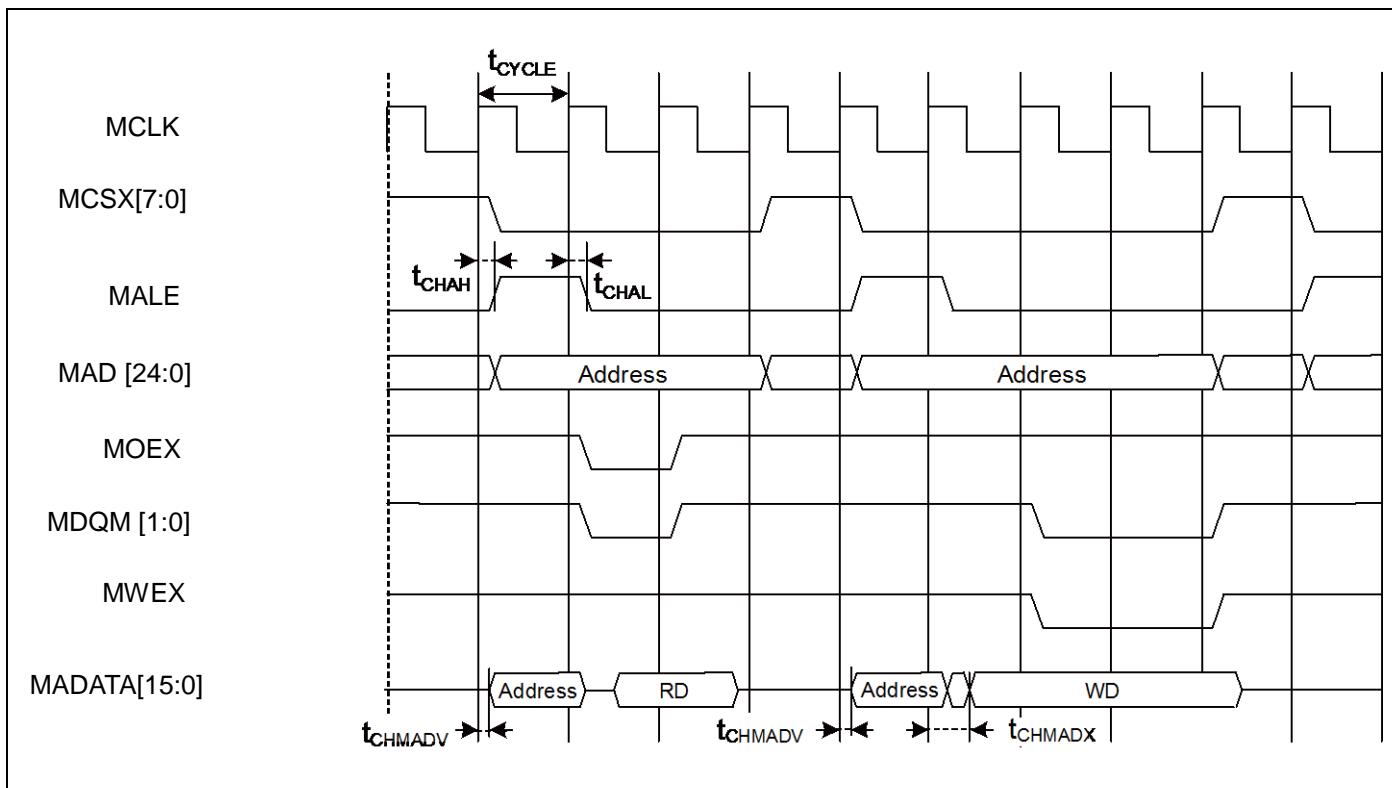

| 12.5.8 外バスタイミング                                        | 77  |

| 12.5.9 ベースタイミング入力タイミング                                 | 85  |

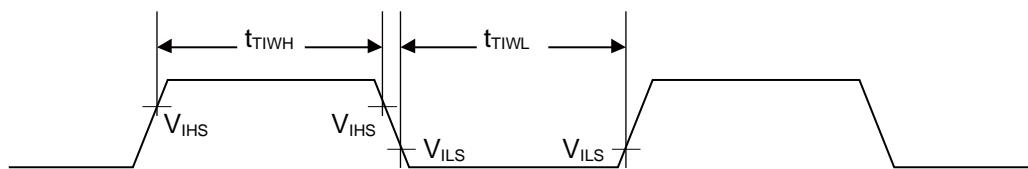

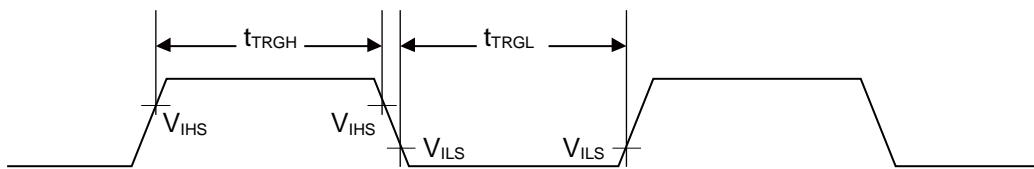

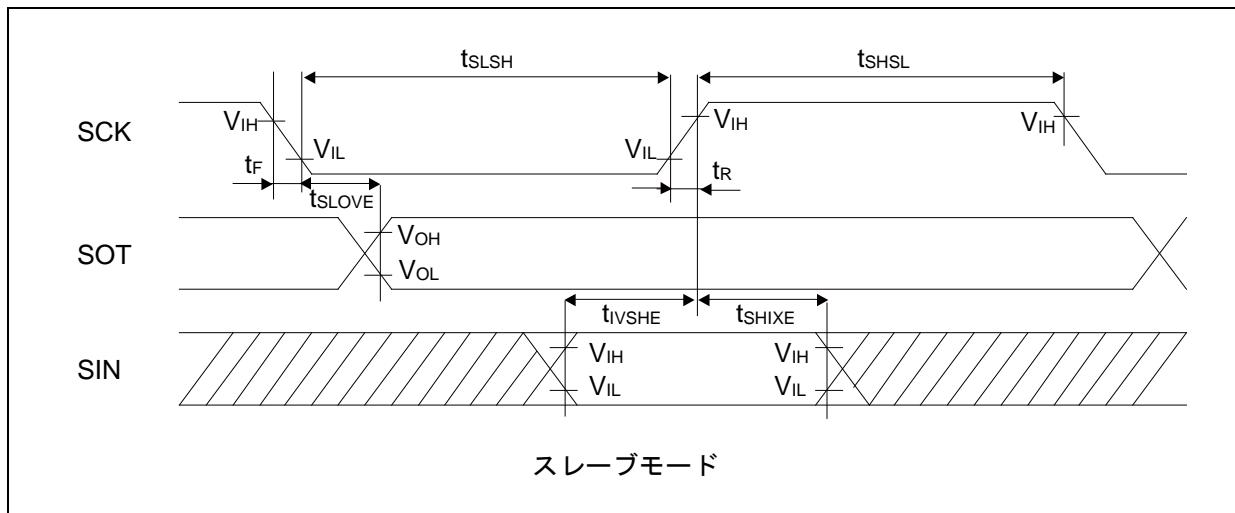

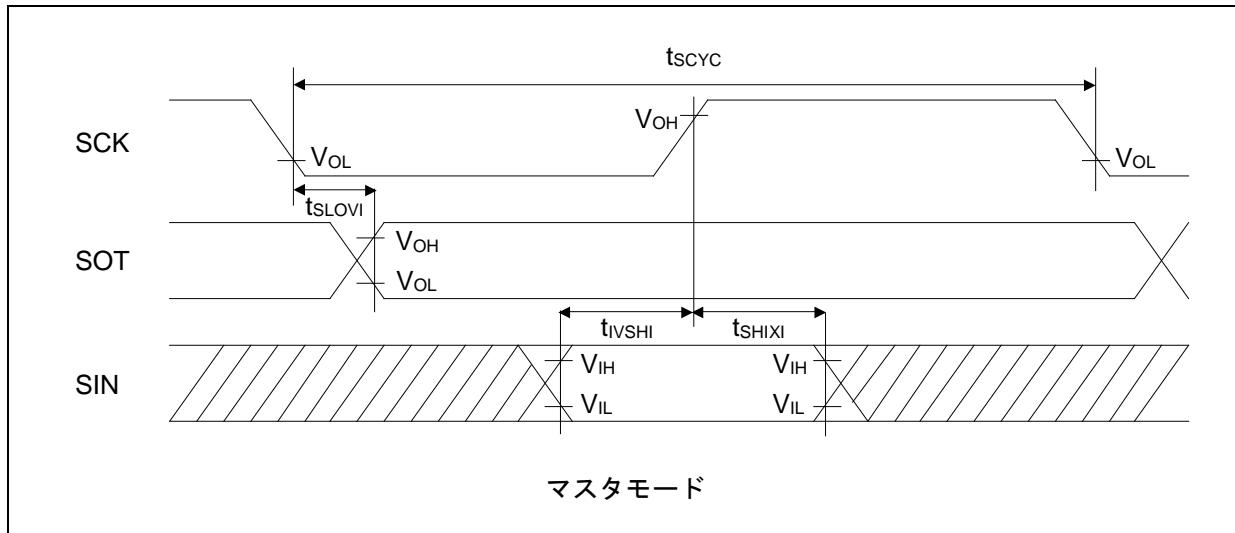

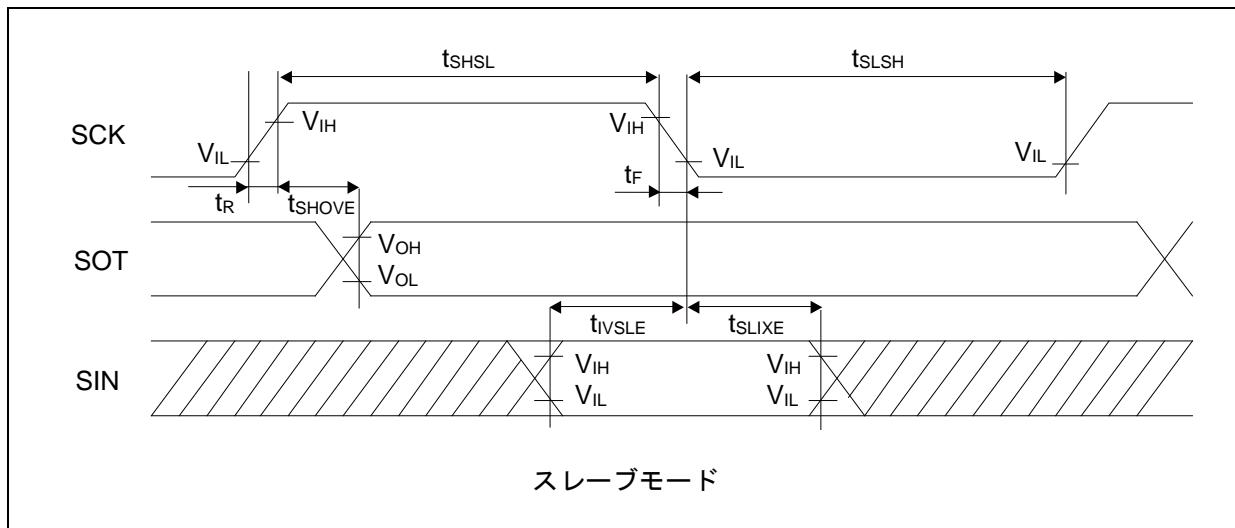

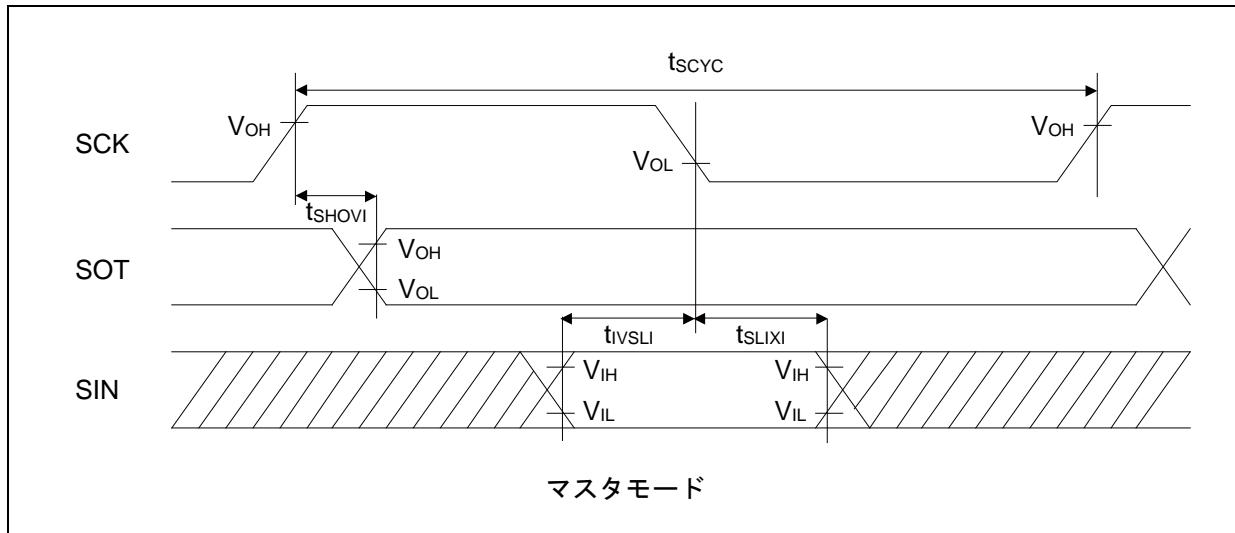

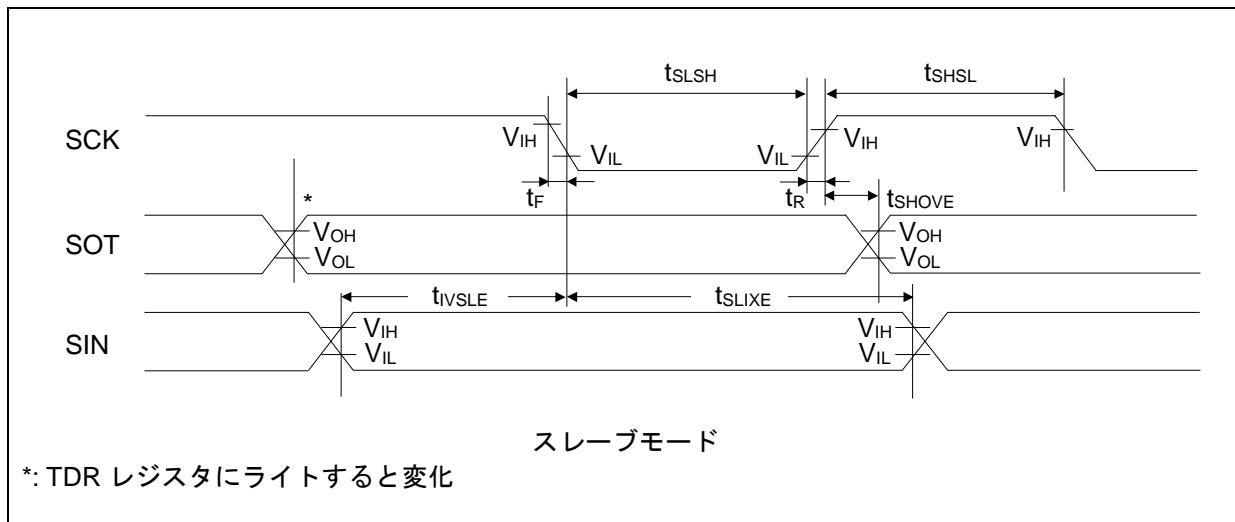

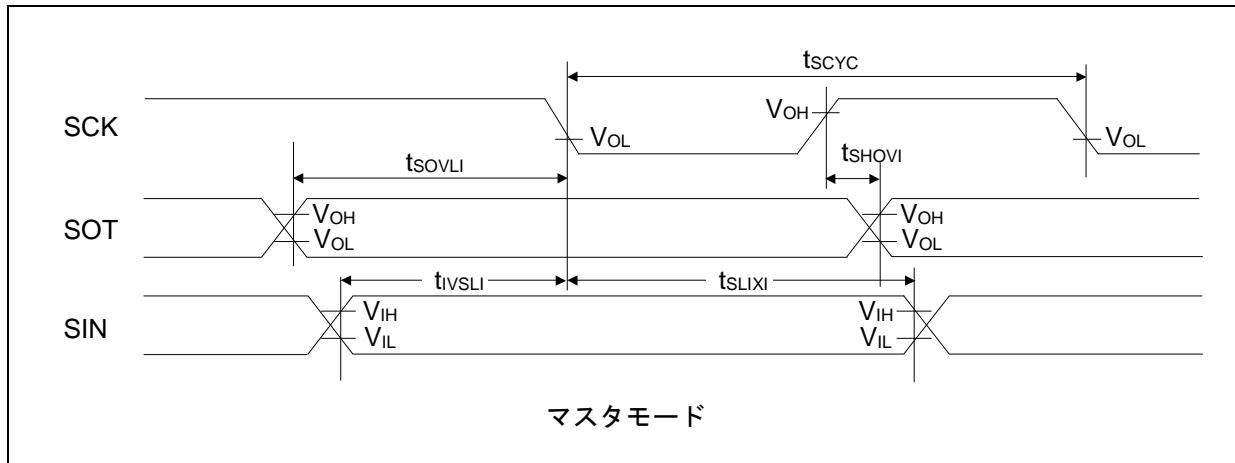

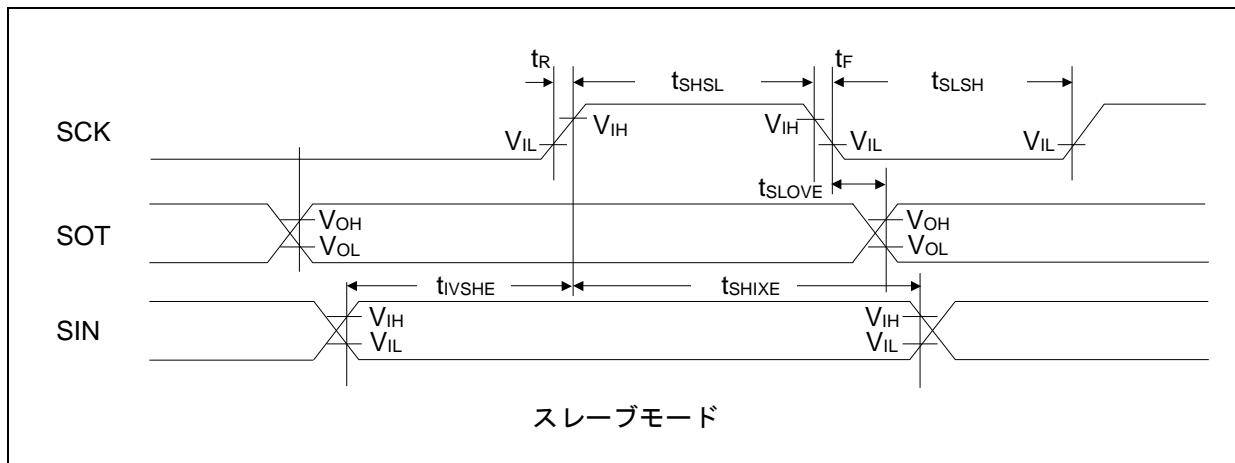

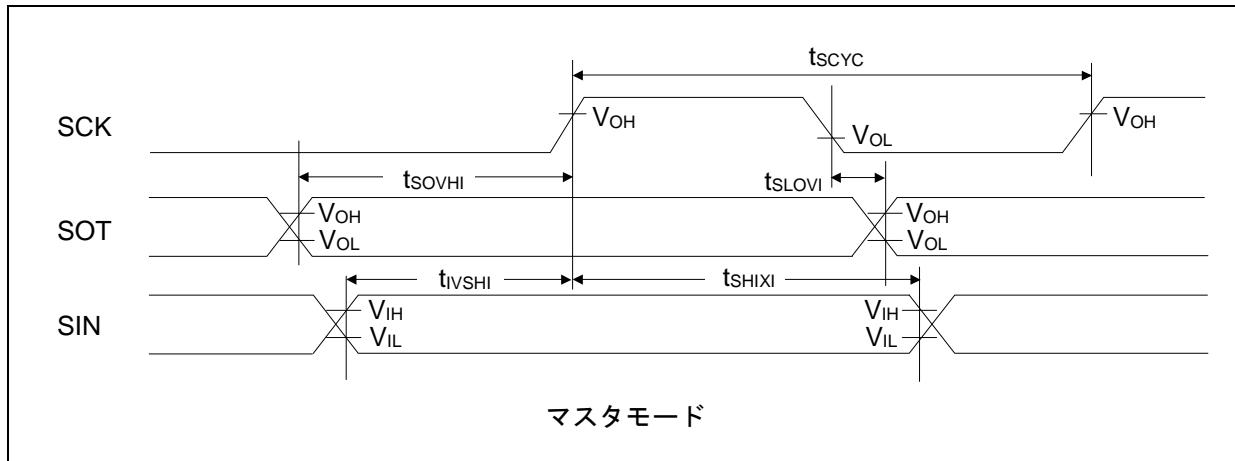

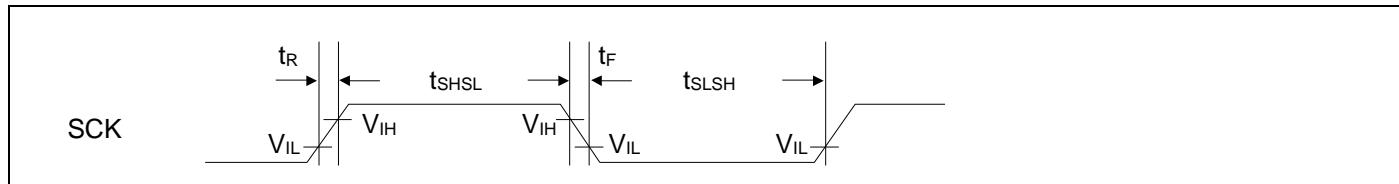

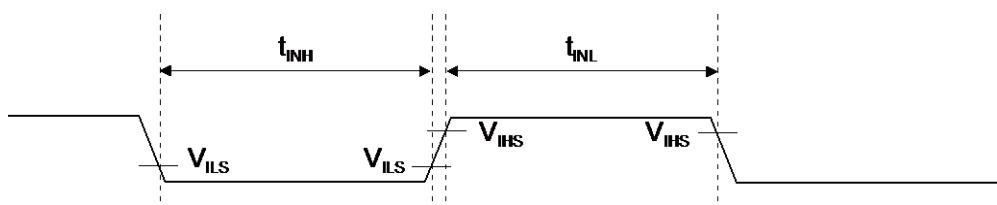

| 12.5.10 CSIO/UART タイミング                                | 86  |

| 12.5.11 外部入力タイミング                                      | 94  |

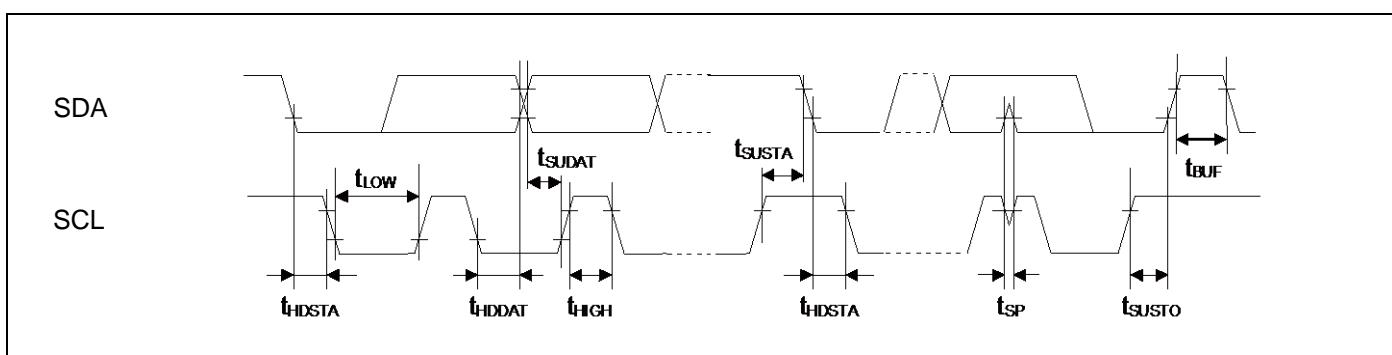

| 12.5.12 I <sup>2</sup> C タイミング                         | 95  |

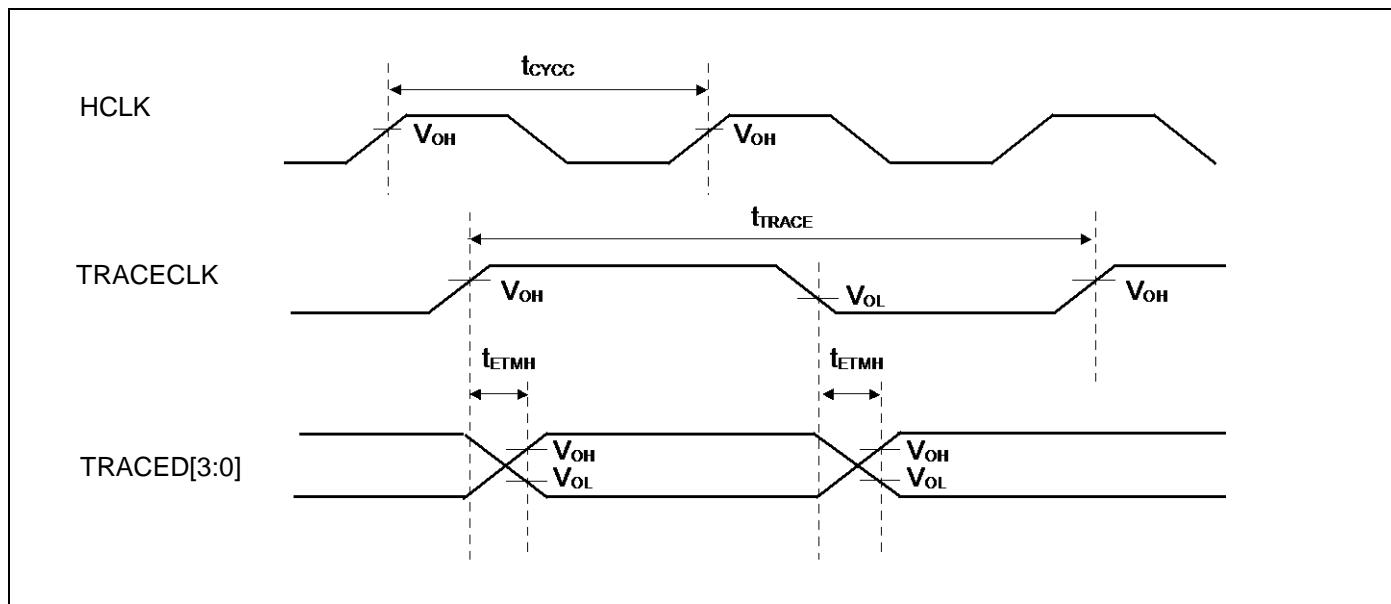

| 12.5.13 ETM タイミング                                      | 96  |

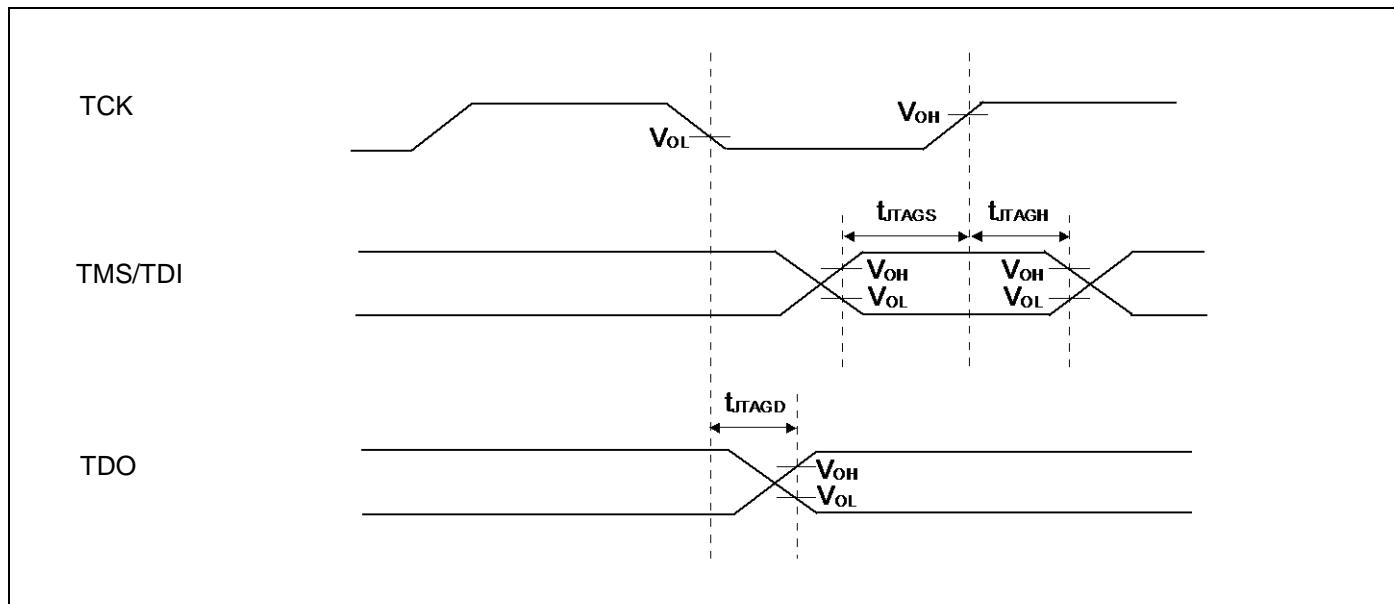

| 12.5.14 JTAG タイミング                                     | 97  |

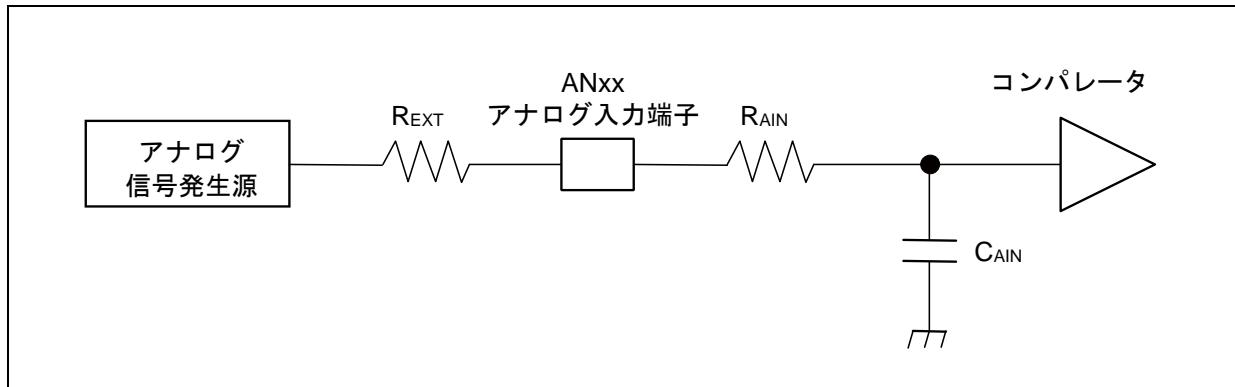

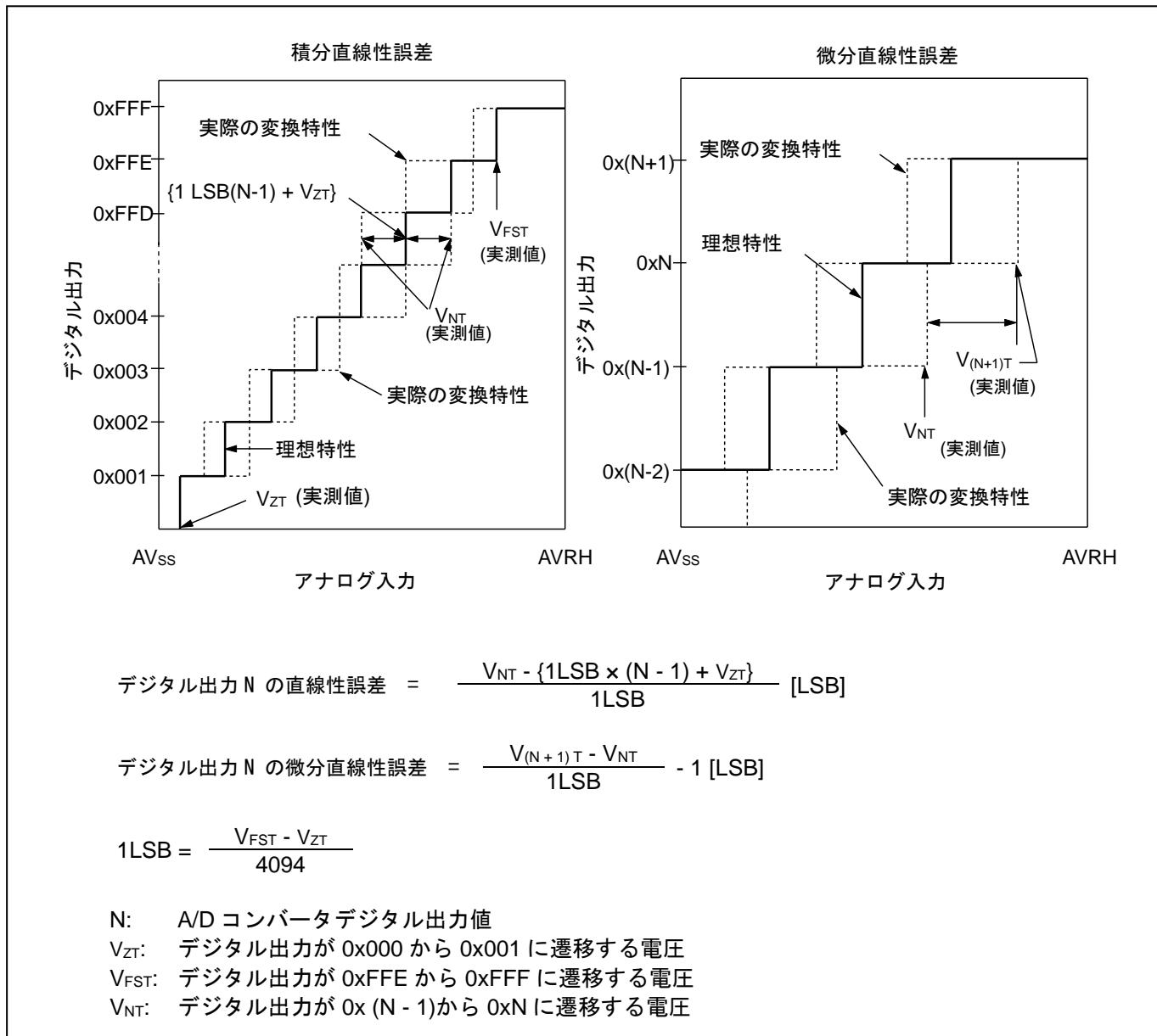

| 12.6 12 ビット A/D コンバータ                                  | 98  |

| 12.7 低電圧検出特性                                           | 101 |

| 12.7.1 低電圧検出リセット                                       | 101 |

|                            |            |

|----------------------------|------------|

| 12.7.2 低電圧検出割込み            | 102        |

| 12.8 フラッシュメモリ書き込み/消去特性     | 103        |

| 12.8.1 書込み/消去時間            | 103        |

| 12.8.2 書込みサイクルとデータ保持時間     | 103        |

| 12.9 スタンバイ復帰時間             | 104        |

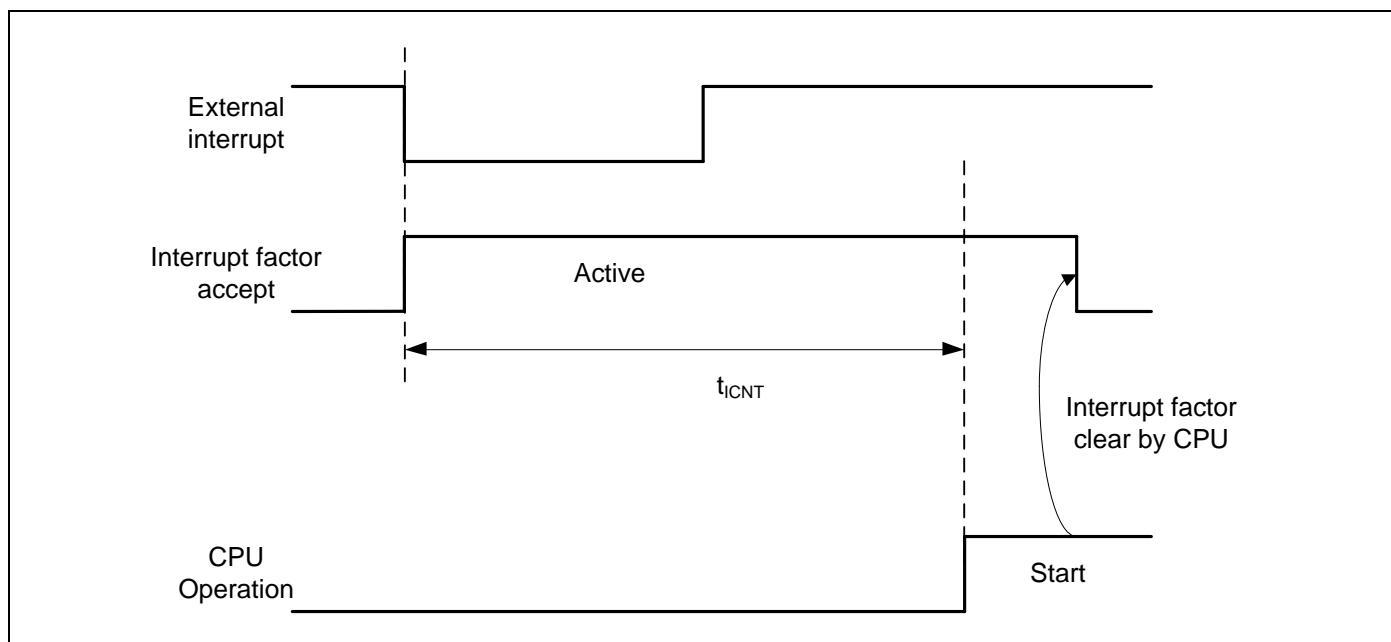

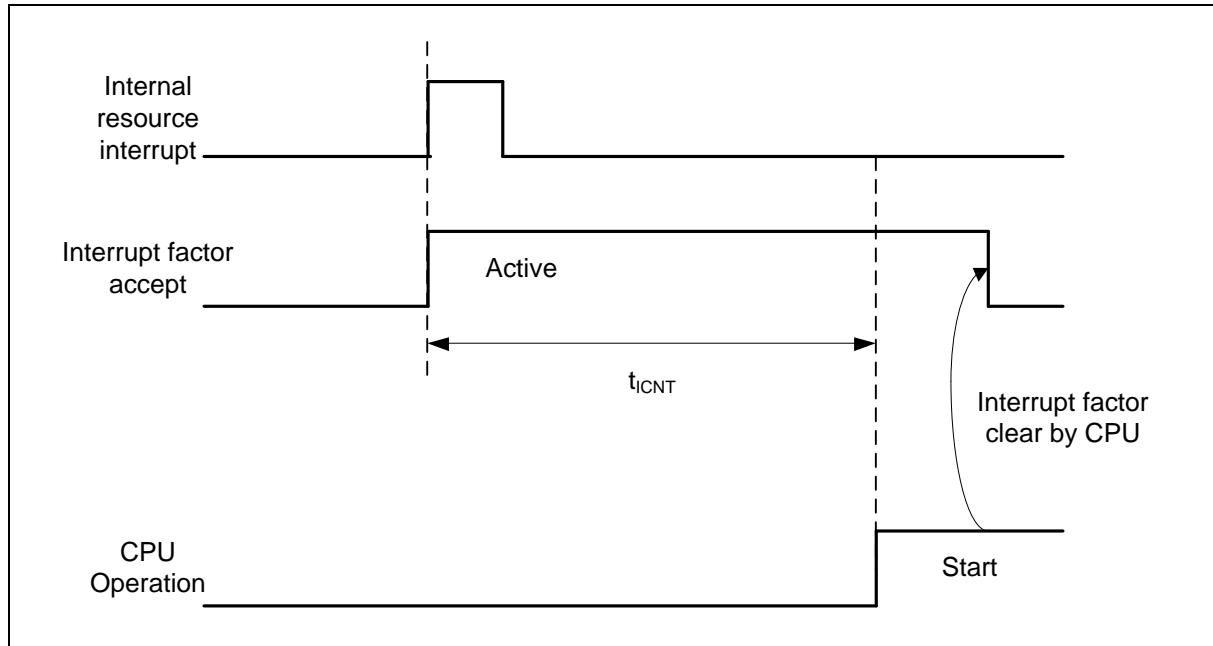

| 12.9.1 復帰要因：割込み/WKUP       | 104        |

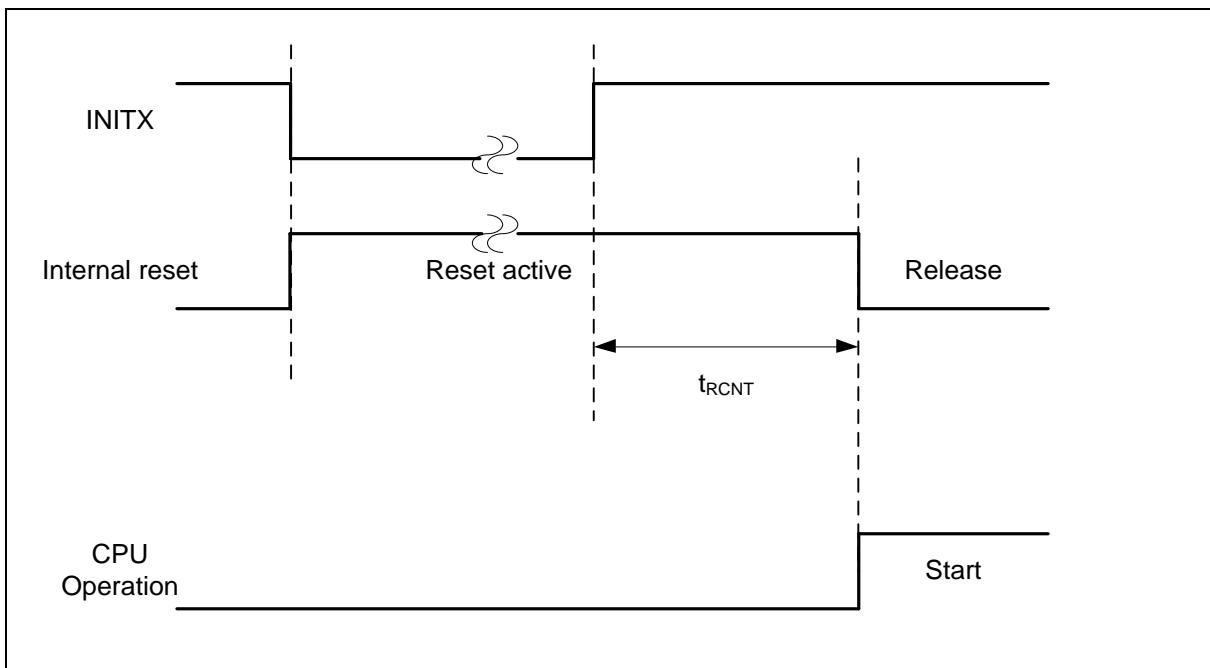

| 12.9.2 復帰要因：リセット           | 106        |

| <b>13.オーダ型格</b>            | <b>108</b> |

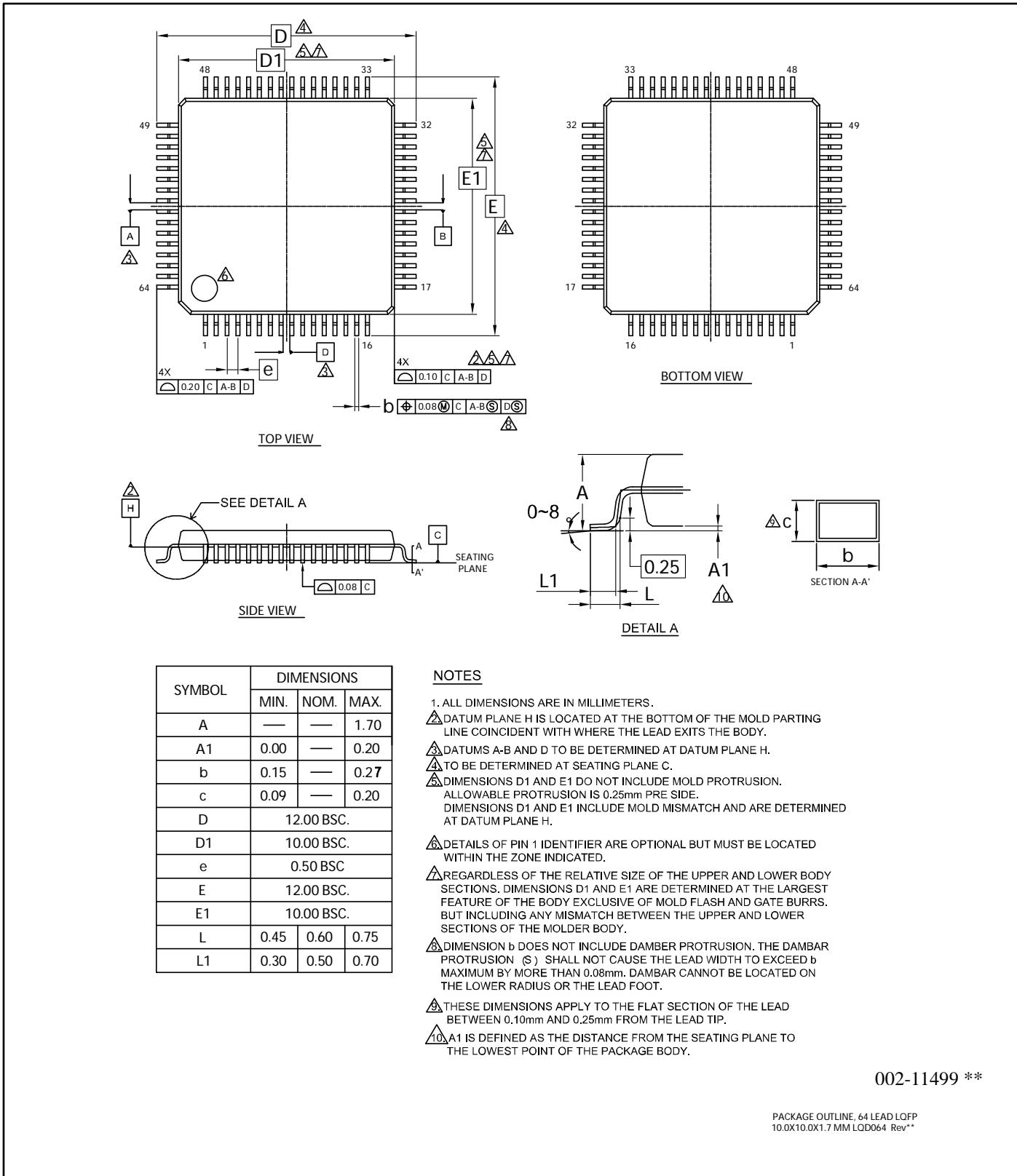

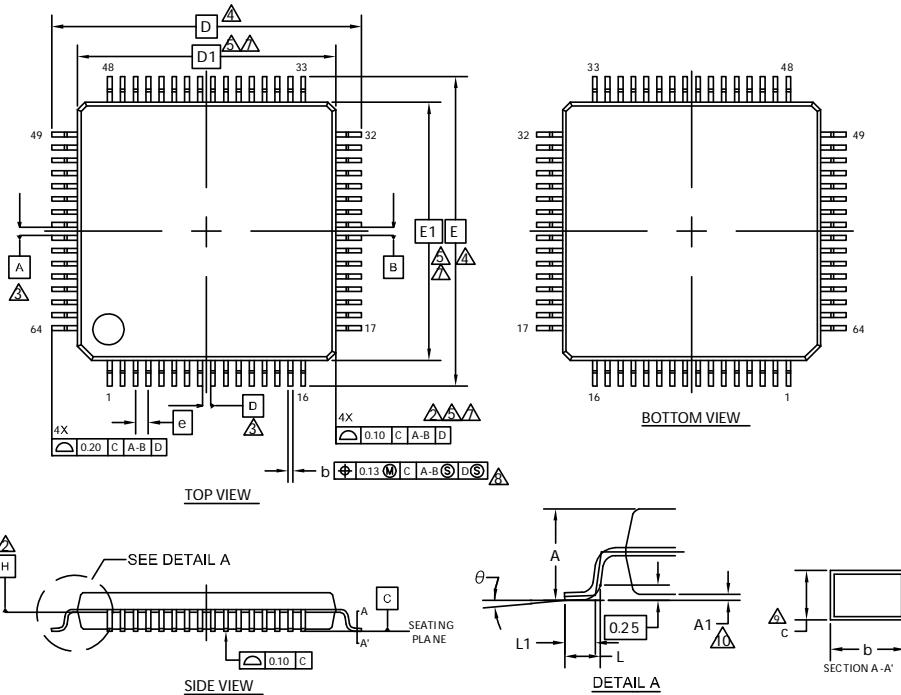

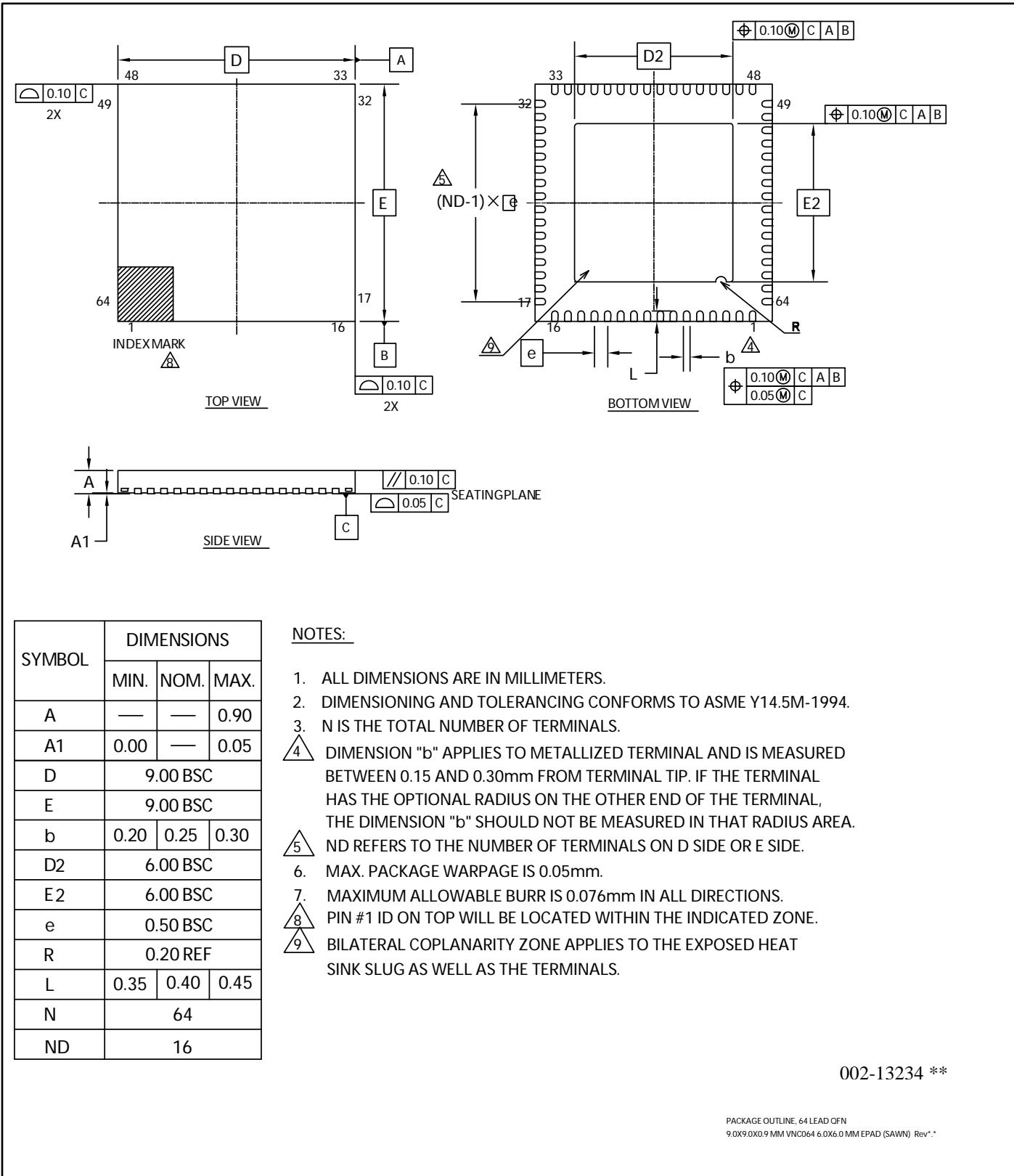

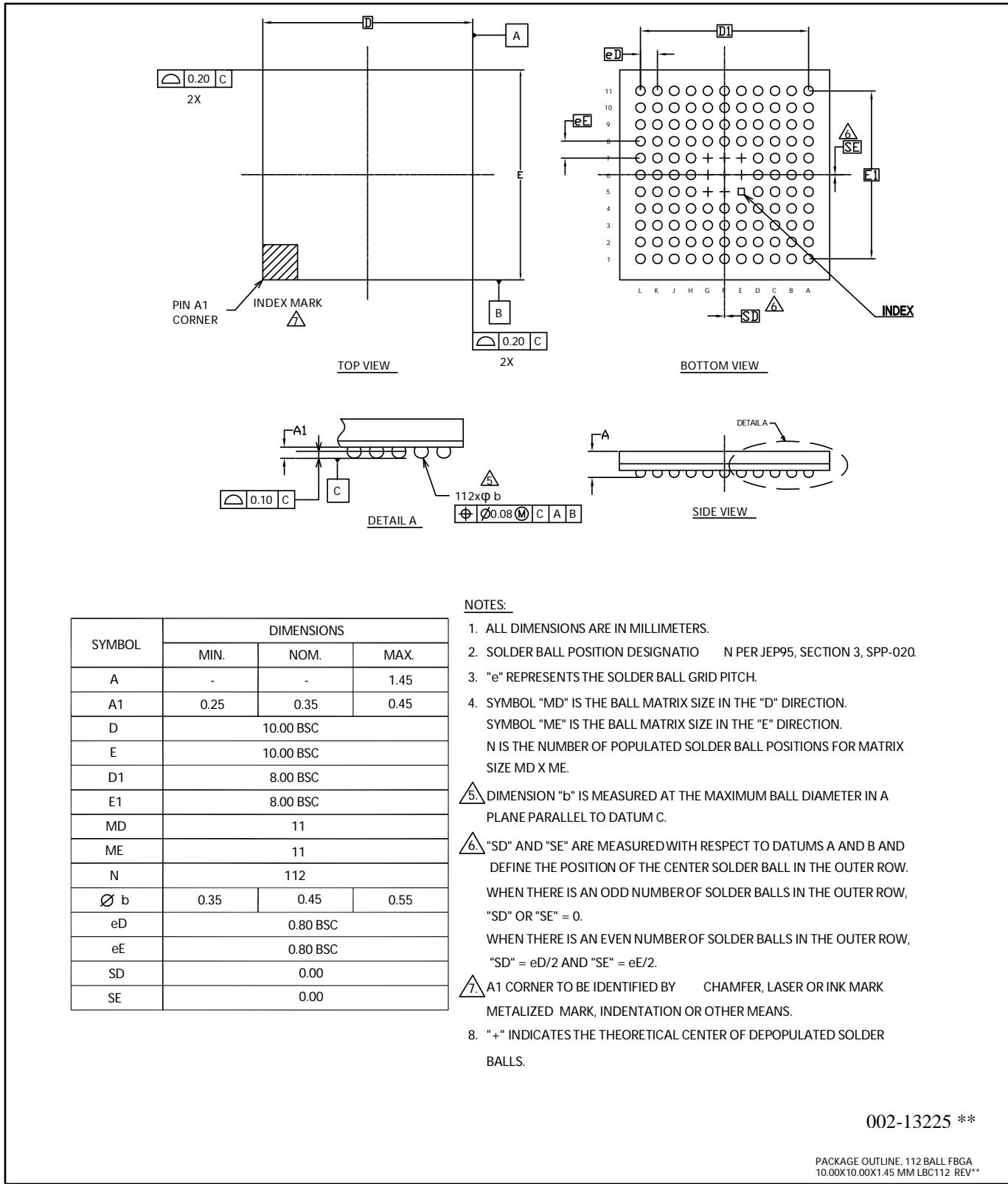

| <b>14.パッケージ・外形寸法図</b>      | <b>110</b> |

| <b>15.エラッタ</b>             | <b>119</b> |

| 15.1 影響を受ける型格              | 119        |

| 15.2 認定の状況                 | 119        |

| 15.3 エラッタのまとめ              | 119        |

| <b>16.主な変更内容</b>           | <b>123</b> |

| <b>改訂履歴</b>                | <b>125</b> |

| <b>セールス、ソリューションおよび法律情報</b> | <b>126</b> |

## 1. 品種構成

### メモリサイズ

| 品種名                   |       | MB9AFA41LB/MB/NB | MB9AFA42LB/MB/NB | MB9AFA44LB/MB/NB |

|-----------------------|-------|------------------|------------------|------------------|

| オンチップ<br>フラッシュ<br>メモリ | メイン領域 | 64 K バイト         | 128 K バイト        | 256 K バイト        |

|                       | ワーク領域 | 32 K バイト         | 32 K バイト         | 32 K バイト         |

| オンチップ<br>SRAM         | SRAM0 | 8 K バイト          | 8 K バイト          | 16 K バイト         |

|                       | SRAM1 | 8 K バイト          | 8 K バイト          | 16 K バイト         |

|                       | 計     | 16 K バイト         | 16 K バイト         | 32 K バイト         |

### ファンクション

| 品種名                                            | MB9AFA41LB              | MB9AFA41MB                                                                     | MB9AFA41NB                                                                         |

|------------------------------------------------|-------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 品種名                                            | MB9AFA42LB              | MB9AFA42MB                                                                     | MB9AFA42NB                                                                         |

| 品種名                                            | MB9AFA44LB              | MB9AFA44MB                                                                     | MB9AFA44NB                                                                         |

| 端子数                                            | 64                      | 80/96                                                                          | 100/112                                                                            |

| CPU                                            |                         | Cortex-M3                                                                      |                                                                                    |

| 周波数                                            |                         | 40 MHz                                                                         |                                                                                    |

| 電源電圧範囲                                         |                         | 1.65 V ~ 3.6 V                                                                 |                                                                                    |

| DMAC                                           |                         | 8 ch.                                                                          |                                                                                    |

| 外部バスインターフェース                                   | -                       | Addr: 21-bit (最大)<br>R/Wdata: 8-bit (最大)<br>CS:4 (最大)<br>SRAM,<br>NOR フラッシュメモリ | Addr: 25-bit (最大)<br>R/Wdata: 8-/16-bit (最大)<br>CS:8 (最大)<br>SRAM,<br>NOR フラッシュメモリ |

| LCD コントローラ                                     | 20 SEG × 8 COM<br>(最大)  | 33 SEG × 8 COM<br>(最大)                                                         | 40 SEG × 8 COM<br>(最大)                                                             |

| マルチファンクションシリアル<br>(UART/CSIO/I <sup>2</sup> C) |                         | 8 ch. (最大)<br>FIFO (16 段 × 9 ビット)あり: ch.4 ~ ch.7<br>FIFO なし: ch.0 ~ ch.3       |                                                                                    |

| ベースタイマ<br>(PWC/リロードタイマ/PWM/PPG)                |                         | 8 ch. (最大)                                                                     |                                                                                    |

| デュアルタイマ                                        |                         | 1 unit                                                                         |                                                                                    |

| HDMI-CEC/リモコン受信                                |                         | 2 ch. (最大)                                                                     |                                                                                    |

| リアルタイムクロック                                     |                         | 1 unit                                                                         |                                                                                    |

| 時計カウンタ                                         |                         | 1 unit                                                                         |                                                                                    |

| CRC アクセラレータ                                    |                         | Yes                                                                            |                                                                                    |

| ウォッチドッグタイマ                                     |                         | 1 ch. (SW) + 1 ch. (HW)                                                        |                                                                                    |

| 外部割込み                                          | 8 pin (最大) +<br>NMI × 1 | 11 pin (最大) +<br>NMI × 1                                                       | 16 pin (最大) +<br>NMI × 1                                                           |

| I/O ポート                                        | 51 pin (最大)             | 66 pin (最大)                                                                    | 83 pin (最大)                                                                        |

| 12 ビット A/D コンバータ                               | 12 ch. (2unit)          | 17 ch. (2unit)                                                                 | 24 ch. (2unit)                                                                     |

| クロック異常検出機能(CSV)                                |                         | Yes                                                                            |                                                                                    |

| 低電圧検出機能(LVD)                                   |                         | 2 ch.                                                                          |                                                                                    |

| 内蔵 CR                                          | 高速                      | 4 MHz (±2%)                                                                    |                                                                                    |

|                                                | 低速                      | 100 kHz (標準)                                                                   |                                                                                    |

| デバッグ機能                                         |                         | SWJ-DP                                                                         | SWJ-DP/ETM                                                                         |

| ユニーク ID                                        |                         | Yes                                                                            |                                                                                    |

### <注意事項>

- 各製品に搭載される周辺機能の信号は、パッケージの端子数制限により、すべて割り当てることはできません。ご使用される機能に応じて、I/O ポートのポートリロケート機能を用いて、端子割り当てを行う必要があります。

- 内蔵 CR のクロック周波数精度については、『12. 電気的特性 12.5. 交流規格 12.5.3 内蔵 CR 発振規格』を参照してください。

## 2. パッケージと品種対応

| パッケージ                        | 品種名 | MB9AFA41LB<br>MB9AFA42LB<br>MB9AFA44LB | MB9AFA41MB<br>MB9AFA42MB<br>MB9AFA44MB | MB9AFA41NB<br>MB9AFA42NB<br>MB9AFA44NB |

|------------------------------|-----|----------------------------------------|----------------------------------------|----------------------------------------|

| LQFP: LQD064 (0.5 mm pitch)  |     | ○                                      | -                                      | -                                      |

| LQFP: LQG064 (0.65 mm pitch) |     | ○                                      | -                                      | -                                      |

| QFN: VNC064 (0.5 mm pitch)   |     | ○                                      | -                                      | -                                      |

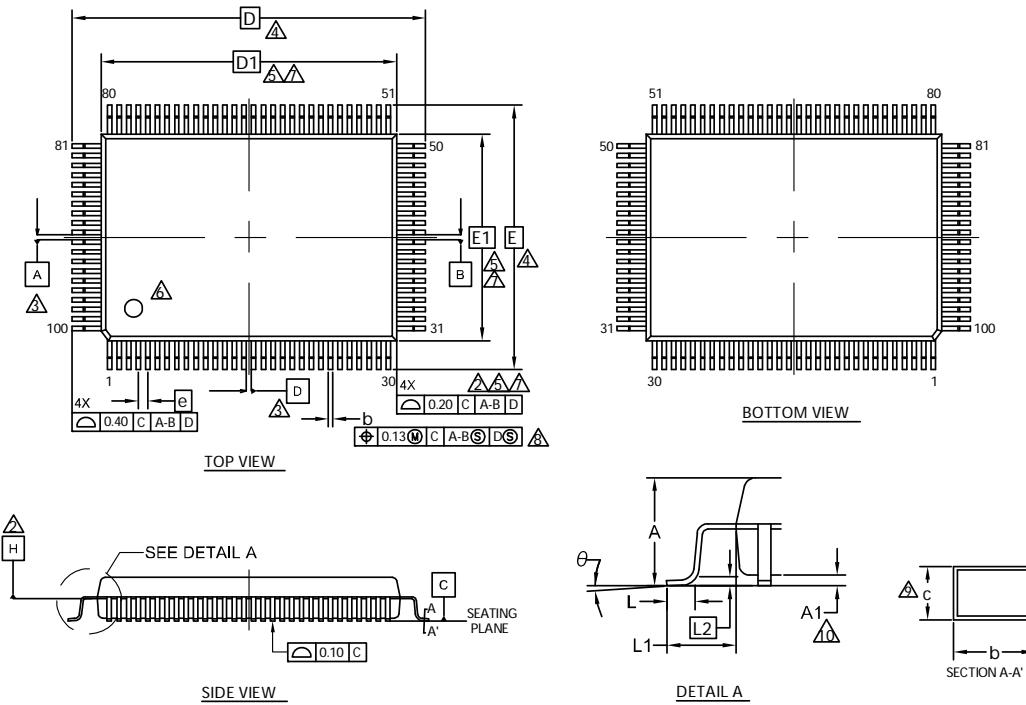

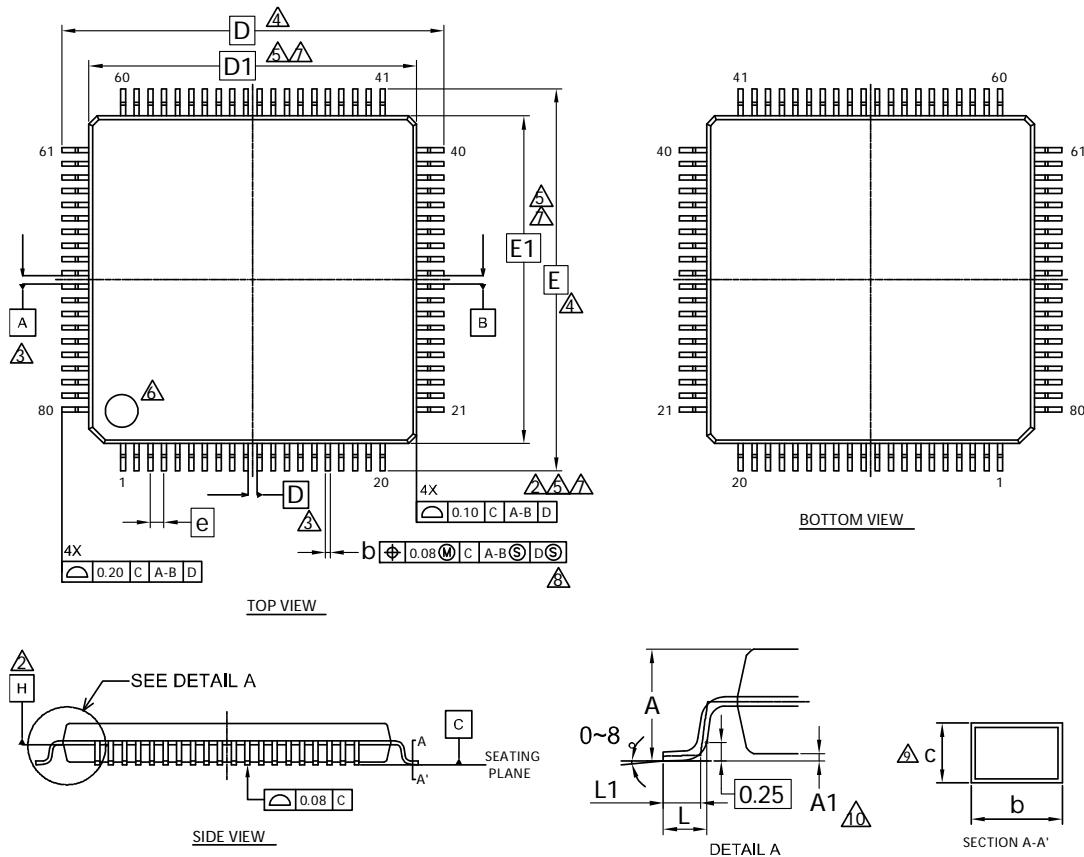

| LQFP: LQH080 (0.5 mm pitch)  |     | -                                      | ○                                      | -                                      |

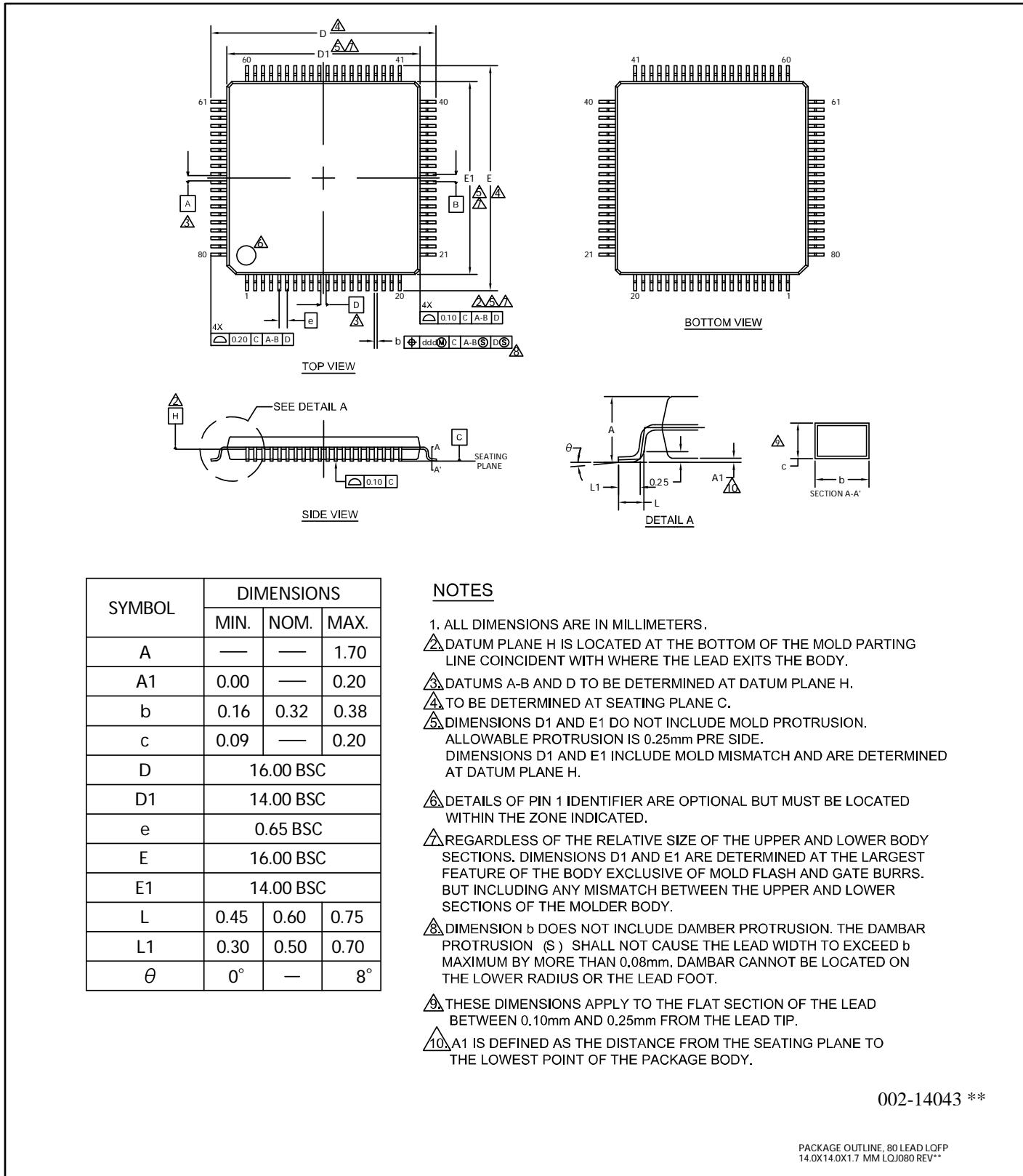

| LQFP: LQJ080 (0.65 mm pitch) |     | -                                      | ○                                      | -                                      |

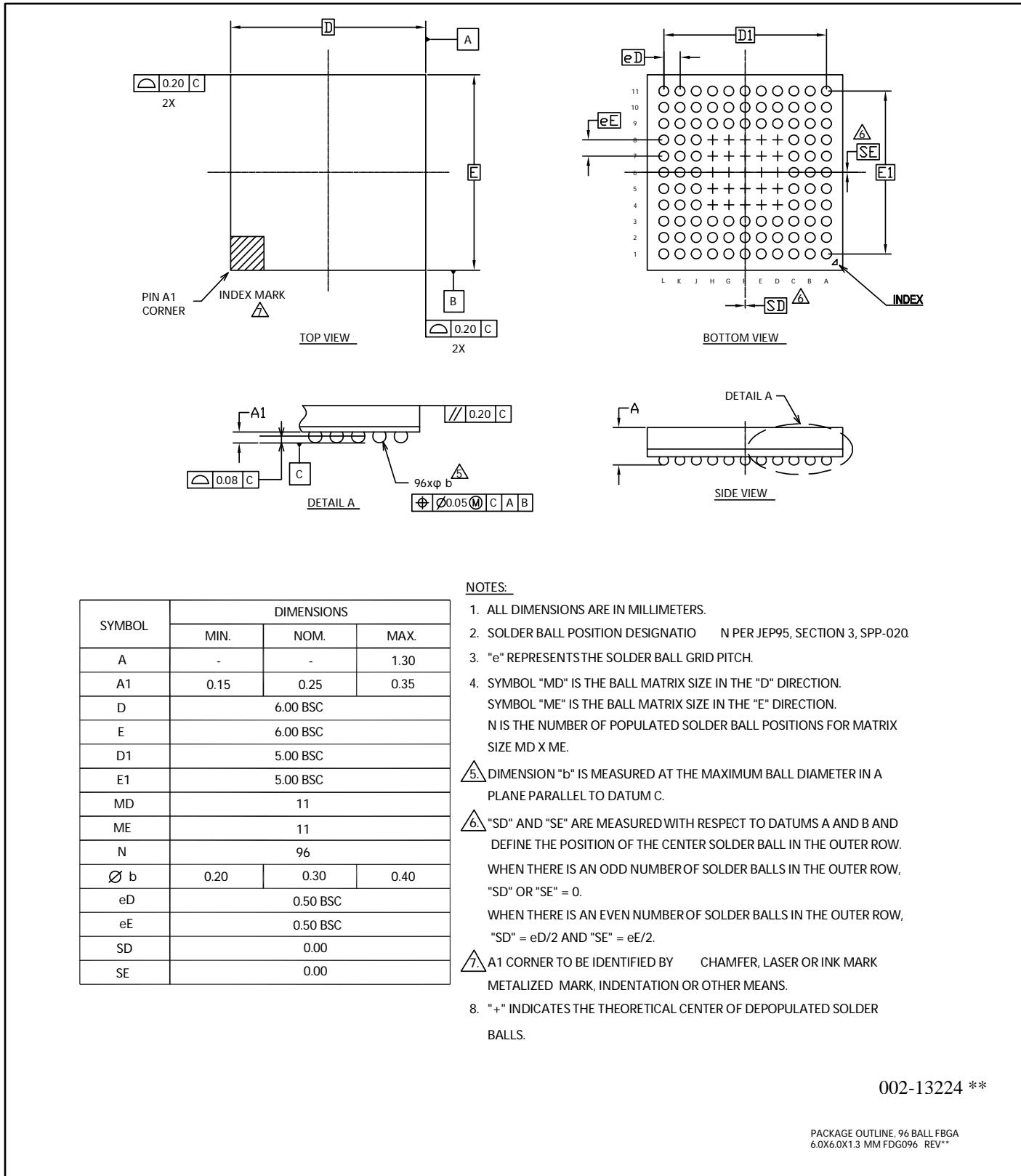

| BGA: FDG096 (0.5 mm pitch)   |     | -                                      | ○                                      | -                                      |

| LQFP: LQI100 (0.5 mm pitch)  |     | -                                      | -                                      | ○                                      |

| QFP: PQH100 (0.65 mm pitch)  |     | -                                      | -                                      | ○                                      |

| BGA: LBC112 (0.8 mm pitch)   |     | -                                      | -                                      | ○                                      |

○: 対応

**<注意事項>**

- 各パッケージの詳細は「14. パッケージ・外形寸法図」を参照してください。

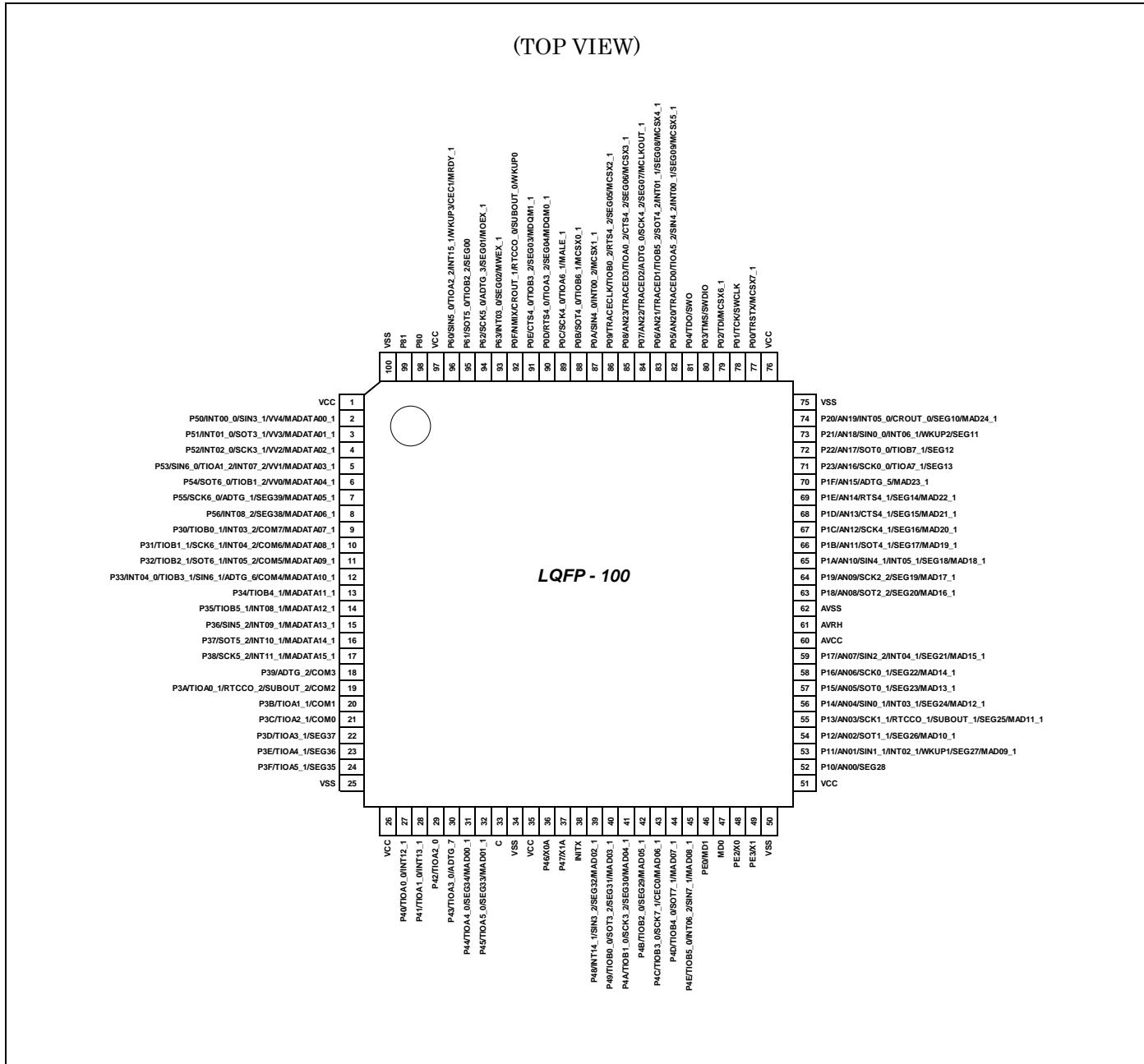

### 3. 端子配列図

LQI100

#### <注意事項>

- XXX\_1, XXX\_2 のように「\_(アンダーバー)」がついている端子の、「\_」以降の数字はリロケーションポート番号を示しています。これらの端子は1つのチャネルに複数の機能があり、それぞれの機能ごとに端子名があります。拡張ポート機能レジスタ (EPFR) によって利用する端子名を選択してください。

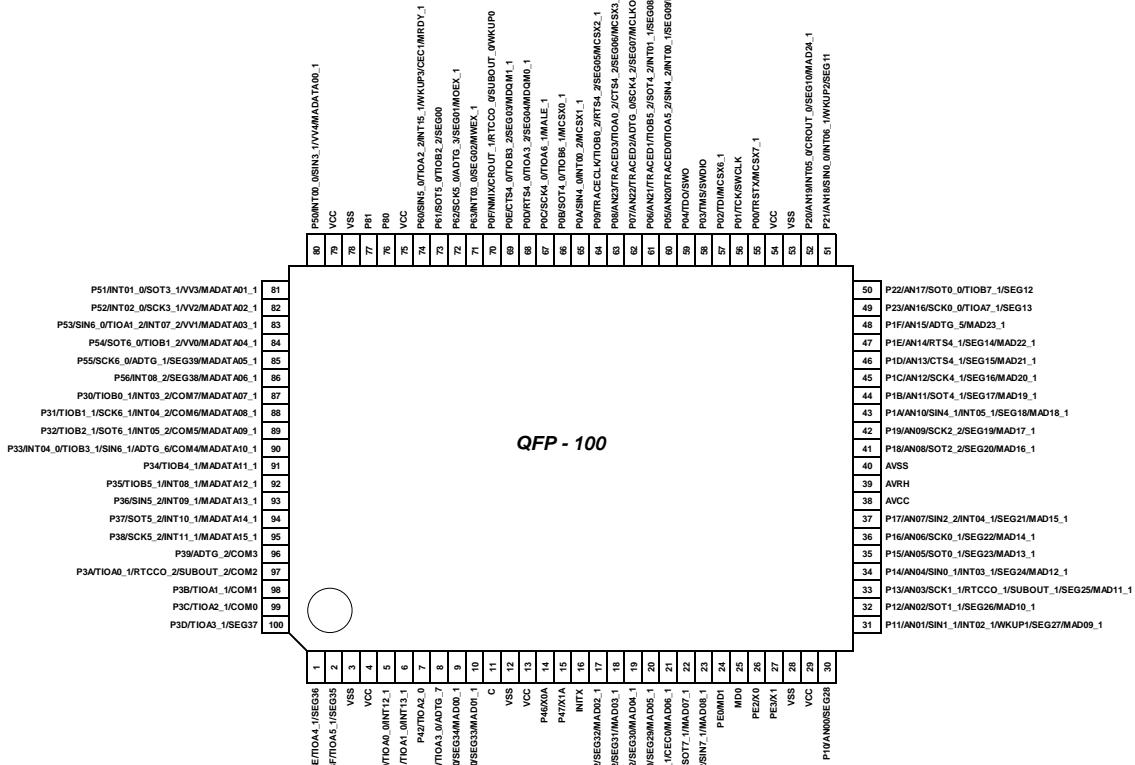

## PQH100

(TOP VIEW)

## &lt;注意事項&gt;

- XXX\_1, XXX\_2 のように「\_ (アンダバー)」がついている端子の、「\_」以降の数字はリロケーションポート番号を示しています。これらの端子は1つのチャネルに複数の機能があり、それぞれの機能ごとに端子名があります。拡張ポート機能レジスタ (EPFR) によって利用する端子名を選択してください。

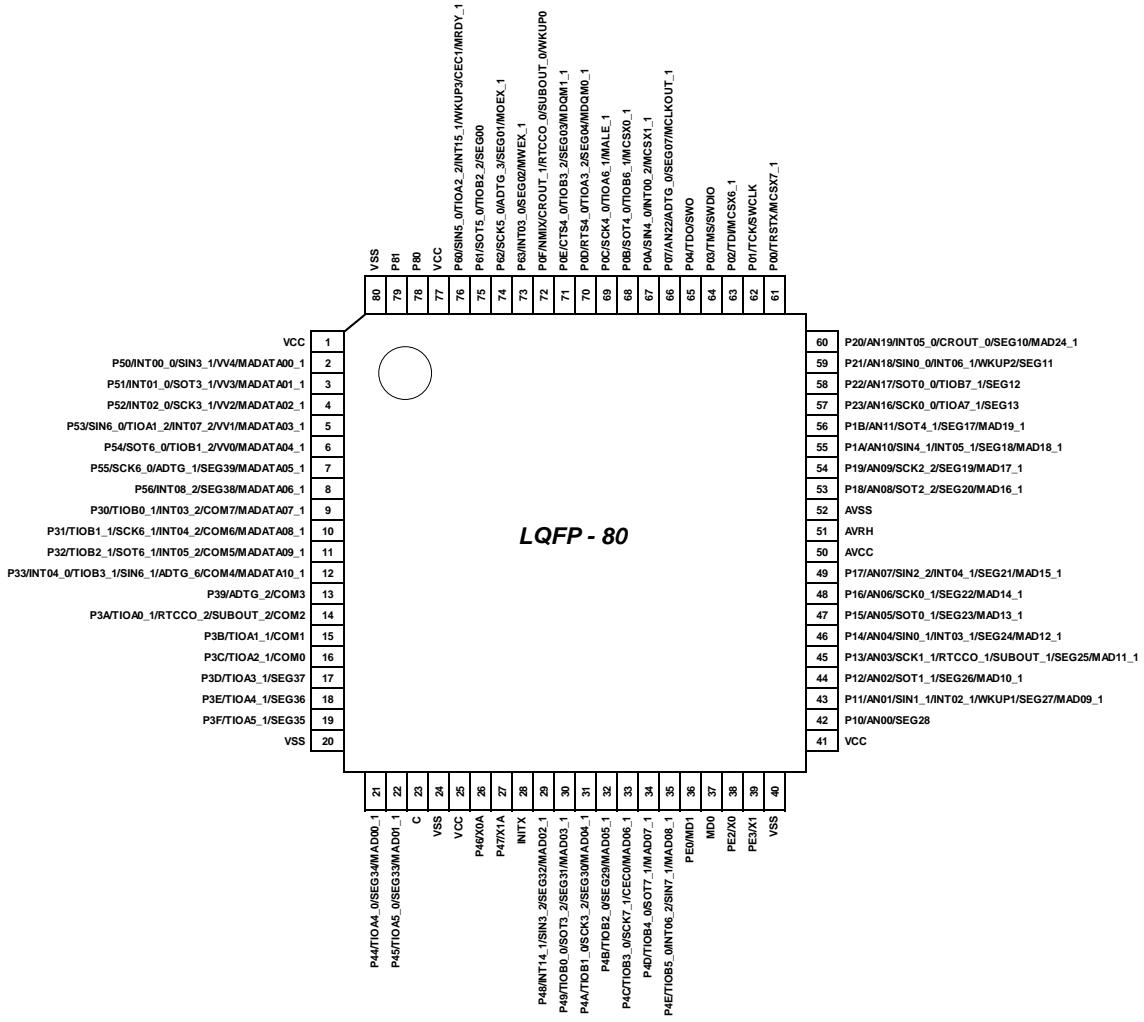

**LQH080/ LQJ080**

(TOP VIEW)

**<注意事項>**

- XXX\_1, XXX\_2 のように「\_(アンダーバー)」がついている端子の、「\_」以降の数字はリロケーションポート番号を示しています。これらの端子は1つのチャネルに複数の機能があり、それぞれの機能ごとに端子名があります。拡張ポート機能レジスタ (EPFR)によって利用する端子名を選択してください。

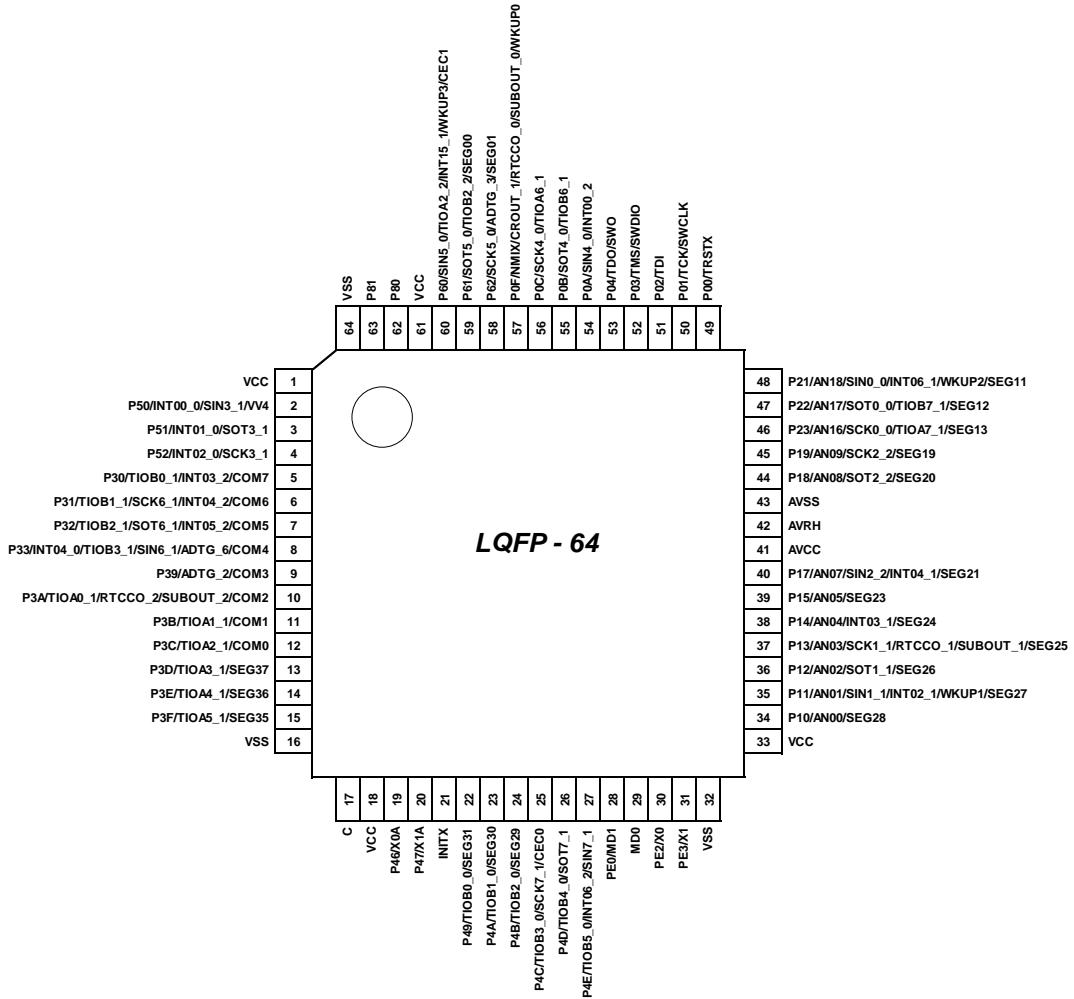

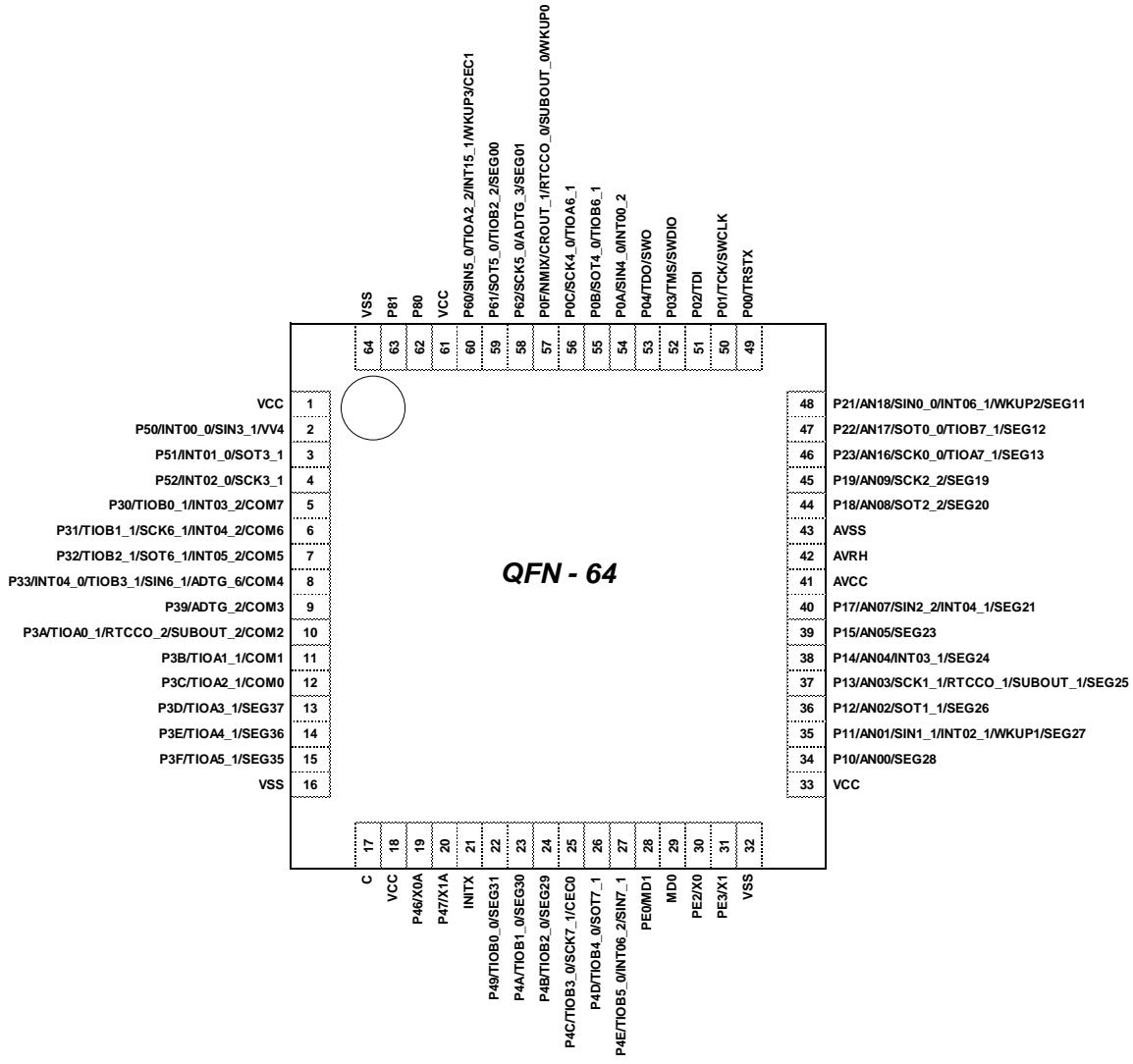

**LQD064/ LQG064**

(TOP VIEW)

**<注意事項>**

- XXX\_1, XXX\_2 のように「\_(アンダーバー)」がついている端子の、「\_」以降の数字はリロケーションポート番号を示しています。これらの端子は1つのチャネルに複数の機能があり、それぞれの機能ごとに端子名があります。拡張ポート機能レジスタ (EPFR) によって利用する端子名を選択してください。

**VNC064**

(TOP VIEW)

**<注意事項>**

- XXX\_1, XXX\_2 のように「\_(アンダバー)」がついている端子の、「\_」以降の数字はリロケーションポート番号を示しています。これらの端子は1つのチャネルに複数の機能があり、それぞれの機能ごとに端子名があります。拡張ポート機能レジスタ (EPFR) によって利用する端子名を選択してください。

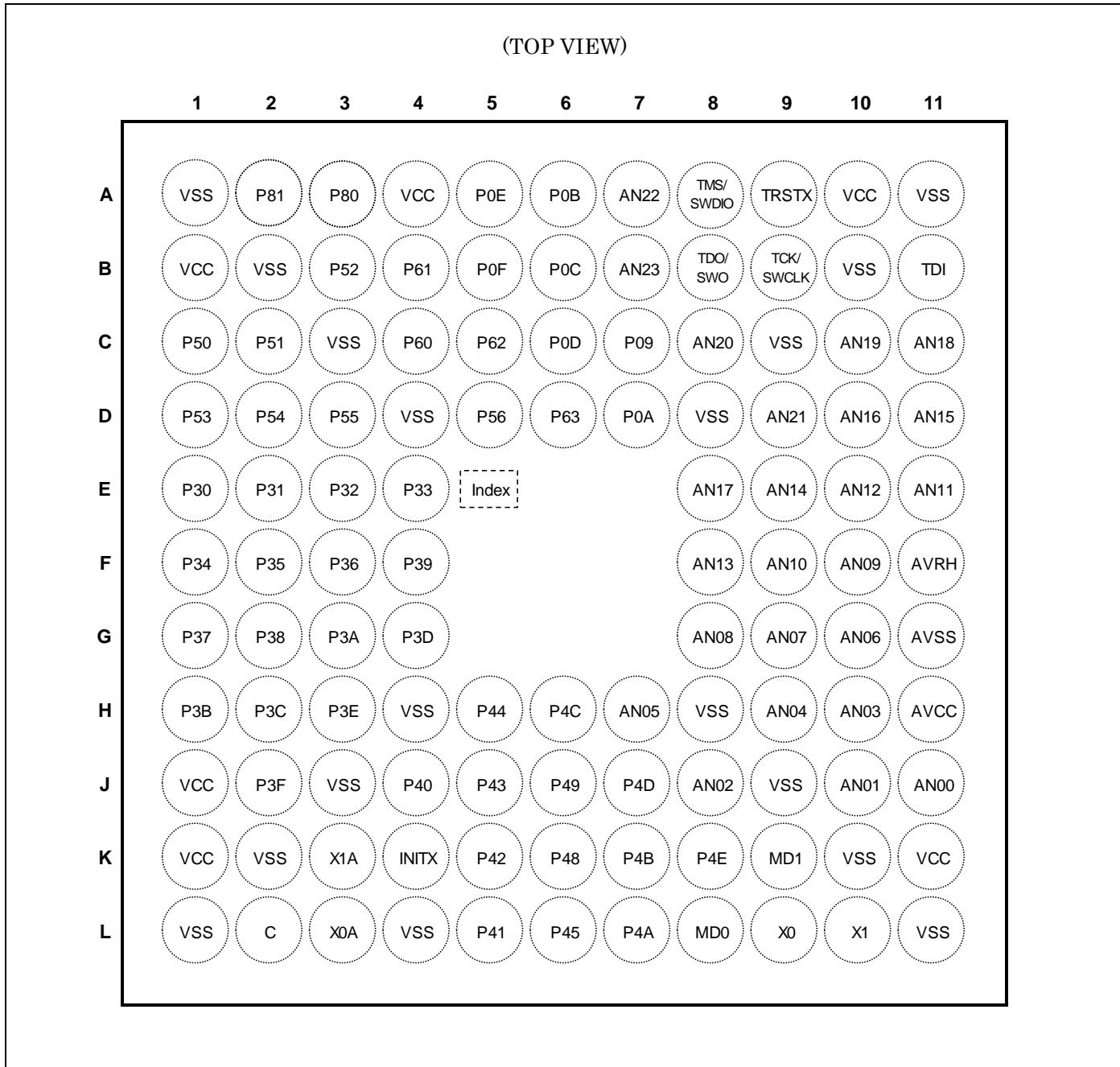

**LBC112**

**<注意事項>**

- XXX\_1, XXX\_2 のように「\_(アンダバー)」がついている端子の、「\_」以降の数字はリロケーションポート番号を示しています。これらの端子は1つのチャネルに複数の機能があり、それぞれの機能ごとに端子名があります。拡張ポート機能レジスタ (EPFR) によって利用する端子名を選択してください。

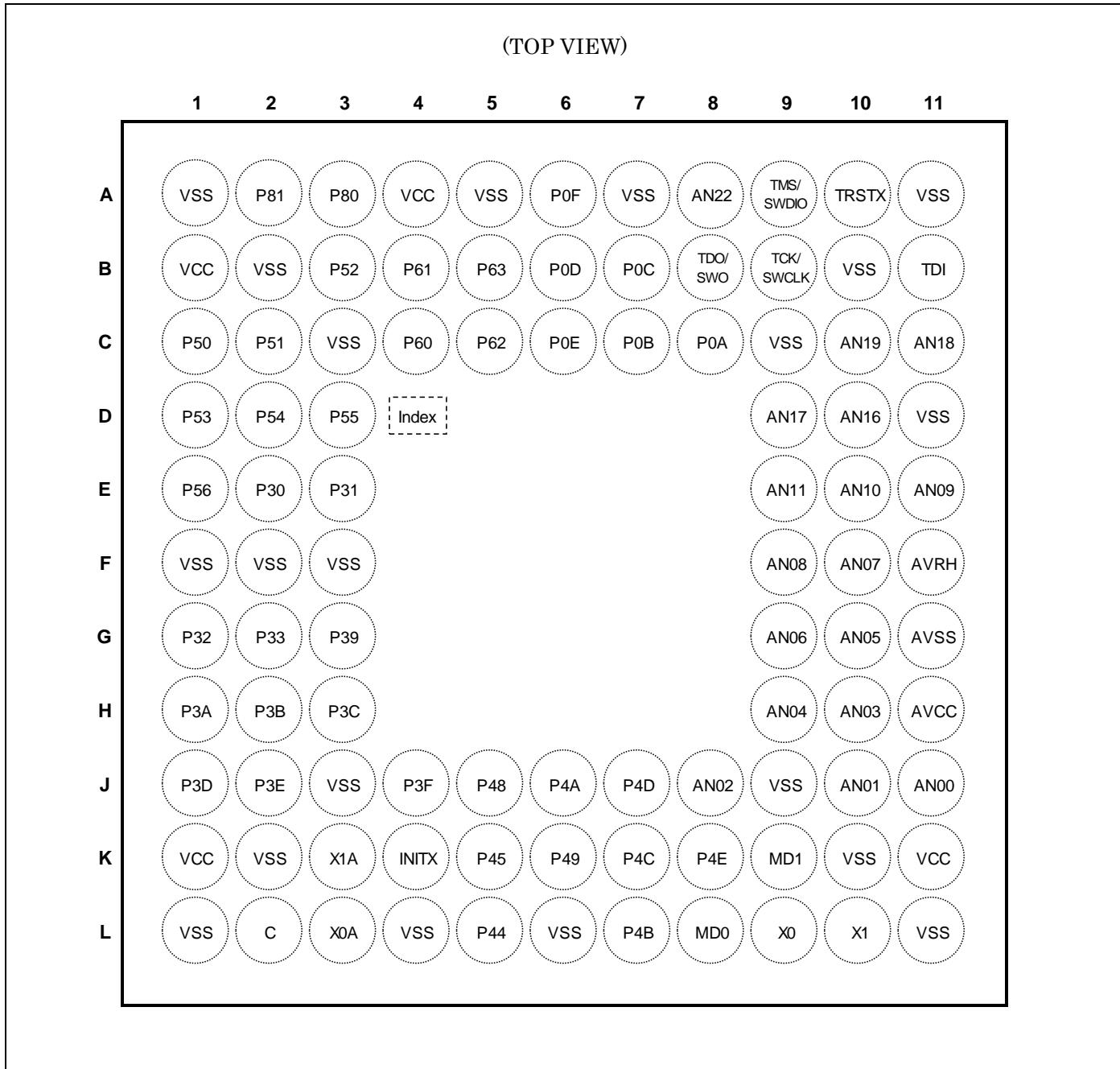

**FDG096**

**<注意事項>**

- XXX\_1, XXX\_2 のように「\_(アンダバー)」がついている端子の、「\_」以降の数字はリロケーションポート番号を示しています。これらの端子は1つのチャネルに複数の機能があり、それぞれの機能ごとに端子名があります。拡張ポート機能レジスタ(EPFR)によって利用する端子名を選択してください。

## 4. 端子機能一覧

### 端子番号別

XXX\_1, XXX\_2 のように、「\_(アンダバー)」がついている端子の、「\_」以降の数字はリロケーションポート番号を示しています。これらの端子は 1 つのチャネルに複数の機能があり、それぞれの機能ごとに端子名があります。拡張ポート機能レジスタ(EPFR)によって利用する端子名を選択してください。

| 端子番号     |         |         |         |        |                   | 端子名                | 入出力<br>回路形式 | 端子状態<br>形式 |

|----------|---------|---------|---------|--------|-------------------|--------------------|-------------|------------|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |                    |             |            |

| 1        | 79      | B1      | 1       | B1     | 1                 | VCC                | -           | -          |

| 2        | 80      | C1      | 2       | C1     | 2                 | P50                | J           | Y          |

|          |         |         |         |        |                   | INT00_0            |             |            |

|          |         |         |         |        |                   | SIN3_1             |             |            |

|          |         |         |         |        |                   | VV4                |             |            |

|          |         |         |         |        |                   | MADATA00_1         |             |            |

| 3        | 81      | C2      | 3       | C2     | -                 | P51                | J           | Y          |

|          |         |         |         |        |                   | INT01_0            |             |            |

|          |         |         |         |        |                   | SOT3_1<br>(SDA3_1) |             |            |

|          |         |         |         |        |                   | VV3                |             |            |

|          |         |         |         |        |                   | MADATA01_1         |             |            |

| -        | -       | -       | -       | -      | 3                 | P51                | E           | L          |

|          |         |         |         |        |                   | INT01_0            |             |            |

|          |         |         |         |        |                   | SOT3_1<br>(SDA3_1) |             |            |

|          |         |         |         |        |                   | P52                |             |            |

| 4        | 82      | B3      | 4       | B3     | -                 | INT02_0            | J           | Y          |

|          |         |         |         |        |                   | SCK3_1<br>(SCL3_1) |             |            |

|          |         |         |         |        |                   | VV2                |             |            |

|          |         |         |         |        |                   | MADATA02_1         |             |            |

|          |         |         |         |        |                   | P52                |             |            |

| -        | -       | -       | -       | -      | 4                 | INT02_0            | E           | L          |

|          |         |         |         |        |                   | SCK3_1<br>(SCL3_1) |             |            |

|          |         |         |         |        |                   | P53                | J           | Y          |

|          |         |         |         |        |                   | SIN6_0             |             |            |

| 5        | 83      | D1      | 5       | D1     | -                 | TIOA1_2            |             |            |

|          |         |         |         |        |                   | INT07_2            |             |            |

|          |         |         |         |        |                   | VV1                |             |            |

|          |         |         |         |        |                   | MADATA03_1         |             |            |

|          |         |         |         |        |                   | P54                | J           | X          |

|          |         |         |         |        |                   | SOT6_0<br>(SDA6_0) |             |            |

| 6        | 84      | D2      | 6       | D2     | -                 | TIOB1_2            |             |            |

|          |         |         |         |        |                   | VV0                |             |            |

|          |         |         |         |        |                   | MADATA04_1         |             |            |

| 端子番号     |         |         |         |        |                   | 端子名                | 入出力<br>回路形式 | 端子状態<br>形式 |

|----------|---------|---------|---------|--------|-------------------|--------------------|-------------|------------|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |                    |             |            |

| 7        | 85      | D3      | 7       | D3     | -                 | P55                | K           | U          |

|          |         |         |         |        |                   | SCK6_0<br>(SCL6_0) |             |            |

|          |         |         |         |        |                   | ADTG_1             |             |            |

|          |         |         |         |        |                   | SEG39              |             |            |

|          |         |         |         |        |                   | MADATA05_1         |             |            |

| 8        | 86      | D5      | 8       | E1     | -                 | P56                | K           | V          |

|          |         |         |         |        |                   | INT08_2            |             |            |

|          |         |         |         |        |                   | SEG38              |             |            |

|          |         |         |         |        |                   | MADATA06_1         |             |            |

| 9        | 87      | E1      | 9       | E2     | 5                 | P30                | K           | V          |

|          |         |         |         |        |                   | TIOB0_1            |             |            |

|          |         |         |         |        |                   | INT03_2            |             |            |

|          |         |         |         |        |                   | COM7               |             |            |

|          |         |         |         |        |                   | MADATA07_1         |             |            |

| 10       | 88      | E2      | 10      | E3     | 6                 | P31                | K           | V          |

|          |         |         |         |        |                   | TIOB1_1            |             |            |

|          |         |         |         |        |                   | SCK6_1<br>(SCL6_1) |             |            |

|          |         |         |         |        |                   | INT04_2            |             |            |

|          |         |         |         |        |                   | COM6               |             |            |

|          |         |         |         |        |                   | MADATA08_1         |             |            |

| 11       | 89      | E3      | 11      | G1     | 7                 | P32                | K           | V          |

|          |         |         |         |        |                   | TIOB2_1            |             |            |

|          |         |         |         |        |                   | SOT6_1<br>(SDA6_1) |             |            |

|          |         |         |         |        |                   | INT05_2            |             |            |

|          |         |         |         |        |                   | COM5               |             |            |

|          |         |         |         |        |                   | MADATA09_1         |             |            |

| 12       | 90      | E4      | 12      | G2     | 8                 | P33                | K           | V          |

|          |         |         |         |        |                   | INT04_0            |             |            |

|          |         |         |         |        |                   | TIOB3_1            |             |            |

|          |         |         |         |        |                   | SIN6_1             |             |            |

|          |         |         |         |        |                   | ADTG_6             |             |            |

|          |         |         |         |        |                   | COM4               |             |            |

|          |         |         |         |        |                   | MADATA10_1         |             |            |

| 13       | 91      | F1      | -       | -      | -                 | P34                | E           | K          |

|          |         |         |         |        |                   | TIOB4_1            |             |            |

|          |         |         |         |        |                   | MADATA11_1         |             |            |

| 14       | 92      | F2      | -       | -      | -                 | P35                | E           | L          |

|          |         |         |         |        |                   | TIOB5_1            |             |            |

|          |         |         |         |        |                   | INT08_1            |             |            |

|          |         |         |         |        |                   | MADATA12_1         |             |            |

| 端子番号     |         |         |         |        |                   | 端子名                | 入出力<br>回路形式 | 端子状態<br>形式 |

|----------|---------|---------|---------|--------|-------------------|--------------------|-------------|------------|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |                    |             |            |

| 15       | 93      | F3      | -       | -      | -                 | P36                | E           | L          |

|          |         |         |         |        |                   | SIN5_2             |             |            |

|          |         |         |         |        |                   | INT09_1            |             |            |

|          |         |         |         |        |                   | MADATA13_1         |             |            |

| -        | -       | -       | -       | F1     | -                 | VSS                | -           | -          |

| -        | -       | -       | -       | F2     | -                 | VSS                | -           | -          |

| -        | -       | -       | -       | F3     | -                 | VSS                | -           | -          |

| 16       | 94      | G1      | -       | -      | -                 | P37                | E           | L          |

|          |         |         |         |        |                   | SOT5_2<br>(SDA5_2) |             |            |

|          |         |         |         |        |                   | INT10_1            |             |            |

|          |         |         |         |        |                   | MADATA14_1         |             |            |

|          |         |         |         |        |                   | P38                |             |            |

| 17       | 95      | G2      | -       | -      | -                 | SCK5_2<br>(SCL5_2) | E           | L          |

|          |         |         |         |        |                   | INT11_1            |             |            |

|          |         |         |         |        |                   | MADATA15_1         |             |            |

|          |         |         |         |        |                   | P39                |             |            |

| 18       | 96      | F4      | 13      | G3     | 9                 | ADTG_2             | K           | U          |

|          |         |         |         |        |                   | COM3               |             |            |

|          |         |         |         |        |                   | P3A                |             |            |

| 19       | 97      | G3      | 14      | H1     | 10                | TIOA0_1            | K           | U          |

|          |         |         |         |        |                   | RTCCO_2            |             |            |

|          |         |         |         |        |                   | SUBOUT_2           |             |            |

|          |         |         |         |        |                   | COM2               |             |            |

|          |         |         |         |        |                   | P3B                |             |            |

| 20       | 98      | H1      | 15      | H2     | 11                | TIOA1_1            | K           | U          |

|          |         |         |         |        |                   | COM1               |             |            |

|          |         |         |         |        |                   | P3C                |             |            |

| 21       | 99      | H2      | 16      | H3     | 12                | TIOA2_1            | K           | U          |

|          |         |         |         |        |                   | COM0               |             |            |

|          |         |         |         |        |                   | P3D                |             |            |

| 22       | 100     | G4      | 17      | J1     | 13                | TIOA3_1            | K           | U          |

|          |         |         |         |        |                   | SEG37              |             |            |

|          |         |         |         |        |                   | VSS                |             |            |

| 23       | 1       | H3      | 18      | J2     | 14                | P3E                | K           | U          |

|          |         |         |         |        |                   | TIOA4_1            |             |            |

|          |         |         |         |        |                   | SEG36              |             |            |

| 24       | 2       | J2      | 19      | J4     | 15                | P3F                | K           | U          |

|          |         |         |         |        |                   | TIOA5_1            |             |            |

|          |         |         |         |        |                   | SEG35              |             |            |

| 25       | 3       | L1      | 20      | L1     | 16                | VSS                | -           | -          |

| 26       | 4       | J1      | -       | -      | -                 | VCC                | -           | -          |

| 端子番号     |         |         |         |        |                   | 端子名                                          | 入出力<br>回路形式 | 端子状態<br>形式 |  |

|----------|---------|---------|---------|--------|-------------------|----------------------------------------------|-------------|------------|--|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |                                              |             |            |  |

| 27       | 5       | J4      | -       | -      | -                 | P40<br>TIOA0_0<br>INT12_1                    | E           | L          |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

| 28       | 6       | L5      | -       | -      | -                 | P41<br>TIOA1_0<br>INT13_1                    | E           | L          |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

| 29       | 7       | K5      | -       | -      | -                 | P42<br>TIOA2_0                               | E           | K          |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

| 30       | 8       | J5      | -       | -      | -                 | P43<br>TIOA3_0<br>ADTG_7                     | E           | K          |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

| 31       | 9       | H5      | 21      | L5     | -                 | P44<br>TIOA4_0<br>SEG34<br>MAD00_1           | K           | U          |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

| 32       | 10      | L6      | 22      | K5     | -                 | P45<br>TIOA5_0<br>SEG33<br>MAD01_1           | K           | U          |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

| -        | -       | K2      | -       | K2     | -                 | VSS                                          | -           |            |  |

| -        | -       | J3      | -       | J3     | -                 | VSS                                          | -           |            |  |

| -        | -       | H4      | -       | -      | -                 | VSS                                          | -           |            |  |

| -        | -       | -       | -       | L6     | -                 | VSS                                          | -           |            |  |

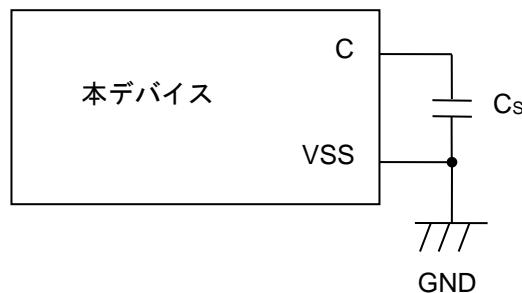

| 33       | 11      | L2      | 23      | L2     | 17                | C                                            | -           |            |  |

| 34       | 12      | L4      | 24      | L4     | -                 | VSS                                          | -           |            |  |

| 35       | 13      | K1      | 25      | K1     | 18                | VCC                                          | -           |            |  |

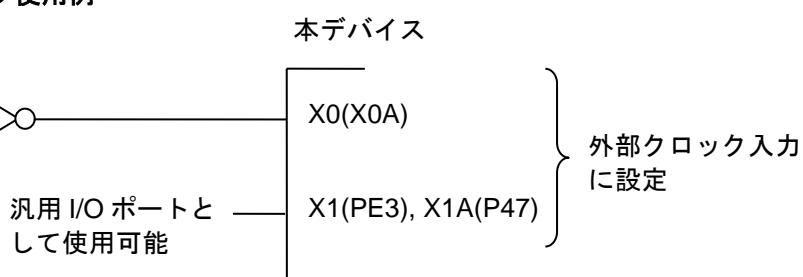

| 36       | 14      | L3      | 26      | L3     | 19                | P46<br>X0A                                   | D           | F          |  |

|          |         |         |         |        |                   |                                              |             |            |  |

| 37       | 15      | K3      | 27      | K3     | 20                | P47<br>X1A                                   | D           | G          |  |

|          |         |         |         |        |                   |                                              |             |            |  |

| 38       | 16      | K4      | 28      | K4     | 21                | INITX                                        | B           | C          |  |

| 39       | 17      | K6      | 29      | J5     | -                 | P48<br>INT14_1<br>SIN3_2<br>SEG32<br>MAD02_1 | K           | V          |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

| 40       | 18      | J6      | 30      | K6     | 22                | P49<br>TIOB0_0<br>SEG31                      | K           | U          |  |

|          |         |         |         |        |                   |                                              |             |            |  |

|          |         |         |         |        | -                 | SOT3_2<br>(SDA3_2)                           |             |            |  |

|          |         |         |         |        |                   | MAD03_1                                      |             |            |  |

|          |         |         |         |        |                   |                                              |             |            |  |

| 端子番号     |         |         |         |        |                   | 端子名                | 入出力<br>回路形式 | 端子状態<br>形式 |  |

|----------|---------|---------|---------|--------|-------------------|--------------------|-------------|------------|--|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |                    |             |            |  |

| 41       | 19      | L7      | 31      | J6     | 23                | P4A                | K           | U          |  |

|          |         |         |         |        |                   | TIOB1_0            |             |            |  |

|          |         |         |         |        |                   | SEG30              |             |            |  |

|          |         |         |         |        |                   | SCK3_2<br>(SCL3_2) |             |            |  |

|          |         |         |         |        |                   | MAD04_1            |             |            |  |

| 42       | 20      | K7      | 32      | L7     | 24                | P4B                | K           | U          |  |

|          |         |         |         |        |                   | TIOB2_0            |             |            |  |

|          |         |         |         |        |                   | SEG29              |             |            |  |

|          |         |         |         |        |                   | -                  |             |            |  |

| 43       | 21      | H6      | 33      | K7     | 25                | P4C                | I*          | S          |  |

|          |         |         |         |        |                   | TIOB3_0            |             |            |  |

|          |         |         |         |        |                   | SCK7_1<br>(SCL7_1) |             |            |  |

|          |         |         |         |        |                   | CEC0               |             |            |  |

|          |         |         |         |        |                   | -                  |             |            |  |

| 44       | 22      | J7      | 34      | J7     | 26                | P4D                | I*          | K          |  |

|          |         |         |         |        |                   | TIOB4_0            |             |            |  |

|          |         |         |         |        |                   | SOT7_1<br>(SDA7_1) |             |            |  |

|          |         |         |         |        |                   | -                  |             |            |  |

|          |         |         |         |        |                   | MAD07_1            |             |            |  |

| 45       | 23      | K8      | 35      | K8     | 27                | P4E                | I*          | L          |  |

|          |         |         |         |        |                   | TIOB5_0            |             |            |  |

|          |         |         |         |        |                   | INT06_2            |             |            |  |

|          |         |         |         |        |                   | SIN7_1             |             |            |  |

|          |         |         |         |        |                   | -                  |             |            |  |

| 46       | 24      | K9      | 36      | K9     | 28                | MD1                | C           | E          |  |

|          |         |         |         |        |                   | PE0                |             |            |  |

| 47       | 25      | L8      | 37      | L8     | 29                | MD0                | G           | D          |  |

| 48       | 26      | L9      | 38      | L9     | 30                | X0                 | A           | A          |  |

|          |         |         |         |        |                   | PE2                |             |            |  |

| 49       | 27      | L10     | 39      | L10    | 31                | X1                 | A           | B          |  |

|          |         |         |         |        |                   | PE3                |             |            |  |

| 50       | 28      | L11     | 40      | L11    | 32                | VSS                | -           |            |  |

| 51       | 29      | K11     | 41      | K11    | 33                | VCC                | -           |            |  |

| 52       | 30      | J11     | 42      | J11    | 34                | P10                | L           | W          |  |

|          |         |         |         |        |                   | AN00               |             |            |  |

|          |         |         |         |        |                   | SEG28              |             |            |  |

| 53       | 31      | J10     | 43      | J10    | 35                | P11                | L           | R          |  |

|          |         |         |         |        |                   | AN01               |             |            |  |

|          |         |         |         |        |                   | SIN1_1             |             |            |  |

|          |         |         |         |        |                   | INT02_1            |             |            |  |

|          |         |         |         |        |                   | WKUP1              |             |            |  |

|          |         |         |         |        |                   | SEG27              |             |            |  |

|          |         |         |         |        |                   | -                  |             |            |  |

| MAD09_1  |         |         |         |        |                   |                    |             |            |  |

| 端子番号     |         |         |         |        |                   | 端子名                | 入出力<br>回路形式 | 端子状態<br>形式 |

|----------|---------|---------|---------|--------|-------------------|--------------------|-------------|------------|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |                    |             |            |

| 54       | 32      | J8      | 44      | J8     | 36                | P12                | L           | W          |

|          |         |         |         |        |                   | AN02               |             |            |

|          |         |         |         |        |                   | SOT1_1<br>(SDA1_1) |             |            |

|          |         |         |         |        |                   | SEG26              |             |            |

|          |         |         |         |        |                   | -                  |             |            |

| -        | -       | K10     | -       | K10    | -                 | MAD10_1            | -           | -          |

| -        | -       | J9      | -       | J9     | -                 | VSS                | -           | -          |

| 55       | 33      | H10     | 45      | H10    | 37                | P13                | L           | W          |

|          |         |         |         |        |                   | AN03               |             |            |

|          |         |         |         |        |                   | SCK1_1<br>(SCL1_1) |             |            |

|          |         |         |         |        |                   | RTCCO_1            |             |            |

|          |         |         |         |        |                   | SEG25              |             |            |

|          |         |         |         |        |                   | SUBOUT_1           |             |            |

|          |         |         |         |        |                   | -                  |             |            |

| 56       | 34      | H9      | 46      | H9     | 38                | P14                | L           | N          |

|          |         |         |         |        |                   | AN04               |             |            |

|          |         |         |         |        |                   | INT03_1            |             |            |

|          |         |         |         |        |                   | SEG24              |             |            |

|          |         |         |         |        |                   | -                  |             |            |

|          |         |         |         |        |                   | SIN0_1             |             |            |

| 57       | 35      | H7      | 47      | G10    | 39                | MAD12_1            | L           | W          |

|          |         |         |         |        |                   | P15                |             |            |

|          |         |         |         |        |                   | AN05               |             |            |

|          |         |         |         |        |                   | SEG23              |             |            |

|          |         |         |         |        |                   | -                  |             |            |

|          |         |         |         |        |                   | SOT0_1<br>(SDA0_1) |             |            |

| 58       | 36      | G10     | 48      | G9     | -                 | MAD13_1            | L           | W          |

|          |         |         |         |        |                   | P16                |             |            |

|          |         |         |         |        |                   | AN06               |             |            |

|          |         |         |         |        |                   | SCK0_1<br>(SCL0_1) |             |            |

|          |         |         |         |        |                   | SEG22              |             |            |

|          |         |         |         |        |                   | MAD14_1            |             |            |

| 59       | 37      | G9      | 49      | F10    | 40                | P17                | L           | N          |

|          |         |         |         |        |                   | AN07               |             |            |

|          |         |         |         |        |                   | SIN2_2             |             |            |

|          |         |         |         |        |                   | INT04_1            |             |            |

|          |         |         |         |        |                   | SEG21              |             |            |

|          |         |         |         |        |                   | -                  |             |            |

| 60       | 38      | H11     | 50      | H11    | 41                | AVCC               | -           | -          |

| 61       | 39      | F11     | 51      | F11    | 42                | AVRH               | -           | -          |

| 62       | 40      | G11     | 52      | G11    | 43                | AVSS               | -           | -          |

| 端子番号     |         |         |         |        |                   | 端子名                | 入出力<br>回路形式 | 端子状態<br>形式 |

|----------|---------|---------|---------|--------|-------------------|--------------------|-------------|------------|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |                    |             |            |

| 63       | 41      | G8      | 53      | F9     | 44                | P18                | L           | W          |

|          |         |         |         |        |                   | AN08               |             |            |

|          |         |         |         |        |                   | SOT2_2<br>(SDA2_2) |             |            |

|          |         |         |         |        |                   | SEG20              |             |            |

|          |         |         |         |        |                   | MAD16_1            |             |            |

| 64       | 42      | F10     | 54      | E11    | 45                | P19                | L           | W          |

|          |         |         |         |        |                   | AN09               |             |            |

|          |         |         |         |        |                   | SCK2_2<br>(SCL2_2) |             |            |

|          |         |         |         |        |                   | SEG19              |             |            |

|          |         |         |         |        |                   | -                  |             |            |

| -        | -       | H8      | -       | -      | -                 | VSS                | -           |            |

| 65       | 43      | F9      | 55      | E10    | -                 | P1A                | L           | N          |

|          |         |         |         |        |                   | AN10               |             |            |

|          |         |         |         |        |                   | SIN4_1             |             |            |

|          |         |         |         |        |                   | INT05_1            |             |            |

|          |         |         |         |        |                   | SEG18              |             |            |

|          |         |         |         |        |                   | MAD18_1            |             |            |

| 66       | 44      | E11     | 56      | E9     | -                 | P1B                | L           | W          |

|          |         |         |         |        |                   | AN11               |             |            |

|          |         |         |         |        |                   | SOT4_1<br>(SDA4_1) |             |            |

|          |         |         |         |        |                   | SEG17              |             |            |

|          |         |         |         |        |                   | MAD19_1            |             |            |

| 67       | 45      | E10     | -       | -      | -                 | P1C                | L           | W          |

|          |         |         |         |        |                   | AN12               |             |            |

|          |         |         |         |        |                   | SCK4_1<br>(SCL4_1) |             |            |

|          |         |         |         |        |                   | SEG16              |             |            |

|          |         |         |         |        |                   | MAD20_1            |             |            |

| 68       | 46      | F8      | -       | -      | -                 | P1D                | L           | W          |

|          |         |         |         |        |                   | AN13               |             |            |

|          |         |         |         |        |                   | CTS4_1             |             |            |

|          |         |         |         |        |                   | SEG15              |             |            |

|          |         |         |         |        |                   | MAD21_1            |             |            |

| 69       | 47      | E9      | -       | -      | -                 | P1E                | L           | W          |

|          |         |         |         |        |                   | AN14               |             |            |

|          |         |         |         |        |                   | RTS4_1             |             |            |

|          |         |         |         |        |                   | SEG14              |             |            |

|          |         |         |         |        |                   | MAD22_1            |             |            |

| 70       | 48      | D11     | -       | -      | -                 | P1F                | F           | M          |

|          |         |         |         |        |                   | AN15               |             |            |

|          |         |         |         |        |                   | ADTG_5             |             |            |

|          |         |         |         |        |                   | MAD23_1            |             |            |

| 端子番号     |         |         |         |        |                   | 端子名                | 入出力<br>回路形式 | 端子状態<br>形式 |

|----------|---------|---------|---------|--------|-------------------|--------------------|-------------|------------|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |                    |             |            |

| -        | -       | B10     | -       | B10    | -                 | VSS                | -           | -          |

| -        | -       | C9      | -       | C9     | -                 | VSS                | -           | -          |

| -        | -       | -       | -       | D11    | -                 | VSS                | -           | -          |

| 71       | 49      | D10     | 57      | D10    | 46                | P23                | L           | W          |

|          |         |         |         |        |                   | AN16               |             |            |

|          |         |         |         |        |                   | SCK0_0<br>(SCL0_0) |             |            |

|          |         |         |         |        |                   | TIOA7_1            |             |            |

|          |         |         |         |        |                   | SEG13              |             |            |

| 72       | 50      | E8      | 58      | D9     | 47                | P22                | L           | W          |

|          |         |         |         |        |                   | AN17               |             |            |

|          |         |         |         |        |                   | SOT0_0<br>(SDA0_0) |             |            |

|          |         |         |         |        |                   | TIOB7_1            |             |            |

|          |         |         |         |        |                   | SEG12              |             |            |

| 73       | 51      | C11     | 59      | C11    | 48                | P21                | L           | R          |

|          |         |         |         |        |                   | AN18               |             |            |

|          |         |         |         |        |                   | SIN0_0             |             |            |

|          |         |         |         |        |                   | INT06_1            |             |            |

|          |         |         |         |        |                   | WKUP2              |             |            |

|          |         |         |         |        |                   | SEG11              |             |            |

| 74       | 52      | C10     | 60      | C10    | -                 | P20                | L           | N          |

|          |         |         |         |        |                   | AN19               |             |            |

|          |         |         |         |        |                   | INT05_0            |             |            |

|          |         |         |         |        |                   | CROUT_0            |             |            |

|          |         |         |         |        |                   | SEG10              |             |            |

|          |         |         |         |        |                   | MAD24_1            |             |            |

| 75       | 53      | A11     | -       | A11    | -                 | VSS                | -           | -          |

| 76       | 54      | A10     | -       | -      | -                 | VCC                | -           | -          |

| 77       | 55      | A9      | 61      | A10    | 49                | P00                | E           | J          |

|          |         |         |         |        |                   | TRSTX              |             |            |

|          |         |         |         |        |                   | MCSX7_1            |             |            |

| 78       | 56      | B9      | 62      | B9     | 50                | P01                | E           | J          |

|          |         |         |         |        |                   | TCK                |             |            |

|          |         |         |         |        |                   | SWCLK              |             |            |

| 79       | 57      | B11     | 63      | B11    | 51                | P02                | E           | J          |

|          |         |         |         |        |                   | TDI                |             |            |

|          |         |         |         |        |                   | MCSX6_1            |             |            |

| 80       | 58      | A8      | 64      | A9     | 52                | P03                | E           | J          |

|          |         |         |         |        |                   | TMS                |             |            |

|          |         |         |         |        |                   | SWDIO              |             |            |

| 81       | 59      | B8      | 65      | B8     | 53                | P04                | E           | J          |

|          |         |         |         |        |                   | TDO                |             |            |

|          |         |         |         |        |                   | SWO                |             |            |

| 端子番号     |         |         |         |        |                   | 端子名                | 入出力<br>回路形式 | 端子状態<br>形式 |  |

|----------|---------|---------|---------|--------|-------------------|--------------------|-------------|------------|--|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |                    |             |            |  |

| 82       | 60      | C8      | -       | -      | -                 | P05                | L           | Q          |  |

|          |         |         |         |        |                   | AN20               |             |            |  |

|          |         |         |         |        |                   | TRACED0            |             |            |  |

|          |         |         |         |        |                   | TIOA5_2            |             |            |  |

|          |         |         |         |        |                   | SIN4_2             |             |            |  |

|          |         |         |         |        |                   | INT00_1            |             |            |  |

|          |         |         |         |        |                   | SEG09              |             |            |  |

|          |         |         |         |        |                   | MCSX5_1            |             |            |  |

| -        | -       | D8      | -       | -      | -                 | VSS                | -           | -          |  |

| 83       | 61      | D9      | -       | -      | -                 | P06                | L           | Q          |  |

|          |         |         |         |        |                   | AN21               |             |            |  |

|          |         |         |         |        |                   | TRACED1            |             |            |  |

|          |         |         |         |        |                   | TIOB5_2            |             |            |  |

|          |         |         |         |        |                   | SOT4_2<br>(SDA4_2) |             |            |  |

|          |         |         |         |        |                   | INT01_1            |             |            |  |

|          |         |         |         |        |                   | SEG08              |             |            |  |

|          |         |         |         |        |                   | MCSX4_1            |             |            |  |

| 84       | 62      | A7      | 66      | A8     | -                 | P07                | L           | P          |  |

|          |         |         |         |        |                   | AN22               |             |            |  |

|          |         |         |         |        |                   | ADTG_0             |             |            |  |

|          |         |         |         |        |                   | SEG07              |             |            |  |

|          |         |         | -       | -      |                   | MCLKOUT_1          |             |            |  |

|          |         |         |         |        |                   | TRACED2            |             |            |  |

|          |         |         |         |        |                   | SCK4_2<br>(SCL4_2) |             |            |  |

|          |         |         |         |        |                   | VSS                | -           | -          |  |

| 85       | 63      | B7      | -       | -      | -                 | P08                | L           | P          |  |

|          |         |         |         |        |                   | AN23               |             |            |  |

|          |         |         |         |        |                   | TRACED3            |             |            |  |

|          |         |         |         |        |                   | TIOA0_2            |             |            |  |

|          |         |         |         |        |                   | CTS4_2             |             |            |  |

|          |         |         |         |        |                   | SEG06              |             |            |  |

|          |         |         |         |        |                   | MCSX3_1            |             |            |  |

|          |         |         |         |        |                   | P09                |             |            |  |

| 86       | 64      | C7      | -       | -      | -                 | TRACECLK           | K           | O          |  |

|          |         |         |         |        |                   | TIOB0_2            |             |            |  |

|          |         |         |         |        |                   | RTS4_2             |             |            |  |

|          |         |         |         |        |                   | SEG05              |             |            |  |

|          |         |         |         |        |                   | MCSX2_1            |             |            |  |

|          |         |         |         |        |                   | P0A                | I*          | L          |  |

|          |         |         |         |        |                   | SIN4_0             |             |            |  |

| 87       | 65      | D7      | 67      | C8     | 54                | INT00_2            |             |            |  |

|          |         |         |         |        |                   | MCSX1_1            |             |            |  |

| 端子番号     |         |         |         |        |                   | 端子名                | 入出力<br>回路形式 | 端子状態<br>形式 |  |

|----------|---------|---------|---------|--------|-------------------|--------------------|-------------|------------|--|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |                    |             |            |  |

| 88       | 66      | A6      | 68      | C7     | 55                | P0B                | I*          | K          |  |

|          |         |         |         |        |                   | SOT4_0<br>(SDA4_0) |             |            |  |

|          |         |         |         |        |                   | TIOB6_1            |             |            |  |

|          |         |         |         |        |                   | MCSX0_1            |             |            |  |

| 89       | 67      | B6      | 69      | B7     | 56                | P0C                | I*          | K          |  |

|          |         |         |         |        |                   | SCK4_0<br>(SCL4_0) |             |            |  |

|          |         |         |         |        |                   | TIOA6_1            |             |            |  |

|          |         |         |         |        |                   | MALE_1             |             |            |  |

| -        | -       | D4      | -       | -      | -                 | VSS                | -           |            |  |

| -        | -       | C3      | -       | C3     | -                 | VSS                | -           |            |  |

| 90       | 68      | C6      | 70      | B6     | -                 | P0D                | K           | U          |  |

|          |         |         |         |        |                   | RTS4_0             |             |            |  |

|          |         |         |         |        |                   | TIOA3_2            |             |            |  |

|          |         |         |         |        |                   | SEG04              |             |            |  |

|          |         |         |         |        |                   | MDQM0_1            |             |            |  |

| 91       | 69      | A5      | 71      | C6     | -                 | P0E                | K           | U          |  |

|          |         |         |         |        |                   | CTS4_0             |             |            |  |

|          |         |         |         |        |                   | TIOB3_2            |             |            |  |

|          |         |         |         |        |                   | SEG03              |             |            |  |

|          |         |         |         |        |                   | MDQM1_1            |             |            |  |

| -        | -       | -       | -       | A5     | -                 | VSS                | -           |            |  |

| 92       | 70      | B5      | 72      | A6     | 57                | P0F                | E           | I          |  |

|          |         |         |         |        |                   | NMIX               |             |            |  |

|          |         |         |         |        |                   | CROUT_1            |             |            |  |

|          |         |         |         |        |                   | RTCCO_0            |             |            |  |

|          |         |         |         |        |                   | SUBOUT_0           |             |            |  |

|          |         |         |         |        |                   | WKUP0              |             |            |  |

| 93       | 71      | D6      | 73      | B5     | -                 | P63                | K           | V          |  |

|          |         |         |         |        |                   | INT03_0            |             |            |  |

|          |         |         |         |        |                   | SEG02              |             |            |  |

|          |         |         |         |        |                   | MWEX_1             |             |            |  |

| 94       | 72      | C5      | 74      | C5     | 58                | P62                | K           | U          |  |

|          |         |         |         |        |                   | SCK5_0<br>(SCL5_0) |             |            |  |

|          |         |         |         |        |                   | ADTG_3             |             |            |  |

|          |         |         |         |        |                   | SEG01              |             |            |  |

|          |         |         |         |        |                   | MOEX_1             |             |            |  |

| 95       | 73      | B4      | 75      | B4     | 59                | P61                | K           | U          |  |

|          |         |         |         |        |                   | SOT5_0<br>(SDA5_0) |             |            |  |

|          |         |         |         |        |                   | TIOB2_2            |             |            |  |

|          |         |         |         |        |                   | SEG00              |             |            |  |

| 端子番号     |         |         |         |        |                   | 端子名     | 入出力<br>回路形式 | 端子状態<br>形式 |

|----------|---------|---------|---------|--------|-------------------|---------|-------------|------------|

| LQFP-100 | QFP-100 | BGA-112 | LQFP-80 | BGA-96 | LQFP-64<br>QFN-64 |         |             |            |

| 96       | 74      | C4      | 76      | C4     | 60                | P60     | I*          | T          |

|          |         |         |         |        |                   | SIN5_0  |             |            |

|          |         |         |         |        |                   | TIOA2_2 |             |            |

|          |         |         |         |        |                   | INT15_1 |             |            |

|          |         |         |         |        |                   | WKUP3   |             |            |

|          |         |         |         |        |                   | CEC1    |             |            |

|          |         |         |         |        |                   | -       |             |            |

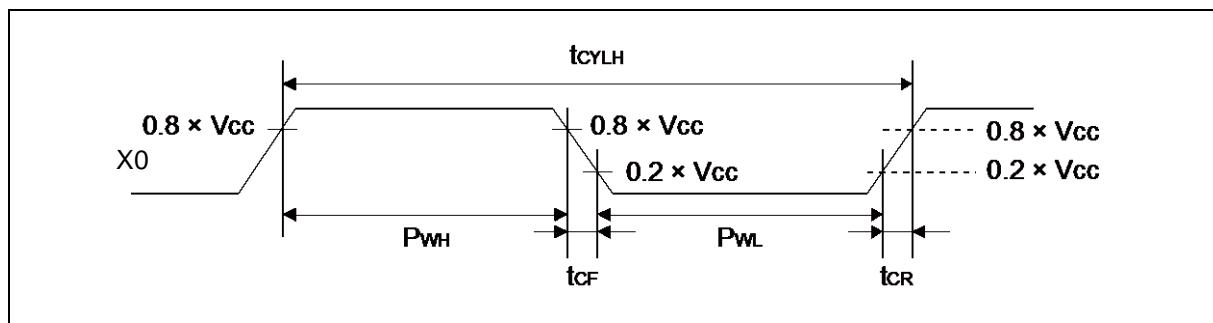

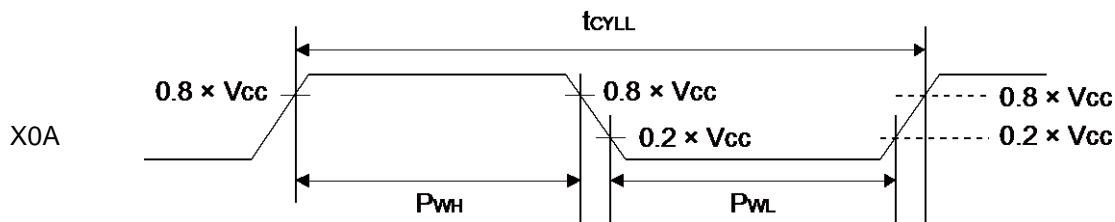

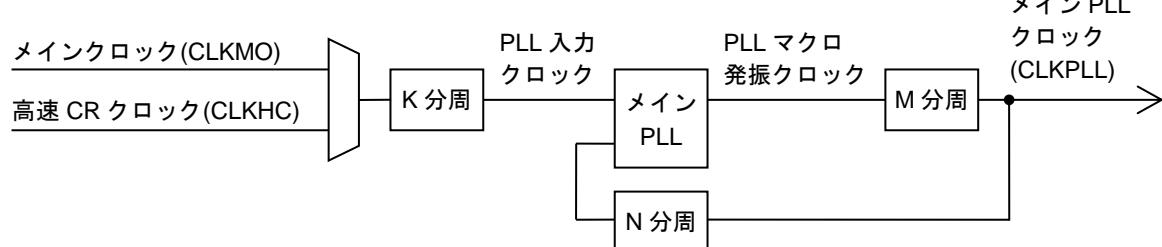

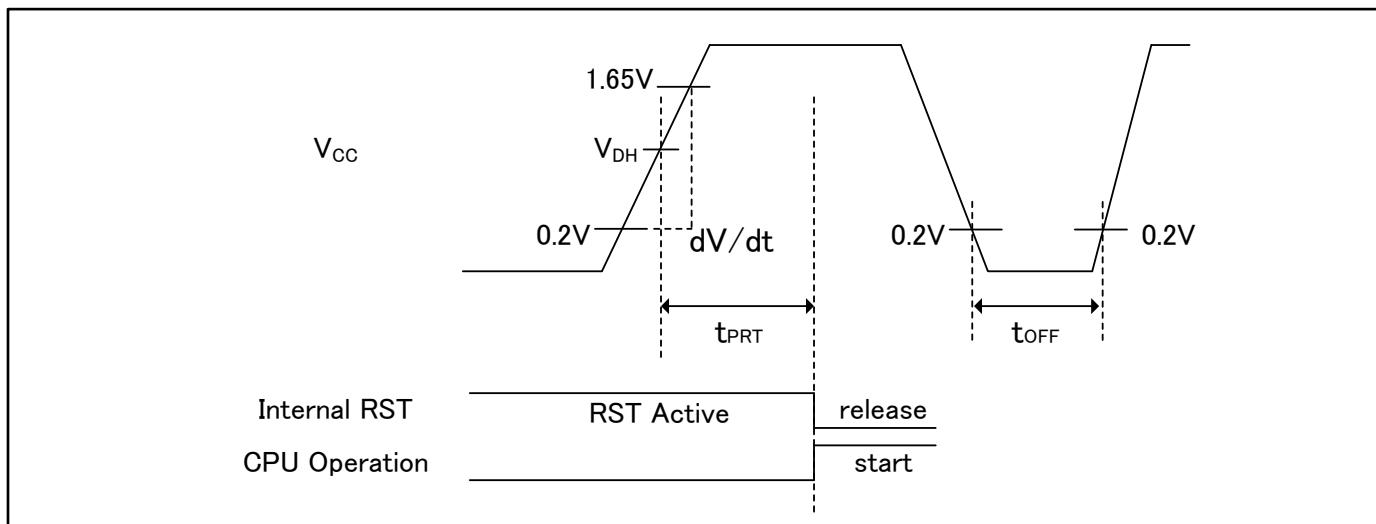

| 97       | 75      | A4      | 77      | A4     | 61                | VCC     | -           |            |