# **FORESEE®**

# 2Gbit SPI NAND Flash F35SQB002G

**Datasheet**

LM-00168

**Rev 0.5**

LONGSYS ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind. All brand names, trademarks and registered trademarks belong to their respective owners.

This document and all information discussed herein remain the sole and exclusive property of Longsys Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or other-wise.

For updates or additional information about Longsys products, contact your nearest Longsys office.

© 2022 Shenzhen Longsys Electronics Co., Ltd. All rights reserved.

# **Revision History**

| Rev. | Date       | Changes                                                                                                |  |  |  |  |

|------|------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0.1  | 2024.01.31 | Preliminary Release                                                                                    |  |  |  |  |

| 0.2  | 2024.05.10 | Jpdate device ID value                                                                                 |  |  |  |  |

| 0.3  | 2024.05.22 | Update t <sub>RD_ECC</sub> /t <sub>PROG</sub> /t <sub>PROG_ECC</sub> /t <sub>ERS</sub> parameter value |  |  |  |  |

|      |            | 1. Remove the blank page 7                                                                             |  |  |  |  |

|      | 2024.09.04 | 2. Update parameter page data definition in Chapter 10.8.3                                             |  |  |  |  |

| 0.4  |            | 3. Fix typo error in Figure 26 of Chapter 11.2                                                         |  |  |  |  |

| 0.4  |            | 4. Update t <sub>PUW</sub> value in Chapter 12.3                                                       |  |  |  |  |

|      |            | 5. Update pin capacitance in Chapter 12.4                                                              |  |  |  |  |

|      |            | 6. Update tprog/tprog_ecc maximum value in Chapter 12.8                                                |  |  |  |  |

|      |            | 1. Fix typo error in Chapter 2                                                                         |  |  |  |  |

| 0.5  | 2025.01.07 | 2. Fix typo error in Figure 4 of Chapter 7                                                             |  |  |  |  |

|      |            | 3. Update tprog/tprog_ecc maximum value in Chapter 12.8                                                |  |  |  |  |

# **Content**

| R  | evision             | History                                  | 2  |  |  |  |  |  |  |

|----|---------------------|------------------------------------------|----|--|--|--|--|--|--|

| С  | ontent              |                                          | 3  |  |  |  |  |  |  |

| 1  | Gene                | eral Description                         | 6  |  |  |  |  |  |  |

|    |                     | Features                                 |    |  |  |  |  |  |  |

| 2  |                     |                                          |    |  |  |  |  |  |  |

| 3  | Prod                | uct List                                 | 7  |  |  |  |  |  |  |

| 4  | Pack                | age Types and Pin Configurations         | 8  |  |  |  |  |  |  |

| 5  |                     | Descriptions                             |    |  |  |  |  |  |  |

|    |                     | •                                        |    |  |  |  |  |  |  |

| 6  |                     | k Diagram                                |    |  |  |  |  |  |  |

| 7  | Array               | / Organization and Mapping               | 11 |  |  |  |  |  |  |

| 8  | Devid               | ce Operation                             | 13 |  |  |  |  |  |  |

|    |                     | General                                  |    |  |  |  |  |  |  |

|    |                     | SPI Modes                                |    |  |  |  |  |  |  |

|    |                     | Hold Function                            |    |  |  |  |  |  |  |

|    |                     | Write Protection                         |    |  |  |  |  |  |  |

| 9  | Statu               | ıs Registers                             | 16 |  |  |  |  |  |  |

| 9  |                     |                                          |    |  |  |  |  |  |  |

|    |                     | Protection Register                      |    |  |  |  |  |  |  |

|    | 9.1.1               | Block Protect Bits (BP3-0, TB)           |    |  |  |  |  |  |  |

|    | 9.1.2               | Status Register Protect Bits (BPRWD, SP) |    |  |  |  |  |  |  |

|    | 9.1.3               | Status Register Memory Protection        |    |  |  |  |  |  |  |

|    |                     | Configuration Register                   |    |  |  |  |  |  |  |

|    | 9.2.1               | One Time Program Lock Bit (OTP-L)        |    |  |  |  |  |  |  |

|    | 9.2.2               | Enter OTP Access Mode Bit (OTP-E)        |    |  |  |  |  |  |  |

|    | 9.2.3               | ECC Enable Bit (ECC-E)                   |    |  |  |  |  |  |  |

|    | 9.2.4               | Output Driver Strength (DRV1-0)          |    |  |  |  |  |  |  |

|    | 9.2.5               | Quad Enable Bit (QE)                     |    |  |  |  |  |  |  |

|    | 9.2.6<br><b>9.3</b> | Status Register                          |    |  |  |  |  |  |  |

|    | 9.3.1               | ECC Status Bit (ECCS2-0)                 |    |  |  |  |  |  |  |

|    | 9.3.2               | Program/Erase Failure (P-FAIL, E-FAIL)   |    |  |  |  |  |  |  |

|    | 9.3.3               | Write Enable Latch (WEL)                 |    |  |  |  |  |  |  |

|    | 9.3.4               | Operation in Progress (OIP)              |    |  |  |  |  |  |  |

|    |                     | Sector ECC Status Register               |    |  |  |  |  |  |  |

|    | 9.4.1               | Sector Information                       |    |  |  |  |  |  |  |

|    | 9.4.2               | Sector ECC Status                        |    |  |  |  |  |  |  |

|    | ) Comi              |                                          | 23 |  |  |  |  |  |  |

| 11 | i Lanni             | manos                                    | 73 |  |  |  |  |  |  |

| 1  | 0.1                    | Comma     | and Set2                                                      | 23         |

|----|------------------------|-----------|---------------------------------------------------------------|------------|

| 1  | 0.2                    | Soft Re   | eset (FFh)                                                    | 24         |

| 1  | 0.3                    | Read JI   | EDEC ID (9Fh)2                                                | 25         |

| 1  | 0.4                    | Feature   | e Operations2                                                 | 26         |

|    | 10.4.                  | 1 Get     | t Feature (0Fh) and Set Feature (1Fh)                         | 26         |

|    | 10.4.                  | 2 Wri     | ite Enable (WREN, 06h)                                        | 27         |

|    | 10.4.                  | 3 Wri     | ite Disable (WRDI, 04h)                                       | 27         |

| 1  | 0.5                    | Read O    | Operations2                                                   | 28         |

|    | 10.5.                  | 1 Page    | ge Read (13h)                                                 | 28         |

|    | 10.5.                  | 2 Rea     | ad From Cache (03h or 0Bh)                                    | 29         |

|    | 10.5.                  | 3 Rea     | ad From Cache x 2 (3Bh)                                       | 29         |

|    | 10.5.                  | 4 Rea     | ad From Cache x 4 (6Bh)                                       | 30         |

|    | 10.5.                  | 5 DTR     | R Read (0Dh)                                                  | 30         |

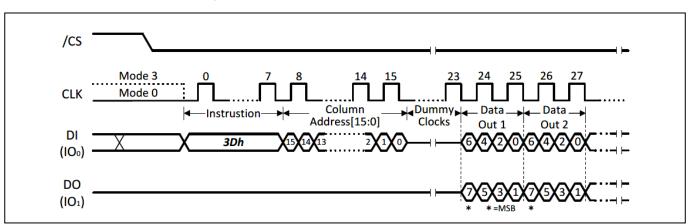

|    | 10.5.                  | 6 DTR     | R Read Dual Output (3Dh)                                      | 31         |

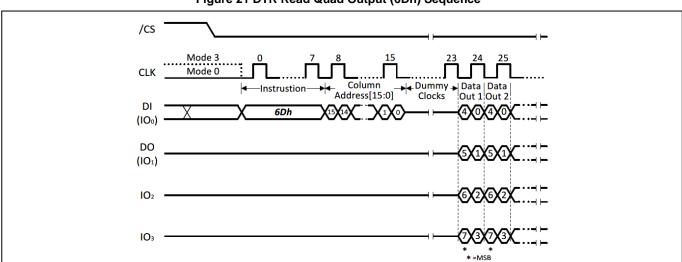

|    | 10.5.                  | 7 DTR     | R Read Quad Output (6Dh)                                      | 31         |

| 1  | 0.6                    | Prograi   | m Operations                                                  | 32         |

|    | 10.6.                  | 1 Page    | ge Program                                                    | 32         |

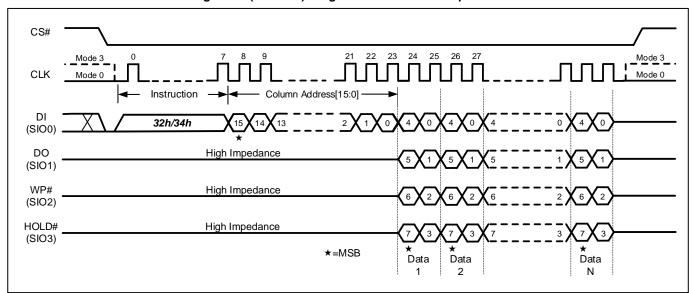

|    | 10.6.                  | 2 Prog    | gram Data Load (02h) / Random Program Data Load (84h)         | 32         |

|    | 10.6.                  | 3 Pro     | gram Data Load x 4 (32h) / Random Program Data Load x 4 (34h) | 33         |

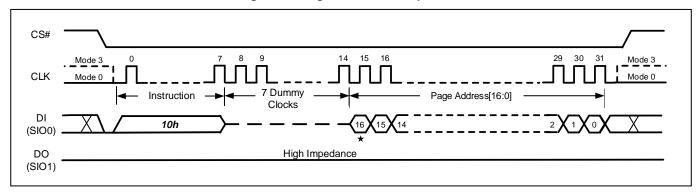

|    | 10.6.                  | 4 Pro     | gram Execute (10h)                                            | 34         |

|    | 10.6.                  | 5 Inte    | ernal Data Move                                               | 35         |

| 1  | 0.7                    | Block E   | Erase Operations                                              | 35         |

| 1  | 0.8                    | UID / Pa  | arameter / OTP Pages                                          | 36         |

|    | 10.8.                  | 1 Rea     | ad UID / Parameter / OTP Pages                                | 36         |

|    | 10.8.                  | 2 Prog    | gram OTP Pages and OTP Lock Operation                         | 36         |

|    | 10.8.                  | 3 Para    | ameter Page Data Definition                                   | 37         |

| 11 | Soft                   | ware Al   | Igorithm3                                                     | 39         |

|    |                        |           |                                                               |            |

|    | 1.1                    |           | nvalid Block(s)                                               |            |

|    | 1.2                    | •         | ving Initial Invalid Block(s)                                 |            |

|    | 1.3                    |           | n Operation4                                                  |            |

|    | 1.4                    |           | i ECC                                                         |            |

| 1  | 1.5                    | Addres    | ssing for Program Operation                                   | <i>1</i> 2 |

| 12 | Elec                   | ctrical C | Characteristics4                                              | 13         |

| 1  | 2.1                    | Absolu    | ite Maximum Ratings                                           | 13         |

|    | 2. <i>1</i><br>2.2     |           | ing Ranges                                                    |            |

|    | 2.3                    | •         | up and Power-down Timing Requirements                         |            |

|    | 2.3<br>2.4             |           | pacitance                                                     |            |

|    | 2. <del>4</del><br>2.5 | -         | ctrical Characteristics                                       |            |

|    | 2.6                    |           | asurement Conditions                                          |            |

|    |                        |           | ctrical Characteristics                                       |            |

|    | 2. <i>1</i><br>2.8     |           | Program / Erase Characteristics                               |            |

|    |                        |           |                                                               |            |

| 13 | Tim                    | ing Diag  | gram4                                                         | 18         |

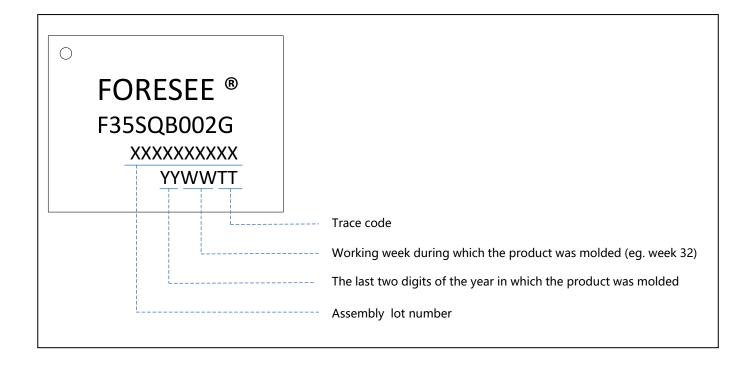

| 14 Pa | art Marking Scheme   | .50  |

|-------|----------------------|------|

| 14.1  | 8-WSON (8x6mm)       | . 50 |

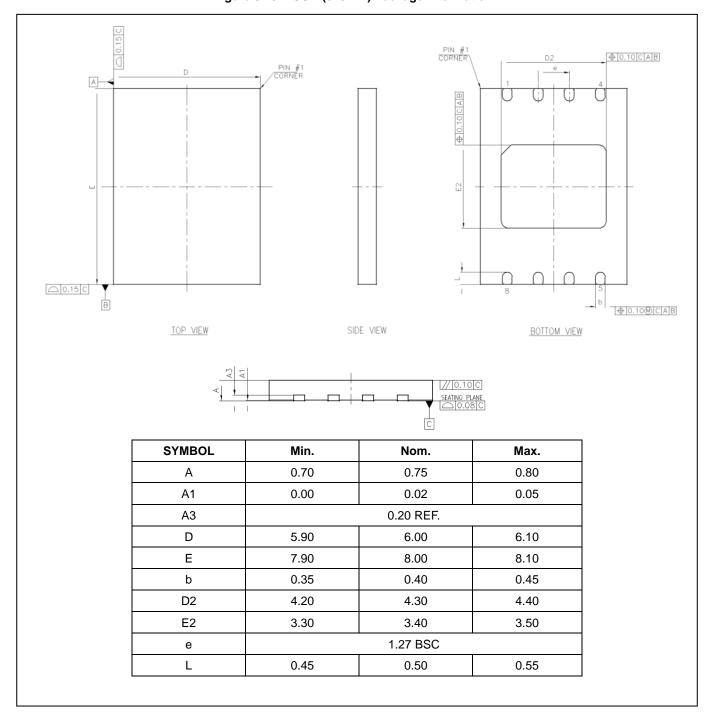

| 15 Pa | ackaging Information | .51  |

| 15.1  | 8-WSON (8x6mm)       | . 51 |

# 1 General Description

The F35SQB002G is a 2G-bit (256Mx8bit) Serial NAND Flash Memory, operates on a single 3.3V VCC. The device supports the standard Serial Peripheral Interface (SPI), Dual/Quad SPI: Serial Clock, Chip Select, Serial Data SIO0 (DI), SIO1 (DO), SIO2 (WP#) and SIO3 (HOLD#).

The F35SQB002G supports JEDEC standard manufacturer and device ID, Unique ID, one parameter page and 62 OTP pages. An internal 8-bit ECC logic is available in the chip, which is enabled by default. The internal ECC can be disabled or enabled by command.

# 2 Features

#### **Voltage Supply**

- VCC: 2.7V ~ 3.6V

#### Organization

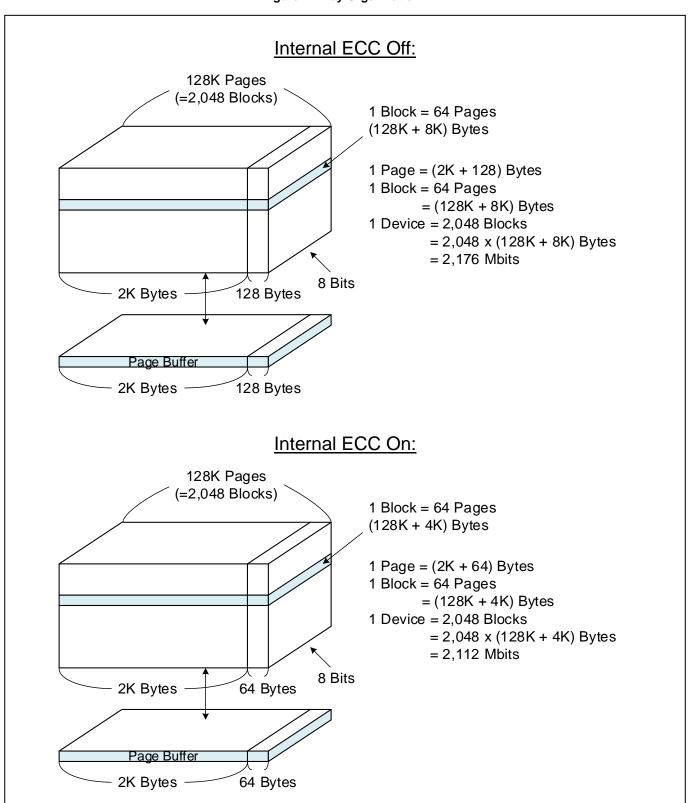

- ♦ Internal ECC Off:

- Memory Cell Array: (256M + 16M) Byte

- Page Size: (2k + 128) Byte

- Block Size: 64 pages, (128k + 8k) Byte

- ♦ Internal ECC On:

- Memory Cell Array: (256M + 8M) Byte

- Page Size: (2k + 64) Byte

- Block Size: 64 pages, (128k + 4k) Byte

#### **Serial Interface**

- Standard SPI: CLK, CS#, DI, DO, WP#, HOLD#

- Dual SPI: CLK, CS#, SIO0-SIO1, WP#, HOLD#

- Quad SPI: CLK, CS#, SIO0-SIO3

#### **High Performance**

- 166 MHz Standard/Dual/Quad SPI clocks

- 83 MHz DTR Read SPI clock

- Page Program Time: 400µs (Typ.)

- Block Erase Time: 3ms (Typ.)

#### **Low Power**

- Standby: 10µA (Typ.)

- Page Read: 10mA (Typ.)

- Program/Erase: 15mA (Typ.)

#### **Advanced Features**

- On chip 8-Bit ECC for memory array

- Software and Hardware write protect

- Unique ID

- One 2kB parameter page

- Sixty-two 2kB OTP Pages

- Promised golden block0

#### **High Reliability**

- Endurance: up to 100k cycles (1)

- Data Retention: 10 years (1)

#### **Package**

- 8-WSON (8x6mm)

#### Note:

Endurance and Data Retention specification is based on 8bit / 544Byte ECC

# 3 Product List

**Table 1 Product List**

| Part Number    | Density | I/O Type   | Voltage Range | Package        | Temp. Range   | Packing |

|----------------|---------|------------|---------------|----------------|---------------|---------|

| F35SQB002G-WWT | 2Gb     | x1, x2, x4 | 2.7V ~ 3.6V   | 8-WSON (8x6mm) | -40°C ~ 85°C  | Tray    |

| F35SQB002G-WAT | 2Gb     | x1, x2, x4 | 2.7V ~ 3.6V   | 8-WSON (8x6mm) | -40°C ~ 105°C | Tray    |

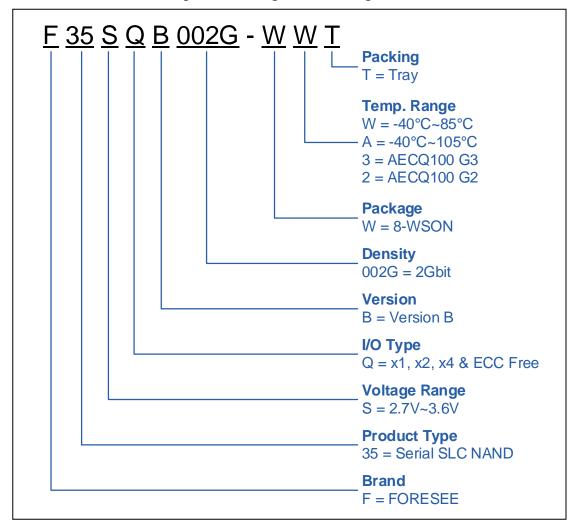

**Figure 1 Marketing Part Numbering Chart**

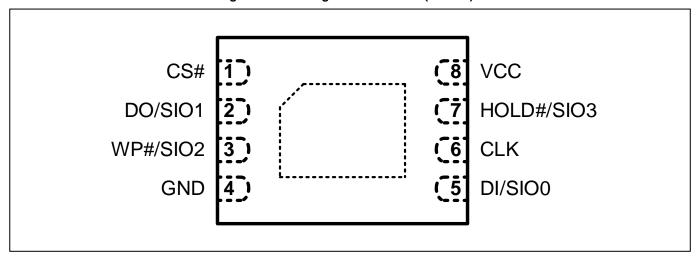

# 4 Package Types and Pin Configurations

Figure 2 Pin Configuration 8-WSON (8x6mm)

# 5 Pin Descriptions

**Table 2 Pin Description**

| Pin Name   | Pin Functions                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------|

|            | Chip Select                                                                                                         |

|            | The SPI Chip Select pin enables and disables device operation. When CS# is high the device is deselected and        |

|            | the Serial Data Output (DO or SIO0-3) pins are at high impedance. When deselected, the devices power                |

| CS#        | consumption will be at standby levels unless an internal erase, program or write status register cycle is in        |

|            | progress. When CS# is brought low the device will be selected, power consumption will increase to active levels     |

|            | and instructions can be written to and data read from the device. After power-up, CS# must transition from high     |

|            | to low before a new instruction will be accepted.                                                                   |

|            | Serial Data Input, Output and IOs                                                                                   |

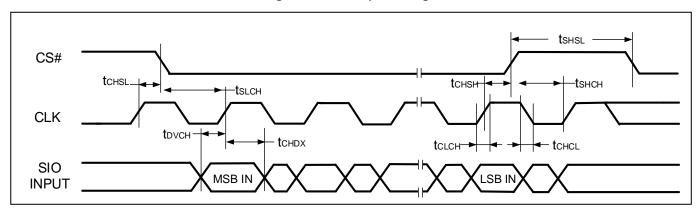

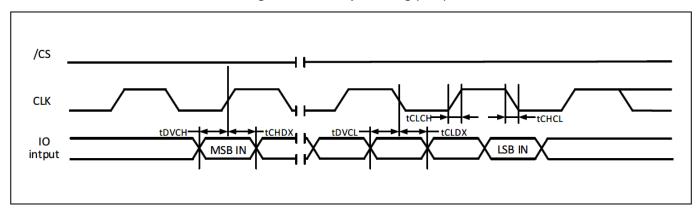

|            | The device supports standard SPI, Dual SPI and Quad SPI operation. Standard SPI instructions use the                |

| DI, DO and | unidirectional DI (input) pin to serially write instructions, addresses or data to the device on the rising edge of |

| SIO0-SIO3  | the Serial Clock (CLK) input pin. Standard SPI also uses the unidirectional DO (output) to read data or status      |

| 0.00 0.00  | from the device on the falling edge of CLK. Dual and Quad SPI instructions use the bidirectional IO pins to         |

|            | serially write instructions, addresses or data to the device on the rising edge of CLK and read data or status      |

|            | from the device on the falling edge of CLK.                                                                         |

|            | Write Protect                                                                                                       |

| WP#        | The WP# pin can be used to prevent the Status Register from being written. Used in conjunction with the Status      |

| **** //    | Register's Block Protect bits (BP3-0, TB) and Status Register Protect bits (BPRWD, SP), a portion as small as       |

|            | 256k-Byte (1 block) or up to the entire memory array can be hardware protected.                                     |

|            | Hold                                                                                                                |

|            | During Standard and Dual SPI operations, the HOLD# pin allows the device to be paused while it is actively          |

|            | selected. When HOLD# is brought low, while CS# is low, the DO pin will be at high impedance and signals on          |

| HOLD#      | the DI and CLK pins will be ignored (don't care). When HOLD# is brought high, device operation can resume.          |

|            | The HOLD function can be useful when multiple devices are sharing the same SPI signals. The HOLD# pin is            |

|            | active low.                                                                                                         |

|            | When a Quad SPI Read/Program Data Load command is issued, HOLD# pin will become a data I/O pin for the              |

|            | Quad operations and no HOLD function is available until the current Quad operation finishes.                        |

| CLK        | Serial Clock                                                                                                        |

|            | The SPI Serial Clock Input (CLK) pin provides the timing for serial input and output operations.                    |

| GND        | Ground                                                                                                              |

| VCC        | vcc                                                                                                                 |

|            | Power Supply                                                                                                        |

| NC         | No Connection                                                                                                       |

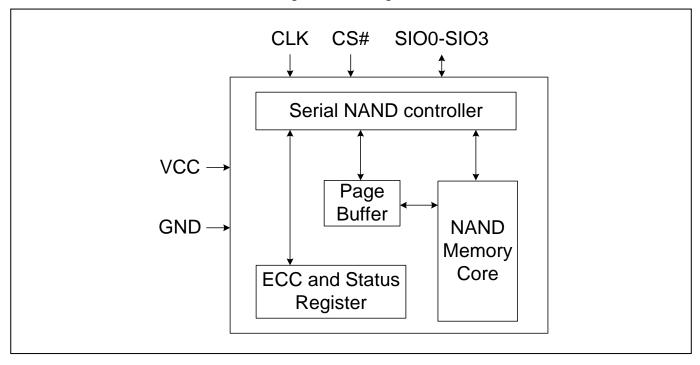

# 6 Block Diagram

Figure 3 Block Diagram

# 7 Array Organization and Mapping

**Figure 4 Array Organization**

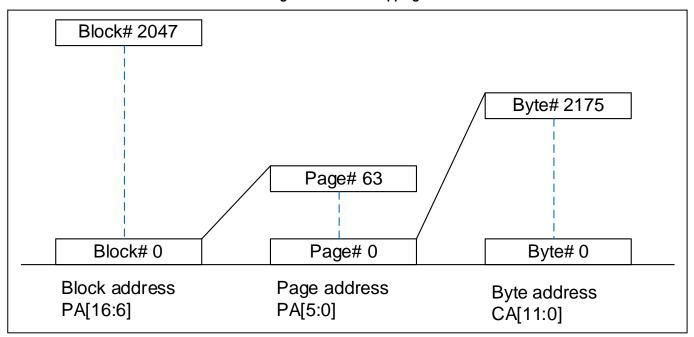

#### Figure 5 Address Mapping

#### Note:

- 1. The 12-bit byte address is capable of addressing from 0 to 4095 bytes. However, only bytes 0 through 2175 are valid, the rests are "out of bounds" and cannot be addressed.

- 2. When Internal ECC is disabled, user can read and program the entire 128 bytes spare area.

- 3. When Internal ECC is enabled, user can read the entire 128 bytes spare area, but can only program the first 64 bytes of the entire 128 bytes spare area.

# 8 Device Operation

#### 8.1 General

- Before a command is issued, status register should be checked via get feature operations to ensure device is ready for the intended operation.

- 2. When incorrect command is inputted to this device, this device becomes standby mode and keeps the standby mode until next CS# falling edge. In standby mode, SIO pin of this device should be High-Z.

- 3. When correct command is inputted to this device, this device becomes active mode and keeps the active mode until next CS# rising edge.

#### 8.2 SPI Modes

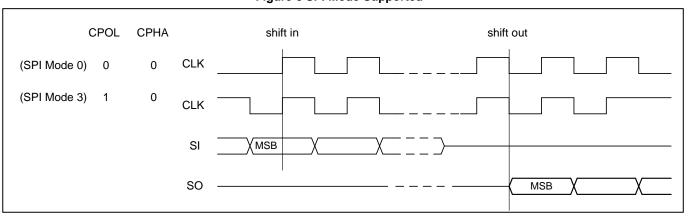

SPI NAND supports two SPI modes:

- CPOL = 0, CPHA = 0 (Mode 0)

- CPOL = 1, CPHA = 1 (Mode 3)

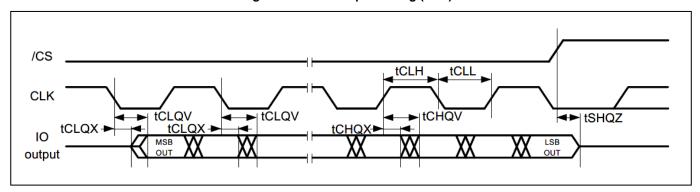

Input data is latched on the rising edge of CLK and data shifts out on the falling edge of CLK for both modes. All timing diagrams shown in this data sheet are mode 0. The difference of Mode 0 and Mode 3 is shown as **Figure 6**.

Figure 6 SPI Mode Supported

#### **Standard SPI**

SPI NAND Flash features a standard serial peripheral interface on 4 signals bus: Serial Clock (CLK), Chip Select (CS#), Serial Data Input (DI) and Serial Data Output (DO).

#### **Dual SPI**

SPI NAND Flash supports Dual SPI operation when using the x2 and dual IO commands. These commands allow data to be transferred to or from the device at two times the rate of the standard SPI. When using the Dual SPI command the DI and DO pins become bidirectional I/O pins: SIO0 and SIO1.

Everything for Memory 13 / 51 Longsys Copyright

#### **Quad SPI**

SPI NAND Flash supports Quad SPI operation when using the x4 and Quad IO commands. These commands allow data to be transferred to or from the device at four times the rate of the standard SPI. When using the Quad SPI command the DI and DO pins become bidirectional I/O pins: SIO0 and SIO1, and WP# and HOLD# pins become SIO2 and SIO3.

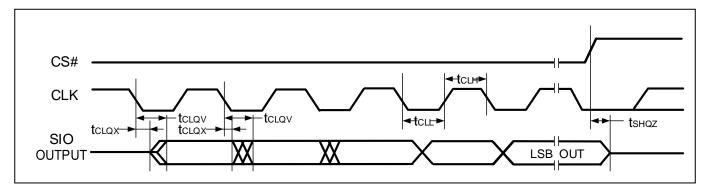

#### **DTR Read**

To effectively improve the read operation throughput without increasing the serial clock frequency, the device introduces DTR (Double Transfer Rate) Read commands that support Standard/Dual/Quad SPI modes. The byte-long command code is latched into the device on the rising edge of the serial clock similar to all other SPI commands. Once a DTR command code is accepted by the device, the address input and data output will be latched on both rising and falling edges of the serial clock.

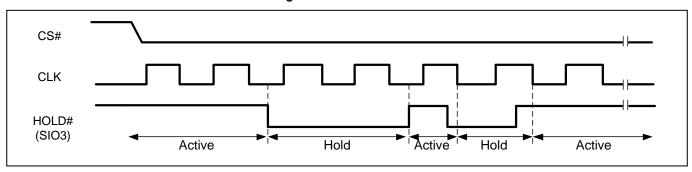

#### 8.3 Hold Function

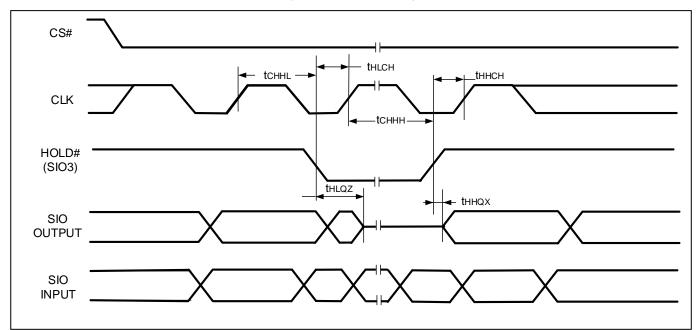

For Standard SPI and Dual SPI operations, the HOLD# signal allows the device operation to be paused while it is actively selected (when CS# is low). The Hold function may be useful in cases where the SPI data and clock signals are shared with other devices. For example, consider if the page buffer was only partially written when a priority interrupt requires use of the SPI bus. In this case the Hold function can save the state of the instruction and the data in the buffer so programming can resume where it left off once the bus is available again. The Hold function is only available for standard SPI and Dual SPI operation, not during Quad SPI or DTR operation. When a Quad SPI command is issued, HOLD# pin will act as a dedicated IO pin (SIO3).

To initiate a HOLD condition, the device must be selected with CS# low. A HOLD condition will activate on the falling edge of the HOLD# signal if the CLK signal is already low. If the CLK is not already low the HOLD condition will activate after the next falling edge of CLK. The HOLD condition will terminate on the rising edge of the HOLD# signal if the CLK signal is already low. If the CLK is not already low the HOLD condition will terminate after the next falling edge of CLK. During a HOLD condition, the Serial Data Output (DO) is high impedance, and Serial Data Input (DI) and serial Clock (CLK) are ignored. The Chip Select (CS#) signal should be kept active (low) for the full duration of the HOLD operation to avoid resetting the internal logic state of the device. See **Figure 7** for more details.

**Figure 7 Hold Condition**

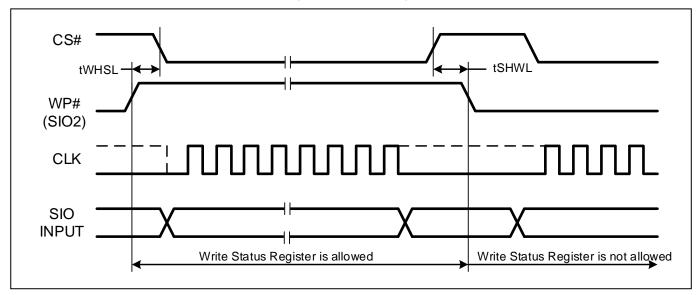

# 8.4 Write Protection

The device provides several means to protect the data from inadvertent writes.

- Device resets when VCC is below threshold

- · Write enable/disable instructions and automatic write disable after erase or program

- Software and Hardware (WP# pin) write protection using Protection Register

- Lock Down write protection for Protection Register until the next power-up

- One Time Program (OTP) write protection for memory array using Protection Register

After power-up the device is automatically placed in a write-disabled state with the Status Register Write Enable Latch (WEL) set to a 0. A Write Enable instruction must be issued before a Program Execute or Block Erase instruction will be accepted. After completing a program or erase instruction the Write Enable Latch (WEL) is automatically cleared to a write-disabled state of 0.

Software controlled write protection is facilitated using the Write Status Register instruction and setting the Status Register Protect (BPRWD, SP) and Block Protect (TB, BP3-0) bits. These settings allow a portion or the entire memory array to be configured as read only. Used in conjunction with the WP# pin, changes to the Status Register can be enabled or disabled under hardware control. See **Protection Register** for further information.

# 9 Status Registers

For Protection Register, Configuration Register and Status Register, each register is accessed by Get Feature (0Fh) and Set Feature (1Fh) commands combined with 1-Byte Register Address respectively. For Sector ECC Status Registers, each one can only be accessed by Get Feature (0Fh) command combined with 1-Byte Register Address.

**Data Bits Address** Register Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Protection A0h **BPRWD** BP3 BP2 BP1 BP0 TB R SP B0h OTP-L OTP-E R ECC-E R DRV0 Configuration DRV1 QΕ C0h ECCS2 ECCS1 ECCS0 P-FAIL E-FAIL WEL OIP Status R Configuration D0h R R R R R R R ECC-M Sector<sub>0</sub> ECC 0 0 0 S0ES3 S0ES2 S0ES1 10h 0 S0ES0 Status Sector1 ECC 0 S1ES1 20h 0 0 1 S1ES3 S1ES2 S1ES0 Status Sector2 ECC 1 0 30h 0 0 S2ES3 S2ES2 S2ES1 S2ES0 Status Sector3 ECC S3ES3 S3ES2 S3ES1 40h 0 0 1 S3ES0 Status

**Table 3 Status Registers**

Note:

The Reset command (FFh) will not clear the previous feature setting, the feature setting data bits remain until the power is being cycled or modified by the settings in the table below. After a Reset command is issued, the OIP bit can be polled to determine when the Reset operation is complete, as it will return to the default value (0) after the reset operation is finished. Issuing the Reset command has no effect on the Block Protection and Configuration registers.

Table 4 Default Values of the Status Registers after power up and Device Reset

| Register      | Address | Bits      | Shipment Default | Power Up               | After Reset Command |

|---------------|---------|-----------|------------------|------------------------|---------------------|

|               |         | BP3-0, TB | 11111            | 11111                  | No Change           |

| Protection    | A0h     | BPRWD     | 0                | 0                      | No Change           |

|               |         | SP        | 0                | 0                      | No Change           |

|               | B0h     | OTP-L     | 0                | Loked:1, else 0        | No Change           |

|               |         | OTP-E     | 0                | 0                      | No Change           |

| Configuration |         | ECC-E     | 1                | 1                      | No Change           |

|               |         | QE        | 0                | 0                      | No Change           |

|               |         | DRV1-0    | 0 0              | 0 0                    | No Change           |

| Status        | C0h     | ECCS2-0   | 000              | Status of Page0/Block0 | 000                 |

Everything for Memory 16 / 51 Longsys Copyright

<sup>(1)</sup> R: Reserved Bit and has no function. They may be read out as a "0" or "1". It is recommended to ignore the values of those bits. During a Set Feature command, the Reserved Bits can be written as "0", but there will not be any effects.

| Register            | Address | Bits    | Shipment Default | Power Up              | After Reset Command |  |

|---------------------|---------|---------|------------------|-----------------------|---------------------|--|

|                     |         | P-FAIL  | 0                | 0                     | 0                   |  |

|                     |         | E-FAIL  | 0                | 0                     | 0                   |  |

|                     |         | WEL     | 0                | 0                     | 0                   |  |

|                     |         | OIP     | 0                | 0                     | 0                   |  |

| Configuration       | D0h     | ECC-M   | 1                | 1                     | No Change           |  |

| Sector0 ECC Status  | 10h     | S0ES3-0 | 0000             | Sector0 ECC Status of | 0000                |  |

| Sectoro ECC Status  | 1011    | 30E33-0 | 0000             | Page0/Block0          | 0000                |  |

| Sector1 ECC Status  | 20h     | C4EC2 0 | 0.000            | Sector1 ECC Status of | 0.0.0               |  |

| Sector r ECC Status | 2011    | S1ES3-0 | 0000             | Page0/Block0          | 0000                |  |

| Sector2 ECC Status  | 30h     | S2ES3-0 | 0000             | Sector2 ECC Status of | 0000                |  |

| Sector2 ECC Status  | 3011    | 32E33-0 | 0000             | Page0/Block0          | 0000                |  |

| Sector3 ECC Status  | 40h     | C2FC2 0 | 0.000            | Sector3 ECC Status of | 0.0.0               |  |

| Sectors ECC Status  | 40h     | S3ES3-0 | 0000             | Page0/Block0          | 0 0 0 0             |  |

# 9.1 Protection Register

# 9.1.1 Block Protect Bits (BP3-0, TB)

The Block Protect bits (BP3-0, TB) are volatile read/write bits that provide Write Protection control and status. Block Protect bits can be set using the Set Feature Instruction. All, none or a portion of the memory array can be protected from Program and Erase instructions (See **Table 6**). The default values for the Block Protection bits are 1 after power up to protect the entire array.

# 9.1.2 Status Register Protect Bits (BPRWD, SP)

The Status Register Protect bits (BPRWD, SP) are volatile read/write bits which control the method of write protection: software protection, hardware protection, power supply lock-down.

| BPRWD | SP | QE | WP# | Descriptions                                                         |

|-------|----|----|-----|----------------------------------------------------------------------|

| Х     | 0  | 1  | Х   | Protection Register can be changed                                   |

| ^     | U  | I  | ^   | No WP# functionality, WP# pin will always function as SIO2           |

| Х     | 1  | Х  | Х   | Protection Register cannot be changed during the current power cycle |

| 0     | 0  | 0  | Х   | Protection Register can be changed                                   |

| 1     | 0  | 0  | 0   | Protection Register can NOT be changed                               |

| 1     | 0  | 0  | 1   | Protection Register can be changed                                   |

**Table 5 Status Register Protection**

Note:

(1) When SP =1, a power-down, power-up cycle will change (BPRWD, SP) to (0, 0) state.

# 9.1.3 Status Register Memory Protection

**Table 6 Block Protection Bits**

| ТВ | BP3 | BP2 | BP1 | BP0 | PROTECTED<br>BLOCK(S) | PROTECTED PAGE ADDRESS PA[16:0] | PROTECTED<br>DENSITY | PROTECTED PORTION |

|----|-----|-----|-----|-----|-----------------------|---------------------------------|----------------------|-------------------|

| Х  | 0   | 0   | 0   | 0   | NONE                  | NONE                            | NONE                 | NONE              |

| 0  | 0   | 0   | 0   | 1   | 2047                  | 1FFC0h – 1FFFFh                 | 128KB                | Upper 1/2048      |

| 0  | 0   | 0   | 1   | 0   | 2046 & 2047           | 1FF80h – 1FFFFh                 | 256KB                | Upper 1/1024      |

| 0  | 0   | 0   | 1   | 1   | 2044 thru 2047        | 1FF00h – 1FFFFh                 | 512KB                | Upper 1/512       |

| 0  | 0   | 1   | 0   | 0   | 2040 thru 2047        | 1FE00h – 1FFFFh                 | 1MB                  | Upper 1/256       |

| 0  | 0   | 1   | 0   | 1   | 2032 thru 2047        | 1FC00h – 1FFFFh                 | 2MB                  | Upper 1/128       |

| 0  | 0   | 1   | 1   | 0   | 2016 thru 2047        | 1F800h – 1FFFFh                 | 4MB                  | Upper 1/64        |

| 0  | 0   | 1   | 1   | 1   | 1984 thru 2047        | 1F000h – 1FFFFh                 | 8MB                  | Upper 1/32        |

| 0  | 1   | 0   | 0   | 0   | 1920 thru 2047        | 1E000h – 1FFFFh                 | 16MB                 | Upper 1/16        |

| 0  | 1   | 0   | 0   | 1   | 1792 thru 2047        | 1C000h – 1FFFFh                 | 32MB                 | Upper 1/8         |

| 0  | 1   | 0   | 1   | 0   | 1536 thru 2047        | 18000h – 1FFFFh                 | 64MB                 | Upper 1/4         |

| 0  | 1   | 0   | 1   | 1   | 1024 thru 2047        | 10000h – 1FFFFh                 | 128MB                | Upper 1/2         |

| 1  | 0   | 0   | 0   | 1   | 0                     | 00000h – 0003Fh                 | 128KB                | Lower 1/2048      |

| 1  | 0   | 0   | 1   | 0   | 0 & 1                 | 00000h – 0007Fh                 | 256KB                | Lower 1/1024      |

| 1  | 0   | 0   | 1   | 1   | 0 thru 3              | 00000h – 000FFh                 | 512KB                | Lower 1/512       |

| 1  | 0   | 1   | 0   | 0   | 0 thru 7              | 00000h – 001FFh                 | 1MB                  | Lower 1/256       |

| 1  | 0   | 1   | 0   | 1   | 0 thru 15             | 00000h – 003FFh                 | 2MB                  | Lower 1/128       |

| 1  | 0   | 1   | 1   | 0   | 0 thru 31             | 00000h – 007FFh                 | 4MB                  | Lower 1/64        |

| 1  | 0   | 1   | 1   | 1   | 0 thru 63             | 00000h – 00FFFh                 | 8MB                  | Lower 1/32        |

| 1  | 1   | 0   | 0   | 0   | 0 thru 127            | 00000h – 01FFFh                 | 16MB                 | Lower 1/16        |

| 1  | 1   | 0   | 0   | 1   | 0 thru 255            | 00000h – 03FFFh                 | 32MB                 | Lower 1/8         |

| 1  | 1   | 0   | 1   | 0   | 0 thru 511            | 00000h – 07FFFh                 | 64MB                 | Lower 1/4         |

| 1  | 1   | 0   | 1   | 1   | 0 thru 1023           | 00000h – 0FFFFh                 | 128MB                | Lower 1/2         |

| Х  | 1   | 1   | Х   | Х   | 0 thru 2047           | 00000h – 1FFFFh                 | 256MB                | ALL               |

#### Note:

- (1) X = don't care

- (2) If any Erase or Program command specifies a memory region that contains protected data portion, this command will be ignored.

# 9.2 Configuration Register

# 9.2.1 One Time Program Lock Bit (OTP-L)

OTP-L is non-volatile.

The device provides an OTP area for the system to store critical data that cannot be changed once it's locked. The OTP area consists of 62 full pages. The default data in the OTP area are FFh. Only Program command can be issued to the OTP area to change the data from "1" to "0", and the OTP area cannot be

erased.

Once the correct data is programmed in and verified, the system developer can set OTP-L bit to 1, so that the entire OTP area will be locked to prevent further alteration to the data.

# 9.2.2 Enter OTP Access Mode Bit (OTP-E)

The OTP-E bit must be set to 1 in order to use the standard Program/Read commands to access the OTP area as well as to read the Unique ID / Parameter Page information. The default value after power up or a RESET command is 0.

# 9.2.3 ECC Enable Bit (ECC-E)

The device has a built-in ECC algorithm that can be used to preserve the data integrity. Internal ECC calculation is done during page programming, and the result is stored in the extra 128-Byte area for each page. During the data read operation, ECC engine will verify the data values according to the previously stored ECC information and to make necessary corrections if needed. The verification and correction status is indicated by the ECC Status Bits. ECC function is enabled by default when power on (ECC-E=1), and it will not be changed by the Device Reset command.

#### 9.2.4 Output Driver Strength (DRV1-0)

DRV1

DRV0

Output Driver Strength

0

0

100% (default)

0

1

75%

1

0

50%

1

1

25%

**Table 7 Output Driver Strength**

# 9.2.5 Quad Enable Bit (QE)

The Quad Enable (QE) bit is a volatile bit, while it is "0" (factory default), it performs non-Quad and WP#, HOLD# are enabled. While QE is "1", it performs Quad I/O mode and WP#, HOLD# are disabled. In another word, if the system goes into four I/O mode (QE=1), the WP# and HOLD# function will be disabled. Upon power cycle, the QE bit will go into the factory default setting "0".

# 9.2.6 ECC Mode Bit (ECC-M)

The volatile ECC-M bit is used to switch internal ECC protection modes. According to requirement, customer can select one of two ECC modes which are described as below.

When ECC-M=0, the entire sector is protected by ECC.

When ECC-M=1, the first four bytes of spare area in each sector are NOT protected by ECC while the rests are protected.

Please refer to **Sector ECC Status Register** for detailed information about ECC sector.

Everything for Memory 19 / 51 Longsys Copyright

After a power cycle, the ECC-M bit will be set to the factory default value "1". Reset command (FFh) has no effect on ECC-M bit.

# 9.3 Status Register

# 9.3.1 ECC Status Bit (ECCS2-0)

ECC function is used in NAND flash memory to correct limited memory errors during read operations. The ECC Status Bits (ECCS2, ECCS1, ECCS0) should be checked after the completion of a Read operation to verify the data integrity. The ECC Status bits values are don't care if ECC-E=0. These bits will be cleared to 0 after a RESET command.

The ECCS2-0 value reflects the ECC status of the content of the page 0 of block 0 after a power-on reset.

| ECCS2 | ECCS1 | ECCS0 | Description                                                                  |  |  |

|-------|-------|-------|------------------------------------------------------------------------------|--|--|

| 0     | 0     | 0     | No bit errors were detected during the previous read operation               |  |  |

| 0     | 0     | 1     | Bit errors (<=3) were detected in one or more sectors and were corrected     |  |  |

| 0     | 1     | 0     | Bit errors (=4) were detected in one or more sectors and were corrected      |  |  |

| 0     | 1     | 1     | Bit errors (=5) were detected in one or more sectors and were corrected      |  |  |

| 1     | 0     | 0     | Bit errors (=6) were detected in one or more sectors and were corrected      |  |  |

| 1     | 0     | 1     | Bit errors (=7) were detected in one or more sectors and were corrected      |  |  |

| 1     | 1     | 0     | Bit errors (=8) were detected in one or more sectors and were corrected      |  |  |

| 1     | 1     | 1     | Bit errors (>8) were detected in one or more sectors and cannot be corrected |  |  |

**Table 8 ECC Bits Status**

#### 9.3.2 Program/Erase Failure (P-FAIL, E-FAIL)

The Program/Erase Failure Bits are used to indicate whether the internally-controlled Program/Erase operation was executed successfully or not. P-FAIL bit will also be set when the Program command is issued to a protected block or locked OTP area, and E-FAIL bit will also be set when the Erase command is issued to a protected block. Both bits will be cleared at the beginning of the Program Execute or Block Erase instructions as well as the device Reset command.

# 9.3.3 Write Enable Latch (WEL)

Write Enable Latch (WEL) is a read only bit. The WEL bit is set to 1 after executing a Write Enable Instruction. The WEL bit is cleared to 0 when the device is write disabled. A write disable state occurs upon power-up or after any of the following instructions: Write Disable, Program Execute, Block Erase, Page Data Read, and Program Execute for OTP pages.

Everything for Memory 20 / 51 Longsys Copyright

#### 9.3.4 Operation in Progress (OIP)

OIP is a read only bit that is set to a 1 state when the device is powering up or executing a Page Read, Program Execute, Block Erase and OTP Locking. During this time the device will ignore further instructions except for the Get Feature or Soft Reset instructions. When the program, erase or page read instruction has completed, the OIP bit will be cleared to a 0 state indicating the device is ready for further instructions.

# 9.4 Sector ECC Status Register

A sector is composed by a 512 Byte main area and a 32 Byte spare area, so a page has four sectors. The Sector ECC Status Register indicates the number of errors in each sector as identified from an ECC check during a read operation.

Main Area (2KB) Spare Area (128B) **User Data** User Meta Data (I + II) **ECC Parity Data** Spare 3 Spare 0 Spare 3 Main 2 Main 0 Spare ' Spare 2 Spare ( Spare ' Spare 2 Main ' Main ( 4B+12B B+12B 512B 512B 16B 16B

**Table 9 2KByte Page Assignment**

| Table 10 | ∆rea <i>L</i> | 22Addraee | and FCC | Protection |

|----------|---------------|-----------|---------|------------|

| Posts Address Barres | A       | ECC Protection |           | Description         |  |

|----------------------|---------|----------------|-----------|---------------------|--|

| Byte Address Range   | Area    | ECC-M = 0      | ECC-M = 1 | Description         |  |

| 0000h ~ 01FFh        | Main 0  | Yes            | Yes       | User Data 0         |  |

| 0200h ~ 03FFh        | Main 1  | Yes            | Yes       | User Data 1         |  |

| 0400h ~ 05FFh        | Main 2  | Yes            | Yes       | User Data 2         |  |

| 0600h ~ 07FFh        | Main 3  | Yes            | Yes       | User Data 3         |  |

| 800h ~ 803h          | Spare 0 | Yes            | No        | User Meta 0 Data I  |  |

| 804h ~ 80Fh          | Spare 0 | Yes            | Yes       | User Meta 0 Data II |  |

| 810h ~ 813h          | Spare 1 | Yes            | No        | User Meta 1 Data I  |  |

| 814h ~ 81Fh          | Spare 1 | Yes            | Yes       | User Meta 1 Data II |  |

| 820h ~ 823h          | Spare 2 | Yes            | No        | User Meta 2 Data I  |  |

| 824h ~ 82Fh          | Spare 2 | Yes            | Yes       | User Meta 2 Data II |  |

| 830h ~ 833h          | Spare 3 | Yes            | No        | User Meta 3 Data I  |  |

| 834h ~ 83Fh          | Spare 3 | Yes            | Yes       | User Meta 3 Data II |  |

| 840h ~ 84Fh          | Spare 0 | Yes            | Yes       | ECC Parity Data 0   |  |

| 850h ~ 85Fh          | Spare 1 | Yes            | Yes       | ECC Parity Data 1   |  |

| 860h ~ 86Fh          | Spare 2 | Yes            | Yes       | ECC Parity Data 2   |  |

| 870h ~ 87Fh          | Spare 3 | Yes            | Yes       | ECC Parity Data 3   |  |

#### **Table 11 Definition of ECC Sector**

| Sector   | Main Area | Spare Aera |

|----------|-----------|------------|

| Sector 0 | Main 0    | Spare 0    |

| Sector 1 | Main 1    | Spare 1    |

| Sector 2 | Main 2    | Spare 2    |

| Sector 3 | Main 3    | Spare 3    |

#### Table 12 Sector ECC Status Register 0-7

| Bit7               | Bit6 | Bit5 | Bit4              | Bit3 | Bit2 | Bit1 | Bit0 |

|--------------------|------|------|-------------------|------|------|------|------|

| Sector Information |      |      | Sector ECC Status |      |      |      |      |

# 9.4.1 Sector Information

#### **Table 13 Sector Information**

| Bit 7 ~ Bit 4 | Sector Information |

|---------------|--------------------|

| 0000          | Sector 0           |

| 0001          | Sector 1           |

| 0010          | Sector 2           |

| 0011          | Sector 3           |

| Others        | Reserved           |

# 9.4.2 Sector ECC Status

#### **Table 14 Sector ECC Status**

| Bit 3 ~ Bit 0 | Sector ECC Status                                                          |  |  |  |

|---------------|----------------------------------------------------------------------------|--|--|--|

| 0000          | No bit error was detected during the previous read operation               |  |  |  |

| 0001          | 1-bit error was detected in the sector and was corrected                   |  |  |  |

| 0010          | 2-bit errors were detected in the sector and were corrected                |  |  |  |

| 0011          | 3-bit errors were detected in the sector and were corrected                |  |  |  |

| 0100          | 4-bit errors were detected in the sector and were corrected                |  |  |  |

| 0101          | 5-bit errors were detected in the sector and were corrected                |  |  |  |

| 0110          | 6-bit errors were detected in the sector and were corrected                |  |  |  |

| 0111          | 7-bit errors were detected in the sector and were corrected                |  |  |  |

| 1000          | 8-bit errors were detected in the sector and were corrected                |  |  |  |

| 1001          | More than 8-bit errors were detected in the sector and cannot be corrected |  |  |  |

| Others        | Reserved                                                                   |  |  |  |

# 10 Commands

# 10.1 Command Set

**Table 15 Command Set**

| Commands                      | Byte1      | Byte2   | Byte3  | Byte4     | Byte5     | ByteN     |

|-------------------------------|------------|---------|--------|-----------|-----------|-----------|

| Soft RESET                    | FFh        |         |        |           |           |           |

| Read JEDEC ID                 | 9Fh        | Dummy   | MID    | DID       | DID       |           |

| Get Feature                   | 0Fh        | SR Addr | S7-0   | S7-0      | S7-0      | S7-0      |

| Set Feature                   | 1Fh        | SR Addr | S7-0   |           |           |           |

| Write Enable                  | 06h        |         |        |           |           |           |

| Write Disable                 | 04h        |         |        |           |           |           |

| Block Erase                   | D8h        | PA23-16 | PA15-8 | PA7-0     |           |           |

| Program Data Load             | 02h        | CA15-8  | CA7-0  | D7-D0     | Next Byte |           |

| Random Program Data Load      | 84h        | CA15-8  | CA7-0  | D7-D0     | Next Byte |           |

| Quad Program Data Load        | 32h        | CA15-8  | CA7-0  | D7-D0 / 4 | Next Byte |           |

| Random Quad Program Data Load | 34h        | CA15-8  | CA7-0  | D7-D0 / 4 | Next Byte |           |

| Program Execute               | 10h        | PA23-16 | PA15-8 | PA7-0     |           |           |

| Page Read (to cache)          | 13h        | PA23-16 | PA15-8 | PA7-0     |           |           |

| Read From Cache               | 03h or 0Bh | CA15-8  | CA7-0  | Dummy     | D7-D0     | Next Byte |

| Read From Cache x 2           | 3Bh        | CA15-8  | CA7-0  | Dummy     | D7-D0 / 2 | Next Byte |

| Read From Cache x 4           | 6Bh        | CA15-8  | CA7-0  | Dummy     | D7-D0 / 4 | Next Byte |

| DTR Read                      | 0Dh        | CA15-0  | Dummy  | D7-D0 / 2 | Next Byte |           |

| DTR Read Dual Output          | 3Dh        | CA15-0  | Dummy  | D7-D0 / 4 | Next Byte |           |

| DTR Read Quad Output          | 6Dh        | CA15-0  | Dummy  | D7-D0 / 8 | Next Byte |           |

#### Note:

- (1) Output designates data output from the device.

- (2) Column Address (CA) only requires CA [11:0], CA [15:12] are considered as dummy bits.

- (3) Page Address (PA) only requires PA [16:0], PA [23:17] are considered as dummy bits. PA [16:6] is the address for 128kB blocks (total 2,048 blocks), PA [5:0] is the address for 2kB pages (total 64 pages for each block).

- (4) Dual SPI Data Output (D7-D0 / 2) format:

SIO0 = D6, D4, D2, D0...

SIO1 = D7, D5, D3, D1...

(5) Quad SPI Data Input / Output (D7-D0 / 4) format:

SIO0 = D4, D0 .....

SIO1 = D5, D1 .....

SIO2 = D6, D2 .....

SIO3 = D7, D3 .....

(6) All Quad Program/Read commands are disabled when QE bit is set to 0 in the Configuration Register.

(7) For DTR read, command input is in STR mode, while address input and data output are in DTR mode with 8 dummy clocks.

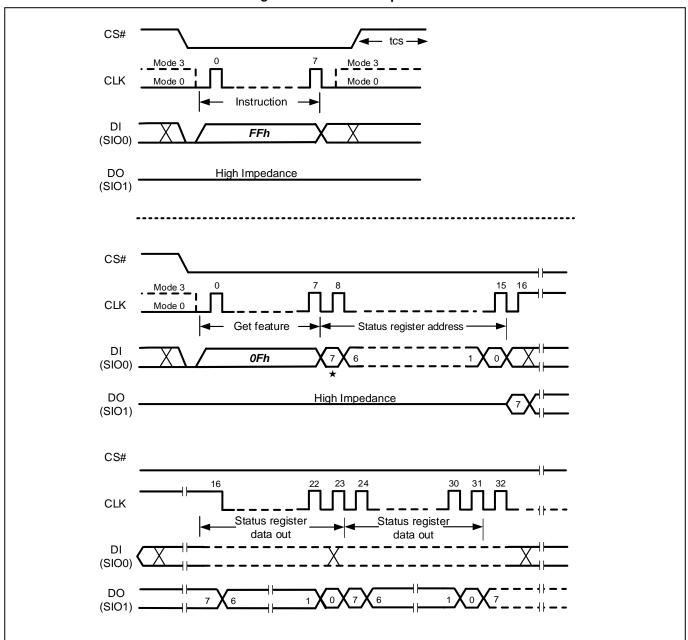

# 10.2 Soft Reset (FFh)

Once the Reset command is accepted by the device, the device will take approximately  $t_{RST}$  to reset, depending on the current operation the device is performing,  $t_{RST}$  can be 5us~200us. During this period, no command will be accepted.

Data corruption may happen if there is an on-going internal Erase or Program operation when Reset command is accepted by the device. It is recommended to check the OIP bit in Status Register before issuing the Reset command.

# Figure 8 Soft Reset Sequence

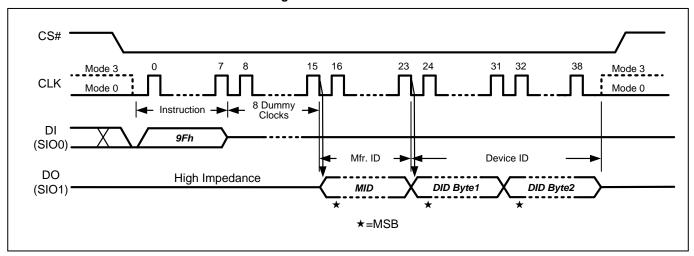

# 10.3 Read JEDEC ID (9Fh)

The Read JEDEC ID instruction is compatible with the JEDEC standard for SPI compatible serial memories that was adopted in 2003.

**Table 16 JEDEC ID**

| II | Value  |     |

|----------------------------------------|--------|-----|

| Manufa                                 | CDh    |     |

| Davies ID                              | Byte 1 | 52h |

| Device ID                              | Byte 2 | 52h |

#### Figure 9 Read JEDEC ID

# 10.4 Feature Operations

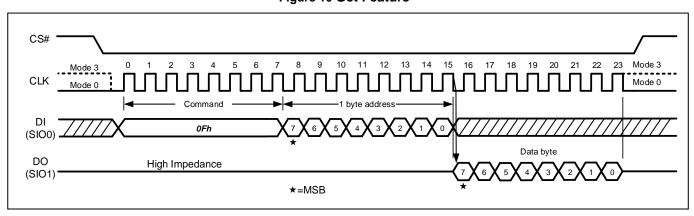

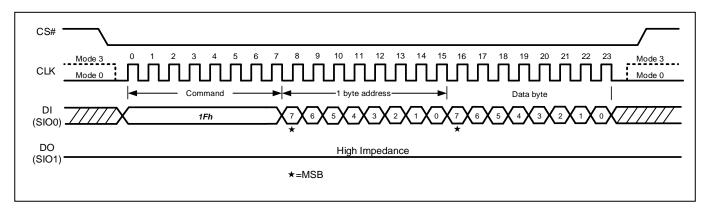

# 10.4.1 Get Feature (0Fh) and Set Feature (1Fh)

The Get Feature (0Fh) and Set Feature (1Fh) commands are used to monitor the device status and alter the device behavior. These commands use a 1-byte feature address to determine which feature is to be read or modified. Features such as OTP and block locking can be enabled or disabled by setting specific feature bits. The status register is mostly read, except WEL, which is a writable bit with the Write Enable (06h) and Write Disable (04h) command. When a feature is set, it remains active until the device is power cycled or the feature is written to. Unless otherwise specified, once the device is set, it remains set, even if a RESET (FFH) command is issued. Refer to **Status Registers** for detail information.

Figure 10 Get Feature

#### Figure 11 Set Feature

# 10.4.2 Write Enable (WREN, 06h)

The Write Enable (WREN, 06h) command is for setting Write Enable Latch (WEL) bit. The WEL bit must be set prior to every Page Program, Block Erase and OTP.

CS#

CLK Mode 3 0 1 2 3 4 5 6 7 Mode 3

CLK Mode 0 Command Mode 0

Command Mode 0

DI (SIO0)

DO High Impedance

Figure 12 Write Enable Sequence

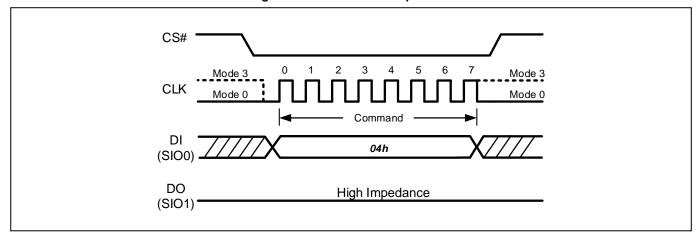

# 10.4.3 Write Disable (WRDI, 04h)

The Write Disable (WRDI, 04h) instruction is to reset Write Enable Latch (WEL) bit. Note that the WEL bit is automatically reset after Power-up and upon completion of the Page Program, Block Erase, and Reset commands.

#### Figure 13 Write Disable Sequence

# 10.5 Read Operations

The device supports Power-on Read function, after power up, the device will automatically load the data of the 1st page of 1st block from array to cache. The host micro-controller may directly read the 1st page of 1st block data from the cache buffer.

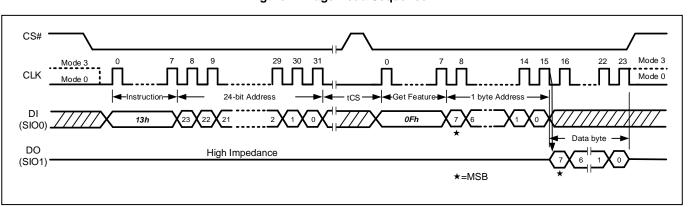

# 10.5.1 Page Read (13h)

The page read operation transfers data from array to cache by issuing the Page Read (13h) command followed by the 24-bit address (including the dummy/block/page address).

The device will have a period of time (**tRD** or **tRD**\_ECC) being busy after the CS# goes high. The Get Feature command may be used to poll the operation status.

After read operation is completed, the Read from Cache (03h or 0Bh), Read from cache (x2) (3Bh), Read from cache (x4) (6Bh) may be issued to fetch the data.

Figure 14 Page Read Sequence

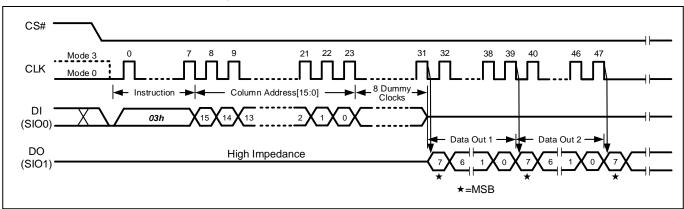

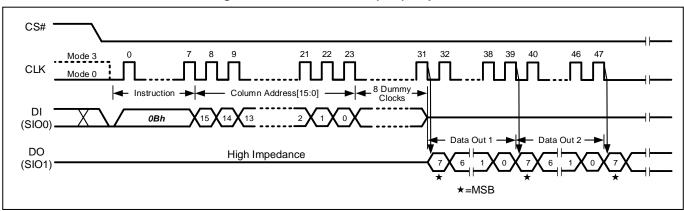

# 10.5.2 Read From Cache (03h or 0Bh)

The Read From Cache command allows one or more data bytes to be sequentially read from the Data Buffer after executing the Read Page command.

Figure 15 Read From Cache (03h) Sequence

# 10.5.3 Read From Cache x 2 (3Bh)

The Read From Cache x 2 command is similar to the Read From Cache command except that data is output on two pins: SIO0 and SIO1. This allows data to be transferred at twice the rate of standard SPI devices.

#### Figure 17 Read From Cache x2 (3Bh) Sequence

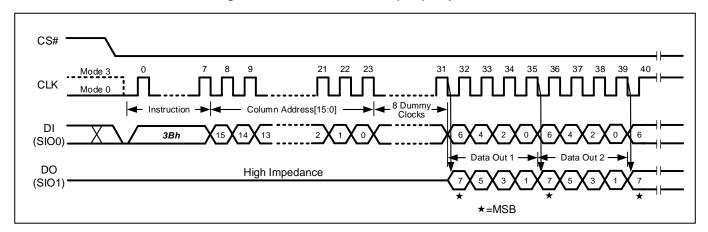

# **10.5.4** Read From Cache x 4 (6Bh)

The Read From Cache x 4 command is similar to the Read From Cache x 2 command except that data is output on four pins: SIO0, SIO1, SIO2 and SIO3. This allows data to be transferred at four times the rate of standard SPI devices.

When QE bit in the Status Register is set to a 0, this command is disabled.

Figure 18 Read From Cache x4 (6Bh) Sequence

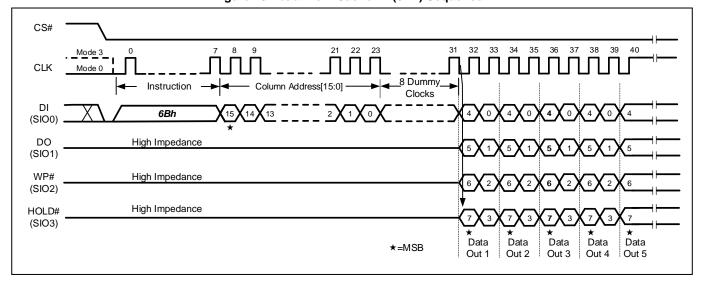

# 10.5.5 DTR Read (0Dh)

The DTR Read command allows one or more data bytes to be sequentially read from the Data Buffer after executing the Read Page command. Address shift in and data shift out are valid at the both edge of CLK, which differs to the Read From Cache command.

#### Figure 19 DTR Read (0Dh) Sequence

# 10.5.6 DTR Read Dual Output (3Dh)

The DTR Read Dual Output command is similar to the DTR Read command except that data is output on two pins: SIO0 and SIO1.

Figure 20 DTR Read Dual Output (3Dh) Sequence

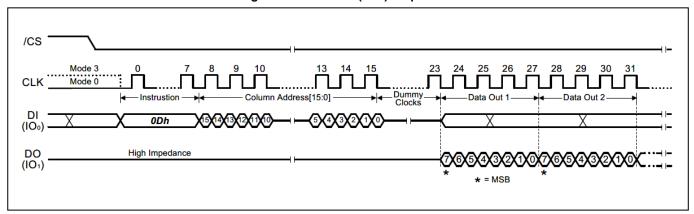

# 10.5.7 DTR Read Quad Output (6Dh)

The DTR Read Quad Output command is similar to the DTR Read Dual Output command except that data is output on four pins: SIO0, SIO1, SIO2 and SIO3.

When QE bit in the Status Register is set to a 0, this command is disabled.

Figure 21 DTR Read Quad Output (6Dh) Sequence

# 10.6 Program Operations

#### 10.6.1 Page Program

The Page Program operation sequence programs 1 byte to whole page of data within a page. The page program sequence is as follows:

- 1. Issue data load command (02h / 32h / 84h / 34h)

- 2. Issue Write Enable command (06h)

- 3. Issue Program Execute command (10h)

- 4. Issue Get Feature command (0Fh) to read the status

# 10.6.2 Program Data Load (02h) / Random Program Data Load (84h)

The Program Data Load or Random Program Data Load command is used to load the program data into the data buffer. The command is initiated by driving the CS# pin low then shifting the command code "02h" or "84h" followed by a 16-bit column address (only CA[11:0] is effective) and at least one byte of data into the DI pin. The CS# pin must be held low for the entire length of the instruction while data is being sent to the device. If the number of data bytes sent to the device exceeds the number of data bytes in the Data Buffer, the extra data will be ignored by the device.

Program Load Data command will reset the unused data bytes in the Data Buffer to FFh value, while Random Program Load Data command will only update the data bytes that are specified by the command input sequence, the rest of the Data Buffer will remain unchanged.

# CS# Mode 3 CLK Mode 0 Instruction Column Address[15:0] DI 02h/84h DO High Impedance (SIO1) CS# Mode 3 CLK Data-N (SIO0) DO High Impedance (SIO1)

Figure 22 (Random) Program Data Load Sequence

# 10.6.3 Program Data Load x 4 (32h) / Random Program Data Load x 4 (34h)

The Program Data Load x 4 and Random Program Data Load x 4 commands are similar to the Program Load Data and Random Program Load Data, the only difference is that "x4" commands will input the data bytes from all four IO pins instead of the single DI pin. This method will significantly shorten the data input time when a large amount of data needs to be loaded into the Data Buffer.

Program Data Load x 4 command will reset the unused data bytes in the Data Buffer to FFh value, while Random Program Data Load x 4 instruction will only update the data bytes that are specified by the command input sequence, the rest of the Data Buffer will remain unchanged.

When QE bit in the Status Register is set to 0, all Quad SPI instructions are disabled.

Figure 23 (Random) Program Data Load x4 Sequence

# 10.6.4 Program Execute (10h)

The Program Execute command will program the Data Buffer content into the physical memory page that is specified in the command. Prior to performing the Program Execute operation, a Write Enable (06h) command must be issued to set the WEL bit.

The Program Execute command is initiated by driving the CS# pin low then shifting the instruction code "10h" followed by 7-bit dummy clocks and the 17-bit Page Address into the DI pin.

After CS# is driven high to complete the instruction cycle, the self-timed Program Execute instruction will commence for time duration of **tPROG** or **tPROG**\_ECC. While the Program Execute cycle is in progress, the Get Feature command (0Fh) may be used for checking the status of the OIP bit. The OIP bit is a 1 during the Program Execute cycle and becomes a 0 when the cycle is finished and the device is ready to accept other instructions again. After the Program Execute cycle has finished, the Write Enable Latch (WEL) bit in the Status Register is cleared to 0. The Program Execute command will not be executed if the addressed page is protected by the Block Protect (TB, BP3, BP2, BP1, and BP0) bits. Only 1 partial page program time is allowed on every single page.

The pages within the block have to be programmed sequentially from the lower order page address to the higher order page address within the block. Programming pages out of sequence is prohibited.

#### Figure 24 Program Execute Sequence

#### 10.6.5 Internal Data Move

The Internal Data Move command sequence programs or replaces data in a page with existing data. The sequence is as follows:

- 1. Issue Page Read command (13h)

- 2. Program Load Random Data (Optional)

- 3. Issue Write Enable command (06h)

- 4. Issue Program Execute command (10h)

- 5. Issue Get Feature command (0Fh) to read the status

Prior to performing an internal data move operation, the target page content must be read out into the cache register by issuing a Page Read (13h) command. One or more Program Load Random Data (84h/34h) command can be issued, if user wants to update bytes of data in the page. After the data is loaded, the Write Enable command (06h) and the Program Execute (10h) command can be issued to start the program operation.

# 10.7 Block Erase Operations

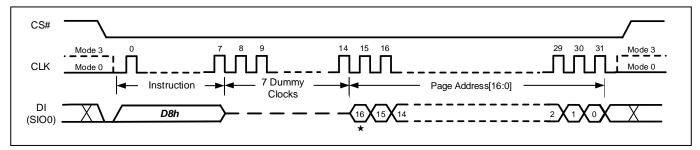

The Block Erase instruction sets all memory within a specified block to the erased state of all 1s (FFh). A Write Enable command must be executed before the device will accept the Block Erase Instruction (Status Register bit WEL must equal 1). The command is initiated by driving the CS# pin low and shifting the command code "D8h" followed by 7-bit dummy clocks and the 17-bit page address.

Figure 25 Block Erase Sequence

# 10.8 UID / Parameter / OTP Pages

In addition to the main memory array, the device has one Unique ID Page, one Parameter Page, and sixty-two OTP Pages.

**Page Address Page Name Descriptions Data Length** PA[16:0] 0\_00\_00h Unique ID Page Factory programmed, Read Only 32-Byte x 16 0\_00\_01h Parameter Page Factory programmed, Read Only 256-Byte x 3 0\_00\_02h OTP Page [0] Program Only, OTP lockable Full Page OTP Pages [1:60] Program Only, OTP lockable Full Page 0\_00\_3Fh OTP Page [61] Program Only, OTP lockable Full Page

Table 17 UID / Parameter / OTP Pages

Unique ID Page: To accommodate robust retrieval of the UID in the case of bit errors, sixteen copies (each copy has 32 bytes) of the UID and the corresponding complement are stored. On each 32-byte, the first 16-byte and following 16-byte are complementary. If the XOR of the UID and its bit-wise complement is all ones, then the UID is valid.

Parameter Page: Contains at least three identical copies of the 256-Byte Parameter Data.

To access these additional data pages, the OTP-E bit in Configuration Register must be set to "1" first. Then, Read operations can be performed on Unique ID and Parameter Pages, Read and Program operations can be performed on the OTP pages if it's not already locked. To return to the main memory array operation, OTP-E bit needs to be to set to 0.

#### 10.8.1 Read UID / Parameter / OTP Pages

The Read UID / Parameter / OTP pages sequence is as follows:

- Issue Set Feature command (1Fh) to set OTP-E=1.

- 2. Issue Page Read command (13h) with address shown in the table above.

- 3. Issue Get Feature command (0Fh) to read the status.

- 4. Issue Read from cache command (03h/0Bh/3Bh/6Bh) to read data.

#### Note:

- (1) For OTP pages, Internal ECC can be enabled for the OTP page read operations to ensure the data integrity.

- (2) When reading UID / Parameter page, Internal ECC is disabled by the chip.

# 10.8.2 Program OTP Pages and OTP Lock Operation

OTP pages provide the additional space (4K-Byte x 62) to store important data or security information that can be locked to prevent further modification in the field. These OTP pages are in an erased state set in the factory, and can only be programmed (change data from "1" to "0") until being locked by OTP-L bit in the Configuration Register.

Everything for Memory 36 / 51 Longsys Copyright

The Program OTP Pages sequence is as follows:

- 1. Issue Set Feature command (1Fh) to set OTP-E=1

- 2. Issue WREN command (06h) to set WEL bit

- 3. Issue Program Data Load and Program Execute command

- 4. Issue Get Feature command (0Fh) to read the status.

When ECC is enabled, ECC calculation will be performed during Program Execute.

Once the OTP pages are correctly programmed, OTP-L bit can be used to permanently lock these pages so that no further modification is possible.

The OTP Lock sequence is as follows:

- 1. Issue Set Feature command (1Fh) to set OTP-E=1 and OTP-L=1

- 2. Issue WREN command (06h) to set WEL bit

- 3. Issue Program Execute command (10h), page address is "don't care"

- 4. Issue Get Feature command (0Fh) to read the status.

- 5. Issue Set Feature command (1Fh) to set OTP-E=0, return to the main memory array operation.

## 10.8.3 Parameter Page Data Definition

**Table 18 Parameter Definition**

| Byte Number | Descriptions                                      | Values          |

|-------------|---------------------------------------------------|-----------------|

| 0~3         | Parameter Page Signature, "ONFI" ASCII characters | 4Fh 4Eh 46h 49h |

| 4~5         | Revision Number                                   | 00h 00h         |

| 6~31        | Reserved (0)                                      | all 00h         |

|             |                                                   | 46h 4Fh 52h 45h |

| 32~43       | Device manufacturer, 12 ASCII characters          | 53h 45h 45h 20h |

|             |                                                   | 20h 20h 20h 20h |

|             |                                                   | 46h 33h 35h 53h |

|             |                                                   | 51h 42h 30h 30h |

| 44-63       | Device Model, 20 ASCII characters                 | 32h 47h 20h 20h |

|             |                                                   | 20h 20h 20h     |

|             |                                                   | 20h 20h 20h     |

| 64          | JEDEC MID                                         | CDh             |

| 65-66       | Date Code                                         | 00h 00h         |

| 67-79       | Reserved (0)                                      | all 00h         |

| 80-83       | Number of Data Bytes per Page                     | 00h 08h 00h 00h |

| 84-85       | Number of Spare Bytes per Page                    | 80h 00h         |

| 86-89       | Number of Data Bytes per Partial Page             | 00h 02h 00h 00h |

| 90-91       | Number of Spare Bytes per Partial Page            | 20h 00h         |

| 92-95       | Number of Pages per Block                         | 40h 00h 00h 00h |

| 96-99       | Number of Block per Logic Unit                    | 00h 08h 00h 00h |

| 100         | Number of Logic Units                             | 01h             |

| Byte Number | Descriptions                                                                                                                                                                                            | Values  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 101         | Reserved (0)                                                                                                                                                                                            | 00h     |

| 102         | Number of Bits per Cell                                                                                                                                                                                 | 01h     |

| 103-104     | Bad Blocks Maximum per Logic Unit                                                                                                                                                                       | 28h 00h |

| 105-106     | Block Endurance                                                                                                                                                                                         | 01h 05h |

| 107         | Guaranteed Valid Blocks at Beginning of Target                                                                                                                                                          | 01h     |

| 108-109     | Block Endurance for Guaranteed Valid Blocks                                                                                                                                                             | 01h 03h |

| 110         | Number of Programs per Page                                                                                                                                                                             | 01h     |

| 111         | Partial Programming Attributes  b5-b7 reserved (0)  b4 1 = partial page layout is partial page data followed by partial page spare  b1-b3 reserved (0)  b0 1 = partial page programming has constraints | 00h     |

| 112         | Number of ECC Bits Correctability                                                                                                                                                                       | 00h     |

| 113-127     | Reserved (0)                                                                                                                                                                                            | all 00h |

| 128         | I/O Pin Capacitance, Maximum                                                                                                                                                                            | 06h     |

| 129-132     | Reserved (0)                                                                                                                                                                                            | all 00h |

| 133-134     | t <sub>PROG</sub> Maximum Page Program Time (us)                                                                                                                                                        | 20h 03h |

| 135-136     | ters Maximum Block Erase Time (us)                                                                                                                                                                      | 10h 27h |

| 137-138     | t <sub>RD</sub> Maximum Page read Time (us)                                                                                                                                                             | 87h 00h |

| 139-163     | Reserved (0)                                                                                                                                                                                            | all 00h |

| 164-165     | Vendor Specific Revision Number                                                                                                                                                                         | 00h 00h |

| 166-253     | Vendor Specific                                                                                                                                                                                         | all 00h |

| 254-255     | Integrity CRC                                                                                                                                                                                           | 62h B4h |

| 256-511     | Value of Bytes 0-255                                                                                                                                                                                    | _       |

| 512-767     | Value of Bytes 0-255                                                                                                                                                                                    | _       |

| 768+        | Additional Redundant Parameter Pages                                                                                                                                                                    |         |

#### Note:

(1) The Integrity CRC (Cycling Redundancy Check) field is used to verify that the contents of the parameters page were transferred correctly to the host. Please refer to ONFI 1.0 specifications for details. The CRC shall be calculated using the following 16-bit generator polynomial: G(X) = X16 + X15 + X2 + 1

# 11 Software Algorithm

### 11.1 Initial Invalid Block(s)

Initial invalid blocks are defined as blocks that contain one or more initial invalid bits whose reliability is not guaranteed. Devices with initial invalid block(s) have the same quality level as devices with all valid blocks and have the same electrical characteristics. An initial invalid block(s) does not affect the performance of valid block(s). The system design must be able to mask out the initial invalid block(s) via address mapping. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block at the time of shipment.

**Table 19 Valid Block Number**

| Parameter          | Symbol   | Min  | Max  | Unit   |

|--------------------|----------|------|------|--------|

| Valid block number | $N_{VB}$ | 2008 | 2048 | Blocks |

## 11.2 Identifying Initial Invalid Block(s)

All device locations are erased (FFh) except locations where the initial invalid block(s) information is written prior to shipping. All initial invalid blocks are marked with non-FFh at the first byte of spare area on the 1st or 2nd page. Since the initial invalid block information is also erasable in most cases, it is impossible to recover the information once it has been erased. Therefore, the system must be able to recognize the initial invalid block(s) based on the original initial invalid block information and create the initial invalid block table via the suggested flow (**Figure 26**). Any intentional erasure of the original initial invalid block information is prohibited.

Set Block Address = 0

Increment Block Address

Note: Check "FFh" at the column address 2048 of the 1st and 2nd page in the block Invalid Block(s) Table

No Last Block?

Yes

End

Figure 26 Flow to Create Initial Invalid Block Table

### 11.3 Error in Operation

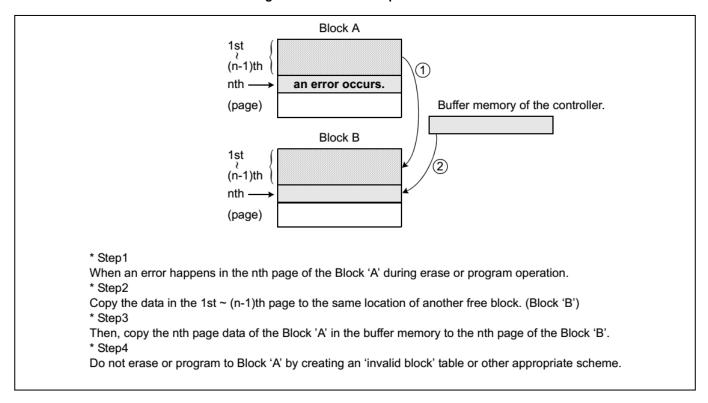

Within its life time, additional invalid blocks may develop with NAND Flash memory. The following possible failure modes should be considered to implement a highly reliable system. In the case of status read failure after erase or program, block replacement should be done. Because program status fail during a page program does not affect the data of the other pages in the same block, block replacement can be executed with a page-sized buffer by finding an erased empty block and reprogramming the current target data and copying the rest of the replaced block. In case of Read, ECC must be employed. To improve the efficiency of memory space, it is recommended that the blocks with correctable bits error reclaimed by ECC don't need to be replaced. The said additional block failure rate does not include those reclaimed blocks.

**Table 20 Failure Modes**

| Operation | Detection and recommended procedure           |

|-----------|-----------------------------------------------|

| Erase     | Status read after erase → Block Replacement   |

| Program   | Status read after program → Block Replacement |

| Read      | Verify ECC → ECC correction                   |

#### Figure 27 Bad Block Replacement

### 11.4 Internal ECC

The internal ECC logic may detect and correct no more than 8-bit error in each ECC sector. An ECC sector is composed by a main area (512 Byte) and a spare area (32 Byte). The default state of the internal ECC is enabled. It is operated by the Set Feature operation to enable or disable internal ECC, and then check the internal ECC state by Get Feature operation.

The internal ECC is enabled by using Set Feature command (1Fh) to set ECC-E. To disable the internal ECC can be done by using the Set Feature command (1Fh) to clear ECC-E.

When the internal ECC is enabled:

- Data in main area and spare area are protected. ECC protection range is depended on ECC-M bit config, refer to **ECC Mode Bit (ECC-M)** for detailed information.

- During a Program operation, an ECC code is calculated and stored in the additional spare area.

- During a Read operation, after the data transfer time (tRD\_ECC) is completed, a Get Feature command should be issued to check the ECC status bits which indicate whether or not the error correction was successful. Please refer to Status Register. Furthermore, user could check the detailed bits error information for each ECC sector by Get Feature operation. See Sector ECC Status Register for details.

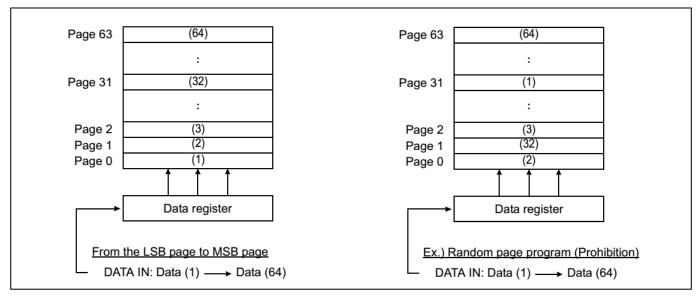

## 11.5 Addressing for Program Operation

Within a block, the pages must be programmed consecutively from the LSB (least significant bit) page of the block to the MSB (most significant bit) pages of the block. The LSB page is defined as the start page among the pages to be programmed, does not need to be page 0 in the block. Random page address programming is prohibited.

Figure 28 Addressing for Program Operation

## 12 Electrical Characteristics

## 12.1 Absolute Maximum Ratings

**Table 21 Absolute Maximum Rating**

| Parameters                         | Symbol            | Range           | Unit |

|------------------------------------|-------------------|-----------------|------|

| Supply Voltage                     | Vcc               | -0.6 to +4.6    | V    |

| Voltage Applied to Any Pin         | Vio               | -0.6 to Vcc+0.4 | V    |

| Temperature under Bias             | T <sub>BIAS</sub> | -40 to +125     | °C   |

| Storage Temperature                | T <sub>STG</sub>  | -65 to +150     | °C   |

| Short circuit output current, I/Os | los               | 5               | mA   |

#### Note:

- (1) Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns.Maximum DC voltage on input/output pins is VCC+0.3V which, during transitions, may overshoot to VCC+2.0V for periods <20ns.</p>

- (2) Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## 12.2 Operating Ranges

**Table 22 Operating Ranges**

| Parameters          | Symbol          | Conditions      | Min | Max  | Unit |

|---------------------|-----------------|-----------------|-----|------|------|

| Supply Voltage      | V <sub>CC</sub> |                 | 2.7 | 3.6  | V    |

| Ambient Temperature | -               | Industrial      | -40 | +85  | °C   |

| Ambient Temperature | IA              | Industrial plus | -40 | +105 | °C   |

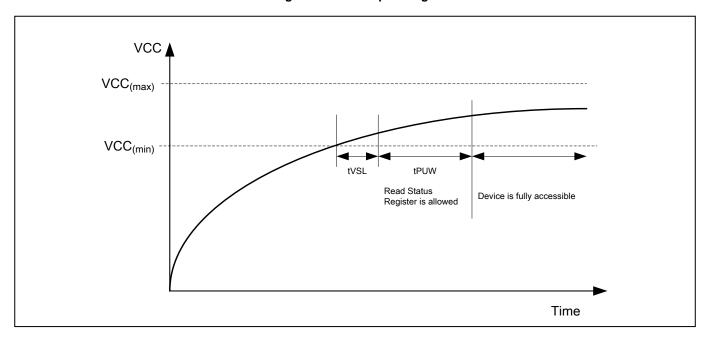

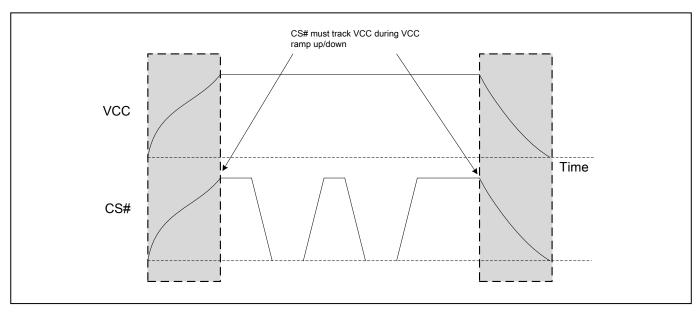

## 12.3 Power-up and Power-down Timing Requirements

**Table 23 Power-up Timing**

| Parameters                                  | Symbol | Min | Max | Unit |