#### 1、MT41K256M16HA-CN

#### (1) Description

DDR3L SDRAM (1.35V) is a low voltage version of the DDR3 (1.5V) SDRAM. When running in 1.5V compatible mode. DDR3 SDRAM uses a double data rate architecture to achieve high-speed operation. The double data rate architecture is an 8n-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write operation for the DDR3 SDRAM effectively consists of a single 8n-bit-wide, four-clock cycle data transfer at the internal DRAM core and eight corresponding n-bit-wide, one half-clock-cycle data transfers at the I/O pins.

#### (2) Features

- VDD = VDDQ = 1.35v (1.283-1.45v)

- VDD = VDDQ = 1.5V±0.075V

- Supports DDR3L devices to be backward compatible in 1.5V applications

- Differential bidirectional data strobe

- 8 internal banks

- 8n-bit prefetch architecture

- Differential clock inputs(CK, CK#)

- ODT function

- For data, strobe and mask signals

- Programmable CAS (READ) latency(CL)

- Programmable posted CAS additive latency (AL)

- Programmable CAS (WRITE) latency(CWL)

- Fixed burst length (BL) of8 and burst chop (BC) of 4(via the

mode register set [MRS])

- Selectable BC4 or BL8 on-the-fly (OTF)

- Self refresh mode

- T<sub>C</sub> of 105°C

- 64ms, 8192-cycle refresh up to 85°C

- 32ms, 8192-cycle refresh at >85°C to 95°C

- 16ms, 8192-cycle refresh at >95°C to 105°C

- Self refresh temperature (SRT)

- Automatic self refresh (ASR)

- Write leveling

- Multipurpose register

- Output driver calibration

## (3) Options and Marking

| Opt                          | Marking                                            |        |

|------------------------------|----------------------------------------------------|--------|

| Configuration                | 256 Meg x 16                                       | 256M16 |

|                              | 96-ball (9mm x 14mm) Type E                        | НА     |

| FBGA package (Pb-free) – x16 | 96-ball (7.5mm x 13.5mm) Type N                    | LY     |

|                              | 96-ball (8mm x 14mm) Type P                        | TW     |

|                              | 938ps @ CL = 14 (DDR3-2133)                        | -093   |

| Timing-cycle time            | 1.07ns @ CL = 13 (DDR3-1866)                       | -107   |

|                              | 1.25ns @ CL = 11 (DDR3-1600)                       | -125   |

|                              | Commercial(0°C≤T <sub>C</sub> ≤ +95°C)             | None   |

| Operating temperature        | perature Industrial (-40°C≤T <sub>C</sub> ≤ +95°C) |        |

|                              | Automotive (-40°C≤T <sub>C</sub> ≤ +105°C)         | AT     |

www.chipnobo.com 2/16

# (4) Key Timing Parameters

| Speed Grade         | Data Rate (MT/s) | Target <sup>t</sup> RCD- <sup>t</sup> RP-CL | <sup>t</sup> RCD (ns) | <sup>t</sup> RP (ns) | CL (ns) |

|---------------------|------------------|---------------------------------------------|-----------------------|----------------------|---------|

| -093 <sup>1,2</sup> | 2133             | 14-14-14                                    | 13.09                 | 13.09                | 13.09   |

| -107 <sup>1</sup>   | 1866             | 13-13-13                                    | 13.91                 | 13.91                | 13.91   |

| -125                | 1600             | 11-11-11                                    | 13.75                 | 13.75                | 13.75   |

Notes: 1 Backward compatible to 1600,CL = 11(-125)

2 Backward compatible to 1866,CL = 13(-107)

## (5) Addressing

| Parameter      | 256 Meg x 16          |

|----------------|-----------------------|

| Configuration  | 32 Meg x 16 x 8 banks |

| Refresh count  | 8K                    |

| Row address    | 32K (A[14:0])         |

| Bank address   | 8 (BA[2:0])           |

| Column address | 1K (A[9:0])           |

| Page size      | 2KB                   |

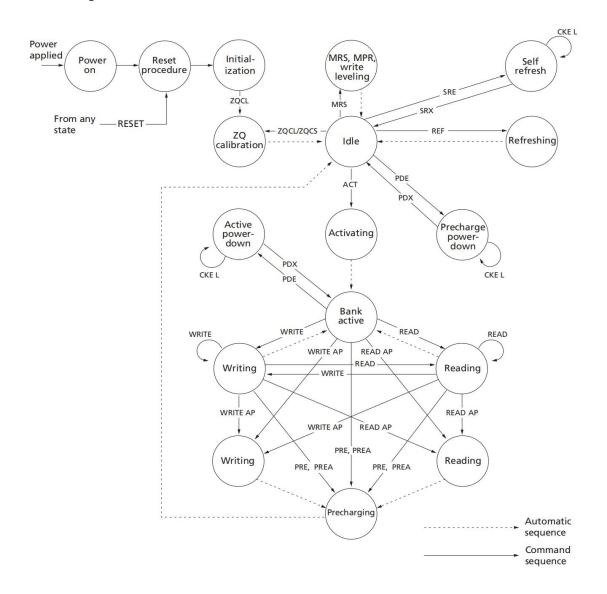

#### (6) State Diagram

ACT=ACTIVATE

E PREA= PRECHARGE ALL

WRITE=WR, WRS4, WRS8

SRX=Self refresh exit

MPR=Multipurpose register

READ AP =RDAP,RDAPS4, RDAPS8

READ= RD, RDS4, RDS8

WRITE AP = WRAP, WRAPS4, WRAPS8

MRS=Mode register set

REF= REFRESH

ZQCL = ZQ LONG CALIBRATION

PDE=Power-down entry

PDX=Power-down exit

RESET=START RESET PROCEDURE

ZQCS = ZQ SHORT CALIBRATION

PRE=PRECHARGE SRE=Self refresh entry

#### (7) Functional Description

DDR3 SDRAM uses a double data rate architecture to achieve high-speed operation. The double data rate architecture is an 8n-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write operation for the DDR3 SDRAM effectively consists of a single 8n-bit-wide, four-clock cycle data transfer at the internal DRAM core and eight corresponding n-bit-wide, one half-clock-cycle data transfers at the I/O pins.

The data used for writing is centre aligned. The read data is transmitted by the DDR3 SDRAM and edgealigned to the data strobes.

The DDR3 SDRAM operates from a differential clock (CK and CK#). The crossing of CK going HIGH and CK# going LOW is referred to as the positive edge of CK. Control, command, and address signals are registered at every positive edge of CK, Input data is registered on the first rising edge of DQS after the WRITE preamble, and output data is referenced on the first rising edge of DQS after the READ preamble.

Read and write accesses to the DDR3 SDRAM are burst-oriented. Accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVATE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVATE command are used to select the bank and row to be accessed. The address bits registered coincident with the READ or WRITE commands are used to select the bank and the starting column location for the burst access.

The device uses a READ and WRITE BL8 and BC4. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access.

As with standard DDR SDRAM, the pipelined, multibank architecture of DDR3 SDRAM allows for concurrent operation, thereby providing high bandwidth by hiding row precharge and activation time.

A self refresh mode is provided, along with a power-saving, power-down mode.

## Industrial Temperature

The industrial temperature (IT) device requires that the case temperature not exceed -40°C or 95°C. JEDEC specifications require the refresh rate to double when Tc exceeds 85°C; this also requires use of the high-temperature self refresh option. Additionally, ODT resistance and the input/output impedance must be derated when Tc is < 0°C or >95°C.

#### **Automotive Temperature**

The Automotive temperature (AT) device requires that the case temperature not exceed - $40^{\circ}$ C or  $105^{\circ}$ C. Micron specification requires the refresh rate to 4X when Tc exceeds  $95^{\circ}$ C; this also requires use of the high-temperature self refresh option. Additionally, ODT resistance and the input/output impedance must be derated when Tc is <  $0^{\circ}$ C or > $95^{\circ}$ C.

#### **General Notes**

- The functionality and the timing specifications discussed in this data sheet are for the DLL enable mode of operation (normal operation).

- Throughout this data sheet, various figures and text refer to DQs as "DQ". DQ is to be interpreted as any and all DQ collectively, unless specifically stated otherwise.

- The terms "DQS" and "CK" found throughout this data sheet are to be interpreted as DQS, DQS# and CK, CK# respectively, unless specifically stated otherwise.

- Complete functionality may be described throughout the document; any page or diagram may have been simplified to convey a topic and may not be inclusive of all requirements.

- Any functionality not specifically stated is considered undefined, illegal, and not supported, and can result in unknown operation.

- Row addressing is denoted as A[n:0]. For example 1Gb:n=12(x16); 1Gb:n=13(x4,x8); 2Gb:n=13(x16) and 2Gb:n=14(x4,x8); 4Gb:n=14(x16); and 4Gb:n=15(x4,x8).

- Dynamic ODT has a special use case: when DDR3 devices are architected for use in a single rank memory array, the ODT ball can be wired HIGH rather than routed. Refer to the Dyamic ODT Special Use Case section.

- Ax16 device's DQ bus is comprised of two bytes. If only one of the bytes needs to be used, use the lower byte for data transfers and terminate the upper byte as noted:

- Connect UDQS to ground via  $1k\Omega^*$  resistor.

- Connect UDQS# to VDD via  $1k\Omega^*$  resistor.

- Connect UDM to VDD via  $1k\Omega^*$  resistor.

- Connect DQ[15:8] individually to either Vss, VDD, or VREF via  $1k\Omega$  resistors,\* or float DQ[15:8].

- \*If ODT is used,  $1k\Omega$  resistor should be changed to 4x that of the selected ODT.

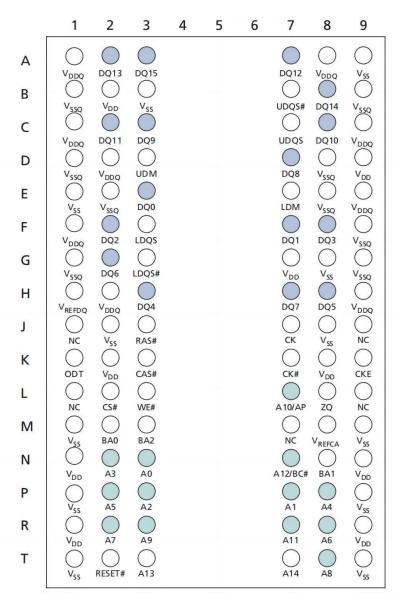

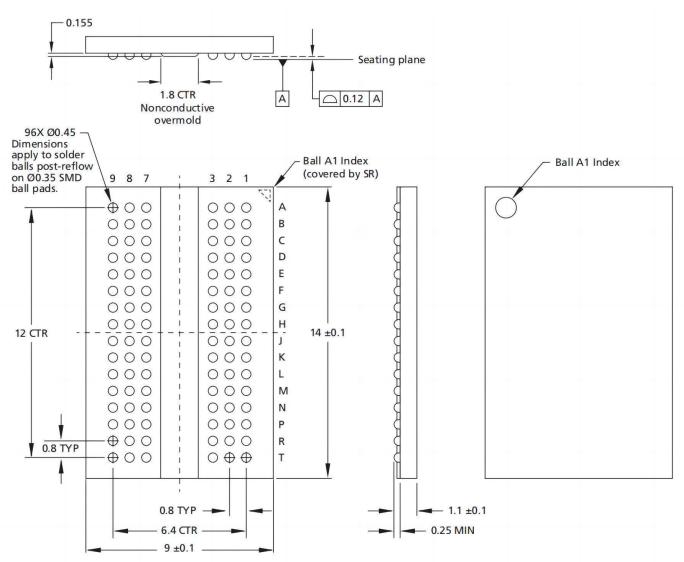

# 2. Pinout and Description

The lead-in end arrangement shall be as specified in the diagram below.

Pin Arrangement Diagram (Top View)

# **Pin Descriptions**

| Symbol                                    | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[14:13], A12/BC#,<br>A11, A10/AP, A[9:0] | Input | Address inputs: Provide the row address for ACTIVATE commands, and the column address and auto precharge bit (A10) for READ/WRITE commands, to select one location out of the memory array in the respective bank. A10 sampled during a PRECHARGE command determines whether the PRECHARGE applies to one bank (A10 LOW, bank selected by BA[2:0]) or all banks (A10 HIGH). The address inputs also provide the op-code during a LOAD MODE command. Address inputs are referenced to V <sub>REFCA</sub> . A12/BC#: When enabled in the mode register (MR), A12 is sampled during READ and WRITE commands to determine whether burst chop (on-the-fly) will be performed (HIGH = BL8 or no burst chop, LOW = BC4). See Table 70 (page 117). |

| BA[2:0]                                   | Input | <b>Bank address inputs:</b> BA[2:0] define the bank to which an ACTIVATE, READ, WRITE, or PRECHARGE command is being applied. BA[2:0] define which mode register (MR0, MR1, MR2, or MR3) is loaded during the LOAD MODE command. BA[2:0] are referenced to $V_{REFCA}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CK, CK#                                   | Input | <b>Clock:</b> CK and CK# are differential clock inputs. All control and address input signals are sampled on the crossing of the positive edge of CK and the negative edge of CK#. Output data strobe (DQS, DQS#) is referenced to the crossings of CK and CK#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CKE                                       | Input | <b>Clock enable:</b> CKE enables (registered HIGH) and disables (registered LOW) internal circuitry and clocks on the DRAM. The specific circuitry that is enabled/disabled is dependent upon the DDR3 SDRAM configuration and operating mode. Taking CKE LOW provides PRECHARGE POWER-DOWN and SELF REFRESH operations (all banks idle), or active power-down (row active in any bank). CKE is synchronous for power-down entry and exit and for self refresh entry. CKE is asynchronous for self refresh exit. Input buffers (excluding CK, CK#, CKE, RESET#, and ODT) are disabled during POWER-DOWN. Input buffers (excluding CKE and RESET#) are disabled during SELF REFRESH. CKE is referenced to V <sub>REFCA</sub> .              |

| CS#                                       | Input | <b>Chip select:</b> CS# enables (registered LOW) and disables (registered HIGH) the command decoder. All commands are masked when CS# is registered HIGH. CS# provides for external rank selection on systems with multiple ranks. CS# is considered part of the command code. CS# is referenced to $V_{REFCA}$ .                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LDM                                       | Input | <b>Input data mask:</b> LDM is a lower-byte, input mask signal for write data. Lower-byte input data is masked when LDM is sampled HIGH along with the input data during a write access. Although the LDM ball is input-only, the LDM loading is designed to match that of the DQ and DQS balls. LDM is referenced to V <sub>REFDQ</sub> .                                                                                                                                                                                                                                                                                                                                                                                                 |

| ODT                                       | Input | <b>On-die termination:</b> ODT enables (registered HIGH) and disables (registered LOW) termination resistance internal to the DDR3 SDRAM. When enabled in normal operation, ODT is only applied to each of the following balls: DQ[15:0], LDQS, LDQS#, UDQS, UDQS#, LDM, and UDM for the x16; DQ0[7:0], DQS, DQS#, DM/TDQS, and NF/TDQS# (when TDQS is enabled) for the x8; DQ[3:0], DQS, DQS#, and DM for the x4. The ODT input is ignored if disabled via the LOAD MODE command. ODT is referenced to V <sub>REFCA</sub> .                                                                                                                                                                                                               |

| RAS#, CAS#, WE#                           | Input | <b>Command inputs:</b> RAS#, CAS#, and WE# (along with CS#) define the command being entered and are referenced to $V_{REFCA}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RESET#                                    | Input | <b>Reset:</b> RESET# is an active LOW CMOS input referenced to $V_{SS}$ . The RESET# input receiver is a CMOS input defined as a rail-to-rail signal with DC HIGH $\geq 0.8 \times V_{DD}$ and DC LOW $\leq 0.2 \times V_{DDQ}$ . RESET# assertion and desertion are asynchronous.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## **Pin Descriptions (Continued)**

| Symbol             | Туре      | Description                                                                                                                                                                                                                                                                                                                                  |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UDM                | Input     | <b>Input data mask:</b> UDM is an upper-byte, input mask signal for write data. Upper-byte input data is masked when UDM is sampled HIGH along with that input data during a WRITE access. Although the UDM ball is input-only, the UDM loading is designed to match that of the DQ and DQS balls. UDM is referenced to V <sub>REFDQ</sub> . |

| DQ[7:0]            | I/O       | <b>Data input/output:</b> Lower byte of bidirectional data bus for the x16 configuration. DQ[7:0] are referenced to V <sub>REFDQ</sub> .                                                                                                                                                                                                     |

| DQ[15:8]           | I/O       | <b>Data input/output:</b> Upper byte of bidirectional data bus for the x16 configuration. DQ[15:8] are referenced to $V_{REFDQ}$ .                                                                                                                                                                                                           |

| LDQS, LDQS#        | I/O       | <b>Lower byte data strobe:</b> Output with read data. Edge-aligned with read data. Input with write data. Center-aligned to write data.                                                                                                                                                                                                      |

| UDQS, UDQS#        | I/O       | <b>Upper byte data strobe:</b> Output with read data. Edge-aligned with read data. Input with write data. DQS is center-aligned to write data.                                                                                                                                                                                               |

| $V_{DD}$           | Supply    | <b>Power supply:</b> 1.5V ±0.075V.                                                                                                                                                                                                                                                                                                           |

| $V_{\mathrm{DDQ}}$ | Supply    | <b>DQ power supply:</b> 1.5V $\pm 0.075$ V. Isolated on the device for improved noise immunity.                                                                                                                                                                                                                                              |

| V <sub>REFCA</sub> | Supply    | <b>Reference voltage for control, command, and address:</b> V <sub>REFCA</sub> must be maintained at all times (including self refresh) for proper device operation.                                                                                                                                                                         |

| $V_{REFDQ}$        | Supply    | <b>Reference voltage for data:</b> $V_{REFDQ}$ must be maintained at all times (excluding self refresh) for proper device operation.                                                                                                                                                                                                         |

| V <sub>SS</sub>    | Supply    | Ground.                                                                                                                                                                                                                                                                                                                                      |

| V <sub>SSQ</sub>   | Supply    | DQ ground: Isolated on the device for improved noise immunity.                                                                                                                                                                                                                                                                               |

| ZQ                 | Reference | External reference ball for output drive calibration: This ball is tied to an external $240\Omega$ resistor (RZQ), which is tied to $V_{SSQ}$ .                                                                                                                                                                                              |

| NC                 | _         | <b>No connect:</b> These balls should be left unconnected (the ball has no connection to the DRAM or to other balls).                                                                                                                                                                                                                        |

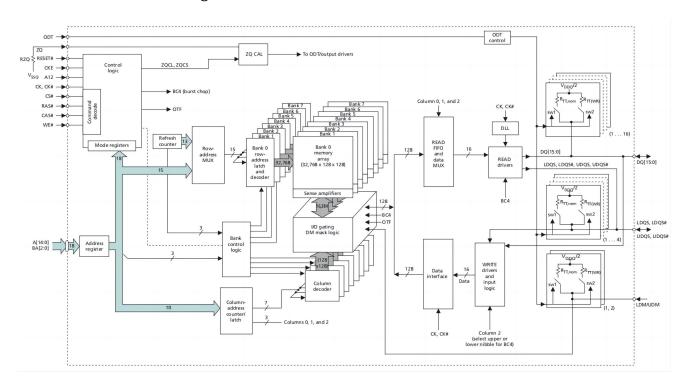

# 3、Functional Block Diagrams

# 4、Electrical Specifications

| Absolute Maximum Ratings |                                         |      |       |      |       |  |  |  |

|--------------------------|-----------------------------------------|------|-------|------|-------|--|--|--|

| Symbol                   | Parameter                               | Min  | Max   | Unit | Notes |  |  |  |

| VDD                      | VDD supply voltage relative to VSS      | -0.4 | 1.975 | V    | 1     |  |  |  |

| VDDQ                     | VDD supply voltage relative to VSSQ     | -0.4 | 1.975 | V    |       |  |  |  |

| VIN, VOUT                | Voltage on any pin relative to VSS      | -0.4 | 1.975 | V    |       |  |  |  |

| тс                       | Operating case temperature - Commercial | 0    | 95    |      |       |  |  |  |

|                          | Operating case temperature - Industrial | -40  | 95    | °C   | 2.2   |  |  |  |

|                          | Operating case temperature - Automotive | -40  | 105   |      | 2,3   |  |  |  |

|                          | Operating case temperature - Military   | -55  | 125   |      |       |  |  |  |

| TSTG                     | Storage temperature                     | -55  | 150   | °C   |       |  |  |  |

Notes: 1. VDD and VDDQ must be within 300mV of each other at all times, and VREF must not be greater than  $0.6 \times \text{VDDQ}$ . When VDD和 VDDQ < 500 mV, VREF can be  $\leq 300 \text{mV}$ .

- 2. MAX operating case temperature. TC is measured in the center of the package.

- 3. Device functionality is not guaranteed if DRAM device exceeds the maximum TC during operation.

|         | Recommended Parameters               |      |      |      |      |  |  |  |

|---------|--------------------------------------|------|------|------|------|--|--|--|

| Symbol  | Parameter                            | Min  | Тур  | Max  | Unit |  |  |  |

| VDD     | Supply voltage                       | 1.28 | 1.35 | 1.45 | V    |  |  |  |

| VDDQ    | I/O Supply voltage                   | 1.28 | 1.35 | 1.45 | V    |  |  |  |

| Backwar | d compatible to VDD=VDDQ=1.5V±0.075V |      |      |      |      |  |  |  |

## 5. Electrical Characteristics

## 5.1 Input/Output Capacitance

DDR3L Input/output capacitance

|                                        |                      | DDR      | 3L-16 | DDR3 | L-186 | DDR: | 3L-21 |      |      |

|----------------------------------------|----------------------|----------|-------|------|-------|------|-------|------|------|

| Capacitance<br>Parameters              | Sym                  | 0        | 00    | 6    |       | 33   |       | Unit | Note |

| Parameters                             |                      | Min      | Max   | Min  | Max   | Min  | Max   |      |      |

| CK and CK#                             | $C_{CK}$             | 0.8      | 1.4   | 0.8  | 1.3   | 0.8  | 1.3   | pF   |      |

| ΔC:CK to                               | C <sub>DCK</sub>     | 0.0      | 0.15  | 0.0  | 0.15  | 0.0  | 0.15  | pF   |      |

| Single-end I/O: DQ, DM                 | $C_{IO}$             | 1.4      | 2.2   | 1.4  | 2.1   | 1.4  | 2.1   | pF   | 2    |

| Differential I/O:DQS,D QS#,TDQS, TDQS# | C <sub>IO</sub>      | 1.4      | 2.2   | 1.4  | 2.1   | 1.4  | 2.1   | pF   | 3    |

| ΔC: DQS to DQS#,TDQ S, TDQS#           | $C_{ m DDQS}$        | 0.0      | 0.15  | 0.0  | 0.15  | 0.0  | 0.15  | pF   | 3    |

| ΔC: DQ to DQS                          | $C_{DIO}$            | -0.5     | 0.3   | -0.5 | 0.3   | -0.5 | 0.3   | pF   | 4    |

| Inputs(CTR<br>L,CMD,AD<br>DR)          | Cı                   | 0.7<br>5 | 1.2   | 0.75 | 1.2   | 0.75 | 1.2   | pF   | 5    |

| ΔC: CTRL to CK                         | C <sub>DI_CTRL</sub> | -0.4     | 0.2   | -0.4 | 0.2   | -0.4 | 0.2   | pF   | 6    |

| ΔC: CMD_ADD R to CK                    | C <sub>DI_CMD</sub>  | -0.4     | 0.4   | -0.4 | 0.4   | -0.4 | 0.4   | pF   | 7    |

| ZQ pin capacitance                     | CzQ                  | -        | 3.0   | -    | 3.0   | -    | 3.0   | pF   |      |

| Reset pin capacitance                  | $C_{RE}$             | -        | 3.0   | -    | 3.0   | -    | 3.0   | pF   |      |

Notes: 1.  $V_{DD} = 1.35V$  (1.283-1.45V),  $V_{DDQ} = V_{DD}$ ,  $V_{REF} = V_{SS}$ , f = 100 MHz,  $T_C = 25$ °C.  $V_{OUT(DC)} = 0.5 \times V_{DDQ}$ ,  $V_{OUT} = 0.1V$  (peak-to-peak.).

- 2. DM input is grouped with I/O pins, reflecting the fact that they are matched in loading.

- 3. Includes TDQS, TDQS#. CDDQS is for DQS vs. DQS# and TDQS vs. TDQS# separately.

- 4.  $C_{DIO} = C_{IO(DQ)} 0.5 \times (C_{IO(DQS)} + C_{IO(DQS\#)})_{\circ}$

- 5. Excludes CK, CK#; CTRL = ODT, CS#, and CKE; CMD = RAS#, CAS#, and WE#; A=[n: 0], BA=[2:0].

- 6.  $C_{DI\_CTRL} = C_{I(CTRL)} 0.5 \times (C_{CK (CK)} + C_{CK (CK \#)})_{\circ}$

- 7.  $C_{DI\_CMD\_ADDR} = C_{I (CMD\_ADDR)} 0.5 \times (C_{CK (CK)} + C_{CK (CK \#)})_{\circ}$

11/16

## 5.2 IDD Specifications and conditions

Within the following IDD measurement tables, the following definitions and conditions are used, unless stated otherwise:

- LOW: $V_{IN} \le V_{IL(AC)max}$ ; HIGH: $V_{IN} \ge V_{IH(AC)min}$ .

- Midlevel: Inputs are VREF=VDD/2.

- $R_{ON}$  set to RZQ/7 (34 $\Omega$ ).

- $R_{TT,nom}$  set to RZQ/6 (40 $\Omega$ ).

- RTT(WR) set to RZQ/2 (120 $\Omega$ ).

- Qoff is enabled in MRl.

- ODT is enabled in MRI (RTT,nom) and MR2 (RTT(WR)).

- TDQS is disabled in MRl.

- External DQ/DQS/DM load resistor is  $25\Omega$  to VDDQ/2.

- Burst lengths are BL8 fixed.

- AL = 0 (except in  $I_{DD7}$ ).

- IDD specifications are tested after the device is properly initialized.

- Input slew rate is specified by AC parametric test conditions.

- Optional ASR is disabled.

- Read burst type uses nibble sequential (MR0[3] = 0).

- Loop patterns must be executed at least once before current measurements begin.

Timing Parameters Used for IDD Measurements - Clock Units

|                           |                     | DDR3     | L-1600               | DDR3L-1866 | DDR3L-2133 |      |

|---------------------------|---------------------|----------|----------------------|------------|------------|------|

| I <sub>DD</sub> Parameter |                     | -125E    | -125E -125 -107 -093 |            | -093       | Unit |

|                           |                     | 10-10-10 | 11-11-11             | 13-13-13   | 14-14-14   |      |

| t CK(M                    | IIN)I <sub>DD</sub> | 1        | .25                  | 1.07       | 0.938      | ns   |

| CL I <sub>DD</sub>        | )                   | 10       | 11                   | 13         | 14         | CK   |

| t RCD(N                   | MIN)I <sub>DD</sub> | 10       | 11                   | 13         | 14         | CK   |

| t RC(M                    | IN)I <sub>DD</sub>  | 38       | 39                   | 45         | 50         | CK   |

| t RAS(N                   | IN)I <sub>DD</sub>  | 28       | 28                   | 32         | 36         | CK   |

| t RP(M                    | IN)I <sub>dd</sub>  | 10       | 11                   | 13         | 14         | CK   |

| <sup>t</sup> AFT          | ×16                 | 32       | 32                   | 33         | 38         | CK   |

| t RRD                     | ×16                 | 6        | 6                    | 6          | 7          | СК   |

|                           | 1Gb                 | 88       | 88                   | 103        | 118        | CK   |

| t DEC                     | 2Gb                 | 128      | 128                  | 150        | 172        | CK   |

| <sup>t</sup> RFC          | 4Gb                 | 208      | 208                  | 243        | 279        | CK   |

|                           | 8Gb                 | 280      | 280                  | 328        | 375        | CK   |

# 5.3 Operating IDD Specifications

## IDD Maximum Limits for 1.35/1.5V Operation

| Spe                                                         | Speed Bin            |        |            | DDD01 1066 | DDDat 0100 |       | N     |  |

|-------------------------------------------------------------|----------------------|--------|------------|------------|------------|-------|-------|--|

| Parameter                                                   | Symbol               | Wi dth | DDR3L-1600 | DDR3L-1866 | DDR3L-2133 | Units | Notes |  |

| Operating current 0:One bank ACTIVATE-to-PRECHARGE          | $I_{\mathrm{DD0}}$   | ×16    | 110        | 130        | 150        | mA    | 1,2   |  |

| Operating current 1:One bank ACTIVATE-to-READ-to- PRECHARGE | $I_{\mathrm{DD1}}$   | ×16    | 120        | 135        | 155        | mA    | 1,2   |  |

| Precharge power-down current:  Slow exit                    | $I_{\mathrm{DD2P0}}$ | ×16    | 22         | 22         | 22         | mA    | 1,2   |  |

| Precharge power-down current: Fast exit                     | $I_{\mathrm{DD2P1}}$ | ×16    | 45         | 47         | 49         | mA    | 1,2   |  |

| Precharge quiet standby current                             | $I_{DD2Q}$           | ×16    | 60         | 65         | 70         | mA    | 1,2   |  |

| Precharge standby current                                   | $I_{DD2N}$           | ×16    | 63         | 68         | 73         | mA    | 1,2   |  |

| Precharge standby ODT current                               | $I_{\text{DD2NT}}$   | ×16    | 85         | 92         | 98         | mA    | 1,2   |  |

| Active power-down current                                   | $I_{DD3P}$           | ×16    | 70         | 80         | 85         | mA    | 1,2   |  |

| Active standby current                                      | $I_{\text{DD3N}}$    | ×16    | 90         | 100        | 105        | mA    | 1,2   |  |

| Burst read operating current                                | $I_{\text{DD4R}}$    | ×16    | 190        | 220        | 240        | mA    | 1,2   |  |

| Burst write operating current                               | $I_{\rm DD4W}$       | ×16    | 210        | 250        | 280        | mA    | 1,2   |  |

| Burst refresh current                                       | $I_{DD5B}$           | ×16    | 235        | 242        | 250        | mA    | 1,2   |  |

| Room temperature self refresh                               | $I_{\mathrm{DD6}}$   | ×16    | 25         | 25         | 25         | mA    | 1,2,3 |  |

| Extended temperature self refresh                           | $I_{\mathrm{DD}6ET}$ | ×16    | 28         | 28         | 28         | mA    | 2,4   |  |

| All banks interleaved read current                          | $I_{DD7}$            | ×16    | 240        | 270        | 290        | mA    | 1,2   |  |

| Reset current                                               | $I_{\mathrm{DD8}}$   | ×16    | 23         | 23         | 24         | mA    | 1,2   |  |

Notes: 1.  $Tc = 85^{\circ}C$ ; SRT and ASR are disabled.

2. Enabling ASR could increase lddx by up to an additional 2mA.

3. Restricted to  $T_C(MAX) = 85^{\circ}C$ .

4. Tc = +85°C; ASR and ODT are disabled: SRT is enabled.

5. When Tc>+95°C: All IDDX parameters must be derated by 30%.

6. When Tc > +105°C: All IDDX parameters must be derated by 50%.

7. When Tc>+105°C: Self-refresh mode is not available.

# 5.4 DC Operating Conditions

DDR3L 1. 35V DC Electrical Characteristics and Operating Conditions

| Parameter                                                                                                                     | Symbol | Min   | Тур  | Max  | Unit |

|-------------------------------------------------------------------------------------------------------------------------------|--------|-------|------|------|------|

| Supply voltage                                                                                                                | VDD    | 1.283 | 1.35 | 1.45 | V    |

| I/O supply voltage                                                                                                            | VDDQ   | 1.283 | 1.35 | 1.45 | V    |

| Input leakage current Any input $0V \le VIN \le VDD$ , VREF Pin $0V \le VIN \le 1.1V$ (All other pins not under test = $0V$ ) | lι     | -2    | -    | 2    | μΑ   |

| VREF supply leakage current  VREFDQ = VDD/2 or VREFCA =  VDD/2  (All other pins not under test = 0V)                          | Ivref  | -1    | -    | 1    | μΑ   |

| Output leakage current (DQ off)                                                                                               | loz    | -5    | -    | 5    | μΑ   |

# 6. Package Dimensions

Notes: 1. All dimensions are in millimeters.

2. Solder ball material: SAC305 (96.5% Sn, 3% Ag, 0.5% Cu).

#### NOTICE

The information presented in this document is for reference only. Involving product optimization and productivity improvement, ChipNobo reserves the right to adjust product indicators and upgrade some technical parameters. ChipNobo is entitled to be exempted from liability for any delay or non-delivery of the information disclosure process that occurs.

本文件中提供的信息仅供参考。涉及产品优化和生产效率改善,ChipNobo 有权调整产品指标和部分技术参数的升级,所出现信息披露过程存在延后或者不能送达的情形,ChipNobo 有获免责权。

The product listed herein is designed to be used with residential and commercial equipment, and do not support sensitive items and specialized equipment in areas where sanctions do exist. ChipNobo Co., Ltd or anyone on its behalf, assumes no responsibility or liability for any damages resulting from improper use.

此处列出的产品旨在民用和商业设备上使用,不支持确有制裁地区的敏感项目和特殊设备,ChipNobo 有限公司或其代表,对因不当使用而造成的任何损害不承担任何责任。

For additional information, please visit our website <a href="http://www.chipnobo.com">http://www.chipnobo.com</a>, or consult your nearest Chipnobo sales office for further assistance.

欲了解更多信息,请访问我们的网站 http://www.chipnobo.com,或咨询离您最近的 Chipnobo 销售办事处以获得进一步帮助。