#### **Features**

- 4ms Soft Start

- Less than 75mW Standby Power

- Frequency Shuffling for EMI

- Audio Noise Free Operation

- Fixed 118KHz Switching Frequency

- Low VDD Start-up Current and Low Operating Current

- Leading Edge Blanking on Current Sense Input

- VDD Over Voltage Clamp and Under Voltage Lockout with Hysteresis (UVLO)

- Line Input Compensated Cycle-by-Cycle Over-Current Threshold Setting For Constant Output Power Limiting Over Universal Input Voltage Range

- Over Load Protection(OLP)

- Over Voltage Protection(OVP)

- Package type ESOP-7

### **Typical Application**

- USB QC/PD

- PD charger

- PDA Power Supply

- VCR,SVR, STB, DVD&DVCD Player SMPS

- Set- Top Box Power

- Auxiliary Power Supply for PC and Server

### **General Description**

The AS8864EM is a high-performance power switch designed for offline flyback power supplies, featuring an integrated D-GaN HEMT, suitable for solutions with power up to 45W. The chip operates in frequency hopping mode when the system output is no-load, in PFM (Pulse Frequency Modulation) mode during light to medium load conditions, and at a maximum constant operating frequency under heavy load. The startup current and operating current of the AS8864EM are set relatively low to reduce power consumption during standby. The chip incorporates a slope compensation circuit to avoid subharmonic oscillation and improve system stability. It also includes a leading-edge blanking time feature to eliminate the impact of diode reverse recovery current in the buffer network on the circuit. The chip is equipped with a frequency jitter function, effectively enhancing the system's EMI performance. The minimum operating frequency is set above the audio range, preventing the system from generating noise during operation. The AS8864EM integrates multiple protection features, including cycle-by-cycle current limit protection (OCP), over-voltage protection (OVP), over-voltage VDD clamping, under-voltage lockout (UVLO), and over-temperature protection (OTP). The internal totem-pole drive structure further enhances the system's EMI characteristics and soft-start control of the switch.

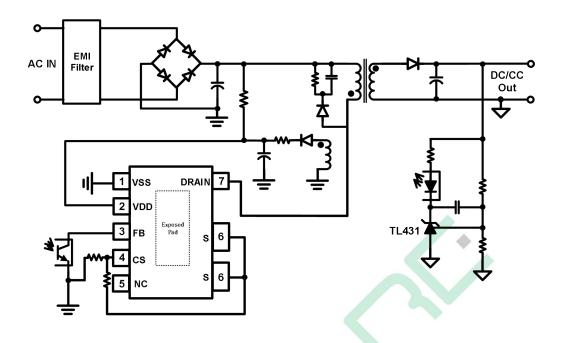

# **Typical Application Circuit**

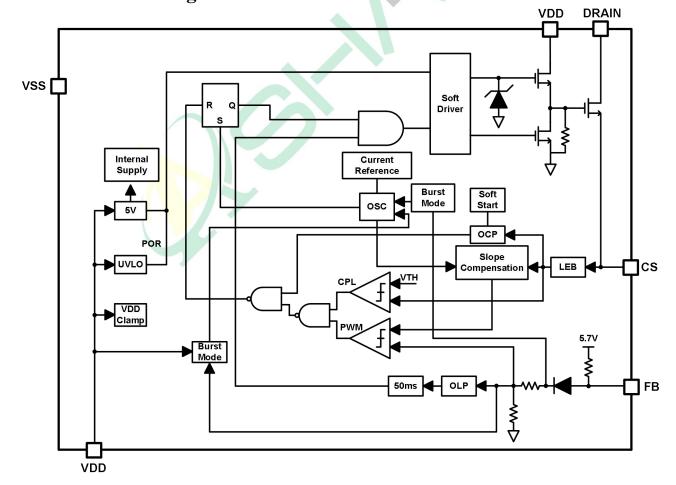

## **Functional Block Diagram**

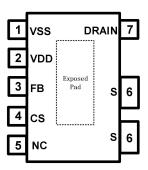

# Pin Assignment & Description

# **Pin Assignment**

**Pin Description**

| 1 in 2 coerrption |          |     |                                                                                                                                                                                  |  |

|-------------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin<br>Number     | Pin Name | I/O | Description                                                                                                                                                                      |  |

| 1                 | VSS      | P   | The Ground of the IC                                                                                                                                                             |  |

| 2                 | VDD      | I   | IC Power Supply Pin                                                                                                                                                              |  |

| 3                 | FB       | I   | Feedback pin. The loop regulation is achieved by connecting a photo-coupler to this pin. PWM duty cycle is determined by this pin voltage and the current sense signal at Pin 4. |  |

| 4                 | CS       | I   | Current Sense Input Pin                                                                                                                                                          |  |

| 5                 | NC       | /   | 1                                                                                                                                                                                |  |

| 6                 | S        | I   | The internal test pin is recommended to be connected with CS pin and 2M resistor for potential balance                                                                           |  |

| 7                 | DRAIN    | I   | D-GaN HEMT DRAIN Pin                                                                                                                                                             |  |

| Exposed Pad I     |          | I   | Connected to the S pin, it can be connected to the PCB to lay copper as an auxiliary heating aid                                                                                 |  |

# **Marking Information**

X: Internal identification

Y: Y--year M: Month

XXXX: Trace Number

## **Ordering Information**

| Part Number | Description                            |

|-------------|----------------------------------------|

| AS8864EM    | ESOP-7, Pb free in T&R, 5,000pcs./Reel |

### **Absolute Maximum Ratings(Note 1)**

| Parameter                                                                                    | Parameter Range | Unit |

|----------------------------------------------------------------------------------------------|-----------------|------|

| Supply Voltage (VCC)                                                                         | -0.3 to 58.5    | V    |

| VDD DC Clamp Current                                                                         | 10              | mA   |

| $V_{DS\_max}$ : The maximum drain-source voltage of the power transistor                     | 700             | V    |

| $V_{DS\_transient}$ : Transient voltage between the drain and source of the power transistor | 800             | V    |

| FB pin Voltage (FB)                                                                          | -0.3~7          | V    |

| CS pin voltage (CS)                                                                          | -0.3~7          | V    |

| Lead Temperature (10s)                                                                       | 260             | °C   |

| Thermal Resistance-Junction to Ambient(ESOP-7)                                               | 31.4            | °C/W |

| Operating Junction Temperature                                                               | -55~150         | °C   |

| Storage Temperature Range                                                                    | -55~150         | °C   |

| V <sub>ESD_HBM</sub>                                                                         | 2,000           | V    |

| V <sub>ESD_MM</sub>                                                                          | 200             | V    |

Note1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

### **Recommended Operation Conditions**

| Parameter                       | Value     | Unit |

|---------------------------------|-----------|------|

| Supply Voltage, V <sub>DD</sub> | 9 to 50   | V    |

| Operating Ambient Temperature   | -40 to 85 | °C   |

# Electrical Characteristics (TA= 25°C, VDD=16V, if not otherwise noted)

| Symbol                          | Parameter                        | Test Conditions                          | Min  | Тур  | Max  | Unit |  |

|---------------------------------|----------------------------------|------------------------------------------|------|------|------|------|--|

| Supply Vol                      | Supply Voltage Section (VDD Pin) |                                          |      |      |      |      |  |

| $I_{DD\_st}$                    | Start-up current into VDD pin    | V <sub>DD</sub> =14.5V                   | 5    |      | 20   | μΑ   |  |

| $I_{VDD\_Op}$                   | Operation Current                | V <sub>FB</sub> =3V                      |      | 1.6  |      | mA   |  |

| $V_{\mathrm{DD\_ON}}$           | VDD Under Voltage Lockout Exit   |                                          | 19.5 | 21   | 22.5 | V    |  |

| $ m V_{DD\_OFF}$                | VDD Under Voltage Lockout Enter  |                                          | 6.5  | 7.2  | 8    | V    |  |

| $V_{DD\_OVP}$                   | VDD OVP Threshold                | V <sub>CS</sub> =0V ,V <sub>FB</sub> =3V | 56   | 58.5 | 61   | V    |  |

| Feedback Input Section (FB Pin) |                                  |                                          |      |      |      |      |  |

| V <sub>FB_Open</sub>             | FB Open Voltage                                                           |                                         |      | 5   |      | V   |

|----------------------------------|---------------------------------------------------------------------------|-----------------------------------------|------|-----|------|-----|

| I <sub>FB_Short</sub>            | FB Short Circuit Current                                                  | Short FB Pin to GND,<br>Measure Current |      | 0.3 |      | mA  |

| V <sub>TH_0D</sub>               | FB threshold voltage at 0 duty cycle                                      |                                         |      | 0.8 |      | V   |

| V <sub>TH_PL</sub>               | Power Limitation FB Threshold<br>Voltage                                  |                                         |      | 3.7 |      | V   |

| $T_{D\_PL}$                      | Limit the anti-jitter time                                                |                                         |      | 50  |      | ms  |

| Z <sub>FB_IN</sub>               | FB Input Impedance                                                        |                                         |      | 4   |      | kΩ  |

| $V_{ m skip}$                    | FB Under Voltage Gate Clock is OFF                                        |                                         |      | 2.2 |      | V   |

| Current Sen                      | ase Input Section (CS Pin)                                                |                                         |      |     |      |     |

| Soft Start<br>Time               |                                                                           |                                         |      | 4   |      | ms  |

| $T_{LEB}$                        | CS Input Leading Edge Blanking Time                                       |                                         |      | 270 |      | ns  |

| Z <sub>CS_IN</sub>               | CS Input Impedance                                                        |                                         |      | 40  |      | kΩ  |

| V <sub>cs(max)</sub>             | Current limiting threshold                                                |                                         | 0.78 | 0.8 | 0.83 | V   |

| Td_oc                            | Over Current Detection and<br>Control Delay                               |                                         |      | 120 |      | ns  |

| Oscillator So                    | ection                                                                    |                                         |      |     |      |     |

| Fosc                             | Normal Oscillation Frequency                                              |                                         | 108  | 118 | 128  | kHz |

| ΔF(shuffle)<br>/F <sub>OSC</sub> | Frequency Shuffling Range                                                 |                                         | -4   |     | 4    | %   |

| ΔF_Temp                          | Frequency temperature stability                                           |                                         |      | 5   |      | %   |

| ΔF_VDD                           | The stability of frequency and voltage                                    |                                         |      | 5   |      | %   |

| D <sub>MAX</sub>                 | Maximum Switching Duty Cycle                                              | $V_{CS}=0V, V_{FB}=3.3V$                | 70   | 80  | 90   | %   |

| F <sub>Bust</sub>                | Burst Mode Base Frequency                                                 |                                         |      | 22  |      | kHz |

| Constant Cu                      | Constant Current (CC) & Constant Power (CP) control of intelligent switch |                                         |      |     |      |     |

| V <sub>CC-CV</sub>               | Switch V <sub>DD</sub> limiting threshold                                 |                                         | 9    |     | 10   | V   |

| V <sub>HYS</sub>                 | Switching V <sub>DD</sub> hysteresis                                      |                                         |      | 0.5 |      | V   |

| Power MOS                        | Power MOSFET Section (DRAIN Pin)                                          |                                         |      |     |      |     |

| V <sub>ds_max</sub>              | Maximum Drain-Source Voltage                                              | Vgs=-25V                                | 700  |     |      | V   |

| I <sub>d</sub>                   | Continuous drain-source current                                           | Tj=150°C                                |      | 6.3 |      | A   |

| R <sub>DS(ON)</sub>              | Drain-source on-resistance                                                | Vgs=0V,Ids=3A,Tj=25°C                   |      | 0.4 | 0.48 | Ω   |

|                                  |                                                                           |                                         |      |     |      |     |

### **Applications Information**

#### **Functional Description**

AS8864EM is an integrated D-GaN HEMT high-performance power switch designed for off-line flyback power supplies. It is suitable for applications such as fast charging, motor drive power supplies, power adapters, and general-purpose switching power supplies.

#### System startup current and operating current

Before the chip starts to operate, the AS8864EM only consumes a startup current with a typical value of 5uA. The ultra-low startup current can help increase the resistance value of the startup resistor, aiming to reduce the current flowing through the startup resistor from the DC bus and the standby power consumption. When the VDD voltage exceeds the turn-on voltage (a typical value of 14.5V), the AS8864EM starts to operate and the operating current of the chip rises to 1.6mA (a typical value). After that, the VDD capacitor continuously supplies power to the chip until the output voltage is established, and then the auxiliary winding supplies power to the chip.

#### Soft start

The AS8864EM has an internally integrated soft-start function with a typical value of 4ms. This function is achieved by gradually increasing the over-current protection threshold cycle by cycle during the startup phase. This is beneficial for avoiding the saturation of the transformer and reducing the stress on the secondary side diodes. Each system restart will be accompanied by a soft-start process.

#### Oscillator with frequency dithering function

Inside the AS8864EM, the PWM switching frequency is strictly fixed at 118kHz through calibration. To improve the system's EMI performance, the chip is equipped with a frequency dithering function within a  $\pm 4\%$  range.

#### Green energy - saving operation mode

In light - load and no - load conditions, the system's losses mainly come from the switching losses that are proportional to the switching frequency. Therefore, to meet the requirements of green energy - saving, it is necessary to reduce the number of switching cycles by means of hiccup mode or reducing the switching frequency to improve the system's average operating efficiency.

#### Hiccup mode

When the load is extremely small, the system enters the hiccup mode. Under light - load or no - load conditions, most of the power consumption in the switching - mode power supply comes from the switching

losses on the D - GaN HEMT, the core losses of the transformer, and the losses on the snubber circuit. The power loss is proportional to the switching frequency. A lower switching frequency leads to a reduction in power loss, thus saving energy. The switching frequency is internally adjusted under no - load or light - load conditions. The gate drive output will only switch when the VDD voltage drops below the preset level and the FB input is active to output an on - state. Otherwise, the gate driver remains in the off - state to minimize switching losses and maximize standby power savings. The switching frequency control also eliminates audio noise under any load conditions.

#### **Leading - edge blanking (LEB)**

Due to the problems of the integrated capacitance of the primary - side D - GaN HEMT and the reverse recovery of the secondary - side output diode, a voltage spike is generated on the sampling resistor when the integrated D - GaN HEMT is turned on. To prevent the GATE signal from being incorrectly turned off, the chip integrates a leading - edge blanking function. During this period (typically 270ns), the PWM comparator stops working and the GATE output is not allowed to turn off.

#### Internal synchronous slope compensation

For traditional current - mode control, the key is to avoid system stability problems when the duty cycle exceeds 50% in continuous mode. The AS8864EM internally implements slope compensation by superimposing a slope voltage on the sampled voltage signal, which greatly increases the system's stability in continuous mode, avoids sub - harmonic oscillations, and reduces the output voltage ripple.

#### VDD over - voltage protection (OVP) and clamping

When the VDD voltage exceeds 58.5V (typical value), the chip stops switching operations. When the VDD voltage drops and is lower than the turn - off voltage  $V_{UVLO\_ON}$  (typical value 7.5V), the system restarts. The chip also integrates a Zener diode, which effectively prevents damage to the chip.

#### Soft drive

The drive circuit of the AS8864EM, through its internal totem - pole drive structure, appropriate gate drive capability, and dead - time control, effectively reduces the cross - over losses during the turn - on process, improves efficiency, and enhances the system's reliability. The soft - drive function balances the problem of strong EMI interference that may occur when the gate drive capability is too strong.

#### **Protection functions**

The AS8864EM has multiple built - in protections, including cycle - by - cycle current - limit protection (OCP), over - voltage protection (OVP), VDD over - voltage clamping, under - voltage protection (UVLO), over - temperature protection (OTP), etc.

Integrated D-GaN HEMT Offline Current-Mode Controlled Power Switch

The AS8864EM has a built - in line - voltage compensation function for the current - limit point. Through a specially designed circuit structure, it can ensure that the current - limit point remains constant within the full operating voltage range, thus ensuring constant power.

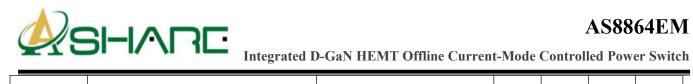

#### **PCB Design suggestions**

- It is recommended that the photocoupler power supply resistor should not pass through the hole, and the distance from the positive terminal wiring should be as short as possible.

- It is recommended to reserve a capacitor position in the first foot of light lotus power supply.

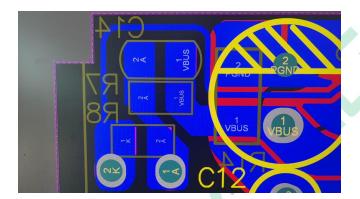

# **Package Dimension**

ESOP-7

**Revision History**

| Date       | Revision | Description                    |  |

|------------|----------|--------------------------------|--|

| 2024/10/17 | 1.0      | Initial Version                |  |

| 2025/5/15  | 1.1      | Update the content description |  |

#### **Disclaimer**

Information that is provided by A-share Tech. is believed to be accurate and reliable. A-share Tech. reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating A-share Tech. products into any application. No legal responsibility for any said applications is assumed by A-share Tech.