## 8 通道, 16 位, 双极性输入同步采样 ADC

### 特性

- 8 路同步采样输入

- 双极性模拟输入范围:  $\pm 10V, \pm 5V$

- 5V 单模拟电源,  $V_{DRIVE}$ : 2.3V to 5V

- 全集成的数据采集解决方案

- 模拟输入钳位保护

- 具有  $1M\Omega$  模拟输入阻抗的输入缓冲器

- 二阶抗混叠模拟滤波器

- 片上精密基准电压及缓冲电路

- 16 位、200kSPS ADC (所有通道)

- 数字滤波提供过采样功能

- 灵活的并行/串行接口

- 模拟输入通道提供 8kV ESD 保护

- 87dB SNR, -91dB THD

- 低功耗: 110mW

- 待机功耗: 35mW

- 工作温度范围: -40°C to +85°C

- 64 引脚 LQFP 封装

### 概述

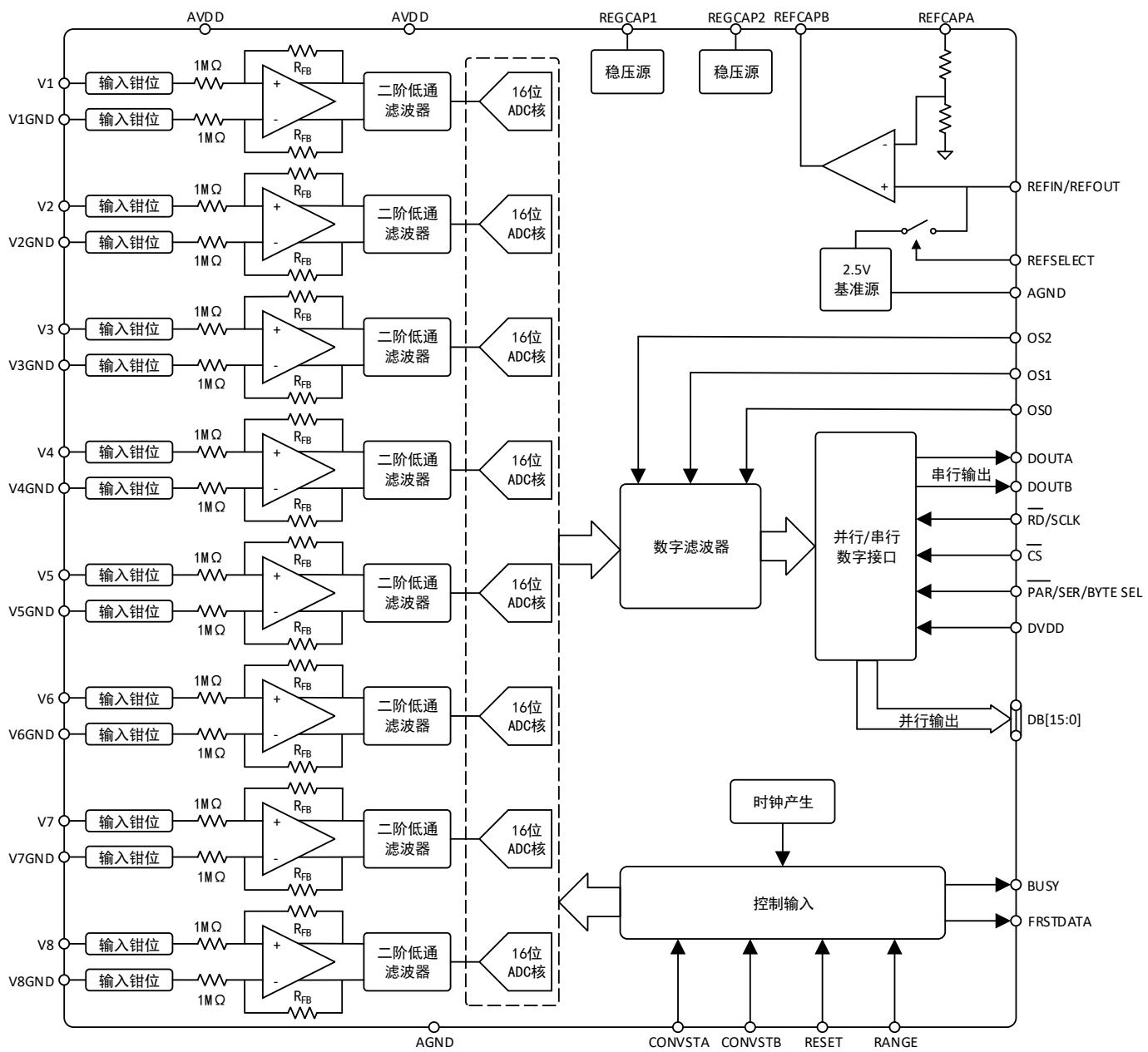

[AD7606](#) 是 16 位、8 通道同步采样的模数转换器芯片。AD7606 内置了模拟输入钳位保护、二阶抗混叠滤波器、跟踪保持放大器、16 位电荷再分配逐次逼近型模数转换器、灵活的数字滤波器、2.5V 基准电压源、基准电压缓冲以及高速串行和并行接口。

AD7606 采用 5V 单电源供电, 可以处理  $\pm 10V$  和  $\pm 5V$  真双极性输入信号, 所有通道均能以高达 200kSPS 的吞吐率采样。输入钳位保护电路可以耐受最高  $\pm 16.5V$  的电压。无论以何种采样频率工作, AD7606 的模拟输入阻抗均为  $1M\Omega$ 。AD7606 采用单电源工作, 具有片内滤波和高的输入阻抗, 因此无需外置运算放大器和双极性电源。AD7606 抗混叠滤波器的 3dB 截止频率为 22kHz, 在 200kSPS 采样率下, 它具有 40dB 的抗混叠抑制特性。灵活的数字滤波器采用引脚驱动, 可以改善信噪比。

### 应用

- 电力线监控和保护系统

- 多相电机控制

- 仪表和控制系统

- 多轴定位系统

- 数据采集系统 (DAS)

### 功能结构框图

图 1. AD7606 功能框图

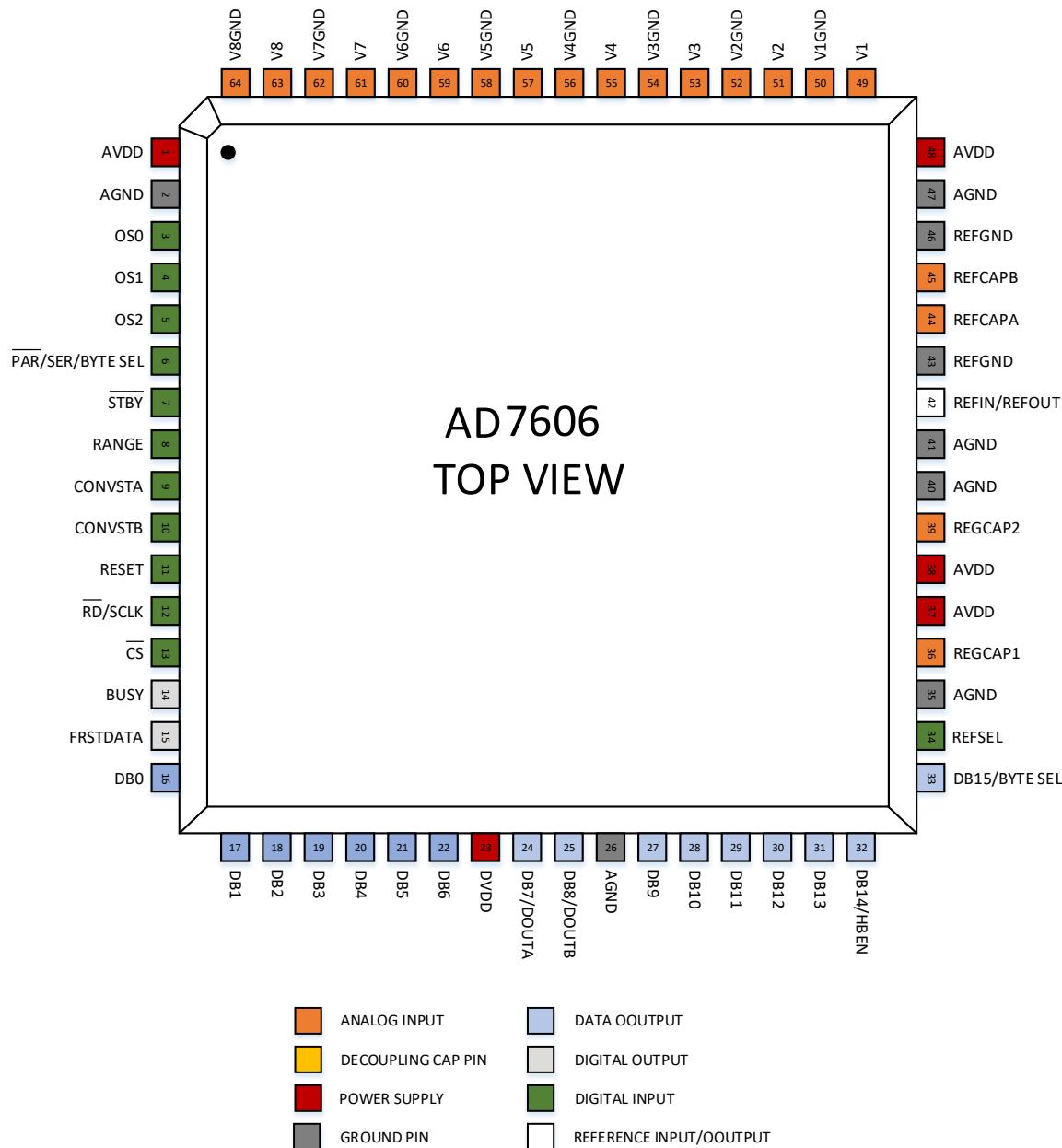

## 引脚配置

图2. AD7606 引脚配置图

表 1. 引脚功能

| 引脚编号       | 类型 <sup>1</sup> | 引脚名称 | 功能描述                                                              |

|------------|-----------------|------|-------------------------------------------------------------------|

| 1,37,38,48 | P               | AVDD | 模拟电源电压, 4.75V 至 5.25V。这是内部前端放大器和 ADC 内核的电源电压。应将这些电源引脚去耦合连接至 AGND。 |

| 引脚编号             | 类型 <sup>1</sup> | 引脚名称             | 功能描述                                                                                                                                                                    |

|------------------|-----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2,26,35,40,41,47 | P               | AGND             | 模拟参考地。这些引脚是 AD 7606 所有模拟电路的参考地，都应当连接到系统的 AGND 平面。                                                                                                                       |

| 5,4,36           | DI              | OS[2:0]          | 过采样模式引脚。逻辑输入。这些输入引脚用来选择过采样的倍数。                                                                                                                                          |

|                  | DI              | PAR/SER/BYTE SEL | 并行/串行/字节接口选择输入。该引脚为逻辑低电平，则选择并行接口；该引脚为逻辑高电平，则选择串行接口；该引脚为逻辑高电平，而且 DB15/BYTE SEL 也为逻辑高电平，则选择并行字节接口模式。                                                                      |

| 7                | DI              | STBY             | 待机模式输入。该引脚为逻辑低电平时，AD7606 进入两种省电模式之一：待机模式或者关断模式。具体进入何种模式取决于 RANGE 引脚的逻辑状态。                                                                                               |

| 8                | DI              | RANGE            | 模拟输入范围选择。该引脚的逻辑状态决定了模拟输入通道的输入范围。该引脚为逻辑高电平，则所有通道的模拟输入范围是±10V；该引脚为逻辑低电平，则所有通道的模拟输入范围是±5V；该引脚的逻辑状态会立刻影响模拟输入范围，建议不要在转换过程中改变该引脚的状态。                                          |

| 9,10             | DI              | CONVSTA, CONVSTB | 转换开始输入 A 和转换开始输入 B。该引脚用来启动模拟输入通道的数据转换。将 CONVSTA 和 CONVSTB 引脚短接在一起，施加满足 t2 时序的低电平脉宽，即可同步启动 8 个通道的数据采样。                                                                   |

| 11               | DI              | RESET            | 复位。当该引脚为逻辑高电平时，上升沿复位 AD7606。AD7606 应该在上电后收到一个 RESET 脉冲，脉冲宽度典型值 50nS。如果在转换期间施加 RESET 脉冲，转换将立刻中断。如果在读取数据期间施加 RESET 脉冲，输出寄存器的内容将复位至 0。                                     |

| 12               | DI              | RD/SCLK          | 并行数据读取控制/串行通信的时钟输入。在并行通信模式下，CS 和 RD 均为逻辑低电平会启动总线输出。串行通信模式下，该引脚用作数据输出的串行时钟输入。                                                                                            |

| 13               | DI              | CS               | 片选。该引脚的低电平使能数据帧的传输。在并行通信模式下，CS 和 RD 均为逻辑低电平会启动总线输出。在串行通信模式下，该引脚的下降沿使数据输出线路 DOUTA 和 DOUTB 脱离三态，并逐个输出转换结果的 MSB。                                                           |

| 14               | DO              | BUSY             | 输出繁忙。CONVSTA 和 CONVSTB 均达到上升沿之后，该引脚变为逻辑高电平，表示转换过程已经开始。该引脚输出保持高电平，直到所有的通道的转换完成为止。该引脚的下降沿表示转换数据正被锁存至输出数据寄存器。                                                              |

| 15               | DO              | FRSTDATA         | 该引脚指示何时在并行、字节或者串行接口上读取第一通道 V1 的转换数据。                                                                                                                                    |

| 16~22            | DO              | DB[6:0]          | 并行输出数据位 DB6 至 DB0。                                                                                                                                                      |

| 23               | P               | DVDD             | 逻辑电源输入。该引脚的电源电压决定了逻辑接口的工作电压。该引脚的标称电源和主机接口的电源应该相同。                                                                                                                       |

| 24               | DO              | DB7/DOUT A       | 并行输出数据位 DB7/串行接口数据输出引脚 DOUTA。                                                                                                                                           |

| 25               | DO              | DB8/DOUT B       | 并行输出数据位 DB8/串行接口数据输出引脚 DOUTB。                                                                                                                                           |

| 27~31            | DO              | DB[13:9]         | 并行输出数据为 DB13 至 DB9。                                                                                                                                                     |

| 32               | DO              | DB14/HBE N       | 并行输出数据为 14/高字节使能。当 PAR/SER/BYTE SEL = 0 时，该引脚充当三态并行数字输出引脚。当 CS = 0 而且 RD = 0 时，该引脚用来输出转换结果的 DB14。当 PAR/SER/BYTE SEL = 1 时，AD7606 工作在并行字节接口模式，该引脚用来选择是首先输出转换结果的高字节还是低字节。 |

| 33               | DO/DI           | DB15/BYTE SEL    | 并行输出数据为 15/并行字节模式选择。当 PAR/SER/BYTE SEL = 0 时，该引脚充当三态并行数字输出引脚。当 CS = 0 而且 RD = 0 时，该引脚用来输出转换结果的 DB15。当 PAR/SER/BYTE SEL = 1 时，该引脚用来选择串行接口模式或者并行字节接口模式。                   |

AI = 模拟输入

P = 电源

DI = 数字输入

DO = 数字输出

REF = 基准电压输入/输出

| 引脚编号  | 类型 <sup>1</sup> | 引脚名称                | 功能描述                                                                                                                         |

|-------|-----------------|---------------------|------------------------------------------------------------------------------------------------------------------------------|

| 34    | DI              | REF_SELECT          | 内部/外部基准电压选择输入。该引脚为逻辑高电平，则选择并使能内部基准电压模式；该引脚为逻辑低电平，则内部基准电压禁用，必须将外部的基准电压施加到REFIN/REFOUT引脚。                                      |

| 36,39 | P               | REGCAP1,R<br>EGCAP2 | 内部1.5V和4.2V稳压器输出电压去耦电容引脚。这两个引脚应分别通过1uF的陶瓷电容去耦至AGND。                                                                          |

| 42    | REF             | REFIN/REF<br>OUT    | 基准电压输入/基准电压输出。如果REF SELECT引脚为逻辑高电平，该引脚将提供2.5V片内基准电压供外部实用。如果REF SELECT引脚为逻辑低电平，该引脚可以连接外部的2.5V基准电压。该引脚需要连接10uF陶瓷电容去耦至REFGND引脚。 |

| 43,46 | REF             | REFGND              | 基准电压接地引脚。这些引脚应当连接到AGND。                                                                                                      |

| 44,45 | REF             | REFCAPA,<br>REFCAPB | 基准电压缓冲输出强制/检测引脚。这些引脚必须连接在一起，并通过低ESR的10uF的此片电容去耦合至AGND。这些引脚上的电压通常为4.5V。                                                       |

| 49    | AI              | V1                  | 1通道模拟输入。该引脚为单端模拟输入，输入范围由RANGE引脚决定。                                                                                           |

| 50    | AI GND          | V1 GND              | 1通道模拟输入参考地。该引脚应连接到系统的AGND平面。                                                                                                 |

| 51    | AI              | V2                  | 2通道模拟输入。该引脚为单端模拟输入，输入范围由RANGE引脚决定。                                                                                           |

| 52    | AI GND          | V2 GND              | 2通道模拟输入参考地。该引脚应连接到系统的AGND平面。                                                                                                 |

| 53    | AI              | V3                  | 3通道模拟输入。该引脚为单端模拟输入，输入范围由RANGE引脚决定。                                                                                           |

| 54    | AI GND          | V3 GND              | 3通道模拟输入参考地。该引脚应连接到系统的AGND平面。                                                                                                 |

| 55    | AI              | V4                  | 4通道模拟输入。该引脚为单端模拟输入，输入范围由RANGE引脚决定。                                                                                           |

| 56    | AI GND          | V4 GND              | 4通道模拟输入参考地。该引脚应连接到系统的AGND平面。                                                                                                 |

| 57    | AI              | V5                  | 5通道模拟输入。该引脚为单端模拟输入，输入范围由RANGE引脚决定。                                                                                           |

| 58    | AI GND          | V5 GND              | 5通道模拟输入参考地。该引脚应连接到系统的AGND平面。                                                                                                 |

| 59    | AI              | V6                  | 6通道模拟输入。该引脚为单端模拟输入，输入范围由RANGE引脚决定。                                                                                           |

| 60    | AI GND          | V6 GND              | 6通道模拟输入参考地。该引脚应连接到系统的AGND平面。                                                                                                 |

| 61    | AI              | V7                  | 7通道模拟输入。该引脚为单端模拟输入，输入范围由RANGE引脚决定。                                                                                           |

| 62    | AI GND          | V7 GND              | 7通道模拟输入参考地。该引脚应连接到系统的AGND平面。                                                                                                 |

| 63    | AI              | V8                  | 8通道模拟输入。该引脚为单端模拟输入，输入范围由RANGE引脚决定。                                                                                           |

| 64    | AI GND          | V8 GND              | 8通道模拟输入参考地。该引脚应连接到系统的AGND平面。                                                                                                 |

## 技术规格

### 最大额定值

表 2.

| 参数              | 额定值                 |

|-----------------|---------------------|

| AVDD 至 AGND     | -0.3 V 至 +7.0 V     |

| DVDD 至 AGND     | -0.3 V 至 AVDD+0.3 V |

| 模拟输入电压至 AGND    | $\pm 16.5V$         |

| 数字输入电压至 AGND    | -0.3 V 至 DVDD+0.3 V |

| 数字输出电压至 AGND    | -0.3 V 至 DVDD+0.3 V |

| REFIN 至 ANGD    | -0.3 V 至 AVDD+0.3 V |

| 输入电流至除电源外的其它引脚  | $\pm 10 \text{ mA}$ |

| 工作温度范围          | -40°C 至 +85°C       |

| 存储温度范围          | -55°C 至 +150°C      |

| 结温              | 150°C               |

| 模拟输入引脚 ESD      | $\pm 8 \text{ kV}$  |

| 除模拟输入以外其它引脚 ESD | $\pm 4 \text{ kV}$  |

注意，超出上述最大额定值可能会导致器件永久性的损坏。这只是额定应力值，不涉及器件在这些或者任何其它条件下超出本技术规格指标的功能性操作。长期在最大额定值条件下工作会影响器件的可靠性。

### ESD 警告

#### ESD (静电放电) 敏感器件

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有保护电路，但在遇到高能量 ESD 事件时，器件可能会损坏。因此，应当采用适当的 ESD 防范措施，以避免器件性能的下降或者功能丧失。

### 热阻

热阻参数和 PCB 板的设计以及工作环境强相关。

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{JC}$  is the junction to case thermal resistance.

表 3. 热阻

| 封装形式         | $\theta_{JA}$ | $\theta_{JC(TOP)}$ | Unit |

|--------------|---------------|--------------------|------|

| 64-Lead LQFP | 45            | 11                 | °C/W |

### 电气指标

AVDD = 4.75~5.25 V, DVDD = 2.3~5.25 V,  $f_{SAMPLE}$  = 200kSPS,  $T_a$  = -40°C 至 +85°C。

**表 4.**

| 参数             | 测试条件                                      | 最小值   | 典型值     | 最大值      | 单位         |

|----------------|-------------------------------------------|-------|---------|----------|------------|

| 电源             |                                           |       |         |          |            |

| AVDD           |                                           | 4.75  | 5.0     | 5.25     | V          |

| DVDD           |                                           | 2.3   | 3.3     | 5.25     | V          |

| 供电电流           |                                           |       |         |          | mA         |

| 正常模式           | 无采样                                       | 16    | 19      | 21       | mA         |

|                | 200kSPS 采样                                | 18    | 21      | 23       | mA         |

| 待机模式           |                                           | 6     | 7       | 8        | mA         |

| 关断模式           |                                           |       | 10      |          | uA         |

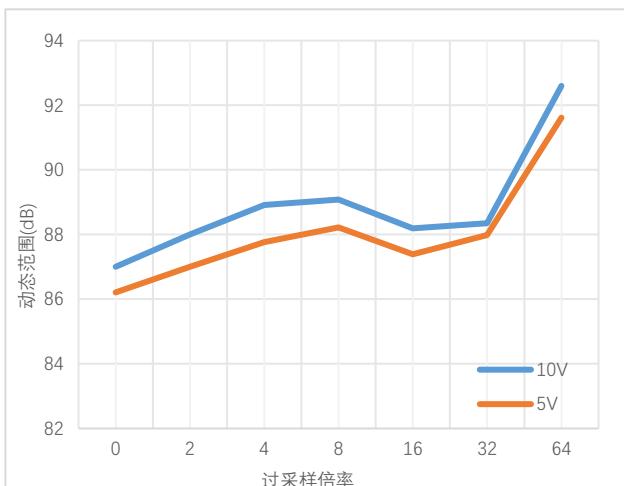

| 动态性能           |                                           |       |         |          |            |

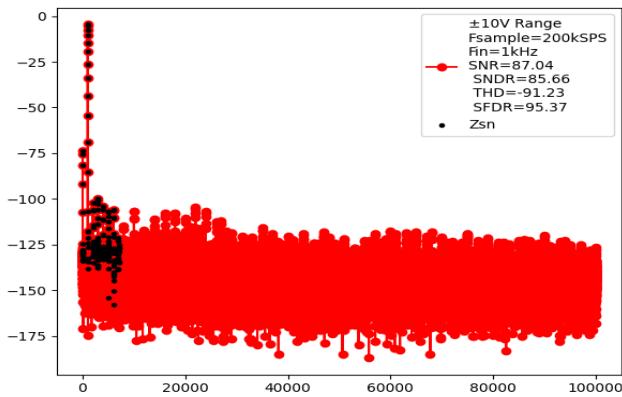

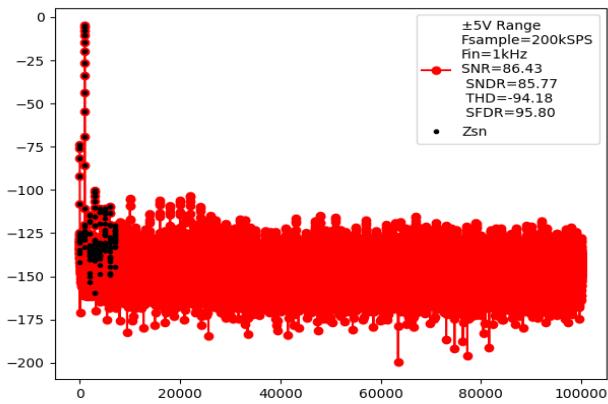

| 信噪比 (SNR)      | 无过采样; $\pm 10V$ 输入范围;                     | 83    | 87      | 87.5     | dB         |

|                | 无过采样; $\pm 5V$ 输入范围;                      | 83    | 86      | 86.5     | dB         |

|                | 64 倍过采样; $\pm 10V$ 输入范围; $f_{IN} = 130Hz$ | 87    | 90      | 91       | dB         |

|                | 64 倍过采样; $\pm 5V$ 输入范围; $f_{IN} = 130Hz$  | 87    | 90      | 91       | dB         |

| 信纳比 (SINAD)    | 无过采样; $\pm 10V$ 输入范围;                     | 83    | 84.5    | 85.5     | dB         |

|                | 无过采样; $\pm 5V$ 输入范围;                      | 83    | 84      | 85       | dB         |

| 总谐波失真 (THD)    | 无过采样; $\pm 10V$ 输入范围;                     | -89   | -91     | -94      | dB         |

|                | 无过采样; $\pm 5V$ 输入范围;                      | -90   | -92     | -96      | dB         |

| 无杂散动态范围 (SFDR) | 无过采样; $\pm 10V$ 输入范围;                     | 90    | 95      | 97       | dB         |

|                | 无过采样; $\pm 5V$ 输入范围;                      | 90    | 95      | 100      | dB         |

| 动态范围           | 无过采样; $\pm 10V$ 输入范围;                     |       | 87      |          | dB         |

|                | 无过采样; $\pm 5V$ 输入范围;                      |       | 86      |          | dB         |

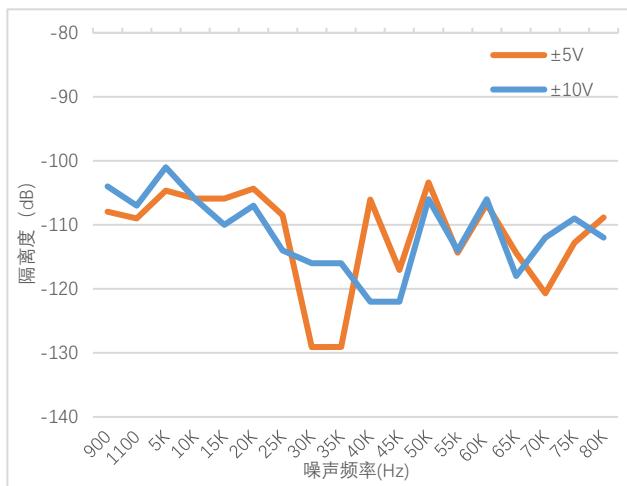

| 通道间隔离度         | 未选中通道的 $0Hz < f_{IN} < 80kHz$             |       | -108    |          | dB         |

| 直流精度           |                                           |       |         |          |            |

| 分辨率            |                                           | 16    |         |          | Bits       |

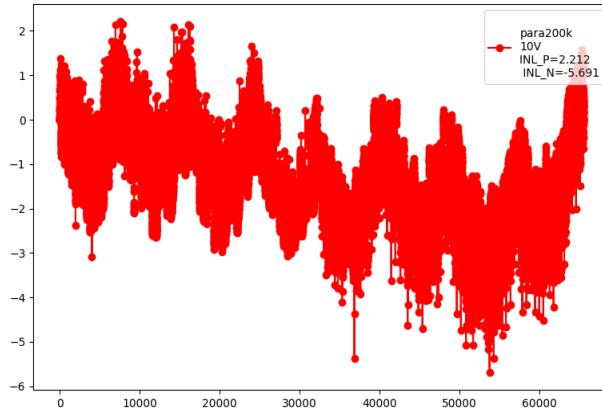

| 微分非线性          |                                           |       | -1/3.5  | -1/8     | LSB        |

| 积分非线性          |                                           |       | $\pm 6$ | $\pm 10$ | LSB        |

| 增益误差           |                                           |       | $\pm 2$ | $\pm 15$ | LSB        |

| 失调误差           |                                           |       | $\pm 1$ | $\pm 5$  | LSB        |

| 模拟输入           |                                           |       |         |          |            |

| 输入电压范围         | RANGE = 1                                 |       |         | $\pm 10$ | V          |

|                | RANGE = 0                                 |       |         | $\pm 5$  | V          |

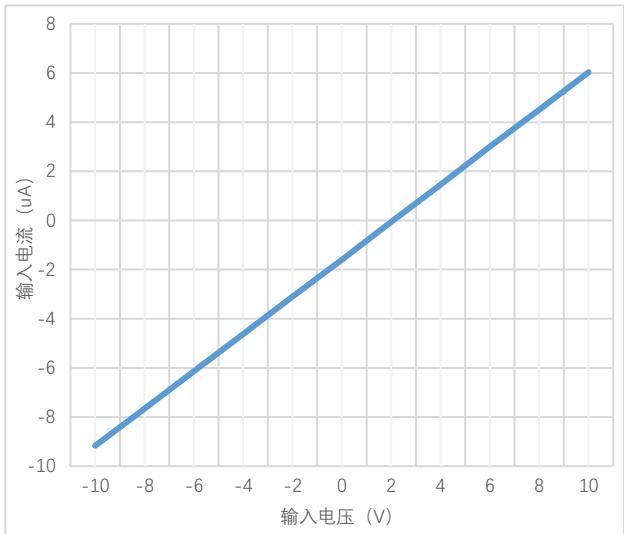

| 模拟输入电流         | 10V                                       |       | 6.01    |          | uA         |

|                | 5V                                        |       | 2.24    |          | uA         |

| 输入阻抗           |                                           |       | 1       |          | M $\Omega$ |

| 模拟输入滤波器        |                                           |       |         |          |            |

| 3dB 带宽         | $\pm 10V$ 输入范围                            |       | 22      |          | kHz        |

|                | $\pm 5V$ 输入范围                             |       | 15      |          | kHz        |

| 整体延时           | $\pm 10V$ 输入范围                            |       | 12      |          | uS         |

|                | $\pm 5V$ 输入范围                             |       | 17.5    |          | uS         |

| 基准输入/输出        |                                           |       |         |          |            |

| 基准输入电压范围       |                                           | 2.475 | 2.5     | 2.525    | V          |

| 参数        | 测试条件                        | 最小值      | 典型值  | 最大值      | 单位      |

|-----------|-----------------------------|----------|------|----------|---------|

| 直流漏电流     |                             |          | 1    |          | uA      |

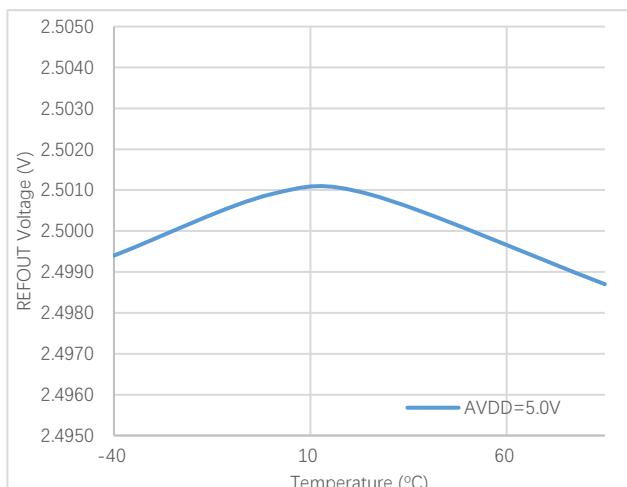

| 基准输出电压    |                             | 2.497    | 2.5  | 2.503    | V       |

| 基准源温度系数   |                             |          | ±6.5 | ±15      | ppm /°C |

| 转换速率      |                             |          |      |          |         |

| 转换时间      |                             |          | 2.9  |          | uS      |

| 采样保持器采集时间 |                             |          | 1    |          | uS      |

| 吞吐速率      |                             |          |      | 200      | kSPS    |

| 逻辑输入      |                             |          |      |          |         |

| 输入高电压     |                             | 0.7xDVDD |      |          | V       |

| 输入低电压     |                             |          |      | 0.3xDVDD | V       |

| 输入电流      |                             |          |      | ±1       | uA      |

| 输入电容      |                             |          |      | 10       | pF      |

| 输出逻辑      |                             |          |      |          |         |

| 输出高电压     | $I_{SOURCE} = 6 \text{ mA}$ | DVDD-0.8 |      |          | V       |

| 输出低电压     | $I_{SINK} = 3 \text{ mA}$   |          |      | 0.5      | V       |

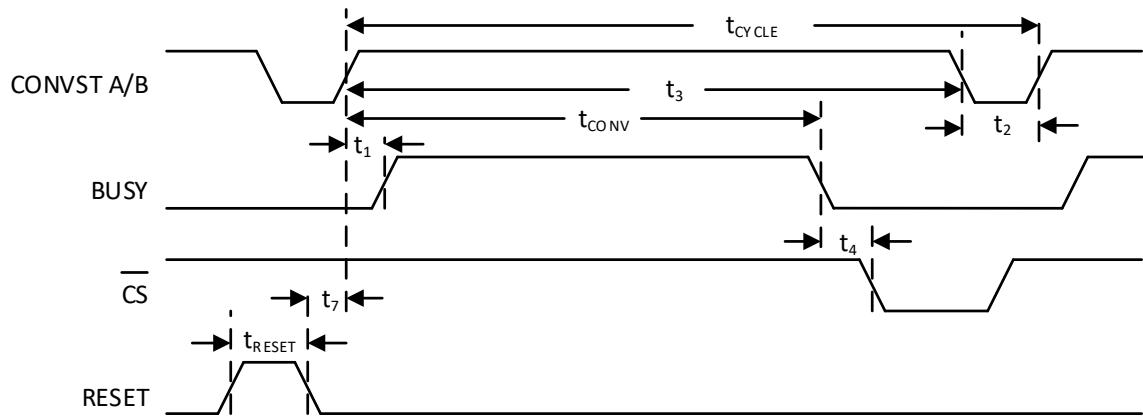

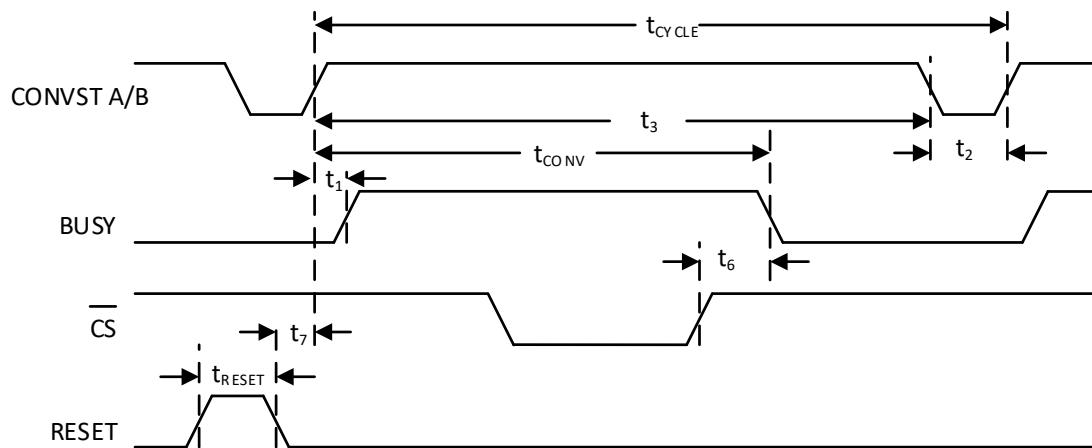

## 时序规格

AVDD = 4.75~5.25 V, DVDD = 3.3 V,  $V_{REF} = 2.5V$  外部 / 内部基准电压,  $T_a = -40^{\circ}\text{C}$  至  $+85^{\circ}\text{C}$ 。

表 5.

| 参数                     | 在 $T_{MIN}, T_{MAX}$ 的限值 |     |      | 单位 | 描述                                                                   |

|------------------------|--------------------------|-----|------|----|----------------------------------------------------------------------|

|                        | 最小值                      | 典型值 | 最大值  |    |                                                                      |

| 并行/串行/字节模式             |                          |     |      |    |                                                                      |

| $t_{CYCLE}$            |                          |     |      |    | 1/吞吐速率                                                               |

|                        | 5                        |     |      | uS | 并行模式, 转换器件或之后读取; 或者串行模式: DVDD=4.75V 至 5.25V, 用 DOUTA 和 DOUTB 在转换期间读取 |

|                        | 10                       |     |      | uS | 串行模式, 转换后读取; DVDD=2.3V, DOUTA 和 DOUTB 线路                             |

| $t_{CONV}$             |                          |     |      |    | 转换时间                                                                 |

|                        | 2.6                      | 2.9 | 3.2  | uS | 过采样关闭                                                                |

|                        | 6.3                      | 7   | 7.7  | uS | 2 倍过采样                                                               |

|                        | 13.5                     | 15  | 16.5 | uS | 4 倍过采样                                                               |

|                        | 28                       | 31  | 34   | uS | 8 倍过采样                                                               |

|                        | 57                       | 63  | 69   | uS | 16 倍过采样                                                              |

|                        | 114                      | 127 | 140  | uS | 32 倍过采样                                                              |

|                        | 229                      | 255 | 280  | uS | 64 倍过采样                                                              |

| $t_{WAKE-UP STANDBY}$  |                          | 100 |      | uS | STBY上升沿到 CONVST x 上升沿; 从待机模式上电的时间。                                   |

| $t_{WAKE-UP SHUTDOWN}$ |                          |     |      |    | STBY上升沿到 CONVST x 上升沿; 从关断模式上电的时间。                                   |

| 内部基准电压                 |                          | 50  |      | mS |                                                                      |

| 外部基准电压                 |                          | 25  |      | mS |                                                                      |

| 参数              | 在 $T_{MIN}$ , $T_{MAX}$ 的限值 |     |     | 单位 | 描述                                  |

|-----------------|-----------------------------|-----|-----|----|-------------------------------------|

|                 | 最小值                         | 典型值 | 最大值 |    |                                     |

| $t_{RESET}$     | 60                          |     |     | nS | RESET 高电平脉冲宽度                       |

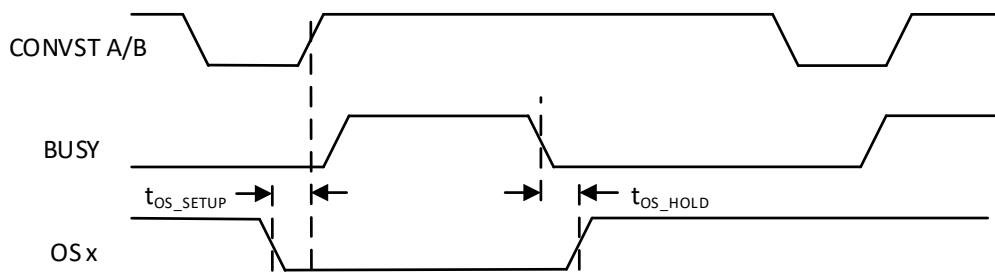

| $t_{OS\_SETUP}$ | 10                          |     |     | nS | OS x 到 CONVSTx 上升沿设置时间              |

| $t_{OS\_hold}$  | 10                          |     |     | nS | BUSY 下降沿到 OS x 保持时间                 |

| $t_1$           |                             | 180 |     | nS | CONVST x 高电平到 BUSY 高电平              |

| $t_2$           | 35                          |     |     | nS | 最短 CONVST x 低电平脉冲                   |

| $t_3$           | 35                          |     |     | nS | 最短 CONVST x 高电平脉冲                   |

| $t_4$           | 40                          |     |     | nS | BUSY 下降沿到 CS 下降沿延时时间                |

| $t_6$           | 40                          |     |     | nS | 最后 CS 上升沿与 BUSY 下降沿之间的最长时间          |

| $t_7$           | 180                         |     |     | nS | RESET 低电平到 CONVST x 高电平之间的最短延迟时间    |

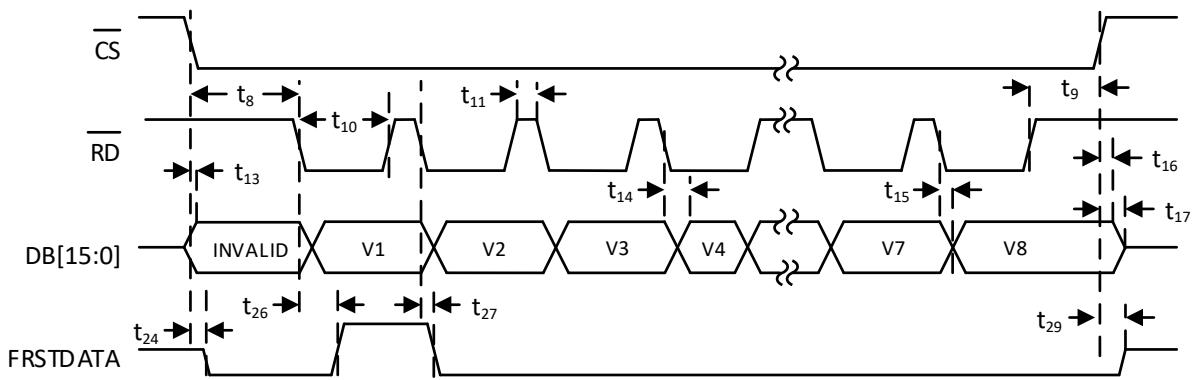

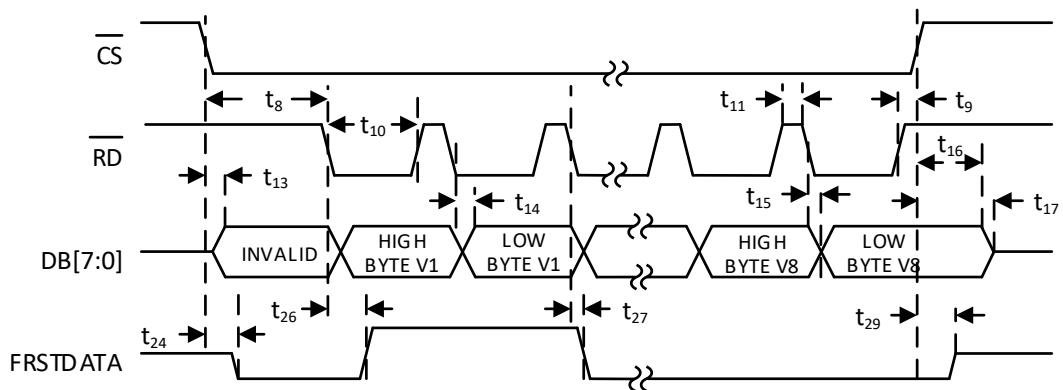

| 并行/字节读取操作       |                             |     |     |    |                                     |

| $t_8$           | 40                          |     |     | nS | CS 到 RD 设置时间                        |

| $t_9$           | 0                           |     |     | nS | CS 到 RD 保持时间                        |

| $t_{10}$        | 40                          |     |     | nS | RD 低电平脉冲宽度                          |

| $t_{11}$        | 15                          |     |     | nS | RD 高电平脉冲宽度                          |

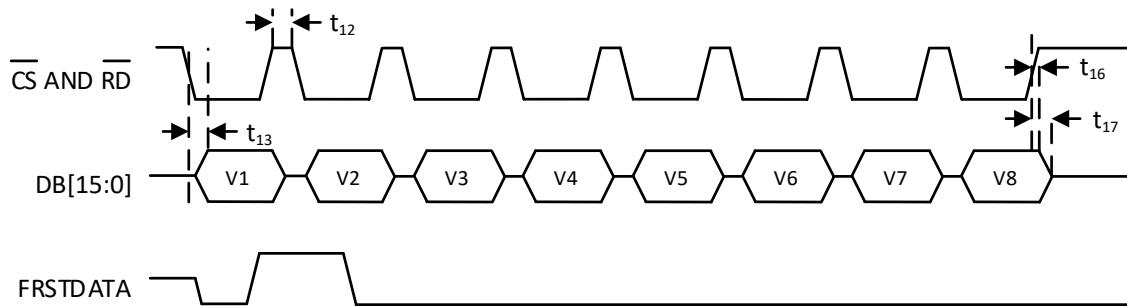

| $t_{12}$        | 20                          |     |     | nS | CS 高电平脉冲宽度; CS 与 RD 相连              |

| $t_{13}$        |                             | 32  |     | nS | CS 到 DB[15: 0] 三态禁用的延迟时间            |

| $t_{14}$        |                             | 34  |     | nS | RD 下降沿后的数据访问时间                      |

| $t_{15}$        | 5                           |     |     | nS | RD 下降沿后的数据保持时间                      |

| $t_{16}$        | 5                           |     |     | nS | CS 到 DB[15:0] 保持时间                  |

| $t_{17}$        |                             | 22  |     | nS | 从 CS 上升沿到 DB[15:0] 三态使能的延迟时间        |

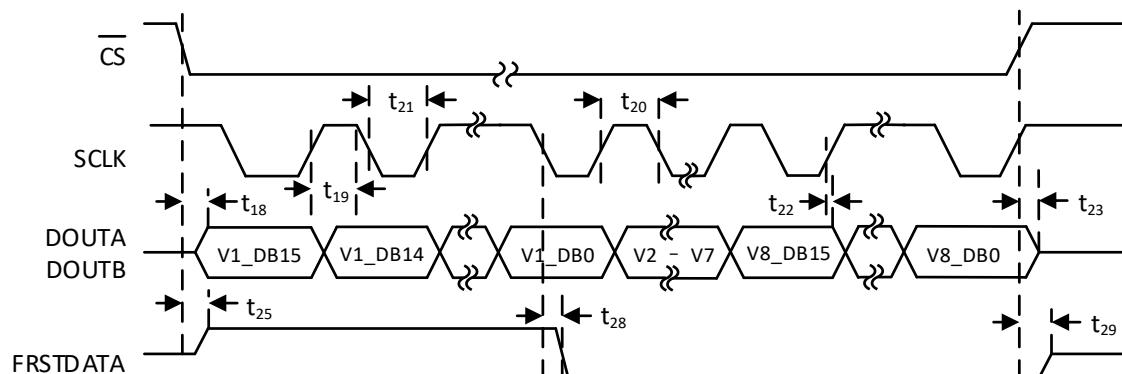

| 串行读取操作          |                             |     |     |    |                                     |

| $f_{SCLK}$      |                             | 25  | MHz |    | 串行读取时钟频率                            |

| $t_{18}$        |                             | 31  | nS  |    | 从 CS 到 DOUTA/DOUTB 三态禁用的延迟时间        |

| $t_{19}$        |                             | 31  | nS  |    | SCLK 上升沿后的数据访问时间                    |

| $t_{20}$        | 0.4xt <sub>SCLK</sub>       |     | nS  |    | SCLK 低电平脉冲宽度                        |

| $t_{21}$        | 0.4xt <sub>SCLK</sub>       |     | nS  |    | SCLK 高电平脉冲宽度                        |

| $t_{22}$        | 5                           |     | nS  |    | SCLK 上升沿到 DOUTA/DOUTB 有效的保持时间       |

| $t_{23}$        |                             | 25  | nS  |    | CS 上升沿到 DOUTA/DOUTB 三态使能            |

| FRSTDATA 操作     |                             |     |     |    |                                     |

| $t_{24}$        |                             | 20  | nS  |    | 从 CS 下降沿到 FRSTDATA 三态禁用的延迟时间        |

| $t_{25}$        |                             | 20  | nS  |    | 从 CS 下降沿到 FRSTDATA 高电平的延迟时间, 串行模式   |

| $t_{26}$        |                             | 20  | nS  |    | 从 RD 下降沿到 FRSTDATA 高电平的延迟时间         |

| $t_{27}$        |                             | 20  | nS  |    | 从 RD 下降沿到 FRSTDATA 低电平的延迟时间         |

| $t_{28}$        |                             | 20  | nS  |    | 从第 16 个 SCLK 下降沿到 FRSTDATA 低电平的延迟时间 |

| $t_{29}$        |                             | 20  | nS  |    | 从 CS 上升沿到 FRSTDATA 三态使能的延迟时间        |

## 时序图

图3 转换时序 (转换后读取数据)

图4 转换时序 (转换间读取数据)

图5 并行接口模式 (独立的CS和RD脉冲)

图6 并行接口模式 ( $\overline{CS}$ 和RD相连)

图7 串行接口模式

图8 并行字节接口模式

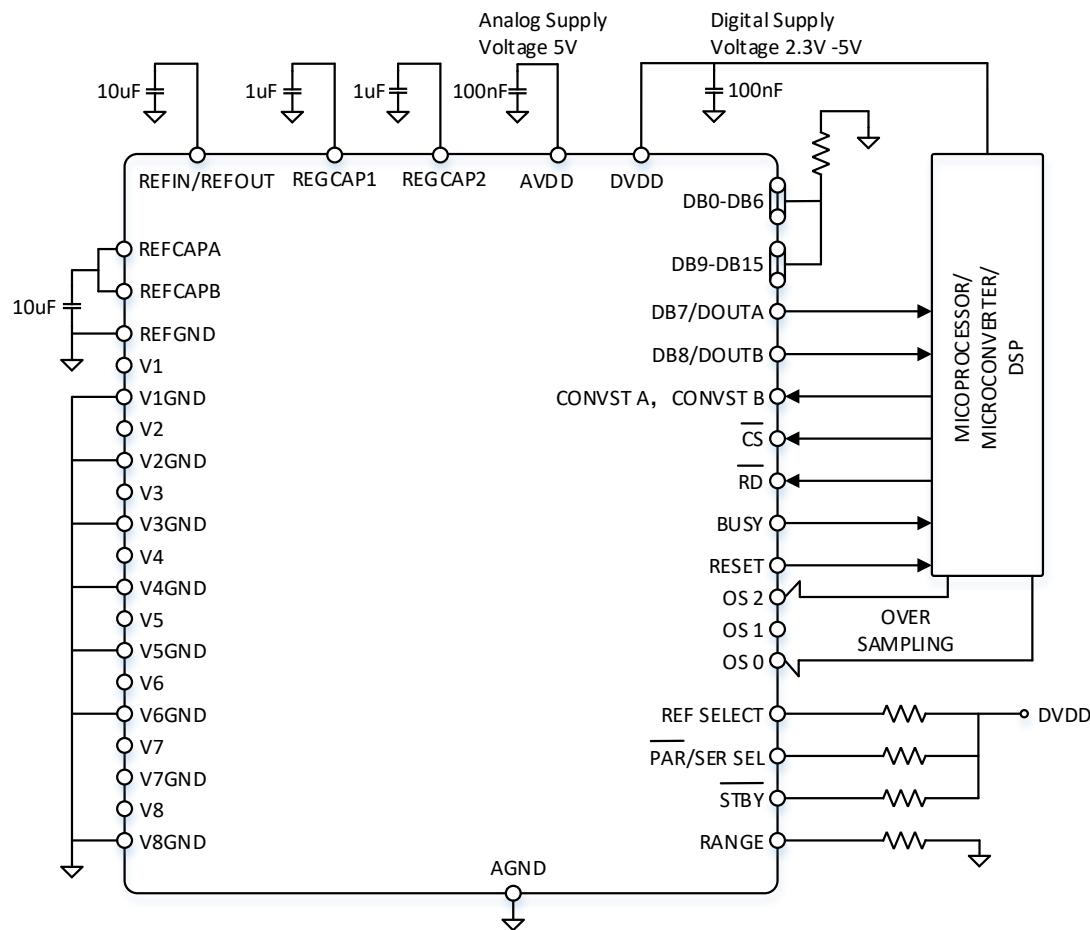

## 典型应用电路

Note: 1) 4 个 AVDD 管脚需要各自独立的去耦电容

2) REGCAP1 和 REGCAP2 需要各自独立的去耦电容

图 9. AD7606 典型应用图 (串行接口)

## 典型工作特性

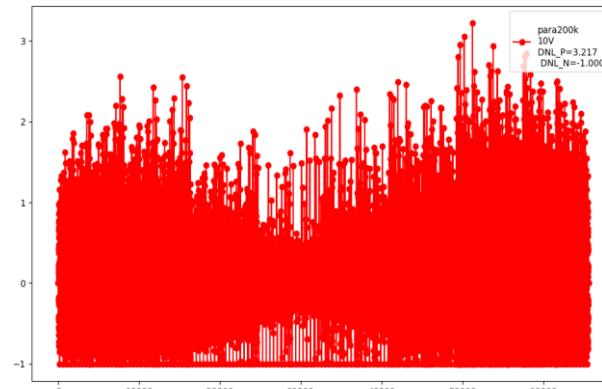

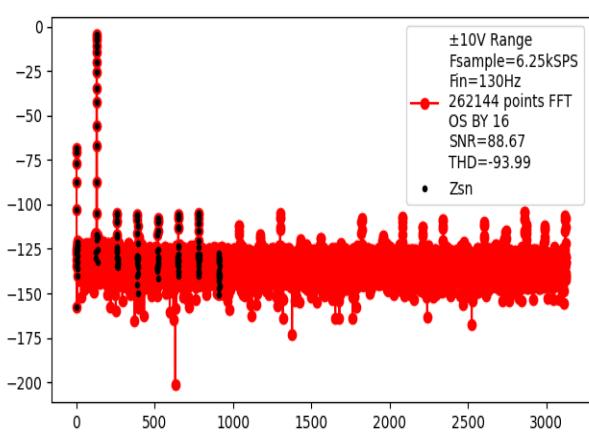

图10 AD7606 FFT,  $\pm 10V$  范围, 并行接口模式, 200kSPS

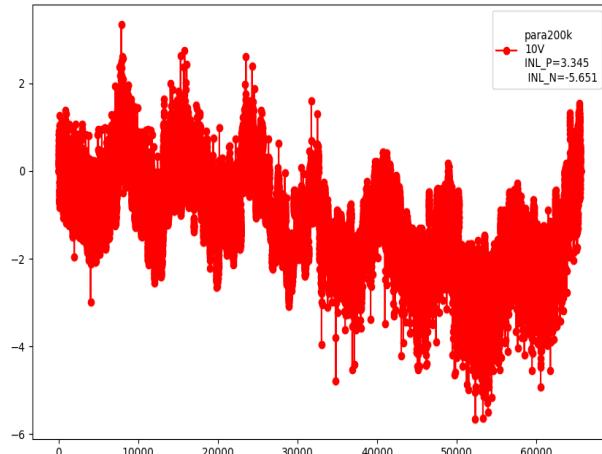

图13. AD7606 典型INL,  $\pm 10V$  范围

图11. AD7606 FFT,  $\pm 5V$  范围, 并行接口模式, 200kSPS

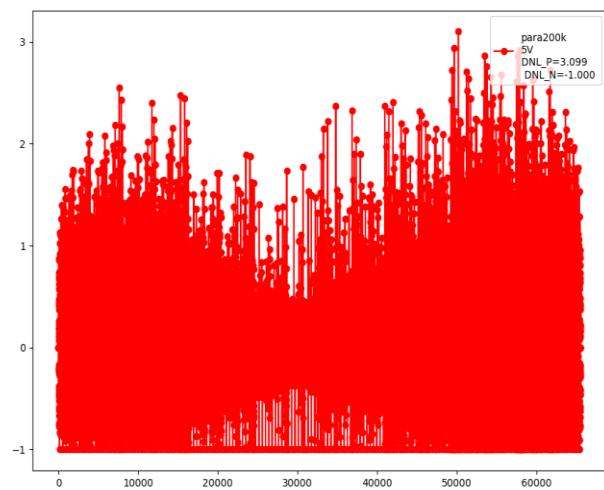

图14. AD7606 典型DNL,  $\pm 10V$  范围

图12. AD7606 FFT,  $\pm 10V$  范围, 并行接口模式, 16 倍过采样

图15 AD7606 典型INL,  $\pm 5V$

图 16 AD7606 典型 DNL,  $\pm 5V$  范围

图 19. 输入电流与模拟输入电压的关系

图 17. 范围通道间隔离度

图 20. 动态范围与过采样倍数的关系

图 18. AD7606 基准电压与温度的关系

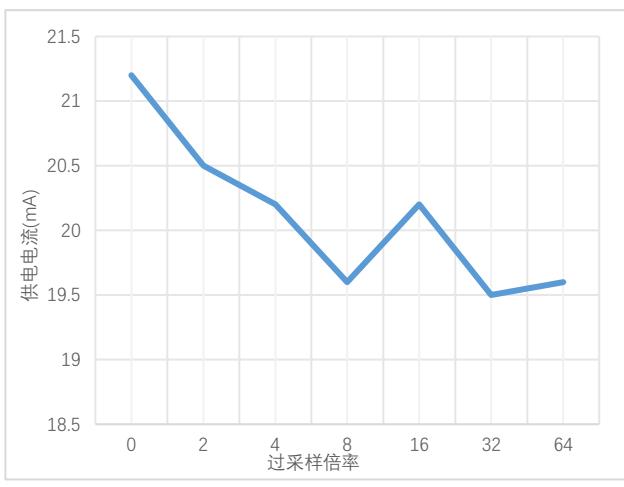

图 21. 供电电流与过采样倍数的关系

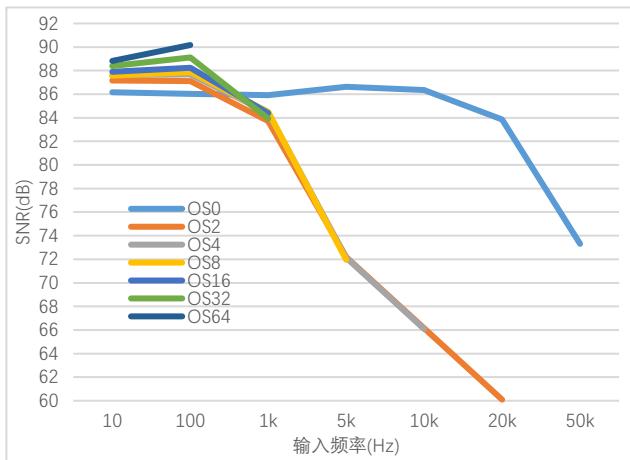

图 22 不同过采样倍数下 SNR 与输入频率的关系,  $\pm 5V$  范围,

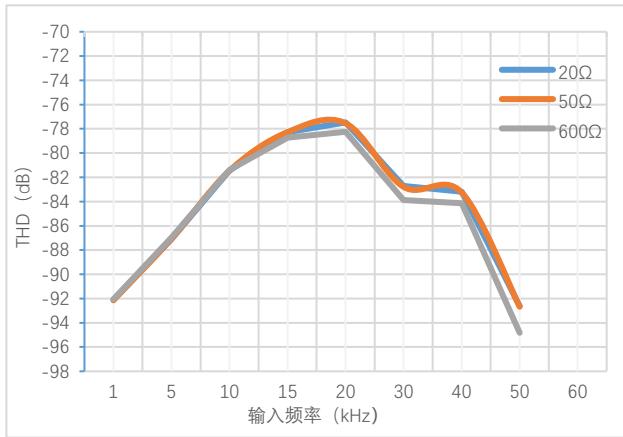

图 24. 各种源阻抗下 THD 与输入频率的关系,  $\pm 5V$  范围

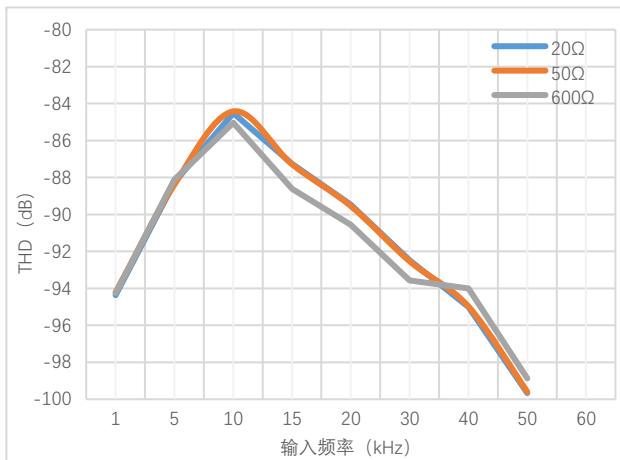

图 23. 各种源阻抗下 THD 与输入频率的关系,  $\pm 10V$  范围

# 工作原理

## 转换器详解

**AD7606** 是采用高速、低功耗、电荷再分配逐次逼近型模数转换器的数据采集系统，可以对 8 个模数输入通道进行同步采样。**AD7606** 采用 5V 的单电源供电，**AD7606** 的模拟输入可以接受真双极性输入信号。用 RANGE 引脚可以选择模拟输入的电压范围。

**AD7606** 内置输入钳位保护电路、输入信号放大电路、二阶抗混叠滤波器、采样保持放大器、片上基准电压源、基准电压缓冲、高速 ADC、数字滤波器以及高速并行和串行接口。**AD7606** 的采样转换通过 CONVST A/B 信号进行使能控制。

## 模拟输入

### 模拟输入范围

**AD7606** 可以处理真双极性、单端输入电压。RANGE 引脚的逻辑电平决定了所有模拟输入通道的输入电压范围。RANGE=1，则所有通道的模拟输入范围为 $\pm 10V$ ；RANGE=0，则所有通道的模拟输入范围为 $\pm 5V$ 。RANGE 引脚的逻辑状态改变会立刻影响模拟输入范围，建议根据系统信号所需的输入范围，通过硬件连线设置 RANGE 引脚。

### 模拟输入阻抗

**AD7606** 的模拟输入阻抗为  $1M\Omega$ ，该阻抗为固定值，不随 **AD7606** 的采样频率而变化。高模拟输入阻抗可以省去 **AD7606** 前端的驱动放大器电路，允许 **AD7606** 和信号源或者传感器直接相连，同时也省去了驱动放大器的双极性供电电源。

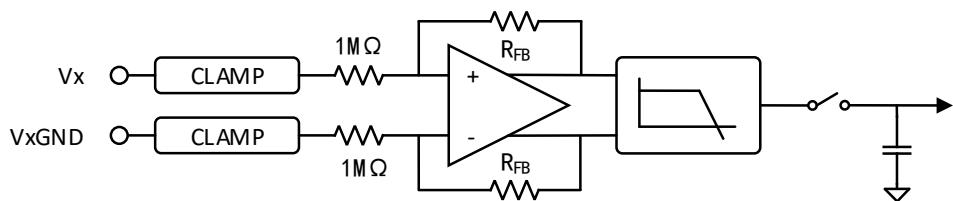

### 模拟输入钳位保护电路

图 25 展示了 **AD7606** 的模拟输入结构，每一路模拟输入均有钳位保护电路。虽然采用 5V 的单电源供电，但是该模拟输入钳位保护电路允许输入过压达到 $\pm 16.5V$ 。

图 25 模拟输入电路

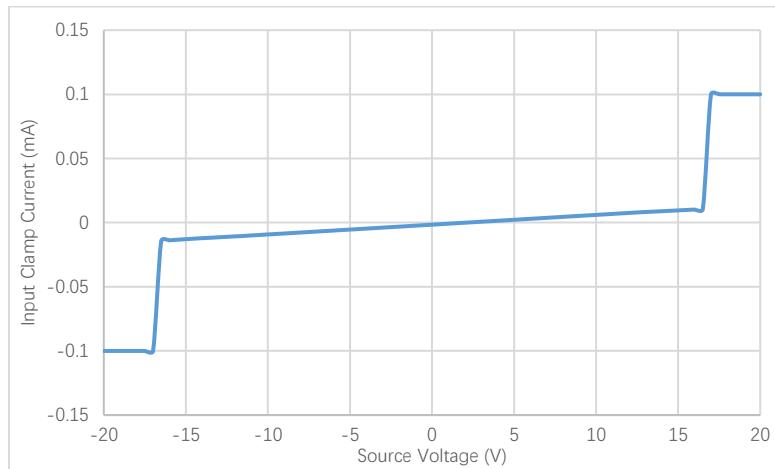

图 26 展示了钳位电路的电源和电流的关系。当输入电压不超过 $\pm 16.5V$  时，钳位电路中无电流。当输入电压超过 $\pm 16.5V$  时，**AD7606** 的钳位电路开启。

图 26 输入钳位保护电路特性

模拟输入通道上应放置一个串联电阻，在输入电压超过 $\pm 16.5V$  时将电流限制在 $\pm 10mA$  以内。如果模拟输入通道  $Vx$  上有串联电阻，则该通道的信号参考地  $VxGND$  上也需要一个对等的电阻，否则该通道将出现输入失调误差。

### 输入模拟抗混叠滤波器

**AD7606** 提供了模拟抗混叠滤波器。在 $\pm 5V$  输入电压范围内，3dB 带宽的典型值为 15kHz；在 $\pm 10V$  的范围内，3dB 带宽典型值为 22kHz。

### 采样保持放大器

**AD7606** 的采样保持放大器可以使 ADC 以 16 位的分辨率精确采集满量程幅值的输入正弦波。采样保持放大器在 CONVST x 上升沿时对其各自输入进行同步采样。一个器件的所有 8 个采样保持放大器以及不同器件的采样保持放大器从使能到进入保持模式的延迟时间严格匹配，因此允许对一个系统中的多片 **AD7606** 进行同步采样控制。

BUSY 的下降沿表示所有的 8 个通道的转换过程均已经结束，此时采样保持器返回跟踪模式，下一批转换的采集时间开始计时。

**AD7606** 的所有通道转换时间为 2.9us，8 个通道均转换完成后，BUSY 信号恢复低电平，表示转换过程结束。在 BUSY 下降沿时，采样保持放大器返回跟踪模式。在 BUSY 变为低电平后，可以通过并行、并行字节或串行接口从输出寄存器中读取新数据。或者，当 BUSY 位高电平时，可以读取前一次转换的数据，在转换期间从 **AD7606** 读取数据对性能几乎没有影响，可以实现更快的吞吐速率。

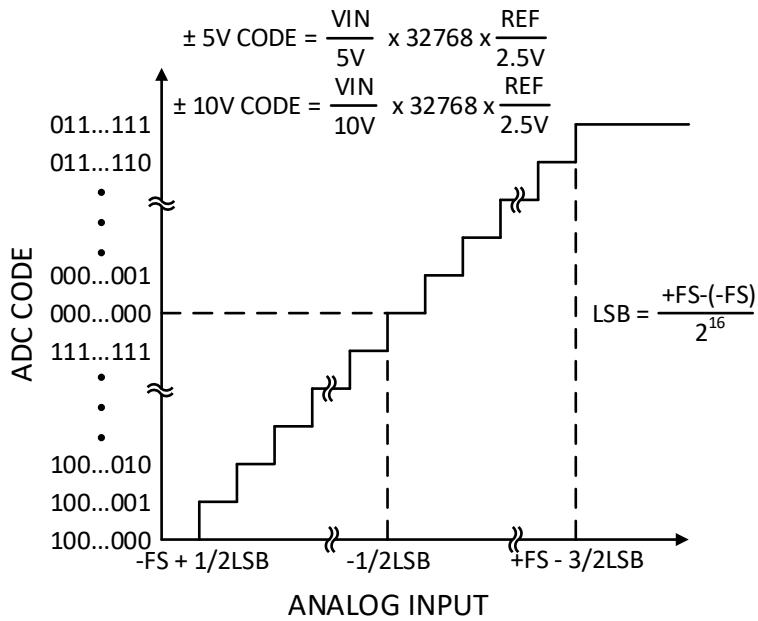

### ADC 传递函数

**AD7606** 的输出编码方式为二进制补码。所设计的码转换在连续的 LSB 整数值的中间（即 1/2LSB 和 3/2LSB）进行。**AD7606** 的 LSB 的大小为 FSR/65536。**AD7606** 的立项传递函数特性如图 27 所示。

图 27 SCA7606 传递函数

LSB 的大小取决于输入电压范围的选择。

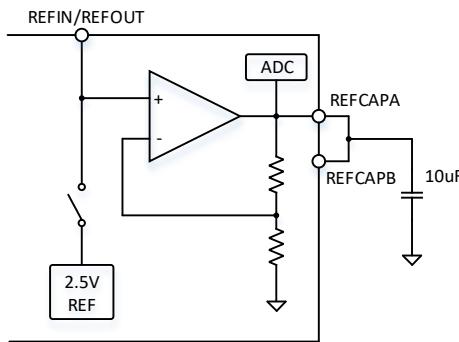

## 内部/外部电压基准

AD7606 内置了 2.5V 的片上带隙基准电压源和基准电压缓冲电路，缓冲电路可以将 REFIN/REFOUT 引脚的电压同通过闭环控制放大到约 4.5V 输出到 REFCAPA 和 REFCAPB 引脚（参考图 28），此放大后的电压给 ADC 作为数据转换时的参考电压。REFCAPA 和 REFCAPB 引脚必须在外部短路在一起，并通过一个 10uF 陶瓷电容连接至 REFGND，以确保基准电压缓冲电路工作在闭环状态。

图 28 基准电压电路

通过配置 REF SELECT 引脚，缓冲电路的输入电压，即 REFIN/REFOUT 引脚的电压，可以被配置为来自片上的带隙基准电压源或者外部施加的一个 2.5V 的基准电压源。REF SELECT 引脚为高电平，选择片上的基准电压源；REF SELECT 为低电平，则内部的基准电压源被禁用，必须在 REFIN/REFOUT 引脚施加一个外部的基准电压源。无论是用片上基准电压或外部的基准电压，REFIN/REFOUT 引脚都必须用 10uF 的陶瓷电容去耦连接到 AGND。

## 典型电路连接

图 9 显示了 **AD7606** 的电性连接图。 **AD7606** 的四个 AVDD 电源引脚，各使用一个 100nF 的陶瓷电容去耦至 AGND，供电电源端再使用一个 1uF 的陶瓷电容。DVDD 电源连接到和处理器相同的电源，并用 100nF 的陶瓷电容去耦至 AGND。

图 9 展示了使用 **AD7606** 片上基准源的内部基准源模式。REFIN/REFOUT 引脚应该使用一个 10uF 陶瓷电容进行去耦，REFCAPA 和 REFCAPB 应当短接在一起并通过 10uF 陶瓷电容去耦至 REFGND。

## 省电模式

**AD7606** 有两种省电模式：待机模式和关断模式。**STBY** 和 **RANGE** 引脚的逻辑状态组合决定了具体进入的省电模式。

**STBY** = 0, **RANGE** = 1, **AD7606** 进入待机模式，待机模式下 **AD7606** 最大的电流为 7 mA。**STBY** = 0, **RANGE** = 0, **AD7606** 进入关断模式，所有电路停止工作，供电电流只有 10 uA。**AD7606** 从关断模式上电之后，需要施加 **RESET** 脉冲。

## 转换控制

### 所有通道同步采样

**AD7606** 可以对所有模拟输入通道进行同步采样。当 **CONVST A** 和 **CONVST B** 引脚连接在一起并施加转换开始信号时，所有 8 个通道同步进行采样。所有通道的转换时间为 **t<sub>CONV</sub>**。**BUSY** 信号的高电平表示转换正在进行，当 **BUSY** 变为低电平时表示转换结束，**BUSY** 信号的下降沿使 8 个通道的采样保持放大器返回跟踪状态。**BUSY** 信号的下降沿还表示可以通过数字接口读取数据。

## 数字接口

**AD7606** 提供三种数字接口选型：并行接口、串行接口和并行字节接口。接口模式可以通过配置 **PAR/SER/BYTE SEL** 和 **DB15/BYTE SEL** 引脚来选择，详情见表 5。

表 6 接口模式选择

| <b>PAR/SER/BYTE SEL</b> | <b>DB15</b> | 接口模式     |

|-------------------------|-------------|----------|

| 0                       | x           | 并行接口模式   |

| 1                       | 0           | 串行接口模式   |

| 1                       | 1           | 并行字节接口模式 |

注：x：并行模式下，DB15 是数据总线，不能进行配置。

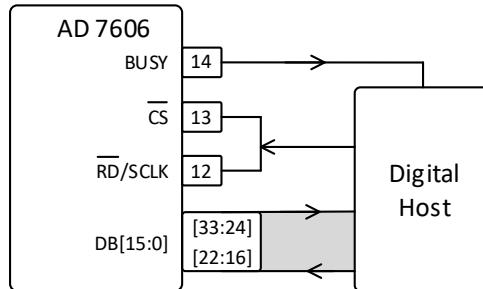

### 并行接口模式

选择并行接口模式时，可以通过控制 **CS** 和 **RD** 引脚，从 **DB[0:15]** 总线上依次读取 8 个通道的采样数据。

图 29 AD7606 并联接口框图

**CS** 是使能数据总线的控制信号，**CS** 的上升沿使总线引脚进入三态，其下降沿使总线引脚脱离高阻态。控制 **CS** 引脚可以使多个 **AD7606** 共享同一个并行的数据总线。

**RD** 用来从输出转换寄存器读取数据。对 **RD** 施加脉冲序列，可以使各通道的转换结果按照升序逐个输出到并行总线。**BUSY** 变为低电平之后的第一个 **RD** 下降沿输出通道 **V1** 的转换结果，下一个 **RD** 下降沿输出 **V2** 的转换结果，依次类推。当系统里只有一个 **AD7606** 时，可以将 **CS** 和 **RD** 连接在一起，用数字主机的同一个信号来控制。

### 并行字节接口模式

并行字节接口模式和并行接口模式的工作原理类似，区别在于 16 位的转换结果分两次从 **DB[0:7]** 总线引脚输出，因此 8 个通道的数据读取需要 16 个 **RD** 的脉冲。并行字节模式下，**DB[0]** 为数据传输的 **LSB**，而 **DB[7]** 为数据传输的 **MSB**，**DB[14]** 充当 **HBEN** 引脚。**DB[14]/HBEN** 引脚为逻辑高电平时，首先输出转换结果的高字节（**MSB**），然后输出转换结果的低字节（**LSB**），**DB[14]/HBEN** 引脚为逻辑低电平时，正好相反。在并行字节模式下，**FRSTDATA** 引脚将维持高电平，直到 **V1** 通道的转换结果全部被读取。

### 串行接口模式

串行接口模式下，**CS**、**SCLK** 和 **DOUTA/DOUTB** 被用来实现数据传输和控制。

**CS** 的下降沿使数据输出总线 **DOUTA/DOUTB** 脱离三态，并逐个输出转换结果的 **MSB**。**SCLK** 的上升沿将随后的所有数据为逐个输出至 **DOUTA** 和 **DOUTB**。在串行读取操作过程中，**CS** 引脚必须全程保持低电平，8 个通道数据全部读取完毕之后才能恢复高电平，因此一次串行读取数据需要 128 个 **SCLK** 周期。

**AD7606** 有两个串行数据总线 **DOUTA** 和 **DOUTB**，用户可以选择通过单总线或双总线从 **AD7606** 读取数据。串行通信开始之后，**DOUTA** 总线上将以 **V1, V2, V3, V4, V5, V6, V7, V8** 的顺序输出数据，而 **DOUTB** 总线将以 **V5, V6, V7, V8, V1, V2, V3, V4** 的顺序输出数据。

**CS** 的下降沿到来之后，总线引脚脱离三态，逐个输出 16 位的转换结果的 **MSB**。**MSB** 在 **CS** 下降沿之后的第一个 **SCLK** 下降沿有效，后续的 15 位数据在 **SCLK** 的上升沿逐个输出，数据在 **SCLK** 的下降沿有效。

### 转换期间读取数据

**AD7606** 允许数字主机在数据转换进行的时候读取数据而不影响其性能，转换期间读取数据可以使用并行或者并行字节，而且不受过采样功能的影响。**BUSY** 下降沿到来的时候，输出结果寄存器会被新的转换数据更新，因此读取数据的操作必须在 **BUSY** 下降沿到来前完成，或者在 **BUSY** 下降沿延时 **t<sub>6</sub>**（见表 6）之后开始，否则某些通道的数据将出现错误。需要注意的是，在采用串行接口读取数据的时候不能在转换期间读取数据，原因是转换时间 **t<sub>CONV</sub>** 太短，采用串行口无法在转换时间内完整的读取数据。

## 数字滤波器

**AD7606** 内置了一个可配置的数字一阶 SINC 滤波器，该数字滤波器的过采样倍数有 OS[2: 0]引脚的逻辑组合来控制，详情见表 7。OS 管脚的逻辑在 **BUSY** 的下降沿被锁存，从而设置下一次转换时的过采样倍数。在 **CONVST x** 的上升沿到来时，各个通道的第一个采样点被采集，**AD7606** 内部会才生采样信号对所有通道其它的采样点进行采样，具体的采样次数由过采样倍数决定，所有采样完成后对采样点求平均值并更新到输出结果寄存器。

过采样操作改善了信噪比，但随着过采样倍数的提高，3dB 带宽以及数据吞吐率均会降低，因此在对较低数据吞吐率或者需要更高信噪比的应用中可以考虑使用数字滤波器。

开启过采样功能必须将 **CONVST A** 和 **CONVST B** 引脚短接在一起，而且转换过程中的 **BUSY** 高电平时间也会延长。

**OS[2:0]**管脚应当在启动转换之前配置好，在完成数据转换之前不能更改配置，具体的时序配置见图 30 和表 5。

图 30 OS x 引脚配置时序

表 7 过采样位解码

| OS[2:0] | 过采样倍数 | 10V 范围的 SNR (dB) | 10V 范围的 3dB 带宽 (kHz) | 最大数据吞吐速率 (kHz) |

|---------|-------|------------------|----------------------|----------------|

| 000     | 无过采样  | 87               | 22                   | 200            |

| 001     | 2     | 88               | 22                   | 100            |

| 010     | 4     | 88.9             | 18                   | 50             |

| 011     | 8     | 89.1             | 12                   | 25             |

| 100     | 16    | 88.2             | 6                    | 12.5           |

| 101     | 32    | 88.4             | 3                    | 6.25           |

| 110     | 64    | 92.5             | 1.5                  | 3.125          |

| 111     | 无效    |                  |                      |                |

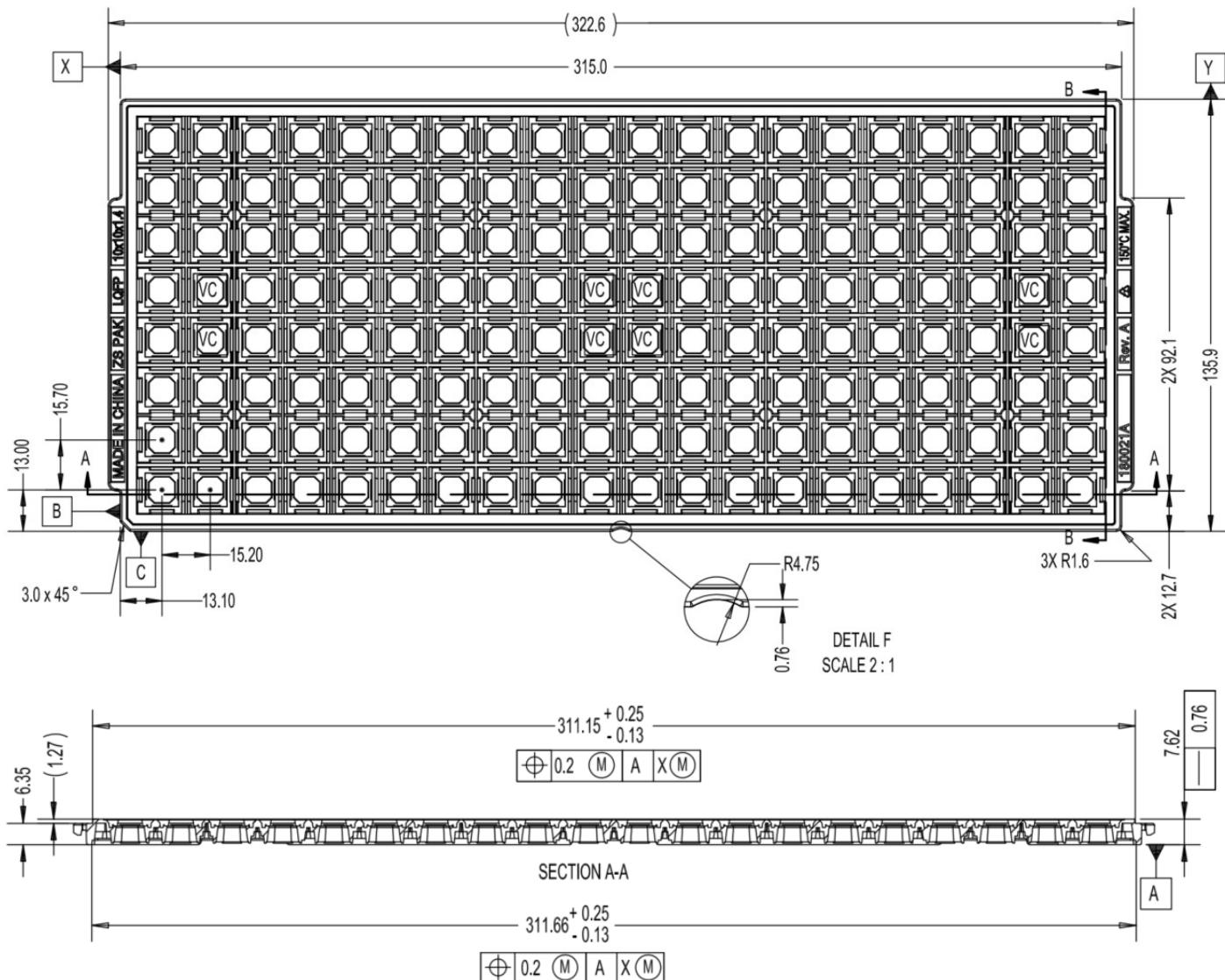

## 包装信息

注：1) 托盘的45°倒角表明芯片1脚的位置。

2) 单位mm。

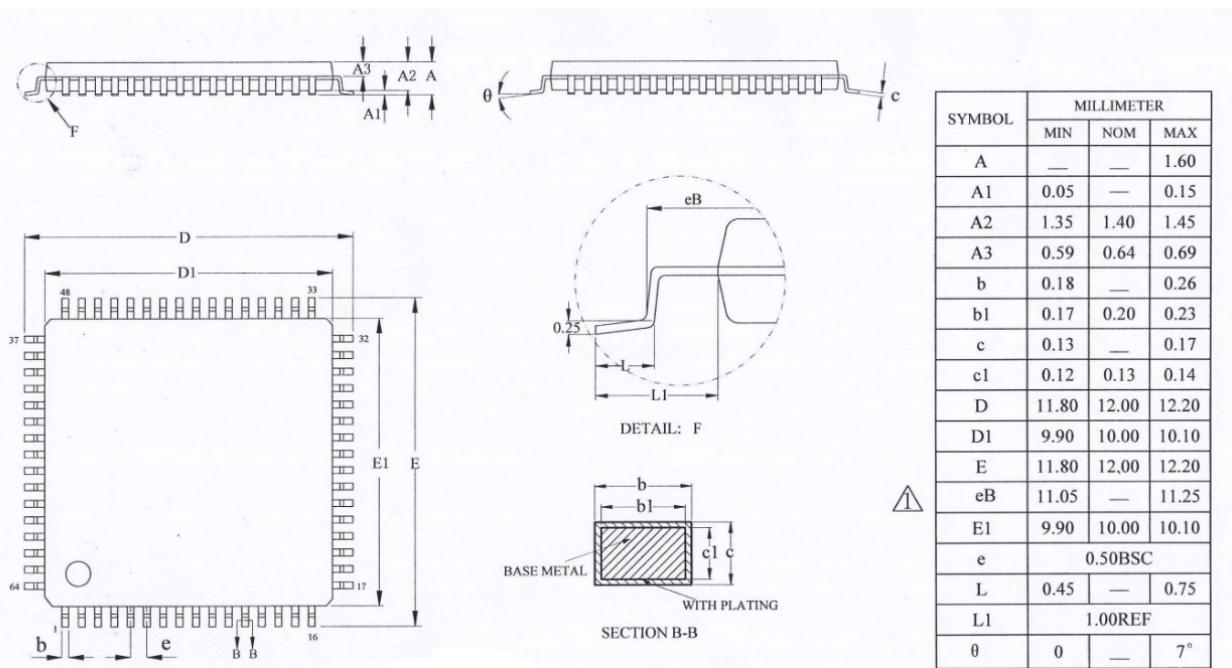

## 封装

图31. 64脚LQFP封装尺寸图 (单位: 毫米)

## 产品订购信息

| 产品型号       | 工作温度范围         | 封装形式        | 封装尺寸        |

|------------|----------------|-------------|-------------|

| AD7606BSTZ | -40°C to +85°C | 64-Pin LQFP | 10mm X 10mm |

|            |                |             |             |