矽源

Silicon

Preliminary Datasheet

3.75KV, 高可靠 4 通道数字隔离器

OSI1400/OSI1401/OSI1402

## 特性

- 隔离耐压:  $> 3.75\text{KV}_{\text{RMS}}$

- 数据传输速率: DC ~ 90Mbps

- 电源电压: 2.5V ~ 5.5V

- 高共模瞬态抑制 (CMTI)  $> 100\text{kV}/\mu\text{s}$

- 输出选择 (型号):

- 输出高电平

- 输出低电平

- 使能选择 (型号):

- EN 型 (电流上拉, 默认使能)

- DIS 型 (电流下拉, 默认使能)

- 功耗:  $< 1.5\text{mA}/\text{ch}$  ( 1 Mbps)

- 传播延迟:  $< 15\text{ns}$

- 抗干扰特性:

- ESD 增强

- 脉冲群增强

- 浪涌增强

- 工作温度: -40°C ~ 125°C

- ESD 等级

- HBM:  $> \pm 6\text{KV}$

- CDM:  $> \pm 2\text{KV}$

- 宽体 16 引脚 SOP 封装

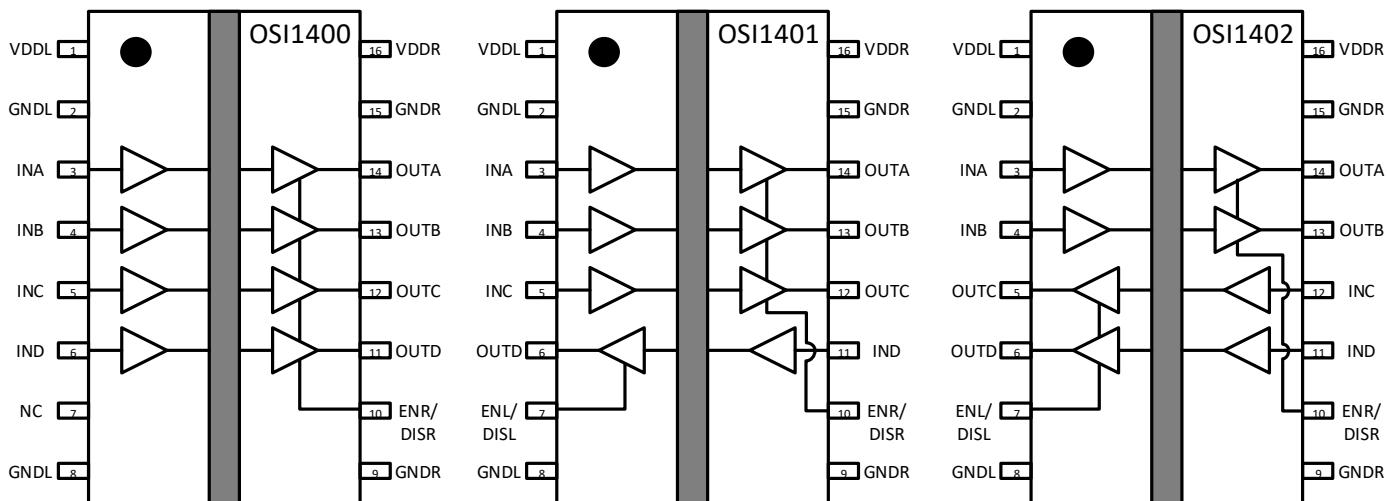

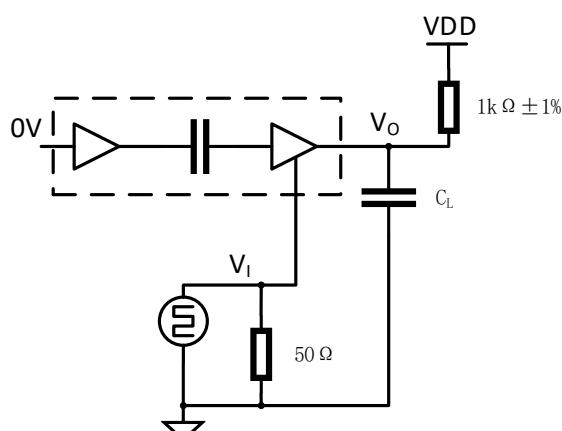

## 功能电路

图 1. 功能电路

Rev. A

Information furnished by orisilicon is believed to be accurate and reliable. However, no responsibility is assumed by orisilicon for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of orisilicon. Trademarks and registered trademarks are the property of their respective owners.

No.67, Keji Road 2, Gaoxin District, Xi'an, Shaanxi 710071, China.

Tel: +86 18591979206

Fax: +86 29 8888 8888

[www.orisilicon.com](http://www.orisilicon.com)

©2024 orisilicon, Inc. All rights reserved.

## 电特性参数

表 1. 电特性

V<sub>DDL</sub>=V<sub>DDR</sub>=5.0V, Ta=25°C, 除非另有说明

| 参数           | 符号                                | 条件                                                         | 最小值     | 典型值 | 最大值 | 单位    |

|--------------|-----------------------------------|------------------------------------------------------------|---------|-----|-----|-------|

| <b>DC 规格</b> |                                   |                                                            |         |     |     |       |

| 电源电压         | V <sub>DDL</sub> V <sub>DDR</sub> |                                                            | 2.5     |     | 5.5 | V     |

| 电源上电复位       | V <sub>POR</sub>                  | V <sub>DDL</sub> /V <sub>DDR</sub> 上电时 POR 阈值电压            | -       | 2.0 | -   | V     |

|              | V <sub>POR.HYS</sub>              | POR 阈值迟滞                                                   |         | 0.1 |     | V     |

| 输入端口高电平      | V <sub>IH</sub>                   |                                                            | 2.0     |     |     | V     |

| 输入端口低电平      | V <sub>IL</sub>                   |                                                            |         |     | 0.8 | V     |

| 输出端口高电平      | V <sub>OH</sub>                   | I <sub>OHi</sub> =-4mA                                     | VDD-0.3 |     |     | V     |

| 输出端口低电平      | V <sub>OL</sub>                   | I <sub>OLO</sub> =4mA                                      |         |     | 0.3 | V     |

| 输出端口阻抗       | R <sub>OUT</sub>                  |                                                            |         | 50  |     | Ω     |

| 使能输入高电平      | V <sub>ENH</sub>                  |                                                            |         | 1.6 |     | V     |

| 使能输入低电平      | V <sub>ENL</sub>                  |                                                            |         | 1.2 |     | V     |

| 使能上拉电流       | I <sub>EN</sub>                   | V <sub>EN</sub> =0V                                        |         | 8   |     | μA    |

| 关断下拉电流       | I <sub>DIS</sub>                  | V <sub>DIS</sub> =5.0V                                     |         | -8  |     | μA    |

| 芯片上电时间       | t <sub>por</sub>                  | V <sub>DDR</sub> /L 达到 POR 点后芯片可正常工作的最长时间                  |         | 100 |     | μs    |

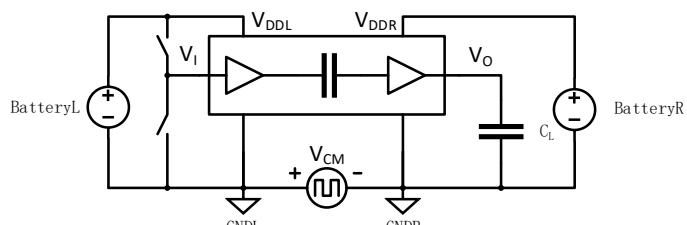

| 共模瞬态抑制       | CMTI                              | 图 5                                                        | 50      |     | 100 | kV/μs |

| <b>时序规格</b>  |                                   |                                                            |         |     |     |       |

| 数据速率         | DR                                |                                                            | 0       |     | 90  | Mbps  |

| 最小脉冲宽度       | PW                                |                                                            |         |     | 5   | ns    |

| 传播延迟         | t <sub>PLH</sub>                  | C <sub>L</sub> =15pF, 图 3                                  |         |     | 25  | ns    |

|              | t <sub>PHL</sub>                  | C <sub>L</sub> =15pF, 图 3                                  |         |     | 22  | ns    |

| 脉冲宽度失真       | PWD                               | t <sub>PHL</sub> -t <sub>PLH</sub>  , C <sub>L</sub> =15pF |         |     | 6   | ns    |

| 上升时间         | t <sub>r</sub>                    | C <sub>L</sub> =15pF, 图 3                                  |         |     | 6   | ns    |

| 下降时间         | t <sub>f</sub>                    | C <sub>L</sub> =15pF, 图 3                                  |         |     | 6   | ns    |

| 眼图抖动峰值       | T <sub>jitt-peak</sub>            |                                                            |         | 400 |     | ps    |

| 通道间时间偏差      | T <sub>ds-c2c</sub>               |                                                            |         |     | 3   | ns    |

| 芯片间的时间偏差     | T <sub>ds-p2p</sub>               |                                                            |         |     | 6   | ns    |

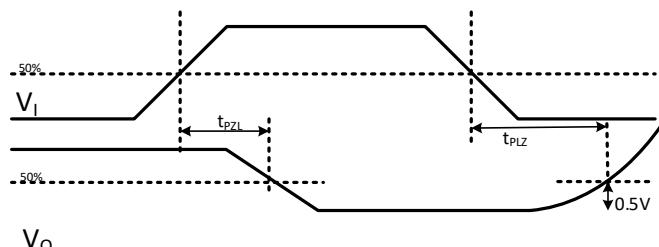

| 关断到输出三态时间    | t <sub>PLZ</sub>                  | C <sub>L</sub> =15pF, R <sub>L</sub> =1KΩ, 图 4             |         | 18  |     | ns    |

| 使能到数据有效时间    | t <sub>PZH</sub>                  | C <sub>L</sub> =15pF, R <sub>L</sub> =1KΩ, 图 4             |         | 11  |     | ns    |

| <b>电流功耗</b>  |                                   |                                                            |         |     |     |       |

| OSI1400      | I <sub>DDL(DC0)</sub>             | OSI1400x0 所有输入电压为 0V                                       |         |     | 2.5 | mA    |

|              | I <sub>DDR(DC0)</sub>             | OSI1400x1 所有输入电压为 V <sub>DDL</sub>                         |         |     | 4.6 | mA    |

|              | I <sub>DDL(DC1)</sub>             | OSI1400x0 所有输入电压为 V <sub>DDL</sub>                         |         |     | 9   | mA    |

|         |                       |                                                     |  |  |      |    |

|---------|-----------------------|-----------------------------------------------------|--|--|------|----|

| OSI1401 | $I_{DDR(DC1)}$        | OSI1400x1 所有输入电压为 0V                                |  |  | 4.8  | mA |

|         | $I_{DDL(1\text{MO})}$ | 所有输入通道 5Mhz 逻辑输入频率<br>$C_L=15\text{pF}$             |  |  | 6    | mA |

|         | $I_{DDR(1\text{MO})}$ | $C_L=15\text{pF}$                                   |  |  | 10   | mA |

|         | $I_{DDL(9\text{MO})}$ | 所有输入通道 45Mhz 逻辑输入频率<br>$C_L=15\text{pF}$            |  |  | 7    | mA |

|         | $I_{DDR(9\text{MO})}$ | $C_L=15\text{pF}$                                   |  |  | 57   | mA |

|         | $I_{DDL(DC0)}$        | OSI1400x0 所有输入电压为 0V<br>OSI1400x1 所有输入电压为 $V_{DDL}$ |  |  | 3    | mA |

|         | $I_{DDR(DC0)}$        | $V_{DDL}$                                           |  |  | 4.5  | mA |

|         | $I_{DDL(DC1)}$        | OSI1400x0 所有输入电压为 $V_{DDL}$<br>OSI1400x1 所有输入电压为 0V |  |  | 9    | mA |

|         | $I_{DDR(DC1)}$        | 0V                                                  |  |  | 7    | mA |

|         | $I_{DDL(1\text{MO})}$ | 所有输入通道 5Mhz 逻辑输入频率<br>$C_L=15\text{pF}$             |  |  | 7    | mA |

|         | $I_{DDR(1\text{MO})}$ | $C_L=15\text{pF}$                                   |  |  | 9.5  | mA |

|         | $I_{DDL(9\text{MO})}$ | 所有输入通道 45Mhz 逻辑输入频率<br>$C_L=15\text{pF}$            |  |  | 17.5 | mA |

|         | $I_{DDR(9\text{MO})}$ | $C_L=15\text{pF}$                                   |  |  | 46   | mA |

| OSI1402 | $I_{DDL(DC0)}$        | OSI1400x0 所有输入电压为 0V<br>OSI1400x1 所有输入电压为 $V_{DDL}$ |  |  | 3.8  | mA |

|         | $I_{DDR(DC0)}$        | $V_{DDL}$                                           |  |  | 3.8  | mA |

|         | $I_{DDL(DC1)}$        | OSI1400x0 所有输入电压为 $V_{DDL}$<br>OSI1400x1 所有输入电压为 0V |  |  | 7.2  | mA |

|         | $I_{DDR(DC1)}$        | 0V                                                  |  |  | 7.2  | mA |

|         | $I_{DDL(1\text{MO})}$ | 所有输入通道 5Mhz 逻辑输入频率<br>$C_L=15\text{pF}$             |  |  | 8.5  | mA |

|         | $I_{DDR(1\text{MO})}$ | $C_L=15\text{pF}$                                   |  |  | 8.5  | mA |

|         | $I_{DDL(9\text{MO})}$ | 所有输入通道 45Mhz 逻辑输入频率<br>$C_L=15\text{pF}$            |  |  | 33   | mA |

|         | $I_{DDR(9\text{MO})}$ | $C_L=15\text{pF}$                                   |  |  | 33   | mA |

注 1:

## 绝对最大额定值

表 2.

| 参数                         | 额定值                           |

|----------------------------|-------------------------------|

| VDDL, VDDR                 | -0.3V 至 6.5V                  |

| VINA, VINB, VINC, VIND     | -0.3V 至 6.5V                  |

| VOUTA, VOUTB, VOUTC, VOUTD | -0.3V 至 6.5V                  |

| CMTI                       | $\pm 90\text{KV}/\mu\text{s}$ |

| IOUTA, IOUTB, IOUTC, IOUTD | -15mA 至 15mA                  |

| 工作温度范围                     | -40°C 至 125°C                 |

| 储存温度范围                     | -65°C 至 90°C                  |

注意, 超出上述绝对最大额定值可能会导致器件永久性损坏。这只是额定应力值, 不涉及器件在这些或任何其他条件下超出本技术规格指标的功能性操作。长期在绝对最大额定值条件下工作会影响器件的可靠性。

## THERMAL DATA

绝对最大额定值仅适合单独应用, 但不适合组合使用。结温高于限制值时, 会损坏器件。监控环境温度并不能保证  $T_J$  不会超出额定温度限值。在功耗高、热阻差的应用中, 可能必须降低最大环境温度。

在功耗适中、PCB 热阻较低的应用中, 只要结温处于额定限值以内, 最大环境温度可以超过最大限值。器件的结温 ( $T_J$ ) 取决于环境温度 ( $T_A$ )、器件的功耗 ( $P_D$ ) 和封装的结到环境热阻 ( $\theta_{JA}$ )。

最高结温 ( $T_J$ ) 由环境温度 ( $T_A$ ) 和功耗 ( $P_D$ ) 通过下式计算:

$$T_J = T_A + (P_D \times \theta_{JA})$$

封装的结到环境热阻 ( $\theta_{JA}$ ) 基于使用 4 层板的建模和计算方法, 主要取决于应用和板布局。在功耗较高的应用中, 需要特别注意热板设计。 $\theta_{JA}$  的值可能随 PCB 材料、布局和环境条件不同而异。 $\theta_{JA}$  的额定值基于 4" × 3" 的 4 层电路板。有关板结构的详细信息, 请参考 JESD 51-7 和 JESD 51-9。

$\Psi_{JB}$  是结到板热特性参数, 单位为 °C/W。封装的  $\Psi_{JB}$  基于使用 4 层板的建模和计算方法。JESD51-12——“报告和使用电子封装热信息指南”中声明, 热特性参数和热阻不是一回事。 $\Psi_{JB}$  衡量沿多条热路径流动的器件功率, 而  $\theta_{JB}$  只涉及一条路径。因此,  $\Psi_{JB}$  热路径包括来自封装顶部的对流和封装的辐射, 这些因素使得  $\Psi_{JB}$  在现实应用中更有用。最高结温 ( $T_J$ ) 由板温度 ( $T_B$ ) 和功耗 ( $P_D$ ) 通过下式计算:

$$T_J = T_B + (P_D \times \Psi_{JB})$$

有关  $\Psi_{JB}$  的详细信息, 请参考 JESD51-8 和 JESD51-12。

## THERMAL RESISTANCE

$\theta_{JA}$  和  $\Psi_{JB}$  针对最差条件, 即器件焊接在电路板上以实现表贴封装。

表. 3 热阻

| Package Type   | $\theta_{JA}$ | $\theta_{JC}$ | Unit  |

|----------------|---------------|---------------|-------|

| 16-Lead W- SOP |               |               | °C /W |

## ESD CAUTION

**ESD (electrostatic discharge) sensitive device.**

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

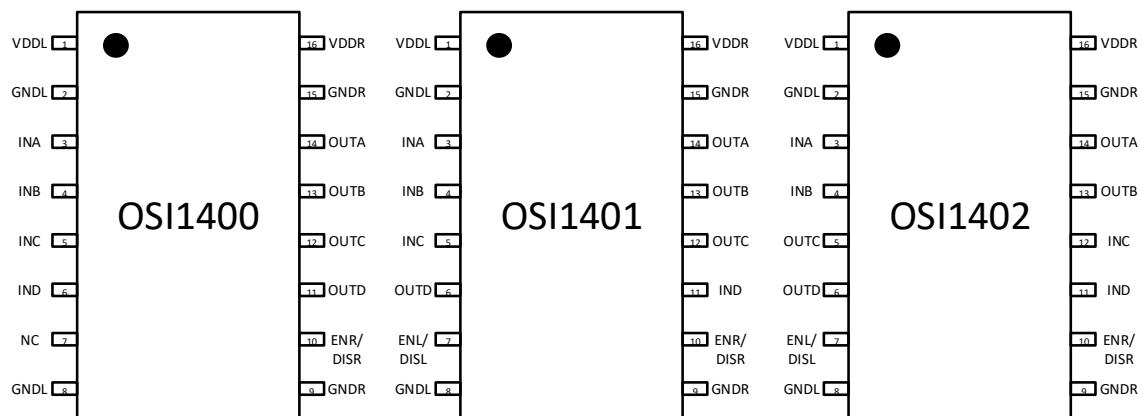

## 引脚配置以及功能描述

图 2. 引脚配置

表 4. 引脚功能描述

| OSI1400 | OSI1401 | OSI1402 | 符号          | 描述                                                                                        |

|---------|---------|---------|-------------|-------------------------------------------------------------------------------------------|

| 1       | 1       | 1       | VDDL        | 隔离左侧电源电压                                                                                  |

| 2       | 2       | 2       | GNDL        | 隔离左侧地电压                                                                                   |

| 3       | 3       | 3       | INA         | 逻辑输入 A                                                                                    |

| 4       | 4       | 4       | INB         | 逻辑输入 B                                                                                    |

| 5       | 5       | 12      | INC         | 逻辑输入 C                                                                                    |

| 6       | 11      | 11      | IND         | 逻辑输入 D                                                                                    |

| 7       | 7       | 7       | NC/ENL/DISL | NC: 无连接;<br>ENL: 高电平或悬空, 左侧输出使能; 低电平, 左侧输出处于高阻状态<br>DISL: 低电平或悬空, 左侧输出使能; 高电平, 左侧输出处于高阻状态 |

| 8       | 8       | 8       | GNDL        | 隔离左侧地电压                                                                                   |

| 9       | 9       | 9       | GNDR        | 隔离右侧地电压                                                                                   |

| 10      | 10      | 10      | ENR/DISR    | ENR: 高电平或悬空, 右侧输出使能; 低电平, 右侧输出处于高阻状态<br>DISR: 低电平或悬空, 右侧输出使能; 高电平, 右侧输出处于高阻状态             |

| 11      | 6       | 6       | OUTD        | 逻辑输出 D                                                                                    |

| 12      | 12      | 5       | OUTC        | 逻辑输出 C                                                                                    |

| 13      | 13      | 13      | OUTB        | 逻辑输出 B                                                                                    |

| 14      | 14      | 14      | OUTA        | 逻辑输出 A                                                                                    |

| 15      | 15      | 15      | GNDR        | 隔离右侧地电压                                                                                   |

| 16      | 16      | 16      | VDDR        | 隔离右侧电源电压                                                                                  |

## 功能描述

OSI140X 芯片时一款 4 通道的数字隔离通讯芯片，芯片采用高压电容作为隔离介质。输入数字信号被 RF 振荡器进行调制，并经过高压电容耦合之后送入解调器，并解调出输入信号。

OSI140X 的最高数据传输速率可达到 90Mbps, 共模电压抑制能力可以达到 90kV/  $\mu$ s 能力。】

OSI140X 提供使能端默认模式，EN 方式时端口默认 8  $\mu$ A 上拉电流，且处于使能模式，当要关断时，需要将 EN 端口拉低到 GND 电压；DIS 方式时端口默认 8  $\mu$ A 下拉电流，且处于使能模式，当要关断时，需要将 DIS 端口拉高到 VDD 电压。

OSI140X 还提供输出电压默认模式，可选择默认输出高电平或者输出低电平。用于在原边电源电压丢失时副边的输出工作在不会造成系统损坏的状态。

OSI140X 较宽的输入电压工作范围使得芯片可应用于各种电源域系统，并可实现电平转移功能。

表 5. 输出电压与电源状态表

| INX | ENX  | VDDL     | VDDR     | OUTX | 说明                                           |

|-----|------|----------|----------|------|----------------------------------------------|

| H   | H/NC | Ready    | Ready    | H    | 正常                                           |

| L   | H/NC | Ready    | Ready    | L    | 正常                                           |

| X   | L    | Ready    | Ready    | Z    | 输出高阻                                         |

| X   | H/NC | No Ready | Ready    | L/H  | VDDL 在 POR 的 100 $\mu$ s 以内依据输出默认输出，之后依据输入状态 |

| X   | L    | No Ready | Ready    | Z    | 输出高阻                                         |

| X   | X    | Ready    | No Ready | X    | VDDR 在 POR 的 100 $\mu$ s 以内输出状态不定，之后与输入状态一致  |

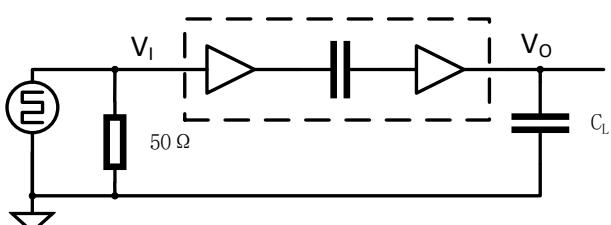

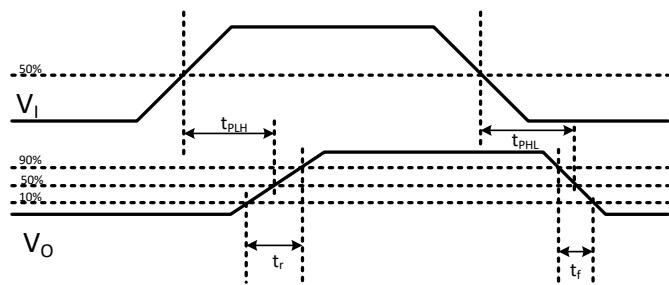

## 时序参数测试

### 输入时序特性测试：

3. 开关时序特性测试电路

图 4. 开关时序波形

### 输出时序特性测试：

图 5. 使能与输出端口间延迟时序测试电路

图 6. 使能与输出端口间延迟波形

### 共模电压抑制测试：

图 7. 共模瞬态抑制测试电路

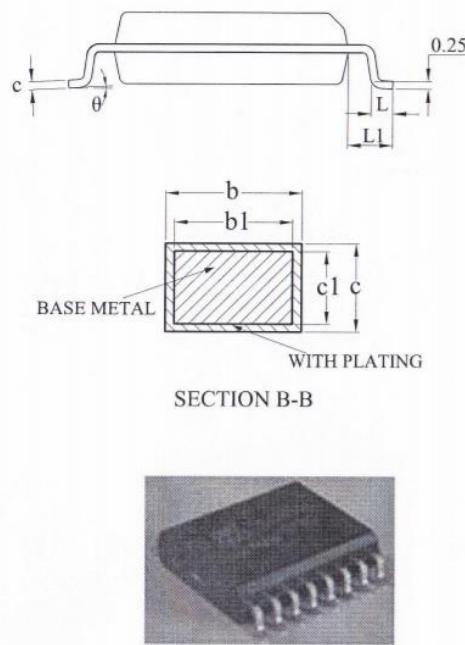

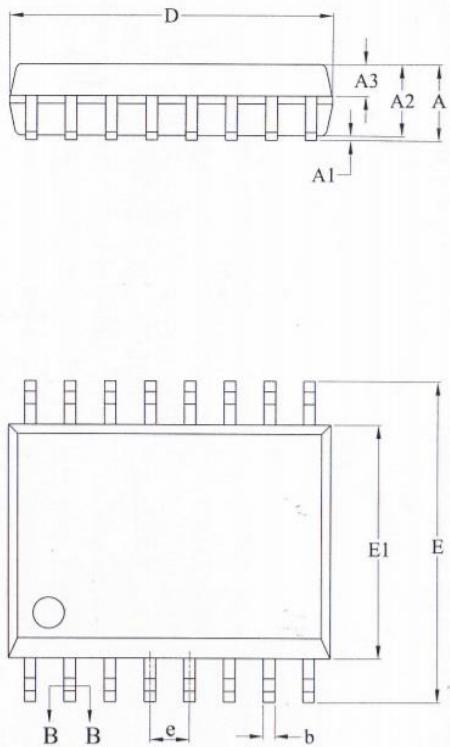

## 封装描述

| SYMBOL   | MILLIMETER |       |       |

|----------|------------|-------|-------|

|          | MIN        | NOM   | MAX   |

| A        | —          | —     | 2.65  |

| A1       | 0.10       | —     | 0.30  |

| A2       | 2.25       | 2.30  | 2.35  |

| A3       | 0.97       | 1.02  | 1.07  |

| b        | 0.35       | —     | 0.43  |

| b1       | 0.34       | 0.37  | 0.40  |

| c        | 0.25       | —     | 0.29  |

| c1       | 0.24       | 0.25  | 0.26  |

| D        | 10.20      | 10.30 | 10.40 |

| E        | 10.10      | 10.30 | 10.50 |

| E1       | 7.40       | 7.50  | 7.60  |

| e        | 1.27BSC    |       |       |

| L        | 0.55       | —     | 0.85  |

| L1       | 1.40REF    |       |       |

| $\theta$ | 0          | —     | 8°    |

图 8. 封装图纸 (WB SOP16)

注:

控制尺寸: 毫米

## 订购信息

表 6. 芯片订购表格

| Part. NO.  | 隔离耐压 (kV) | 左侧输入个数 | 右侧输入个数 | 最大数据率 (Mbps) | 默认使能状态 | 默认输出状态 | 工作温度          | 封装形式     |

|------------|-----------|--------|--------|--------------|--------|--------|---------------|----------|

| OSI1400WE0 | 3.75      | 4      | 0      | 90           | EN     | Low    | -40°C ~ 125°C | WB SOP16 |

| OSI1400WE1 | 3.75      | 4      | 0      | 90           | EN     | High   | -40°C ~ 125°C | WB SOP16 |

| OSI1400WD0 | 3.75      | 4      | 0      | 90           | DIS    | Low    | -40°C ~ 125°C | WB SOP16 |

| OSI1400WD1 | 3.75      | 4      | 0      | 90           | DIS    | High   | -40°C ~ 125°C | WB SOP16 |

| OSI1401WE0 | 3.75      | 3      | 1      | 90           | EN     | Low    | -40°C ~ 125°C | WB SOP16 |

| OSI1401WE1 | 3.75      | 3      | 1      | 90           | EN     | High   | -40°C ~ 125°C | WB SOP16 |

| OSI1401WD0 | 3.75      | 3      | 1      | 90           | DIS    | Low    | -40°C ~ 125°C | WB SOP16 |

| OSI1401WD1 | 3.75      | 3      | 1      | 90           | DIS    | High   | -40°C ~ 125°C | WB SOP16 |

| OSI1402WE0 | 3.75      | 2      | 2      | 90           | EN     | Low    | -40°C ~ 125°C | WB SOP16 |

| OSI1402WE1 | 3.75      | 2      | 2      | 90           | EN     | High   | -40°C ~ 125°C | WB SOP16 |

| OSI1402WD0 | 3.75      | 2      | 2      | 90           | DIS    | Low    | -40°C ~ 125°C | WB SOP16 |

| OSI1402WD1 | 3.75      | 2      | 2      | 90           | DIS    | High   | -40°C ~ 125°C | WB SOP16 |