# UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER

### **FEATURES**

- Wide power supply voltage range from 3 V to 6 V

- Wide temperature range from –40<sup>°</sup>C to 85<sup>°</sup>C

- Synchronous communication upto 64 Kbaud

- Asynchronous communication upto 38.4 Kbaud

- Transmitting/receiving operations under double buffered configuration.

- Error detection (parity, overrun and framing)

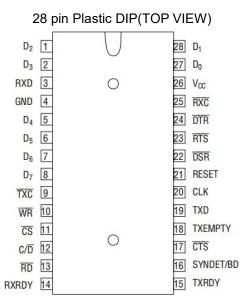

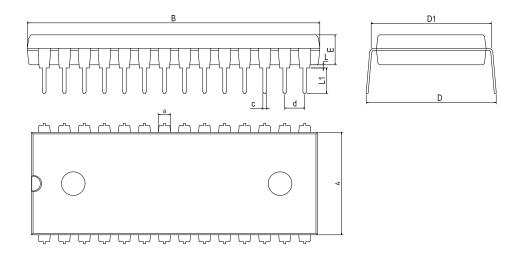

- •28-pin Plastic DIP (DIP-28-P-600-2.54)

### ORDERING INFORMATION

| DEVICE   | Package Type | MARKING | Packing | Packing Qty |

|----------|--------------|---------|---------|-------------|

| HG82C51N | DIP-28       | HG82C51 | TUBE    | 300pcs/Box  |

### **GENERAL DESCRIPTION**

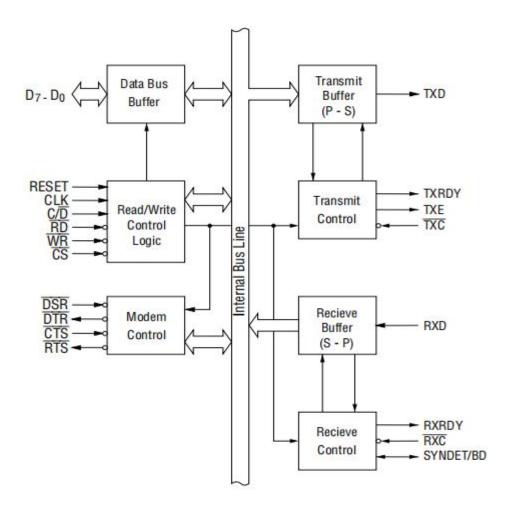

The HG82C51 is a USART (Universal Synchronous Asynchronous Receiver Transmitter) for serial data communication. As a peripheral device of a microcomputer system, the HG82C51 receives parallel data from the CPU and transmits serial data after conversion. This device also receives serial data from the outside and transmits parallel data to the CPU after conversion. The HG82C51 configures a fully static circuit using silicon gate CMOS technology. Therefore, it operates on extremely low power at 100 mA (max) of standby current by suspending all operations.

### PIN CONFIGURATION

### **FUNCTIONAL BLOCK DIAGRAM**

### **FUNCTION**

### **OUTLINE**

The HG82C51's functional configuration is programed by software.

Operation between the HG82C51 and a CPU is executed by program control. Table 1 shows the operation between a CPU and the device.

| CS | C/D̄ | RD | WR |                   |  |  |  |  |  |  |

|----|------|----|----|-------------------|--|--|--|--|--|--|

| 1  | ×    | ×  | ×  | Data Bus 3-State  |  |  |  |  |  |  |

| 0  | ×    | 1  | 1  | Data Bus 3-State  |  |  |  |  |  |  |

| 0  | 1    | 0  | 1  | Status → CPU      |  |  |  |  |  |  |

| 0  | 1    | 1  | 0  | Control Word ←CPU |  |  |  |  |  |  |

| 0  | 0    | 0  | 1  | Data →CPU         |  |  |  |  |  |  |

| 0  | 0    | 1  | 0  | Data ←CPU         |  |  |  |  |  |  |

Table 1 Operation between HG82C51 and CPU

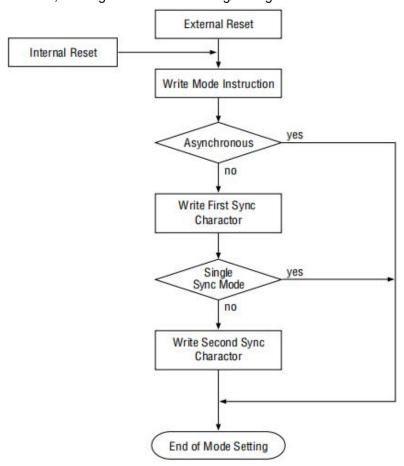

It is necessary to execute a function-setting sequence after resetting the HG82C51. Fig. 1 shows the function-setting sequence.

If the function was set, the device is ready to receive a command, thus enabling the transfer of data by setting a necessary command, reading a status and reading/writing data.

Fig. 1 Function-setting Sequence (Mode Instruction Sequence)

### **CONTROL WORDS**

There are two types of control word.

- 1. Mode instruction (setting of function)

- 2. Command (setting of operation)

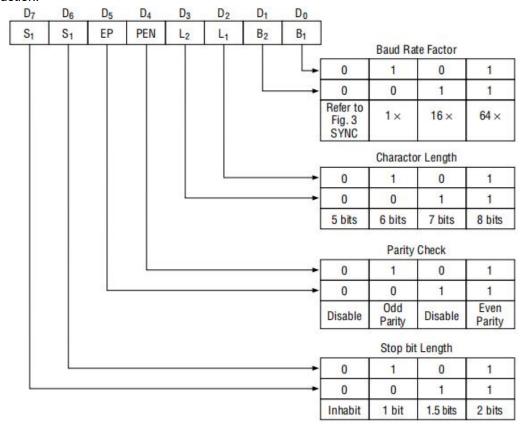

### 1) MODE INSTRUCTION

Mode instruction is used for setting the function of the HG82C51. Mode instruction

will be in "wait for write" at either internal reset or external reset. That is, the writing of a control word after resetting will be recognized as a "mode instruction."

Items set by mode instruction are as follows:

- Synchronous/asynchronous mode

- Stop bit length (asynchronous mode)

- Character length

- Parity bit

- Baud rate factor (asynchronous mode)

- Internal/external synchronization (synchronous mode)

- Number of synchronous characters (Synchronous mode)

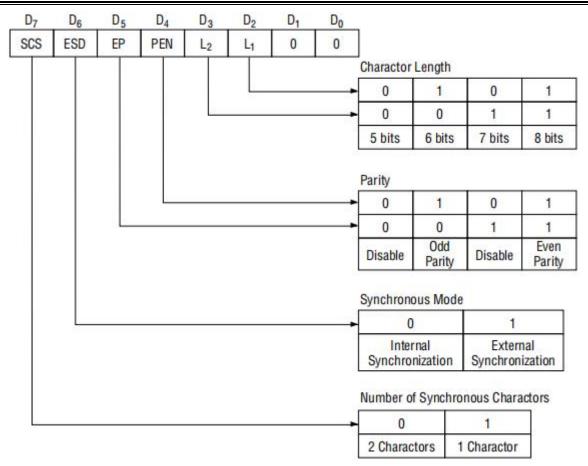

The bit configuration of mode instruction is shown in Figures 2 and 3. In the case of synchronous mode, it is necessary to write one-or two byte sync characters.

If sync characters were written, a function will be set because the writing of sync characters constitutes part of mode instruction.

Fig. 2 Bit Configuration of Mode Instruction (Asynchronous)

Fig. 3 Bit Configuration of Mode Instruction (Synchronous)

### 2) Command

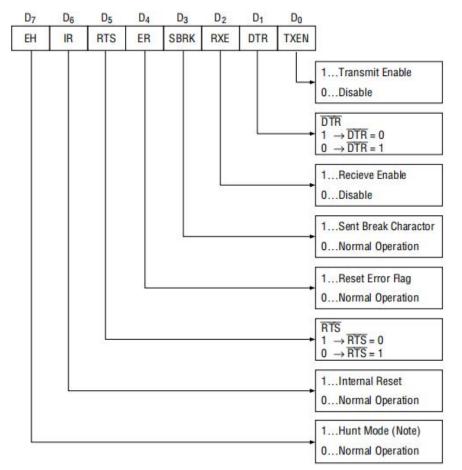

Command is used for setting the operation of the HG82C51.

It is possible to write a command whenever necessary after writing a mode instruction and sync characters.

Items to be set by command are as follows:

- Transmit Enable/Disable

- Receive Enable/Disable

- DTR, RTS Output of data.

- · Resetting of error flag.

- Sending to break characters

- Internal resetting

- Hunt mode (synchronous mode)

### THE BIT CONFIGURATION OF A COMMAND IS SHOWN IN FIG. 4.

Note: Seach mode for synchronous

charactors in synchronous mode.

Fig. 4 Bit Configuration of Command

### **Status Word**

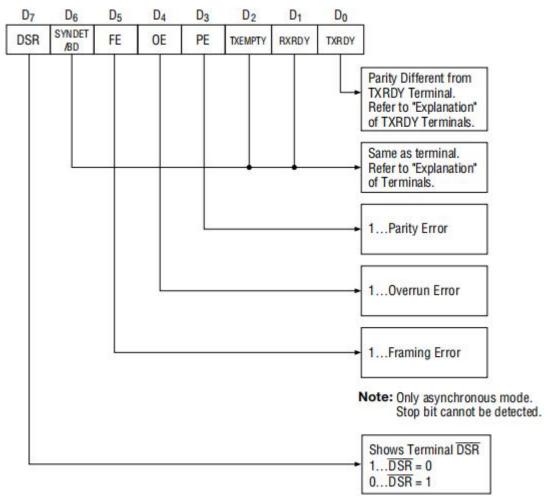

It is possible to see the internal status of HG82C51 by reading a status word.

The bit configuration of status word is shown in Fig. 5.

Fig. 5 Bit Configuration of Status Word

# **Standby Status**

It is possible to put the HG82C51 in standby status

When the following conditions have been satisfied the HG82C51 is in standby status.

- (1)  $\overline{CS}$  terminal is fixed at Vcc level.

- (2) Input pins other  $\overline{CS}$ , D0 to D7,  $\overline{RD}$ ,  $\overline{WR}$  and C/D are fixed at Vcc or GND level (including SYNDET in external synchronous mode).

Note: When all output currents are 0, ICCS specification is applied.

### **Pin Description**

### D<sub>0</sub> to D<sub>7</sub> (I/O terminal)

This is bidirectional data bus which receive control words and transmits data from the CPU and sends status words and received data to CPU.

### **RESET (Input terminal)**

A High on this input forces the HG82C51 into reset status.

The device waits for the writing of "mode instruction."

The min. reset width is six clock inputs during the operating status of CLK.

### **CLK** (Input terminal)

CLK signal is used to generate internal device timing.

CLK signal is independent of  $\overline{RXC}$  or  $\overline{TXC}$ .

However, the frequency of CLK must be greater than 30 times the  $\overline{\text{RXC}}$  and  $\overline{\text{TXC}}$  at Synchronous mode and Asynchronous "x1" mode, and must be greater than 5 times at Asynchronous "x16" and "x64" mode.

### WR (Input terminal)

This is the "active low" input terminal which receives a signal for writing transmit data and control words from the CPU into the HG82C51.

### **RD** (Input terminal)

This is the "active low" input terminal which receives a signal for reading receive data and status words from the HG82C51.

### C/D(Input terminal)

This is an input terminal which receives a signal for selecting data or command words and status words when the HG82C51 is accessed by the CPU.

If C/D = low, data will be accessed.

If C/D = high, command word or status word will be accessed.

### **CS** (Input terminal)

This is the Úactive lowÛ input terminal which selects the HG82C51 at low level when the CPU accesses.

Note: The device won't be in "standby status"; only setting CS = High.

Refer to "Explanation of Standby Status."

### TXD (output terminal)

This is an output terminal for transmitting data from which serial-converted data is sent out. The device is in "mark status" (high level) after resetting or during a status when transmit is disabled. It is also possible to set the device in "break status" (low level) by a command.

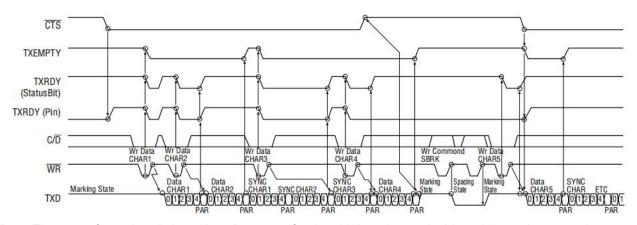

### **TXRDY** (output terminal)

This is an output terminal which indicates that the HG82C51 is ready to accept a transmitted data character. But the terminal is always at low level if  $\overline{CTS}$  = high or the device was set in "TX disable status" by a command.

Note: TXRDY status word indicates that transmit data character is receivable, regardless of  $\overline{\text{CTS}}$  or command. If the CPU writes a data character, TXRDY will be reset by the leading edge or  $\overline{\text{WR}}$  signal.

### **TXEMPTY (Output terminal)**

This is an output terminal which indicates that the HG82C51 has transmitted all the characters and had no data character.

In "synchronous mode," the terminal is at high level, if transmit data characters are no longer remaining and sync characters are automatically transmitted. If the CPU writes a data character, TXEMPTY will be reset by the leading edge of  $\overline{WR}$  signal.

Note: As the transmitter is disabled by setting  $\overline{\text{CTS}}$  "High" or command, data written before disable will be sent out. Then TXD and TXEMPTY will be "High".

Even if a data is written after disable, that data is not sent out and TXE will be "High". After the transmitter is enabled, it sent out. (Refer to Timing Chart of Transmitter Control and Flag Timing)

### TXC (Input terminal)

This is a clock input signal which determines the transfer speed of transmitted data.

In "synchronous mode," the baud rate will be the same as the frequency of  $\overline{TXC}$ .

In "asynchronous mode", it is possible to select the baud rate factor by mode instruction.

It can be 1, 1/16 or 1/64 the  $\overline{TXC}$ .

The falling edge of  $\overline{TXC}$  sifts the serial data out of the HG82C51.

#### **RXD** (input terminal)

This is a terminal which receives serial data.

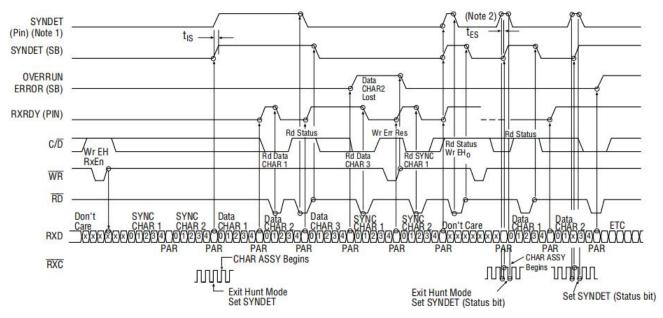

### **RXRDY** (Output terminal)

This is a terminal which indicates that the HG82C51 contains a character that is ready to READ. If the CPU reads a data character, RXRDY will be reset by the leading edge of  $\overline{\text{RD}}$  signal. Unless the CPU reads a data character before the next one is received completely, the preceding data will be lost. In such a case, an overrun error flag status word will be set.

### **RXC** (Input terminal)

This is a clock input signal which determines the transfer speed of received data.

In "synchronous mode," the baud rate is the same as the frequency of  $\overline{RXC}$ .

In "asynchronous mode," it is possible to select the baud rate factor by mode instruction.

It can be 1, 1/16, 1/64 the  $\overline{RXC}$ .

### SYNDET/BD (Input or output terminal)

This is a terminal whose function changes according to mode.

In "internal synchronous mode." this terminal is at high level, if sync characters are received and synchronized. If a status word is read, the terminal will be reset.

In "external synchronous mode, "this is an input terminal.

A High on this input forces the HG82C51 to start receiving data characters.

In "asynchronous mode," this is an output terminal which generates "high level"output upon the detection of a "break" character if receiver data contains a "low-level" space between the stop bits of two continuous characters. The terminal will be reset, if RXD is at high level.

After Reset is active, the terminal will be output at low level.

### **DSR** (Input terminal)

This is an input port for MODEM interface. The input status of the terminal can be recognized by the CPU reading status words.

### **DTR** (Output terminal)

This is an output port for MODEM interface. It is possible to set the status of  $\overline{DTR}$  by a command.

### **CTS** (Input terminal)

This is an input terminal for MODEM interface which is used for controlling a transmit circuit.

The terminal controls data transmission if the device is set in "TX Enable" status by a command.

Data is transmitable if the terminal is at low level.

### **RTS** (Output terminal)

This is an output port for MODEM interface. It is possible to set the status  $\overline{RTS}$  by a command.

### **ABSOLUTE MAXIMUM RATING**

| Parameter                                   | Symbol           | Rating           | Unit | Conditions          |  |

|---------------------------------------------|------------------|------------------|------|---------------------|--|

| Power Supply Voltage                        | V <sub>CC</sub>  | –0.5 to +7       | V    | 1450                |  |

| Input Voltage                               | V <sub>IN</sub>  | -0.5 to VCC +0.5 | V    | With respect to GND |  |

| Output Voltage                              | V <sub>OUT</sub> | -0.5 to VCC +0.5 | V    | IO GND              |  |

| Storage Temperature                         | T <sub>STG</sub> | –55 to +150      | °C   | _                   |  |

| Power Dissipation                           | P <sub>D</sub>   | 0.9              | W    | Ta = 25°C           |  |

| Lead Temperature<br>(Soldering, 10 seconds) | T∟               | 260              | °C   |                     |  |

Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured.

# **OPERATING RANGE**

| Parameter             | Symbol          | Range      | Unit |

|-----------------------|-----------------|------------|------|

| Power Supply Voltage  | V <sub>cc</sub> | 3 - 6      | V    |

| Operating Temperature | T <sub>op</sub> | -40 to +85 | °C   |

### RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol   | Min. | Тур. | Max.     | Unit |

|-----------------------|----------|------|------|----------|------|

| Power Supply Voltage  | $V_{CC}$ | 4.5  | 5    | 5.5      | V    |

| Operating Temperature | $T_{op}$ | -40  | +25  | +85      | °C   |

| "L" Input Voltage     | $V_{IL}$ | -0.3 | _    | +0.8     | V    |

| "H" Input Voltage     | $V_{IH}$ | 2.2  | _    | VCC +0.3 | V    |

### **DC CHARACTERISTICS**

$(V_{CC} = 4.5 \text{ to } 5.5 \text{ V Ta} = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter               | Symbol           | Min. | Тур. | Max. | Unit | Measurement Conditions                                            |

|-------------------------|------------------|------|------|------|------|-------------------------------------------------------------------|

| "L" Output Voltage      | V <sub>OL</sub>  |      | _    | 0.45 | V    | IOL = 2.5 mA                                                      |

| "H" Output Voltage      | V <sub>OH</sub>  | 3.7  | _    | _    | V    | IOH = -2.5 mA                                                     |

| Input Leak Current      | I <sub>LI</sub>  | -10  | _    | 10   | MA   | $0 \le V_{IN} \le V_{CC}$                                         |

| Output Leak Current     | I <sub>LO</sub>  | -10  | _    | 10   | μA   | 0 ≤V <sub>OUT</sub> ≤V <sub>CC</sub>                              |

| Operating SupplyCurrent | I <sub>cco</sub> | 1    | _    | 5    | mA   | Asynchronous X64 during Transmitting/<br>Receiving                |

| Standby SupplyCurrent   | I <sub>ccs</sub> | _    | _    | 100  | μA   | All Input voltage shall be fixed at V <sub>CC</sub> or GND level. |

# **AC CHARACTERISTICS**

### **CPU Bus Interface Part**

$(V_{CC} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Ta} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                             | Symbol            | Min. | Max. | Unit | Remarks |

|---------------------------------------|-------------------|------|------|------|---------|

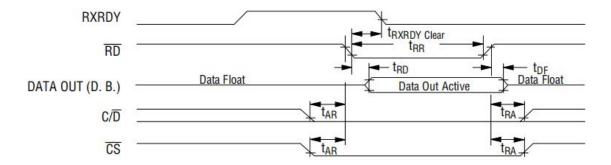

| Address Stable before RD              | t <sub>AR</sub>   | 20   | _    | ns   | Note 2  |

| Address Hold Time for $\overline{RD}$ | t <sub>RA</sub>   | 20   | _    | ns   | Note 2  |

| RD Pulse Width                        | t <sub>RR</sub>   | 130  | _    | ns   | _       |

| Data Delay from $\overline{RD}$       | t <sub>RD</sub>   | _    | 100  | ns   | _       |

| RD to Data Float                      | t <sub>DF</sub>   | 10   | 75   | ns   | _       |

| Recovery Time between $\overline{RD}$ | t <sub>RVR</sub>  | 6    | _    | tCY  | Note 5  |

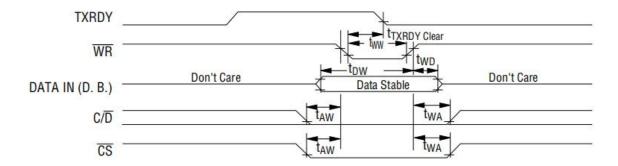

| Address Stable before WRR             | t <sub>AW</sub>   | 20   | _    | ns   | Note 2  |

| Address Hold Time for WR              | t <sub>WA</sub>   | 20   | _    | ns   | Note 2  |

| WR Pulse Width                        | t <sub>ww</sub>   | 100  | _    | ns   | _       |

| Data Set-up Time for WR               | t <sub>DW</sub>   | 100  | _    | ns   | _       |

| Data Hold Time for $\overline{WR}$    | t <sub>WD</sub>   | 0    | _    | ns   | _       |

| Recovery Time between WR              | t <sub>Rvw</sub>  | 6    | _    | tCY  | Note 4  |

| RESET Pulse Width                     | t <sub>RESW</sub> | 6    | _    | tCY  | _       |

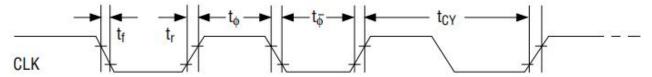

### **SERIAL INTERFACE PART**

$(V_{CC} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Ta} = -40 \text{ to } 85^{\circ}\text{C})$

| Parame                            | Symbol                 | Min.                            | Max. | Unit            | Remarks         |        |  |

|-----------------------------------|------------------------|---------------------------------|------|-----------------|-----------------|--------|--|

| Main Clock Period                 |                        | t <sub>CY</sub>                 | 160  | _               | ns              | Note 3 |  |

| Clock Low Tme                     |                        | t <sub>f</sub>                  | 50   | _               | ns              | _      |  |

| Clock High Time                   |                        | t <sub>f</sub>                  | 70   | tCY -50         | ns              | _      |  |

| Clock Rise/Fall Time              |                        | t <sub>r</sub> , t <sub>f</sub> | _    | 20              | ns              | _      |  |

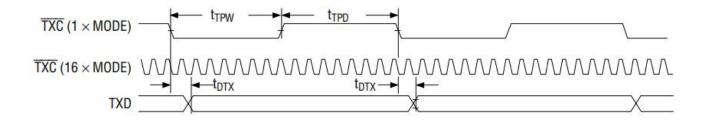

| TXD Delay from Falling Edge of 7  | t <sub>DTX</sub>       | _                               | 1    | mS              | _               |        |  |

|                                   | 1 ×Baud                | f <sub>TX</sub>                 | DC   | 64              | kHz             |        |  |

| Transmitter Clock Frequency       | 16 ×Baud               | f <sub>TX</sub>                 | DC   | 615             | kHz             | Note 3 |  |

| . ,                               | 64 ×Baud               | f <sub>TX</sub>                 | DC   | 615             | kHz             | 1      |  |

| T ''' OLI I T'                    | 1 ×Baud                | t <sub>TPW</sub>                | 13   | _               | t <sub>CY</sub> | _      |  |

| Transmitter Clock Low Time        | 16 ×, 64 ×Baud         | t <sub>TPW</sub>                | 2    | _               | t <sub>CY</sub> | _      |  |

| - ··· o                           | 1 ×Baud                | t <sub>TPD</sub>                | 15   | _               | t <sub>CY</sub> | _      |  |

| Transmitter Clock High Time       | 16 ×, 64 ×Baud         | t <sub>TPD</sub>                | 3    | _               | t <sub>CY</sub> | _      |  |

|                                   | 1 ×Baud                | f <sub>RX</sub>                 | DC   | 64              | kHz             |        |  |

| Receiver Clock Frequency          | 16 ×Baud               | f <sub>RX</sub>                 | DC   | 615             | kHz             | Note 3 |  |

|                                   | 64 ×Baud               | f <sub>RX</sub>                 | DC   | 615             | kHz             |        |  |

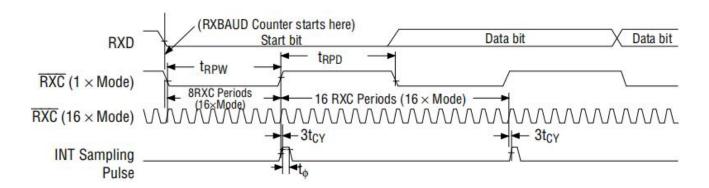

|                                   | 1 ×Baud                | t <sub>RPW</sub>                | 13   | _               | t <sub>CY</sub> | _      |  |

| Receiver Clock Low Time           | 16 ×, 64 ×Baud         | t <sub>RPW</sub>                | 2    | _               | t <sub>CY</sub> | _      |  |

| D : 0: 11:1 T                     | 1 ×Baud                | t <sub>RPD</sub>                | 15   | _               | t <sub>CY</sub> | _      |  |

| Receiver Clock High Time          | 16×, 64 ×Baud          | t <sub>RPD</sub>                | 3    | _               | t <sub>CY</sub> | _      |  |

| Time from the Center of Last Bit  | to the Rise ofTXRDY    | t <sub>TXRDY</sub>              | _    | 8               | t <sub>CY</sub> | _      |  |

| Time from the Leading Edge of V   | VR to the Fallof TXRDY | t <sub>TXRDY CLEAR</sub>        | _    | 400             | ns              | _      |  |

| Time From the Center of Last Bit  | to the Rise of RXRDY   | t <sub>RXRDY</sub>              | _    | 26              | t <sub>CY</sub> | _      |  |

| Time from the Leading Edge of F   | TD to the Fallof RXRDY | t <sub>rxrdy clear</sub>        | _    | 400             | ns              | _      |  |

| Internal SYNDET Delay Time from   | n Rising Edge of RXC   | t <sub>IS</sub>                 | _    | 26              | t <sub>CY</sub> | _      |  |

| SYNDET Setup Time for RXC         | t <sub>ES</sub>        | 18                              | _    | t <sub>CY</sub> |                 |        |  |

| TXE Delay Time from the Center    | t <sub>TXEMPTY</sub>   | 20                              | _    | t <sub>CY</sub> | _               |        |  |

| MODEM Control Signal Delay Tir    | t <sub>wc</sub>        | 8                               | _    | t <sub>CY</sub> |                 |        |  |

| MODEM Control Signal Setup Tir    | t <sub>CR</sub>        | 20                              | _    | t <sub>CY</sub> | _               |        |  |

| RXD Setup Time for Rising Edge    | of RXC (1X Baud)       | t <sub>RXDS</sub>               | 11   | _               | t <sub>CY</sub> | _      |  |

| RXD Hold Time for Falling Edge of | of RXC (1X Baud)       | t <sub>RXDH</sub>               | 17   |                 | t <sub>CY</sub> |        |  |

### Notes:

- 1. AC characteristics are measured at 150 pF capacity load as an output load based on 0.8 V at low level and 2.2 V at high level for output and 1.5 V for input.

- 2. Addresses are  $\overline{\text{CS}}$  and  $\text{C}/\overline{\text{D}}$ .

- 3. fTX or fRX  $\leq$  1/(30 Tcy) 1× Baud , fTX or fRX  $\leq$  1/(5 Tcy) 16×, 64× Baud

- 4. This recovery time is mode Initialization only. Recovery time between command writes for Asynchronous Mode is 8 tCY and for Synchronous Mode is 18 tCY. Write Data is allowed only when TXRDY = 1.

- 5. This recovery time is Status read only. Read Data is allowed only when RXRDY = 1.

- 6. Status update can have a maximum delay of 28 clock periods from event affecting the status.

### **TIMING CHART**

### **Sytem Clock Input**

# TRANSMITTER CLOCK AND DATA

### **RECEIVER CLOCK AND DATA**

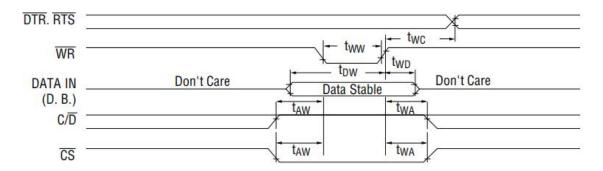

# Write Data Cycle (CPU → USART)

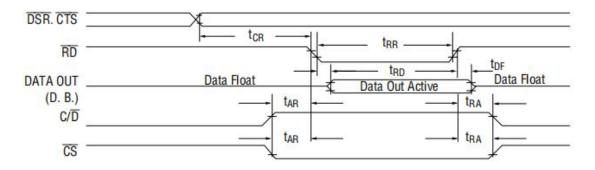

# Read Data Cycle (CPU←USART)

# Write Control or Output Port Cycle (CPU → USART)

# Read Control or Input Port Cycle (CPU→USART)

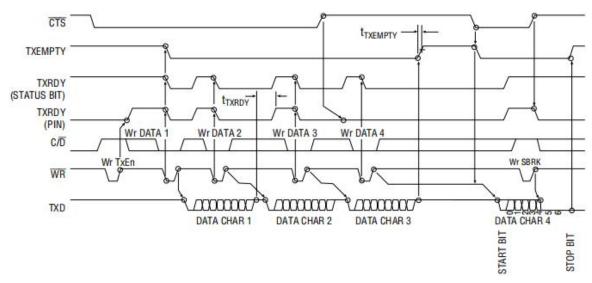

# TRANSMITTER CONTROL AND FLAG TIMING (ASYNC Mode)

Note: The wave-form chart is based on the case of 7-bit data length + parity bit + 2 stop bit.

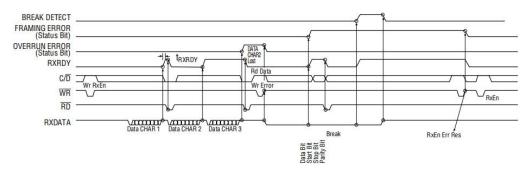

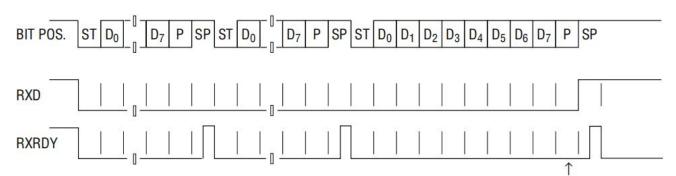

# RECEIVER CONTROL AND FLAG TIMING (ASYNC Mode)

Note: The wave-form chart is based on the case of 7 data bit length + parity bit + 2 stop bit.

# TRANSMITTER CONTROL AND FLAG TIMING (SYNC Mode)

Note: The wave-form chart is based on the case of 5 data bit length + parity bit and 2 synchronous charactors.

# RECEIVER CONTROL AND FLAG TIMING (SYNC Mode)

#### Note:

- 1. Internal Synchronization is based on the case of 5 data bit length + parity bit and 2 synchronous charactor.

- 2. External Synchronization is based on the case of 5 data bit length + parity bit.

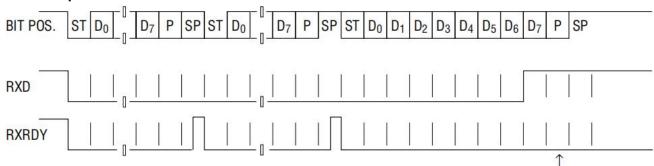

**Note:** 1. Half-bit processing for the start bit When the HG82C51 is used in the asynchronous mode, some problems are caused in the processing for the start bit whose length is smaller than the 1-data bit length. (See Fig. 1.)

| Start bit Length                      | Mode | Operation                                               |

|---------------------------------------|------|---------------------------------------------------------|

| Smaller than 7-Receiver Clock Length  | ×16  | The short start bit is ignored. (Normal)                |

| Smaller than 31-Receiver Clock Length | ×64  | The short start bit is ignored. (Normal)                |

| 8-Receiver Clock Length               | ×16  | Data cannot be received correctly due to a malfunction. |

| 32-Receiver Clock Length              | ×64  | Data cannot be received correctly due to a malfunction. |

| 9 to 16-Receiver Clock Length         | ×16  | The bit is regarded as a start bit. (normal)            |

| 33 to 64-Receiver Clock Length        | ×64  | The bit is regarded as a start bit. (normal)            |

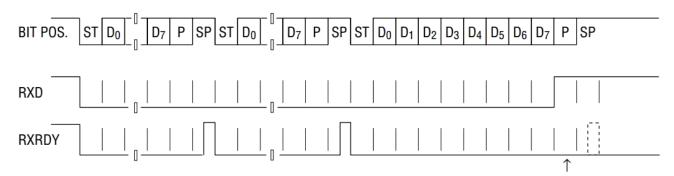

2. Parity flag after a break signal is received (See Fig. 2.)

When the HG82C51 is used in the asynchrous mode, a parity flag may be set when the next normal data is read after a break signal is received.

A parity flag is set when the rising edge of the break signal (end of the break signal) is changed between the final data bit and the parity bit, through a RXRDY signal may not be outputted.

If this occurs, the parity flag is left set when the next normal dats is received, and the received data seems to be a parity error.

# HALF-BIT PROCESSING TIMING CHART FOR THE START BIT (Fig. 1)

#### **Normal Operation** ST D<sub>0</sub> D<sub>1</sub> D<sub>2</sub> D<sub>3</sub> D<sub>4</sub> D<sub>5</sub> D<sub>6</sub> D<sub>7</sub> SP ST D<sub>0</sub> D<sub>1</sub> D<sub>2</sub> D<sub>3</sub> D<sub>4</sub> D<sub>5</sub> D<sub>6</sub> D<sub>7</sub> P SP RXD **RXRDY** The Start bit Is Shorter Than a 1/2 Data bit $D_0$ SP ST $D_1$ D<sub>2</sub> D<sub>3</sub> D<sub>4</sub> D<sub>5</sub> D<sub>6</sub> D<sub>7</sub> RXD ST **RXRDY** The Start bit Is a 1/2 Data bit (A problem of HG82C51) $D_5$ $D_6$ SP ST D<sub>0</sub> $D_1$ $D_2$ RXD ST **RXRDY** A RXRDY signal is outputted during data reception due to a malfunction. The Start bit Is Longer Than a 1/2 Data bit $D_2$ SP ST $D_0$ $D_1$ D<sub>3</sub> D<sub>4</sub> D<sub>5</sub> D<sub>6</sub> D<sub>7</sub> RXD ST **RXRDY** ST: Start bit SP: Stop bit P: Parity bit D<sub>0</sub> - D<sub>7</sub>: Data bits

# **BREAK SIGNAL RECEPTION TIMING AND PARITY FLAG (Fig. 2)**

### **Normal Operation**

A parity flag is set, but, no RXRDYsignal is outputted.

# **BUG** timing

A parity flag is set. But ,no RXRDY signal is outputted.

# **Normal Operation**

19 / 22

A parity flag is set. and a RXRDY signal is outputted.

# PHYSICAL DIMENSIONS

### DIP-28

| Dimensions In Millimeters(DIP-28) |       |       |       |       |      |      |      |      |      |          |

|-----------------------------------|-------|-------|-------|-------|------|------|------|------|------|----------|

| Symbol:                           | Α     | В     | D     | D1    | Е    | L    | L1   | а    | С    | d        |

| Min:                              | 13.21 | 36.70 | 16.00 | 14.99 | 3.71 | 0.38 | 3.00 | 1.45 | 0.38 | 0.54.000 |

| Max:                              | 14.22 | 36.96 | 17.28 | 15.49 | 3.91 | 0.55 | 3.60 | 1.65 | 0.53 | 2.54 BSC |

# **Revision History**

| DATE      | REVISION                                                      | PAGE |

|-----------|---------------------------------------------------------------|------|

| 2018-8-9  | New                                                           | 1-22 |

| 2023-9-11 | Update encapsulation type、Add annotation for Maximum Ratings. | 1、11 |

| 2024-11-7 | Update Lead Temperature                                       | 11   |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.