# Digital Totem Pole PFC Controller with I2C & UART Interfaces

# Hynetek Semiconductor Co., Ltd.

**HP1010**

#### **FEATURES**

Highly flexible digital Totem Pole PFC controller High flexibility digital PWM

- PWM frequency ranges from 20 kHz to 200 kHz

- · PWM soft start during AC line zero-crossing

- Switching frequency spread spectrum for improved EMI

High performance control loop

- 25 MHz sigma-delta ADC for line voltage and current sense, 12.5 MHz sigma-delta ADC for output voltage

- Enhanced dynamic loop response

- Input voltage feedforward to avoid reverse current during AC drop

- Support HVDC input

Multi-mode operations

- Continuous Conduction Mode (CCM) in heavy load Conditions

- Discontinuous Conduction Mode (DCM) in light load conditions

- · Burst mode in the zero load conditions

Advanced control functions

- True RMS power metering

- Inrush current control with programming relay delay

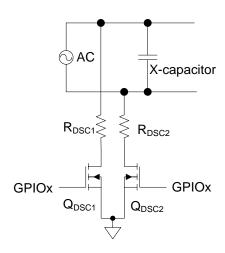

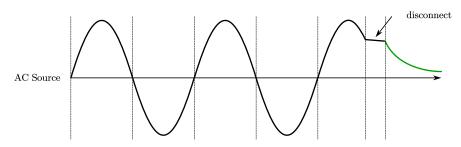

- Two channels X-cap discharge during shut down Extensive fault protections

- Fast over-voltage protection

- Bulk under-voltage protection and over-voltage protection

- External NTC thermal protection

- Cycle-by-cycle current limit

- Average switching current protection

- · Built-in 1 kBit MTP to store custom configurations

Low power consumption

I<sup>2</sup>C and UART interfaces

Programming via easy-to-use Graphical User Interface (GUI)

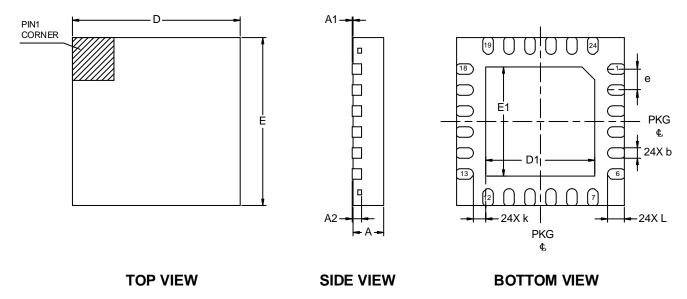

Available in QFN-24L packages

-40°C to 125°C operating temperature

#### **APPLICATIONS**

Ultra-High Efficiency Power Supplies

**LED Lighting**

**Industrial Power Supplies**

Server/Telecom

EV/E-Bike Charger

Supercomputing

Variable-Frequency Drivers (VFD)

#### GENERAL DESCRIPTION

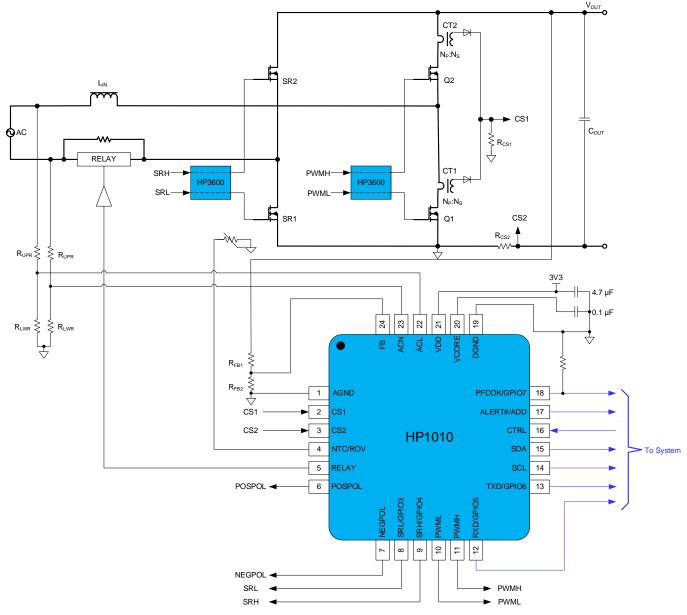

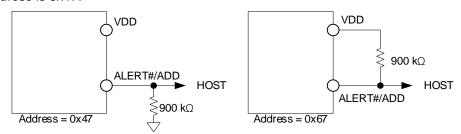

The HP1010 is a highly flexible digital Power Factor Correction (PFC) controller designed to drive a totem pole PFC power stage.

Totem-pole PFC composes of a fast-leg using the third-generation semiconductor (GaN or SiC MOSFET) switching at PWM frequency and a slow-leg operating at the AC frequency. This design allows for a considerable increase in efficiency and power density by removing the diode bridge that is present at the input of a traditional PFC circuit.

The HP1010 offers RMS values of input voltage, current, and power. Through the I<sup>2</sup>C and UART interfaces, this information can be communicated to a microcontroller.

The HP1010 operates from a single 3.3 V supply. The device is available in 4 mm x 4 mm QFN-24L package specified over an ambient temperature range of −40°C to +125°C.

#### **Device Information**

| PART NUMBER | PACKAGE | BODY SIZE   |  |  |

|-------------|---------|-------------|--|--|

| HP1010      | QFN-24L | 4 mm x 4 mm |  |  |

#### TYPICAL APPLICATION CIRCUIT

Figure 1 Typical Application Circuit

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                |    |

| General Description                         |    |

| Typical Application Circuit                 | 2  |

| Table of Contents                           |    |

| Revision History                            |    |

| Pin Configuration and Function Descriptions | 5  |

| Specifications                              |    |

| Absolute Maximum Ratings                    |    |

| Thermal Resistance                          |    |

| ESD Caution                                 | 13 |

| Typical Performance Characteristics         | 14 |

| Theory of Operation                         |    |

| Basic Operating Principle                   |    |

| VDD and VCORE Pins                          | 18 |

| CTRL Pin and Software Enable                |    |

| Input AC voltage (ACL and ACN Pins)         | 19 |

| Output Voltage (FB Pin)                     | 21 |

| Current Sense (CS1 and CS2 Pins)            | 2  |

| Power Factor Correction Control Loop        | 25 |

| Digital Pulse Modulation                    | 26 |

| Operation Modes                             | 27 |

| GPIO Pins & Functions                       | 28 |

| Relay Control                               | 28 |

| X-capacitor Discharge                       | 29 |

| Fault, Protections and Monitorins           | 3′ |

| Fault Flags and Protections                 | 3′ |

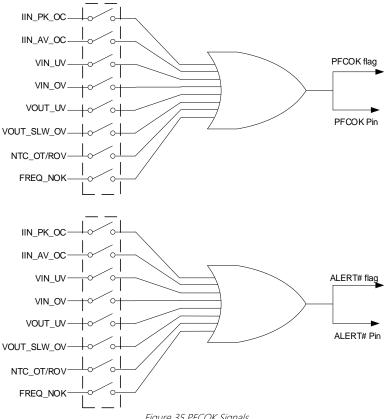

| PFCOK And Alert# Pins                       | 32 |

| OTP & Redundant OVP (NTC/ROV Pin)           | 32 |

| Surge protection                            | 33 |

| Power Metering                              | 34 |

| Commication Interfaces And EEPROM           | 35 |

| I <sup>2</sup> C Interface                  | 35 |

| UART Interface                              | 35 |

| EEPROM                                      | 36 |

| Application Information                     | 37 |

| Totem Pole Power Factor Correction          | 37 |

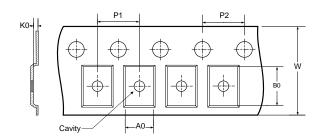

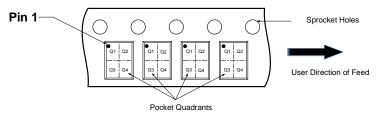

| Package Outline Dimensions                  | 38 |

| Package Top Marking                         | 39 |

| Ordering Guide                              | 40 |

| Tape And Reel Information                   |    |

| Important Notice                            | 42 |

# **REVISION HISTORY**

| Version  | Date    | Owner    | Descriptions    |

|----------|---------|----------|-----------------|

| Rev. 1.0 | 03/2024 | Eric Liu | Initial version |

|          |         |          |                 |

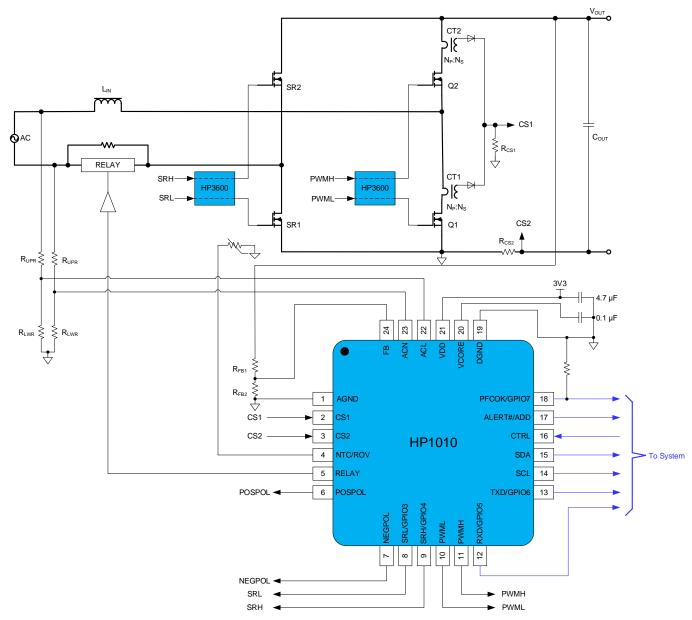

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

**TOP VIEW** 1 **AGND** 18 PFCOK/GPIO7 2 17 CS1 ALERT#/ADD 3 16 **CTRL** CS2 HP1010 4 mm x 4 mm QFN-24 4 15 NTC/ROV **SDA RELAY/GPIO0** 5 14 SCL (Not to Scale) POSPOL/GPIO1 6 13 TXD/GPIO6 NEGPOL/GPI02 RXD/GPI05 SRL/GPI03 SRH/GPI04

Figure 2 HP1010-BA000-QN24R Pin Assignment

**Table 1. Pin Function Descriptions**

| Pin No. | Name             | Type <sup>1</sup> | Description                                                                                                                                                                                                                                 | GPIO |

|---------|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1       | AGND             | Р                 | Analog ground. AGND should be connected directly to DGND.                                                                                                                                                                                   |      |

| 2       | CS1              | Al                | This pin senses the inductor current upslope through current sense transformers in the TPPFC topology. It is used to reconstruct the inductor current. It is also used for cycle-by-cycle current limiting. The signal is referred to AGND. |      |

| 3       | CS2              | Al                | The pin optionally senses the inductor current downslope. The signal is referred to AGND.                                                                                                                                                   |      |

| 4       | NTC/ROV          | Al                | Dual function for this pin. NTC: Temperature sense input, which is inverse proportional to the temperature, triggers the comparator when OTP happens.                                                                                       |      |

|         |                  |                   | ROV: redundant OVP comparator with a programmable reference. The signal is referred to AGND.                                                                                                                                                |      |

| 5       | RELAY/GPIO<br>0  | DO                | Relay control output. The turn-on delay can be programmed. The signal is referred to DGND.                                                                                                                                                  | Yes  |

|         |                  |                   | It can be re-used as GPIO pin.                                                                                                                                                                                                              |      |

| 6       | POSPOL/GPI<br>O1 | DO                | Output of the internal AC polarity detection circuit. The signal is referred to DGND.                                                                                                                                                       | Yes  |

|         |                  |                   | It can be re-used as GPIO pin.                                                                                                                                                                                                              |      |

| 7       | NEGPOL/GPI<br>O2 | DO                | Inverted output of the internal AC polarity detection circuit. The signal is referred to DGND.                                                                                                                                              | Yes  |

|         |                  |                   | It can be re-used as GPIO pin.                                                                                                                                                                                                              |      |

| 8       | SRL/GPIO3        | DO                | Control signal for low side slow leg device. The signal is referred to DGND.                                                                                                                                                                | Yes  |

|         |                  |                   | It can be re-used as GPIO pin.                                                                                                                                                                                                              |      |

| 9       | SRH/GPIO4        | DO                | Control signal for high side slow leg device. The signal is referred to DGND.                                                                                                                                                               | Yes  |

|         |                  |                   | It can be re-used as GPIO pin.                                                                                                                                                                                                              |      |

| 10      | PWML             | DO                | PWM logic output for control of low side fast leg switch. The signal is referred to DGND.                                                                                                                                                   |      |

| Pin No. | Name            | Type <sup>1</sup> | Description                                                                                                                                                                    | GPIO |

|---------|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 11      | PWMH            | DO                | PWM logic output for control of high side fast leg switch. The signal is referred to DGND.                                                                                     |      |

| 12      | RXD/GPIO5       | DIO               | UART_RX pin. The signal is referred to DGND.                                                                                                                                   | Yes  |

|         |                 |                   | It can be re-used as GPIO pin.                                                                                                                                                 |      |

| 13      | TXD/GPIO6       | DIO               | UART_TX pin. The signal is referred to DGND.                                                                                                                                   | Yes  |

|         |                 |                   | It can be re-used as GPIO pin.                                                                                                                                                 |      |

| 14      | SCL             | AIO               | I <sup>2</sup> C serial clock line. The SCL signal is referred to DGND.                                                                                                        |      |

| 15      | SDA             | AIO               | I <sup>2</sup> C serial data line. The SDA signal is referred to DGND.                                                                                                         |      |

| 16      | CTRL            | DI                | Remote control pin. The signal is referred to DGND.                                                                                                                            |      |

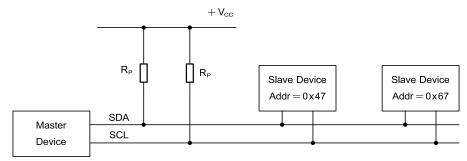

| 17      | ALERT#/ADD      | DIO               | I <sup>2</sup> C alert pin. The signal is referred to DGND.                                                                                                                    |      |

|         |                 |                   | During the power on reset, the state of this pin is sampled as address select input for I <sup>2</sup> C bus.                                                                  |      |

|         |                 |                   | Note: a 900 k $\Omega$ resistor should be used when connecting to VDD or DGND to reduce standby current.                                                                       |      |

|         |                 |                   | HIGH = I <sup>2</sup> C address is 0x67                                                                                                                                        |      |

|         |                 |                   | LOW = I <sup>2</sup> C address is 0x47                                                                                                                                         |      |

| 18      | PFCOK/GPIO<br>7 | DIO               | The PFCOK/GPIO supports dual functions. The PFCOK function is held low when the PFC output voltage is out of regulation and during fault conditions. It is a push-pull output. | Yes  |

|         |                 |                   | It can be re-used as GPIO pin.                                                                                                                                                 |      |

| 19      | DGND            | Р                 | Digital Ground. DGND should be connected directly to AGND.                                                                                                                     |      |

| 20      | VCORE           | Р                 | 1.8 V VDD for digital core. The VCORE signal is referred to DGND. Connect a 100 nF capacitor from VCORE to DGND.                                                               |      |

| 21      | VDD             | Р                 | 3.3 V main supply input. The VDD signal is referred to AGND. Connect a 4.7 µF capacitor from VDD to AGND.                                                                      |      |

| 22      | ACL             | Al                | AC line voltage sense. The signal is referred to AGND.                                                                                                                         |      |

| 23      | ACN             | Al                | AC neutral voltage sense. The signal is referred to AGND.                                                                                                                      |      |

| 24      | FB              | Al                | PFC output voltage sense for loop regulation. The signal is referred to AGND.                                                                                                  |      |

<sup>&</sup>lt;sup>1</sup> Legend: A = Analog Pin P = Power Pin D = Digital Pin I = Input Pin O = Output Pin

# **SPECIFICATIONS**

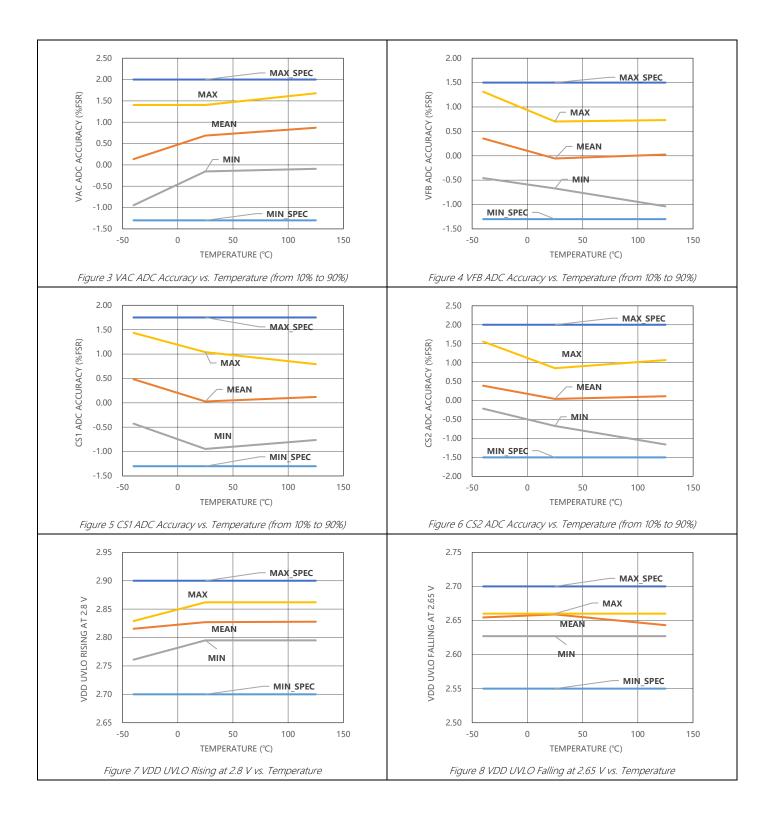

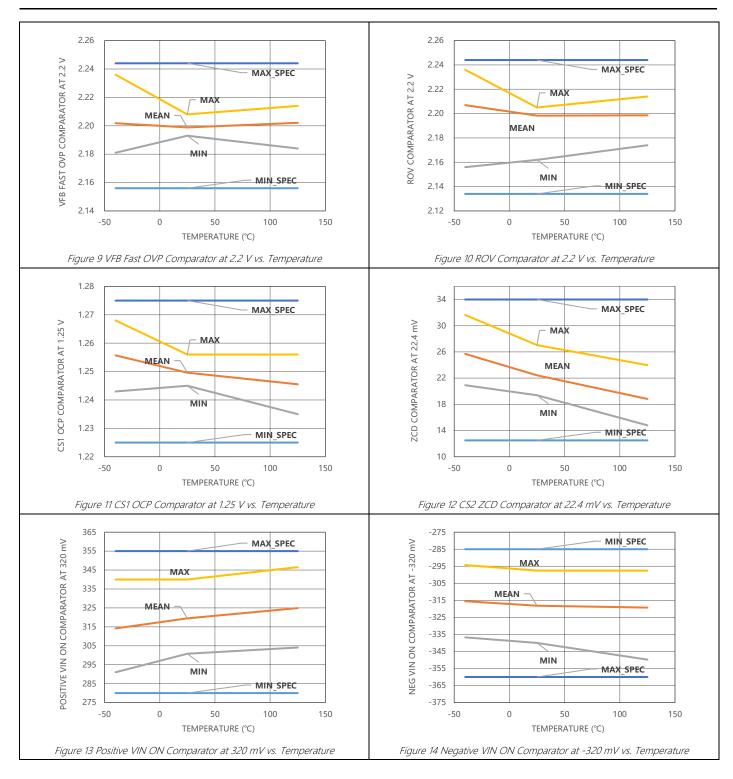

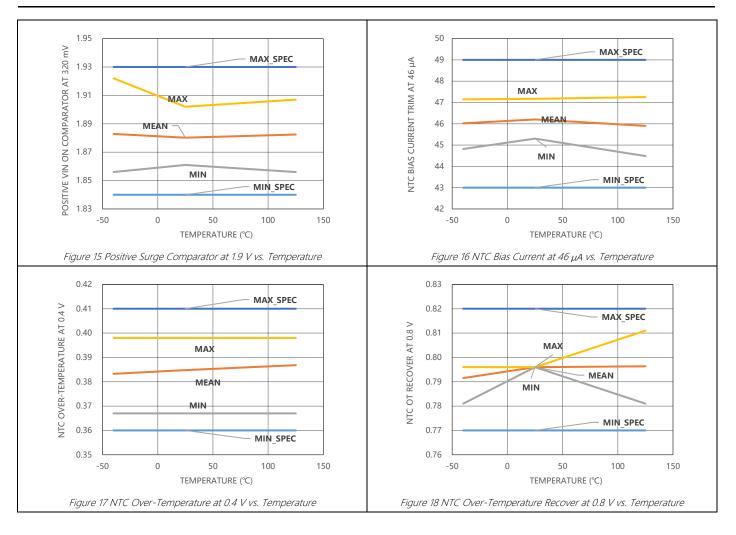

$V_{DD} = 3.3 \text{ V}$ ,  $T_J = -40 ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$  for minimum and maximum specifications, and  $T_A = 25 ^{\circ}\text{C}$  for typical specifications, unless otherwise noted.

**Table 2. Specifications**

| Parameter                                        | Symbol                  | Conditions                                 | Min                  | Тур   | Max    | Unit |

|--------------------------------------------------|-------------------------|--------------------------------------------|----------------------|-------|--------|------|

| POWER SUPPLY                                     |                         |                                            |                      |       |        |      |

| Operating Supply Voltage                         | V <sub>DD</sub>         | 4.7 μF capacitor connected to AGND         | 3                    | 3.3   | 3.6    | V    |

| Supply Current                                   | I <sub>DD</sub>         | Normal operation                           |                      | 10.0  |        | mA   |

| Peak Supply Current                              | I <sub>DD_PK</sub>      | $V_{DD} = 4.0 \text{ V}$ while programming |                      |       | 7.5    | mA   |

| Shutdown Current                                 | I <sub>DD_SD</sub>      | PFC off state                              |                      | 8.1   |        | mA   |

| Sleep Mode Current                               | I <sub>DD_SM</sub>      | Sleep mode enabled.                        |                      | 1.0   |        | mA   |

| POWER-ON RESET                                   |                         |                                            |                      |       |        |      |

| Power-on Reset                                   | $V_{DD\_POR}$           | V <sub>DD</sub> rising                     | 2.7                  | 2.8   | 2.9    | V    |

| UVLO                                             | $V_{DD\_UVLO}$          | V <sub>DD</sub> falling                    | 2.55                 | 2.65  | 2.75   | V    |

| VCORE PIN                                        |                         |                                            |                      |       |        |      |

| Output Voltage                                   | V <sub>CORE</sub>       | 100 nF capacitor connected to DGND         | 1.7                  | 1.8   | 1.9    | V    |

| OSCILLATOR, CLOCK, PLL                           |                         |                                            |                      |       |        |      |

| Oscillator Frequency                             | fosc                    |                                            | 11.875               | 12.5  | 13.125 | MHz  |

| PLL Frequency                                    | $f_{PLL}$               |                                            | 190                  | 200   | 210    | MHz  |

| Digital PWM Resolution                           | tpwm_res                | For PWML and PWMH pins                     |                      | 5     |        | ns   |

| PWMH, PWML, SRH, SRL, POSPOL, NEGPOL, RELAY PINS |                         |                                            |                      |       |        |      |

| Output Low Voltage                               | V <sub>PWMOL</sub>      | Sink current = 10 mA                       |                      |       | 0.4    | V    |

| Output High Voltage                              | V <sub>PWMOH</sub>      | Source current = 10 mA                     | V <sub>DD</sub> -0.4 |       |        | V    |

| Rise time                                        | t <sub>RISE</sub>       | C <sub>LOAD</sub> = 50 pF                  |                      | 4.0   |        | ns   |

| Fall time                                        | t <sub>FALL</sub>       | C <sub>LOAD</sub> = 50 pF                  |                      | 4.0   |        | ns   |

| Output Source Current                            | I <sub>OL</sub>         |                                            | -10                  |       |        | mA   |

| Output Sink Current                              | Іон                     |                                            |                      |       | 10     | mA   |

| SWITCHING FREQUENCY                              |                         |                                            |                      |       |        |      |

| Frequency Range                                  | fsw                     | See Table 8                                | 20                   |       | 195    | kHz  |

| Accuracy                                         |                         |                                            | -3                   |       | 3      | %    |

| ACN AND ACL PINS                                 |                         |                                            |                      |       |        |      |

| External Divider Ratio                           | K <sub>AC_DIV_EXT</sub> |                                            |                      | 1/200 |        |      |

| Input Voltage Range                              | V <sub>AC</sub>         |                                            | 0                    |       | 2.8    | V    |

| Amplifier Gain                                   | G <sub>AC_OP</sub>      |                                            |                      | 0.5   |        |      |

| ADC                                              |                         |                                            |                      |       |        |      |

| ADC Range                                        |                         |                                            | 0                    |       | 1.4    | V    |

| ADC Clock Frequency                              |                         |                                            |                      | 25    |        | MHz  |

| Equivalent Resolution                            |                         | Data updating frequency 25 kHz             |                      | 10    |        | Bits |

| Voltage Sense Accuracy                           |                         | 10% to 90% of usable range                 | -1.3                 |       | 2.0    | %FSR |

| Positive Comparator for VIN On                   |                         |                                            |                      |       |        |      |

| Threshold Range <sup>1</sup>                     | V <sub>AC_POS</sub>     |                                            | 200                  | 320   | 480    | mV   |

| -                                                | I                       |                                            | 1                    |       |        | 1    |

| Parameter                           | Symbol                  | Conditions                                      | Min   | Тур  | Max  | Unit   |

|-------------------------------------|-------------------------|-------------------------------------------------|-------|------|------|--------|

| Resolution                          |                         |                                                 |       | 3    |      | Bits   |

| LSB                                 |                         |                                                 |       | 40   |      | mV     |

| Hysteresis                          |                         |                                                 | 30    | 45   | 70   | mV     |

| Propagation Delay                   |                         |                                                 |       |      | 1.0  | μs     |

| Negative Comparator for VIN On      |                         |                                                 |       |      |      |        |

| Threshold Range <sup>1</sup>        | V <sub>AC_NEG</sub>     |                                                 | -480  | -320 | -200 | mV     |

| Threshold Accuracy                  |                         | Factory trimmed at -320 mV                      | -340  | -318 | -297 | mV     |

| Resolution                          |                         |                                                 |       | 3    |      | Bits   |

| LSB                                 |                         |                                                 |       | 40   |      | mV     |

| Hystersis Width                     |                         |                                                 |       | 40   |      | mV     |

| Propagation Delay                   |                         |                                                 |       |      | 1.0  | μs     |

| Positive Comparator for Surge       |                         |                                                 |       |      |      |        |

| Threshold Range <sup>1</sup>        | V <sub>AC_PSUR</sub>    |                                                 | 1.6   | 1.9  | 2.2  | V      |

| Threshold Accuracy                  |                         | Factory trimmed at 1.9 V                        | -2.32 |      | 1.16 | %      |

| Resolution                          |                         |                                                 |       | 4    |      | Bits   |

| LSB                                 |                         |                                                 |       | 40   |      | mV     |

| Hysteresis                          |                         |                                                 | 110   | 135  | 165  | mV     |

| Propagation Delay                   |                         |                                                 |       |      | 1.0  | μs     |

| AC Line Frequency Monitor           |                         |                                                 |       |      |      |        |

| High Threshold                      | f <sub>5060</sub> _H    |                                                 | 68    | 70   | 72   | Hz     |

| Lower Threshold                     | f <sub>5060_L</sub>     |                                                 | 37    | 40   | 43   | Hz     |

| Detection Timer                     | NLINE_DET               |                                                 |       | 4    |      | cycles |

| Exceed Timer                        | N <sub>LINE_FREQ_</sub> |                                                 |       | 4    |      | cycles |

| Brown-out and SAG                   |                         |                                                 |       |      |      |        |

| Vin On Threshold                    | V <sub>IN_ON</sub>      | Programmable,<br>K <sub>AC DIV</sub> EXT=1/200  | 0     | 78   | 255  | VAC    |

| Vin Off Threshold                   | V <sub>IN_OFF</sub>     | Programmable,<br>K <sub>AC_DIV_EXT</sub> =1/200 | 0     | 71   | 255  | VAC    |

| Brown-out Debounce                  | t <sub>BO_DEB</sub>     |                                                 | -     | 0.5  | -    | cycles |

| Line Sag Timeout Range              | tsag_to                 | Programmable 4 to 32 AC cycles                  | 4     | 12   | 32   | cycles |

| High/Low Line Detection             |                         |                                                 |       |      |      |        |

| High Threshold                      | VHLINE                  | Programmable,<br>K <sub>AC_DIV_EXT</sub> =1/200 | 120   | 168  | 180  | VAC    |

| Low Threshold                       | VLLINE                  | Programmable,<br>K <sub>AC_DIV_EXT</sub> =1/200 | 120   | 156  | 180  | VAC    |

| High Line to Low Line Debounce Time | t <sub>H2L_DED</sub>    |                                                 | 20    | 25   | 30   | ms     |

| VAC ZERO CROSSING DETECTION         |                         |                                                 |       |      |      |        |

| VAC Zero Detection Comparator       |                         | Between ACL Pin to ACN pin                      |       |      |      |        |

| Threshold                           | V <sub>POL_DET</sub>    |                                                 | -0.01 | 0    | 0.01 | V      |

| Hysteresis Width                    | V <sub>POL_HYS</sub>    |                                                 |       | 10   |      | mV     |

| Propagation Delay                   | t <sub>POL_PD</sub>     |                                                 |       |      | 1.0  | μs     |

| Digital Polarity Detection          |                         |                                                 |       |      |      |        |

| Digital Propagation Delay           |                         |                                                 |       | 5    |      | μs     |

| VIN_POL Detection Debounce          | tpol_deb                |                                                 | 20    | 200  | 320  | μs     |

| Parameter                     | Symbol                  | Conditions                 | Min   | Тур   | Max  | Unit |

|-------------------------------|-------------------------|----------------------------|-------|-------|------|------|

| VIN_POL Detection LSB         |                         |                            |       | 20    |      | μs   |

| Main PWM Drive Control        |                         |                            |       |       |      |      |

| Main PWM On Threshold         | V <sub>PWM_ON</sub>     |                            | 0     |       | 66   | V    |

| Main PWM Off Threshold        | V <sub>PWM_OFF</sub>    |                            | 0     |       | 66   | V    |

| SYNC PWM Drive Control        |                         |                            |       |       |      |      |

| SYNC On Threshold             | Vsyn_on                 |                            | 0     |       | 66   | V    |

| SYNC Off Threshold            | Vsyn_off                |                            | 0     |       | 66   | V    |

| Slow Leg (SR) Drive Control   |                         |                            |       |       |      |      |

| SR On Threshold               | Vsr_on                  |                            | 0     |       | 66   | V    |

| SR Off Threshold              | Vsr_off                 |                            | 0     |       | 66   | V    |

| SYNC PWM Drive Control 2      |                         |                            |       |       |      |      |

| SYNC On Threshold             | I <sub>SYN_ON_CS</sub>  | Low-line Mode              | 0.2   |       | 3.5  | Α    |

|                               |                         | High-line Mode             | 0.1   |       | 1.75 | Α    |

| SYNC Off Threshold            | I <sub>SYN_OFF_CS</sub> | Low-line Mode              | 0.2   |       | 3.5  | Α    |

|                               |                         | High-line Mode             | 0.1   |       | 1.75 | Α    |

| Slow Leg (SR) Drive Control 2 |                         |                            |       |       |      |      |

| SR On Threshold               | Isron_cs                | Low-line Mode              | 0.2   |       | 3.5  | Α    |

|                               | _                       | High-line Mode             | 0.1   |       | 1.75 | Α    |

| SR Off Threshold              | Isroff_cs               | Low-line Mode              | 0.2   |       | 3.5  | Α    |

|                               |                         | High-line Mode             | 0.1   |       | 1.75 | Α    |

| FB PIN                        |                         |                            |       |       |      |      |

| External Divider Ratio        | K <sub>FB_DIV_EXT</sub> |                            |       | 1/200 |      |      |

| Input Voltage                 |                         |                            | 0     |       | 2.8  | V    |

| Input Impedance               |                         |                            | 500   |       |      | kΩ   |

| Amplifier GBW                 |                         |                            |       | 2     |      | MHz  |

| Amplifier Gain                |                         |                            |       | 0.5   |      |      |

| ADC                           |                         |                            |       |       |      |      |

| ADC Range                     |                         |                            | 0     |       | 1.4  | V    |

| ADC Clock Frequency           |                         |                            |       | 12.5  |      | MHz  |

| Equivalent Resolution         |                         |                            |       | 11    |      | Bits |

| Voltage Sense Accuracy        |                         | 10% to 90% of usable range | -1.3  |       | 1.5  | %FSR |

| Fast Over-Voltage Protection  |                         |                            |       |       |      |      |

| Threshold Range <sup>1</sup>  | V <sub>FB</sub> FOV_LIM |                            | 1.9   | 2.2   | 2.5  | V    |

| Threshold Accuracy            |                         | Factory trimmed at 2.2 V   | -0.86 |       | 1.64 | %    |

| Resolution                    |                         |                            |       | 6     |      | Bits |

| Hysteresis                    |                         |                            | 110   | 135   | 160  | mV   |

| Propagation Delay             | t <sub>FB_FOV_PD</sub>  |                            |       |       | 160  | ns   |

| Debounce Time                 | teb for db              | Programmable in 4 steps    | 40    |       | 100  | μs   |

| Blanking time                 | t <sub>FB_FOV_BK</sub>  |                            |       | 10    |      | μs   |

| Open Loop Protection          |                         |                            |       |       |      | '    |

| Sink Current                  | I <sub>FB_SNK</sub>     |                            |       | 250   |      | nA   |

| Threshold                     | V <sub>FB_OL</sub>      |                            | 20    | -     | 88   | V    |

| Hysteresis                    | V <sub>FB_OLHYS</sub>   |                            |       | 18    |      | V    |

| Debounce Time                 | t <sub>FB_OLDB</sub>    | Programmable in 4 steps    | 0     | -     | 30   | ms   |

| Parameter                        | Symbol                  | Conditions                    | Min                  | Тур  | Max                  | Unit |

|----------------------------------|-------------------------|-------------------------------|----------------------|------|----------------------|------|

| Slow Over-Voltage Protection     |                         |                               |                      |      |                      |      |

| Threshold                        | V <sub>FB_SOV_LIM</sub> |                               | V <sub>REF</sub>     |      | V <sub>REF</sub> +68 | V    |

| Resolution                       |                         |                               |                      | 5    |                      | Bits |

| Accuracy                         |                         |                               | -2                   |      | +2                   | %    |

| Debounce Time                    | t <sub>FB_SOV_DB</sub>  |                               | 0                    |      | 30                   | ms   |

| Slow Under-Voltage Protection    |                         |                               |                      |      |                      |      |

| Threshold                        |                         |                               | V <sub>REF</sub> -68 |      | $V_{REF}$            | V    |

| Resolution                       | $V_{FB\_SUV\_LIM}$      |                               |                      | 5    |                      | Bits |

| Accuracy                         |                         |                               | -2                   |      | +2                   | %    |

| Debounce Time                    | t <sub>FB_SUV_DB</sub>  |                               | 0                    |      | 30                   | ms   |

| CS1 AND CS2 PINS                 |                         |                               |                      |      |                      |      |

| Input Voltage                    |                         |                               | 0                    |      | 1.4                  | V    |

| Input Impedance                  |                         |                               | 1                    |      |                      | МΩ   |

| Amplifier                        |                         |                               |                      |      |                      |      |

| GBW                              |                         |                               |                      | 2    |                      | MHz  |

| Gain                             |                         |                               |                      | 1    |                      |      |

| ADC                              |                         |                               |                      |      |                      |      |

| High Input Voltage Range         |                         |                               | 0                    |      | 1.4                  | V    |

| ADC Clock Frequency              |                         |                               |                      | 25   |                      | MHz  |

| Equivalent Resolution            |                         | Updating frequency at 100 kHz |                      | 8    |                      | Bits |

| Current Sense Accuracy           |                         | 10% to 90% of usable range    | -1.5                 |      | 2.0                  | %FSF |

| CS1 Fast Over Current Protection |                         |                               |                      |      |                      |      |

| Threshold Range <sup>1</sup>     | Vcs1_oc_lim             |                               | 1.0                  | 1.25 | 1.5                  | V    |

| Threshold Accuracy               |                         | Factory trimmed at 1.25 V     | -1.2                 |      | 0.48                 | %    |

| Resolution                       |                         |                               |                      | 6    |                      | Bits |

| LSB                              |                         |                               |                      | 7.8  |                      | mV   |

| Hysteresis                       |                         |                               | 15                   | 25   | 35                   | mV   |

| Propagation Delay                |                         |                               |                      |      | 100                  | ns   |

| Blanking Time                    |                         | Programmable in 4 steps       | 480                  |      | 1920                 | ns   |

| Debounce Time                    |                         | Programmable in 4 steps       | 40                   |      | 160                  | ns   |

| CS2 Zero Crossing Detection      |                         |                               |                      |      |                      |      |

| Threshold Range <sup>1</sup>     | V <sub>CS2_ZCD</sub>    |                               | -100                 | 22.4 | 48                   | mV   |

| Threshold Accuracy               |                         | Factory trimmed at 22.4 mV    | 12.5                 | 22.4 | 33.5                 | mV   |

| Resolution                       |                         |                               |                      | 6    |                      | Bits |

| LSB                              |                         |                               |                      | 3.2  |                      | mV   |

| Hysteresis                       |                         |                               | 35                   | 50   | 75                   | mV   |

| Propagation Delay                |                         |                               |                      |      | 100                  | ns   |

| CTRL PIN                         |                         |                               |                      |      |                      |      |

| Input High Voltage               | V <sub>CTRL_IL</sub>    |                               |                      |      | 8.0                  | V    |

| Input Low Voltage                | V <sub>CTRL_IH</sub>    |                               | 2.0                  |      |                      | V    |

| Debounce Time                    | tctrl_deb               |                               |                      | 10   |                      | μs   |

| Leakage Current                  | ictrl_lk                |                               |                      |      | 1.0                  | μA   |

| Parameter                                 | Symbol               | Conditions               | Min   | Тур | Max  | Unit         |

|-------------------------------------------|----------------------|--------------------------|-------|-----|------|--------------|

| Output Low Level                          |                      |                          |       |     | 0.8  | V            |

| Output High Level                         |                      |                          | 2.0   |     |      | V            |

| Debounce Time                             |                      |                          | 0     |     | 600  | ms           |

| OVER AVERAGE SWITCHING CURRENT PROTECTION |                      |                          |       |     |      |              |

| Average OCP Threshold                     |                      | CS1 Sense ratio is 10:1  | 0     |     | 7    | Α            |

| Resolution                                |                      |                          |       | 7   |      | Bits         |

| Accuracy                                  |                      |                          | -2    |     | +2   | %            |

| Debounce                                  |                      |                          |       | 2   |      | Switch cycle |

| NTC/ROV PIN                               |                      |                          |       |     |      | - ,          |

| Current Source                            | Intc                 |                          | 43    | 46  | 49   | μΑ           |

| Over-temperature Threshold                | V <sub>NTC_OT</sub>  |                          | 0.36  | 0.4 | 0.41 | V            |

| OT Recover Threshold                      | V <sub>NTC_REC</sub> |                          | 0.78  | 0.8 | 0.82 | V            |

| Debounce Time                             | t <sub>NTC_DEB</sub> | Programmable in 2 steps  |       | 500 | 1000 | ms           |

| Redundant Over-Voltage<br>Protection      |                      |                          |       |     |      |              |

| Threshold Range <sup>1</sup>              | $V_{ROV\_LIM}$       |                          | 1.9   | 2.2 | 2.5  | V            |

| Threshold Accuracy                        |                      | Factory trimmed at 2.2 V | -2.00 |     | 1.64 | %            |

| Resolution                                |                      |                          |       | 6   |      | Bits         |

| Hysteresis                                |                      |                          | 115   | 135 | 160  | mV           |

| Propagation Delay                         |                      |                          |       |     | 160  | ns           |

| Debouncing Time                           |                      | Programmable in 4 steps  | 40    |     | 100  | μs           |

| Blanking Time                             |                      |                          |       | 10  |      | μs           |

| SDA/SCL PINS                              |                      |                          |       |     |      |              |

| Input Voltage Low                         |                      |                          |       |     | 8.0  | V            |

| Input Voltage High                        |                      |                          | 2.2   |     |      | V            |

| Output Voltage Low                        |                      |                          |       |     | 0.4  | V            |

| Pull-Up Current                           |                      |                          | 100   |     | 350  | μA           |

| Leakage Current                           |                      |                          | -5    |     | +5   | μΑ           |

| SERIAL BUS TIMING                         |                      |                          |       |     |      |              |

| Clock Frequency                           | fiic                 |                          |       |     | 400  | kHz          |

| Glitch Immunity                           | tsw                  |                          |       |     | 50   | ns           |

| Bus Free Time                             | t <sub>BUF</sub>     |                          | 4.7   |     |      | μs           |

| Start Setup Time                          | t <sub>SU_STA</sub>  |                          | 4.7   |     |      | μs           |

| Start Hold Time                           | thd_sta              |                          | 4     |     |      | μs           |

| SCL Low Time                              | t <sub>LOW</sub>     |                          | 4.7   |     |      | μs           |

| SCL High Time                             | tніgн                |                          | 4     |     |      | μs           |

| SCL, SDA Rise Time                        | t <sub>R_I2C</sub>   |                          |       |     | 1000 | ns           |

| SCL, SDA Fall Time                        | t <sub>F_I2C</sub>   |                          |       |     | 300  | ns           |

| Data Setup Time                           | tsu_dat              |                          | 250   |     |      | ns           |

| Data Hold Time                            | t <sub>HD_DAT</sub>  |                          | 300   |     |      | ns           |

| Parameter          | Symbol            | Conditions                                               | Min    | Тур  | Max    | Unit   |

|--------------------|-------------------|----------------------------------------------------------|--------|------|--------|--------|

| Baud Rate          | f <sub>UART</sub> | Programmable with (0:9600; 1: 1200; 2: 57600; 3: 115200) | 1200   | 9600 | 115200 | bps    |

| Data Length        |                   |                                                          |        | 8    |        |        |

| Stop Bits          |                   |                                                          |        | 1    |        |        |

| Polarity Check Bit |                   |                                                          |        | 1    |        |        |

| EEPROM RELIABILITY |                   |                                                          |        |      |        |        |

| Endurance          |                   | T <sub>A</sub> = 85°C                                    | 10,000 |      |        | Cycles |

|                    |                   | T <sub>A</sub> = 125°C                                   | 1000   |      |        | Cycles |

| Data Retention     |                   | T <sub>A</sub> = 85°C                                    | 20     |      |        | Years  |

|                    |                   | T <sub>A</sub> = 125°C                                   | 15     |      |        | Years  |

<sup>&</sup>lt;sup>1</sup> The final range of thresholds will be determined by factory trimmed result.

#### ABSOLUTE MAXIMUM RATINGS

Table 3. Absolute maximum ratings

| Parameter                                                                                                                                                     | Rating                            |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|

| VDD (Continuous)                                                                                                                                              | 4.2 V                             |  |  |

| ACL, ACN, FB, CS1, CS2, RELAY/GPIO0, NTC/ROV, POSPOL/GPIO1, NEGPOL/GPIO2, SRL/GPIO3, SRH/GPIO4, PWML, PWMH, RXD/GPIO5, TXD/GPIO6, SCL, SDA, CTRL, PFCOK/GPIO7 | -0.3 V to V <sub>DD</sub> + 0.3 V |  |  |

| VCORE                                                                                                                                                         | 2 V                               |  |  |

| Operating Temperature Range                                                                                                                                   | −40°C to +125°C                   |  |  |

| Storage Temperature Range                                                                                                                                     | -65°C to +150°C                   |  |  |

| Maximum Junction Temperature                                                                                                                                  | 150°C                             |  |  |

| Soldering Conditions                                                                                                                                          | JEDEC J-STD-020                   |  |  |

| Electrostatic Discharge (ESD)                                                                                                                                 |                                   |  |  |

| Human Body Model                                                                                                                                              | ±6000 V                           |  |  |

| Charge Device Model                                                                                                                                           | ±2000 V                           |  |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

#### **Table 4. Thermal Resistance**

| Package Type | θ <sub>JA</sub> | <b>θ</b> ЈС | Unit |

|--------------|-----------------|-------------|------|

| QFN4x4-24L   | 46              | 23          | °C/W |

#### **ESD CAUTION**

#### **Electrostatic Discharge Sensitive Device.**

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# TYPICAL PERFORMANCE CHARACTERISTICS

#### THEORY OF OPERATION

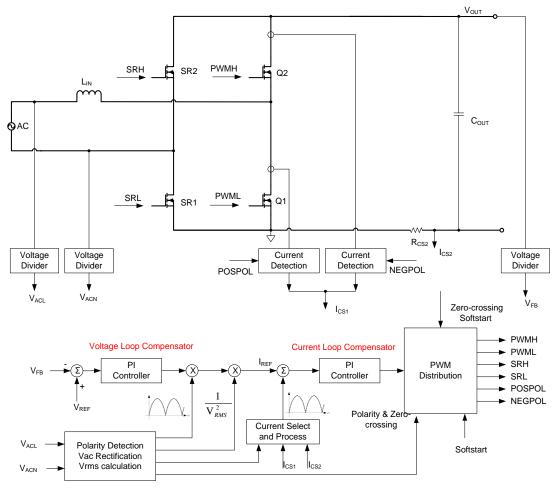

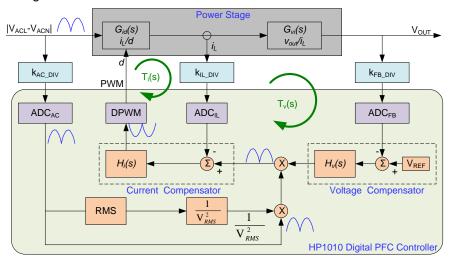

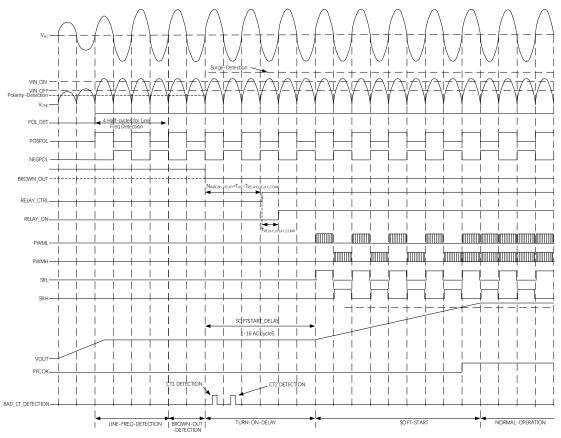

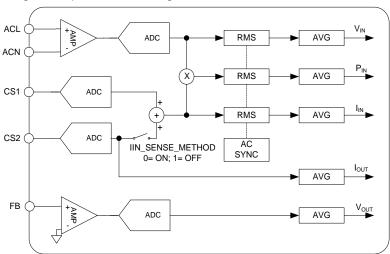

Figure 19 shows the overall control diagram for the totem-pole power factor correction (TPPFC) with MOSFET for synchronized line rectification. The voltage and current loop control are the same as conventional boost PFC converter. The feedback signals from the PFC power stage are the V<sub>FB</sub>, V<sub>ACL</sub>, V<sub>ACN</sub>, I<sub>CS1</sub> and I<sub>CS2</sub>. The input voltage polarity and RMS value are determined from V<sub>ACL</sub> and V<sub>ACN</sub>. The outer voltage loop output multiplied by |VAC| gives sinusoidal current reference. Current loop gives the proper duty-ratio for boost circuit. The polarity determines how the PWM signal is distributed for switches Q1 and Q2. The soft-start duty ratio is used for a short period after the zero-crossing.

Figure 19 HP1010 Control Loop Scheme

#### **BASIC OPERATING PRINCIPLE**

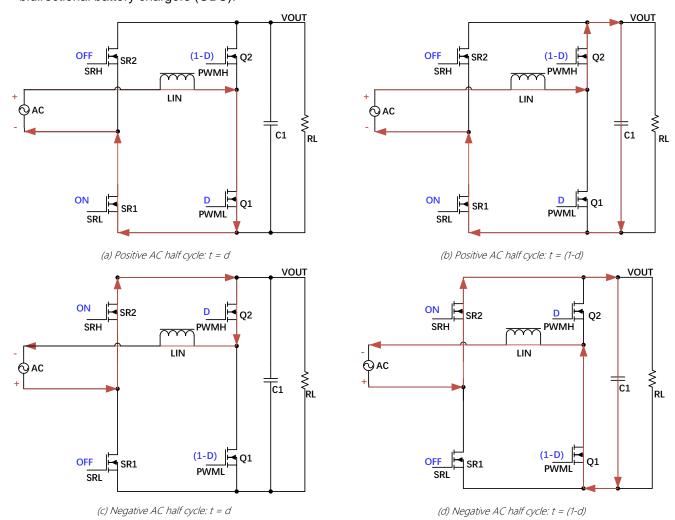

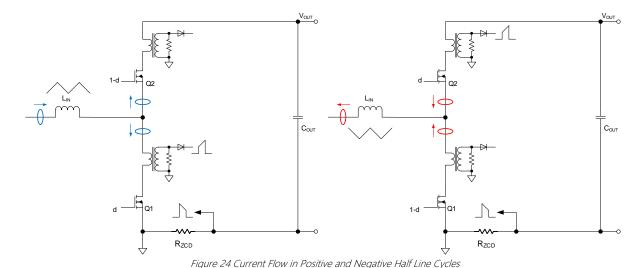

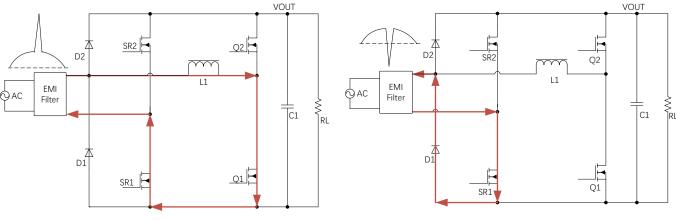

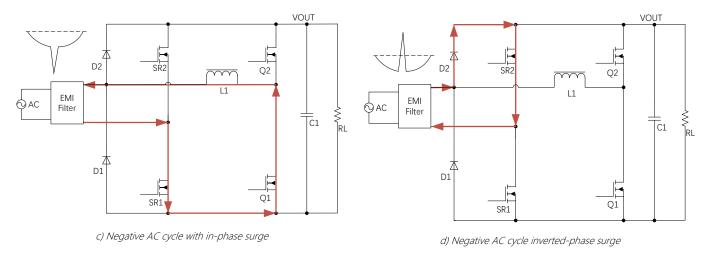

The Totem-Pole PFC topology operates in two modes depending on the polarity of input AC voltage, as shown in the Figure 20. During the positive half cycle (line > neutral): Q1 is the main switch and Q2 is driven with a complementary PWM signal. Q1/Q2 and  $L_{IN}$  form the boost DC/DC stage. During this positive half cycle, half bridge leg SR1 is turned on and SR2 is always inactive. During the time when the main switch Q1 is turned on, current flows from  $L_{IN}$  ->Q1->SR1 and back to neutral. During the period of (1-d) when Q1 is turned off, Q2 is turned on and current flows through Q2 and back to N via SR1. The DC bus ground VDC- is tied to neutral potential as SR1 is conducting all the time.

During negative half cycle (neutral > line): the operation in the negative half cycle is similar except the role of top and bottom switches are swapped. Now Q2 becomes the main switch and Q1 is free-wheeling, and SR2 is turned on and SR1 is inactive.

Compared to the conventional bridgeless PFC, the TPPFC has the following advantages:

Improved efficiency: main current only flows through two switches at a time. Q1/Q2 are driven synchronously

with complimentary PWM signals and the SR1/SR2 on the slow line frequency legs can be low Rds(on) Si

MOSFETs to further reduce the conduction loss.

- Lower part counts, higher power density and lower BOM cost. It uses fewer parts and has a simpler circuit: It

needs only one inductor and neither SiC diodes nor AC return diodes are required.

- Bidirectional power flow. TPPFC is inherently capable of bidirectional operation, which is ideal for applications

which may require power flow in both directions, such as Energy Storage System (ESS) and on-board

bidirectional battery chargers (OBC).

Figure 20 Totem-pole PFC Operation

#### **VDD AND VCORE PINS**

When the voltage of the VDD pin is applied (VDD), there is a delay before the part can regulate the power supply. When VDD voltage rises above the power-on reset and UVLO levels, it takes  $\sim$ 20  $\mu$ s for the VCORE pin (Pin 23) to reach its operational point of 1.8 V. The EEPROM contents are then downloaded to the registers. After the EEPROM contents are downloaded, the HP1010 is ready for operation; however, it takes a maximum of 20 ms for the HP1010 to complete initialization of the address after a power-on reset. Therefore, it is recommended that the master device access the HP1010 at least 20 ms after power-on reset.

#### CTRL PIN AND SOFTWARE ENABLE

The HP1010 is in the PFC off state upon power-on reset. PFC\_ON configuration can be enabled in one of four ways, depending on the setting:

- Always on whenever the input voltage is ready.

- Hardware CTRL only. Power on whenever the CTRL pin is pulled high, and the input voltage is ready.

- Software ENABLE only. Power on whenever the ENABLE bit is set and the input voltage is ready.

- Both hardware CTRL being pulled high, and software ENABLE bit being set to turn on the PFC when the input voltage is ready.

Once the PFC\_ON flag is set, the HP1010 follows the state machine as shown in section Operation for details.

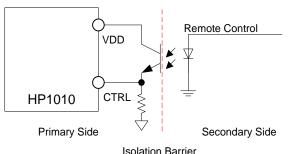

The CTRL pin has a control debounce of *tctrl\_deb*, which is 10 µs, for both the rising edge and falling edge. The CTRL pin is used to control the HP1010 from the second side controller via an optical coupler, as shown in Figure 21. The remote signal is generated from the second-side controller.

Figure 21 Remote Control Signal to Enable HP1010

#### **INPUT AC VOLTAGE (ACL AND ACN PINS)**

External resistor dividers are required to divide down two high voltage nodes to perform differential line sensing. The recommended divide down factor for universal input consumer applications is Kac\_DIV\_EXT, typically 1/200.

$$K_{AC\_DIV\_EXT} = \frac{R_{LWR}}{R_{UPR} + R_{LWR}} \tag{1}$$

The ACL pin is intended to interface with the low-frequency node of the main boost inductor,  $L_{\text{IN}}$ , and the ACN pin is intended to interface with the bridge voltage of the slow-leg power switches. The internal line detector circuit is designed with substantially high input impedance, allowing for large external resistors to minimize the power dissipation in the dividers, enabling the application to achieve low no-load power consumption. Typical values for  $R_{\text{UPR}}$  can be in the range of 993 k $\Omega$ , while  $R_{\text{LWR}}$  can be 4.99 k $\Omega$ . In practice, the upper portion of the resistor divider should consist of at least two 1206 components connected in series to withstand the voltage drop.

Since there is an additional amplifier U2 with a gain of K<sub>AC\_DIV\_INT</sub> = 1/2. The total gain of line voltage sense to the ADC is:

$$K_{AC\ DIV} = K_{AC\ DIV\ EXT} \times K_{AC\ DIV\ INT} \tag{2}$$

Therefore  $K_{AC\_DIV} = 1/400$ .

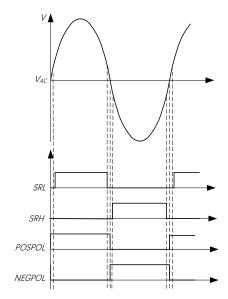

#### **POLARITY DETECTION**

The ACL and ACN pins sense signals are compared directly against each other to determine when they cross. The crossover of the two signals indicates that the AC line voltage has changed polarity. When the AC line is in a positive cycle, POSPOL is high and NEGPOL signal is low. When the AC line is in a negative cycle, POSPOL is low and NEGPOL signal is high.

External filter capacitance may be needed to improve the noise immunity of the polarity detection circuitry; the recommended time constant of the RC filter is about 20 to 200 µs, enough to provide noise immunity from the switching frequency of the power supply but not such a large time constant to introduce significant lag in the line sense signals.

The output of the polarity comparison circuit is passed through a digital debounce filter, which will provide additional immunity if the comparison circuit is toggling due to the noise. The debounce filter has a programmable debounce time, typical 200 µs.

#### AC LINE FREQUENCY MONITORING

The HP1010 supports different input line types, including 50 Hz/60 Hz AC input and DC input.

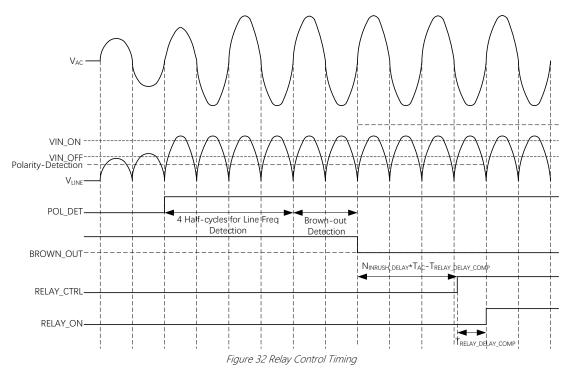

#### **BROWN-OUT AND LINE SAG PROTECTION**

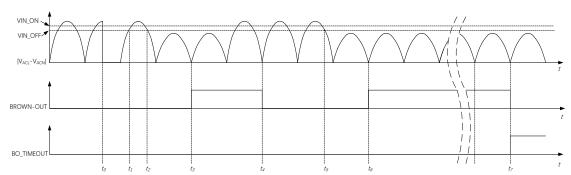

The HP1010 features line voltage Brown–out (BO) and Line sag (SAG) detection. These detection circuits' function works as a line voltage UVLO, enabling drive pulses when the RMS voltage exceeds the  $V_{IN\_ON}$  threshold, typically 78 VAC, and disabling drive pulses when the line voltage falls below the  $V_{IN\_OFF}$  threshold, typically 71 VAC, for a given timer duration.

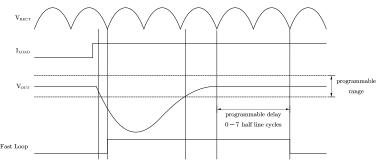

When the line voltage VAC voltage drops below VIN\_OFF for a debounce of \$t\_{BO\_DEB}\$, which is half an AC cycle, the BROWN-OUT flag is trigged. The SAG timer, programmable from 4-cycle to 32-cycle from the BROWN-OUT flag being triggered, allows the application to sustain a line voltage dropout for a single or multiple AC line cycles while the controller continues to deliver drive pulses. Within the timer, if the output voltage drops below the output under-voltage limit, the VOUT\_UV\_FAULT will trigger protection action. If the input current exceeds the input peak current limit or the input average current limit, the IIN\_PK\_OC fault or the IIN\_AV\_OC fault will trigger protection actions. If the protection action is selected as fault recovery, since the BROWN\_OUT flag is triggered, the HP1010 resets to Mode 0. If the SAG timer expires, the controller will reset to Mode 0 for a new start-up. Figure 22 shows the timing diagram for the Brown-out and SAG. The missing cycle between t1 to t0 is smaller than \$t\_{BO\_DEB}\$, the BROWN\_OUT flag is not triggered.

Figure 22 Brown-out and Sag Timing Diagram

#### LINE RANGE DETECTION

The HP1010 features input voltage range detection, which distinguishes between high line (nominally 230 VAC) and low line (nominally 115 VAC) input voltages. The input voltage range is detected based on the RMS value calculated with the VAC line signal. By default, the controller will power up into low line mode. If VAC exceeds the high line threshold, V<sub>HLINE</sub>, typically 168 V, for one half cycle, the controller transitions to high line mode. Once in high line mode the peak line voltage must fall below V<sub>LLINE</sub>, typically 156 VAC, to enter back into the low line mode for one half cycle. The debounce duration, t<sub>H2L\_DEB</sub>, typically 25 ms is set long enough to allow the controller to remain in high line mode in the event of a single line cycle dropout.

#### AC ZERO CROSSING MANAGEMENT

AC zero crossing management is the feature in the HP1010 that determines when to enable and disable the various drive signals at the beginning and end of each of the half line cycles. This feature is critical to the robustness and performance of the TPPFC topology. The 4 drive signals that can be divided into three classes: 1) The primary or d controlled PWM drive signal; 2) The synchronous (sync) PWM drive signal that occurs during the (1 - d) portion of the switching period; and 3) The slow leg "rectifier" or SR drive signal that switches once per half line cycle. Each drive signal has a respective stop and start threshold, which is a function of the line voltage amplitude,  $|V_{ACL}-V_{ACN}|$ .

#### **OPEN LOOP DRIVE PULSES**

Another critical feature of the HP1010 is the open-loop drive pulses that are issued immediately following a polarity transition. After the AC line zero crossing, the slow leg bridge maintains a residual voltage charge from the previous half line cycle and must be transitioned from V<sub>OUT</sub> to 0 V (or vice versa) during the upcoming half line cycle.

Considering that PWM-controlled drive pulses near an AC line zero crossing would typically operate with a high duty cycle, using these pulses to transition the slow bridge voltage can result in excessively high current spikes in the

inductor; hence, it is beneficial to use shorter drive pulses with a smaller, fixed duty cycle to initiate the slow leg bridge node transition.

#### **OUTPUT VOLTAGE (FB PIN)**

#### **REGULATION BLOCK**

The bulk voltage is divided down via a resistor divider and input to an ADC, which converts the feedback voltage to a digital signal. This digital signal compares against a digital reference voltage. The recommended divide-down factor for universal output voltage sense is K<sub>FB DIV</sub>, typically 1/200.

$$K_{FB\_DIV\_EXT} = \frac{R_{FB2}}{R_{FB1} + R_{FB2}} \tag{3}$$

Typical values for  $R_{FB1}$  can be in the range of 993 k $\Omega$  while  $R_{FB2}$  can be 4.99 k $\Omega$ . In practice the upper portion of the resistor divider should consist of at least two 1206 components connected in series to withstand the voltage drop.

Since there is an additional amplifier with a gain of  $K_{FB\_DIV\_INT} = 1/2$ . The total gain of output voltage sense to the ADC is:

$$K_{FB\ DIV} = K_{FB\ DIV\ EXT} \times K_{FB\ DIV\ INT} \tag{4}$$

Therefore  $K_{FB\_DIV} = 1/400$ . During nominal condition, the output voltage is 400 V, resulting in FB pin sense voltage of 2 V and ADC input voltage of 1 V.

#### **OUTPUT VOLTAGE REGULATION**

In the HP1010, the output voltage can be regulated with a low line and a high line separately. As low-line and high-line references, the regulation range is from 250 V to 505 V, with a nominal voltage of 400 V.

#### **OUTPUT VOLTAGE PROTECTION FEATURES**

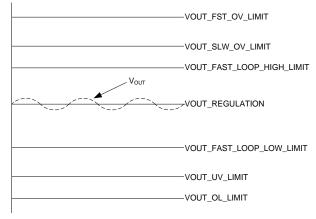

The HP1010 features multiple protection and enhancement features for improved performance and robustness of the application. The slow OVP, fast OVP, slow UVP, and fast loop blocks monitor the sampled FB pin voltage.

Figure 23 Output Voltage Protection Thresholds

#### **CURRENT SENSE (CS1 AND CS2 PINS)**

#### **CURRENT SENSE METHODS**

In CCM mode, the HP1010 implements average current mode control that requires the controller to receive an accurately sensed average value of the inductor current. This is a challenge with the TPPFC topology because the inductor and each of the fast leg switches conduct current bidirectionally, as shown in Figure 24. Depending on the line cycle polarity, the inductor current flows in either the 1st or 3rd quadrant, while the duty-controlled fast leg device conducts current from drain to source, and the (1-d) fast leg device conducts current from source to drain.

The purpose of the current sense is to obtain the input and output currents. The input current is the inductor current, which is used in the control and the input power metering. The output current is used in the output power metering. Figure 24 shows the current sense block diagram in HP1010.

For the TPPFC topology, the HP1010 supports current sense schemes as following:

Two current transformers + one sense resistor (2\*CT+1\*R<sub>sen</sub>)

To achieve input and output current sense monitoring and protection, the CS1 and CS2 can be configured as Table 5 for correctly sense the input and output current.

**Table 5. Input and Output Current Sense**

| Topology | Current Sense Scheme              | Input Current Sense | Output Current Sense |  |  |

|----------|-----------------------------------|---------------------|----------------------|--|--|

| TPPFC    | Scheme 1: 2*CT+1*R <sub>sen</sub> | CS1+CS2             | CS2                  |  |  |

Since different current sense components are used, the CS1 and CS2 current sense equivalent resistances can be selected as  $6.25~\text{m}\Omega$ ,  $12.5~\text{m}\Omega$ ,  $25~\text{m}\Omega$ ,  $50~\text{m}\Omega$ ,  $100~\text{m}\Omega$ ,  $200~\text{m}\Omega$ , and  $400~\text{m}\Omega$ . The goal of adopting different equivalent resistances is to optimize the usage of 1.4 V full-range input ADC and achieve power savings. For example, in the current transformer method, if the turn ratio of CT1 and CT2 (NP:NS) is 1:100 and the R<sub>CS1</sub> is  $10~\Omega$ , then the CS1 equivalent resistance is  $1/100*10=100~\text{m}\Omega$ .

# CURRENT SENSE SCHEME: TWO CURRENT TRANSFORMERS + ONE SENSE RESISTER FOR TPPFC TOPOLOGY

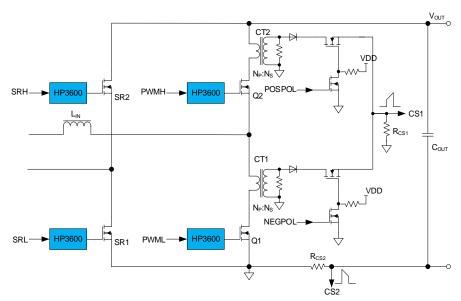

The HP1010 incorporates a novel current sensing scheme utilizing two inputs: one for sensing inductor current during the duty-controlled portion (d portion) of the switching cycle and one for sensing inductor current during the (1–d) portion of the switching cycle. These two signals are summed together inside the controller to reconstruct an image of the inductor current. The current sense configuration used in a typical application is illustrated in Figure 25.

The CS1 and CS2 inputs sense the inductor current during the duty-controlled portion of the switching cycle. This can be referred to as the inductor current upslope. The recommended scheme for the CS input requires two current sense transformers (CT1 and CT2), one in series with each of the fast leg switches, a diode OR'ed output from the secondary side of CTs, a single current sense resistor, and an RC filter to mitigate noise pickup on the sense circuit. Additionally, a "blanking" circuit is required across each secondary to selectively shunt with the CT output to ground.

Each of the CTs is active during the half line cycle when the respective switch is duty controlled. When the respective switch is (1-d) controlled then the blanking circuit is active, and the CT secondary is blocked. In Figure 25 the blocking circuits are shown. CT1 is blocked during negative AC cycle by the NEGPOL signal as Q1 switch is (1-d) controlled during negative AC cycle. CT2 is blocked during positive AC cycle by the POSPOL signal as Q2 switch is (1-d) controlled during positive AC cycle. The POSPOL and NEGPOL timing diagram is shown in Figure 26.

The CS1 pin is also utilized for cycle-by-cycle peak current limiting and overload protection. It protects the power devices from destructive damage due to inductor saturation, output power overload, or thermal overstress by immediately terminating the duty-controlled drive pulse when the peak current limit threshold is reached.

Figure 25 Two Current Transformers + one Sense Resistor Scheme

Figure 26 POSPOL and NEGPOL Timing to Control Current Transformers Signal

The R<sub>CS1</sub> resistor value is calculated based on peak current limiting. The maximum peak inductor current is calculated in the application using Equation (3) where  $P_O$  is output power,  $\eta$  is efficiency,  $V_{AC}$  is the RMS input voltage,  $L_{IN}$  is the inductance of the boost,  $f_{SW}$  is the CCM switching frequency, and  $D_{PK}$  is duty cycle at the peak AC line voltage. Once the maximum peak current is determined, Equation (4) is used to find an upper limit on the CS1 resistor based on the CS1 current limit threshold,  $V_{CS1\_OCP}$ , and the turns ratio of the current sense transformers. This calculation should be done at the minimum AC input voltage, usually 90 VAC, and may also need to be repeated at the minimum high line voltage in the application, typically 180 VAC, depending on the application's output power requirements.

$$I_{L\_PK} = \frac{\sqrt{2} \times P_O}{\eta \times V_{AC}} + \frac{\sqrt{2} \times V_{AC} \times D_{PK}}{2 \times L_{IN} \times f_{SW}}$$

(5)

$$R_{CS1} < \frac{N_S}{N_P} \times \frac{V_{CS1\_OCP}}{I_{L\_PK}} \tag{6}$$

The CS2 senses the voltage across a sense resistor, which senses the inductor current during the (1–d) portion of the switching cycle. This can be referred to as the inductor current downslope or demagnetization. The recommended sensing element for the CS2 is a high-power, low-inductance, current sense resistor. The HP1010 converts the CS1 and CS2 inputs separately and sums their digital values together to obtain the digital value of the inductor current. This inductor current signal is critical to optimizing THD performance in the application. Since the CS2 resistor causes some power loss, a smaller resistor value is preferred. As shown in Table 6, a half of the CS1 CT gain is chosen to be the CS2 resistor value. In the internal a gain of 2x is applied to the digital CS2 to ensure that CS1 and CS2 have the equal magnitude.

Same as before, the CS1 and CS2 sense gain is calculated based on the output power level.

Table 6. Recommended Equivalent Resistance Selection

| Output Power(W)                                                                    | 200  | 400  | 800   | 1600  | 3200  | 6400   |

|------------------------------------------------------------------------------------|------|------|-------|-------|-------|--------|

| Input current RMS value @ VAC = 85 VAC (A)                                         | 2.35 | 4.71 | 9.41  | 18.82 | 37.65 | 75.29  |

| Input current Peak value @ VAC = 85 VAC (A)                                        | 3.33 | 6.65 | 13.31 | 26.62 | 53.23 | 106.47 |

| CS1 equivalent resistance (N <sub>P</sub> /N <sub>S</sub> *R <sub>CS1</sub> ) (mΩ) | 0.4  | 0.2  | 0.1   | 0.05  | 0.025 | 0.0125 |

| CS1 peak voltage (V)                                                               | 1.33 | 1.33 | 1.33  | 1.33  | 1.33  | 1.33   |

| CS2 resistance (R <sub>CS2</sub> ) (mΩ)                                            | 0.2  | 0.1  | 0.05  | 0.025 | 0.125 | 0.0625 |

| CS2 peak voltage (V)                                                               | 0.67 | 0.67 | 0.67  | 0.67  | 0.67  | 0.67   |

#### CS1 AND CS2 COMPARATORS

For the TPPFC topology and current sense schemes 1, the HP1010 has a programmable cycle-by-cycle current limit threshold (Vcs1\_oc) for the CS1 pin, which can be set based on the power level. The cycle-by-cycle current limit is triggered by an analog comparator that compares the CS1 signal and the set threshold Vcs1\_oc. When the threshold is crossed, the PWM pulse is terminated. The next switching cycle resumes normally.

The cycle-by-cycle current limit comparator also features programmable blanking and debounce times. See Table 7 for the debounce and blanking time option.

Table 7. Debounce and Blanking Time for CS1 and CS2 Cycle-by-cycle Limit

| Parameter              | Values or Options                                                                                                                                                           |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Debounce Time          | 40 ns, 80 ns, 120 ns, 160 ns                                                                                                                                                |

| Blanking Time          | 480 ns, 960 ns, 1440 ns, 1920 ns                                                                                                                                            |

| Propagation Delay      | 100 ns maximum                                                                                                                                                              |

| Threshold Value        | Programmable from 1.0 V to 1.5 V with 7.8 mV step for V <sub>CS1_OC</sub> and V <sub>CS2_OC</sub> (positive)                                                                |

| Actions for Protection | Terminate 'd' drive signal and turn on the '1-d' drive signal earlier (dead time remain unchanged) for 16 consecutively switching cycles, and then trigger IIN_PK_OC fault. |

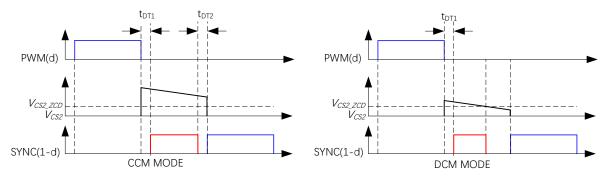

#### SYNCHRONOUS PWM DRIVE CONTROL

The synchronous PWM of the fast leg in the TPPFC topology enables higher efficiency performance but proper gating of the device is necessary for optimizing efficiency and ensuring robustness. A diagram of the sync control methodology is shown in Figure 27. First, a dead time, T<sub>DT1</sub>, typically 100 ns, follows the falling edge of the PWM duty–controlled drive to prevent cross conduction. At the same time, the current measured through CS1 or CS1+CS2 needs to exceed a threshold to enable the sync drive. In lighter loads, the current may never exceed this threshold, and the sync device will never enable. This is done to prevent switching of the sync device at light loads where the associated switching losses could negatively impact the overall efficiency of the application.

At increasing loads, the current will exceed the threshold, and the sync drive will remain enabled until the current falls below the threshold. It is noted that the Sync PWM cannot let the inductor current reverse polarity. If the sync device remains on for too long, the inductor current would reverse polarity and begin cycling energy from the bulk capacitor. This would lead to increased RMS currents in the system and could diminish overall efficiency.

Figure 27 Synchronous PWM Drive Control

#### POWER FACTOR CORRECTION CONTROL LOOP

The HP1010 implement the average current mode power factor correction control loop. The implementation of the loop is digital, and all the signals are converted from analog to digital before they are processed by the control loop.  $\Sigma$ -  $\Delta$  ADCs are used to achieve high performance, cost-effective implementation. The diagram of the current loop and voltage loop is shown in Figure 28.

Figure 28 Current and Voltage Control Loops Diagram

#### **FAST LOOP MODE**

During transients, a fast loop mode is enabled in order to provide quicker loop responses. Typical timing can be seen in Figure 29. Fast loop mode has separate settings that can be programmed to respond quickly to load transients. The fast loop mode can be disabled by the user if it is not necessary by the application.

Figure 29 Fast Loop for Transient Response Improvement

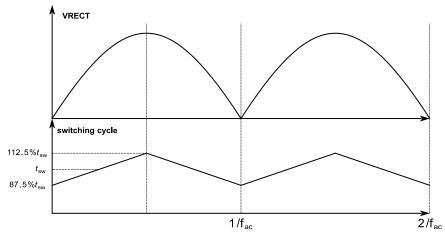

#### **DIGITAL PULSE MODULATION**

The switching frequency is programmed in the SWTICHING\_FREQ command. The switching frequency options are list in Table 8.