## 特征

- 双极性模拟输入范围:  $\pm 10V$ 、 $\pm 5V$

- 5V 模拟电源, 2.3V 至 5V 数字接口电源

- 8 通道同步采样输入

- 性能

- 模拟输入 ESD 可达 8kV

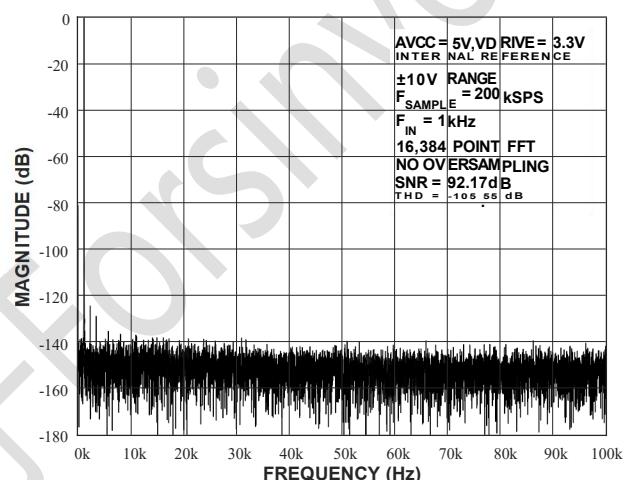

- 92dB SNR (无过采样), -105dB THD

- $\pm 1LSB$  INL,  $\pm 0.8LSB$  DNL

- 灵活的并行/串行接口

- SPI/QSPI/MICROWIRE/DSP 兼容

- 完全集成的数据采集解决方案

- 模拟输入钳位保护

- 具有  $1M\Omega$  模拟输入阻抗的输入缓冲器

- 二阶抗混叠模拟滤波器

- 片内精密基准电压及缓冲

- 16 位、200kSPSADC (所有通道)

- 通过数字滤波器提供过采样功能

- 低功耗: 运行 107.5mW, 待机 28.5mW

- LQFP64 10mm×10mm 封装

## 应用

- 数据采集系统

- 电力线监控和保护系统

- 多轴定位系统

- 多相电机系统

- 仪表和控制系统

## 概述

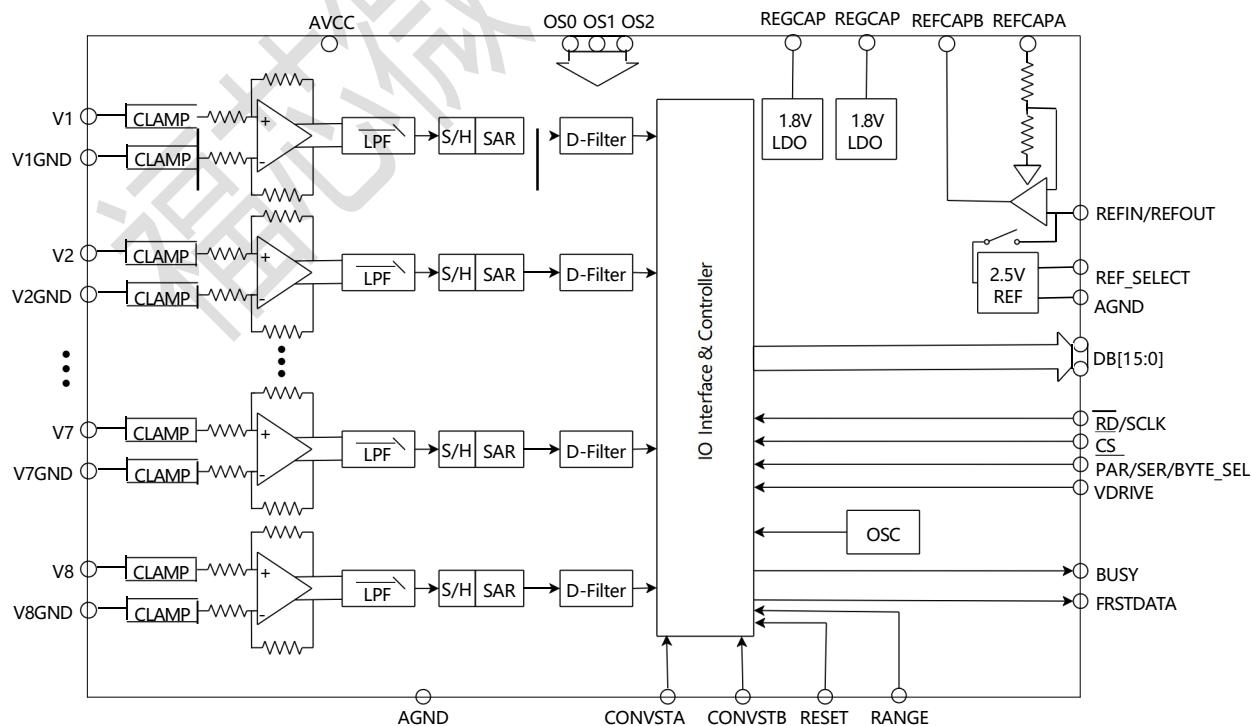

FSV7606 是一款 16 位、8 通道同步采样模拟数据采集系统 (DAS)。各通道均内置模拟输入钳位保护、二阶抗混叠滤波器、跟踪保持放大器、16 位 SAR ADC，内置了灵活的数字滤波器、2.5V 基准电压源、基准电压缓冲以及高速串行和并行接口。

FSV7606 采用 5V 单电源供电，可以处理  $\pm 10V$ 、 $\pm 5V$  真双极性输入信号，同时所有通道均能以高达 200kSPS 的吞吐速率采样。在各种采样频率工作下，输入钳位保护电路可以承受高达  $\pm 18.5V$  的电压。 $1M\Omega$  的高输入阻抗以及片内滤波器，可以极大 简化外围电路设计。

## 架构框图

# 目录

|               |    |               |    |

|---------------|----|---------------|----|

| 封页            | 1  | 封页            | 20 |

| 特征            | 1  | 钳位保护          | 20 |

| 应用            | 1  | 抗混叠滤波器        | 20 |

| 概述            | 1  | 采样保持放大器       | 21 |

| 架构框图          | 1  | 内部/外部基准       | 21 |

| 文档历史          | 3  | 多芯片并联外部基准电压模式 | 21 |

| 管脚配置和功能       | 4  | 多芯片并联内部基准电压模式 | 21 |

| 管脚配置          | 4  | ADC 传递函数      | 22 |

| 管脚功能          | 4  | 数字滤波器         | 22 |

| 绝对最大额定值       | 8  | 功能与模式         | 23 |

| 电气规格          | 9  | 功耗模式          | 23 |

| 时序规格          | 11 | 转换控制          | 23 |

| 通用时序规格        | 11 | 数字接口          | 24 |

| FRSTDATA 时序规格 | 12 | 并行接口          | 24 |

| 并行模式时序规格      | 12 | 串行接口          | 24 |

| 串行模式时序规格      | 14 | 并行字节接口        | 24 |

| 典型特征          | 16 | 应用            | 25 |

| 工作原理          | 20 | 典型连接          | 25 |

| 模拟输入          | 20 | 封装及订购信息       | 26 |

| 输入范围          | 20 | 封装方式          | 26 |

| 输入阻抗          | 20 | 产品外形图         | 26 |

|               |    | 订购信息          | 27 |

## Ⅰ 文档历史

下表列举了本文档自产品发布后的所有更新。

| 文档版本 | 修订日期       | 内容描述                                                                                                                                                                                                                                                        |

|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0 | 2023-11-27 | 初版发布。                                                                                                                                                                                                                                                       |

| V2.0 | 2024-06-19 | <p>内容更新如下：</p> <ul style="list-style-type: none"><li>修正<a href="#">绝对最大额定值</a>表中的 ESD 值。</li><li>根据量产数据修正<a href="#">电气规格</a>表中的参数值。</li><li>修正<a href="#">图 10</a>中的纵坐标。</li><li>新增章节<a href="#">数字滤波器</a>。</li><li>优化<a href="#">产品外形图</a>章节的图。</li></ul> |

## 管脚配置和功能

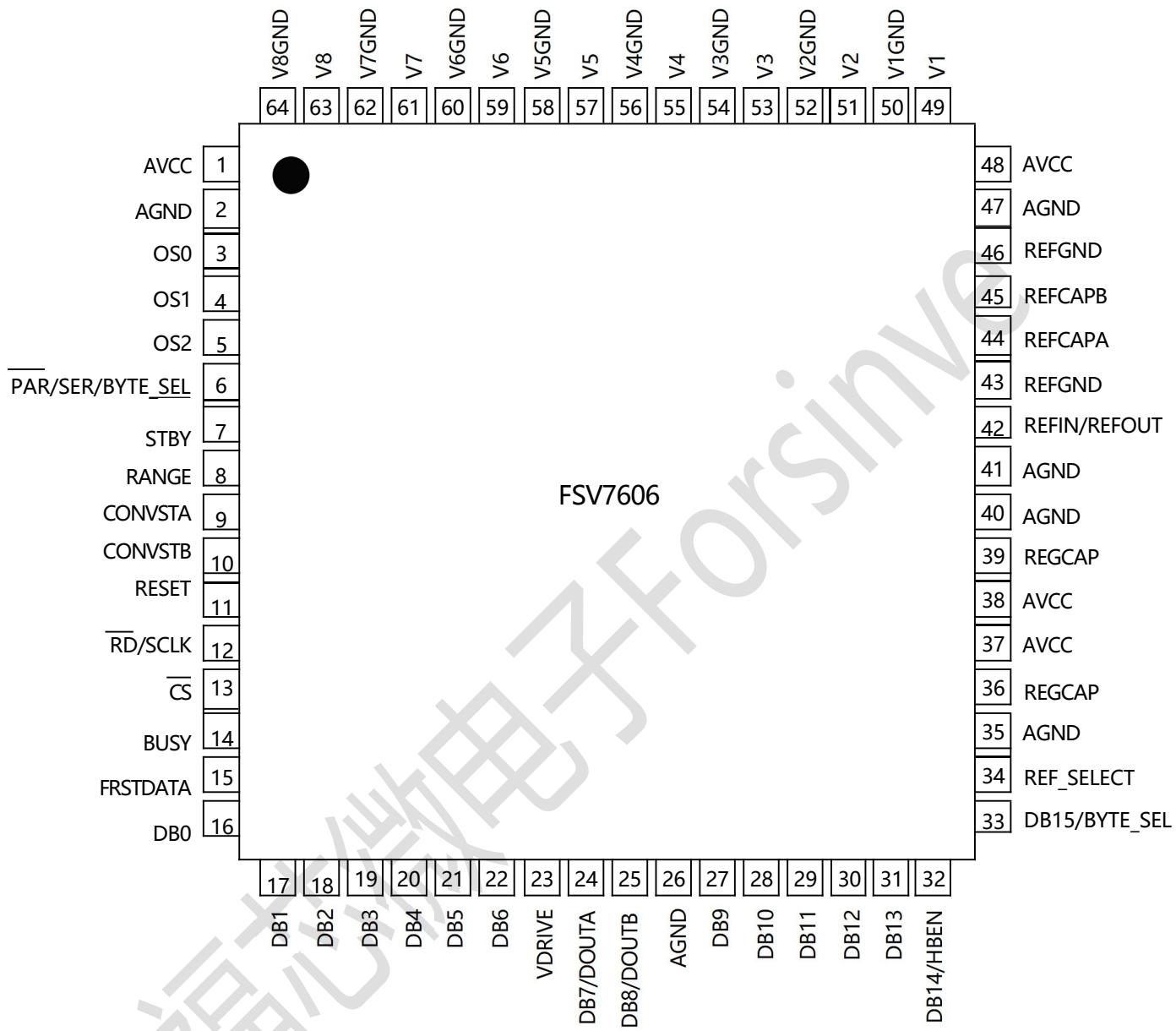

### 管脚配置

以下为 FSV7606 LQFP64 封装管脚示意图：

图 1 管脚示意图 (顶视图)

### 管脚功能

表 1 管脚功能描述

| 编号 | 名称   | 类型  | 说明                                                                                      |

|----|------|-----|-----------------------------------------------------------------------------------------|

| 1  | AVCC | PWR | 模拟电源电压。通过 100nF 与 10μF 的并联去耦电容连接至 AGND。                                                 |

| 2  | AGND | GND | 模拟地。这些管脚是 FSV7606 所有模拟电路的接地基准点，所有模拟输入信号 和外部基准信号都应该参考这些管脚。所有 6 个 AGND 管脚都应连到系统的 AGND 平面。 |

| 编号    | 名称                      | 类型  | 说明                                                                                                                                                                                                                                                                 |

|-------|-------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3     | OS0                     | DI  | 过采样模式管脚，这些输入用来选择过采样倍率。<br>OS2 为 MSB 控制位，OS0 为 LSB 控制位。                                                                                                                                                                                                             |

| 4     | OS1                     |     |                                                                                                                                                                                                                                                                    |

| 5     | OS2                     |     |                                                                                                                                                                                                                                                                    |

| 6     | <u>PAR/SER/BYTE_SEL</u> | DI  | 与 DB15/BYTE_SEL 管脚共同决定数字接口模式。如果此管脚接逻辑低电平，则选择并行接口。如果此管脚接逻辑高电平并且 DB15/BYTE_SEL 接逻辑低电平，则选择串行接口。如果此管脚与 DB15/BYTE_SEL 管脚都接高电平，则选择并行字节模式。                                                                                                                                |

| 7     | <u>STBY</u>             | DI  | 待机模式输入。此管脚用来让 FSV7606 进入两种低功耗模式之一：待机模式或关断模式。RANGE 管脚状态则决定进入具体某种低功耗模式。待机模式下，除片内基准电压、稳压器和稳压器缓冲外的所有其他电路均关断。关断模式下，所有电路均关断。                                                                                                                                             |

| 8     | RANGE                   | DI  | 模拟输入范围选择。此管脚的极性决定模拟输入通道的输入范围。如果此管脚与逻辑高电平相连，则所有通道的模拟输入范围为 $\pm 10V$ 。如果此管脚与逻辑低电平相连，则所有通道的模拟输入范围为 $\pm 5V$ 。此管脚的逻辑状态改变会立即影响模拟输入范围，对于快速吞吐速率应用，转换期间建议不要更改此管脚的逻辑状态。                                                                                                     |

| 9     | CONVSTA                 | DI  | 转换开始控制信号。V1、V2、V3、V4 由 CONVSTA 启动同步采样，V5、V6、V7、V8 由 CONVSTB 启动同步采样。如果要对所有输入通道同时采样，可以将 CONVSTA 和 CONVSTB 短接在一起，并施加一个转换开始信号。                                                                                                                                         |

| 10    | CONVSTB                 |     |                                                                                                                                                                                                                                                                    |

| 11    | RESET                   | DI  | 该管脚输入逻辑高电平将芯片复位，进行中的转换将中断，输出寄存器的内容将复位至全 0。                                                                                                                                                                                                                         |

| 12    | <u>RD/SCLK</u>          | DI  | 并行接口模式下，该管脚为并行数据读取控制输入( <u>RD</u> )；串行接口模式下，该管脚为串行时钟输入(SCLK)。                                                                                                                                                                                                      |

| 13    | <u>CS</u>               | DI  | 片选。此管脚处于逻辑低电平将使能数据帧传输。                                                                                                                                                                                                                                             |

| 14    | BUSY                    | DI  | 转换指示信号。CONVSTA 和 CONVSTB 均达到高电平后，此管脚变为逻辑高电平，表示转换过程已经开始。BUSY 输出将保持高电平，直到所有通道的转换过程完成为止。BUSY 信号的下降沿将转换数据锁存至输出数据寄存器。当 BUSY 信号为高电平时，CONVSTA 或 CONVSTB 管脚的上升沿信号将不起作用。                                                                                                    |

| 15    | <u>FRSTDATA</u>         | DO  | FRSTDATA 指示第一通道 V1 的数据可以通过数字接口回读。当 CS 输入为高电平时，FRSTDATA 输出管脚处于三态。CS 下降沿使 FRSTDATA 脱离三态。在并行模式下，与 V1 结果对应的 RD 下降沿将 FRSTDATA 管脚设为高电平，在下一个 RD 下降沿之后，FRSTDATA 输出恢复逻辑低电平。在串行模式下，FRSTDATA 在 CS 下降沿变为高电平，此时将在 DOUTA 上输出 V1 的 MSB。在 CS 下降沿之后的第 16 个 SCLK 下降沿，FRSTDATA 恢复低电平。 |

| 16~22 | DB0 到 DB6               | DO  | 并行输出数据位 DB0 到 DB6。当 <u>PAR/SER/BYTE_SEL</u> 为逻辑低电平时，这些管脚充当并行数字输入/输出管脚。当 <u>PAR/SER/BYTE_SEL</u> 为逻辑高电平时，这些管脚应连接至 AGND。当工作在并行字节接口模式时，DB[7:0] 通过 2 个 RD 操作输出 16 位转换结果。DB7(管脚 24) 为 MSB，DB0 为 LSB。                                                                    |

| 23    | VDRIVE                  | PWR | 逻辑电源输入。此管脚的电源电压 (2.3V 至 5.25V) 决定逻辑接口的工作电压。此管脚的标称电源应与控制器 (DSP 或 FPGA) 接口电源相同。                                                                                                                                                                                      |

| 24    | DB7/DOUTA               | DO  | 并行输出数据位 DB7 或串行接口数据输出管脚 DOUTA。                                                                                                                                                                                                                                     |

| 25    | DB8/DOUTB               | DO  | 并行输出数据位 DB8 或串行接口数据输出管脚 DOUTB。                                                                                                                                                                                                                                     |

| 26    | AGND                    | GND | 模拟地                                                                                                                                                                                                                                                                |

| 编号       | 名称            | 类型   | 说明                                                                                                                                                                                                                                                                                                         |

|----------|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27~31    | DB9 到 DB13    | DO   | 并行输出数据位 DB9 至 DB13。当 <u>PAR/SER/BYTE_SEL</u> 为逻辑低电平时，这些管脚充当并行数字输出管脚。当 <u>PAR/SER/BYTE_SEL</u> 为逻辑高电平时，这些管脚应连接至 AGND。                                                                                                                                                                                       |

| 32       | DB14/HBEN     | DI/O | <p>当 <u>PAR/SER/BYTE_SEL</u> 为逻辑低电平时，此管脚充当并行数字输出管脚。当 <u>PAR/SER/BYTE_SEL</u> 为高电平时，该管脚应连接至 AGND。当 <u>PAR/SER/BYTE_SEL</u> = 1 且 <u>DB15/BYTE_SEL</u> = 1 时，FSV7606 工作在并行字节接口模式。在该模式下，HBEN 管脚用来选择是首先输出转换结果的高字节 (MSB) 还是低字节 (LSB)。</p> <p>当 HBEN = 1 时，首先输出 MSB，然后输出 LSB。当 HBEN = 0 时，首先输出 LSB，然后输出 MSB。</p> |

| 33       | DB15/BYTE_SEL | DI/O | <p>当 <u>PAR/SER/BYTE_SEL</u> 为逻辑低电平时，此管脚充当并行数字输出管脚。当 <u>PAR/SER/BYTE_SEL</u> 为逻辑高电平时，<u>BYTE_SEL</u> 管脚用来在串行接口模式与并行字节接口模式之间做出选择。当 <u>PAR/SER/BYTE_SEL</u> = 1 且 <u>BYTE_SEL</u> = 0 时，FSV7606 工作在串行接口模式。</p> <p>当 <u>PAR/SER/BYTE_SEL</u> = 1 且 <u>BYTE_SEL</u> = 1 时，FSV7606 工作在并行字节接口模式。</p>             |

| 34       | REF_SELECT    | DI   | 内部/外部基准电压选择输入。如果 <u>REF_SELECT</u> 为逻辑高电平，则选择并使能内部基准电压。如果此管脚为逻辑低电平，则必须将外部基准电压施加在 <u>REFIN/REFOUT</u> 管脚。                                                                                                                                                                                                   |

| 35       | AGND          | GND  | 模拟地                                                                                                                                                                                                                                                                                                        |

| 36,39    | REGCAP        | PWR  | 内部稳压器电压输出。应分别将这两个输出管脚与 AGND 之间连接一个 $1\mu\text{F}$ 去耦电容。这些管脚上的电压在 1.9V 左右。                                                                                                                                                                                                                                  |

| 37,38    | AVCC          | PWR  | 模拟电源电压。通过 $100\text{nF}$ 与 $10\mu\text{F}$ 的并联去耦电容连接至 AGND。                                                                                                                                                                                                                                                |

| 40,41,47 | AGND          | GND  | 模拟地                                                                                                                                                                                                                                                                                                        |

| 42       | REFIN/REFOUT  | A    | 基准电压输入 (REFIN) / 基准电压输出 (REFOUT)。如果 <u>REF_SELECT</u> 管脚为逻辑高电平，此管脚将提供 2.5V 片内基准电压供外部使用。如果 <u>REF_SELECT</u> 管脚设置为逻辑低电平，需要将 2.5V 外部基准电压施加到此输入端。无论使用内部还是外部基准电压，都需要在该管脚与 <u>REFGND</u> 之间连接一个 $10\mu\text{F}$ 电容。                                                                                             |

| 43,46    | REFGND        | GND  | 基准电压接地管脚。这些管脚应连接至 AGND。                                                                                                                                                                                                                                                                                    |

| 44       | REFCAPA       | A    | 基准电压缓冲器输出管脚。必须将 <u>REFCAPA</u> 和 <u>REFCAPB</u> 连接在一起，并通过低有效串联电阻 (ESR) 的 $10\mu\text{F}$ 陶瓷电容将此管脚连接至 AGND，这些管脚上的电压通常为 4V。                                                                                                                                                                                  |

| 45       | REFCAPB       | A    | 参见 <u>REFCAPA</u> 。                                                                                                                                                                                                                                                                                        |

| 48       | AVCC          | PWR  | 模拟电源电压。通过 $100\text{nF}$ 与 $10\mu\text{F}$ 的并联去耦电容连接至 AGND。                                                                                                                                                                                                                                                |

| 49       | V1            | AI   | 模拟输入管脚。此管脚为单端模拟输入，它的模拟输入范围由 <u>RANGE</u> 管脚决定。                                                                                                                                                                                                                                                             |

| 50       | V1GND         | GND  | 模拟输入接地管脚。所有模拟输入接地管脚都应当连接至系统 AGND 平面。                                                                                                                                                                                                                                                                       |

| 51       | V2            | AI   | 模拟输入管脚。此管脚为单端模拟输入，它的模拟输入范围由 <u>RANGE</u> 管脚决定。                                                                                                                                                                                                                                                             |

| 52       | V2GND         | GND  | 模拟输入接地管脚。所有模拟输入接地管脚都应当连接至系统 AGND 平面。                                                                                                                                                                                                                                                                       |

| 53       | V3            | AI   | 模拟输入管脚。此管脚为单端模拟输入，它的模拟输入范围由 <u>RANGE</u> 管脚决定。                                                                                                                                                                                                                                                             |

| 54       | V3GND         | GND  | 模拟输入接地管脚。所有模拟输入接地管脚都应当连接至系统 AGND 平面。                                                                                                                                                                                                                                                                       |

| 编号 | 名称    | 类型  | 说明                                      |

|----|-------|-----|-----------------------------------------|

| 55 | V4    | AI  | 模拟输入管脚。此管脚为单端模拟输入，它的模拟输入范围由 RANGE 管脚决定。 |

| 56 | V4GND | GND | 模拟输入接地管脚。所有模拟输入接地管脚都应当连接至系统 AGND 平面。    |

| 57 | V5    | AI  | 模拟输入管脚。此管脚为单端模拟输入，它的模拟输入范围由 RANGE 管脚决定。 |

| 58 | V5GND | GND | 模拟输入接地管脚。所有模拟输入接地管脚都应当连接至系统 AGND 平面。    |

| 59 | V6    | AI  | 模拟输入管脚。此管脚为单端模拟输入，它的模拟输入范围由 RANGE 管脚决定。 |

| 60 | V6GND | GND | 模拟输入接地管脚。所有模拟输入接地管脚都应当连接至系统 AGND 平面。    |

| 61 | V7    | AI  | 模拟输入管脚。此管脚为单端模拟输入，它的模拟输入范围由 RANGE 管脚决定。 |

| 62 | V7GND | GND | 模拟输入接地管脚。所有模拟输入接地管脚都应当连接至系统 AGND 平面。    |

| 63 | V8    | AI  | 模拟输入管脚。此管脚为单端模拟输入，它的模拟输入范围由 RANGE 管脚决定。 |

| 64 | V8GND | GND | 模拟输入接地管脚。所有模拟输入接地管脚都应当连接至系统 AGND 平面。    |

## 绝对最大额定值

| 参数                | 最小值                 | 最大值        | 单位 |

|-------------------|---------------------|------------|----|

| <b>温度</b>         |                     |            |    |

| 工作温度              | -40                 | 125        | °C |

| 存储温度              | -65                 | 150        | °C |

| 结温                |                     | 150        | °C |

| 回流焊               | 铅锡焊接温度 (10 秒到 30 秒) | 240        | °C |

|                   | 无铅焊接温度              | 260        | °C |

| <b>耐压</b>         |                     |            |    |

| AVCC 至 AGND       | -0.3                | 7          | V  |

| VDRIVE 至 AGND     | -0.3                | AVCC+0.3   | V  |

| 模拟输入至 AGND        | -18.5               | 18.5       | V  |

| 数字输入至 AGND        | -0.3                | VDRIVE+0.3 | V  |

| 数字输出至 AGND        | -0.3                | VDRIVE+0.3 | V  |

| REFIN 至 AGND      | -0.3                | AVCC+0.3   | V  |

| <b>限流</b>         |                     |            |    |

| 输入电流 <sup>1</sup> | -10                 | 10         | mA |

| <b>ESD</b>        |                     |            |    |

| HBM               | 除模拟输入外的所有管脚         | 7000       | V  |

|                   | 仅模拟输入管脚             | 7000       | V  |

| CDM               |                     | 500        | V  |

注 1: 只针对除电源管脚外任意管脚。另外, 瞬态电流达到 100mA 不会引起芯片闩锁。

## 电气规格

默认测试条件: VREF = 2.5V 内部/外部基准电压、AVCC = 4.75V 至 5.25V、VDRIVE = 1.7V 至 5.25V、fSAMPLE = 200kSPS、TA = -40°C 至 125°C。

| 参数          | 测试条件                          | 最小值  | 典型值    | 最大值 | 单位     |

|-------------|-------------------------------|------|--------|-----|--------|

| <b>动态性能</b> |                               |      |        |     |        |

| SNR         | ±10V 单端                       | 89.5 | 92     |     | dB     |

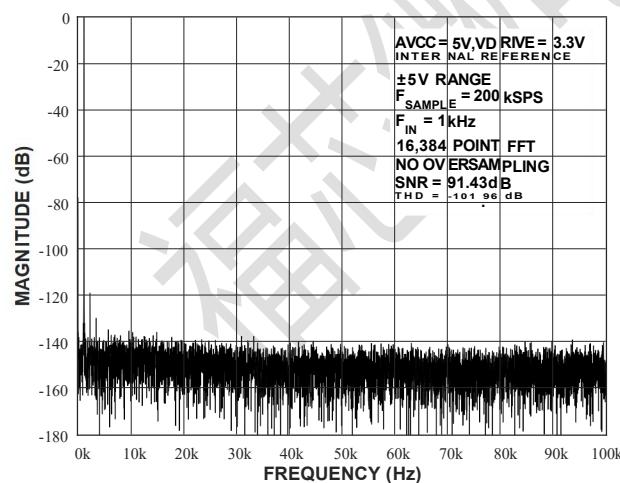

|             | ±5V 单端                        | 88.5 | 91     |     | dB     |

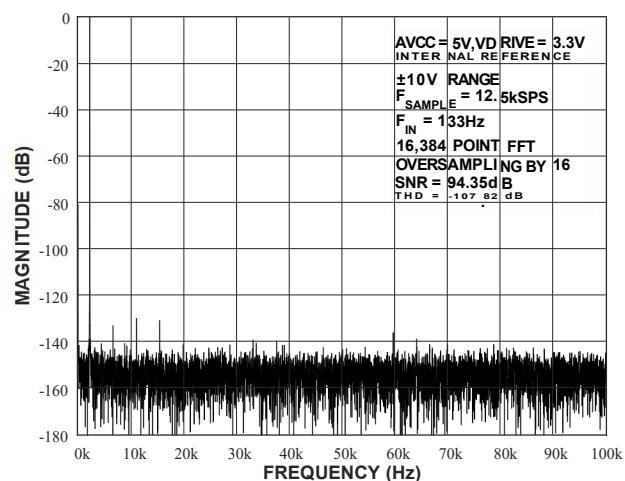

|             | OS = 16, ±5V 单端, fIN = 130Hz  |      | 93.5   |     | dB     |

|             | OS = 16, ±10V 单端, fIN = 130Hz |      | 94.3   |     | dB     |

| SINAD       | ±10V 单端                       | 89.2 | 92     |     | dB     |

|             | ±5V 单端                        | 88.2 | 91     |     | dB     |

| SFDR        | ±10V 单端                       | 96   | 108    |     | dB     |

| THD         | ±10V 单端                       |      | -105   | -95 | dB     |

| IMD         | fa = 1kHz, fb = 1.1kHz, 二阶项   |      | -105.4 |     | dB     |

|             | fa = 1kHz, fb = 1.1kHz, 三阶项   |      | -112.7 |     | dB     |

| 通道隔离度       | 未选中通道的 fIN 不超过 100 kHz        |      | -110   |     | dB     |

| <b>直流精度</b> |                               |      |        |     |        |

| DNL         | 16bit                         | ±0.8 | ±0.99  |     | LSB    |

| INL         | 16bit                         | ±1   | ±2     |     | LSB    |

| PFS         | 外部基准电压源                       | ±4   | ±16    |     | LSB    |

|             | 内部基准电压源                       | ±4   |        |     | LSB    |

| PFS 匹配      | ±10V 范围                       | 2    | 8      |     | LSB    |

|             | ±5V 范围                        | 6    | 16     |     | LSB    |

| PFS 漂移      | 外部基准电压源                       | ±2   |        |     | ppm/°C |

|             | 内部基准电压源                       | ±8   |        |     | ppm/°C |

| NFS         | 外部基准电压源                       | ±4   | ±16    |     | LSB    |

|             | 内部基准电压源                       | ±4   |        |     | LSB    |

| NFS 匹配      | ±10V 范围                       | 2    | 8      |     | LSB    |

|             | ±5V 范围                        | 6    | 16     |     | LSB    |

| NFS 漂移      | 外部基准电压源                       | ±2   |        |     | ppm/°C |

|             | 内部基准电压源                       | ±8   |        |     | ppm/°C |

| 双极性 0 码误差   | ±10V 范围                       | ±1   | ±3     |     | LSB    |

|             | ±5V 范围                        | ±5   | ±12    |     | LSB    |

| 双极性 0 码误差匹配 | ±10V 范围                       | 1    | 6      |     | LSB    |

|             | ±5V 范围                        | 6    | 15     |     | LSB    |

| 参数               | 测试条件                    | 最小值   | 典型值  | 最大值   | 单位     |

|------------------|-------------------------|-------|------|-------|--------|

| 双极性 0 码误差漂移      | ±10V 范围                 |       | 10   |       | µV/°C  |

|                  | ±5V 范围                  |       | 5    |       | µV/°C  |

| <b>模拟输入滤波器</b>   |                         |       |      |       |        |

| 全功率带宽            | -3dB, ±10V 范围           |       | 20.6 |       | kHz    |

|                  | -3dB, ±5V 范围            |       | 13.3 |       | kHz    |

|                  | -0.1dB, ±10V 范围         |       | 4.4  |       | kHz    |

|                  | -0.1dB, ±5V 范围          |       | 2    |       | kHz    |

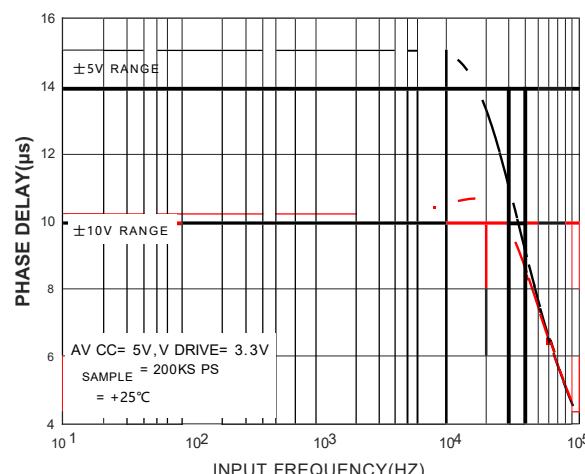

| 群延迟              | ±10V 范围                 |       | 11   |       | us     |

|                  | ±5V 范围                  |       | 15   |       | us     |

| <b>模拟输入</b>      |                         |       |      |       |        |

| 模拟输入电流           | 输入电压 10V                |       | 6.67 |       | µA     |

| 输入阻抗             |                         |       | 1    |       | MΩ     |

| <b>基准电压输入/输出</b> |                         |       |      |       |        |

| 基准输入电压范围         |                         | 2.475 | 2.5  | 2.525 | V      |

| 基准输出电压           | REFIN/REFOUT            |       | 2.5  |       | V      |

| 基准源温度系数          |                         |       | ±7   |       | ppm/°C |

| <b>电源功耗</b>      |                         |       |      |       |        |

| AVCC             |                         | 4.75  |      | 5.25  | V      |

| VDRIVE           |                         | 1.7   |      | 5.25  | V      |

| IAVCC            | 关断模式                    |       | 1    | 3     | µA     |

|                  | 待机模式                    |       | 5.7  | 8.5   | mA     |

|                  | 静态模式                    |       | 16.5 | 23    | mA     |

|                  | 转换模式, fSAMPLE = 200kSPS |       | 21.5 | 28    | mA     |

| IVDRIVE          | 转换模式, fSAMPLE = 200kSPS |       |      | 2     | mA     |

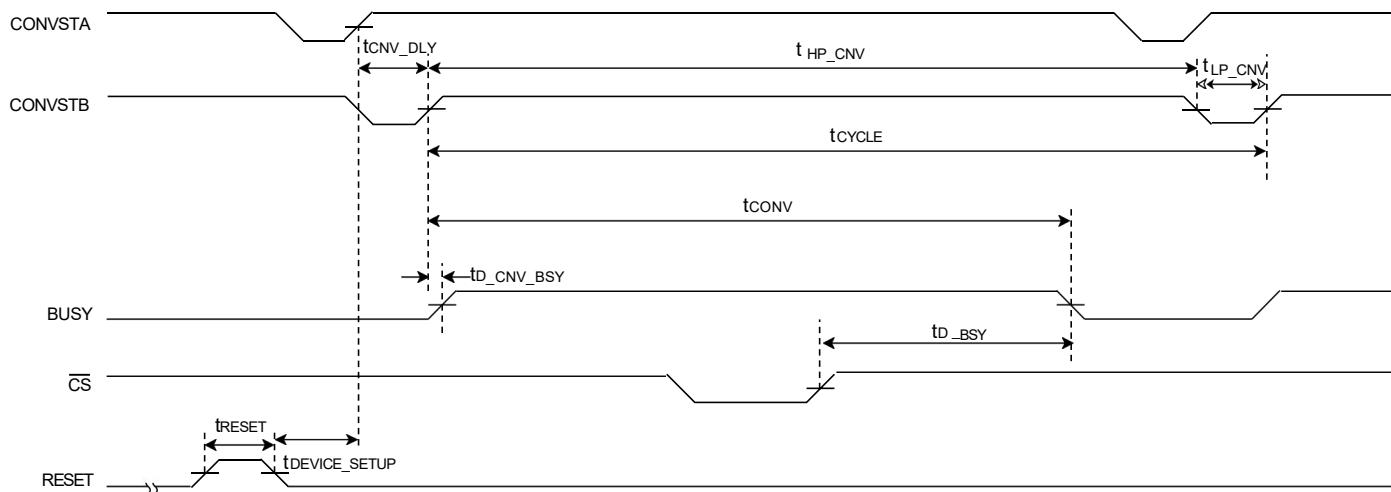

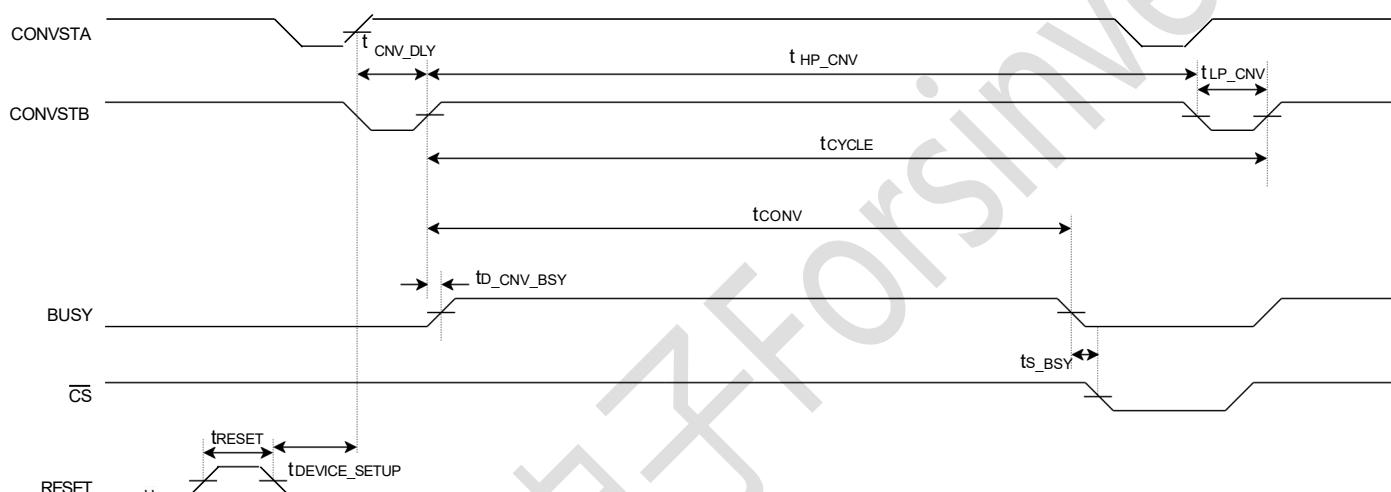

## 时序规格

默认测试条件: TA = -40°C 至 125°C、AVCC = 4.75V 至 5.25V、VDRIVE = 1.7V 至 5.25V、VREF = 2.5V 内部/外部基准。

### 通用时序规格

| 参数                | 描述                                       | 最小值              | 典型值 | 最大值 | 单位 |

|-------------------|------------------------------------------|------------------|-----|-----|----|

| tCYCLE            | 计算公式为: 1/最大吞吐率                           | 1                |     |     | μs |

| tLP_CNV           | 最短 CONVSTx 低电平脉冲。                        | 10               |     |     | ns |

| tHP_CNV           | 最短 CONVSTx 高电平脉冲。                        | 10               |     |     | ns |

| tD_CNV_BSY        | CONVSTx 高电平到 BUSY 高电平。                   |                  | 25  |     | ns |

| ts_BSY            | BUSY 下降沿到 CS 下降沿信号建立时间。                  | 0                |     |     | ns |

| tD_BSY            | 最后 CS 上升沿与 BUSY 下降沿之间的最长时间。              | 25               |     |     | ns |

| tDEVICE_SETUP     | RESET 低电平到 CONVSTx 高电平之间的最短延迟时间。         | 25               |     |     | ns |

| tCNV_DLY          | CONVSTA/B 上升沿之间最大容许延迟时间。                 |                  | 0.5 |     | ms |

| tCONV             | 转换时间, OS = 0                             |                  | 3   |     | μs |

|                   | 转换时间, OS = 2                             |                  | 8   |     | μs |

|                   | 转换时间, OS = 4                             |                  | 18  |     | μs |

|                   | 转换时间, OS = 8                             |                  | 38  |     | μs |

|                   | 转换时间, OS = 16                            |                  | 78  |     | μs |

|                   | 转换时间, OS = 32                            |                  | 158 |     | μs |

|                   | 转换时间, OS = 64                            |                  | 318 |     | μs |

| tRESET            | RESET 高电平脉冲宽度。                           | 50               |     |     | ns |

| tWAKE-UP_STANDBY  | STBY 上升沿到 CONVSTx 上升沿 (从待机模式上电时间)。       | 1                |     |     | μs |

| tWAKE-UP_SHUTDOWN | 内部基准, STBY 上升沿到 CONVSTx 上升沿 (从关断模式上电时间)。 | 200 <sup>1</sup> |     |     | ms |

|                   | 外部基准, STBY 上升沿到 CONVSTx 上升沿 (从关断模式上电时间)。 | 12               |     |     | ms |

注 1: 负载 10μF 电容。

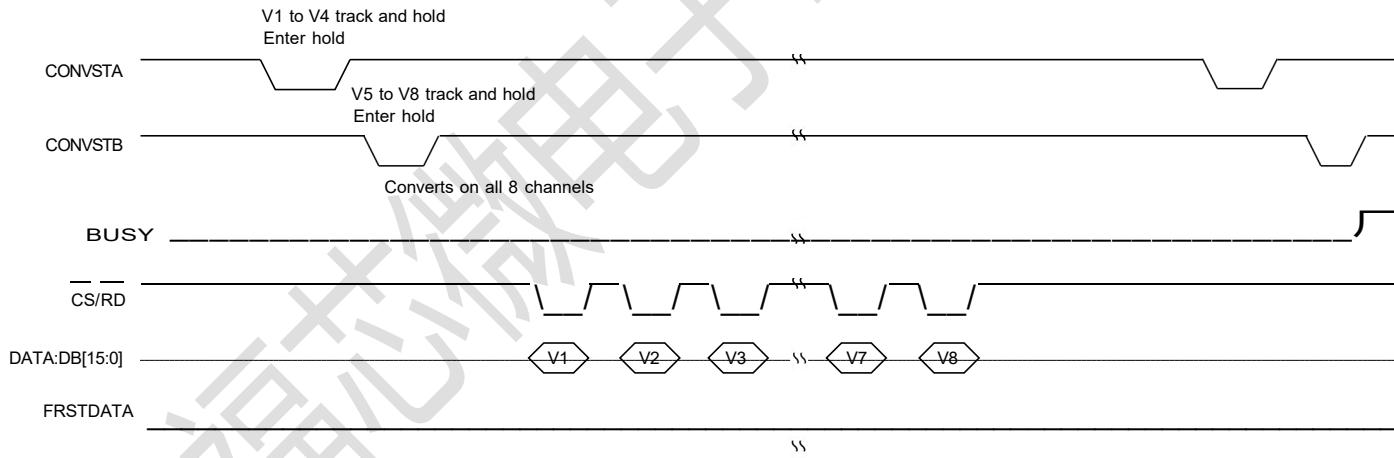

图 2 CONVST 时序-转换期间读取

图 3 CONVST 时序-转换之后读取

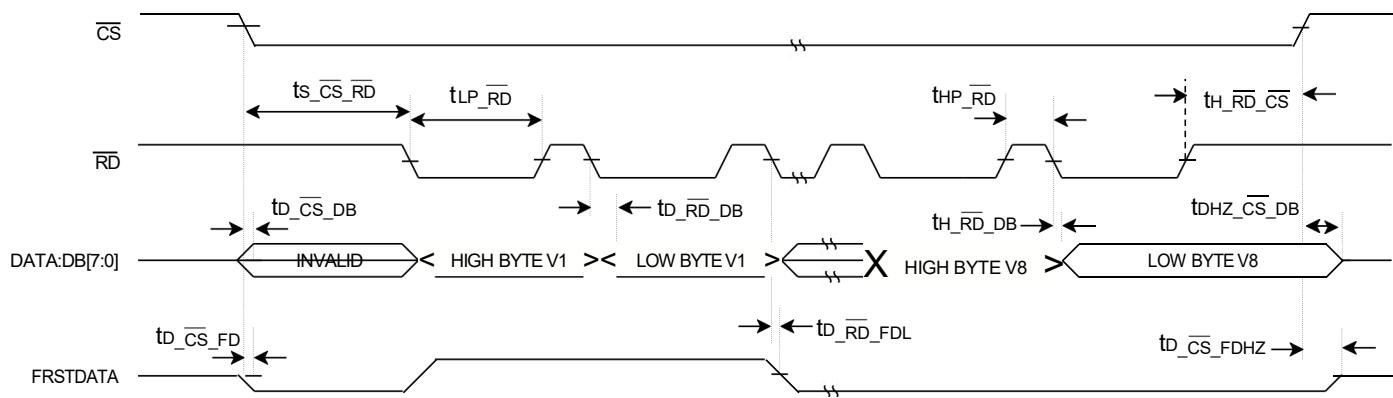

## FRSTDATA 时序规格

| 参数                | 描述                                        | 最小值 | 典型值 | 最大值 | 单位 |

|-------------------|-------------------------------------------|-----|-----|-----|----|

| $t_{D\_CS\_FD}$   | $\overline{CS}$ 下降沿到 FRSTDATA 的变化。        | 10  | 15  | 15  | ns |

| $t_{D\_RD\_FDL}$  | 从 $\overline{RD}$ 下降沿到 FRSTDATA 低电平的延迟时间。 | 13  | 21  | 21  | ns |

| $t_{D\_SCK\_FDL}$ | 从第 16 个 SCLK 下降沿到 FRSTDATA 低电平的延迟时间。      | 13  | 21  | 21  | ns |

| $t_{D\_CS\_FDHZ}$ | $\overline{CS}$ 上升沿到 FRSTDATA 高阻的延迟时间。    | 10  | 15  | 15  | ns |

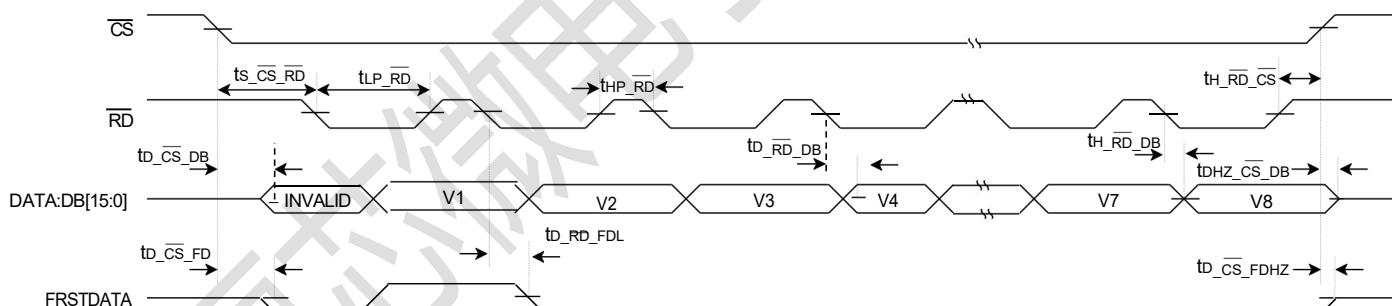

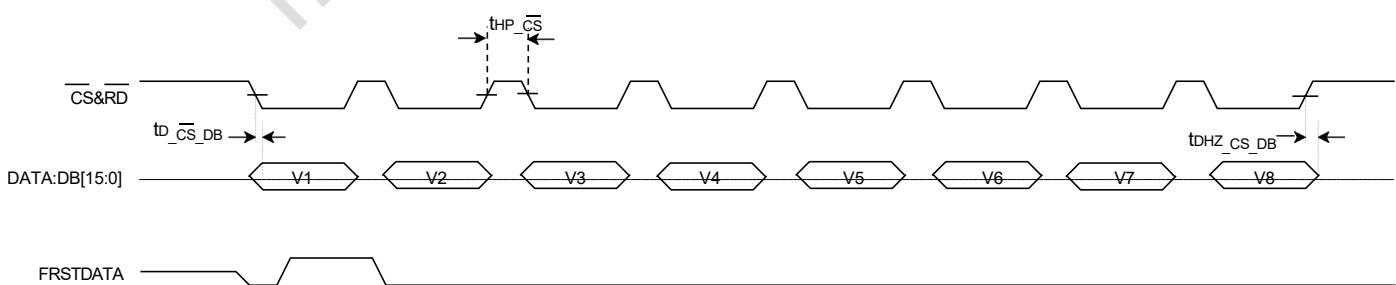

## 并行模式时序规格

| 参数              | 描述                                                | 最小值 | 典型值 | 最大值 | 单位 |

|-----------------|---------------------------------------------------|-----|-----|-----|----|

| $t_{S\_CS\_RD}$ | $\overline{CS}$ 下降沿到 $\overline{RD}$ 下降沿所需信号建立时间。 | 0   |     |     | ns |

| $t_{H\_RD\_CS}$ | $\overline{RD}$ 上升沿到 $\overline{CS}$ 上升沿所需信号保持时间。 | 0   |     |     | ns |

| $t_{HP\_RD}$    | $\overline{RD}$ 高电平脉冲宽度。                          | 17  |     |     | ns |

| 参数         | 描述                               | 最小值 | 典型值 | 最大值 | 单位 |

|------------|----------------------------------|-----|-----|-----|----|

| tLP_RD     | RD低电平脉冲宽度。<br>VDRIVE > 5.25V。    |     | 23  |     | ns |

|            | VDRIVE > 3.3V。                   | 25  |     |     | ns |

|            | VDRIVE > 2.3V。                   | 29  |     |     | ns |

|            | VDRIVE > 1.7V。                   | 36  |     |     | ns |

|            | CS高电平脉冲宽度。                       | 22  |     |     | ns |

| tD_CS_DB   | CS有效到数据位有效延迟。<br>VDRIVE > 5.25V。 | 15  | 23  |     | ns |

|            | VDRIVE > 3.3V。                   | 16  | 25  |     | ns |

|            | VDRIVE > 2.3V。                   | 18  | 29  |     | ns |

|            | VDRIVE > 1.7V。                   | 23  | 36  |     | ns |

|            | RD下降沿后的数据访问时间。                   |     |     |     |    |

| tD_RD_DB   | VDRIVE > 5.25V。                  | 15  | 23  |     | ns |

|            | VDRIVE > 3.3V。                   | 16  | 25  |     | ns |

|            | VDRIVE > 2.3V。                   | 18  | 29  |     | ns |

|            | VDRIVE > 1.7V。                   | 23  | 36  |     | ns |

|            | RD下降沿后数据保持时间。                    | 5   |     |     | ns |

| tDHZ_CS_DB | CS上升沿到数据无效保持时间。                  |     | 22  |     | ns |

图 4 并行模式, 独立的CS和RD脉冲

图 5 并行模式, CS和RD相连

图 6 字节模式读取操作

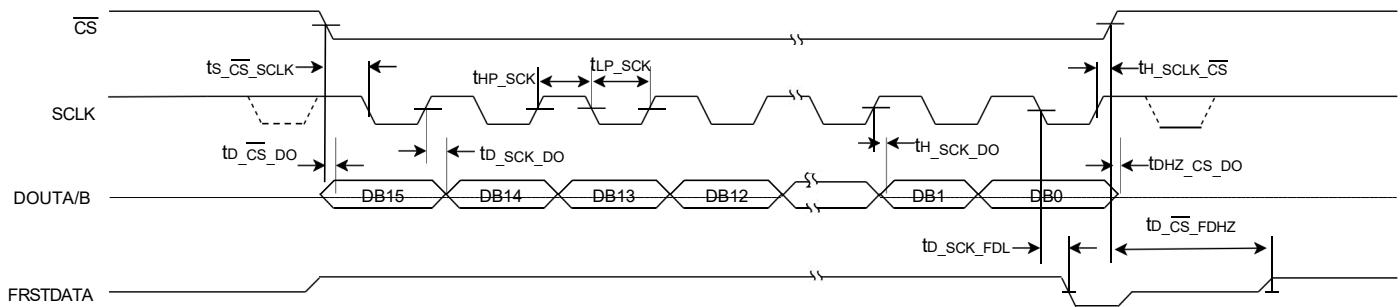

## 串行模式时序规格

| 参数         | 描述                              | 最小值      | 典型值 | 最大值 | 单位  |

|------------|---------------------------------|----------|-----|-----|-----|

| fSCLK      | 串行时钟频率, $f_{SCLK} = 1/t_{SCLK}$ |          |     |     |     |

|            | VDRIVE > 5.25V。                 |          | 20  |     | MHz |

|            | VDRIVE > 3.3V。                  |          | 16  |     | MHz |

|            | VDRIVE > 2.3V。                  |          | 14  |     | MHz |

|            | VDRIVE > 1.7V。                  |          | 11  |     | MHz |

| tLP_SCK    | SCLK 低电平脉冲宽度。                   | 0.4tSCLK |     |     | ns  |

| tHP_SCK    | SCLK 高电平脉冲宽度。                   | 0.4tSCLK |     |     | ns  |

| tD_CS_DO   | CS有效到数据有效的延迟。                   |          |     |     |     |

|            | VDRIVE > 5.25V。                 | 8        | 13  |     | ns  |

|            | VDRIVE > 3.3V。                  | 9        | 14  |     | ns  |

|            | VDRIVE > 2.3V。                  | 12       | 18  |     | ns  |

|            | VDRIVE > 1.7V。                  | 17       | 26  |     | ns  |

| tD_SCK_DO  | SCLK 上升沿后数据访问时间。                |          |     |     |     |

|            | VDRIVE > 5.25V。                 | 14       | 20  |     | ns  |

|            | VDRIVE > 3.3V。                  | 15       | 24  |     | ns  |

|            | VDRIVE > 2.3V。                  | 18       | 28  |     | ns  |

|            | VDRIVE > 1.7V。                  | 23       | 36  |     | ns  |

| tH_SCK_DO  | SCLK 上升沿后数据的保持时间。               | 5        |     |     | ns  |

| tDHZ_CS_DO | CS上升沿到数据不定态的延迟时间。               | 18       | 27  |     | ns  |

| ts_CS_SCLK | CS下降沿到 SCLK 下降沿的建立时间            | 2        |     |     | ns  |

| tH_SCLK_CS | SCLK 上升沿到CS上升沿的保持时间             | 3        |     |     | ns  |

图 7 串行读取操作

## 典型特征

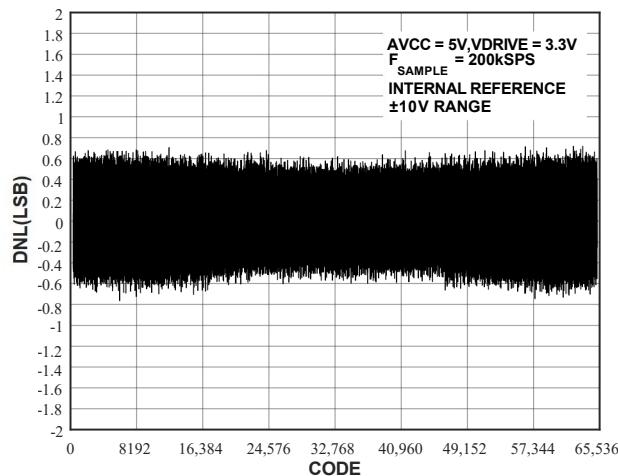

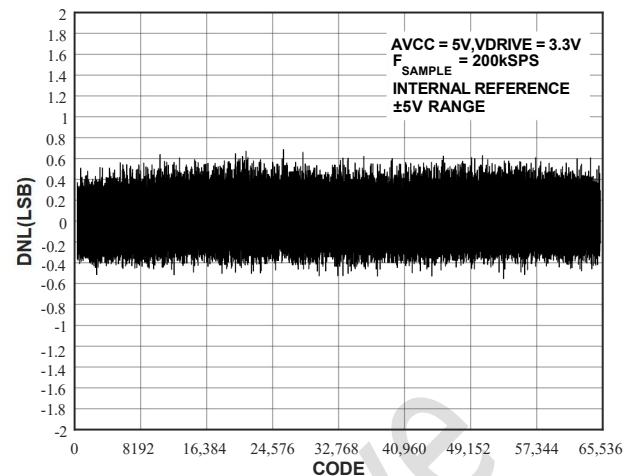

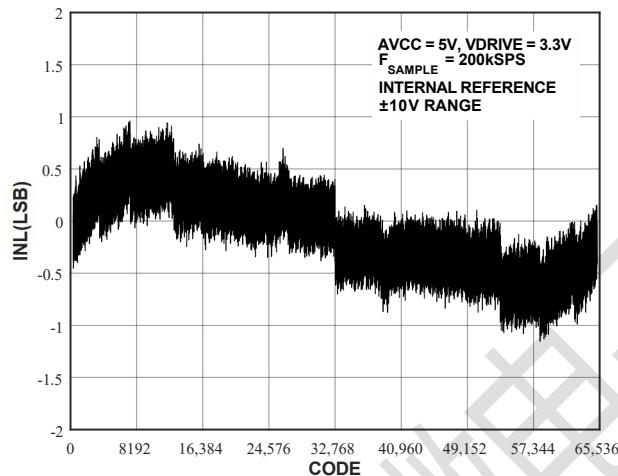

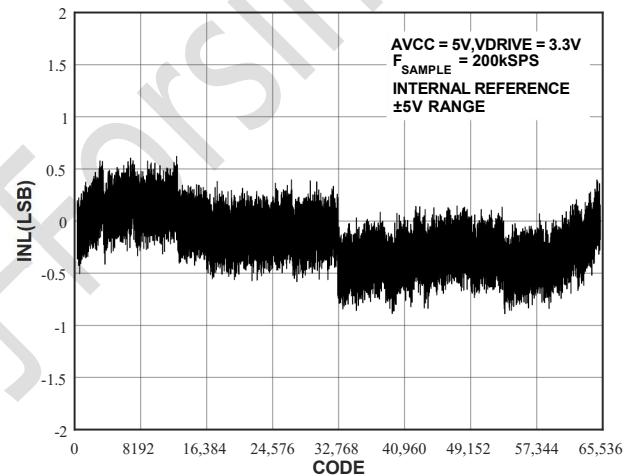

图 8 DNL 误差,  $\pm 10V$  范围图 9 DNL 误差,  $\pm 5V$  范围图 10 INL 误差,  $\pm 10V$  范围图 11 INL 误差,  $\pm 5V$  范围

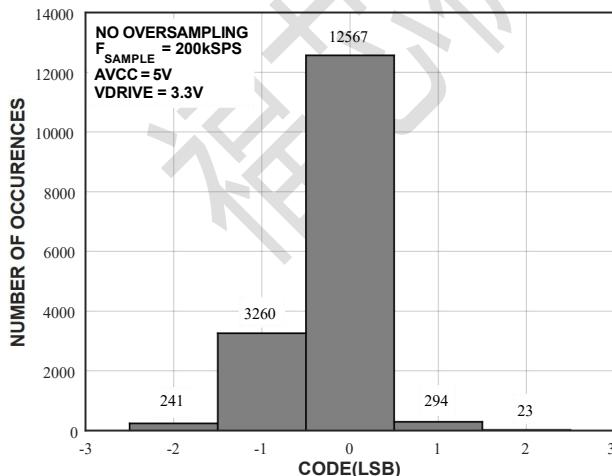

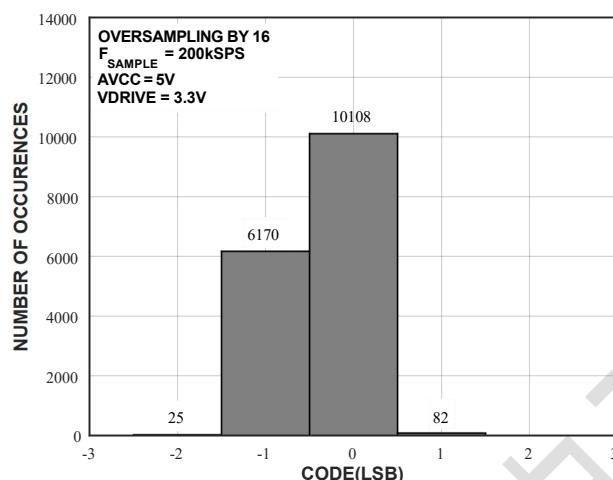

图 12 零输入直方图-No OS

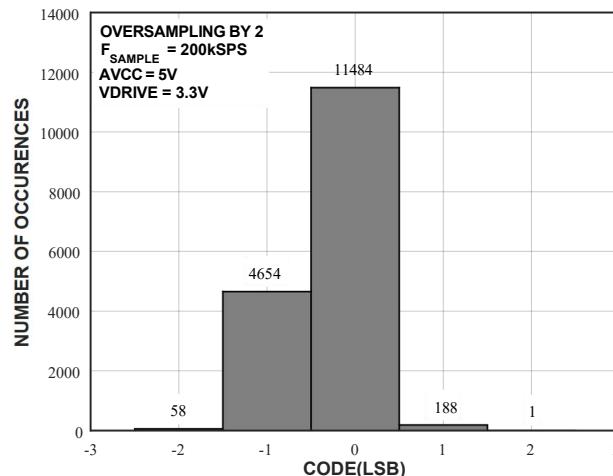

图 13 零输入直方图-OS×2

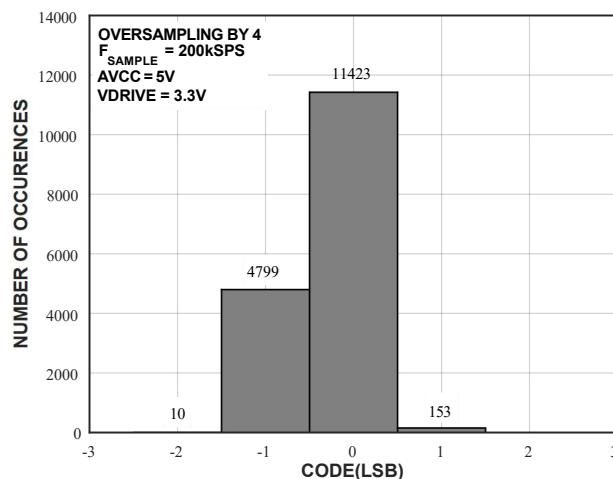

图 14 零输入直方图-OS×4

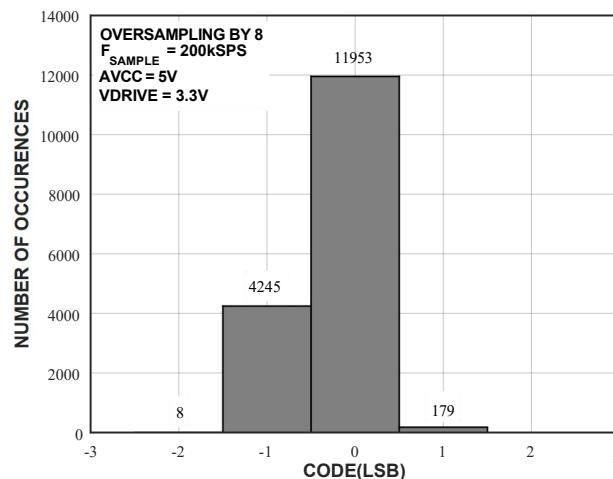

图 15 零输入直方图-OS×8

图 16 零输入直方图-OS×16

图 17 FFT, ±10V 范围

图 18 FFT, ±5V 范围

图 19 FFT 过采样(16), ±10V 范围

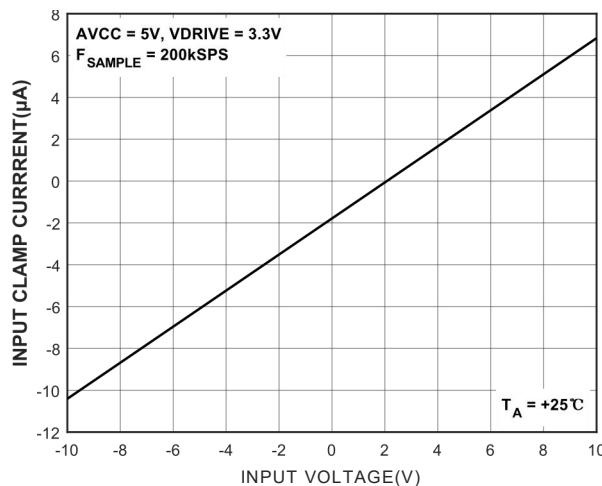

图 20 模拟输入电流与输入电压的关系

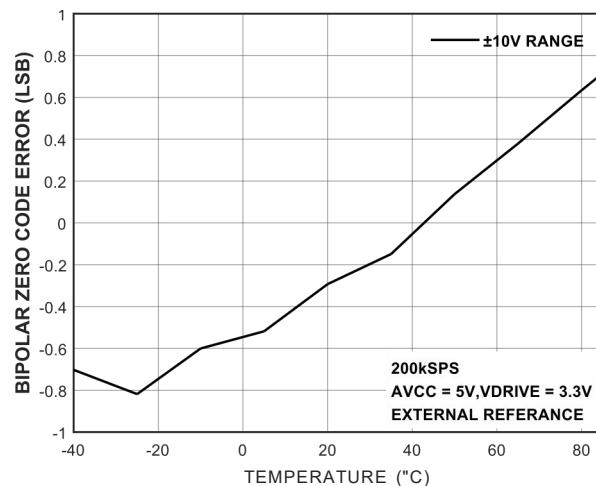

图 21 双极性 0 码误差的温度特性

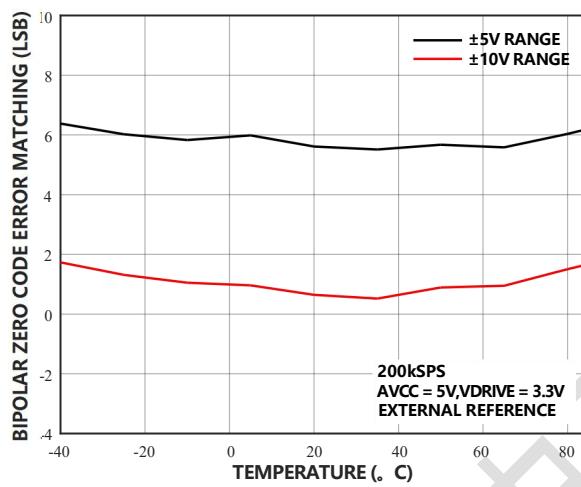

图 22 双极性 0 码误差匹配的温度特性

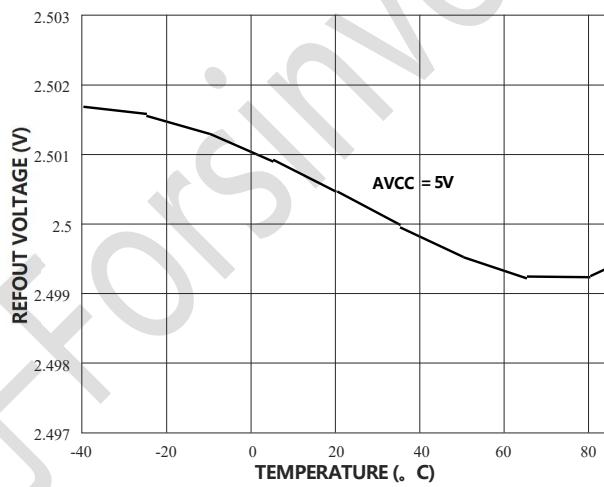

图 23 基准电压温度漂移

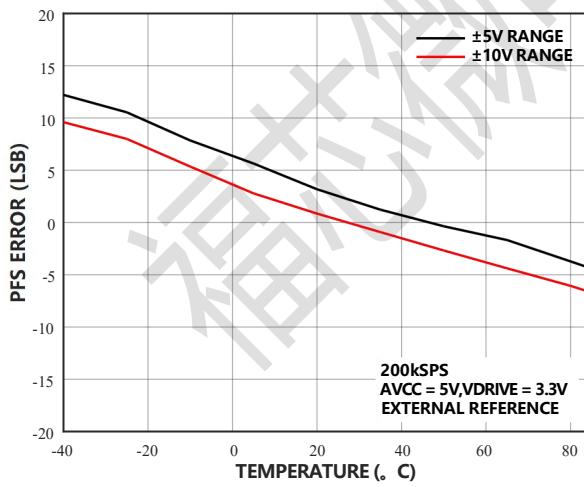

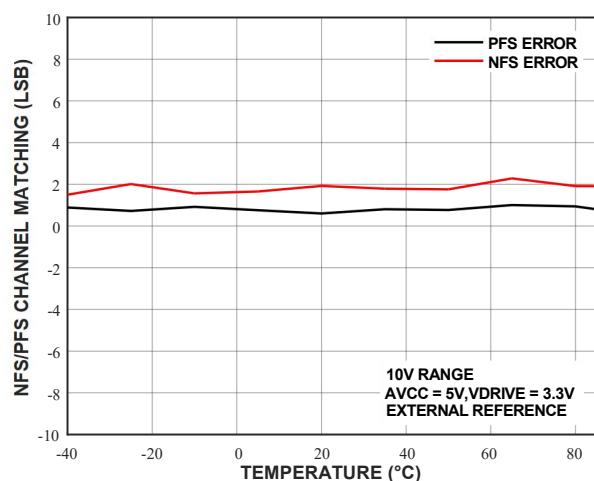

图 24 PFS 误差的温度特性

图 25 NFS 误差的温度特性

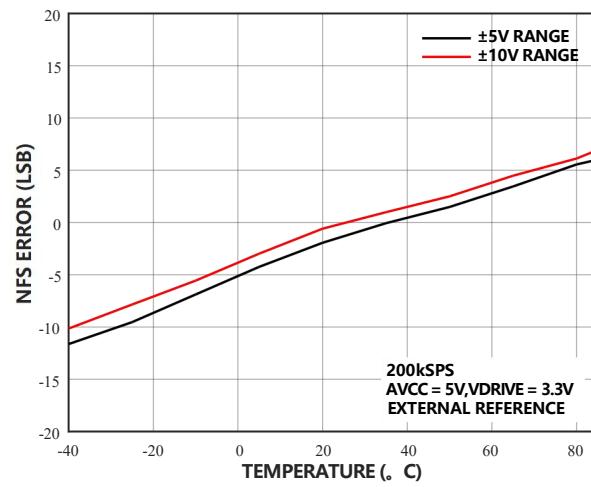

图 26 PFS/NFS 误差匹配的温度特性

## 工作原理

FSV7606 是一款采用高速、低功耗逐次逼近型 (SAR) 模数转换器的数据采集系统，可以分别对多至 8 个模拟输入通道进行同步采样，通过配置 RANGE 管脚，可选择  $\pm 5V$  或者  $\pm 10V$  的输入范围。FSV7606 采用单电源供电，但其所有模拟输入通道均可以接受真双极性输入信号。

芯片内置输入钳位保护、可编程放大器、二阶抗混叠滤波器、采样保持放大器、内部基准电压、基准电压缓冲器、高速 ADC、数字滤波器以及高速并行和串行接口。通过 CONVST 信号控制 FSV7606 的采样过程。

## 模拟输入

### 输入范围

FSV7606 可处理真双极性的单端输入信号，可通过 RANGE 管脚来配置模拟输入通道的电压范围。RANGE 为高电平时，则所有模拟输入电压范围为  $\pm 10V$ ；RANGE 为低电平时，则所有模拟输入电压范围为  $\pm 5V$ 。RANGE 管脚逻辑状态的改变会立即影响模拟通道的输入范围，在改变 RANGE 管脚逻辑状态的后，要预留  $80\mu s$  典型值的信号建立时间，再进行下次采样。

### 输入阻抗

FSV7606 的模拟输入阻抗均为  $1M\Omega$  的固定输入阻抗，不随芯片采样频率的变化而变化。高模拟输入阻抗可消除前端驱动放大器的需求，使其可以直接连接至信号源或传感器。该特性可以大大简化客户的硬件设计。

### 钳位保护

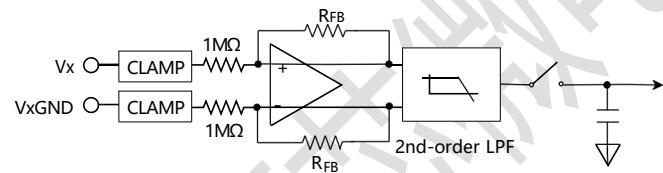

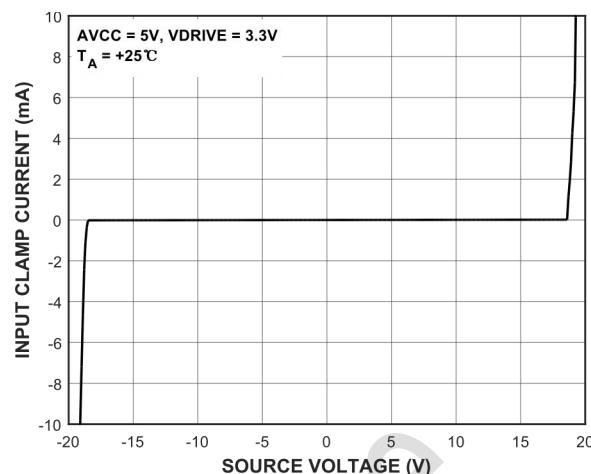

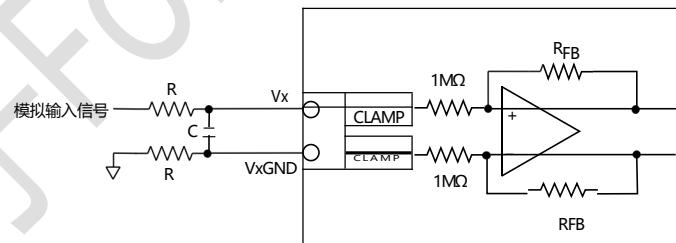

图 27 所示的各通道模拟输入均含有钳位保护电路。芯片在单 5V 供电的情况下，其模拟输入通道允许过压达到  $\pm 18.5V$ 。

图 27 模拟输入电路

图 28 显示了钳位电路的电压电流特性曲线。当输入电压不超过  $\pm 18.5V$  时，钳位电路不会开启。当输入电压超过  $\pm 18.5V$  时，钳位电路开启，模拟通道输入电流快速增加。

图 28 输入钳位电路 V-I 特性曲线

对于输入电压超过  $\pm 18.5V$  的应用，可以在外部串联电阻解决。值得注意的是，如果模拟输入通道 Vx 上添加了一个串联电阻，则其对应的模拟输入 GND 管脚，VxGND 上也需要串联一个与之相等的电阻。如果不添加这个电阻，该通道将出现额外的失调误差。

图 29 模拟输入端上输入电阻匹配

### 抗混叠滤波器

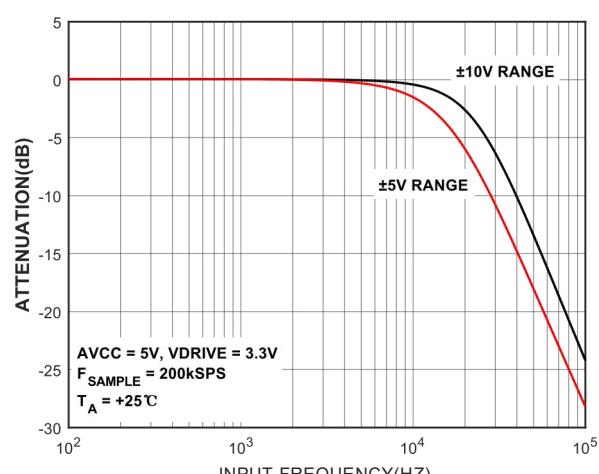

FSV7606 还提供了模拟抗混叠滤波器。在  $\pm 5V$  的范围内，-3dB 带宽的典型值为  $13.3kHz$ ，在  $\pm 10V$  的范围内，-3dB 带宽典型值为  $20.6kHz$ 。

图 30 模拟抗混叠滤波器幅频特性

图 31 模拟抗混叠滤波器相频特性

## 采样保持放大器

FSV7606 的采样保持放大器可使 ADC 精确采集满量程幅值的输入正弦波。采样保持放大器在 CONVST<sub>x</sub> 上升沿的时候完成对各自输入信号的同步采样，随后进入信号保持阶段。在整个转换期间，采样保持放大器都处于信号保持阶段，直到所有 8 个通道的转换过程已经全部结束，BUSY 的下降沿使得采样保持放大器重新回到采样阶段。

采样保持电路使得在转换期间进行数据的读取几乎不会影响 ADC 的性能，同时有助于实现更快的数据吞吐速率。但是在 VDRIVE 较高同时采用并行接口时，在转换期间读取数据可能会略微降低 ADC 的 SNR 性能。

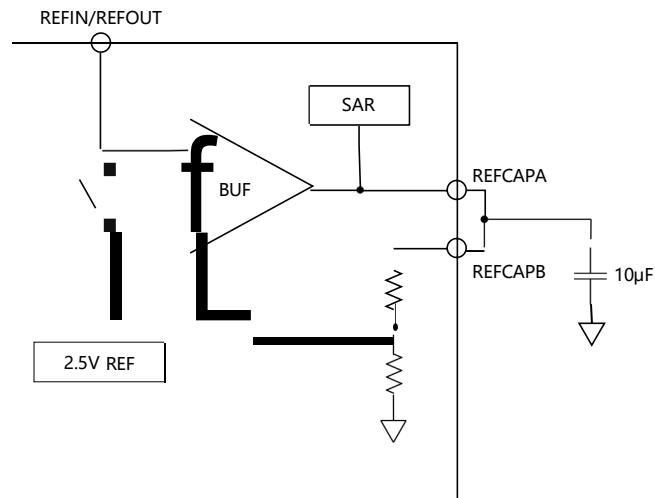

## 内部/外部基准

FSV7606 内置了一个 2.5V 的 Bandgap 基准电压源。REFIN/ REfout 管脚既可以使用该 2.5V 的基准电压，也允许从外部施加一个 2.5V 的基准电压。REF\_SELECT 管脚允许用户选择使用内部基准抑或是外部基准电压。如果此管脚设置为逻辑高，则选择并使能内部基准电压；如果此管脚设置为逻辑低电平，内部基准电压将被禁用，必须从外部施加一个基准电压到 REFIN/ REfout 管脚。无论使用内部基准还是外部基准模式，都需要在 REFIN/ REfout 管脚连接去耦电容，一般需要 10μF 的陶瓷去耦电容。FSV7606 内置了一个基准电压缓冲器，缓冲器可以将基准电压放大至约 4V。REFCAPA 和 REFCAPB 管脚必须外部短路在一起，并在尽量靠近芯片的位置放置一个 10μF 的陶瓷去耦电容，通过电容将这两个管脚连接至 REFGND，以确保基准电压缓冲器正常工作。

图 32 基准电压电路

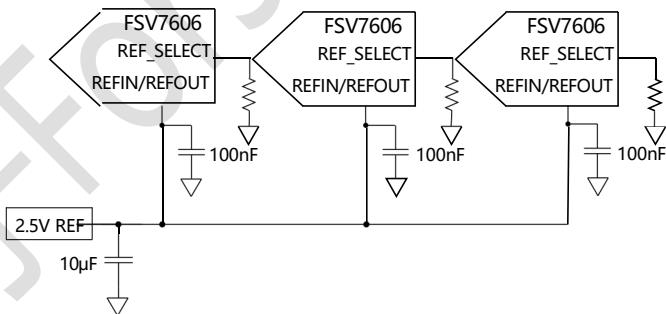

## 多芯片并联外部基准电压模式

对于使用多个 FSV7606 芯片的应用，如果采用外部基准电压，可以使用一个外部基准电压源驱动所有 FSV7606 芯片的 REFIN/ REfout 管脚。如图 33 所示，建议每一个 FSV7606 的 REFIN/ REfout 管脚都应使用至少一个 100nF 的去耦电容。

图 33 一个外部基准电压源驱动多个 FSV7606

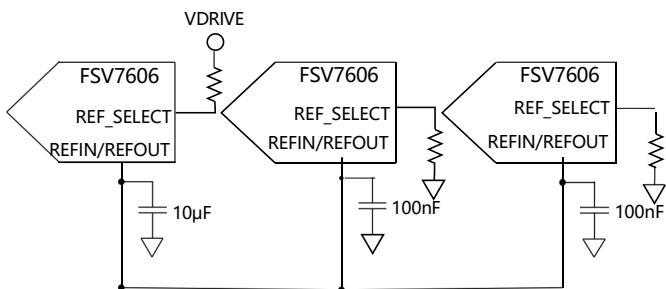

## 多芯片并联内部基准电压模式

当芯片配置为内部基准电压模式，其内部基准电压输出可以作为其余 FSV7606 芯片的外部基准源。其中，配置为内部基准电压模式的 FSV7606 应采用一个 10μF 的陶瓷电容对其实 REFIN/ REfout 管脚去耦。配置为外部基准电压模式的其他 FSV7606 芯片，在每个 REFIN/ REfout 管脚上，都应至少采用一个 100nF 的去耦电容。

图 34 内部基准电压源驱动多个 FSV7606

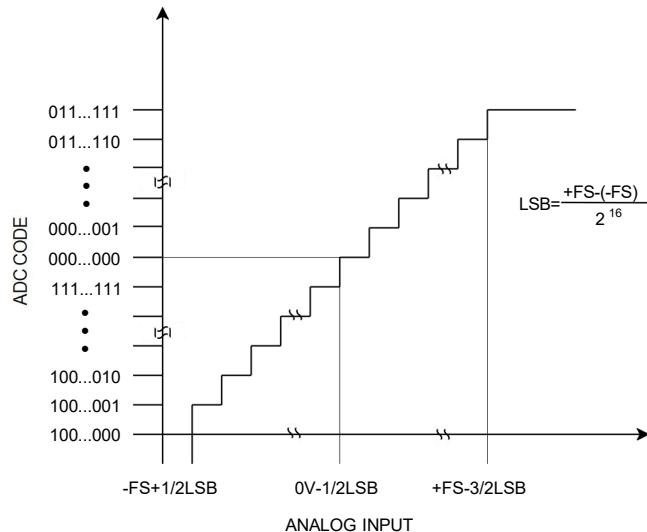

## ADC 传递函数

FSV7606 的 LSB 大小取决于 FSR 的大小, 即 FSR/65536, 其输出转换值的编码方式为二进制补码。

ADC 在  $\pm 10V$  RANGE、 $\pm 5V$  RANGE 的传递函数为:

$$\pm 10V \text{ CODE} = \frac{VIN}{10V} \times 32768 \times \frac{2.5V}{REF}$$

$$\pm 5V \text{ CODE} = \frac{VIN}{5V} \times 32768 \times \frac{2.5V}{REF}$$

图 35 传递特性

| RANGE     | +FS  | MIDSCALE | -FS  | LSB        |

|-----------|------|----------|------|------------|

| $\pm 10V$ | +10V | 0V       | -10V | $305\mu V$ |

| $\pm 5V$  | +5V  | 0V       | -10V | $152\mu V$ |

## 数字滤波器

FSV7606 内置一个可选的数字一阶 sinc 滤波器, 使用该滤波器能够得到更宽的动态范围, 但会降低模拟输入的带宽和 ADC 最大数据输出速率。数字滤波器的过采样率由过采样管脚 OS[2:0] 控制, 见表 2。OS2 为 MSB 控制位, OS0 为 LSB 控制位。表 2 提供了不同过采样率下的配置及带宽限制。

表 2 过采样位解码

| OS[2:0] | 过采样率 | 5V 范围 3dB 带宽(kHz) | 10V 范围 3dB 带宽(kHz) | 最大吞吐量 CONVST 频率(kHz) |

|---------|------|-------------------|--------------------|----------------------|

| 000     | 无过采样 | 13.3              | 20.6               | 200                  |

| 001     | 2    | 13.2              | 20.4               | 100                  |

| 010     | 4    | 11.1              | 17.5               | 50                   |

| 011     | 8    | 9.9               | 11.8               | 25                   |

| 100     | 16   | 6                 | 5.8                | 12.5                 |

| 101     | 32   | 3                 | 3                  | 6.25                 |

| 110     | 64   | 1.5               | 1.6                | 3.125                |

| 111     | 无效   |                   |                    |                      |

## 功能与模式

### 功耗模式

FSV7606 有四种功耗模式：转换模式、静态模式、待机模式和关断模式。

转换模式下，8 个通道 ADC 同时进行转换，此时为芯片的最大功耗模式，典型功耗为 107.5mW。

转换完成后，芯片进入静态模式，ADC 处于低功耗状态，但采样电路仍然保持在工作状态，以便能够随时响应 CONVST 信号立即进入转换模式。静态模式下功耗略有降低，典型功耗为 82.5mW。

STBY 管脚接低电平，RANGE 管脚接高电平时，进入待机模式，ADC 和采样电路都处于低功耗状态，芯片整体功耗进一步降低，典型值为 28.5mW。从待机模式退出后，内部电路需要 100μs 的建立时间，然后进入静态模式。

STBY 管脚和 RANGE 管脚都接低电平时，进入关断模式，大部分电路模块均关断，此时芯片的典型功耗为 5μW。从关断模式退出后需要 12ms 的等待时间才可以开始进行正常的转换功能。

表 3 显示了不同功耗模式的配置情况。

表 3 功耗模式选择

| 功耗模式 | STBY | RANGE |

|------|------|-------|

| 转换   | 1    | X     |

| 静态   | 1    | X     |

| 待机   | 0    | 1     |

| 关断   | 0    | 0     |

### 转换控制

CONVSTA 的上升沿用于通道 V1 至 V4 的同步采样控制，CONVSTB 的上升沿用于通道 V5 至 V8 的同步采样控制。基于这种分组控制逻辑，用户可选择对 8 个通道进行同步采样，此时应将 CONVSTA 和 CONVSTB 两个管脚连接在一起，同时给予上升沿激励。用户也可以对两组通道进行独立采样，分别在不同时刻给予 CONVSTA 和 CONVSTB 上升沿。通过对 CONVSTA 和 CONVSTB 的时间间隔控制，实现对采样信号的相位补偿。只有当两个 CONVST 信号均已收到上升沿激励后，BUSY 才会变为高电平，表示转换开始。在此独立采样模式下，不可使用过采样功能。时序如图 36 所示。

图 36 CONVSTA 和 CONVSTB 分别进行同步采样

## 数字接口

FSV7606 提供三种接口选项：并行接口、高速串行接口和并行字节接口。所需接口模式可通过 PAR/SER/BYTE\_SEL 和 DB15/BYTE\_SEL 管脚来选择，见表 4。

表 4 接口模式选择

| PAR/SER/BYTE_SEL | DB15 | 接口模式     |

|------------------|------|----------|

| 0                | -    | 并行接口模式   |

| 1                | 0    | 串行接口模式   |

| 1                | 1    | 并行字节接口模式 |

### 并行接口

可以用标准 CS 和 RD 信号通过并行数据总线从 FSV7606 读取数据。CS 输入信号上升沿使并行数据总线进入高阻态，下降沿则使总线脱离高阻状态。RD 管脚用来从转换结果寄存器中读取数据，对 FSV7606 的 RD 管脚施加低脉冲序列，可使各通道的转换结果按照通道序号逐个输出到并行总线 DB[15:0]。

BUSY 信号变为低电平后，第一个 RD 下降沿，并行总线上将输出通道 V1 的转换结果，下一个 RD 下降沿则将在总线上输出 V2 通道的转换结果，依此类推。

并行模式下，FRSTDATA 表示何时回读第一个转换通道 V1 的结果。第一个 RD 下降沿，FRSTDATA 变为高电平，在 V1 的结果全部读取完毕后，恢复低电平。

### 串行接口

FSV7606 有两个串行数据输出管脚：DOUTA 和 DOUTB。DOUTA 顺序输出通道转换数据，即按 V1、V2、V3、V4、V5、V6、V7、V8 的顺序输出；DOUTB 则是按照 V5、V6、V7、V8、V1、V2、V3、V4 的顺序输出转换数据。

CS 下降沿使数据线路 DOUTA 和 DOUTB 脱离高阻态，随后的 SCLK 上升沿则依次将所有数据位逐个送至对应的串行总线输出。可以使 CS 输入在整个串行读取的过程中拉低，也可以通过低脉冲的方式，以 16 个 SCLK 周期为一帧，逐帧读取。

可以仅用一路 DOUT，通过 8 帧读取所有通道的转换数据，这种情况下，建议用 DOUTA 访问所有转换数据。也可以双路同时读取，这样 4 帧读取即可完成所有通道的转换数据，此时 DOUTA 依次输出 V1、V2、V3、V4 的数据转换结果，DOUTB 依次输出 V5、V6、V7、V8 的数据转换结果。

FRSTDATA 输出信号指示何时回读第一通道 V1 的转换结果。在串行模式下，CS 下降沿使 FRSTDATA 脱离高阻态，并将 FRSTDATA 管脚设为高电平。在第 16 个 SCLK 下降沿后，FRSTDATA 输出恢复逻辑低电平。

### 并行字节接口

并行字节接口模式的工作原理与并行接口模式非常相似，不过各通道的转换结果是分两次 8 位传输读出。因此，读取 FSV7606

所有通道的转换结果需要 16 个 RD 脉冲。

在并行字节输出模式下，DB[7:0] 用来将数据并行输出，DB14 充当 HBEN 管脚。当 DB14/HBEN 被设置为逻辑高电平时，FSV7606 将首先输出转换数据的高字节 (MSB)，然后输出低字节 (LSB)。当 DB14/HBEN 设置为逻辑低电平时，则首先输出转换结果的低字节。

并行字节接口模式下，FRSTDATA 在读取 V1 通道的 MSB 和 LSB 数据过程中都保持高电平。

## 应用

### 典型连接

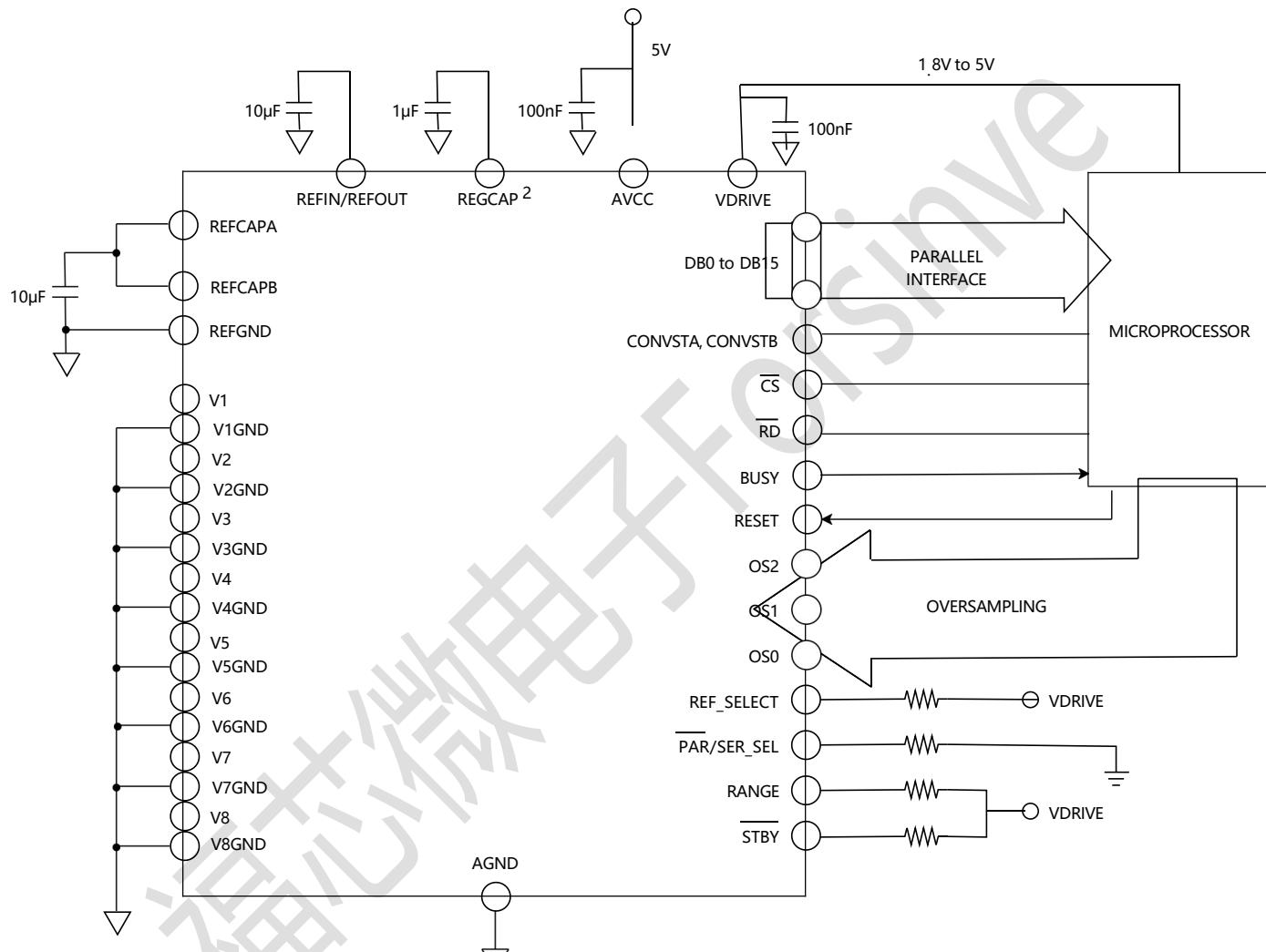

图 37 显示了 FSV7606 的典型连接图。FSV7606 有 4 个 AVCC 管脚，应当使用 4 个 100nF 去耦电容分别就近加在 4 个 AVCC 管脚处。4 个 AVCC 连接到一个总电源，并在总电源侧采用一个 10μF 去耦电容。

FSV7606 既可以在内部基准电压模式下工作，也可以在外部基准电压下工作。在图 37 配置中，FSV7606 被配置为在内部基准电

压下工作。当电路板上只有一个 FSV7606 芯片时，应采用一个 10μF 的电容对其 REFIN/REFOUT 管脚去耦。当应用中使用多个 FSV7606 芯片时，请参考[多芯片并联外部基准电压模式](#)以及[多芯片并联内部基准电压模式](#)章节。

REFCAPA 和 REFCAPB 管脚应当短路在一起，并与 REFGND 之间连接一个 10μF 的低 ESR 陶瓷去耦电容。

图 37 典型连接

## Ⅰ 封装及订购信息

### 封装方式

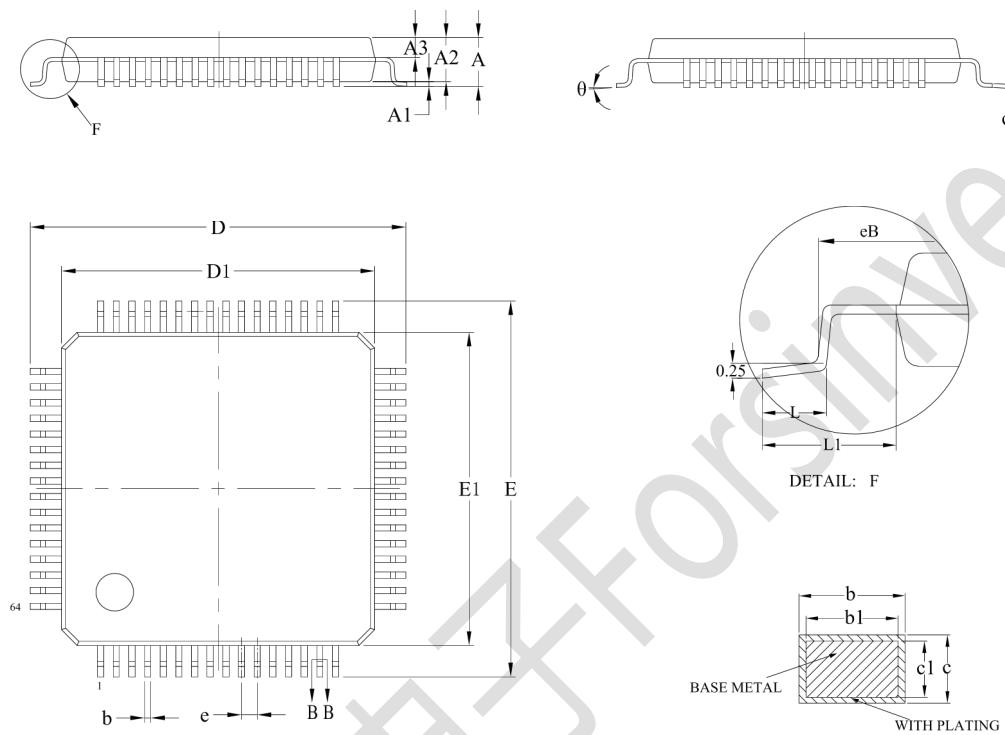

FSV7606 采用 LQFP64 封装。

### 产品外形图

产品外形图如下图所示。

| 标识 | 尺寸 (毫米)    |       |       |

|----|------------|-------|-------|

|    | 最小值        | 典型值   | 最大值   |

| A  | -          | -     | 1.60  |

| A1 | 0.05       | 0.10  | 0.15  |

| A2 | 1.35       | 1.40  | 1.45  |

| A3 | 0.59       | 0.64  | 0.69  |

| b  | 0.18       | 0.22  | 0.26  |

| b1 | 0.17       | 0.20  | 0.23  |

| c  | 0.13       | 0.15  | 0.17  |

| c1 | 0.12       | 0.13  | 0.14  |

| D  | 11.80      | 12.00 | 12.20 |

| D1 | 9.90       | 10.00 | 10.10 |

| E  | 11.80      | 12.00 | 12.20 |

| E1 | 9.90       | 10.00 | 10.10 |

| e  | 0.50 (BSC) |       |       |

| eB | 11.05      | 11.15 | 11.25 |

| L  | 0.45       | 0.60  | 0.75  |

| L1 | 1.00 (REF) |       |       |

| θ  | 0          | 3.5°  | 7°    |

## 订购信息

| 型号         | 温度范围        | 封装     | 包装   |

|------------|-------------|--------|------|

| FSV7606-LT | -40°C~125°C | LQFP64 | Tray |