# 5-Channel Capacitive Touch and Proximity Controller

# **FEATURES**

- 5-channel capacitive sensing

- > Self-capacitive sensing techniques

- Auto-Calibration

- Capacitance resolution down to 4aF

- ➤ With range of parasitic capacitance: 0~220pF

- Independent configurations per channel

- 400kHz I<sup>2</sup>C interface

- Default address: 0x12

- Address can be modified through CS2 pin

- External interrupt pin, open-drain output

- Built-in brown-out reset(BOR)

- Low power consumption

Active mode: 26 uA

Doze mode: 9uA

Deep sleep mode: 4 uA

- 1.7V~3.6V power supply

- Operation temperature range:-25°C~85°C

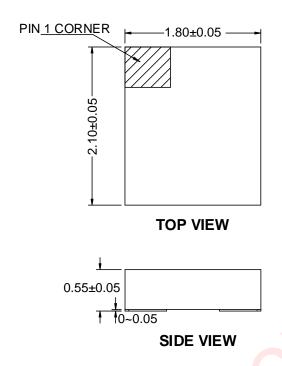

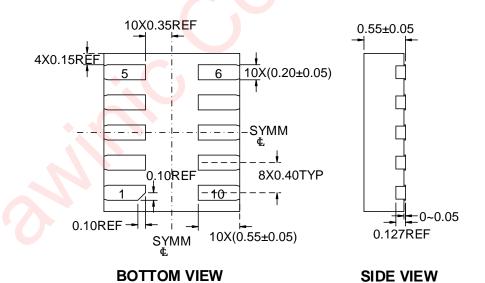

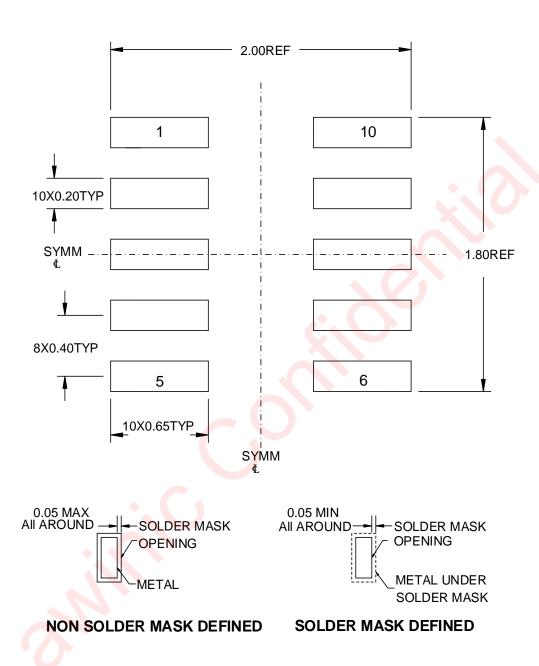

- DFN 2.1mm×1.8mm×0.55mm-10L package

## **APPLICATIONS**

Mobile phones

Wearable Devices

## **GENERAL DESCRIPTION**

AW96105 is a 5-channel low power capacitive touch and proximity controller. Each channel can be independently configured as sensor input, shield output.

Advanced self-capacitance technology is adopted in AW96105, which supports parasitic capacitance compensation for each channel up to 220pF. For the device has a high resolution ADC, the minimal capacitance that can be detected is as low as 4aF.

AW96105 integrates a low power MCU, by executing the algorithm program in the ROM, it is capable to perform the basic operations such as signal filtering, baseline calculation, automatic compensation for environmental drift, RF noise suppression, proximity judgment, etc..

One or two sensor channels can be configured as reference channel. The reference channel and internal temperature sensor can be used to correct the detected result. With the help of auto calibration, the device is able to track slow environmental variations(such as temperature, humidity, etc.) and maintain high performance operation.

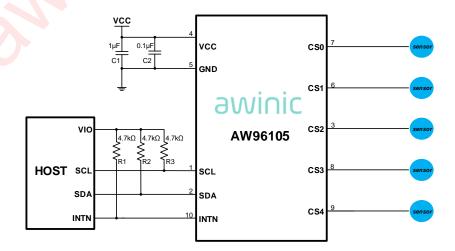

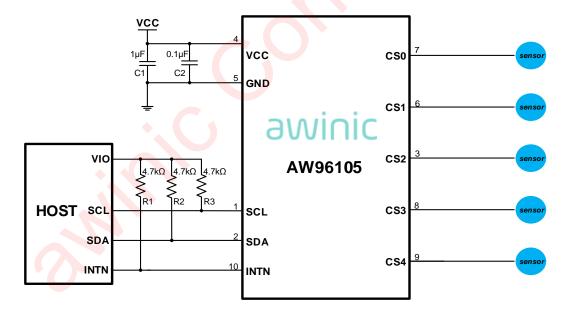

## TYPICAL APPLICATION CIRCUIT

Figure 1 AW96105 Typical Application Circuit

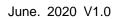

# PIN CONFIGURATION AND TOP MARK

AW96105DNR Marking (TOP View)

YWP5 - AW96105DNR XXXX - Product Tracing Code

## **PIN DEFINITION**

| No. | NAME | DESCRIPTION                                                                                                 |  |  |  |  |  |

|-----|------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1   | SCL  | I <sup>2</sup> C clock, requires pull-up resistor                                                           |  |  |  |  |  |

| 2   | SDA  | I <sup>2</sup> C data, requires pull-up resistor                                                            |  |  |  |  |  |

| 3   | CS2  | Capacitive Sensor input/shield or I <sup>2</sup> C address select Input (Floating:0x12, GND:0x13, VCC:0x14) |  |  |  |  |  |

| 4   | VCC  | Power supply (1.7V~3.6V), requires decoupling capacitor                                                     |  |  |  |  |  |

| 5   | GND  | Ground                                                                                                      |  |  |  |  |  |

| 6   | CS1  | Capacitive sensor input/shield                                                                              |  |  |  |  |  |

| 7   | CS0  | Capacitive sensor input/shield                                                                              |  |  |  |  |  |

| 8   | CS3  | Capacitive sensor input/shield                                                                              |  |  |  |  |  |

| 9   | CS4  | Capacitive sensor input/shield                                                                              |  |  |  |  |  |

| 10  | INTN | Interrupt output, requires pull-up resistor                                                                 |  |  |  |  |  |

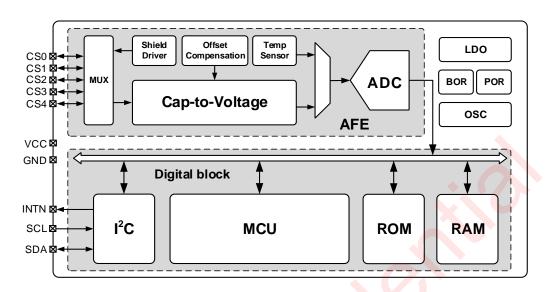

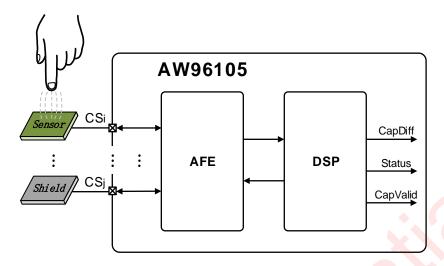

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2 Functional Block Diagram

Notes: AFE means Analog Front-End.

## TYPICAL APPLICATION CIRCUITS

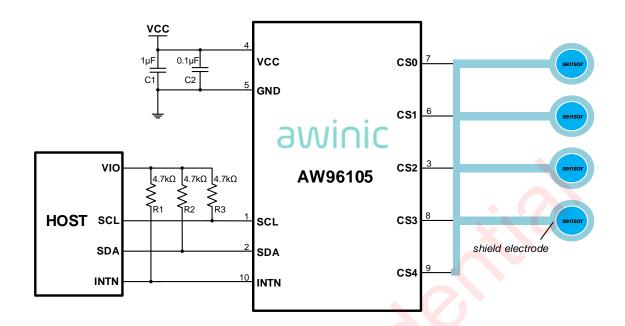

Figure 3 AW96105 Typical Application Circuit (for Touch Key)

Figure 4 AW96105 Typical Application Circuit (for Touch Key)

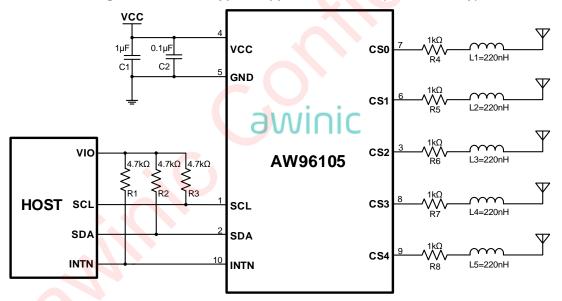

Figure 5 AW96105 Typical Application Circuit (for SAR Sensor)

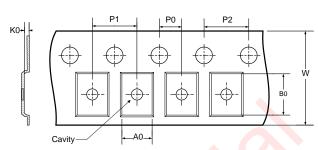

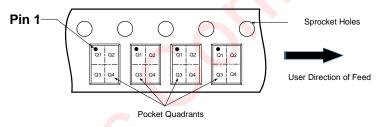

## **ORDERING INFORMATION**

| Part Number | Temperature | Package                    | Marking | Moisture<br>Sensitivity Level | Environmental<br>Information | Delivery Form                |

|-------------|-------------|----------------------------|---------|-------------------------------|------------------------------|------------------------------|

| AW96105DNR  | -25°C∼85°C  | DFN<br>2.1mmX1.8mm-<br>10L | YWP5    | MSL1                          | ROHS+HF                      | 3000 units/<br>Tape and Reel |

# **ABSOLUTE MAXIMUM RATINGS**(NOTE1)

| PARAMETER                    | RANGE                                                    |               |  |  |  |

|------------------------------|----------------------------------------------------------|---------------|--|--|--|

| Supply voltage ran           | Supply voltage range Vcc                                 |               |  |  |  |

| Input voltage range          | CSx, SCL, SDA, INTN                                      | -0.5V to 3.6V |  |  |  |

| Output voltage range         | CSx, SCL, SDA, INTN                                      | -0.5V to 3.6V |  |  |  |

| Junction-to-ambient therma   | Junction-to-ambient thermal resistance θ <sub>JA</sub>   |               |  |  |  |

| Operating free-air temper    | Operating free-air temperature range                     |               |  |  |  |

| Maximum operating junction t | Maximum operating junction temperature T <sub>JMAX</sub> |               |  |  |  |

| Storage temperatur           | Storage temperature T <sub>STG</sub>                     |               |  |  |  |

| Lead temperature (soldering  | Lead temperature (soldering 10 seconds)                  |               |  |  |  |

| ES                           | ESD(Including CDM HBM MM)                                |               |  |  |  |

| НВМ                          |                                                          | ±4kV          |  |  |  |

| CDM                          | CDM                                                      |               |  |  |  |

|                              | Latch-Up                                                 |               |  |  |  |

| Test condition: according    | to JESD78E                                               | +IT: 350mA    |  |  |  |

| rest condition, according    | IO JESDIOE                                               | -IT: -350mA   |  |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: The HBM test method: MIL MIL-STDSTDSTDSTD-883J, the CDM test method: ANSI/ESDA/JEDEC JS-002-2018.

# **ELECTRICAL CHARACTERISTICS**

Note:Typical values are given for T<sub>A</sub>= +25°C, VCC=2.8V unless otherwise specified.

| PAR                            | AMETER                                       | TEST CONDITION                                                                                                                                     | MIN   | TYP  | MAX   | UNIT |

|--------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| CHIP CURREN                    | ITS                                          |                                                                                                                                                    |       |      |       |      |

| IDEEPSLEEP                     | Deep Sleep Mode<br>Current                   | LDO on, OSC off, I <sup>2</sup> C listening.                                                                                                       | -     | 4    | 8     | μA   |

| Idoze                          | Doze Mode<br>Current                         | SCANPERIOD=400ms;<br>FREQ =100kHz;<br>RESOLUTION=64;<br>SSEN=1;ADC filt. and Adv.<br>features/engines OFF.<br>I <sup>2</sup> C listening. No load. | -     | 9    | 16    | μА   |

| IACTIVE                        | Active Mode<br>Current                       | SCANPERIOD=30ms;<br>FREQ=100kHz;<br>RESOLUTION=64;<br>SSEN=1; ADC filt. and Adv.<br>features/engines OFF.<br>I <sup>2</sup> C listening. No load.  | 0     | 26   | 48    | μА   |

| CAPACITANC                     | E SENSING                                    |                                                                                                                                                    |       |      |       |      |

| Crange                         | Measurement<br>Range                         |                                                                                                                                                    | ±0.55 | ±2.2 | ±9.9  | pF   |

| $N_{BIT}$                      | Measurement                                  |                                                                                                                                                    | -     | 20   | -     | bits |

| Cres                           | Resolution                                   |                                                                                                                                                    | -     | 4    | -     | aF   |

| Fosc                           | Nominal OSC<br>Frequency                     |                                                                                                                                                    | -     | 4    | -     | MHz  |

| F <sub>Trim</sub>              | OSC Trim<br>Accuracy                         | Ar <mark>ou</mark> nd Nominal Value,<br>Ta=25°C,VCC=2.8V                                                                                           | -4    | -    | 4     | %    |

| F <sub>Temp</sub>              | OSC Temp. Dependency                         | Around Nominal Value,<br>Ta=25°C,VCC=2.8V                                                                                                          |       | ±1   | -     | %    |

| F <sub>VCC</sub>               | OSC VCC<br>Dependency                        | Around Nominal Value,<br>Ta=25°C,VCC=2.8V                                                                                                          | -     | ±0.6 | -     | %    |

| Fs                             | Nominal Sampling Freq                        | Programmable with FREQ                                                                                                                             | -     | -    | 250   | kHz  |

| Сосехт                         | External DC Cap.to GND per Measurement Phase | One CSx as measured input                                                                                                                          | -     | -    | 220   | pF   |

| RFILTINUNIT                    | Pre-Charge Input<br>Res                      |                                                                                                                                                    | 0     | -    | 30    | kΩ   |

| RINTUNIT                       | Compensation Res                             |                                                                                                                                                    | 0     | -    | 8     | kΩ   |

| TEMPERATUR                     | RE SENSING                                   |                                                                                                                                                    |       |      |       |      |

| Tinrange                       | Input Range                                  | Ambient Temperature(T <sub>A</sub> )                                                                                                               | -25   | -    | 85    | °C   |

| T <sub>OUTRANGE</sub>          | Output Range                                 |                                                                                                                                                    | 0     | -    | 32767 | LSB  |

| I <sup>2</sup> C INTERFAC      | E                                            |                                                                                                                                                    |       |      |       |      |

| I <sub>OL</sub><br>(SDA, INTN) | Output low current                           | VOL≪0.4                                                                                                                                            | 8     |      |       | mA   |

| V <sub>IH</sub>                | Input high level                             | SCL, SDA                                                                                                                                           | 1.35  |      | 3.6   | V    |

| VIL                            | Input low level                              | SCL, SDA                                                                                                                                           | -0.5  |      | 0.45  | V    |

| tdeg_sda                       | SDA deglitch time                            | SDA                                                                                                                                                |       | 110  |       | ns   |

| t <sub>DEG_SCL</sub>           | SCL deglitch time                            | SCL                                                                                                                                                |       | 95   |       | ns   |

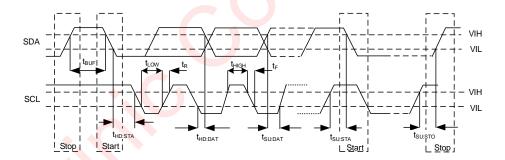

# I<sup>2</sup>C INTERFACE TIMING

|                     | PARAMETER                                 | MIN | TYP | MAX | UNIT |

|---------------------|-------------------------------------------|-----|-----|-----|------|

| F <sub>SCL</sub>    | Interface Clock frequency                 | -   |     | 400 | kHz  |

| T <sub>HD:STA</sub> | (Repeat-start) Start condition hold time  | 0.6 |     | -   | μS   |

| T <sub>LOW</sub>    | Low level width of SCL                    | 1.3 |     | -   | μS   |

| T <sub>HIGH</sub>   | High level width of SCL                   | 0.6 |     | -   | μs   |

| T <sub>SU:STA</sub> | (Repeat-start) Start condition setup time | 0.6 |     | - ( | μs   |

| T <sub>HD:DAT</sub> | Data hold time                            | 0   |     | -   | μS   |

| T <sub>SU:DAT</sub> | Data setup time                           | 0.1 |     | _   | μS   |

| T <sub>R</sub>      | Rising time of SDA and SCL                |     |     | 0.3 | μS   |

| T <sub>F</sub>      | Falling time of SDA and SCL               | -   |     | 0.3 | μS   |

| T <sub>SU:STO</sub> | Stop condition setup time                 | 0.6 |     | -   | μS   |

| T <sub>BUF</sub>    | Time between start and stop condition     | 1.3 |     | -   | μS   |

Figure 6 I<sup>2</sup>C Interface Timing

## **DETAILED FUNCTIONAL DESCRIPTION**

#### **OVERVIEW**

AW96105 is a capacitive touch and proximity controller with built-in a low power MCU. It's based on self-capacitive sensing technology, and mainly includes AFE, MCU, ROM, RAM, OSC, I<sup>2</sup>C, etc.. AFE is mainly used to drive the sensor and shield electrode, and convert the capacitance of sensor to digital data. MCU executes the algorithm program in the ROM, and perform basic operations such as signal filtering, baseline calculation, automatic compensation for environmental drift, radio frequency(RF) noise suppression, proximity judgment, etc..

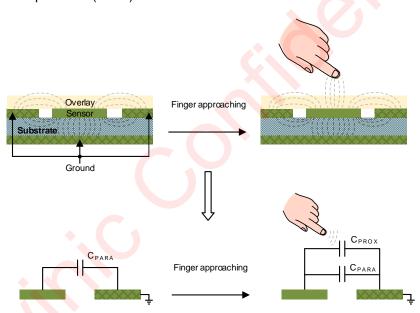

#### CAPACITIVE SENSOR INTRODUCTION

Self-capacitive sensing technology detects the change in the capacitance of a touch or proximity sensor when a target object approaches the sensor. The target object can be a human finger, face, or any conductive object. The figure below shows the basic structure and equivalent model of a capacitance sensor. The top layer is the overlay, and the middle green area below is a copper sensor pad. The sensor is usually surrounded by ground, resulting in a parasitic capacitance (CPARA).

Figure 7 Capacitive sensor structure

An electric field is created around the sensor when it is working. As the target object approaches the electrode, some of the electric field lines couples to the target object and add a small amount of finger capacitance (Cprox) to the existing Cpara. This feature can be used to detect proximity or touch action.

#### CAPACITIVE SENSING TECHNIQUES

The proximity sensing system consists of three parts, capacitive sensor, AFE and DSP. The sensor capacitance will change when the target object is approaching or moving away. AFE drives the capacitive sensors and shield electrodes, and converts the sensor capacitance to digital data. DSP deals with the data from AFE, and passes sensor capacitor value(CapDiff, CapValid) and proximity status(Status) to the host.

Figure 8 Proximity Sensor Operation Overview

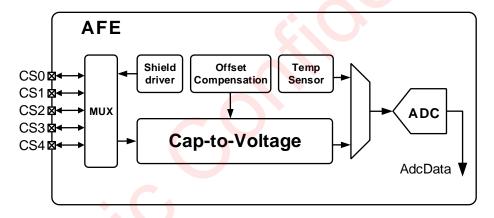

#### AFE DESCRIPTION

Figure 9 AFE Block Diagram

- MUX selects CSx as capacitance measurement input or shield output

- \* If CSx is used as shield electrode, it is excited by shield driver. The driven shield signal is a replica of the sensor signal. Shield electrode around can protect the sensor from noisy environment, and reduce the parasitical capacitance.

- Cap-to-Voltage integrates a charge amplifier, it detects the sensor capacitance with a charge-transfer method. The capacitance is converted into a voltage signal, which is the input of ADC.

- Offset Compensation measures parasitic capacitance(C<sub>PARA</sub>), and C<sub>PARA</sub> is compensated in the

process of charge transferring of Cap-to-Voltage. Thus, the input capacitance of Cap-to-Voltage is

almost only C<sub>PROX</sub>.

- \* Temp Sensor measures the temperature of the chip, and the output is converted by ADC to digital data. The temperature data can be used as reference to correct the capacitance measurement result.

- ADC converts voltage signals obtained by Cap-to-Voltage or Temp Sensor into AdcData.

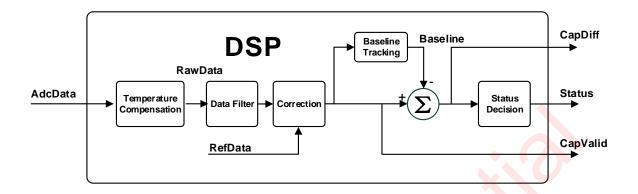

#### DSP DESCRIPTION

Figure 10 Digital signal processing diagram

- \* DSP mainly processes the data from the AFE to judge whether a target object is approaching.

- \*\* Temperature Compensation is mainly used to reduce the effect of temperature drift.

When set AFECFG3\_CHx.TEMPCOMPEN\_CHx = 1 (Addr: 001Ch), the temperature compensation is performed for Channel x (x=0~4). The RawData after compensation can be expressed as follows,

RawData = AdcData\*(1+ TEMPGAIN \*DeltaT) + CAPTEMPCOEF \*TEMPGAIN \*DeltaT

Where, TEMPGAIN is defined in register TEMPCOMP(Addr: 000Ch), DeltaT is the AdcData change corresponding to the temperature change sensing by temperature channel, CAPTEMPCOEF is decided by the register AFECFG3\_CHx.CAPTEMPCOEF\_CHx(Addr: 001Ch). And the temperature channel can be configured as CH0~CH5 through the register TEMPCOMP. TEMPCH.

- \* Data Filter filters the input RawData, and high-frequency noise is filtered out, then the output data shows a higher signal-to-noise ratio(SNR).

- \* In order to further eliminate data fluctuations due to the noise source, the data from Data Filter will be corrected by the RefData. RefData is from reference channel or internal temperature sensor.

- Baseline Tracking provides a baseline that follows undesired variations caused by environmental changes(such as temperature, humidity, etc.)

- X The calculation of data change due to human proximity is

CapDiff = CapValid - Baseline

Status Decision uses CapDiff to decide whether a target object is approaching.

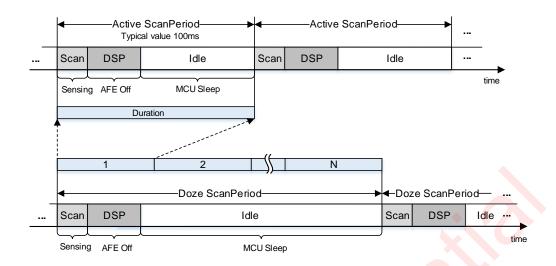

#### SCAN PERIOD

A scan period is divided into 3 segments. In first segment, AFE scan the sensor channels to get the RawData. Then, AFE is off and DSP starts processing the RawData. The chip will be in idle state in the last segment during which MCU sleeps.

The figure above shows the scanning period of active mode and doze mode. The scan period of active mode can be configured by register SCANCTRL1( Address: 0x004H). Scan period of doze mode is N times of active mode. And N can be configured through the register SCANCTRL0(Address: 0x000H). Thus, doze mode consumes much lower power than active mode. Scan period can be configured independently for each channel.

Figure 11 Active mode and Doze mode scan period

## **CLOCK**

OSC is built in the chip, so no external clock is needed. It generates a 4MHz clock to the digital circuit.

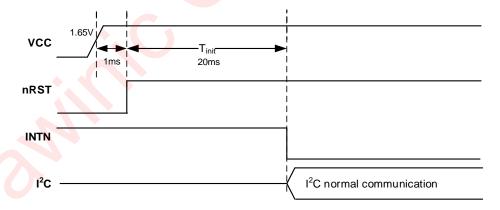

#### RESET

#### **POWER ON RESET (POR)**

Reset operation is triggered during power up. When nRST released, the initialization process starts to perform and it will last for about 20ms. INTN will be set to low when the initialization process is completed, then I<sup>2</sup>C can communicate normally.

**Figure 12 Power On Timing**

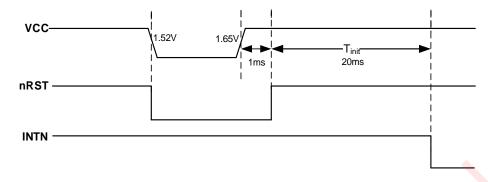

## **BROWN OUT RESET (BOR)**

Reset operation is triggered when VCC drop to the threshold of BOR. After the reset operation, all the registers will be reset to the default value. The chip returns to normal operation mode until the power supply rises to a normal value.

**Figure 13 Brown Out Timing**

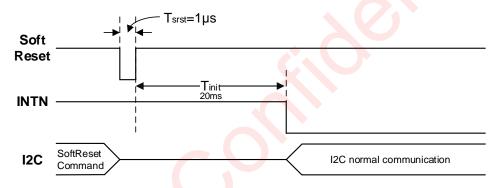

#### SOFT RESET

The soft reset operation can be triggered by writing the soft reset register (Address: 0xFF0F). After the reset operation, all the registers will be reset to the default value.

Figure 14 Soft Reset Timing

#### INITIALIZATION

After power on, OSC runs normally, and MCU starts to execute the initialization program in ROM. It performs the following operations.

- Read information from NVM

- Set I<sup>2</sup>C device address according to CS2 pin status

- Complete high-resolution ADC calibration

- Set interrupt for initialization completion and enter sleep state

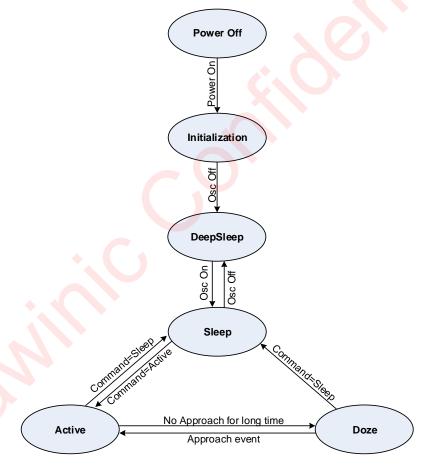

## **OPERATION MODE**

There are four operation modes in the chip: DeepSleep, Sleep, Active and Doze. When a certain condition is met, it will change from one operation mode to another.

#### **DEEPSLEEP**

The device consumes the lowest power. OSC and AFE are off, CPU is sleeping, only I2C interface is active.

#### SLEEP

The device is in a low power state. OSC is on, AFE is off, and MCU is sleeping, waiting for interrupt to wake up.

#### **ACTIVE**

The device works at full speed. All modules including AFE, MCU, OSC, etc., are running normally. When no detection has occurred for some time, it will automatically switch to Doze mode. In this mode the external HOST can send SLEEP command to switch the device to sleep mode.

#### **DOZE**

The scan period is long, MCU and AFE work intermittently. During the large part of period, most modules are in idle state. So the average power consumption is lower.

Once a proximity is detected in doze mode, it will automatically return to active mode. The external HOST can also send SLEEP command to switch the device to sleep mode.

Figure 15 Operation Mode Switching

#### **INTERRUPT**

The chip reports the interrupt signal to the host through the INTN pin. Register HOSTIRQSRC(Address: 0xF080) stores interrupt information, including the completion of parasitic capacitance calibration, scan cycle completion, and so on. Register HOSTIRQSRC is cleared after reading. By configuring HOSTIRQEN(Address: 0xF084), you can mask the specified interrupt signal.

#### I<sup>2</sup>C INTERFACE

AW96105 supports the I²C serial bus and data transmission protocol in fast mode at 400kHz. It operates as a slave on the I²C bus. Connections to the bus are made via the open-drain I/O pins SCL and SDA. The pull-up resistor can be selected in the range of  $1k\sim10k\Omega$  and the typical value is  $4.7k\Omega$ . AW96105 can support different high level ( $1.8V\sim3.3V$ ) of the I²C interface. Additionally, the I²C device supports continuous read and write operations. I²C Register address is 16-bit and register data is 32-bit,transfer of data is big-endian mode.

#### **DEVICE ADDRESS**

## I<sup>2</sup>C device address configuration

| CS2 Connection | Device Address |

|----------------|----------------|

| Floating       | 0x12           |

| GND            | 0x13           |

| VCC            | 0x14           |

The I<sup>2</sup>C device address (7-bit, followed by the R/W bit(Read=1/Write=0)) of AW96105 depends on the CS2 pin status. The default value of I<sup>2</sup>C device address is 0x12, connecting pad CS2 to GND or VCC will change the device address as showed in table above. Note that when pad CS2 is connected to GND or VCC, it can't be used as sensor pad.

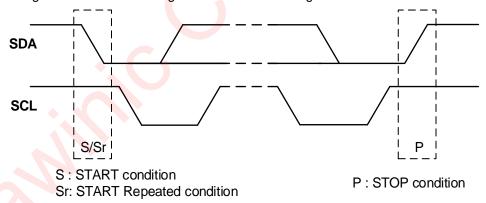

#### PC START/STOP

I<sup>2</sup>C start: SDA changes from high level to low level when SCL is high level. I<sup>2</sup>C stop: SDA changes from low level to high level when SCL is high level.

Figure 16 I<sup>2</sup>C Start/Stop Condition Timing

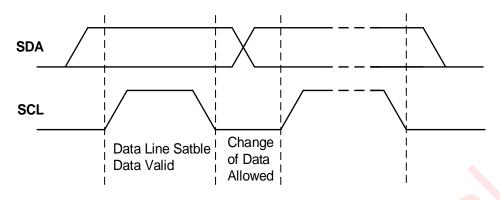

#### DATA VALIDATION

When SCL is high level, SDA level must be constant. SDA can be changed only when SCL is low level.

Figure 17 Data Validation Diagram

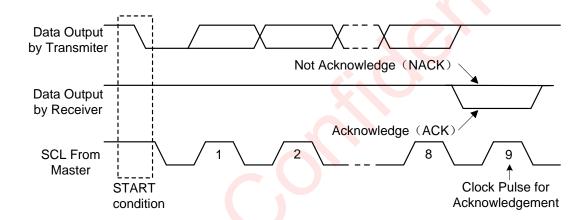

#### ACK (ACKNOWLEDGEMENT)

Figure 18 I<sup>2</sup>C ACK Timing

ACK means the successful transfer of I<sup>2</sup>C bus data. After master sends an 8-bit data, SDA must be released; SDA is pulled down to GND by slave device when slave acknowledges.

When master reads, slave device sends 8-bit data, releases the SDA and waits for ACK from master. If ACK is sent and I<sup>2</sup>C stop is not sent by master, slave device sends the next data. If ACK is not sent by master, slave device stops to send data and waits for I<sup>2</sup>C stop.

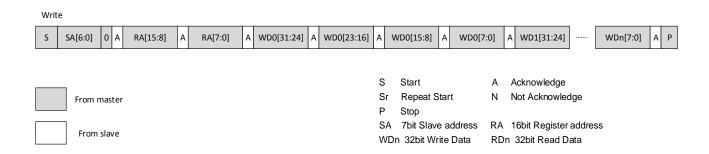

#### WRITE CYCLE

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a start condition, a number of byte transfers (set by the software) and a stop condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

I<sup>2</sup>C Register address is 16-bit and register data is 32-bit. Note that I<sup>2</sup>C also support 8-bit data transfer. Writing process of I<sup>2</sup>C is showed as below picture.

Figure 19 I<sup>2</sup>C Write Byte Cycle

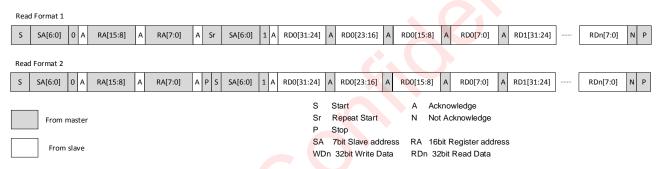

#### **READ CYCLE**

I<sup>2</sup>C supports read operation data format with repeated start conditions, so there are two formats of I<sup>2</sup>C read operations. Read process of I<sup>2</sup>C is showed as below picture.

Figure 20 I<sup>2</sup>C Read Byte Cycle

# **Register List**

| ADDR   | NAME         | R/W | Description                                               | Default    |

|--------|--------------|-----|-----------------------------------------------------------|------------|

| 0x0000 | SCANCTRL0    | RW  | Scan Control Register 0                                   | 0x00000000 |

| 0x0004 | SCANCTRL1    | RW  | Scan Control Register 1                                   | 0x03F00032 |

| 0x000C | TEMPCOMP     | RW  | Temperature Compensation Register                         | 0x05000000 |

| 0x0010 | AFECFG0_CH0  | RW  | AFE Configure Register 0 for CH0                          | 0x00050000 |

| 0x0014 | AFECFG1_CH0  | RW  | AFE Configure Register 1 for CH0                          | 0x00000009 |

| 0x001C | AFECFG3_CH0  | RW  | AFE Configure Register 3 for CH0                          | 0xFF000000 |

| 0x0020 | AFECFG4_CH0  | RW  | AFE Configure Register 4 for CH0                          | 0x00000000 |

| 0x0024 | AFECFG0_CH1  | RW  | AFE Configure Register 0 for CH1                          | 0x00050000 |

| 0x0028 | AFECFG1_CH1  | RW  | AFE Configure Register 1 for CH1                          | 0x00000009 |

| 0x0030 | AFECFG3_CH1  | RW  | AFE Configure Register 3 for CH1                          | 0xFF000000 |

| 0x0034 | AFECFG4_CH1  | RW  | AFE Configure Register 4 for CH1                          | 0x00000000 |

| 0x0038 | AFECFG0_CH2  | RW  | AFE Configure Register 0 for CH2                          | 0x00050000 |

| 0x003C | AFECFG1_CH2  | RW  | AFE Configure Register 1 for CH2                          | 0x00000009 |

| 0x0044 | AFECFG3_CH2  | RW  | AFE Configure Register 3 for CH2                          | 0xFF000000 |

| 0x0048 | AFECFG4_CH2  | RW  | AFE Configure Register 4 for CH2                          | 0x00000000 |

| 0x004C | AFECFG0_CH3  | RW  | AFE Configure Register 0 for CH3                          | 0x00050000 |

| 0x0050 | AFECFG1_CH3  | RW  | AFE Configure Register 1 for CH3                          | 0x00000009 |

| 0x0058 | AFECFG3_CH3  | RW  | AFE Configure Register 3 for CH3                          | 0xFF000000 |

| 0x005C | AFECFG4_CH3  | RW  | AFE Configure Register 4 for CH3                          | 0x00000000 |

| 0x0060 | AFECFG0_CH4  | RW  | AFE Configure Register 0 for CH4                          | 0x00050000 |

| 0x0064 | AFECFG1_CH4  | RW  | AFE Configure Register 1 for CH4                          | 0x00000009 |

| 0x006C | AFECFG3_CH4  | RW  | AFE Configure Register 3 for CH4                          | 0xFF000000 |

| 0x0070 | AFECFG4_CH4  | RW  | AFE Configure Register 4 for CH4                          | 0x00000000 |

| 0x0074 | AFECFG0_CH5  | RW  | AFE Configure Register 0 for CH5                          | 0x00050000 |

| 0x0078 | AFECFG1_CH5  | RW  | AFE Configure Register 1 for CH5                          | 0x00000009 |

| 0x0080 | AFECFG3_CH5  | RW  | AFE Configure Register 3 for CH5                          | 0xFF000000 |

| 0x0084 | AFECFG4_CH5  | RW  | AFE Configure Register 4 for CH5                          | 0x00000000 |

| 0x0088 | FWVER        | RO  | Firmware Version Register                                 | 0x02001000 |

| 0x008C | PST          | RO  | Program Status Register                                   | 0x00000003 |

| 0x0090 | STAT0        | RO  | Status Register 0                                         | 0x00000000 |

| 0x0094 | STAT1        | RO  | Status Register 1                                         | 0x00000000 |

| 0x0098 | STAT2        | RO  | Status Register 2                                         | 0x00000000 |

| 0x009C | PROXINTEN    | RW  | Proximity Interrupt Enable Register                       | 0x3F3F3F3F |

| 0x00A0 | FILTREF0_CH0 | RW  | Filter and Reference Channel Configure Register 0 for CH0 | 0xE0400000 |

| 0x00A4 | FILTREF1_CH0 | RW  | Filter and Reference Channel Configure Register 1 for CH0 | 0x00000000 |

| 0x00A8 | BLFILT1_CH0  | RW  | Baseline Filter 1 Configure Register for CH0              | 0x000008D2 |

| 0x00B0 | PROXCTRL_CH0 | RW  | Proximity Control Register for CH0                        | 0x00000000 |

| 0x00B8 | PROXTH0_CH0  | RW  | Proximity Threshold 0 Control Register for CH0            | 0x00000000 |

| 0x00BC | PROXTH1_CH0  | RW  | Proximity Threshold 1 Control Register for CH0            | 0x00000000 |

| ADDR   | NAME            | R/W | Description                                                | Default    |

|--------|-----------------|-----|------------------------------------------------------------|------------|

| 0x00C0 | PROXTH2_CH0     | RW  | Proximity Threshold 2 Control Register for CH0             | 0x00000000 |

| 0x00C4 | PROXTH3_CH0     | RW  | Proximity Threshold 3 Control Register for CH0             | 0x00000000 |

| 0x00C8 | STDDET_CH0      | RW  | Steady Detection Configure Register for CH0                | 0x00000000 |

| 0x00CC | INITPROX0_CH0   | RW  | Start-up Proximity Detection Register 0 for CH0            | 0x00000000 |

| 0x00D0 | INITPROX1_CH0   | RW  | Start-up Proximity Detection Register 1 for CH0            | 0x00000000 |

| 0x00D4 | DATAOFFSET_CH0  | RW  | Data Offset Control Register for CH0                       | 0x00000000 |

| 0x00D8 | CORRTARDATA_CH0 | RW  | Target Data Setting for Offset Compensation for CH0        | 0x00000000 |

| 0x00DC | FILTREF0_CH1    | RW  | Filter and Reference Channel Configure Register 0 for CH1  | 0xE0400000 |

| 0x00E0 | FILTREF1_CH1    | RW  | Filter and Reference Channel Configure Register 1 for CH1  | 0x00000000 |

| 0x00E4 | BLFILT1_CH1     | RW  | Baseline Filter 1 Configure Register for CH1               | 0x000008D2 |

| 0x00EC | PROXCTRL_CH1    | RW  | Proximity Control Register for CH1                         | 0x00000000 |

| 0x00F4 | PROXTH0_CH1     | RW  | Proximity Threshold 0 Control Register for CH1             | 0x00000000 |

| 0x00F8 | PROXTH1_CH1     | RW  | Proximity Threshold 1 Control Register for CH1             | 0x00000000 |

| 0x00FC | PROXTH2_CH1     | RW  | Proximity Threshold 2 Control Register for CH1             | 0x00000000 |

| 0x0100 | PROXTH3_CH1     | RW  | Proximity Threshold 3 Control Register for CH1             | 0x00000000 |

| 0x0104 | STDDET_CH1      | RW  | Stea <mark>dy Det</mark> ection Configure Register for CH1 | 0x00000000 |

| 0x0108 | INITPROX0_CH1   | RW  | Start-up Proximity Detection Register 0 for CH1            | 0x00000000 |

| 0x010C | INITPROX1_CH1   | RW  | Start-up Proximity Detection Register 1 for CH1            | 0x00000000 |

| 0x0110 | DATAOFFSET_CH1  | RW  | Data Offset Control Register for CH1                       | 0x00000000 |

| 0x0114 | CORRTARDATA_CH1 | RW  | Target Data Setting for Offset Compensation for CH1        | 0x00000000 |

| 0x0118 | FILTREF0_CH2    | RW  | Filter and Reference Channel Configure Register 0 for CH2  | 0xE0400000 |

| 0x011C | FILTREF1_CH2    | RW  | Filter and Reference Channel Configure Register 1 for CH2  | 0x00000000 |

| 0x0120 | BLFILT1_CH2     | RW  | Baseline Filter 1 Configure Register for CH2               | 0x000008D2 |

| 0x0128 | PROXCTRL_CH2    | RW  | Proximity Control Register for CH2                         | 0x00000000 |

| 0x0130 | PROXTH0_CH2     | RW  | Proximity Threshold 0 Control Register for CH2             | 0x00000000 |

| 0x0134 | PROXTH1_CH2     | RW  | Proximity Threshold 1 Control Register for CH2             | 0x00000000 |

| 0x0138 | PROXTH2_CH2     | RW  | Proximity Threshold 2 Control Register for CH2             | 0x00000000 |

| 0x013C | PROXTH3_CH2     | RW  | Proximity Threshold 3 Control Register for CH2             | 0x00000000 |

| 0x0140 | STDDET_CH2      | RW  | Steady Detection Configure Register for CH2                | 0x00000000 |

| 0x0144 | INITPROX0_CH2   | RW  | Start-up Proximity Detection Register 0 for CH2            | 0x00000000 |

| 0x0148 | INITPROX1_CH2   | RW  | Start-up Proximity Detection Register 1 for CH2            | 0x00000000 |

| 0x014C | DATAOFFSET_CH2  | RW  | Data Offset Control Register for CH2                       | 0x00000000 |

| ADDR   | NAME            | R/W | Description                                                       | Default    |

|--------|-----------------|-----|-------------------------------------------------------------------|------------|

| 0x0150 | CORRTARDATA_CH2 | RW  | Target Data Setting for Offset Compensation                       | 0x00000000 |

| 0x0154 | FILTREF0_CH3    | RW  | for CH2 Filter and Reference Channel Configure Register 0 for CH3 | 0xE0400000 |

| 0x0158 | FILTREF1_CH3    | RW  | Filter and Reference Channel Configure Register 1 for CH3         | 0x00000000 |

| 0x015C | BLFILT1_CH3     | RW  | Baseline Filter 1 Configure Register for CH3                      | 0x000008D2 |

| 0x0164 | PROXCTRL_CH3    | RW  | Proximity Control Register for CH3                                | 0x00000000 |

| 0x016C | PROXTH0_CH3     | RW  | Proximity Threshold 0 Control Register for CH3                    | 0x00000000 |

| 0x0170 | PROXTH1_CH3     | RW  | Proximity Threshold 1 Control Register for CH3                    | 0x00000000 |

| 0x0174 | PROXTH2_CH3     | RW  | Proximity Threshold 2 Control Register for CH3                    | 0x00000000 |

| 0x0178 | PROXTH3_CH3     | RW  | Proximity Threshold 3 Control Register for CH3                    | 0x00000000 |

| 0x017C | STDDET_CH3      | RW  | Steady Detection Configure Register for CH3                       | 0x00000000 |

| 0x0180 | INITPROX0_CH3   | RW  | Start-up Proximity Detection Register 0 for CH3                   | 0x00000000 |

| 0x0184 | INITPROX1_CH3   | RW  | Start-up Proximity Detection Register 1 for CH3                   | 0x00000000 |

| 0x0188 | DATAOFFSET_CH3  | RW  | Data Offset Control Register for CH3                              | 0x00000000 |

| 0x018C | CORRTARDATA_CH3 | RW  | Target Data Setting for Offset Compensation for CH3               | 0x00000000 |

| 0x0190 | FILTREF0_CH4    | RW  | Filter and Reference Channel Configure Register 0 for CH4         | 0xE0400000 |

| 0x0194 | FILTREF1_CH4    | RW  | Filter and Reference Channel Configure Register 1 for CH4         | 0x00000000 |

| 0x0198 | BLFILT1_CH4     | RW  | Baseline Filter 1 Configure Register for CH4                      | 0x000008D2 |

| 0x01A0 | PROXCTRL_CH4    | RW  | Proximity Control Register for CH4                                | 0x00000000 |

| 0x01A8 | PROXTH0_CH4     | RW  | Proximity Threshold 0 Control Register for CH4                    | 0x00000000 |

| 0x01AC | PROXTH1_CH4     | RW  | Proximity Threshold 1 Control Register for CH4                    | 0x00000000 |

| 0x01B0 | PROXTH2_CH4     | RW  | Proximity Threshold 2 Control Register for CH4                    | 0x00000000 |

| 0x01B4 | PROXTH3_CH4     | RW  | Proximity Threshold 3 Control Register for CH4                    | 0x00000000 |

| 0x01B8 | STDDET_CH4      | RW  | Steady Detection Configure Register for CH4                       | 0x00000000 |

| 0x01BC | INITPROX0_CH4   | RW  | Start-up Proximity Detection Register 0 for CH4                   | 0x00000000 |

| 0x01C0 | INITPROX1_CH4   | RW  | Start-up Proximity Detection Register 1 for CH4                   | 0x00000000 |

| 0x01C4 | DATAOFFSET_CH4  | RW  | Data Offset Control Register for CH4                              | 0x00000000 |

| 0x01C8 | CORRTARDATA_CH4 | RW  | Target Data Setting for Offset Compensation for CH4               | 0x00000000 |

| 0x01CC | FILTREF0_CH5    | RW  | Filter and Reference Channel Configure Register 0 for CH5         | 0xE0400000 |

| 0x01D0 | FILTREF1_CH5    | RW  | Filter and Reference Channel Configure Register 1 for CH5         | 0x00000000 |

| 0x01D4 | BLFILT1_CH5     | RW  | Baseline Filter 1 Configure Register for CH5                      | 0x000008D2 |

| 0x01DC | PROXCTRL_CH5    | RW  | Proximity Control Register for CH5                                | 0x00000000 |

| 0x01E4 | PROXTH0_CH5     | RW  | Proximity Threshold 0 Control Register for CH5                    | 0x00000000 |

| ADDR   | NAME            | R/W | Description                                         | Default    |

|--------|-----------------|-----|-----------------------------------------------------|------------|

| 0x01E8 | PROXTH1_CH5     | RW  | Proximity Threshold 1 Control Register for          | 0x00000000 |

| 0.0120 | _               |     | CH5 Proximity Threshold 2 Control Register for      | скоооооо   |

| 0x01EC | PROXTH2_CH5     | RW  | CH5                                                 | 0x00000000 |

| 0x01F0 | PROXTH3_CH5     | RW  | Proximity Threshold 3 Control Register for CH5      | 0x0000000  |

| 0x01F4 | STDDET_CH5      | RW  | Steady Detection Configure Register for CH5         | 0x00000000 |

| 0x01F8 | INITPROX0_CH5   | RW  | Start-up Proximity Detection Register 0 for CH5     | 0x00000000 |

| 0x01FC | INITPROX1_CH5   | RW  | Start-up Proximity Detection Register 1 for CH5     | 0x00000000 |

| 0x0200 | DATAOFFSET_CH5  | RW  | Data Offset Control Register for CH5 🔷 🌖            | 0x00000000 |

| 0x0204 | CORRTARDATA_CH5 | RW  | Target Data Setting for Offset Compensation for CH5 | 0x00000000 |

| 0x0208 | REF1CFG         | RW  | Reference 1 Configure Register                      | 0x00000005 |

| 0x020C | REF2CFG         | RW  | Reference 2 Configure Register                      | 0x00000005 |

| 0x0210 | VALID_CH0       | RO  | Valid Data Register of CH0                          | 0x00000000 |

| 0x0214 | VALID_CH1       | RO  | Valid Data Register of CH1                          | 0x00000000 |

| 0x0218 | VALID_CH2       | RO  | Valid Data Register of CH2                          | 0x00000000 |

| 0x021C | VALID_CH3       | RO  | Valid Data Register of CH3                          | 0x00000000 |

| 0x0220 | VALID_CH4       | RO  | Valid Data Register of CH4                          | 0x00000000 |

| 0x0224 | VALID_CH5       | RO  | Valid Data Register of CH5                          | 0x00000000 |

| 0x0228 | BASELINE_CH0    | RO  | Baseline Data Register of CH0                       | 0x00000000 |

| 0x022C | BASELINE_CH1    | RO  | Baseline Data Register of CH1                       | 0x00000000 |

| 0x0230 | BASELINE_CH2    | RO  | Baseline Data Register of CH2                       | 0x00000000 |

| 0x0234 | BASELINE_CH3    | RO  | Baseline Data Register of CH3                       | 0x00000000 |

| 0x0238 | BASELINE_CH4    | RO  | Baseline Data Register of CH4                       | 0x00000000 |

| 0x023C | BASELINE_CH5    | RO  | Baseline Data Register of CH5                       | 0x00000000 |

| 0x0240 | DIFF_CH0        | RO  | Difference Value Register of CH0                    | 0x00000000 |

| 0x0244 | DIFF CH1        | RO  | Difference Value Register of CH1                    | 0x00000000 |

| 0x0248 | DIFF_CH2        | RO  | Difference Value Register of CH2                    | 0x00000000 |

| 0x024C | DIFF_CH3        | RO  | Difference Value Register of CH3                    | 0x00000000 |

| 0x0250 | DIFF_CH4        | RO  | Difference Value Register of CH4                    | 0x00000000 |

| 0x0254 | DIFF_CH5        | RO  | Difference Value Register of CH5                    | 0x00000000 |

| 0x0258 | ADCMIN_CH0      | RO  | ADC Min Data Register of CH0                        | 0x00000000 |

| 0x025C | ADCMIN_CH1      | RO  | ADC Min Data Register of CH1                        | 0x00000000 |

| 0x0260 | ADCMIN_CH2      | RO  | ADC Min Data Register of CH2                        | 0x00000000 |

| 0x0264 | ADCMIN_CH3      | RO  | ADC Min Data Register of CH3                        | 0x00000000 |

| 0x0268 | ADCMIN_CH4      | RO  | ADC Min Data Register of CH4                        | 0x00000000 |

| 0x026C | ADCMIN_CH5      | RO  | ADC Min Data Register of CH5                        | 0x00000000 |

| 0x0270 | ADCMAX_CH0      | RO  | ADC Max Data Register of CH0                        | 0x00000000 |

| 0x0274 | ADCMAX_CH1      | RO  | ADC Max Data Register of CH1                        | 0x00000000 |

| 0x0274 | ADCMAX_CH2      | RO  | ADC Max Data Register of CH2                        | 0x00000000 |

| 0x027C | ADCMAX_CH3      | RO  | ADC Max Data Register of CH3                        | 0x00000000 |

| 0x027C | ADCMAX_CH4      | RO  | ADC Max Data Register of CH4                        | 0x00000000 |

| 0x0284 | ADCMAX_CH5      | RO  | ADC Max Data Register of CH5                        | 0x00000000 |

| 0x0284 | ADCAVG_CH0      | RO  | ADC Average Data Register of CH0                    | 0x00000000 |

| 0.0200 | ADOAVG_ON       |     | ADO Average Data Negister of Orio                   | 0,00000000 |

| ADDR   | NAME         | R/W | Description                                | Default    |

|--------|--------------|-----|--------------------------------------------|------------|

| 0x028C | ADCAVG_CH1   | RO  | ADC Average Data Register of CH1           | 0x00000000 |

| 0x0290 | ADCAVG_CH2   | RO  | ADC Average Data Register of CH2           | 0x00000000 |

| 0x0294 | ADCAVG_CH3   | RO  | ADC Average Data Register of CH3           | 0x00000000 |

| 0x0298 | ADCAVG_CH4   | RO  | ADC Average Data Register of CH4           | 0x00000000 |

| 0x029C | ADCAVG_CH5   | RO  | ADC Average Data of CH5                    | 0x00000000 |

| 0x02A0 | STDMIN_CH0   | RO  | Steady Min Data Register of CH0            | 0x00000000 |

| 0x02A4 | STDMIN_CH1   | RO  | Steady Min Data Register of CH1            | 0x00000000 |

| 0x02A8 | STDMIN_CH2   | RO  | Steady Min Data Register of CH2            | 0x00000000 |

| 0x02AC | STDMIN_CH3   | RO  | Steady Min Data Register of CH3            | 0x00000000 |

| 0x02B0 | STDMIN_CH4   | RO  | Steady Min Data Register of CH4            | 0x00000000 |

| 0x02B4 | STDMIN_CH5   | RO  | Steady Min Data Register of CH5            | 0x00000000 |

| 0x02B8 | STDMAX_CH0   | RO  | Steady Max Data Register of CH0            | 0x00000000 |

| 0x02BC | STDMAX_CH1   | RO  | Steady Max Data Register of CH1            | 0x00000000 |

| 0x02C0 | STDMAX_CH2   | RO  | Steady Max Data Register of CH2            | 0x00000000 |

| 0x02C4 | STDMAX_CH3   | RO  | Steady Max Data Register of CH3            | 0x00000000 |

| 0x02C8 | STDMAX_CH4   | RO  | Steady Max Data Register of CH4            | 0x00000000 |

| 0x02CC | STDMAX_CH5   | RO  | Steady Max Data Register of CH5            | 0x00000000 |

| 0x02D0 | RAW_CH0      | RO  | Raw Data Register of CH0                   | 0x00000000 |

| 0x02D4 | RAW_CH1      | RO  | Raw Data Register of CH1                   | 0x00000000 |

| 0x02D8 | RAW_CH2      | RO  | Raw Data Register of CH2                   | 0x00000000 |

| 0x02DC | RAW_CH3      | RO  | Raw Data Register of CH3                   | 0x00000000 |

| 0x02E0 | RAW_CH4      | RO  | Raw Data Register of CH4                   | 0x00000000 |

| 0x02E4 | RAW_CH5      | RO  | Raw Data Register of CH5                   | 0x00000000 |

| 0x02E8 | LPF_CH0      | RO  | LPF Data Register of CH0                   | 0x00000000 |

| 0x02EC | LPF_CH1      | RO  | LPF Data Register of CH1                   | 0x00000000 |

| 0x02F0 | LPF_CH2      | RO  | LPF Data Register of CH2                   | 0x00000000 |

| 0x02F4 | LPF_CH3      | RO  | LPF Data Register of CH3                   | 0x00000000 |

| 0x02F8 | LPF_CH4      | RO  | LPF Data Register of CH4                   | 0x00000000 |

| 0x02FC | LPF_CH5      | RO  | LPF Data Register of CH5                   | 0x00000000 |

| 0xF008 | CMD          | WO  | Command Register                           | 0x00000000 |

| 0xF080 | HOSTIRQSRC   | RC  | IC To Host Interrupt Source Register       | 0x00000000 |

| 0xF084 | HOSTIRQEN    | RW  | CPU to Host Interrupt Enable Register      | 0x00000FFF |

| 0xF0F0 | I2CADDR      | RO  | I2C Device Address Register                | 0x00000012 |

| 0xFF00 | HOSTCTRL     | R/W | Host Control Register                      | 0x00000101 |

| 0xFF0C | HOSTCTRL2    | R/W | Host Control Register 2                    | 0x01000000 |

| 0xFF10 | CHIP_ID      | RO  | CHIP ID Register                           | 0xA9610B00 |

| 0xFFF4 | ACESS_APB_EN | RO  | Host Access APB Peripheral Enable Register | 0x0000E39F |

# **Register Detailed Description**

| SCANCTRL0: Scan Control Register 0 (Address 0000h) |          |     |             |         |  |  |  |  |

|----------------------------------------------------|----------|-----|-------------|---------|--|--|--|--|

| Bit                                                | Symbol   | R/W | Description | Default |  |  |  |  |

| 31:20                                              | Reserved | RO  | Reserved    | b00     |  |  |  |  |

| 19    | WDTEN      | RW | Watchdog timer enable. b0: Disable b1: Enable. When the watchdog overflows, the whole chip except IIC will be reset automatically.                                                                                  | b0      |

|-------|------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 18:16 | DOZEFACTOR | RW | Scan period in doze mode. $T_{scan}$ (doze) = 2^DOZEFACTOR x $T_{scan}$ (active) Where $T_{scan}$ (active) is scan period in active mode defined by register SCANCTRL1 (Address 0004h).                             | b000    |

| 15:14 | Reserved   | RO | Reserved                                                                                                                                                                                                            | b00     |

| 13:8  | COMPEN     | WC | Defines which channels need auto offset tuning (AOT). And after the offset compensation, the corresponding bit will be cleared to "0". b0: Doesn't need AOT b1: Need AOT Bit[13:8] = [CH5, CH4, CH3, CH2, CH1, CH0] | b000000 |

| 7:6   | Reserved   | RO | Reserved                                                                                                                                                                                                            | b00     |

| 5:0   | CHEN       | RW | Enable the measurement channel.<br>b0: Disable<br>b1: Enable<br>Bit[5:0] = [CH5, CH4, CH3, CH2, CH1, CH0]                                                                                                           | b000000 |

| SCANCTRL1: Scan Control Register 1 (Address 0004h) |            |     |                                                                                                                                                                                                                                        |         |

|----------------------------------------------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Bit                                                | Symbol     | R/W | Description                                                                                                                                                                                                                            | Default |

| 31:26                                              | Reserved   | RO  | Reserved                                                                                                                                                                                                                               | b000000 |

| 25:20                                              | DOZEEN     | RO  | Doze mode enable.  0: Disable  1: Enable  Bit[5:0] = [CH5, CH4, CH3, CH2, CH1, CH0]                                                                                                                                                    | h3F     |

| 19:16                                              | Reserved   | RO  | Reserved                                                                                                                                                                                                                               | b0000   |

| 15:11                                              | DOZEDEB    | RW  | Debounce times setting for entering into doze mode. b00000: Never enter into doze mode Others: In active mode, it none proximity has been detected continuously for 4×DOZEDEB times, the chip will enter into doze mode automatically. | p00000  |

| 10:0                                               | SCANPERIOD | RW  | Setting basic scan period for active mode: h000: Reserved other: T <sub>scan</sub> (active) = SCANPERIOD * 2 ms                                                                                                                        | h032    |

| TEMPC | TEMPCOMP: Temperature Compensation Register (Address 000Ch) |     |                                                                                                                   |         |

|-------|-------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------|---------|

| Bit   | Symbol                                                      | R/W | Description                                                                                                       | Default |

| 31:27 | Reserved                                                    | RO  | Reserved                                                                                                          | b00000  |

| 26:24 | TEMPCH                                                      | RW  | Temperature sensor channel selection. b000: CH0 b001: CH1 b010: CH2 b011: CH3 b100: CH4 b101: CH5 other: Reserved | b101    |

| 23:22 | Reserved                                                    | RO  | Reserved                                                                                                          | b00     |

| 21:0 | TEMPGAIN | RW | Temperature gain coefficient.  TEMPGAIN = S.21 format.  RawData=AdcData*(1+ TEMPGAIN *DeltaT) + CAPTEMPCOEF_CHx *TEMPGAIN *DeltaT Where, CAPTEMPCOEF_CHx is defined in register AFECFG3_CHx(Addr: 001Ch), DeltaT is the data corresponding to the temperature change from temperature sensor. | h000000 |

|------|----------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|------|----------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

AFECFG0\_CH0: AFE Configure Register 0 for CH0 (Address 0010h)

AFECFG0\_CH1: AFE Configure Register 0 for CH1 (Address 0024h)

AFECFG0\_CH2: AFE Configure Register 0 for CH2 (Address 0038h)

AFECFG0\_CH3: AFE Configure Register 0 for CH3 (Address 004Ch)

AFECFG0\_CH4: AFE Configure Register 0 for CH4 (Address 0060h)

AFECFG0\_CH5: AFE Configure Register 0 for CH5 (Address 0074h)

| Bit   | Symbol      | R/W | Description                                                                                                                                                                                                                    | Default |

|-------|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31:30 | MEASMOD_CHx | RW  | Measurement mode selection of CHx (x = 0, 1,, 5). b00: Capacitance b10: Temperature other: Reserved                                                                                                                            | р00     |

| 29:26 | RDRV_CHx    | RW  | Driving resistance setting of sensing electrode for CHx.  Resistance = $2k\Omega * RDRV_CHx$                                                                                                                                   | b0000   |

| 25:23 | RSHLD_CHx   | RW  | Driving resistance setting of shield electrode for CHx. Resistance = 8kΩ * RSHLD_CHx                                                                                                                                           | p000    |

| 22:20 | ROFF_CHx    | RW  | Driving resistance setting of offset capacitance for CHx. b000: 125 $\Omega$ b001: 250 $\Omega$ b010: 500 $\Omega$ b011: 1 k $\Omega$ b100: 2 k $\Omega$ b101: 4 k $\Omega$ b110: 6 k $\Omega$ b111: 8 k $\Omega$              | p000    |

| 19:16 | CDCRES_CHx  | RW  | Capacitance-digital-conversion resolution setting for CHx.  Resolution = 15bit + CDCRES_CHx  Higher resolution achieves higher SNR, but takes longer measurement time.                                                         | b0101   |

| 15:12 | CRANGE_CHx  | RW  | Capacitance measurement range of CHx. b0000: 1.1 pF b0001: 2.2 pF b0010: 3.3 pF b0011: 4.4 pF b0100: 6.6 pF b0101: 7.7 pF b0110: 8.8 pF b0111: 9.9 pF b1000: 11 pF b1001: 12.1 pF b1010: 13.2 pF b1011: 14.3 pF b1100: 16.5 pF | b0000   |

|       |            |    | b1101: 17.6 pF<br>b1110: 18.7 pF<br>b1111: 19.8 pF                               |     |

|-------|------------|----|----------------------------------------------------------------------------------|-----|

| 11:10 | Reserved   | RO | Reserved                                                                         | h00 |

| 9:8   | CS4SEL_CHx | RW | CS4 connection setting for CHx. b00: HZ b01: Measured input b10: Shield b11: GND | b00 |

| 7:6   | CS3SEL_CHx | RW | Same as CS4SEL_CHx for pad CS1.                                                  | b00 |

| 5:4   | CS2SEL_CHx | RW | Same as CS4SEL_CHx for pad CS1.                                                  | b00 |

| 3:2   | CS1SEL_CHx | RW | Same as CS4SEL_CHx for pad CS1.                                                  | b00 |

| 1:0   | CS0SEL_CHx | RW | Same as CS4SEL_CHx for pad CS0.                                                  | b00 |

| AFECFG1_CH0: AFE Configure Register 1 for CH0 (Addre | ss 0014h)  |

|------------------------------------------------------|------------|

| AFECFG1_CH1: AFE Configure Register 1 for CH1 (Addre | ess 0028h) |

| AFECFG1_CH2: AFE Configure Register 1 for CH2 (Addre | ess 003Ch) |

| AFECFG1_CH3: AFE Configure Register 1 for CH3 (Addre | ess 0050h) |

| AFECFG1_CH4: AFE Configure Register 1 for CH4 (Addre | ess 0064h) |

| AFECEG1 CH5: AFE Configure Register 1 for CH5 (Addre | ess 0078h) |

| Bit   | Symbol   | R/W | Description                                                                                                                           | Default |

|-------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31:16 | COFF_CHx | RW  | Current offset capacitance setting for CHx ( $x = 0$ , 1,, 5).                                                                        | h0000   |

| 15:8  | Reserved | RO  | Reserved                                                                                                                              | b0      |

| 7:0   | FREQ_CHx | RW  | Frequency setting for Cx drive signal of CHx.  F <sub>smpl</sub> = F <sub>afe</sub> /(2*FREQ_CHx+2)/2  Where F <sub>afe</sub> = 4MHz. | h09     |

|       |          |     |                                                                                                                                       |         |

| Dit Cumbal                 | D AM     | Decembetion                         | Defecult |

|----------------------------|----------|-------------------------------------|----------|

| AFECFG3_CH5: AFE Configure | Register | 3 for CH5 (Address 0080h, not open) |          |

|                            |          | 3 for CH4 (Address 006Ch, not open) |          |

| _                          |          | 3 for CH3 (Address 0058h, not open) |          |

|                            |          | 3 for CH2 (Address 0044h, not open) |          |

| AFECFG3_CH1: AFE Configure | Register | 3 for CH1 (Address 0030h, not open) |          |

| AFECFG3_CH0: AFE Configure | Register | 3 for CH0 (Address 001Ch, not open) |          |

|                            |          |                                     |          |

| Bit   | Symbol              | R/W | Description                                                                                                                                                                                                                                                                            | Default |

|-------|---------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31:24 | Reserved            | RO  | Reserved                                                                                                                                                                                                                                                                               | h00     |

| 23:16 | SCANMULTACT_CH      | RW  | Scan period in active mode for CHx. 0: 1x T <sub>scan</sub> (active) Else: SCANMULTACT x T <sub>scan</sub> (active)                                                                                                                                                                    | h00     |

| 15    | TEMPCOMPEN_CH       | RW  | Temperature compensation enable. 0: Disable 1: Enable                                                                                                                                                                                                                                  | b0      |

| 14:0  | CAPTEMPCOEF_C<br>Hx | RW  | Linear coefficient for temperature compensation. RawData(temp comp)=AdcData(1+ TEMPGAIN *DeltaT) + CAPTEMPCOEF_CHx *TEMPGAIN *DeltaT Where, TEMPGAIN is defined in register TEMPGAIN(Addr: 000Ch), DeltaT is the data corresponding to the temperature change from temperature sensor. | h0000   |

| AFECFG4_CH0: AFE Configure Register 4 for CH0 (Address 0020h) |

|---------------------------------------------------------------|

| AFECFG4_CH1: AFE Configure Register 4 for CH1 (Address 0034h) |

| AFECFG4_CH2: AFE Configure Register 4 for CH2 (Address 0048h) |

| AFECFG4 CH3: AFE Configure Register 4 for CH3 (Address 005Ch) |

|       | AFECFG4_CH4: AFE Configure Register 4 for CH4 (Address 0070h) AFECFG4_CH5: AFE Configure Register 4 for CH5 (Address 0084h) |         |                                    |         |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------|---------|--|--|

| AFECE | 34_CH3. AFE Configure                                                                                                       | Negisie | ,                                  |         |  |  |

|       |                                                                                                                             |         | Scan period in dozen mode for CHx. |         |  |  |

| 31:25 | SCANMULTDOZE                                                                                                                | RW      | 0: 1x Tscan(doze)                  | h00     |  |  |

|       |                                                                                                                             |         | Else: SCANMULTACT x Tscan(doze)    |         |  |  |

| 24:0  | Reserved                                                                                                                    | RO      | Reserved                           | h000000 |  |  |

| FWVER: Firmware Version Register (Address 0088h) |       |    |                           |           |  |  |

|--------------------------------------------------|-------|----|---------------------------|-----------|--|--|

| Bit Symbol R/W Description D                     |       |    |                           |           |  |  |

| 31:0                                             | FWVER | RO | The firmware Information. | h02000C00 |  |  |

| PST: Program Status Register (Address 008Ch) |          |     |                                                                           |         |

|----------------------------------------------|----------|-----|---------------------------------------------------------------------------|---------|

| Bit                                          | Symbol   | R/W | Description                                                               | Default |

| 31:24                                        | SCANST   | RO  | Current work mode status. h00: Active mode h01: Doze mode Other: Reserved | h00     |

| 23:0                                         | Reserved | RO  | Reserved                                                                  | h000000 |

| STAT0: Status Register 0 (Address 0090h) |          |     |                                                                                                                      |         |

|------------------------------------------|----------|-----|----------------------------------------------------------------------------------------------------------------------|---------|

| Bit                                      | Symbol   | R/W | Description                                                                                                          | Default |

| 31:30                                    | Reserved | RO  | Reserved                                                                                                             | b00     |

| 29:24                                    | PROX0ST  | RO  | Level0 proximity status indication (decision with proximity threshold 0).  Bit[29:24]=[CH5, CH4, CH3, CH2, CH1, CH0] | b000000 |

| 23:22                                    | Reserved | RO  | Reserved                                                                                                             | b00     |

| 21:16                                    | PROX1ST  | RO  | Level1 proximity status indication (decision with proximity threshold 1).  Bit[21:16]=[CH5, CH4, CH3, CH2, CH1, CH0] | b000000 |

| 15:14                                    | Reserved | RO  | Reserved                                                                                                             | b00     |

| 13:8                                     | PROX2ST  | RO  | Level2 proximity status indication (decision with proximity threshold 2). Bit[13:8]=[CH5, CH4, CH3, CH2, CH1, CH0]   | b000000 |

| 7:6                                      | Reserved | RO  | Reserved                                                                                                             | b00     |

| 5:0                                      | PROX3ST  | RO  | Level3 proximity status indication (decision with proximity threshold 3).  Bit[5:0]=[CH5, CH4, CH3, CH2, CH1, CH0]   | b000000 |

| STAT1: | STAT1: Status Register 1 (Address 0094h) |     |                                                                                                                                                                       |         |  |

|--------|------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit    | Symbol                                   | R/W | Description                                                                                                                                                           | Default |  |

| 31:30  | Reserved                                 | RO  | Reserved                                                                                                                                                              | b00     |  |

| 29:24  | STDST                                    | RO  | Steady status indication. Bit[29:24]=[CH5, CH4, CH3, CH2, CH1, CH0]                                                                                                   | b000000 |  |

| 23:22  | Reserved                                 | RO  | Reserved                                                                                                                                                              | b00     |  |

| 21:16  | COFFERRST                                | RO  | Offset capacitance error status, indicating whether offset capacitance is out of the range defined by COFFMAX and COFFMIN.  Bit[21:16]=[CH5, CH4, CH3, CH2, CH1, CH0] | b000000 |  |

| 15:14  | Reserved                                 | RO  | Reserved                                                                                                                                                              | b00     |  |

| 13:8   | COMPST                                   | RO  | Indicates whether AOT is being performed Bit[13:8]=[CH5, CH4, CH3, CH2, CH1, CH0]                                                                                     | b000000 |  |

| 7:6    | Reserved                                 | RO  | Reserved                                                                                                                                                              | b00     |  |

|             |       | _  |                                        |         |

|-------------|-------|----|----------------------------------------|---------|

| <b>5</b> ·0 | SATST | PO | CDC data saturation status indication. | b000000 |

| 5.0         | SAISI | KU | Bit[5:0]_[CH5 CH4 CH3 CH2 CH4 CH0]     | 0000000 |

| STAT2: | STAT2: Status Register 2 (Address 0098h) |     |                                                                                                                                   |         |

|--------|------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|---------|

| Bit    | Symbol                                   | R/W | Description                                                                                                                       | Default |

| 31:30  | Reserved                                 | RW  | Reserved                                                                                                                          | b00     |

| 29:24  | RPTST                                    | RW  | Data report status. Indicates that current DIFF data is bigger than report threshold Bit[29:24]=[CH5, CH4, CH3, CH2, CH1, CH0]    | b000000 |

| 23:22  | Reserved                                 | RO  | Reserved                                                                                                                          | b00     |

| 21:16  | INITPROXST                               | RW  | Indicates if proximity has being detected when performing start-up offset compensation. Bit[21:16]=[CH5, CH4, CH3, CH2, CH1, CH0] | p000000 |

| 15:9   | Reserved                                 | RO  | Reserved                                                                                                                          | b00     |

| 8      | CSNUM                                    | RO  | Indicate IC channel number 0:5 channel 1:3 channel                                                                                | b0      |

| 7:5    | Reserved                                 | RO  | Reserved                                                                                                                          | b00     |

| 4      | CONVST                                   | RW  | Indicates if any channel is being measured or processed.  0: Idle  1: Data is being measured or processed                         | b0      |

| 3      | INITPROXSTANY                            | RW  | Indicates if any INITPROXST is set to 1.                                                                                          | b0      |

| 2      | ERRSTANY                                 | RW  | Indicates if any ERRST is set to 1.                                                                                               | b0      |

| 1      | STDSTALL                                 | RW  | Indicates if all STDST bits are set to 1.                                                                                         | b0      |

| 0      | PROXSTANY                                | RW  | Indicates if any PROXST is set to 1.                                                                                              | b0      |

| PROXINTEN : Proximity Interrupt Enable (Address 009Ch) |               |     |                                                                                                                              |         |

|--------------------------------------------------------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------|---------|

| Bit                                                    | Symbol        | R/W | Description                                                                                                                  | Default |

| 31:30                                                  | Reserved      | RW  | Reserved                                                                                                                     | 0       |

| 29:24                                                  | PROXSTATINTEN | RW  | Enable proximity interrupt when diff data > proximity threshold 0:disable 1:enable Bit[29:24]=[CH5, CH4, CH3, CH2, CH1, CH0] | h3F     |

| 23:22                                                  | Reserved      | RO  | Reserved                                                                                                                     | 0       |

| 21:16                                                  | CLOSEINTEN    | RW  | Enable the interrupt when channel from far to close. b0: Disable b1: Enable Bit[29:24]=[CH5, CH4, CH3, CH2, CH1, CH0]        | h3F     |

| 15:14                                                  | Reserved      | RO  | Reserved                                                                                                                     | 0       |

| 13:8                                                   | FARINTEN      | RO  | Enable the interrupt when channel from close to far. b0: Disable b1: Enable Bit[29:24]=[CH5, CH4, CH3, CH2, CH1, CH0]        | h3F     |

| 7:6                                                    | Reserved      | RO  | Reserved                                                                                                                     | 0       |

| 5:0                                                    | SCANOVERINTEN | RW  | Enable the interrupt when channel scan over. b0: Disable b1: Enable Bit[29:24]=[CH5, CH4, CH3, CH2, CH1, CH0]                | h3F     |

FILTREF0\_CH0: Filter and Reference Channel Configure Register 0 for CH0 (Address 00A0h) FILTREF0\_CH1: Filter and Reference Channel Configure Register 0 for CH1 (Address 00DCh) FILTREF0\_CH2: Filter and Reference Channel Configure Register 0 for CH2 (Address 0118h) FILTREF0\_CH3: Filter and Reference Channel Configure Register 0 for CH3 (Address 0154h) FILTREF0\_CH4: Filter and Reference Channel Configure Register 0 for CH4 (Address 0190h) FILTREF0\_CH5: Filter and Reference Channel Configure Register 0 for CH5 (Address 01CCh)

| Bit   | Symbol         | R/W | Description                                                                                                                                  | Default |

|-------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31    | RAWFILTSEL_CHx | RW  | Filter type selection for raw data of CHx (x=0, 1,, 5). b0: RawFilter1 b1: RawFilter2                                                        | b1      |

| 30:29 | FILT2COEF1_CHx | RW  | Coefficient A of RawFilter2 for CHx. b00: 1 (Bypass) b11: 0 (Keep last value) Other: 1/(2^ FILT2COEF1_CHx)                                   | b11     |

| 28:27 | FILT2COEF2_CHx | RW  | Coefficient B of RawFilter2 for CHx. b00: 1 (Bypass) b11: 0 (Keep last value) Other: 1/(2^ FILT2COEF2_CHx)                                   | b00     |

| 26:25 | SMPLNUM_CHx    | RW  | The number of sample for CHx.  Num = 2^ SMPLNUM_CHx                                                                                          | b00     |