## CLCS82C55AZ

## CMOS 可编程外围接口

### 概述

CLCS82C55AZ是一款CMOS可编程外围接口电路，是通用的可编程I/O设备，可以与许多不同的微处理器一起兼容使用。提供24条可编程I/O引脚，可以分别以12组为一组进行编程，并可以在3种主要工作模式下使用，拥有控制字读回功能，拥有直接置位/复位功能，所有I/O端口具有2.5mA驱动能力，适用性强，在静态CMOS电路设计可确保工作功耗更低。

### 特征

- 24个可编程I/O引脚

- 完全兼容TTL

- 高速时无“等待状态”

- 直接位设置/复位功能

- 增强的控制字读取功能

- 所有I/O端口具有2.5mA驱动能力

- 低静态功率 (ICCSB) -10uA

### 应用

- 开关电源

- 家电电机控制

- 印刷设备

- 数控机床

- 包装设备

- 智能安防

### 产品外形

**谨慎!** 建议在操作和组装本部件时采取正常的防静电措施，以防止静电损坏和/或退化。本数据表中的组件不能用于军事或航空航天应用或环境。

## 订购信息

| 制造商零件号        | 温度 范围 ( °C ) | 封装        | 标记信息         | 湿敏等级 | 包装 , 数量     | 生态计划 |

|---------------|--------------|-----------|--------------|------|-------------|------|

| CLCP82C55AZ   | 0 to 70°C    | DIP-40    | CLCP82C55AZ  | MSL3 | 管件,99PCS    | 绿色   |

| CLIP82C55AZ   | -40 to 85°C  | DIP-40    | CLIP82C55AZ  | MSL3 | 管件,99PCS    | 绿色   |

| CLCS82C55AZ   | 0 to 70°C    | PLCC-44   | CLCS82C55AZ  | MSL3 | 管件,520PCS   | 绿色   |

| CLCS82C55AZ96 | 0 to 70°C    | PLCC-44   | CLCS82C55AZ  | MSL3 | 卷带 , 500PCS | 绿色   |

| CLIS82C55AZ   | -40 to 85°C  | PLCC-44   | CLIS82C55AZ  | MSL3 | 管件,520PCS   | 绿色   |

| CLIS82C55AZ96 | -40 to 85°C  | PLCC-44   | CLIS82C55AZ  | MSL3 | 卷带 , 500PCS | 绿色   |

| CLCQ82C55AZ   | 0 to 70°C    | MQFP-44   | CLCQ82C55AZ  | MSL3 | 托盘,440PCS   | 绿色   |

| CLIQ82C55AZ   | -40 to 85°C  | MQFP-44   | CLIQ82C55AZ  | MSL3 | 托盘,440PCS   | 绿色   |

| CLID82C55A    | -40 to 85°C  | CERDIP-40 | CLID82C55A   | MSL3 | 管件,99PCS    | 绿色   |

| CLMD82C55A/B  | -55 to 125°C | CERDIP-40 | CLMD82C55A/B | MSL3 | 管件,99PCS    | 绿色   |

| CLMD82C55QA   | -55 to 125°C | CLCC-44   | CLMD82C55QA  | MSL3 | 管件,500PCS   | 绿色   |

启珑微电子将“绿色”定义为符合RoHS标准，并且不含卤素物质。

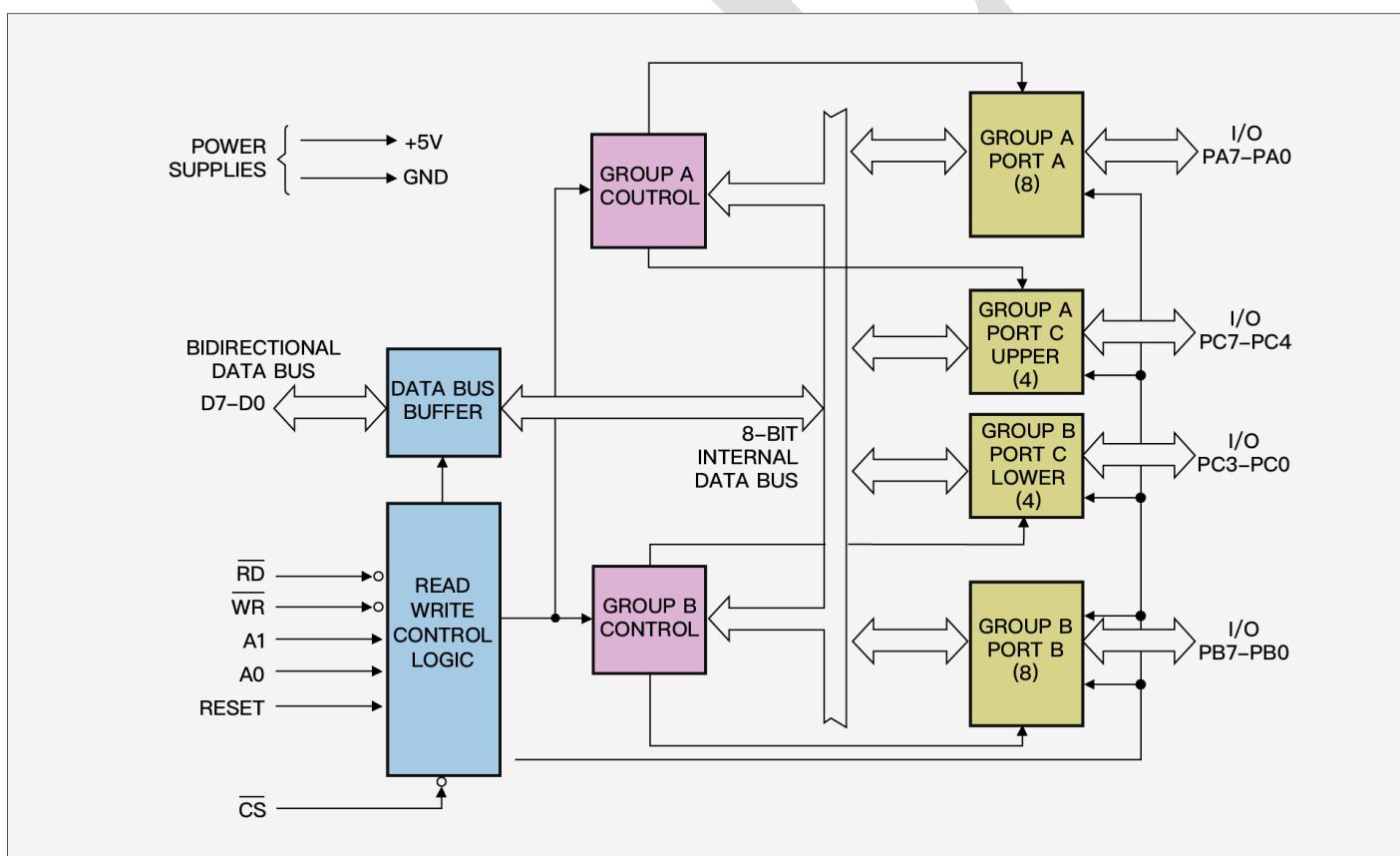

## 功能块

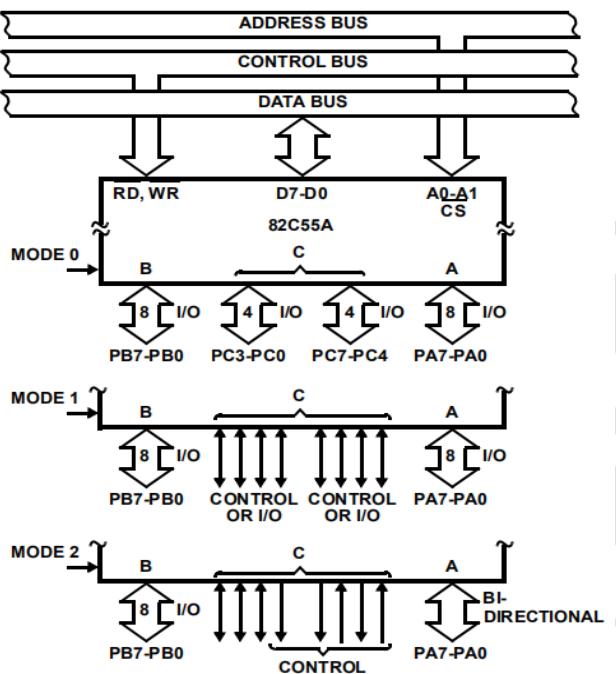

82C55框图

# 目录

|                             |    |

|-----------------------------|----|

| 概述.....                     | 1  |

| 特征.....                     | 1  |

| 应用.....                     | 1  |

| 产品外形.....                   | 1  |

| 订购信息.....                   | 2  |

| 功能块.....                    | 2  |

| 目录.....                     | 3  |

| 图表目录.....                   | 5  |

| 术语.....                     | 6  |

| 1. 引脚排列.....                | 8  |

| 2. 引脚说明.....                | 9  |

| 3. 功能描述.....                | 10 |

| 3.1.数据总线缓冲器 .....           | 10 |

| 3.2.读/写和控制逻辑.....           | 10 |

| 3.3.A组和B组控件 .....           | 10 |

| 3.4.操作说明 .....              | 11 |

| 3.5.单个位置位/复位功能 .....        | 12 |

| 3.5.1.中断控制功能 .....          | 12 |

| 3.5.2.INTE触发器定义 .....       | 12 |

| 3.5.3.操作模式.....             | 12 |

| 3.6.模式0基本功能定义： .....        | 12 |

| 4. 模式0 ( 基本输入 ) .....       | 13 |

| 5. 模式0 ( 基本输出 ) .....       | 13 |

| 6. 模式0配置 .....              | 13 |

| 7. 操作模式.....                | 16 |

| 7.1.INTR ( 中断请求 ) .....     | 16 |

| 7.2.INTE A .....            | 16 |

| 7.3.INTE B .....            | 16 |

| 7.4.输出控制信号定义 .....          | 16 |

| 7.5.NTE A .....             | 17 |

| 7.6.INTE B .....            | 17 |

| 8. 操作模式.....                | 18 |

| 9. 输出操作.....                | 18 |

| 10.特殊模式组合注意事项 .....         | 21 |

| 11.CLCS82C55AZ的应用 .....     | 22 |

| 12.绝对最大额定值TA = + 25°C ..... | 25 |

| 13.芯片参数 .....               | 25 |

| 14.热信息 .....                | 25 |

|                                |    |

|--------------------------------|----|

| 15.电气规格 .....                  | 25 |

| 16.电容 .....                    | 26 |

| 17.交流电气规格 .....                | 26 |

| 18.时序波形 .....                  | 27 |

| 19.交流测试电路 .....                | 29 |

| 20.交流测试输入，输出波形 .....           | 29 |

| 21.老化电路 .....                  | 30 |

| 22.芯片特性 .....                  | 31 |

| 23.陶瓷双列直插式密封包装（ CERDIP ） ..... | 32 |

| 24.陶瓷无铅芯片载体封装（ CLCC ） .....    | 33 |

| 25.塑料引线芯片载体封装（ PLCC ） .....    | 34 |

| 26.公制塑料四方扁平包装（ MQFP ） .....    | 35 |

| 27.联系方式 .....                  | 36 |

# 图表目录

|                           |    |

|---------------------------|----|

| 图7.1 总线保持配置 .....         | 10 |

| 图7.2 基本模式定义和总线接口 .....    | 11 |

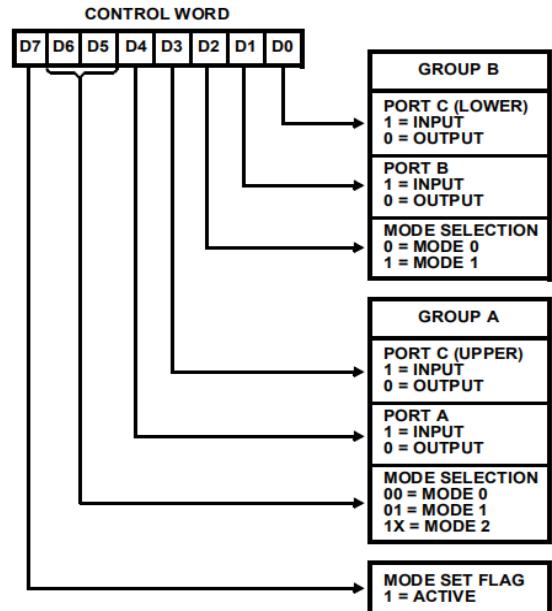

| 图7.3 模式定义格式 .....         | 11 |

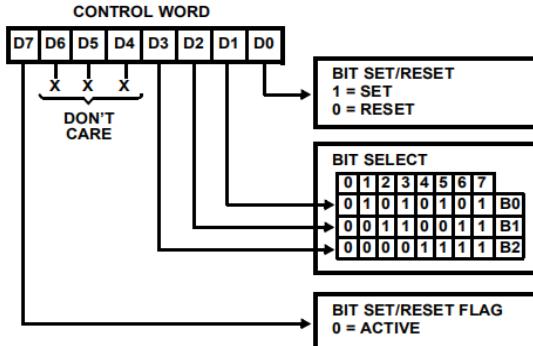

| 图7.4. 位设置/重置格式 .....      | 12 |

| 图11.1. 模式1输入 .....        | 16 |

| 图11.2. 模式1 ( 选通输入 ) ..... | 16 |

| 图11.3 模式1输出 .....         | 17 |

| 图11.4 模式1 ( 选通输出 ) .....  | 17 |

| 图11.5. 模式1的组合 .....       | 17 |

| 图13.1 模式2 ( 双向 ) .....    | 19 |

| 图13.2 模式2组合 .....         | 20 |

| 图14.1 模式1状态字格式 .....      | 21 |

| 图14.2 模式2状态字格式 .....      | 21 |

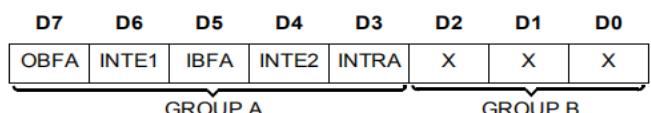

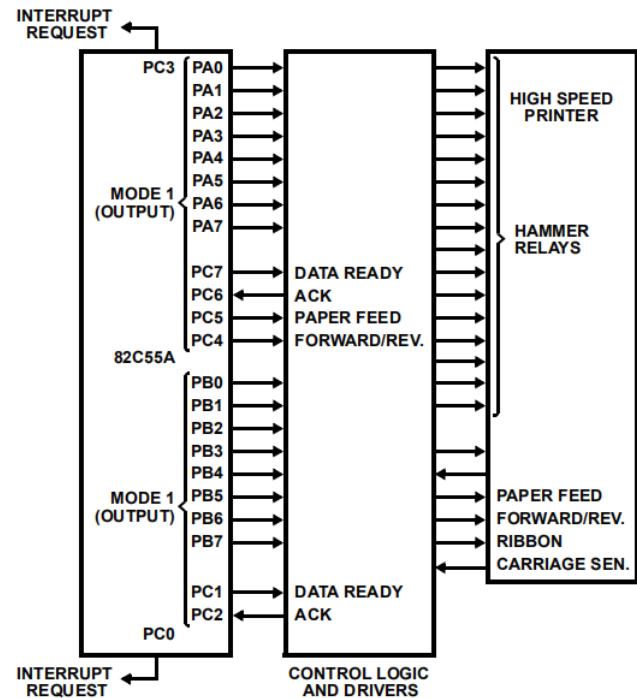

| 图15.1. 打印机接口 .....        | 22 |

| 图22.1 模式0 ( 基本输入 ) .....  | 27 |

| 图22.2 模式0 ( 基本输出 ) .....  | 27 |

| 图22.3 模式1 ( 脉冲输入 ) .....  | 27 |

| 图22.4 模式1 ( 选通输出 ) .....  | 28 |

| 图22.5 模式2 ( 双向 ) .....    | 28 |

# 术语

|        |                                                                  |

|--------|------------------------------------------------------------------|

| ADR    | Address 地址                                                       |

| AL     | Application Layer 应用层                                            |

| BD     | Bidirectional 双向                                                 |

| BGA    | Ball Grid Array 球阵列封装                                            |

| BHE    | Bus High Enable 总线高电平使能                                          |

| CMD    | Command 命令                                                       |

| CS     | Chip Select 片选                                                   |

| DC     | Distributed Clock 集成分布时钟                                         |

| DL     | Data Link Layer 数据链接层                                            |

| EMC    | Electromagnetic Compatibility 电磁兼容性                              |

| EMI    | Electromagnetic Interference 电磁干扰                                |

| EOF    | End of Frame 帧结尾                                                 |

| EEPROM | Electrically Erasable Programmable read only memory 带电可擦可编程只读存储器 |

| FMMU   | Fieldbus Memory Management Unit 现场总线内存管理单元                       |

| GPI    | General Purpose Input 通用数字量输入引脚                                  |

| GPO    | General Purpose Output 通用数字量输出引脚                                 |

| I      | Input 输入                                                         |

| I/O    | Input or Output 输入或者输出                                           |

| I2C    | Inter-Intergrated Circuit 集成电路总线                                 |

| IRQ    | Interrupt Request 中断请求                                           |

| LDO    | Low Drop-Out regulator 低压差线性稳压器                                  |

| LVDS   | Low Voltage Differential Signaling 低压差分信号                        |

| LI-    | LVDS RX- 低压差分信号负接收端                                              |

| LI+    | LVDS RX+ 低压差分信号正接收端                                              |

| LO-    | LVDS TX- 低压差分信号负发射端                                              |

| LO+    | LVDS TX+ 低压差分信号正发射端                                              |

| LED    | Light Emitting Diode 发光二极管                                       |

| MAC    | Media Access Controller 介质访问控制                                   |

| MDIO   | Management Data Input / Output 管理数据输入/输出                         |

| MI     | (PHY) Management Interface 以太网物理层接口器件管理接口                        |

| MII    | Media Independent Interface 介质无关接口                               |

|       |                                                                   |

|-------|-------------------------------------------------------------------|

| MISO  | Master In – Slave Out 主站输入-从站输出                                   |

| MOSI  | Master Out – Slave In 主站输出-从站输入                                   |

| n.a.  | not available 未使用                                                 |

| n.c.  | not connected 未连接                                                 |

| O     | Output 输出                                                         |

| PD    | Pull-down 下拉                                                      |

| PDI   | Process Data Interface 过程数据接口<br>Physical Device Interface 物理设备接口 |

| PLL   | Phase Locked Loop 锁相回路                                            |

| PU    | Pull-up 上拉                                                        |

| PHY   | Physical 以太网物理层器件                                                 |

| QFN   | Quad Flat package No leads 方形扁平无引脚封装                              |

| RD    | Read 读                                                            |

| SII   | Slave Information Interface 从站信息接口                                |

| SM    | SyncManager 同步管理器                                                 |

| SOF   | Start of Frame 帧起始                                                |

| SPI   | Serial Peripheral Interface 串行外设接口                                |

| TA    | Transfer Acknowledge 传输应答                                         |

| TFBGA | Thin-profile Fine-pitch BGA 薄型球栅阵列封装                              |

| TS    | Transfer Start 传输周期启动                                             |

| UI    | Unused Input (PDI: PD, 其它: GND)未使用的输入引脚                           |

| WD    | Watchdog 看门狗                                                      |

| WPD   | Weak Pull-down 弱下拉，只够配置信号                                         |

| WPU   | Weak Pull-up 弱上拉，只够配置信号                                           |

| WR    | Write 写                                                           |

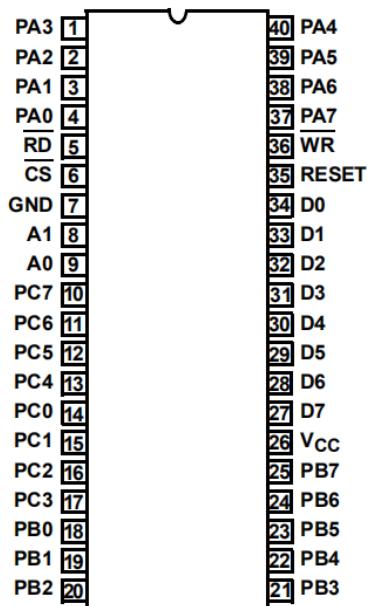

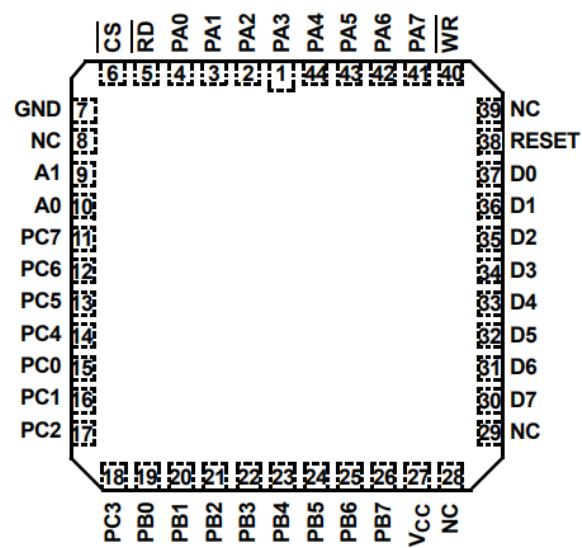

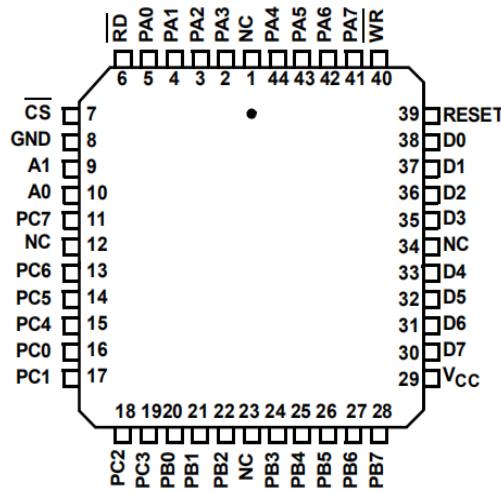

## 1. 引脚排列

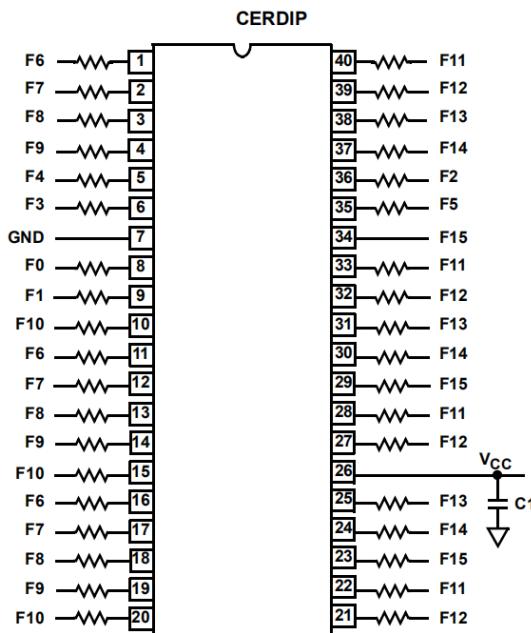

82C55A(PDIP,CERDIP)

顶视图

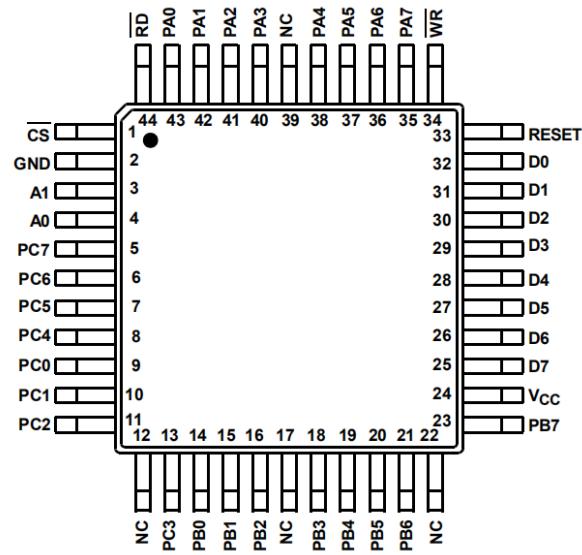

82C55A(CLCC)

顶视图

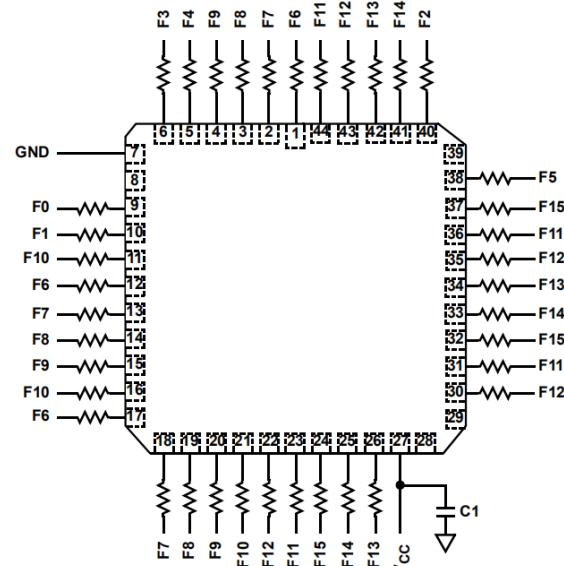

82C55A(PLCC)

顶视图

82C55A(MQFP)

顶视图

## 2. 引脚说明

| 符号              | 类型  | 描述                                                                  |

|-----------------|-----|---------------------------------------------------------------------|

| V <sub>CC</sub> |     | V <sub>CC</sub> : + 5V电源引脚。建议在V <sub>CC</sub> 和GND之间连接一个0.1μF的去耦电容。 |

| GND             |     | 地                                                                   |

| D0-D7           | I/O | 数据总线：数据总线是连接到系统数据总线的双向三态引脚。                                         |

| RESET           | I   | 复位：此输入上的高电平清除控制寄存器，并且所有端口（A，B，C）均在“总线保持”电路开启的情况下设置为输入模式。            |

|                 | I   | 片选：片选是低电平有效输入，用于将CLCS82C55AZ启用到数据总线上以进行CPU通信。                       |

|                 | I   | 读取：读取是低电平有效的输入控制信号，CPU使用它来通过数据总线读取状态信息或数据。                          |

|                 | I   | 写：写是低电平有效输入控制信号，CPU使用它来将控制字和数据加载到CLCS82C55AZ中。                      |

| A0-A1           | I   | 地址：这些输入信号与RD和WR输入一起控制三个端口之一或控制字寄存器的选择。A0和A1通常连接到地址总线A0和A1的最低有效位。    |

| PA0-PA7         | I/O | 端口A：8位输入和输出端口。此端口上同时存在总线保持高电平和总线保持低电平电路。                            |

| PB0-PB7         | I/O | 端口B：8位输入和输出端口。该端口上存在总线保持高电平电路。                                      |

| PC0-PC7         | I/O | 端口C：8位输入和输出端口。该端口上有总线保持电路。                                          |

### 3. 功能描述

#### 3.1. 数据总线缓冲器

该三态双向8位缓冲器用于将CLCS82C55AZ连接到系统数据总线。CPU执行输入或输出指令后，缓冲区将发送或接收数据。控制字和状态信息也通过数据总线缓冲区传输。

#### 3.2. 读/写和控制逻辑

该块的功能是管理数据和控制逻辑或状态字的所有内部和外部传输。它接受来自CPU地址和控制总线的输入，并且依次向两个控制组发出命令。

(0) 片选。该输入引脚为低电平时CLCS82C55AZ与CPU进行通信。

(0) 读。该输入引脚为低电平时CLCS82C55AZ可以将数据或状态信息发送到数据总线上的CPU。从本质上讲，它允许CPU“读取”CLCS82C55AZ。

(0) 写。该输入引脚为低电平时CPU可以将数据或控制字写入CLCS82C55AZ。

(A0和A1) 端口选择0和端口选择1。这些输入信号与RD和WR输入一起控制三个端口之一或控制字寄存器的选择。它们通常连接到地址总线的最低有效位(A0和A1)。

#### CLCS82C55AZ基本操作

|    |    | 输入操作(读) |   |   |          |  |

|----|----|---------|---|---|----------|--|

| A1 | A0 |         |   |   |          |  |

| 0  | 0  | 0       | 1 | 0 | 端口A→数据总线 |  |

| 0  | 1  | 0       | 1 | 0 | 端口B→数据总线 |  |

| 1  | 0  | 0       | 1 | 0 | 端口C→数据总线 |  |

| 1  | 1  | 0       | 1 | 0 | 控制字→数据总线 |  |

|    |    | 输出操作(写) |   |   |          |  |

| 0  | 0  | 1       | 0 | 0 | 数据总线→端口A |  |

| 0  | 1  | 1       | 0 | 0 | 数据总线→端口B |  |

| 1  | 0  | 1       | 0 | 0 | 数据总线→端口C |  |

| 1  | 1  | 1       | 0 | 0 | 数据总线→控制字 |  |

|    |    | 禁用功能    |   |   |          |  |

| x  | x  | x       | x | 1 | 数据总线→三态  |  |

| x  | x  | 1       | 1 | 0 | 数据总线→三态  |  |

(RESET)复位。当输入高电平时会将控制寄存器初始化为9Bh，并且所有端口(A, B, C)均设置为输入模式。CLCS82C55AZ内部的“总线保持”设备将I/O端口输入保持为逻辑“1”状态，最大保持电流为400μA。

#### 3.3. A组和B组控件

每个端口的功能配置由系统软件编程。本质上，CPU将控制字“输出”到CLCS82C55AZ。该控制字包含诸如“模式”，“位设置”，“位复位”等信息，这些信息可初始化CLCS82C55AZ的功能配置。

每个控制块(组A和组B)都接收来自读/写控制逻辑的“命令”，接收来自内部数据总线的“控制字”，并向其关联的端口发出正确的命令。

控制组A-端口A和端口C的高四位(C7-C4)

控制组B-端口B和端口C的低四位(C3-C0)

控制字寄存器可以如“基本操作”表中所示进行读写。图4显示了读写操作的控制字格式。读取控制字时，D7位将始终为逻辑“1”，因为这意味着控制字模式信息。

端口A,B,C

CLCS82C55AZ包含三个8位端口(A, B和C)。所有这些都可以通过系统软件配置为多种功能特性，但是每种功能都有其自己的特殊功能或“个性”，以进一步增强CLCS82C55AZ的功能和灵活性。

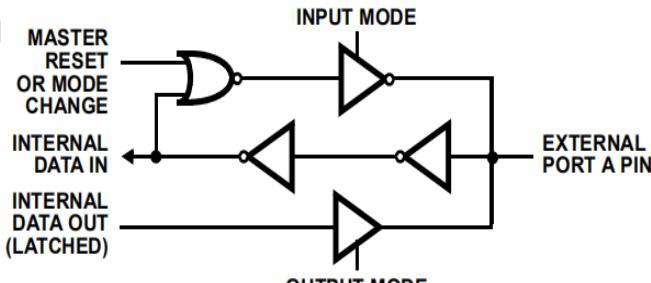

端口A：1个8位数据输出锁存器/缓冲器和1个8位数据输入锁存器。端口A上同时存在“上拉”和“下拉”总线保持设备。请参见图2A。

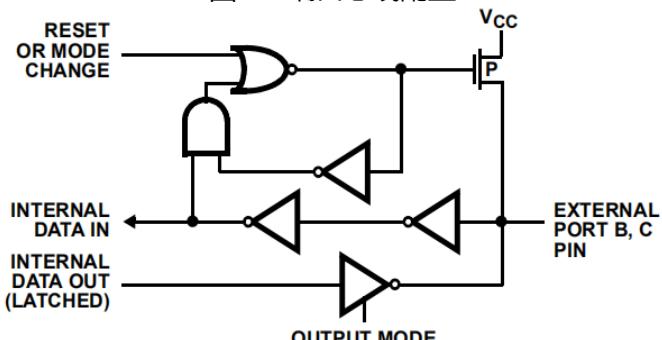

端口B：1个8位数据输入/输出锁存器/缓冲器和1个8位数据输入缓冲器。参见图2B。

端口C：1个8位数据输出锁存器/缓冲器和1个8位数据输入缓冲器(无输入锁存器)。在模式控制下，此端口可以分为两个4位端口。每个4位端口包含一个4位锁存器，可与端口A和B一起用于控制信号输出和状态信号输入。请参见图2B。

图2A. 端口总线配置

图2B. B和C端口的总线保持配置

图7.1 总线保持配置

### 3.4.操作说明

#### 模式选择

系统软件可以选择三种基本的操作模式：

模式0-基本输入/输出

模式1-交错输入/输出

模式2-双向总线

当复位输入变为“高电平”时，所有端口将被设置为输入模式，所有24条端口线均通过内部总线保持设备保持在逻辑“1”电平。清除复位后，无需额外初始化即可将CLCS82C55AZ保持在输入模式。这消除了在全CMOS设计中上拉或下拉电阻的需要。控制字寄存器将包含9Bh。在执行系统程序期间，可以使用单个输出指令选择其他任何模式。这样，一个CLCS82C55AZ即可通过简单的软件维护协议为各种外围设备提供服务。写入控制字时，任何被编程为输出端口的端口都将初始化为全零。

图7.2 基本模式定义和总线接口

图7.3 模式定义格式

端口A和端口B的模式可以分别定义，而端口C根据端口A和端口B的定义分为两部分。每当更改模式时，所有输出寄存器（包括状态触发器）都将复位。可以组合模式，以便可以将其功能定义“定制”到几乎任何I/O结构。例如：可以在模式0中对B组进行编程以监视简单的开关闭合或显示计算结果，在模式1下对A组进行编程以在中断驱动的基础上监视键盘或磁带读取器。

模式定义和可能的模式组合乍一看似乎令人困惑，但是在粗略检查整个设备操作之后，将出现一种简单的逻辑I/O方法。CLCS82C55AZ的设计考虑了诸如高效的PC板布局，控制信号定义与PC布局之类的因素以及完整的功能灵活性，以支持几乎所有没有外部逻辑的外围设备。这种设计最大程度地利用了可用的引脚。

### 3.5.单个位置位/复位功能

可以使用单个输出指令设置或复位端口C的八位中的任何一位。此功能降低了基于控制的应用程序中的软件需求。

当端口C用作端口A或B的状态/控制时，可以使用位设置/重置操作来设置或重置这些位，就像它们是输出端口一样。

图7.4. 位设置/重置格式

#### 3.5.1. 中断控制功能

当将CLCS82C55AZ编程为在模式1或模式2下运行时，提供的控制信号可用作CPU的中断请求输入。通过使用端口C的位设置/复位功能来设置或复位相关的INTE触发器，可以禁止或启用从端口C生成的中断请求信号。

此功能允许程序员通过特定的I/O设备启用或禁用CPU中断，而不会影响中断结构中的任何其他设备。

#### 3.5.2. INTE触发器定义

( BIT-SET ) -INTE置位-中断使能

( BIT-RESET ) -INTE复位-禁止中断

注意：在模式选择和器件复位期间，所有的Mask触发器都会自动复位。

#### 3.5.3. 操作模式

模式0（基本输入/输出）。此功能配置为三个端口中每个端口提供了简单的输入和输出操作。无需握手，只需将数据写入特定端口或从特定端口读取即可。

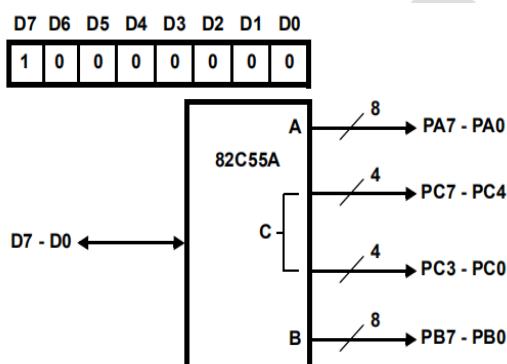

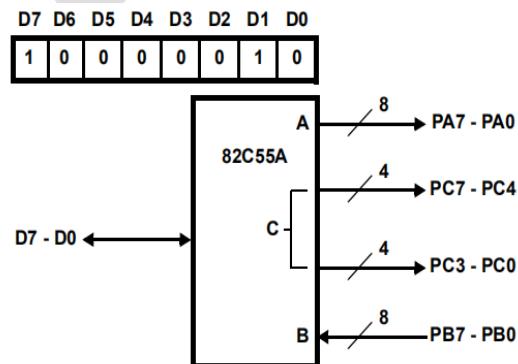

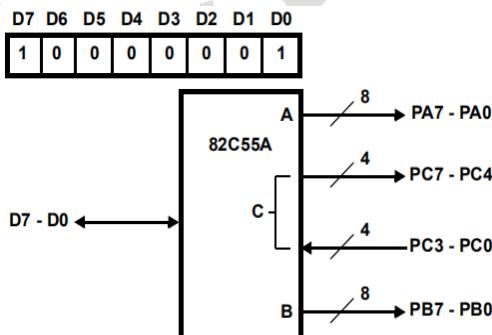

### 3.6.模式0基本功能定义：

- 两个8位端口和两个4位端口

- 任何端口均可输入或输出

- 输出被锁存

- 输入未锁存

- 16种不同的输入/输出配置

模式0端口定义

| A  |    |    |    | B   |              | A组 |     | B组           |  |

|----|----|----|----|-----|--------------|----|-----|--------------|--|

| D4 | D3 | D1 | D0 | 端口A | 端口C<br>(高四位) | #  | 端口B | 端口C<br>(低四位) |  |

| 0  | 0  | 0  | 0  | 输出  | 输出           | 0  | 输出  | 输出           |  |

| 0  | 0  | 0  | 1  | 输出  | 输出           | 1  | 输出  | 输入           |  |

| 0  | 0  | 1  | 0  | 输出  | 输出           | 2  | 输入  | 输出           |  |

| 0  | 0  | 1  | 1  | 输出  | 输出           | 3  | 输入  | 输入           |  |

| 0  | 1  | 0  | 0  | 输出  | 输入           | 4  | 输出  | 输出           |  |

| 0  | 1  | 0  | 1  | 输出  | 输入           | 5  | 输出  | 输入           |  |

| 0  | 1  | 1  | 0  | 输出  | 输入           | 6  | 输入  | 输出           |  |

| 0  | 1  | 1  | 1  | 输出  | 输入           | 7  | 输入  | 输入           |  |

| 1  | 0  | 0  | 0  | 输入  | 输出           | 8  | 输出  | 输出           |  |

| 1  | 0  | 0  | 1  | 输入  | 输出           | 9  | 输出  | 输入           |  |

| 1  | 0  | 1  | 0  | 输入  | 输出           | 10 | 输入  | 输出           |  |

| 1  | 0  | 1  | 1  | 输入  | 输出           | 11 | 输入  | 输入           |  |

| 1  | 1  | 0  | 0  | 输入  | 输入           | 12 | 输出  | 输出           |  |

| 1  | 1  | 0  | 1  | 输入  | 输入           | 13 | 输出  | 输入           |  |

| 1  | 1  | 1  | 0  | 输入  | 输入           | 14 | 输入  | 输出           |  |

| 1  | 1  | 1  | 1  | 输入  | 输入           | 15 | 输入  | 输入           |  |

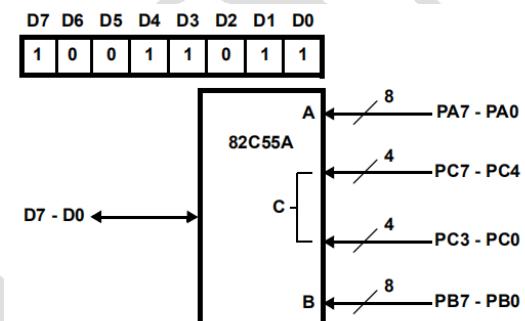

## 4. 模式0 ( 基本输入 )

## 5. 模式0 ( 基本输出 )

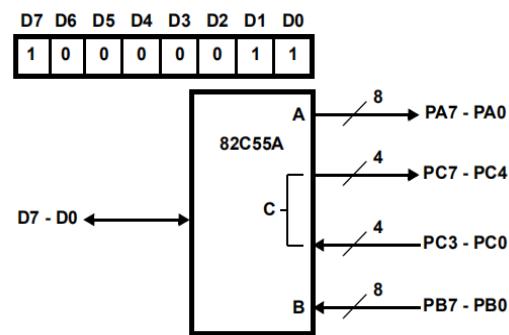

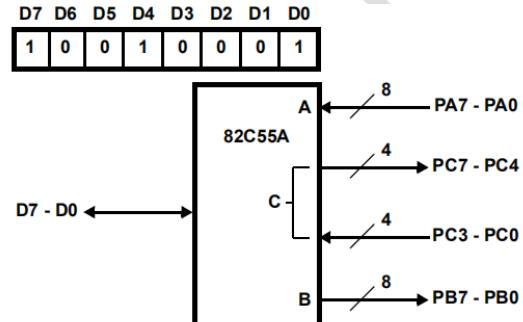

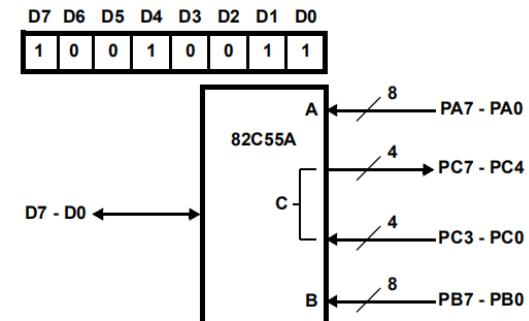

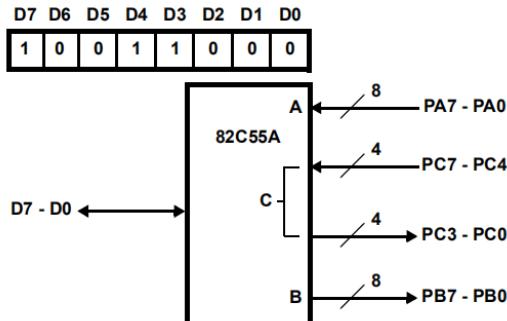

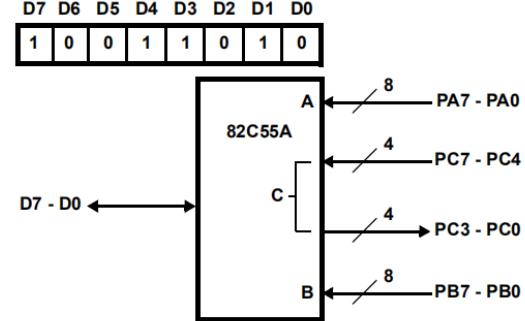

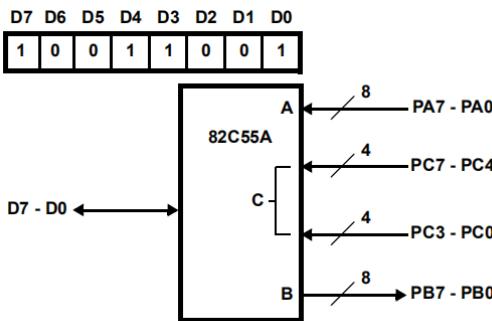

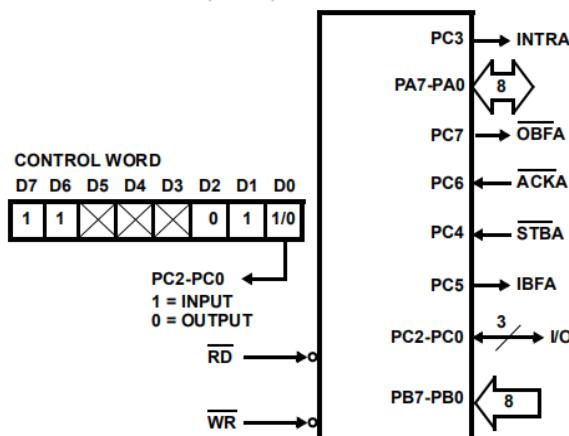

## 6. 模式0配置

控制字 # 0

控制字 # 2

控制字 # 1

控制字 # 3

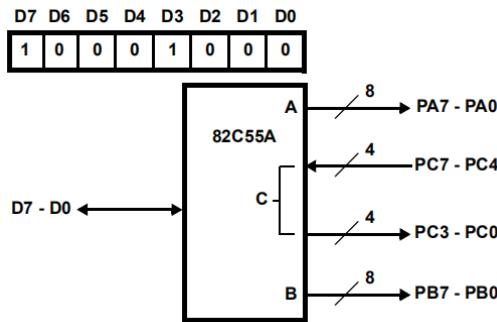

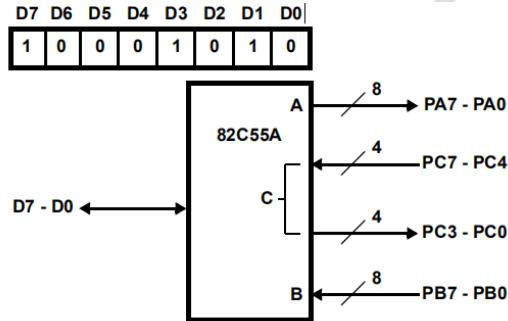

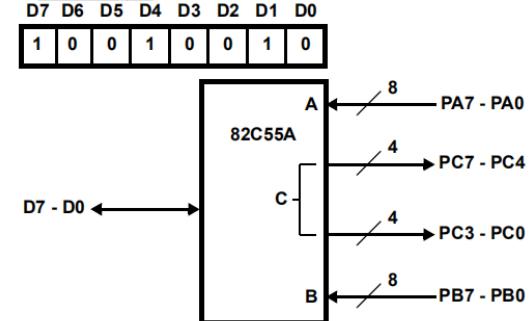

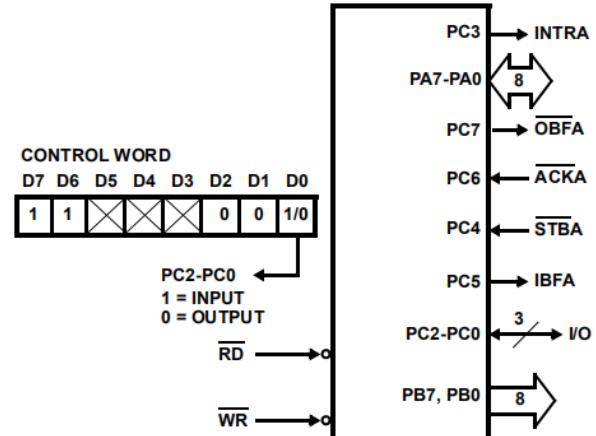

## 模式0配置 (续)

控制字 # 4

控制字 # 8

控制字 # 5

控制字 # 9

控制字 # 6

控制字 # 10

控制字 # 7

控制字 # 11

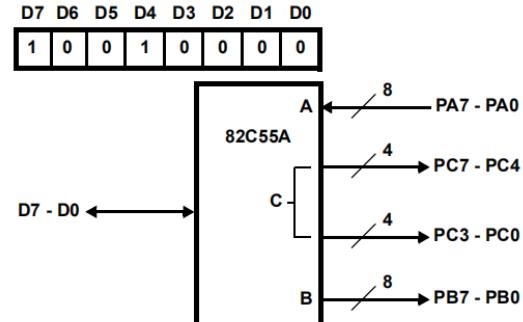

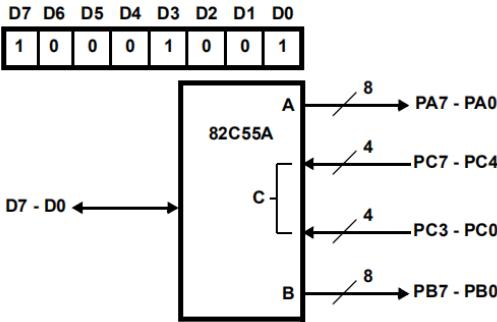

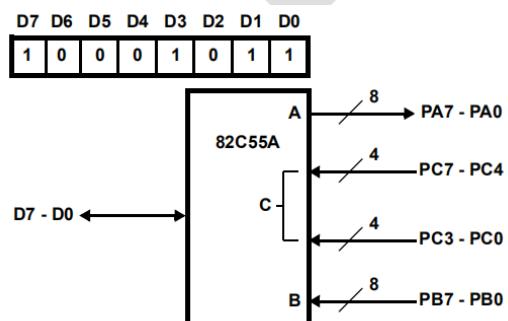

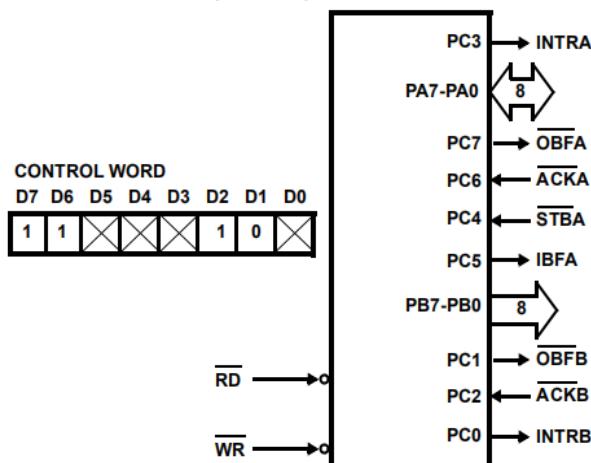

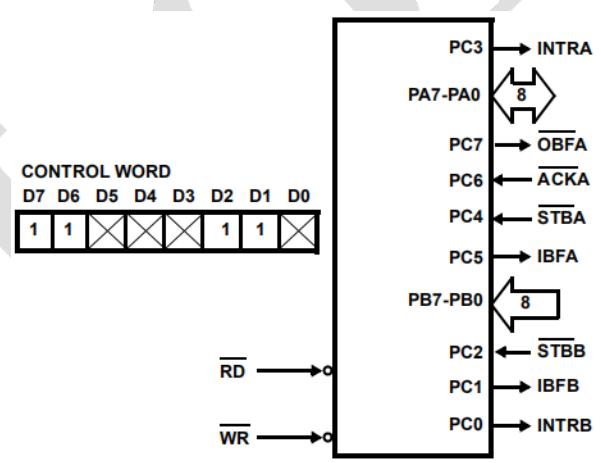

## 模式0配置 (续)

控制字 # 12

控制字 # 14

控制字 # 13

控制字 # 15

## 7. 操作模式

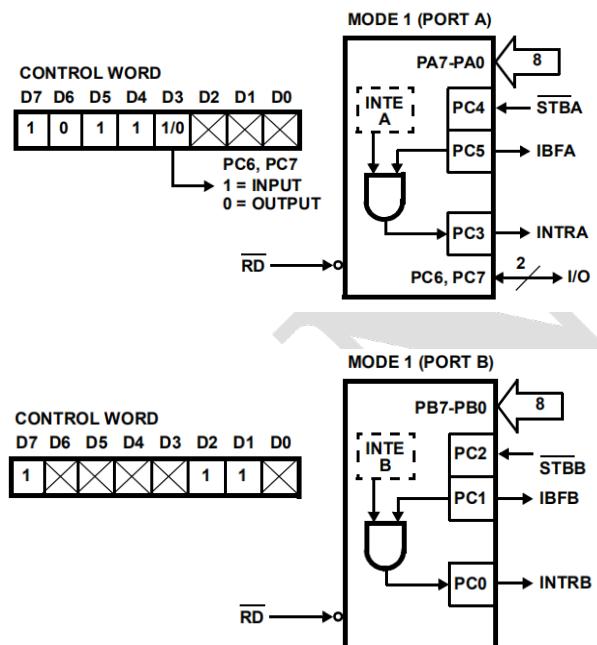

模式1-（频闪输入/输出）。此功能配置提供了一种与选通信号或“握手”信号一起向指定端口或从指定端口传输I/O数据的方法。在模式1中，端口A和端口B使用端口C上的线路生成或接收这些“握手”信号。

模式1基本功能定义：

- 两组（A组和B组）

- 每组包含一个8位端口和一个4位控制/数据端口

- 8位数据端口既可以是输入也可以是输出。输入和输出均被锁存。

- 4位端口用于8位端口的控制和状态。

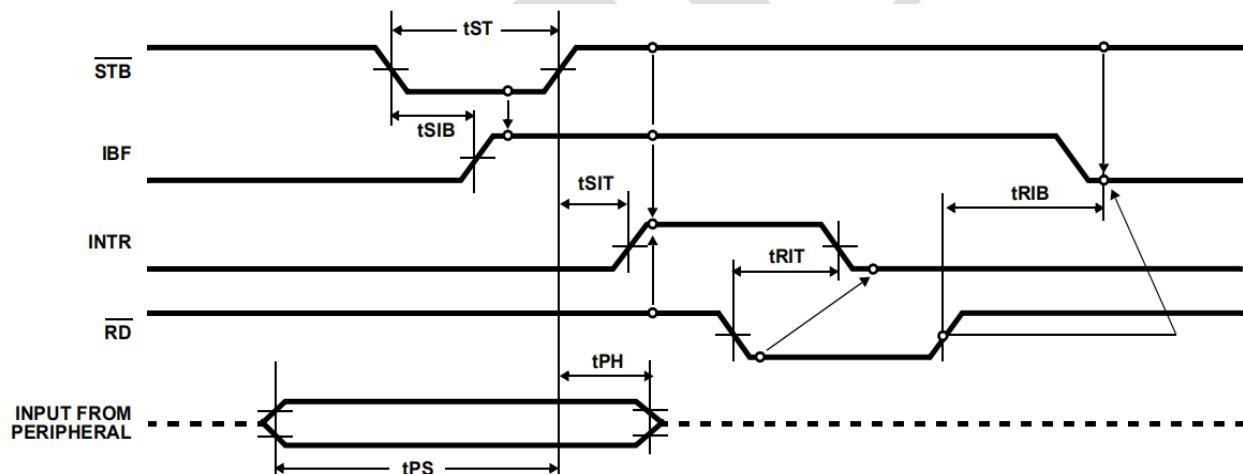

输入控制信号定义

（图6、7）

（选通输入）

该端口输入低电平时将数据加载到输入锁存器中。

IBF（输入缓冲满F/F）

输出高电平时表示数据已加载到输入锁存器中，实质上是一个确认。当输入低电平时IBF被置位，并在输入信号的上升沿复位。

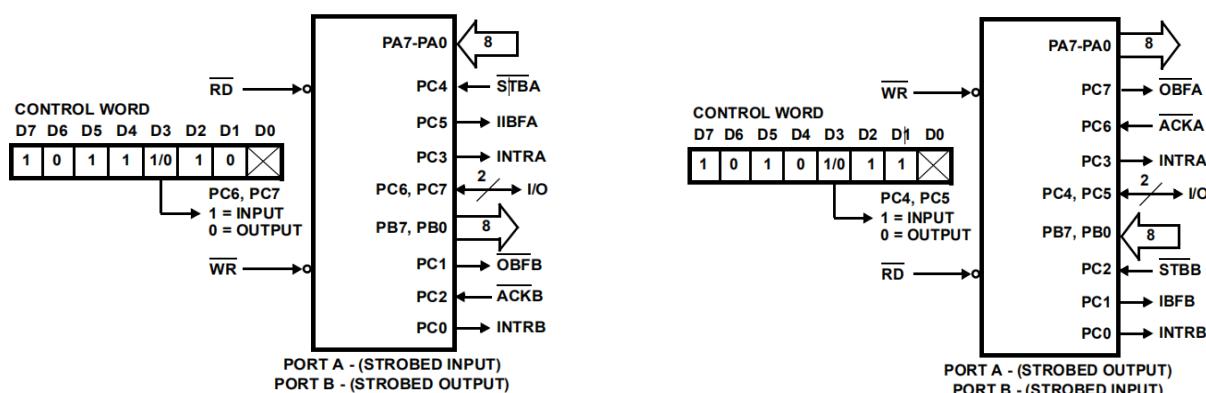

图11.1. 模式1输入

图11.2.模式1（选通输入）

### 7.1.INTR (中断请求)

当输入设备正在请求维修时，此输出上的“高”电平可用于中断CPU。INTR在以下条件下置位：STB为“1”，IBF为“1”，INTE为“1”。并在RD的下降沿复位。此过程允许输入设备通过简单地向CPU请求服务将其数据选通到端口来。

### 7.2.INTE A

由PC4的置位/复位控制。

### 7.3.INTE B

由PC2的位置位/复位控制。

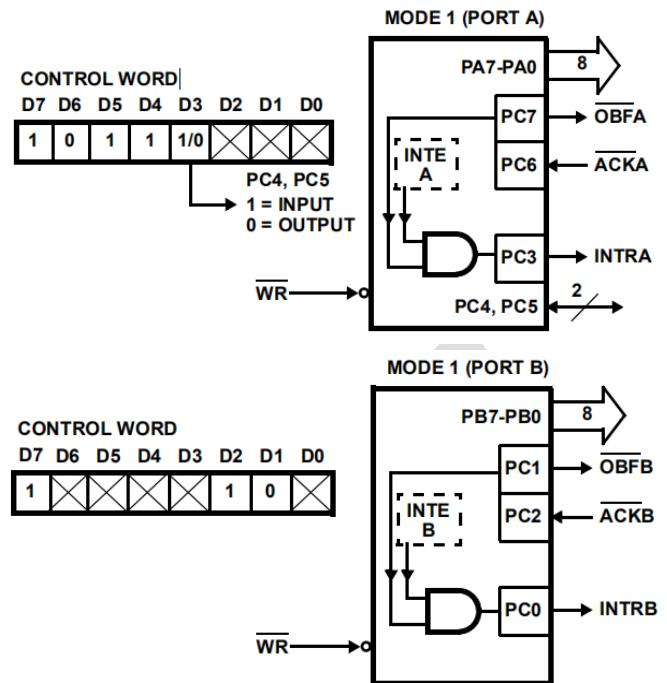

### 7.4.输出控制信号定义

（图8和图9）

-（满输出缓冲F/F）。输出将变为“低”电平，表示CPU已将数据写出到指定的端口。这并不意味着此时将有效数据发送出端口，因为在数据可用之前可以变为“真”。保证数据在上升沿有效（请参见注1）。F/F在输入的上升沿置位，并当输入为低电平时复位。

- (确认输入)。当输入低电平时通知CLCS82C55AZ，端口A或端口B的数据已准备好被接收。本质上，来自外围设备的响应表明它已准备好接收数据（请参见注1）。

INTR- (中断请求)。当输出设备接受CPU传输的数据时，此输出上的“高”电平可用于中断CPU。当 $= 1$ ， $= 1$ 且 $\text{INTE} = 1$ 时INTR置位。当的下降沿时INTR复位。

图11.3 模式1输出

## 7.5.NTE A

由PC6的位置位/复位控制。

## 7.6.INTE B

由PC2的位置位/复位控制。

注意：要将数据选通到外围设备中，用户必须在握手模式下操作选通线。用户需要将发送到外围设备，从外围设备生成，然后在的上升沿将数据锁存到外围设备中。

图11.4 模式1（选通输出）

模式1的组合：在模式1中，可以将端口A和端口B分别定义为输入或输出，以支持多种选通的I/O应用。

图11.5. 模式1的组合

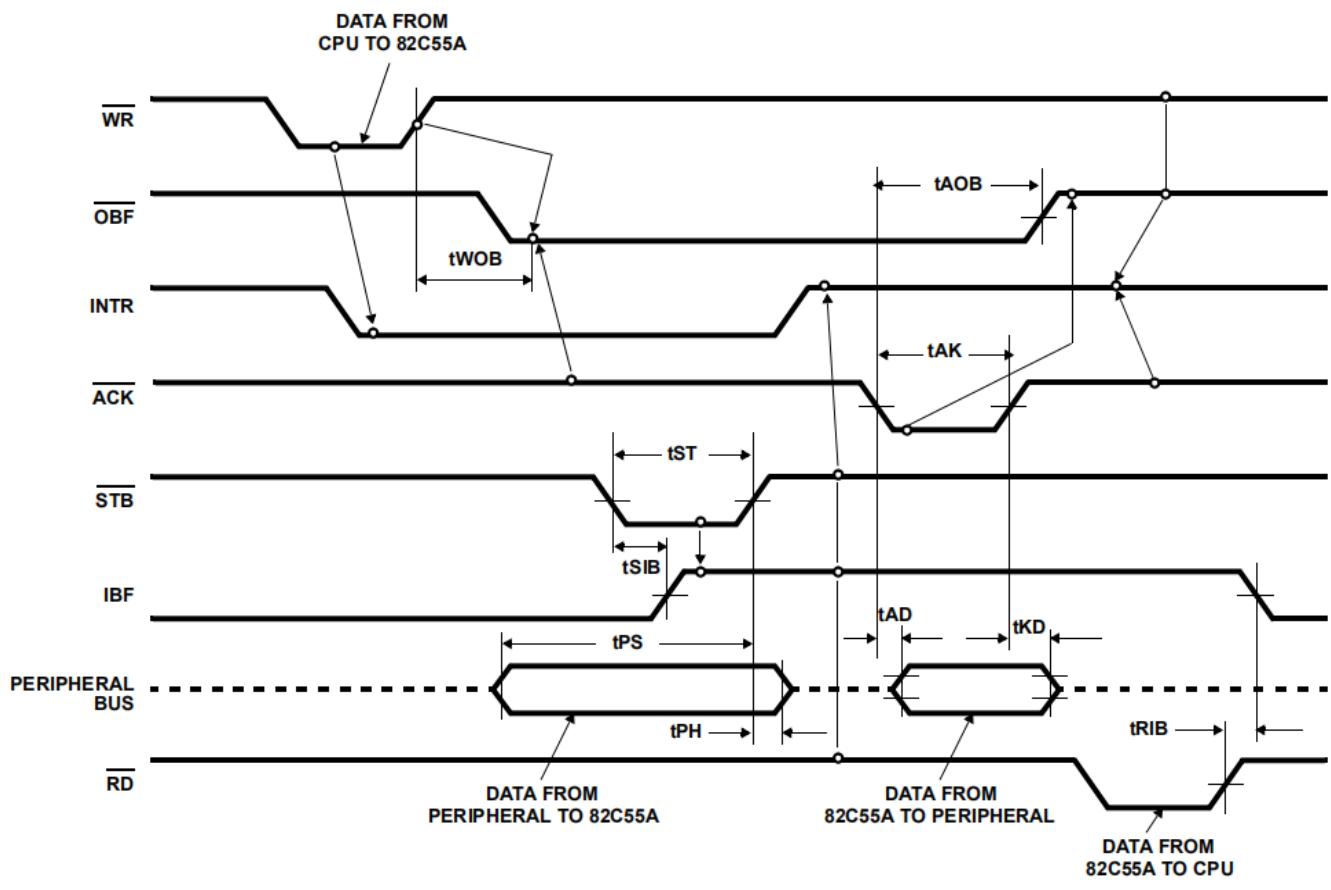

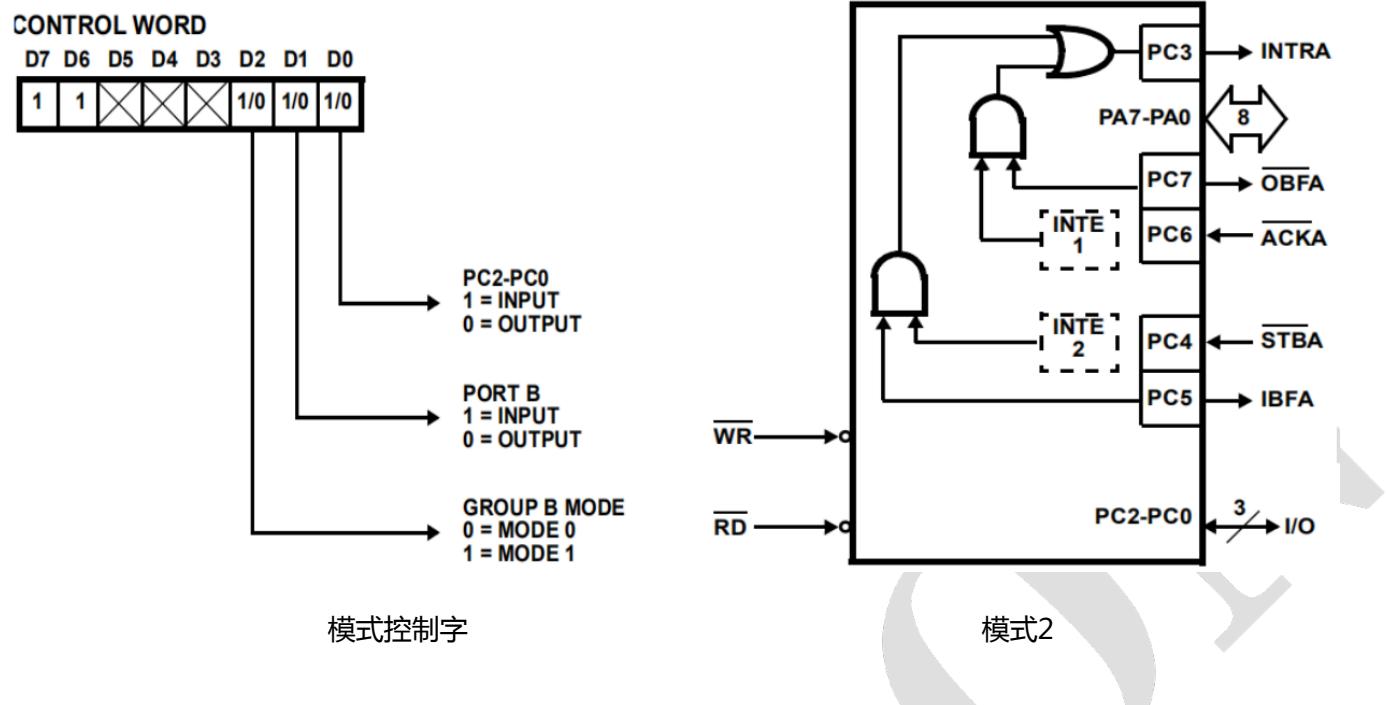

## 8. 操作模式

### 模式2 ( 交错双向总线I/O )

该功能配置提供了一种用于与单个8位总线上的外围设备或结构进行通信的方式，以用于发送和接收数据（双向总线I/O）。提供类似于“模式1”的“握手”信号，以保持适当的总线流规律。还提供中断产生和启用/禁用功能。

模式2基本功能定义：

- 仅用于A组

- 1个8位双向总线端口（端口A）和5位控制端口（端口C）

- 输入和输出均被锁存

- 5位控制端口（端口C）用于8位双向总线端口（端口A）的控制和状态的改变

### 双向总线I/O控制信号定义

（图11、12、13、14）

INTR - ( 中断请求 )。此输出的高电平可用于中断CPU的输入或输出操作。

## 9. 输出操作

- ( 输出缓冲区已满 )。输出变为“低”电平表示CPU已将数据写出到端口A。

- ( 确认 )。此输入端口上的“低”电平使端口A的三态输出缓冲器可以发送数据。否则，输出缓冲器将处于高阻抗状态。

INTE 1- ( 与相关的INTE触发器 )。由PC4的位置位/复位控制。

### 输入操作

- ( 选通输入 )。该端口输入低电平时将数据加载到输入锁存器中。

IBF - ( 满输入缓冲F/F )。输出高电平时表示数据已加载到输入锁存器中。

INTE 2- ( 与IBF相关的INTE触发器 )。由PC4的位置位/复位控制。

注意：允许在之前发生，在RD之前发生的任何序列。 (  $INTR = IBF \cdot MASK \cdot \overline{STB} \cdot \overline{RD} + OBF \cdot MASK$  )

图13.1 模式2 (双向)

模式2和模式0 ( 输入 )

模式2和模式0 ( 输出 )

模式2和模式1 ( 输出 )

模式2和模式1 ( 输入 )

图13.2 模式2组合

## 模式定义摘要

|     | 模式0 |    | 模式1   |       | 模式2               |

|-----|-----|----|-------|-------|-------------------|

|     | 输入  | 输出 | 输入    | 输出    | 仅A组               |

| PA0 | 输入  | 输出 | 输入    | 输出    | ↔                 |

| PA1 | 输入  | 输出 | 输入    | 输出    | ↔                 |

| PA2 | 输入  | 输出 | 输入    | 输出    | ↔                 |

| PA3 | 输入  | 输出 | 输入    | 输出    | ↔                 |

| PA4 | 输入  | 输出 | 输入    | 输出    | ↔                 |

| PA5 | 输入  | 输出 | 输入    | 输出    | ↔                 |

| PA6 | 输入  | 输出 | 输入    | 输出    | ↔                 |

| PA7 | 输入  | 输出 | 输入    | 输出    | ↔                 |

| PB0 | 输入  | 输出 | 输入    | 输出    | 只有<br>模式0<br>或模式1 |

| PB1 | 输入  | 输出 | 输入    | 输出    |                   |

| PB2 | 输入  | 输出 | 输入    | 输出    |                   |

| PB3 | 输入  | 输出 | 输入    | 输出    |                   |

| PB4 | 输入  | 输出 | 输入    | 输出    |                   |

| PB5 | 输入  | 输出 | 输入    | 输出    |                   |

| PB6 | 输入  | 输出 | 输入    | 输出    |                   |

| PB7 | 输入  | 输出 | 输入    | 输出    |                   |

| PC0 | 输入  | 输出 | INTRB | INTRB | I/O               |

| PC1 | 输入  | 输出 | IBFB  | OBFB  | I/O               |

| PC2 | 输入  | 输出 | STBB  | ACKB  | I/O               |

| PC3 | 输入  | 输出 | INTRA | INTRA | INTRA             |

| PC4 | 输入  | 输出 | STBA  | I/O   | STBA              |

| PC5 | 输入  | 输出 | IBFA  | I/O   | IBFA              |

| PC6 | 输入  | 输出 | I/O   | ACKA  | ACKA              |

| PC7 | 输入  | 输出 | I/O   | OBFA  | OBFA              |

## 10.特殊模式组合注意事项

有几种可能的模式组合。对于任何组合，需要将部分或全部C端口线用于控制或状态改变。其余位是“设置模式”命令定义的输入或输出。

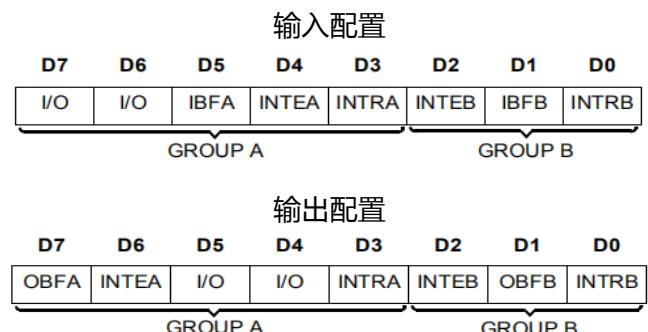

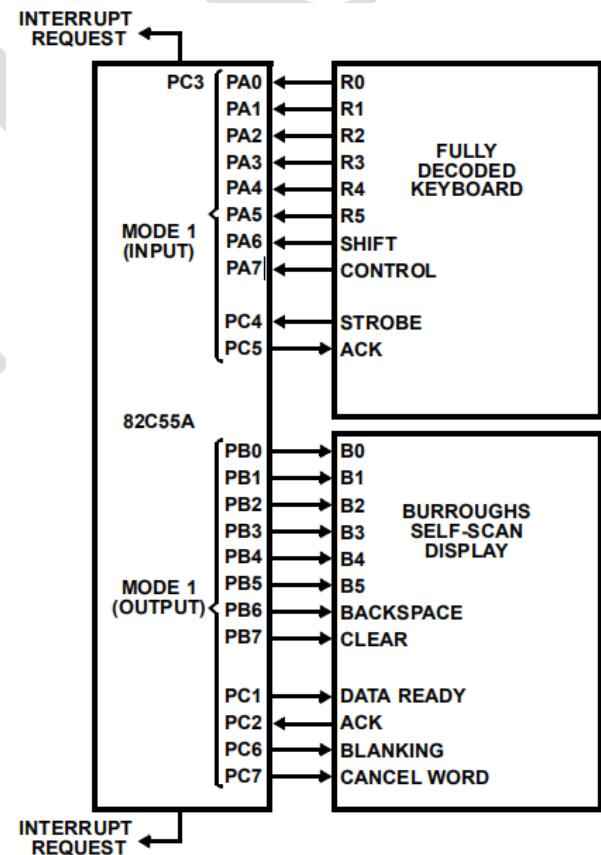

在读取端口C的过程中，除和线外，所有端口C线的状态都将放置在数据总线上。标志状态将出现在PC2，PC4和PC6位位置的数据总线上以代替和线路状态，如图17所示。

通过“Write Port C”（写入端口C）命令，只能写入模式0组中编程为输出的端口C引脚。“写端口C”命令不会影响其他引脚，也不能访问中断使能标志。要写入任何在模式1组中编程为输出的端口C输出或更改中断允许标志，必须使用“设置/复位端口C位”命令。

通过“置位/复位端口C位”命令，可以写入任何编程为输出的端口C线（包括IBF和），或者可以置位或复位中断允许信号。与端口C相关的被编程为输入的端口C线（包括和线）不受“置位/复位端口C位”命令的影响。使用“置位/复位端口C位”命令写入和线的相应

端口C位位置将影响A组和B组中断使能标志，如图17所示。

图14.1 模式1状态字格式

(由模式0或模式1选择定义)

图14.2 模式2状态字格式

## 电流驱动能力

端口A，B或C上的任何输出均可接收或提供2.5mA电流。此功能使CLCS82C55AZ可以直接驱动需要此类电流或源电流的Darlington（达灵顿）型驱动器和高压显示器。

读取端口C状态（图15和16）

在模式0中，端口C用于与外围设备传输（接发）数据。当将CLCS82C55AZ编程为在模式1或2下工作时，端口C会与外围设备产生或接收“握手”信号。读取端口C的内容可使程序员测试或验证每个外围设备的“状态”，并相应地更改程序流程。

没有从端口C读取状态信息的特殊指令。执行端口C的常规读取操作即可执行此功能。

| 中断使能标志  | 位置  | 备用端口C引脚信号（模式）                                        |

|---------|-----|------------------------------------------------------|

| INTE B  | PC2 | $\overline{ACKB}$ （输出模式1）或 $\overline{STBB}$ （输入模式1） |

| INTE A2 | PC4 | $\overline{STBA}$ （输入模式1或模式2）                        |

| INTE A1 | PC6 | $\overline{ACKA}$ （输出模式1或模式2）                        |

模式1和2中的中断使能标志

图15.1.打印机接口

键盘和显示界面

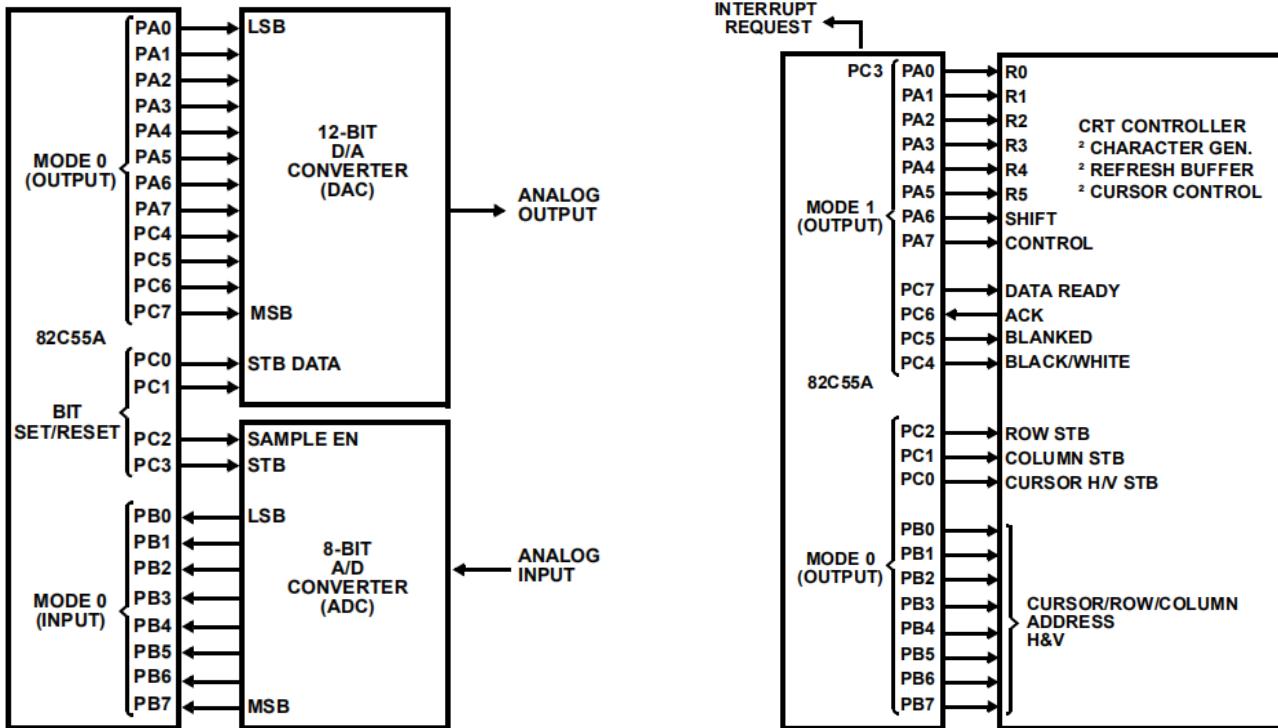

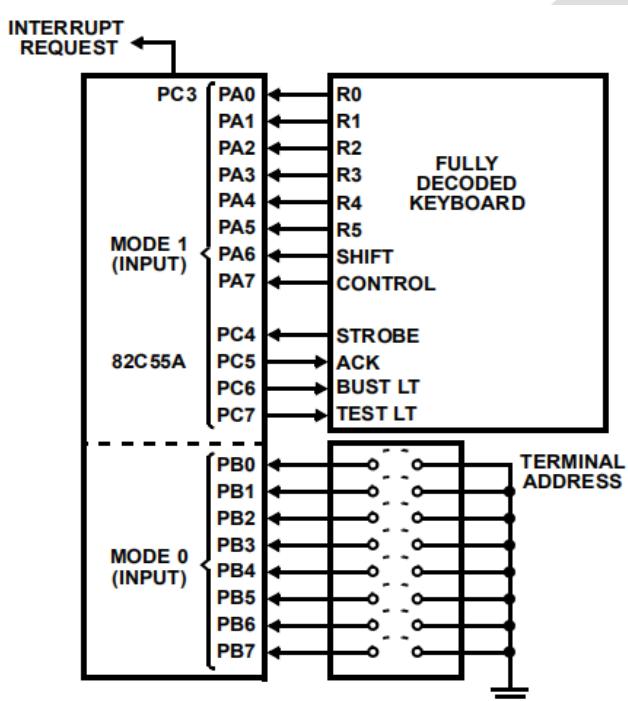

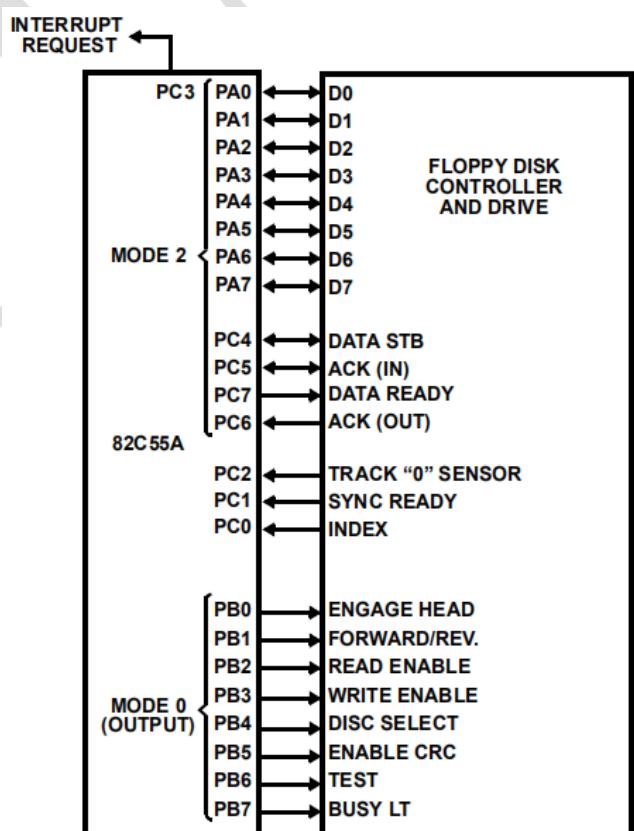

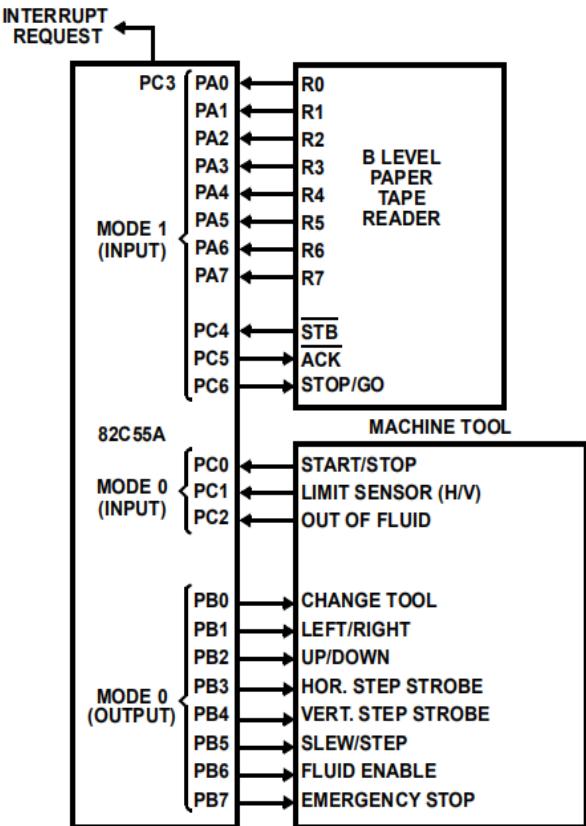

## 11.CLCS82C55AZ的应用

CLCS82C55AZ是非常强大的工具，主要用于将外围设备连接到微型计算机系统。它代表了可用引脚的最佳使用，并且足够灵活，可以连接几乎所有I/O设备，而无需其他外部逻辑。

微型计算机系统中的每个外围设备通常都具有与其相关联的“服务协议”。这些协议管理外围设备和CPU之间的软件接口。CLCS82C55AZ的功能定义由I/O服务协议编程，并成为系统软件的扩展。通过检查I/O设备的数据传输和时序接口特性，并将此信息与详细操作说明中的示例和表格进行匹配，可以轻松开发出控制字来初始化CLCS82C55AZ，以使其完全“适合”应用程序。图18至24给出了CLCS82C55AZ典型应用的一些示例。

基本的CRT控制器接口

键盘和终端地址接口

基本的软盘界面

机床控制器接口

## 12. 绝对最大额定值 $T_A = + 25^\circ\text{C}$

电源电压.....+ 8.0V

输入,输出或I/O电压....GND-0.5V至 $V_{CC} + 0.5\text{V}$

ESD分类.....1级

## 运行条件

电压范围.....+4.5V~5.5V

工作温度范围

CLCS82C55AZ.....0~70°C

CLIS82C55AZ.....-40°C~85°C

CLMD82C55QA.....-55°C~125°C

## 13. 芯片参数

门数量.....1000门

注意：高于“绝对最大额定值”中列出的压力可能会导致设备永久损坏。这仅是压力等级，并不暗示在这些或任何其他超出本规范操作部分指示的条件下的器件操作。

注意： $\theta_{JA}$ 是通过将器件安装在评估PC板上的自由空气中进行测量的。

## 15. 电气规格

$V_{CC} = 5.0\text{V} \pm 10\%$  ;  $T_A$ =工作温度范围

| 符号       | 参数             | 测试条件                                                          | 最小值                   | 最大值  | 单位            |

|----------|----------------|---------------------------------------------------------------|-----------------------|------|---------------|

| $V_{IH}$ | 逻辑“1”输入电压      |                                                               | 2.0<br>2.2            | -    | V             |

| $V_{IL}$ | 逻辑“0”输入电压      |                                                               | -                     | 0.8  | V             |

| $V_{OH}$ | 逻辑“1”输出电压      | $I_{OH} = -2.5\text{mA}$<br>$I_{OH} = -100\mu\text{A}$        | 3.0<br>$V_{CC} - 0.4$ |      | V             |

| $V_{OL}$ | 逻辑“0”输出电压      | $I_{OL} = +2.5\text{mA}$                                      | -                     | 0.4  | V             |

| $I_I$    | 输入漏电流          | $V_{IN} = V_{CC}/\text{GND}, A1, A0, \text{RESET}, \text{WR}$ | -1.0                  | +1.0 | $\mu\text{A}$ |

| $IO$     | I/O引脚漏电流       | $VO = V_{CC}/\text{GND}, D0 \sim D7$                          | -10                   | +10  | $\mu\text{A}$ |

| $IBHH$   | 总线保持高电流        | $VO = 3.0\text{V}$ 。端口A,B,C<br>$T_A = -55^\circ\text{C}$      | -50                   | -450 | $\mu\text{A}$ |

|          |                | $T_A = +128^\circ\text{C}$                                    | -50                   | -400 | $\mu\text{A}$ |

| $IBHL$   | 总线保持低电流        | $VO = 1.0\text{V}$ ,只有端口A<br>$T_A = -55^\circ\text{C}$        | 50                    | 450  | $\mu\text{A}$ |

|          |                | $T_A = +128^\circ\text{C}$                                    | 50                    | 400  | $\mu\text{A}$ |

| $IDAR$   | Darlington驱动电流 | 端口A, B, C。测试条件3                                               | -2.5                  | 注2、4 | mA            |

| $ICCSB$  | 待机电流           | $V_{CC} = 5.5\text{V}$ , $V_{IN} = V_{CC}$ 或GND。输出打开          | -                     | 10   | $\mu\text{A}$ |

| $ICCOP$  | 工作电源电流         | $TA = +25^\circ\text{C}$ , $V_{CC} = 5.0\text{V}$ , 典型值(见注3)  | -                     | 1    | mA/MHz        |

注意：

2. 端口输出上没有内部电流限制。必须在外部添加一个电阻以限制电流。

3.  $ICCOP = 1\text{mA}/\text{MHz}$ 的外设读/写周期时间。(例如：1.0  $\mu\text{s}$ 的I/O读/写周期时间= 1mA)。

4. 在-2.5mA下作为 $V_{OH}$ 测试。

## 14. 热信息

| 热阻(典型值,注1)     | $\theta_{JA}(\text{°C/W})$ | $\theta_{JA}(\text{°C/W})$ |

|----------------|----------------------------|----------------------------|

| CERIP封装        | 50                         | 10                         |

| CLCC封装         | 65                         | 14                         |

| PDIP封装         | 50                         | N/A                        |

| PLCC封装         | 55                         | N/A                        |

| MQFP封装         | 62                         | N/A                        |

| 最高储存温度范围       | -65°C~+150°C               |                            |

| 最高结温           |                            | +175°C                     |

| CDIP封装         |                            | +150°C                     |

| PDIP封装         |                            | +300°C                     |

| 最高引线温度 (焊接10s) |                            | (仅PLCC和MQFP Lead (铅) 引线)   |

## 16.电容

$T_A = +25$

| 符号   | 参数    | 典型 | 单位 | 测试条件                     |

|------|-------|----|----|--------------------------|

| CIN  | 输入电容  | 10 | pF | FREQ = 1MHz , 所有测量均参考GND |

| CI/O | I/O电容 | 20 | pF |                          |

## 17.交流电气规格

$V_{CC} = +5V \pm 10\%$  , GND = 0V ;  $T_A$  = 工作温度范围

| 符号          | 参数           | 82C55A-5 |     | 82C55A |     | 单位 | 测试条件   |

|-------------|--------------|----------|-----|--------|-----|----|--------|

|             |              | 最小值      | 最大值 | 最小值    | 最大值 |    |        |

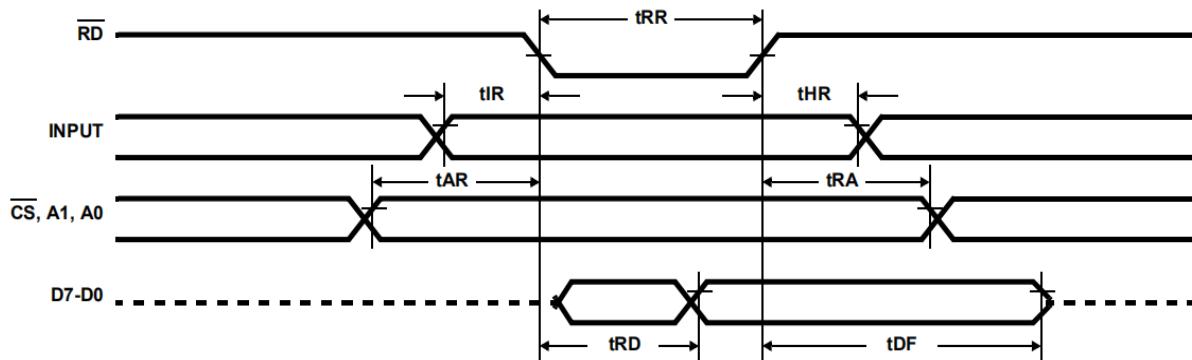

| <b>读取时间</b> |              |          |     |        |     |    |        |

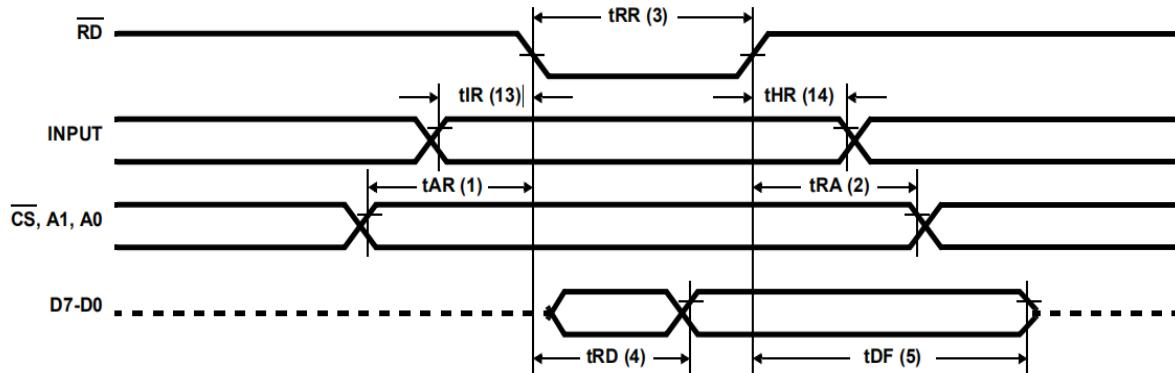

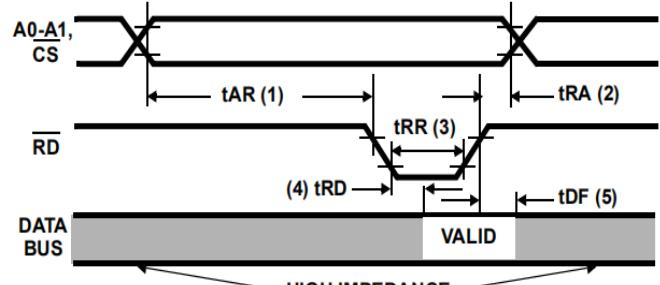

| (1) tAR     | 之前的地址稳定      | 0        | -   | 0      | -   | ns |        |

| (2) tRA     | 后地址稳定        | 0        | -   | 0      | -   | ns |        |

| (3) tRR     | 脉冲宽度         | 250      | -   | 150    | -   | ns |        |

| (4) tRD     | 来自的有效数据      | -        | 200 | -      | 120 | ns | 1      |

| (5) tDF     | 之后的数据浮动      | 10       | 75  | 10     | 75  | ns | 2      |

| (6) tRV     | 和之间的时间       | 300      | -   | 300    | -   | ns |        |

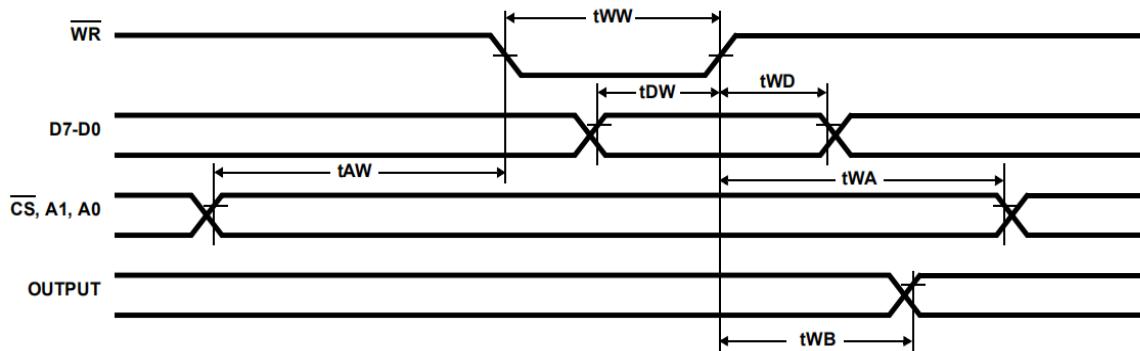

| <b>写时间</b>  |              |          |     |        |     |    |        |

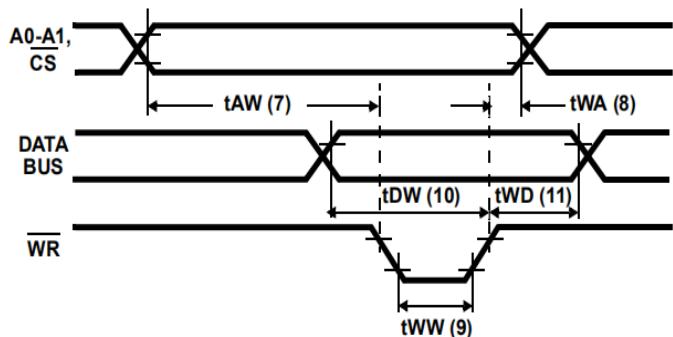

| (7) tAW     | 前地址稳定        | 0        | -   | 0      | -   | ns |        |

| (8) tWA     | 后地址稳定        | 20       | -   | 20     | -   | ns |        |

| (9) tWW     | 脉冲宽度         | 100      | -   | 100    | -   | ns |        |

| (10) tDW    | 数据有效至高       | 100      | -   | 100    | -   | ns |        |

| (11) tWD    | 高后数据有效       | 30       | -   | 30     | -   | ns |        |

| <b>其它时间</b> |              |          |     |        |     |    |        |

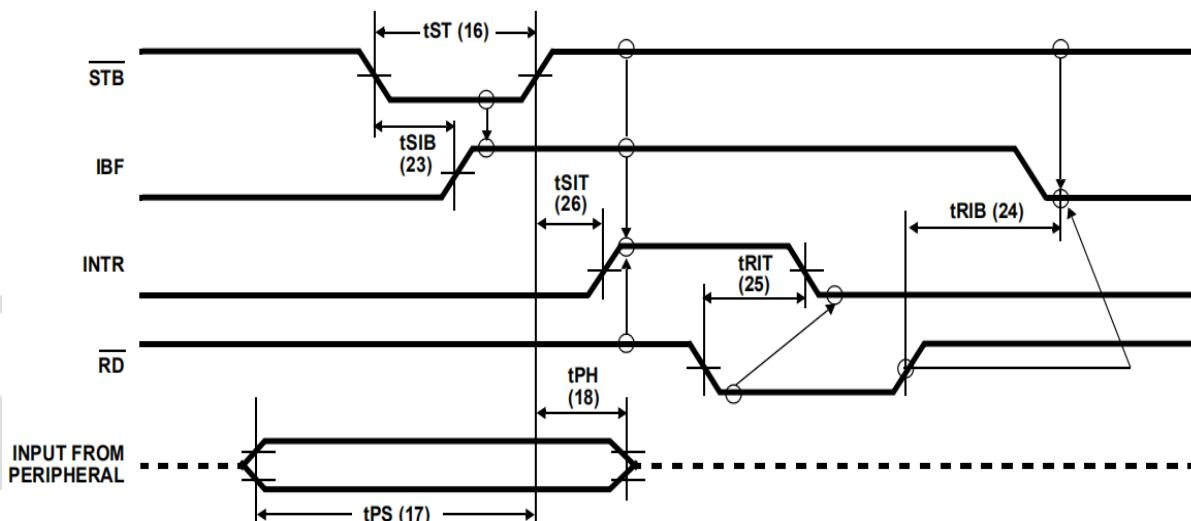

| (12) tWB    | =1至输出        | -        | 350 | -      | 350 | ns | 1      |

| (13) tIR    | 之前的外围数据      | 0        | -   | 0      | -   | ns |        |

| (14) tHR    | 后的外围数据       | 0        | -   | 0      | -   | ns |        |

| (15) tAK    | ACK脉冲宽度      | 200      | -   | 200    | -   | ns |        |

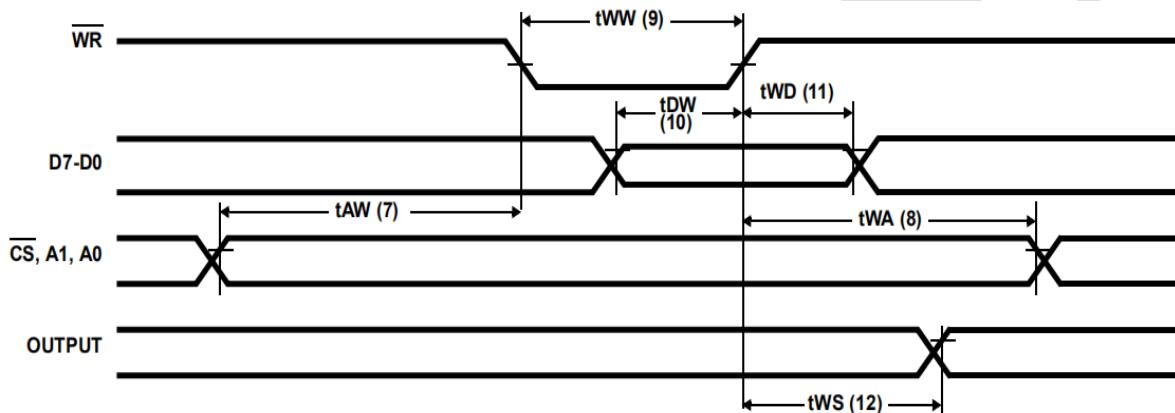

| (16) tST    | STB脉冲宽度      | 100      | -   | 100    | -   | ns |        |

| (17) tPS    | STB高之前的外围数据  | 20       | -   | 20     | -   | ns |        |

| (18) tPH    | STB高之后的外围数据  | 50       | -   | 50     | -   | ns |        |

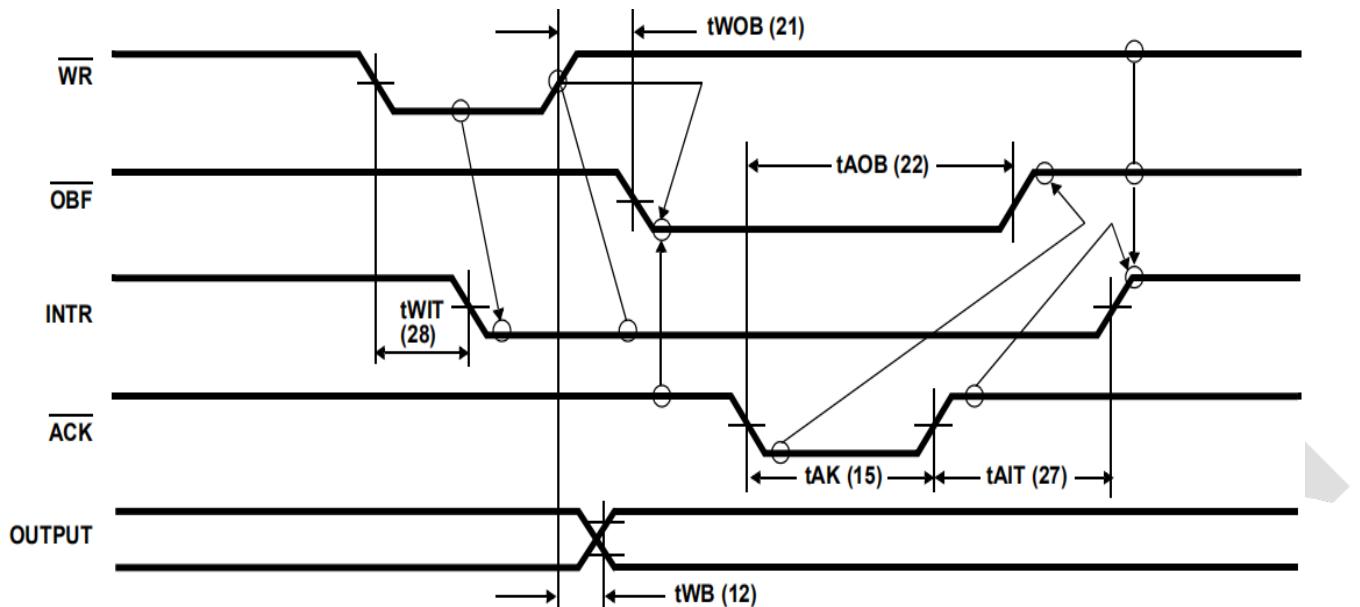

| (19) tAD    | ACK=0至输出     | -        | 175 | -      | 175 | ns | 1      |

| (20) tKD    | ACK=1至输出悬空   | 20       | 250 | 20     | 250 | ns | 2      |

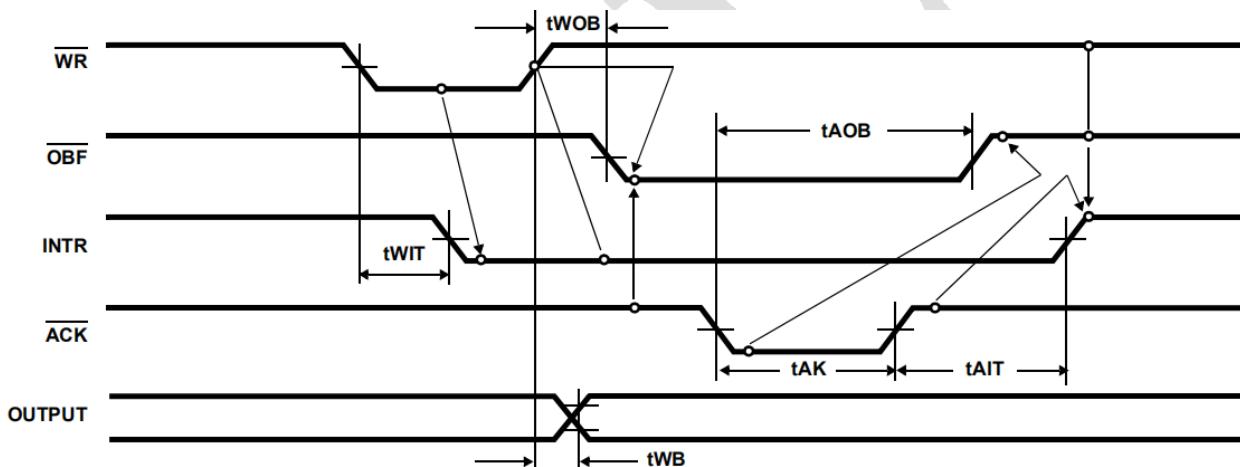

| (21) tWOB   | =1到OBF=0     | -        | 150 | -      | 150 | ns | 1      |

| (22) tAOB   | ACK=0到OBF=1  | -        | 150 | -      | 150 | ns | 1      |

| (23) tSIB   | STB=0到IBF=1  | -        | 150 | -      | 150 | ns | 1      |

| (24) tRIB   | =1到IBF=0     | -        | 150 | -      | 150 | ns | 1      |

| (25) tRIT   | =0到INTR=0    | -        | 200 | -      | 200 | ns | 1      |

| (26) tSIT   | STB=1到INTR=1 | -        | 150 | -      | 150 | ns | 1      |

| (27) tAIT   | ACK=1到INTR=1 | -        | 150 | -      | 150 | ns | 1      |

| (28) tWIT   | =0到INTR=0    | -        | 200 | -      | 200 | ns | 1      |

| (29) tRES   | 复位脉冲宽度       | 500      | -   | 500    | -   | ns | 1, (注) |

注意：上电后的初始复位脉冲周期必须至少为50μs。随后的复位脉冲可能至少为500ns。

## 18.时序波形

图22.1 模式0 (基本输入)

图22.2 模式0 (基本输出)

图22.3 模式1 (脉冲输入)

## 时序波形 (续)

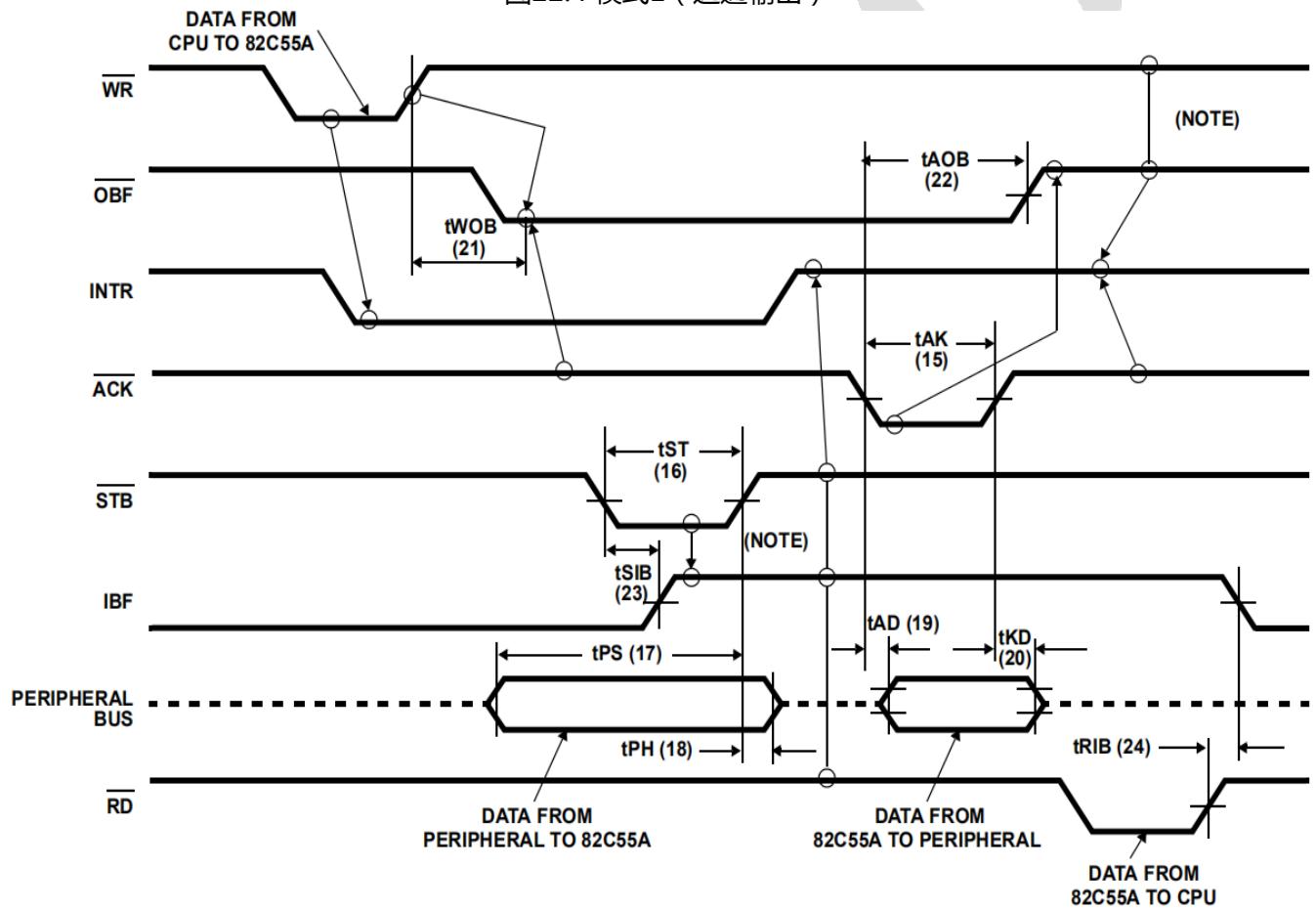

图22.4 模式1 (选通输出)

图22.5 模式2 (双向)

注意：允许在之前发生，在之前发生的任何序列。 ( $INTR = IBF \cdot \overline{MASK} \cdot STB \cdot \overline{RD} + OBF \cdot \overline{MASK} \cdot \overline{ACK} \cdot \overline{WR}$ )

## 时序仿真 (续表)

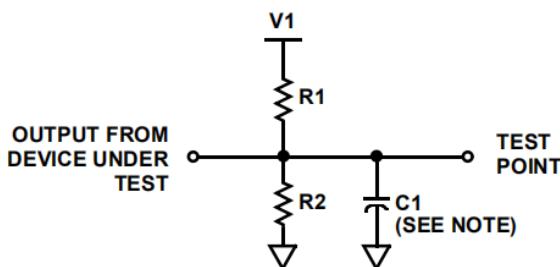

## 19.交流测试电路

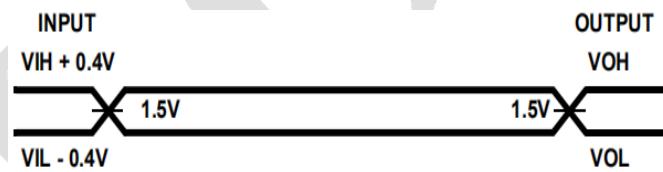

## 20.交流测试输入，输出波形

交流测试：按照测试电路测试所有交流参数。输入上升和下降时间以1ns/V驱动。

测试条件定义表

| 测试条件 | V1              | R1   | R2    | C1    |

|------|-----------------|------|-------|-------|

| 1    | 1.7V            | 523Ω | 开     | 150pF |

| 2    | V <sub>CC</sub> | 2kΩ  | 1.7kΩ | 50pF  |

| 3    | 1.5V            | 750Ω | 开     | 50pF  |

## 21. 老化电路

CERDIP

CLCC

**注意：**

- $$\begin{aligned}1. V_{CC} &= 5.5V \pm 0.5V \\2. VIH &= 4.5V \pm 10\% \\3. Vil &= -0.2V \sim 0.4V \\4. GND &= 0V\end{aligned}$$

注意：

- 1.C1 = 0.01μF , 最小值

- 2.所有电阻均为 $47\text{k}\Omega \pm 5\%$

- 3.f0 = 100kHz ± 10%

4.  $f_0 = f_0 \div 2 ; f_2 = f_1 \div 2 ; \dots ; f_{15} = f_{14} \div 2$

## 22.芯片特性

**金属化：**

类型：硅-铝

厚度 :  $11\text{ k}\text{\AA} \pm 1\text{ k}\text{\AA}$

玻璃化度：

类型：SiO<sub>2</sub>

厚度 :  $8\text{ k}\text{\AA} \pm 1\text{ k}\text{\AA}$

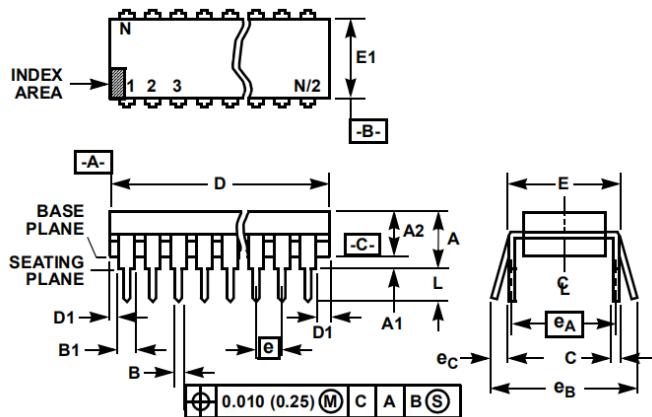

## 双列直插式塑料封装 (PDIP)

| 符号 | 英寸        |       | 毫米        |       | 备注 |

|----|-----------|-------|-----------|-------|----|

|    | 最小值       | 最大值   | 最小值       | 最大值   |    |

| A  | -         | 0.250 | -         | 6.35  | 4  |

| A1 | 0.015     | -     | 0.39      | -     | 4  |

| A2 | 0.125     | 0.195 | 3.18      | 4.95  | -  |

| B  | 0.014     | 0.022 | 0.356     | 0.558 | -  |

| B1 | 0.030     | 0.070 | 0.77      | 1.77  | 8  |

| C  | 0.008     | 0.015 | 0.204     | 0.381 | -  |

| D  | 1.980     | 2.095 | 50.3      | 53.2  | 5  |

| D1 | 0.005     | -     | 0.13      | -     | 5  |

| E  | 0.600     | 0.625 | 15.24     | 15.87 | 6  |

| e  | 0.100 BSC |       | 2.54 BSC  |       | -  |

| eA | 0.600 BSC |       | 15.24 BSC |       | 6  |

| eB | -         | 0.700 | -         | 17.78 | 7  |

| L  | 0.115     | 0.200 | 2.93      | 5.08  | 4  |

| N  | 40        |       | 40        |       | 9  |

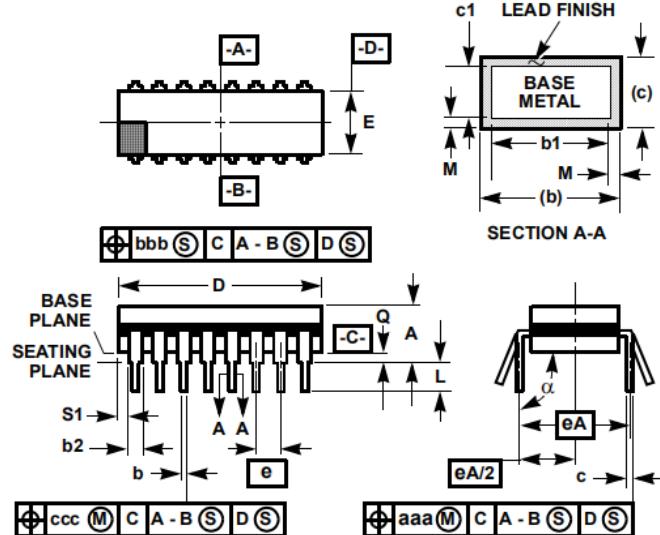

## 23.陶瓷双列直插式密封包装 ( CERDIP )

| 符号       | 英寸        |        | 毫米        |       | 备注  |

|----------|-----------|--------|-----------|-------|-----|

|          | 最小值       | 最大值    | 最小值       | 最大值   |     |

| A        | -         | 0.225  | -         | 5.72  | -   |

| b        | 0.014     | 0.026  | 0.36      | 0.66  | 2   |

| $b_1$    | 0.014     | 0.023  | 0.36      | 0.58  | 3   |

| $b_2$    | 0.045     | 0.065  | 1.14      | 1.65  | -   |

| $b_3$    | 0.023     | 0.045  | 0.58      | 1.14  | 4   |

| c        | 0.008     | 0.018  | 0.20      | 0.46  | 2   |

| $c_1$    | 0.008     | 0.015  | 0.20      | 0.38  | 3   |

| D        | -         | 2.096  | -         | 53.24 | 5   |

| E        | 0.510     | 0.620  | 12.95     | 15.75 | 5   |

| e        | 0.100 BSC |        | 2.54 BSC  |       | -   |

| $e_A$    | 0.600 BSC |        | 15.24 BSC |       | -   |

| $e_A/2$  | 0.300 BSC |        | 7.62 BSC  |       | -   |

| L        | 0.125     | 0.200  | 3.18      | 5.08  | -   |

| Q        | 0.015     | 0.070  | 0.38      | 1.78  | 6   |

| $S_1$    | 0.005     | -      | 0.13      | -     | 7   |

| $\alpha$ | 90°       | 105°   | 90°       | 105°  | -   |

| aaa      | -         | 0.015  | -         | 0.38  | -   |

| bbb      | -         | 0.030  | -         | 0.76  | -   |

| ccc      | -         | 0.010  | -         | 0.25  | -   |

| M        | -         | 0.0015 | -         | 0.038 | 2,3 |

| N        | 40        |        | 40        |       | 8   |

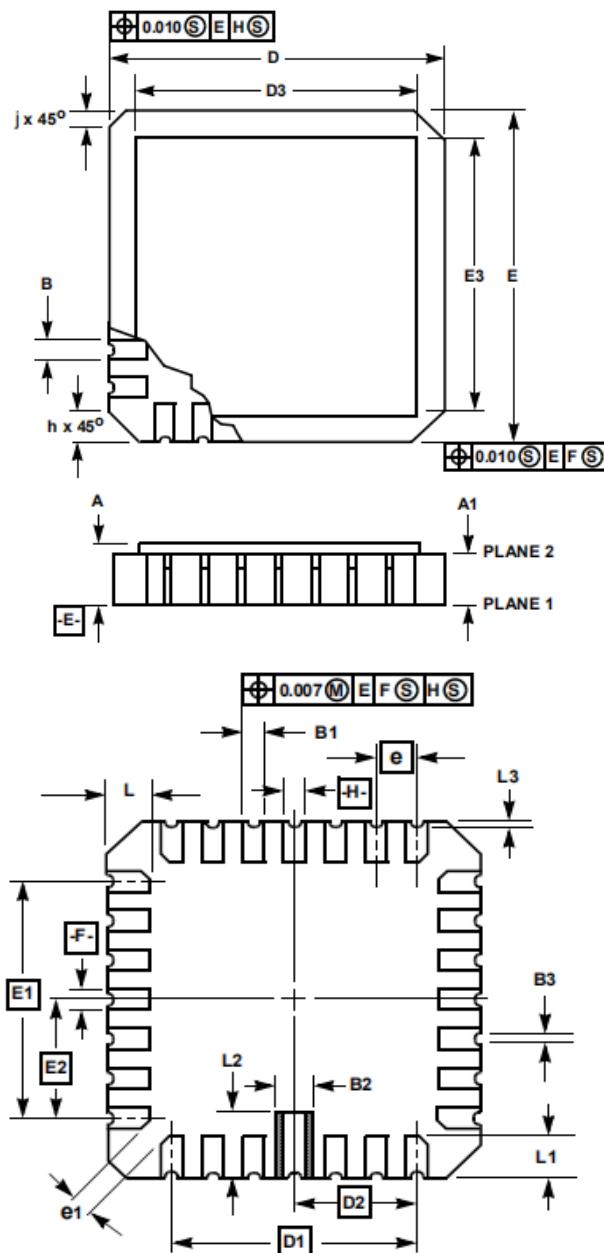

## 24.陶瓷无铅芯片载体封装 ( CLCC )

| 符号 | 英寸        |       | 毫米        |       | 备注  |

|----|-----------|-------|-----------|-------|-----|

|    | 最小值       | 最大值   | 最小值       | 最大值   |     |

| A  | 0.064     | 0.120 | 1.63      | 3.05  | 6,7 |

| A1 | 0.054     | 0.088 | 1.37      | 2.24  | -   |

| B  | 0.033     | 0.039 | 0.84      | 0.99  | 4   |

| B1 | 0.022     | 0.028 | 0.56      | 0.71  | 2,4 |

| B2 | 0.072 REF |       | 1.83 REF  |       | -   |

| B3 | 0.006     | 0.022 | 0.15      | 0.56  | -   |

| D  | 0.640     | 0.662 | 16.26     | 16.81 | -   |

| D1 | 0.500 BSC |       | 12.70 BSC |       | -   |

| D2 | 0.250 BSC |       | 6.35 BSC  |       | -   |

| D3 | -         | 0.662 | -         | 16.81 | 2   |

| E  | 0.640     | 0.662 | 16.26     | 16.81 | -   |

| E1 | 0.500 BSC |       | 12.70 BSC |       | -   |

| E2 | 0.250 BSC |       | 6.35 BSC  |       | -   |

| E3 | -         | 0.662 | -         | 16.81 | 2   |

| e  | 0.050 BSC |       | 1.27 BSC  |       | -   |

| e1 | 0.015     | -     | 0.38      | -     | 2   |

| h  | 0.040 REF |       | 1.02 REF  |       | 5   |

| j  | 0.020 REF |       | 0.51 REF  |       | 5   |

| L  | 0.045     | 0.055 | 1.14      | 1.40  | -   |

| L1 | 0.045     | 0.055 | 1.14      | 1.40  | -   |

| L2 | 0.075     | 0.095 | 1.90      | 2.41  | -   |

| L3 | 0.003     | 0.015 | 0.08      | 0.38  | -   |

| ND | 11        |       | 11        |       | 3   |

| NE | 11        |       | 11        |       | 3   |

| N  | 44        |       | 44        |       | 3   |

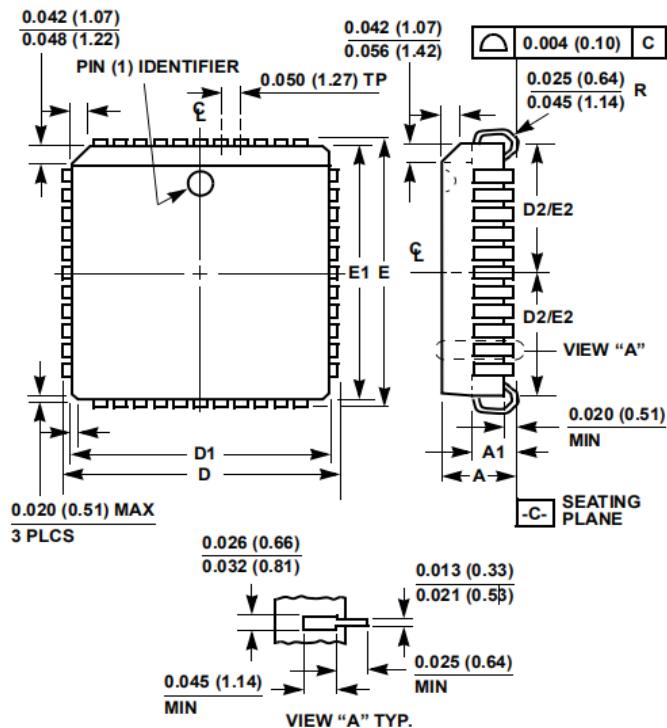

## 25.塑料引线芯片载体封装 (PLCC)

| 符号 | 英寸    |       | 毫米    |       | 备注  |

|----|-------|-------|-------|-------|-----|

|    | 最小值   | 最大值   | 最小值   | 最大值   |     |

| A  | 0.165 | 0.180 | 4.20  | 4.57  | -   |

| A1 | 0.090 | 0.120 | 2.29  | 3.04  | -   |

| D  | 0.685 | 0.695 | 17.40 | 17.65 | -   |

| D1 | 0.650 | 0.656 | 16.51 | 16.66 | 3   |

| D2 | 0.291 | 0.319 | 7.40  | 8.10  | 4,5 |

| E  | 0.685 | 0.695 | 17.40 | 17.65 | -   |

| E1 | 0.650 | 0.656 | 16.51 | 16.66 | 3   |

| E2 | 0.291 | 0.319 | 7.40  | 8.10  | 4,5 |

| N  | 44    |       | 44    |       | 6   |

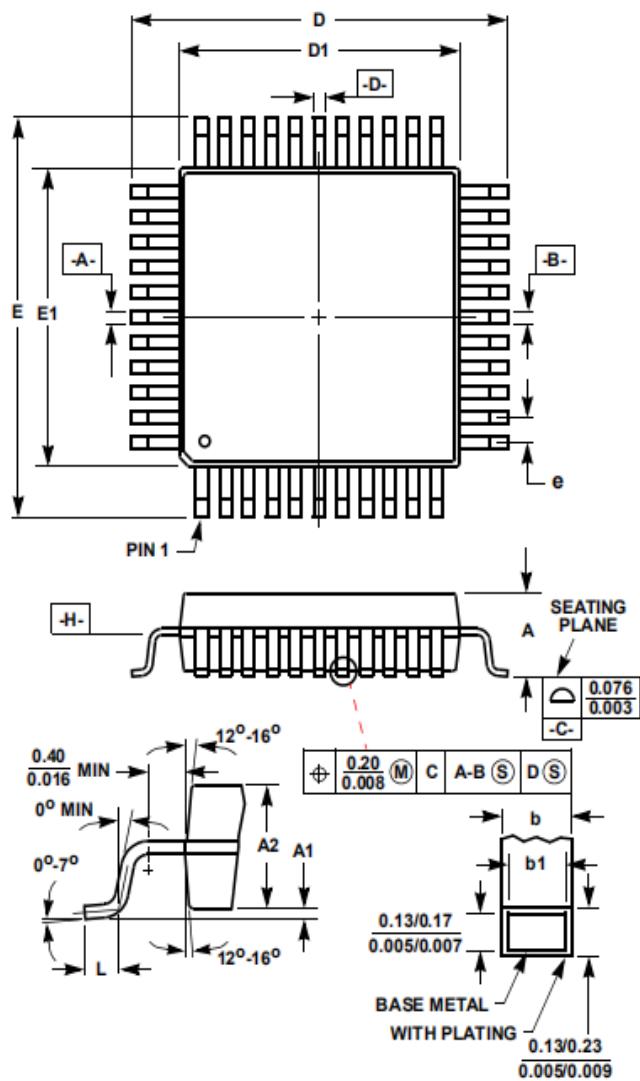

## 26.公制塑料四方扁平包装 ( MQFP )

| 符号 | 英寸        |       | 毫米       |       | 备注  |

|----|-----------|-------|----------|-------|-----|

|    | 最小值       | 最大值   | 最小值      | 最大值   |     |

| A  | -         | 0.096 | -        | 2.45  | -   |

| A1 | 0.004     | 0.010 | 0.10     | 0.25  | -   |

| A2 | 0.077     | 0.083 | 1.95     | 2.10  | -   |

| b  | 0.012     | 0.018 | 0.30     | 0.45  | 6   |

| b1 | 0.012     | 0.016 | 0.30     | 0.40  | -   |

| D  | 0.515     | 0.524 | 13.08    | 13.32 | 3   |

| D1 | 0.389     | 0.399 | 9.88     | 10.12 | 4,5 |

| E  | 0.516     | 0.523 | 13.10    | 13.30 | 3   |

| E1 | 0.390     | 0.398 | 9.90     | 10.10 | 4,5 |

| L  | 0.029     | 0.040 | 0.73     | 1.03  | -   |

| N  | 44        |       | 44       |       | 7   |

| e  | 0.032 BSC |       | 0.80 BSC |       | -   |

## 27.联系方式

启珑微电子（北京）有限公司

北京市海淀区稻香湖路绿地云谷科技中心7号楼4层

邮政编码： 100095

联系电话： +86-10-82466062 62106606

邮箱：[sales@chiplon.com](mailto:sales@chiplon.com)

技术支持：[support@chiplon.com](mailto:support@chiplon.com)

网址：[www.chiplon.com](http://www.chiplon.com)

**Copyright. Chiplon Microelectronics Co., Ltd. All rights are reserved.**

The information furnished by Chiplon is believed to be accurate and reliable. However, no responsibility is assumed for inaccuracies and specifications within this document are subject to change without notice. The material contained herein is the exclusive property of Chiplon and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Chiplon. Chiplon products are not authorized for use as critical components in life support devices or systems without express written approval of Chiplon. The Chiplon logo is a registered trademark of Chiplon Microelectronics Co., Ltd. All other names are the property of their respective owners.