## 具有热插拔、失效保护、 $\pm 16kV$ ESD 保护的 3.3V RS485 收发器

### 特性

- 真正的失效保护接收器 低功耗

- 关断模式

- DE 与  $\overline{RE}$  采用热插拔输入结构

- +3.3V 工作电压 总线上允许挂接多达 256 个收发器 具有摆率限制功能有助于实现无差错数距传输

- I/O 口采用增强型 ESD 保护

- ( $\pm 16kV$  IEC 61000-4-2 模型)

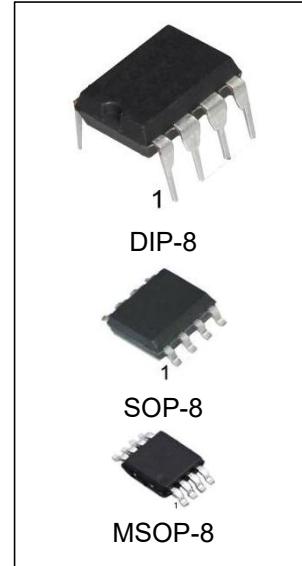

### 产品订购信息

| 产品名称             | 封装     | 打印名称    | 包装 | 包装数量     |

|------------------|--------|---------|----|----------|

| SN65HVD72ECN     | DIP-8  | HVD72EC | 管装 | 2000 只/盒 |

| SN65HVD75ECN     | DIP-8  | HVD75EC | 管装 | 2000 只/盒 |

| SN65HVD78ECN     | DIP-8  | HVD78EC | 管装 | 2000 只/盒 |

| SN65HVD72EIN     | DIP-8  | HVD72EI | 管装 | 2000 只/盒 |

| SN65HVD75EIN     | DIP-8  | HVD75EI | 管装 | 2000 只/盒 |

| SN65HVD78EIN     | DIP-8  | HVD78EI | 管装 | 2000 只/盒 |

| SN65HVD72ECM/TR  | SOP-8  | HVD72EC | 编带 | 2500 只/盘 |

| SN65HVD75ECM/TR  | SOP-8  | HVD75EC | 编带 | 2500 只/盘 |

| SN65HVD78ECM/TR  | SOP-8  | HVD78EC | 编带 | 2500 只/盘 |

| SN65HVD72EIM/TR  | SOP-8  | HVD72EI | 编带 | 2500 只/盘 |

| SN65HVD75EIM/TR  | SOP-8  | HVD75EI | 编带 | 2500 只/盘 |

| SN65HVD78EIM/TR  | SOP-8  | HVD78EI | 编带 | 2500 只/盘 |

| SN65HVD72ECMM/TR | MSOP-8 | D72EC   | 编带 | 3000 只/盘 |

| SN65HVD75ECMM/TR | MSOP-8 | D75EC   | 编带 | 3000 只/盘 |

| SN65HVD78ECMM/TR | MSOP-8 | D78EC   | 编带 | 3000 只/盘 |

| SN65HVD72EIMM/TR | MSOP-8 | D72EI   | 编带 | 3000 只/盘 |

| SN65HVD75EIMM/TR | MSOP-8 | D75EI   | 编带 | 3000 只/盘 |

| SN65HVD78EIMM/TR | MSOP-8 | D78EI   | 编带 | 3000 只/盘 |

## 概述

SN65HVD72/75/78E 是+3.3V 供电、具有 $\pm 16\text{kV}$  ESD 保护的 RS-485/RS-422 收发器。具有失效保护电路，当接收器输入开路或短路、或者挂接在终端匹配总线上的所有发送器都禁用时，接收器将输出逻辑高电平。全系列都具有热插拔功能，在上电或热插入时可以消除总线上的故障瞬变信号。

SN65HVD72/75E 具有低摆率驱，动器能够减小 EMI 和由于不恰当的终端匹配电缆所引起的反射，实现高达 500kbps 的无差错数据传输； SN65HVD78E 驱动器的摆率不受限制，可实现高达 16Mbps 的传输速率。

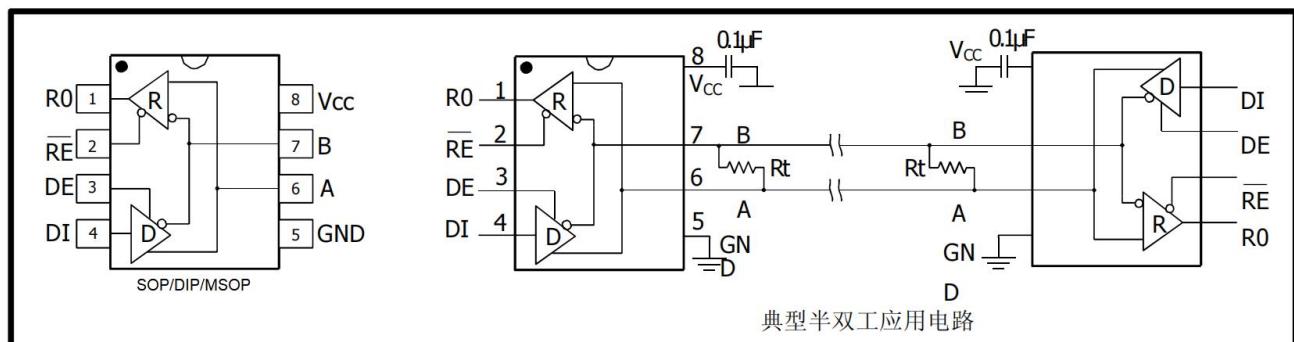

SN65HVD72/75/78E 用于半双工通信。

所有器件的接收器具有 1/8 单位负载输入阻抗，总线上可以挂接多达 256 个收发器。

采用 8 脚 DIP 和 8 脚 SOP 封装，这些器件可以提供商用级或工业级温度范围。

## 应用

- RS-422/RS-485 通讯

- 数字电表水表、工业控制、

- 工业嵌入电脑和外设、安防监控系统

- 路由器和交换机、仪器仪表、电平转换

- 对 EMI 敏感收发器应用

## 绝对最大额定值

| 参数                           | 符号           | 大小范围                          | 单位 |

|------------------------------|--------------|-------------------------------|----|

| 供应电压                         | VCC          | 6                             | V  |

| 控制输入电压                       | RE, DE       | -0.3 到 6                      | V  |

| 驱动器输入电压                      | DI           | -0.3 到 6                      | V  |

| 驱动器输出电压                      | A,B          | -7V 到 +12                     | V  |

| 接收器输入电压                      | A,B          | -7V 到 +12                     | V  |

| 接收器输出电压                      | RO           | -0.3 到 (V <sub>CC</sub> +0.3) | V  |

| 连续功耗 (T <sub>A</sub> =+70°C) | 8Plastic DIP | 725                           | mW |

|                              | 8SOP         | 500                           | mW |

| 工作温度范围                       | SN65HVDxxEC  | 0 到 +70                       | °C |

|                              | SN65HVDxxEI  | -40 到 +85                     | °C |

| 储存温度                         |              | -65 到 +150                    | °C |

| 引脚温度 (焊接 10s)                | TLEAD        | 260                           | °C |

注：任何高于绝对最大额定值的应用尝试都有可能对产品造成永久的损害，绝对最大额定值并不意味着产品会在标定的电气特性以外条件下正常工作。

## 直流电气特性

(如无另外说明, VCC=+3.3V±5%, TA=TMIN~TMAX, 典型值在 VCC=+3.3V, TA=25°C) (注释 1)

| 参数                    | 符号               | 条件                                             | 最小   | 典型                 | 最大   | 单位 |

|-----------------------|------------------|------------------------------------------------|------|--------------------|------|----|

| 驱动器                   |                  |                                                |      |                    |      |    |

| 电源电压                  | VCC              |                                                | 3.15 |                    | 3.45 | V  |

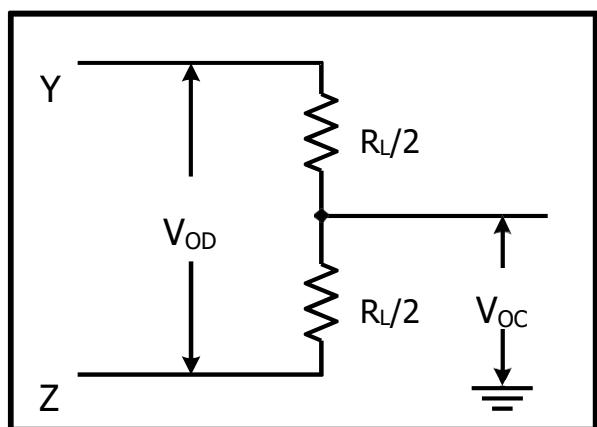

| 差分驱动器输出               | VOD              | 无负载                                            |      |                    | VCC  | V  |

|                       |                  | 图1, R <sub>L</sub> =100Ω (RS-422)              | 2    |                    | VCC  | V  |

|                       |                  | 图1, R <sub>L</sub> =54Ω (RS-485)               | 1.5  |                    | VCC  | V  |

| 差分驱动器输出电压的幅度变化 (注释 2) | ΔV <sub>OD</sub> | 图1, R <sub>L</sub> =100Ω 或 R <sub>L</sub> =54Ω |      |                    | 0.2  | V  |

| 驱动器共模输出电压             | V <sub>OC</sub>  | 图1, R <sub>L</sub> =100Ω 或 R <sub>L</sub> =54Ω |      | V <sub>CC</sub> /2 | 3    | V  |

| 共模电压的幅度变化 (注释 2)      | ΔV <sub>OC</sub> | 图1, R <sub>L</sub> =100Ω 或 R <sub>L</sub> =54Ω |      |                    | 0.2  | V  |

## 直流电气特性 (续)

(如无另外说明,  $V_{CC}=+3.3V \pm 5\%$ ,  $TA=T_{MIN} \sim T_{MAX}$ , 典型值在  $V_{CC}=+3.3V$ ,  $TA=25^{\circ}C$ ) (注释 1)

| 参数                       | 符号              | 条件                                        | 最小             | 典型   | 最大       | 单位          |

|--------------------------|-----------------|-------------------------------------------|----------------|------|----------|-------------|

| 驱动器 (续)                  |                 |                                           |                |      |          |             |

| 输入高电压                    | $V_{IH}$        | $DE, DI, \overline{RE}$                   | 2              |      |          | V           |

| 输入低电压                    | $V_{IL}$        | $DE, DI$                                  |                |      | 0.8      | V           |

| 输入迟滞                     | $V_{HYS}$       | $DE, DI, \overline{RE}$                   |                | 100  |          | mV          |

| 输入电流                     | $I_{IN}$        | $DE, DI, \overline{RE}$                   |                |      | $\pm 1$  | $\mu A$     |

| 输入电流 (A,B) 全双工           | $I_{A,}, I_B$   | $DE=GND, V_{CC}=GND$ 或 $V_{CC}$           | $V_{IN}=12V$   |      | 125      | $\mu A$     |

|                          |                 |                                           | $V_{IN}=-7V$   | -75  |          |             |

| 输出漏电流 (Y,Z) 全双工          | $I_O$           | $DE=GND$<br>$V_{CC}=GND$ 或 $V_{CC}$       | $V_{IN}=12V$   |      | 125      | $\mu A$     |

|                          |                 |                                           | $V_{IN}=-7V$   | -100 |          |             |

| 驱动器短路输出电流<br>(注释 3)      | $I_{OSD}$       | $0 \leq V_{OUT} \leq 12V$                 |                |      | 250      | $mA$        |

|                          |                 | $-7 \leq V_{OUT} \leq V_{CC}$             |                | -250 |          |             |

| 驱动器短路回馈限制输出<br>电流 (注释 3) | $I_{OSDF}$      | $V_{CC}-1V \leq V_{OUT} \leq V_{CC}+0.5V$ |                | 20   |          | $mA$        |

|                          |                 | $-0.5V \leq V_{OUT} \leq +1V$             |                |      | -20      | $mA$        |

| 热关断温度                    | $T_{TS}$        |                                           |                | 165  |          | $^{\circ}C$ |

| 热关断迟滞                    | $T_{TSH}$       |                                           |                | 15   |          | $^{\circ}C$ |

| 接收器                      |                 |                                           |                |      |          |             |

| 接收器差分阈值电压                | $V_{TH}$        | $-7V \leq V_{CM} \leq 12V$                | -200           | -125 | -50      | mV          |

| 接收器输入迟滞                  | $\Delta V_{TH}$ | $V_A + V_B = 0$                           |                | 15   |          | mV          |

| 接收器输出高压                  | $V_{OH}$        | $IO = -4mA, V_{ID} = 200mV$               | $V_{CC} - 0.6$ |      |          | V           |

| 接收器输出低压                  | $V_{OL}$        | $IO = 4mA, V_{ID} = -200mV$               |                |      | 0.4      | V           |

| 接收器端三态输出电流               | $I_{OZR}$       | $0 \leq V_O \leq V_{CC}$                  |                |      | $\pm 1$  | $\mu A$     |

| 接收器输入阻抗                  | $R_{IN}$        | $-7V \leq V_{CM} \leq 12V$                | 96             |      |          | $k\Omega$   |

| 接收器输出短路电流                | $I_{OSR}$       | $0V \leq V_{RO} \leq V_{CC}$              | $\pm 7$        |      | $\pm 95$ | $mA$        |

## 直流电气特性 (续)

(如无另外说明,  $V_{CC}=+3.3V\pm 5\%$ ,  $TA=TMIN\sim TMAX$ , 典型值在  $V_{CC}=+3.3V$ ,  $TA=25^\circ C$ ) (注释 1)

| 参数                 | 符号                | 条件                                                   |               | 最小  | 典型       | 最大   | 单位      |

|--------------------|-------------------|------------------------------------------------------|---------------|-----|----------|------|---------|

| 供应电流               |                   |                                                      |               |     |          |      |         |

| 供应电流               | I <sub>CC</sub>   | 无负载, $\overline{RE} = V_{CC}$<br>DI = GND 或 $V_{CC}$ | DE = $V_{CC}$ |     | 400      | 900  | $\mu A$ |

|                    |                   |                                                      | DE = GND      |     | 330      | 600  |         |

|                    |                   | 无负载, $\overline{RE} = GND$<br>DI = GND 或 $V_{CC}$    | DE = $V_{CC}$ |     | 400      | 1000 | $\mu A$ |

|                    |                   |                                                      | DE = GND      |     | 330      | 800  | $\mu A$ |

| 待机模式中的供应电流         | I <sub>SHDN</sub> | DE = GND, $\overline{RE} = V_{CC}$                   |               |     | 0.05     | 10   | $\mu A$ |

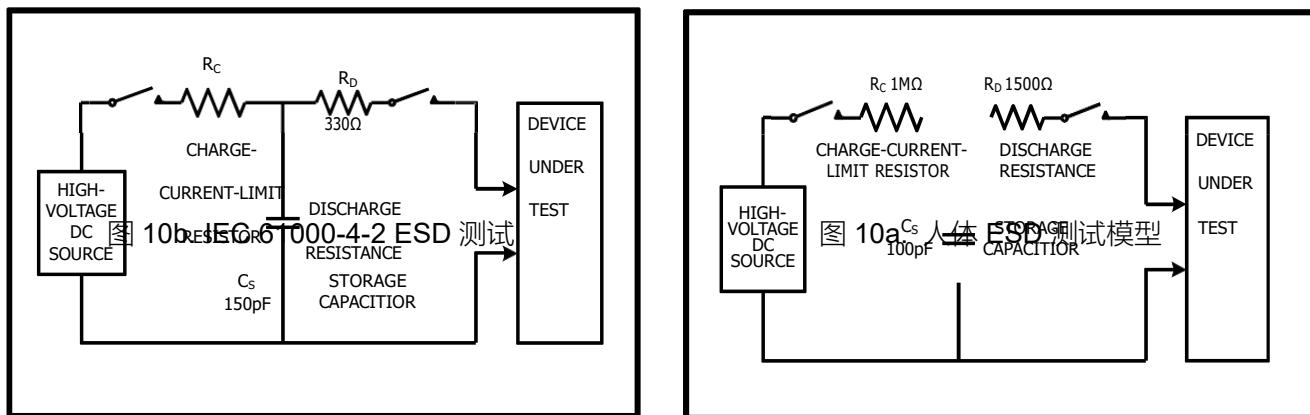

| 静电保护               |                   |                                                      |               |     |          |      |         |

| RS-485 管脚<br>(A、B) |                   | IEC61000-4-2                                         | 间隙放电          |     | $\pm 16$ |      | kV      |

|                    |                   |                                                      | 接触            | 半双工 | $\pm 16$ |      | kV      |

|                    |                   | HBM                                                  | 管脚到地          |     | $\pm 16$ |      | kV      |

注释 1: 进入器件的所有电流都是正的, 从器件输出的所有电流都是负的; 所有的电压, 如果无例外说明都是对地的。

注释 2: 当 DI 输入改变状态时,  $\Delta V_{OD}$  和  $\Delta V_{OC}$  分别为  $V_{OD}$  和  $V_{OC}$  变化。

注释 3: 最大电流是在回馈电流限制前的峰值电流, 短路回馈限制电流是总线竞争恢复期间的限制电流。

## 驱动器开关特性 SN65HVD72 (115kbps)

(如无另外说明,  $V_{CC}=+3.3V\pm 5\%$ ,  $TA=TMIN\sim TMAX$ , 典型值在  $V_{CC}=+3.3V$ ,  $TA=25^\circ C$ )

| 参数                                                        | 符号                              | 条件                                  | 最小  | 典型 | 最大        | 单位   |

|-----------------------------------------------------------|---------------------------------|-------------------------------------|-----|----|-----------|------|

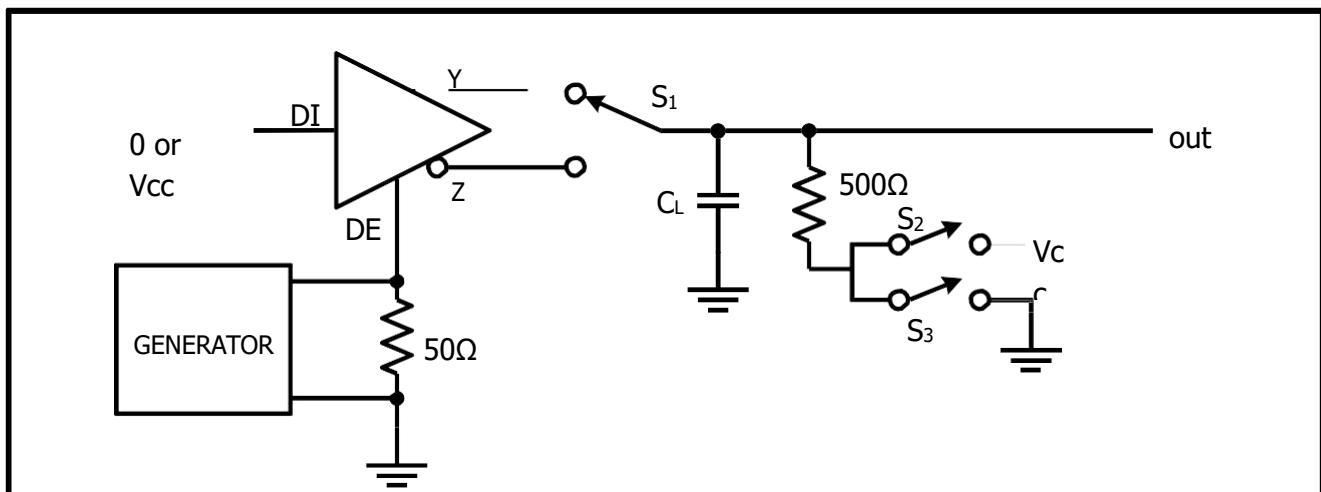

| 驱动器传输延迟                                                   | t <sub>DPLH</sub>               | 图2 和5, $R_L=54\Omega$<br>$C_L=50pF$ | 500 |    | 2600      | ns   |

|                                                           | t <sub>DPHL</sub>               |                                     | 500 |    | 2600      |      |

| 驱动器输出的上升和下降时间不对称度   t <sub>DPLH</sub> - t <sub>DPHL</sub> | t <sub>DSKEW</sub>              | 图2 和5, $R_L=54\Omega$<br>$C_L=50pF$ |     |    | $\pm 200$ | ns   |

| 驱动器上升或下降时间                                                | t <sub>DR</sub> t <sub>DF</sub> | 图2 和5, $R_L=54\Omega$<br>$C_L=50pF$ | 650 |    | 2500      | ns   |

| 最大数据速率                                                    | f <sub>MAX</sub>                |                                     | 115 |    |           | kbps |

| 驱动器使能到输出高                                                 | t <sub>DZH</sub>                | 图3 和6, $C_L=100pF$ , S3 闭合          |     |    | 3500      | ns   |

## 驱动器开关特性 SN65HVD72 (续)

(如无另外说明, VCC=+3.3V±5%, TA=TMIN~TMAX, 典型值在 VCC=+3.3V, TA=25°C)

| 参数            | 符号               | 条件                                  | 最小 | 典型  | 最大   | 单位 |

|---------------|------------------|-------------------------------------|----|-----|------|----|

| 驱动器使能到输出低     | $t_{DZL}$        | 图3 和6, $C_L = 100\text{pF}$ , S2 闭合 |    |     | 3500 | ns |

| 从低到驱动器无效时间    | $t_{DLZ}$        | 图3 和6, $C_L = 15\text{pF}$ S2 闭合    |    |     | 100  | ns |

| 从高到驱动器无效时间    | $t_{DHZ}$        | 图3 和6, $C_L = 15\text{pF}$ S3 闭合    |    |     | 100  | ns |

| 从待机到输出高的驱动器使能 | $t_{DZH}$ (SHDN) | 图3 和6, $C_L = 15\text{pF}$ S3 闭合    |    |     | 5500 | ns |

| 从待机到输出低的驱动器使能 | $t_{DZL}$ (SHDN) | 图3 和6, $C_L = 15\text{pF}$ S2 闭合    |    |     | 5500 | ns |

| 待机时间          | $t_{SHDN}$       | 注释4                                 | 50 | 350 | 700  | ns |

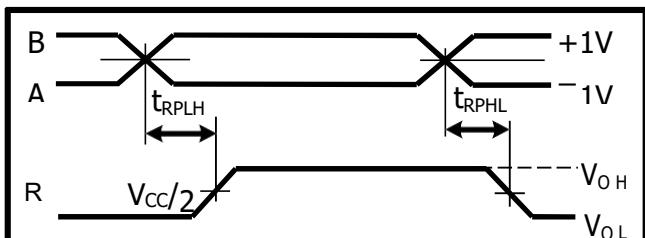

## 接收器开关特性 SN65HVD72 (115kbps)

(如无另外说明, VCC=+3.3V±5%, TA=TMIN~TMAX, 典型值在 VCC=+3.3V, TA=25°C)

| 参数                                          | 符号                       | 条件                                                                                     | 最小  | 典型 | 最大   | 单位   |

|---------------------------------------------|--------------------------|----------------------------------------------------------------------------------------|-----|----|------|------|

| 接收器传输延迟                                     | $t_{RPLH}$<br>$t_{RPHL}$ | 图7 和8, $C_L = 15\text{pF}$   $V_{ID}$   $\geq 2.0\text{V}$ , $V_{ID} \leq 15\text{ns}$ |     |    | 200  | ns   |

| 差分接收器输出的上升和下降时间不对称度   $t_{DPLH} - t_{DPHL}$ | $t_{RSKEW}$              | 图7 和8, $C_L = 15\text{pF}$   $V_{ID}$   $\geq 2.0\text{V}$ , $V_{ID} \leq 15\text{ns}$ |     |    | ±30  | ns   |

| 最大数据速率                                      | $f_{MAX}$                |                                                                                        | 115 |    |      | kbps |

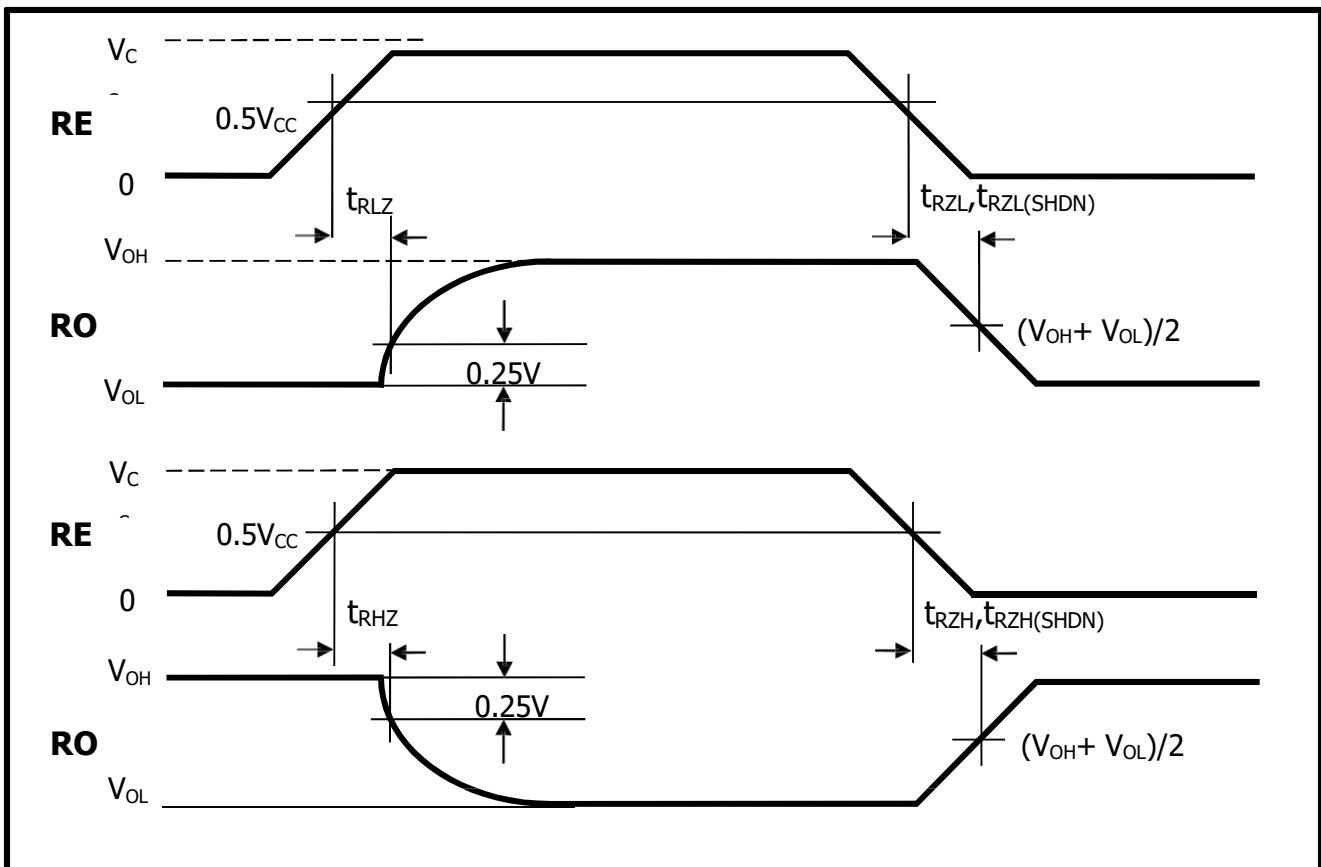

| 接收器使能到输出低                                   | $t_{RZL}$                | 图 4 和 9, S1=-1.5V, S2 接 VCC                                                            |     |    | 50   | ns   |

| 接收器使能到输出高                                   | $t_{RZH}$                | 图 4 和 9 S1=+1.5V, S2 接 GND                                                             |     |    | 50   | ns   |

| 接收器从低到无效时间                                  | $t_{RLZ}$                | 图4 和9 S1=-1.5V, S2 接VCC                                                                |     |    | 50   | ns   |

| 接收器从高到无效时间                                  | $t_{RHZ}$                | 图 4 和 9 S1=+1.5V, S2 接 GND                                                             |     |    | 50   | ns   |

| 从待机到输出高的接收器使能                               | $t_{RZH}$ (SHDN)         | 图4 和9 S1=-1.5V, S2 接VCC                                                                |     |    | 5500 | ns   |

| 从待机到输出低的接收器使能                               | $t_{RZL}$ (SHDN)         | 图 4 和 9 S1=+1.5V, S2 接 GND                                                             |     |    | 5500 | ns   |

| 待机时间                                        | $t_{SHDN}$               | 注释4                                                                                    | 50  |    | 700  | ns   |

注释 4: 参考详细说明中的低功耗关断模式

## 驱动器开关特性 SN65HVD75 (500kbps)

(如无另外说明, VCC=+3.3V±5%, TA=TMIN~TMAX, 典型值在 VCC=+3.3V, TA=25°C)

| 参数                                        | 符号                  | 条件                                         | 最小  | 典型 | 最大   | 单位   |

|-------------------------------------------|---------------------|--------------------------------------------|-----|----|------|------|

| 驱动器传输延迟                                   | $t_{DPLH}$          | 图2 和5, $R_L=54\Omega$<br>$C_L=50\text{pF}$ | 200 |    | 1000 | ns   |

|                                           | $t_{DPHL}$          |                                            | 200 |    | 1000 |      |

| 驱动器输出的上升和下降时间不对称度 $ t_{DPLH} - t_{DPHL} $ | $t_{DSKEW}$         | 图2 和5, $R_L=54\Omega$<br>$C_L=50\text{pF}$ |     |    | ±140 | ns   |

| 驱动器上升或下降时间                                | $t_{DR}$ $t_{DF}$   | 图2 和5, $R_L=54\Omega$<br>$C_L=50\text{pF}$ | 250 |    | 900  | ns   |

| 最大数据速率                                    | $f_{MAX}$           |                                            | 500 |    |      | kbps |

| 驱动器使能到输出高                                 | $t_{DZH}$           | 图3 和6, $C_L=100\text{pF}$ , S3 闭合          |     |    | 2500 | ns   |

| 驱动器使能到输出低                                 | $t_{DZL}$           | 图3 和6, $C_L=100\text{pF}$ , S2 闭合          |     |    | 2500 | ns   |

| 从低到驱动器无效时间                                | $t_{DLZ}$           | 图3 和6, $C_L=15\text{pF}$ S2 闭合             |     |    | 100  | ns   |

| 从高到驱动器无效时间                                | $t_{DHZ}$           | 图3 和6, $C_L=15\text{pF}$ S3 闭合             |     |    | 100  | ns   |

| 从待机到输出高的驱动器使能                             | $t_{DZH}$<br>(SHDN) | 图3 和6, $C_L=15\text{pF}$ S3 闭合             |     |    | 5500 | ns   |

| 从待机到输出低的驱动器使能                             | $t_{DZL}$<br>(SHDN) | 图3 和6, $C_L=15\text{pF}$ S2 闭合             |     |    | 5500 | ns   |

| 待机时间                                      | $t_{SHDN}$          |                                            | 50  |    | 700  | ns   |

## 接收器开关特性 SN65HVD75 (500kbps)

(如无另外说明, VCC=+3.3V±5%, TA=TMIN~TMAX, 典型值在 VCC=+3.3V, TA=25°C)

| 参数                                          | 符号                       | 条件                                                                               | 最小  | 典型 | 最大   | 单位   |

|---------------------------------------------|--------------------------|----------------------------------------------------------------------------------|-----|----|------|------|

| 接收器传输延迟                                     | $t_{RPLH}$<br>$t_{RPHL}$ | 图7 和8, $C_L=15\text{pF}$ $ V_{ID}  \geq 2.0\text{V}$ , $V_{ID} \leq 15\text{ns}$ |     |    | 200  | ns   |

| 差分接收器输出的上升和下降时间不对称度 $ t_{DPLH} - t_{DPHL} $ | $t_{RSKEW}$              | 图7 和8, $C_L=15\text{pF}$ $ V_{ID}  \geq 2.0\text{V}$ , $V_{ID} \leq 15\text{ns}$ |     |    | ±30  | ns   |

| 最大数据速率                                      | $f_{MAX}$                |                                                                                  | 500 |    |      | kbps |

| 接收器使能到输出低                                   | $t_{RZL}$                | 图4 和9, S1=-1.5V, S2 接VCC                                                         |     |    | 50   | ns   |

| 接收器使能到输出高                                   | $t_{RZH}$                | 图4 和9 S1=+1.5V, S2 接 GND                                                         |     |    | 50   | ns   |

| 接收器从低到无效时间                                  | $t_{RLZ}$                | 图4 和9 S1=-1.5V, S2 接VCC                                                          |     |    | 50   | ns   |

| 接收器从高到无效时间                                  | $t_{RHZ}$                | 图4 和9 S1=+1.5V, S2 接 GND                                                         |     |    | 50   | ns   |

| 从待机到输出高的接收器使能                               | $t_{RZH}$ (SHDN)         | 图4 和9 S1=-1.5V, S2 接VCC                                                          |     |    | 5500 | ns   |

| 从待机到输出低的接收器使能                               | $t_{RZL}$ (SHDN)         | 图4 和9 S1=+1.5V, S2 接 GND                                                         |     |    | 5500 | ns   |

| 待机时间                                        | $t_{SHDN}$               |                                                                                  | 50  |    | 700  | ns   |

## 驱动器开关特性 SN65HVD78 (16Mbps)

(如无另外说明, VCC=+3.3V±5%, TA=TMIN~TMAX, 典型值在 VCC=+3.3V, TA=25°C)

| 参数                                      | 符号                  | 条件                                  | 最小 | 典型  | 最大   | 单位   |

|-----------------------------------------|---------------------|-------------------------------------|----|-----|------|------|

| 驱动器传输延迟                                 | $t_{DPLH}$          | 图2 和5, $R_L=54\Omega$<br>$C_L=50pF$ |    |     | 50   | ns   |

|                                         | $t_{DPHL}$          |                                     |    |     | 50   |      |

| 驱动器输出的上升和下降时间不对称度 $ t_{DPLH}-t_{DPHL} $ | $t_{DSKEW}$         | 图2 和5, $R_L=54\Omega$<br>$C_L=50pF$ |    |     | 10   | ns   |

| 驱动器上升或下降时间                              | $t_{DR}$ $t_{DF}$   | 图2 和5, $R_L=54\Omega$<br>$C_L=50pF$ |    |     | 20   | ns   |

| 最大数据速率                                  | $f_{MAX}$           |                                     | 16 |     |      | Mbps |

| 驱动器使能到输出高                               | $t_{DZH}$           | 图3 和6, $C_L=100pF$ , S3 闭合          |    |     | 150  | ns   |

| 驱动器使能到输出低                               | $t_{DZL}$           | 图3 和6, $C_L=100pF$ , S2 闭合          |    |     | 150  | ns   |

| 从低到驱动器无效时间                              | $t_{DLZ}$           | 图3 和6, $C_L=15pF$ S2 闭合             |    |     | 100  | ns   |

| 从高到驱动器无效时间                              | $t_{DHZ}$           | 图3 和6, $C_L=15pF$ S3 闭合             |    |     | 100  | ns   |

| 从待机到输出高的驱动器使能                           | $t_{DZH}$<br>(SHDN) | 图3 和6, $C_L=15pF$ S3 闭合             |    |     | 2200 | ns   |

| 从待机到输出低的驱动器使能                           | $t_{DZL}$<br>(SHDN) | 图3 和6, $C_L=15pF$ S2 闭合             |    |     | 2200 | ns   |

| 待机时间                                    | $t_{SHDN}$          |                                     | 50 | 350 | 700  | ns   |

## 接收器开关特性 SN65HVD78 (16Mbps)

(如无另外说明, VCC=+3.3V±5%, TA=TMIN~TMAX, 典型值在 VCC=+3.3V, TA=25°C) (注释 1)

| 参数                                        | 符号                       | 条件                                                           | 最小 | 典型  | 最大   | 单位   |

|-------------------------------------------|--------------------------|--------------------------------------------------------------|----|-----|------|------|

| 接收器传输延迟                                   | $t_{RPLH}$<br>$t_{RPHL}$ | 图7 和8, $C_L=15pF$   $V_{ID}  \geq 2.0V$ , $V_{ID} \leq 15ns$ |    |     | 50   | ns   |

| 差分接收器输出的上升和下降时间不对称度 $ t_{DPLH}-t_{DPHL} $ | $t_{RSKEW}$              | 图7 和8, $C_L=15pF$   $V_{ID}  \geq 2.0V$ , $V_{ID} \leq 15ns$ |    |     | 20   | ns   |

| 最大数据速率                                    | $f_{MAX}$                |                                                              | 16 |     |      | Mbps |

| 接收器使能到输出低                                 | $t_{RZL}$                | 图4 和9, S1=-1.5V, S2 接VCC                                     |    |     | 50   | ns   |

| 接收器使能到输出高                                 | $t_{RZH}$                | 图4 和9 S1=+1.5V, S2 接 GND                                     |    |     | 50   | ns   |

| 接收器从低到无效时间                                | $t_{RLZ}$                | 图4 和9 S1=-1.5V, S2 接VCC                                      |    |     | 50   | ns   |

| 接收器从高到无效时间                                | $t_{RHZ}$                | 图4 和9 S1=+1.5V, S2 接 GND                                     |    |     | 50   | ns   |

| 从待机到输出高的接收器使能                             | $t_{RZH}$ (SHDN)         | 图4 和9, S1=-1.5V, S2 接VCC                                     |    |     | 2200 | ns   |

| 从待机到输出低的接收器使能                             | $t_{RZL}$ (SHDN)         | 图4 和9 S1=+1.5V, S2 接 GND                                     |    |     | 2200 | ns   |

| 待机时间                                      | $t_{SHDN}$               |                                                              | 50 | 350 | 700  | ns   |

## 测试电路和时序图

(如无另外说明,  $VCC = +3.3V$ ,  $TA = +25^{\circ}C$ )

图 1. 驱动器 DC 测试负载

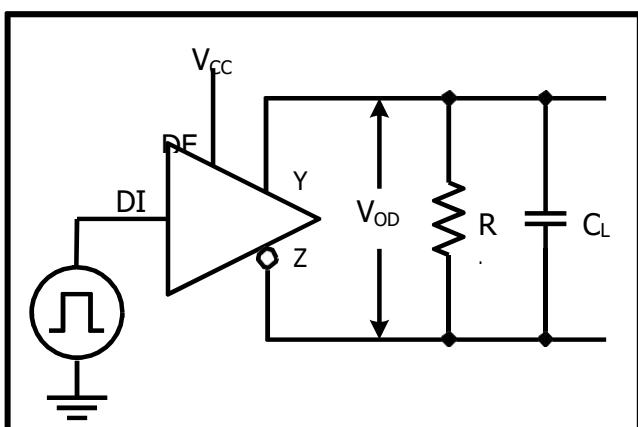

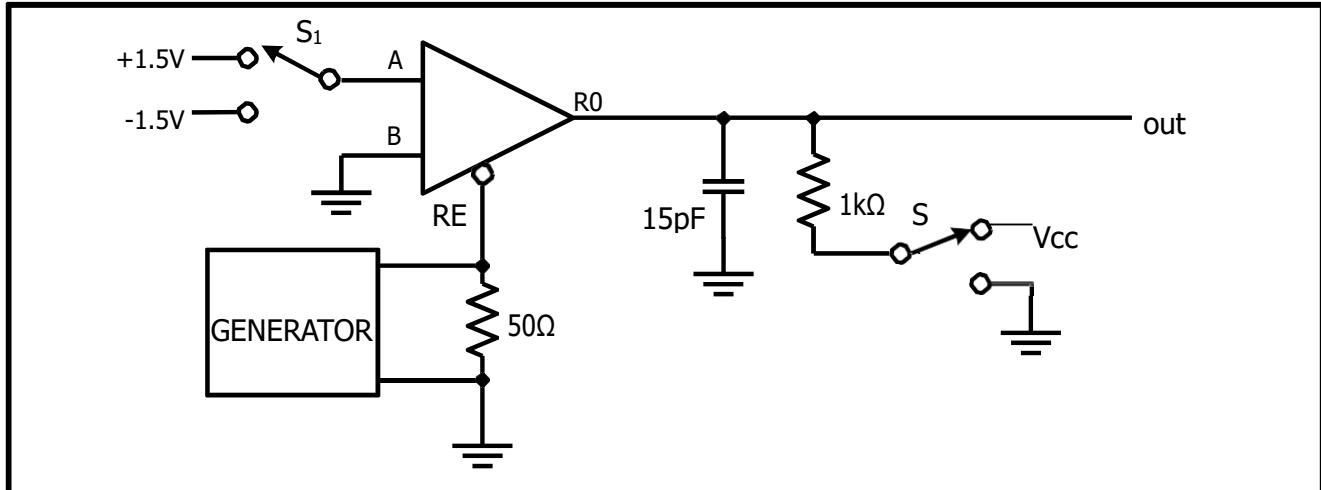

图 2. 驱动器时序测试电路

图3.驱动器使能和禁用测试电路

图 4. 接收器使能和禁用测试电路

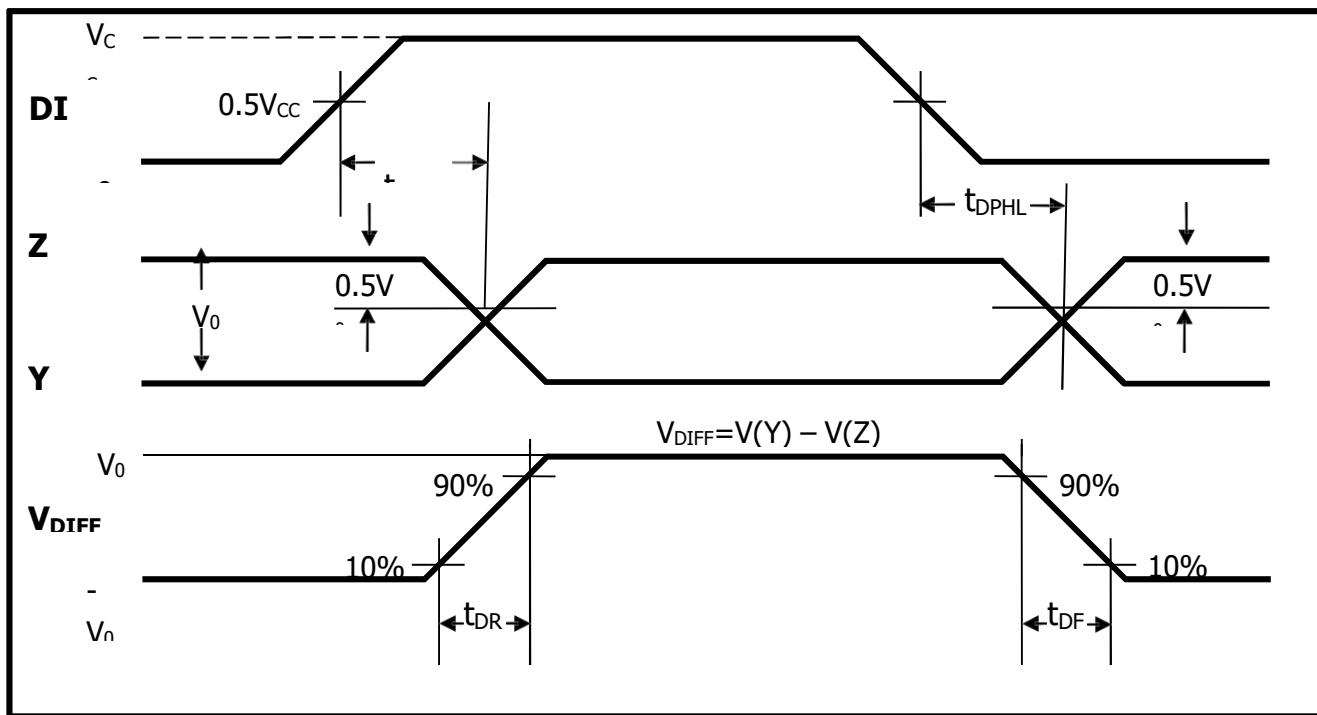

图 5. 驱动器传输延时

图 6. 驱动器使能和禁用时序( $t_{DHZ}$ 、 $t_{DZH}$ 、 $t_{DZH}(\text{SHDN})$ 、 $t_{DZL}$ 、 $t_{DLZ}$ 、 $t_{DLZ}(\text{SHDN})$ )

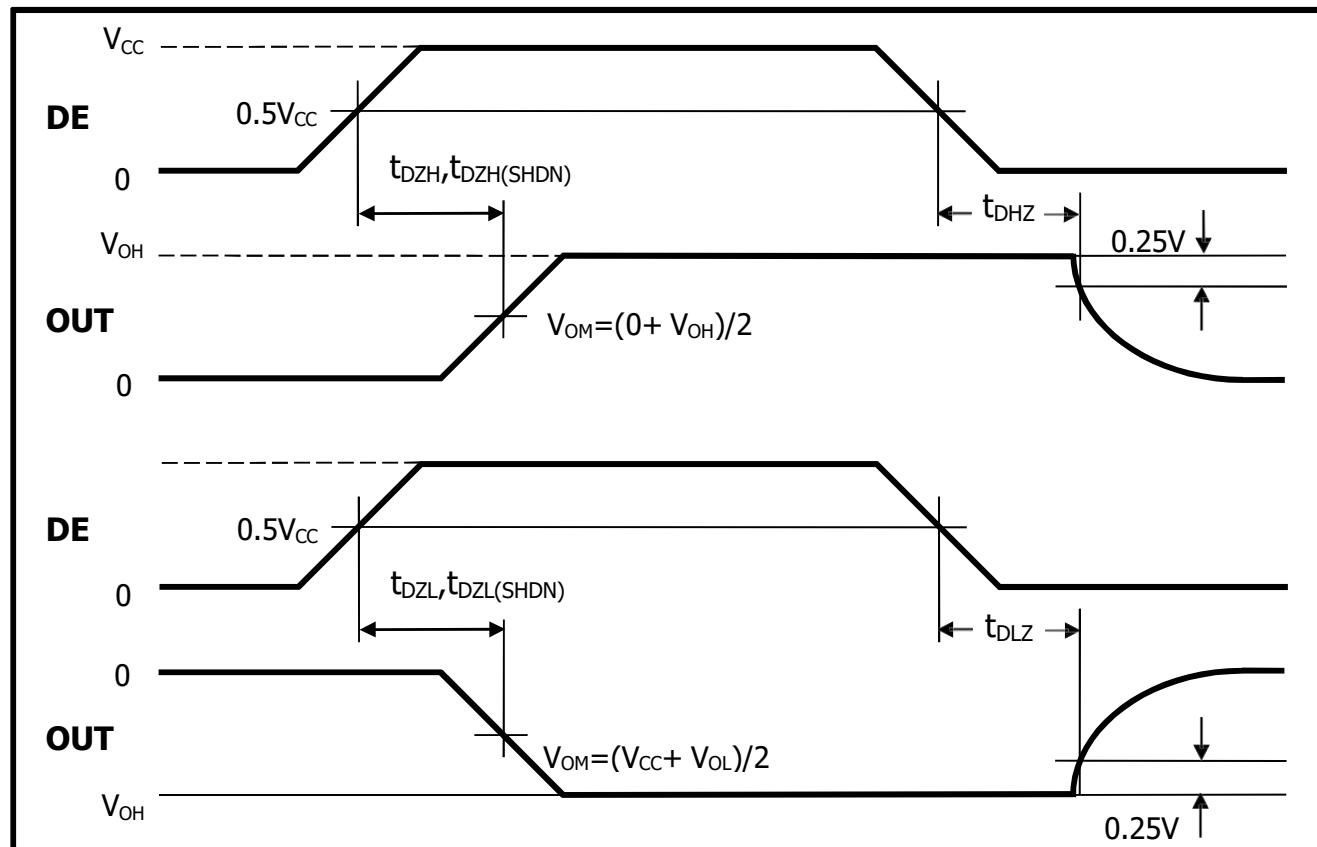

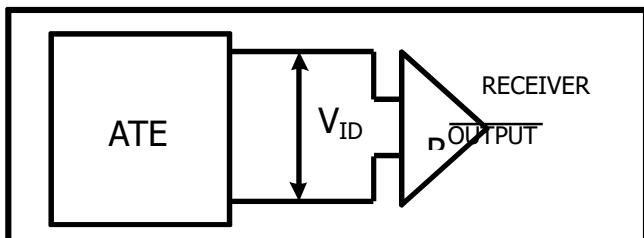

图 7. 接收器传输延时测试电路

图 8. 接收器传输延时

图 9. 接收器使能和禁用时序

## 引脚说明

| 引脚 | 名称              | 功能                                                                                                                                            |

|----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | RO              | 接收器输出: 当 $\overline{RE}$ 为低电平时, 如 (A-B) 不小于 200mV, 则 RO 输出高电平; 如(A-B) 不大于 -200mV, 则 RO 输出低电平。                                                 |

| 2  | $\overline{RE}$ | 接收器输出使能: 当 $\overline{RE}$ 为低电平时 RO 有效; $RE$ 为高电平时 RO 为高阻态。 $\overline{RE}$ 为高电平时 DE 为低电平, 器件进入低功耗关断模式。 $\overline{RE}$ 采用热插拔输入结构(请参考热插拔功能部分) |

| 3  | DE              | 驱动器输出使能: DE 为高电平时驱动器输出有效。 DE 为低电平时输出高阻态。 $\overline{RE}$ 为高电平时 DE 为低电平, 器件进入低功耗关断模式。 DE 采用热插拔输入结构(请参考热插拔功能部分)。                                |

| 4  | DI              | 驱动器输入: DE 为高电平时, DI 上的低电平使输出 A 为低电平, 输出 B 为高电平。类似的, DI 上的高电平使输出 A 为高电平, 输出 B 为低电平。                                                            |

| 5  | GND             | 地                                                                                                                                             |

| 6  | A               | 接收器同相输入端和驱动器同相输出端                                                                                                                             |

| 7  | B               | 接收器反相输入端和驱动器反相输出端                                                                                                                             |

| 8  | VCC             | 正电源: $3.15V \leq V_{CC} \leq 3.45V$ 。连 $0.1\mu F$ 电容接地。                                                                                       |

## 功能表

SN65HVD72/75/78E

| 传输              |    |    |          |     | 接收              |    |               |          |  |

|-----------------|----|----|----------|-----|-----------------|----|---------------|----------|--|

| 输入              |    |    | 输出       |     | 输入              |    |               | 输出       |  |

| $\overline{RE}$ | DE | DI | B        | A   | $\overline{RE}$ | DE | A - B         | RO       |  |

| X               | 1  | 1  | 0        | 1   | 0               | X  | $\geq -50mV$  | 1        |  |

|                 |    |    |          |     |                 |    | $\leq -200mV$ | 0        |  |

| X               | 1  | 0  | 1        | 0   | 0               | X  | Open/Shorted  | 1        |  |

| 0               | 0  | X  | 高阻抗      | 高阻抗 | 1               | 1  | X             | 高阻抗      |  |

| 1               | 0  | X  | Shutdown |     | 1               | 0  | X             | Shutdown |  |

## 详细说明

SN65HVD72/75/78 系列高速 RS-485/RS-422 收发器包括一路驱动器和一路接收器。这些器件具有失效保护电 (路参考失效保护部分)。SN65HVD72/75/78 具有热插拔功能，支持热插入而不会产生数据传输错误 (参考热插拔功 能部分)。SN65HVD72/75 的低摆率驱动器可降低 EMI，并减小由不恰当的端接电缆引起的反射，能够实现最大 500kbps 的无差错数据传输；SN65HVD78 的驱动器摆率不受限制，能够实现最大 16Mbps 的传输速率；所有器件均采用 +3.3V 单电源供电。驱动器具有输出短路限流功能。热关断电路保护驱动器不会出现功耗过大。进入热关断保护后，驱动器输出被置于高阻态。

## 接收器输入滤波

SN65HVD72/75 接收器具有输入滤波功能。此滤波功能提高了上升和下降缓慢的差分信号的噪声抑制能力。滤波器使接收器传输延时增加 25%。

## 热插拔功能

把电路板插入带电或正在工作的背板时 (热插拔输入)，数据总线的差分干扰可能导致数据错误。电路板插入背板时，数据通信处理器启动一次上电过程。在此过程中，处理器的逻辑输出驱动器为高阻态，不能将这些器件的 DE 和 RE 输入 驱动至规定的逻辑电平。处理器的逻辑驱动器在高阻态时可能会有高达  $\pm 10\mu A$  的漏电流，这会引起收发器的标准 CMOS 使能输入漂移到不正确的逻辑电平。此外，电路板寄生电容还会将 VCC 或者 GND 耦合至使能输入端。如果不具备热插拔 能力，以上因素会错误地使能收发器的驱动器或接收器。SN65HVD72/75/78 的热插拔功能保证在 VCC 上升时，内部路电保持 RE 为低电平，RE 为高电平。在完成初始上电过程后，下拉电路将不再起作用，并复位热插拔输入端。

## ±16kV ESD 保护

类似于铭芯的其它相关器件，所有引脚都采用了 ESD 保护结构，在操作与装配过程中出现静电放电时可对器件提供保护。SN65HVD72/75/78 系列产品的驱动器输出与接收器输入具有额外的静电保护能力。铭芯的工程师们已开发出专用的电路结构，为这些引脚提供保护，使其能够承受 IEC 61000-4-2 模型±16kV 的 ESD 冲击。ESD 保护结构在各种状态下都可承受高 ESD 冲击，包括标准工作模式、关断和断电模式。ESD 保护可以采用不同方法进行测试。SN65HVD72/75/78 的发送器输出与接收器输入在以下条件下进行了保护测试：

- ±16kV, HBM 人体模型。

- ±16kV, IEC 61000-4-2 规定的间隙放电方法。

- ±16kV, IEC 61000-4-2 规定的接触放电方法。

## 失效保护

接收器输入短路或开路时，或挂接在终端匹配传输线上的所有驱动器均处于禁用状态时，SN65HVD72/75/78 系列可确保接收器输出逻辑高电平。这是通过将接收器输入门限分别设置为 -50mV 和 -200mV 来实现的。若差分接收器输入电压 (A - B) 大于或等于 -50mV, RO 为逻辑高电平；若电压 (A - B) 小于或等于 -200mV, RO 为逻辑低电平。当挂接在终端匹配总线上的所有发送器都禁用时，接收器差分输入电压将通过终端电阻拉至 0V。

依据 SN65HVD72/75/78 系列的接收器门限，可实现具有 50 mV 最小噪声容限的逻辑高电平。-50 mV 至-200mV 门限电压符合±200mV 的 EIA/ TIA-485 标准。

## 应用信息

### 总线上挂接 256 个收发器

标准 RS-485 接收器的输入阻抗为  $12\text{k}\Omega$  (1 个单位负载), 标准驱动器可最多驱动 32 个单位负载。SN65HVD72/75/78 系列收发器的接收器具有  $1/8$  单位负载输入阻抗( $96\text{k}\Omega$ ), 允许最多 256 个收发器并行挂接在同一通信总 线上。这些器件可任意组合, 或与其它 RS-485 收发器进行 组合, 只要总负载不超过 32 个单位负载, 都可以挂接在同 一总线上。

### 降低 EMI 和反射

SN65HVD72 的低摆率驱动器可以减小 EMI , 并降低由不恰当的终端匹配电缆引起的反射, 可实现最大  $115\text{kbps}$  的无差错数据传输, SN65HVD75 提供较高的驱动器输出摆率, 可实现 高达  $500\text{kbps}$  的传输速率。

### 低功耗关断模式

RE 接高电平且 DE 接低电平时, 启动低功耗关断模式。关断模式下, 器件仅吸收典型值为  $0.05\mu\text{A}$  的电源电流。如果 RE 为高电平且 DE 为低电平的持续时间小于  $50\text{ns}$ , 可以确保器件不会进入关断模式。如果输入端维持这种状态  $700\text{ns}$  以上, 则可确保这些器件进入关断模式。使能时间  $t_{ZH}$  与  $t_{ZL}$ (见开关部分)假定器件并未处于低功耗关断状态。使能时间  $t_{ZH}(\text{SHDN})$ 与  $t_{ZL}(\text{SHDN})$ 假定器件处于关断状态。从低功耗关断模式到驱动器和接收器转变为有效状态所需要的时间( $t_{ZH}(\text{SHDN})$ 、  $t_{ZL}(\text{SHDN})$ ), 要比从禁用模式下转 变为有效状态所需要的时间( $t_{ZH}$ 、  $t_{ZL}$ )长。驱动器输出保护 通过两种机制避免故障或总线冲突引起输出电流过大和功耗过高。第一, 输出短路反向限流, 在整个共模电压范围(参考典型工作特性)内提供快速短路保护。第二, 热关断电路, 当管芯温度超过  $+165^\circ\text{C}$  (典型值)时, 强制驱动器输出进入高阻状态。

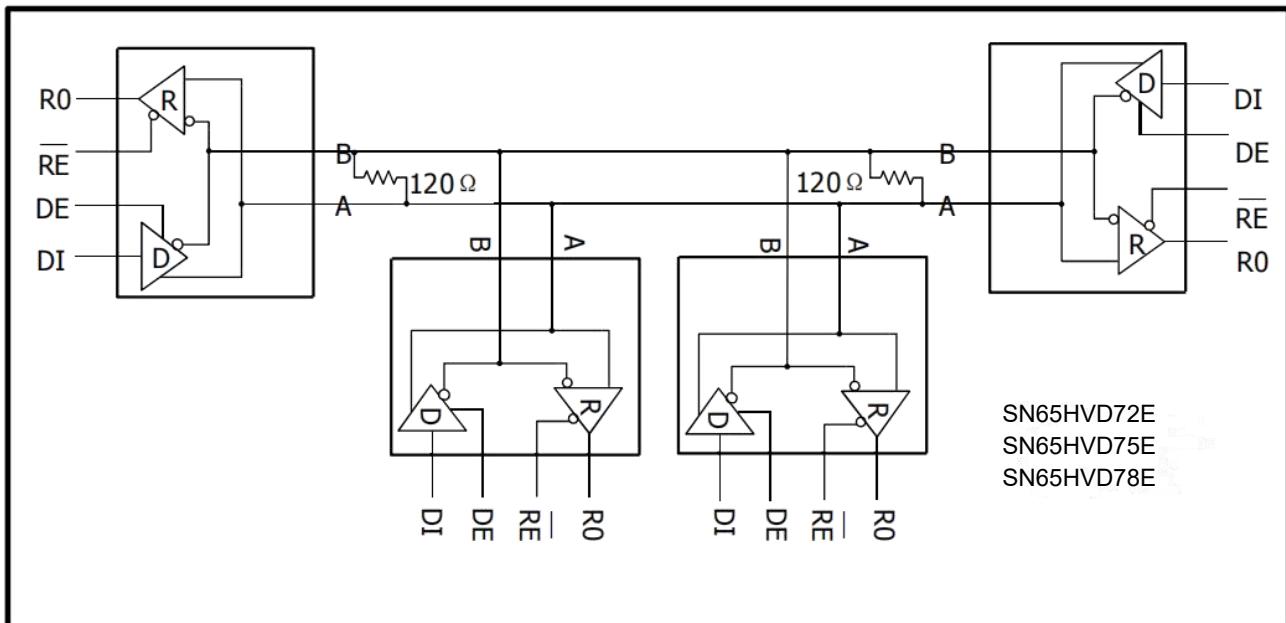

### 典型应用

SN65HVD72/75/78 收发器设计用于多点总线传输线上的双向数据通信。图 11 给出了典型网络应用电路。为减小反射, 应当在传输线两端以其特性阻抗进行终端匹配, 主干线以外的分支连线长度应尽可能短, 具有摆率限制的 SN65HVD72/75 能够允许不良终端匹配。

RS-485/RS-422 标准适用于最大 4000 英尺的线路长度。

图 11. 典型半双工模式下 RS485 网络

## 引脚配置和典型工作电路

## 选型指南

| 型号         | 双工  | 数据速率 | 摆率限制 | 低功耗关断 | 收发器使能 | 总线上的传输器数 | 管脚数 |

|------------|-----|------|------|-------|-------|----------|-----|

| SN65HVD72E | 半双工 | 115K | √    | √     | √     | 256      | 8   |

| SN65HVD75E | 半双工 | 500K | √    | √     | √     | 256      | 8   |

| SN65HVD78E | 半双工 | 16M  |      | √     | √     | 256      | 8   |

## 封装外形尺寸

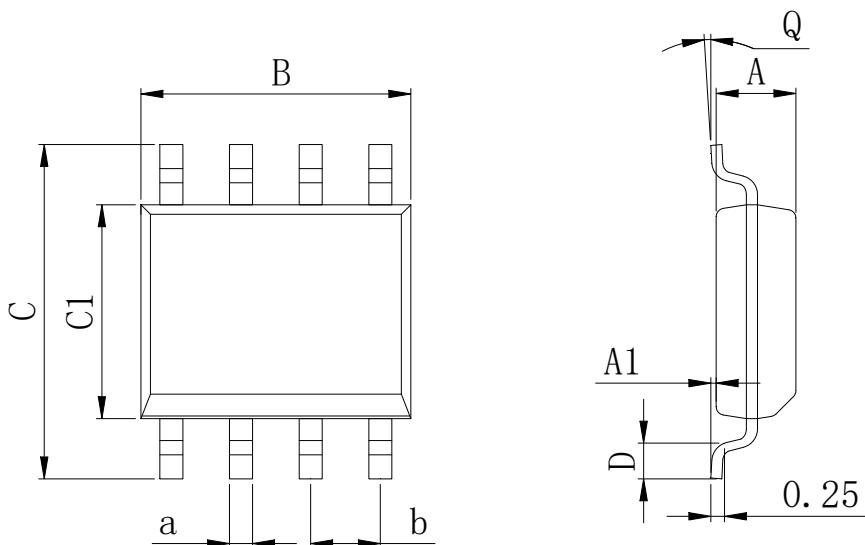

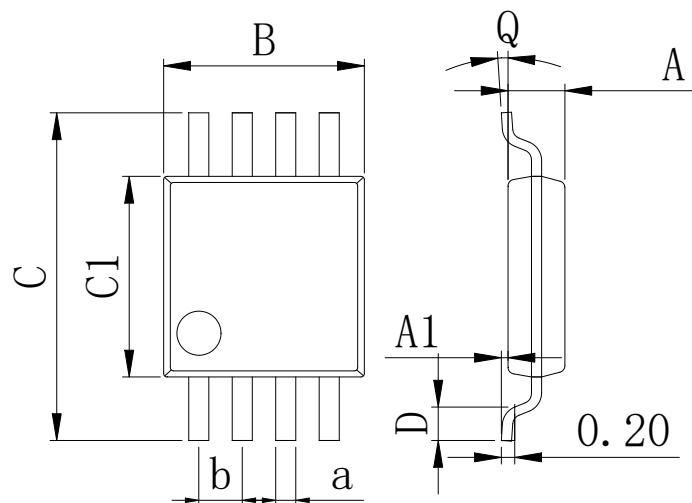

SOP-8

Dimensions In Millimeters(SOP-8)

| Symbol:     | A    | A1   | B    | C    | C1   | D    | Q  | a    | b        |

|-------------|------|------|------|------|------|------|----|------|----------|

| <b>Min:</b> | 1.35 | 0.05 | 4.90 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.27 BSC |

| <b>Max:</b> | 1.55 | 0.20 | 5.10 | 6.20 | 4.00 | 0.80 | 8° | 0.45 |          |

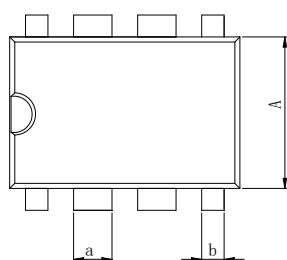

DIP-8

Dimensions In Millimeters(DIP-8)

| Symbol:     | A    | B    | D    | D1   | E    | L    | L1   | a    | b    | c    | d        |

|-------------|------|------|------|------|------|------|------|------|------|------|----------|

| <b>Min:</b> | 6.10 | 9.00 | 8.10 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 2.54 BSC |

| <b>Max:</b> | 6.68 | 9.50 | 10.9 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 |          |

封装外形尺寸

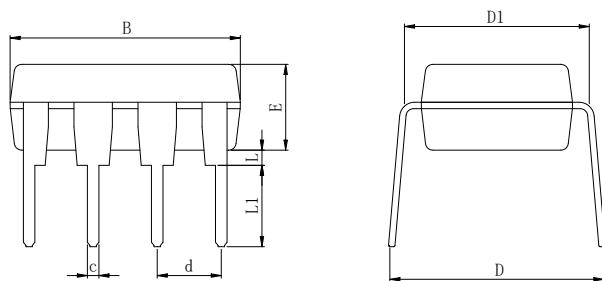

MSOP-8

Dimensions In Millimeters(MSOP-8)

| Symbol: | A    | A1   | B    | C    | C1   | D    | Q  | a    | b        |

|---------|------|------|------|------|------|------|----|------|----------|

| Min:    | 0.80 | 0.05 | 2.90 | 4.75 | 2.90 | 0.35 | 0° | 0.25 | 0.65 BSC |

| Max:    | 0.90 | 0.20 | 3.10 | 5.05 | 3.10 | 0.75 | 8° | 0.35 |          |

## 修订历史

| 日期        | 修改内容             | 页码     |

|-----------|------------------|--------|

| 2019-8-15 | 新修订              | 1-20   |

| 2023-8-28 | 更新封装、更新 DIP-8 尺寸 | 1、3、17 |

| 2024-11-8 | 更新引脚焊接温度         | 3      |

## 重要声明：

华冠半导体保留未经通知更改所提供的产品和服务。客户在订货前应获取最新的相关信息，并核实这些信息是否最新且完整的。华冠半导体对篡改过的文件不承担任何责任或义务。

客户在使用华冠半导体产品进行系统设计和整机制造时有责任遵守安全标准并采取安全措施。您将自行承担以下全部责任：针对您的应用选择合适的华冠半导体产品；设计、验证并测试您的应用；确保您的应用满足相应标准以及任何其他安全、安保或其他要求。以避免潜在风险可能导致人身伤害或财产损失情况的发生。

华冠半导体产品未获得生命支持、军事、航空航天等领域应用之许可，华冠半导体将不承担产品在这些领域应用造成的后果。因使用方超出该产品适用领域使用所产生的一切问题和责任、损失由使用方自行承担，与华冠半导体无关，使用方不得以本协议条款向华冠半导体主张任何赔偿责任。

华冠半导体所生产半导体产品的性能提供技术和可靠性数据（包括数据表）、设计资源（包括参考设计）、应用或其他设计建议、网络工具、安全信息和其他资源，不保证没有瑕疵且不做出任何明示或暗示的担保，测试和其他质量控制技术的使用只限于华冠半导体的质量保证范围内。每个器件并非所有参数均需要检测。

华冠半导体的文档资料，授权您仅可将这些资源用于研发本资料所述的产品的应用。您无权使用任何其他华冠半导体知识产权或任何第三方知识产权。严禁对这些资源进行其他复制或展示，您应全额赔偿因在这些资源的使用中对华冠半导体及其代理造成的任何索赔、损害、成本、损失和债务，华冠半导体对此概不负责。