# TDSEMIC 拓電半導體

## 自主封測 品質把控 售後保障

WEB | WWW.TDSEMIC.COM

Q

電源管理 顯示驅動 二三極管 LDO穩壓器 觸摸芯片

MOS管 運算放大器 存儲芯片

MCU

串口通信

**TJA1044GT-1Z-TD**

產品規格說明書

## TAJ1044T/1,TAJ1044GT High-speed CAN transceiver with Standby mode

#### 1. DESCRIPTION

The TAJ1044 is part of the family of high-speed CAN transceivers. It provides an interface between a Controller Area Network (CAN) protocol controller and the physical two-wire CAN bus. The transceiver is designed for high-speed CAN applications in the automotive industry, providing the differential transmit and receive capability to (a microcontroller with) a CAN protocol controller.

The TAJ1044 offers a feature set optimized for 12 V automotive applications, Significant improvements have been made, and excellent ElectroMagnetic Compatibility (EMC) performance. Additionally, the TAJ1044 features:

- Ideal passive behavior to the CAN bus when the supply voltage is off

- A very low-current Standby mode with bus wake-up capability

- Excellent EMC performance, even without a common mode choke

- Variants with a VIO pin can be interfaced directly with microcontrollers with supply voltages from 3.3 V to 5 V

These features make the TAJ1044 an excellent choice for all types of HS-CAN, in nodes that require a low-power mode with wake-up capability via the CAN bus.

The TAJ1044 implements the CAN physical layer as defined in ISO 11898-2:2016 and SAE J2284-1 to SAE J2284-5. The TAJ1044T is specified for data rates up to 1 Mbit/s. Additional timing parameters defining loop delay symmetry are specified for the other variants. This implementation enables reliable communication in the CAN FD fast phase at data rates up to 5 Mbit/s.

#### 2. FEATURES

#### 2.1. General

- Fully ISO 11898-2:2016, SAE J2284-1 to SAE J2284-5 and SAE J1939-14 compliant

- Very low-current Standby mode with local and bus wake-up capability

- Optimized for use in 12 V automotive systems

- Low Electromagnetic Emission (EME) and high Electromagnetic Immunity (EMI),

- according to proposed EMC Standards IEC 62228-3 and SAE J2962-2

- Dark green product (halogen free and Restriction of Hazardous Substances (RoHS) compliant)

- Variants with a VIO pin allow for direct interfacing with 3.3 V to 5 V microcontrollers. Variants without a VIO pin can interface with 3.3V and 5 V-supplied microcontrollers, provided the microcontroller I/Os are 5 V tolerant.

#### 2.2. Predictable and fail-safe behavior

- Functional behavior predictable under all supply conditions

- Transceiver disengages from the bus (high-ohmic) when the supply voltage drops below the switch-off undervoltage threshold

- Transmit Data (TXD) dominant time-out functions

- Internal biasing of TXD and STB input pins

#### 2.3. Low-power management

- Very low-current Standby mode with host and bus wake-up capability

- Variants with V<sub>IO</sub> pin: CAN wake-up receiver powered by VIO allowing VCC to be shut down

#### 2.4. Protection

- High ESD handling capability on the bus pins (8 kV IEC and HBM)

- Bus pins protected against transients in automotive environments

- Undervoltage detection on pins V<sub>CC</sub> and V<sub>IO</sub>

- Thermally protected

### 3. QUICK REFERENCE DATA

Table 1. Quick reference data

| Symbol                | Parameter                             | Conditions                           | Min  | Тур | Max  | Unit |

|-----------------------|---------------------------------------|--------------------------------------|------|-----|------|------|

| $V_{cc}$              | supply voltage                        |                                      | 4.5  | -   | 5.5  | V    |

|                       |                                       | Standby mode                         |      |     |      |      |

|                       |                                       | TAJ1044T,GT                          | -    | 10  | 15   | μΑ   |

|                       | aa.b. aaaa                            | variants with a V <sub>IO</sub> pin  | 1-   | 0.1 | 1    | μΑ   |

| $I_{CC}$              | supply current                        | Normal mode                          |      |     |      |      |

|                       |                                       | bus recessive                        | 2    | 5   | 10   |      |

|                       |                                       | bus dominant                         | 20   | 45  | 60   | m/   |

| $V_{uvd(stb)(VCC)}$   | standbyundervoltage                   |                                      |      |     |      |      |

|                       | detection voltage on pin              |                                      | 3.5  | 4   | 4.3  | m/   |

|                       | V <sub>CC</sub>                       |                                      |      |     |      |      |

| $V_{uvd(swoff)(VCC)}$ | switch-off undervoltage               |                                      |      |     |      |      |

|                       | detection voltage on pin              | TAJ1044T,GT                          | 1.3  | 2.4 | 3.4  | V    |

|                       | V <sub>cc</sub>                       |                                      |      |     |      |      |

| $V_{IO}$              | supply voltage on pin V <sub>IO</sub> |                                      | 2.91 | -   | 5.5  | V    |

|                       | supply current on pin V <sub>IO</sub> | Standby mode                         | -    | 10  | 16.5 | μA   |

| I <sub>IO</sub>       |                                       | Normal mode; bus recessive           | 10   | 17  | 30   | μA   |

|                       |                                       | variants with a V <sub>IO</sub> pin  | -    | 170 | 300  | μA   |

|                       | switch-off undervoltage               |                                      |      |     |      |      |

| $V_{uvd(swoff)(VIO)}$ | detection voltage on pin              | variants with a V <sub>IO</sub> pin  | 2.4  | 2.6 | 2.8  | V    |

|                       | V <sub>IO</sub>                       |                                      |      |     |      |      |

| $V_{ESD}$             | electrostatic discharge               | IEC 61000-4-2 at pins CANH and CANL  | -8   |     | +8   | kV   |

| VESD                  | voltage                               | TEC 01000-4-2 at pins CANT and CANE  | -6   | _   | 70   | N.V  |

| $V_{CANH}$            | voltage on pin CANH                   | limiting value according to IEC60134 | -42  | -   | +42  | V    |

| V <sub>CANL</sub>     | voltage on pin CANL                   | limiting value according to IEC60134 | -42  | -   | +42  | V    |

|                       | virtual junction                      |                                      | 10   |     | .450 | 0.0  |

| $T_{v_{j}}$           | temperature                           |                                      | -40  | -   | +150 | °C   |

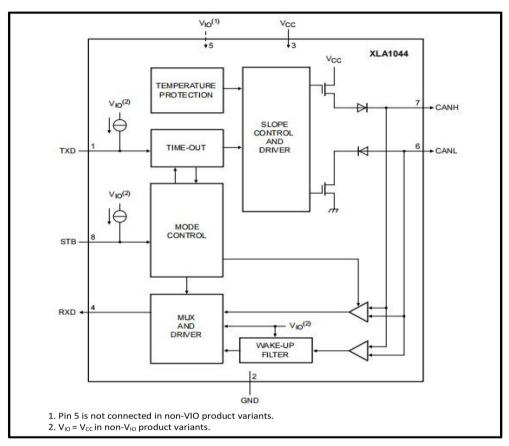

#### 4. BLOCK DIAGRAM

Figure 1. Block diagram

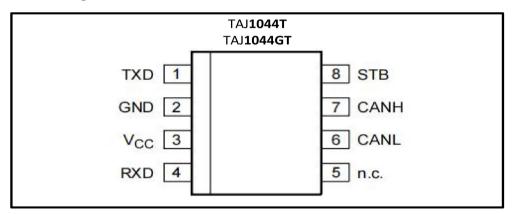

#### 5. PINNING INFORMATION

#### 5.1. Pinning

Figure 2. Pin configuration diagrams

#### 5.2. Pin description

Table 3. Pin description

| Symbol          | Pin | Type <sup>(1)</sup> | Description                                            |

|-----------------|-----|---------------------|--------------------------------------------------------|

| TXD             | 1   | I                   | transmit data input                                    |

| GND             | 2   | G                   | ground supply                                          |

| V <sub>cc</sub> | 3   | Р                   | supply voltage                                         |

| RXD             | 4   | 0                   | receive data output; reads out data from the bus lines |

| n.c.            | 5   | `                   | ot connected; TAJ1044T,GT                              |

| CANL            | 6   | AIO                 | LOW-level CAN bus line                                 |

| CANH            | 7   | AIO                 | HIGH-level CAN bus line                                |

| STB             | 8   | Ī                   | Standby mode control input                             |

[1] I: digital input; O: digital output; AIO: analog input/output; P: power supply; G: ground.

#### 6. FUNCTIONAL DESCRIPTION

#### 6.1. Operating modes

The TAJ1044 supports two operating modes, Normal and Standby. The operating mode is selected via pin STB. See Table 4 for a description of the operating modes under normal supply conditions.

Table 4. Operating modes

| Mode    | Inputs  |         | Outputs          |                                   |     |  |

|---------|---------|---------|------------------|-----------------------------------|-----|--|

|         | Pin STB | Pin TXD | CAN driver       | Pin RXD                           |     |  |

| Normal  | LOW     |         | LOW              | dominant                          | LOW |  |

|         |         | HIGH    | recessive        | LOW when bus dominant             |     |  |

|         |         |         |                  | HIGH when bus recessive           |     |  |

| Ctandby | HIGH    | X [1]   | biased to ground | follows BUS when wake-up detected |     |  |

| Standby |         | X (1)   |                  | HIGH when no wake-up detected     |     |  |

Note:[1] 'x' = don't care

#### 6.1.1 Normal mode

A LOW level on pin STB selects Normal mode. In this mode, the transceiver can transmit and receive data via the bus lines CANH and CANL (see Figure 1 for the block diagram). The differential receiver converts the analog data on the bus lines into digital data which is output on pin RXD. The slopes of the output signals on the bus lines are controlled internally and are optimized in a way that guarantees the lowest possible EME.

#### 6.1.2 Standby mode

A HIGH level on pin STB selects Standby mode. In Standby mode, the transceiver is not able to transmit or correctly receive data via the bus lines. The transmitter and Normalmode receiver blocks are switched off to reduce supply current, and only a low-power differential receiver monitors the bus lines for activity.

In Standby mode, the bus lines are biased to ground to minimize system supply current. The low-power receiver is supplied from  $V_{IO}$  ( $V_{CC}$  in non- $V_{IO}$  variants) and can detect CAN bus activity even if  $V_{IO}$  is the only available supply voltage. Pin RXD follows the bus after a wake-up request has been detected. A transition to Normal mode is triggered when STB is forced LOW.

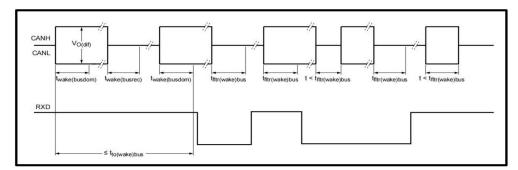

#### 6.2. Remote wake-up (via the CAN bus)

The TAJ1044 wakes up from Standby mode when a dedicated wake-up pattern (specified in ISO 11898-2:2016) is detected on the bus. This filtering helps avoid spurious wake-up events. A spurious wake-up sequence could be triggered by, for example, a dominant clamped bus or by dominant phases due to noise or spikes on the bus. The wake-up pattern consists of:

- a dominant phase of at least twake(busdom) followed by

- a recessive phase of at least twake(busrec) followed by

- a dominant phase of at least twake(busdom)

Dominant or recessive bits between the above mentioned phases that are shorter than twake(busdom) and twake(busrec) respectively are ignored.

The complete dominant-recessive-dominant pattern must be received within tto(wake)bus to be recognized as a valid wake-up pattern (see Figure 3). Otherwise, the internal wake-up logic is reset. The complete wake-up pattern will then need to be retransmitted to trigger a wake-up event. Pin RXD remains HIGH until the wake-up event has been triggered.

After a wake-up sequence has been detected, the TAJ1044 will remain in Standby mode with the bus signals reflected on RXD. Note that dominant or recessive phases lasting less than tfltr(wake)bus will not be detected by the low-power differential receiver and will not be reflected on RXD in Standby mode. A wake-up event is not flagged on RXD if any of the following events occurs while a valid wake-up pattern is being received:

The TAJ1044 switches to Normal mode

The complete wake-up pattern was not received within tto(wake)bus

A  $V_{CC}$  or  $V_{IO}$  undervoltage is detected ( $V_{CC} < V_{uvd(swoff)}(V_{CC})$  or  $V_{IO} < V_{uvd(swoff)}(V_{IO})$ ; see Section 6.3.3)

Figure 3. Wake-up timing

#### 6.3. Fail-safe features

#### 6.3.1 TXD dominant time-out function

A 'TXD dominant time-out' timer is started when pin TXD is set LOW. If the LOW state on this pin persists for longer than  $t_{\text{to}(\text{dom})\text{TXD}}$ , the transmitter is disabled, releasing the bus lines to recessive state. This function prevents a hardware and/or software application failure from driving the bus lines to a permanent dominant state (blocking all network communications). The TXD dominant time-out timer is reset when pin TXD is set HIGH.

#### 6.3.2 Internal biasing of TXD and STB input pins

Pins TXD and STB have internal pull-ups to  $V_{CC}$  ( $V_{IO}$  for variants with a  $V_{IO}$  pin) to ensure a safe, defined state in case one or both of these pins are left floating. Pull-upcurrents flow in these pins in all states; both pins should be held HIGH in Standby mode to minimize supply current.

#### 6.3.3 Undervoltage detection on pins VCC and VIO

If  $V_{CC}$  drops below the standby undervoltage detection level,  $V_{uvd(stb)}(V_{CC})$ , the transceiver switches to Standby mode. The logic state of pin STB is ignored until VCC has recovered.

In versions with a  $V_{IO}$  pin, if  $V_{IO}$  drops below the switch-off undervoltage detection level ( $V_{uvd(swoff)}(V_{IO})$ ), the transceiver switches off and disengages from the bus (zero load) until  $V_{IO}$  has recovered.

In versions without a  $V_{1O}$  pin, if  $V_{CC}$  drops below the switch-off undervoltage detection level ( $V_{uvd(swoff)}(V_{CC})$ ), the transceiver switches off and disengages from the bus (zero load) until  $V_{CC}$  has recovered.

#### 6.3.4 Overtemperature protection

The output drivers are protected against overtemperature conditions. If the virtual junction temperature exceeds the shutdown junction temperature, Tj(sd), both output drivers are disabled. When the virtual junction temperature drops below Tj(sd) again, the output drivers recover once TXD has been reset to HIGH. Including the TXD condition prevents output driver oscillation due to small variations in temperature.

#### 7. LIMITING VALUES

Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134); all voltages are referenced to ground.

| Symbol                   | Parameter                                | Conditions                                                 | Min  | Max                                  | Unit |

|--------------------------|------------------------------------------|------------------------------------------------------------|------|--------------------------------------|------|

|                          |                                          | on pins CANH, CANL                                         | -45  | +42                                  | V    |

| $V_X$                    | voltage on pin x <sup>(1)</sup>          | on pin VCC, VIO                                            | -0.3 | +7                                   | V    |

|                          |                                          | on any other pin (2)                                       | -0.3 |                                      | V    |

| V <sub>(CANH-CANL)</sub> | voltage between pin CANH<br>and pin CANL |                                                            | 27   | +27                                  | V    |

|                          |                                          | on pins CANH and CANL (4)                                  |      | V <sub>IO</sub> + 0.3 <sup>(3)</sup> |      |

|                          | **************************************   | pulse 1                                                    | -100 | -                                    | V    |

| $V_{\mathrm{trt}}$       | transient voltage                        | pulse 2a                                                   | -    | 75                                   | V    |

|                          |                                          | pulse 3a                                                   | -150 | -                                    | V    |

|                          |                                          | pulse 3b                                                   | -    | 100                                  | V    |

|                          |                                          | IEC 61000-4-2 (150 pF, 330 $\Omega$ discharge circuit) (5) |      |                                      |      |

|                          |                                          | on pins CANH and CANL                                      | -8   | +8                                   | kV   |

|                          |                                          | Human Body Model (HBM)                                     |      |                                      |      |

|                          |                                          | on any pin (6)                                             | -4   | +4                                   | kV   |

| 1/                       | electrostatic discharge                  | on pins CANH and CANL (7)                                  | -8   | +8                                   | kV   |

| $V_{ESD}$                | voltage                                  | Machine Model (MM); 200 pF, 0.75 $\mu$ H, 10 $\Omega$      |      |                                      |      |

|                          |                                          | on any pin                                                 | -200 | +200                                 | V    |

|                          |                                          | Charged Device Model (CDM) (9)                             |      |                                      |      |

|                          |                                          | on corner pins                                             | -750 | +750                                 | V    |

|                          |                                          | on any other pin                                           | -500 | +500                                 | V    |

| $T_{vj}$                 | virtual junction temperature             | (10)                                                       | -40  | +125                                 | °C   |

| T <sub>stg</sub>         | storage temperature                      | (11)                                                       | -55  | +150                                 | °C   |

Note:

(1) The device can sustain voltages up to the specified values over the product lifetime, provided applied voltages (including transients) never exceed these values.

(2) Maximum voltage should never exceed 7 V.

<sup>(2)</sup> Vcc+ 0.3 in the non-Vio product variants.

(3) Vcc+ 0.3 in the non-Vio product variants.

(4) Verified by an external test house according to IEC TS 62228, Section 4.2.4; parameters for standard pulses defined in ISO 7637.

(5) Verified by an external test house according to IEC TS 62228, Section 4.3.

<sup>(6)</sup> In accordance with IEC 60747-1. An alternative definition of virtual junction temperature is: T v<sub>j</sub> = T<sub>amb</sub> + P × Rth(v<sub>j</sub>-a), where Rth(v<sub>j</sub>-a) is a fixed value to be used for the calculation of Tv<sub>j</sub>. The rating for Tv<sub>j</sub> limits the allowable combinations of power dissipation (P) and ambient temperature (T<sub>amb</sub>).

<sup>(7)</sup> T stg in application according to IEC61360-4. For component transport and storage conditions, see instead IEC61760-2

#### 8. THERMAL CHARACTERISTICS

Table 6. Thermal characteristics

Value determined for free convection conditions on a JEDEC 2S2P board.

| Symbol         | Parameter                                                          | Conditions <sup>(1)</sup> | Тур | Unit |  |  |  |

|----------------|--------------------------------------------------------------------|---------------------------|-----|------|--|--|--|

| $R_{th(j-a)}$  | thermal resistance from junction to ambient                        | SOP8 package; in free air | 94  | K/W  |  |  |  |

| $\Psi_{j-top}$ | thermal characterization parameter from junction to top of package | SOP8 package; in free air | 13  | K/W  |  |  |  |

Note:(1) According to JEDEC JESD51-2, JESD51-5 and JESD51-7 at natural convection on 2s2p board. Board with two inner copper layers (thickness: 35 µm) and thermal via array under the exposed pad connected to the first inner copper layer (thickness: 70 µm)

#### 9. STATIC CHARACTERISTICS

#### **Table 7. Static characteristics**

Tvj = -40 °C to +125°C; V  $_{CC}$  = 4.5 V to 5.5 V; V $_{IO}$  = 2.91 V to 5.5 V $^{[1]}$ ;  $R_{L}$  = 60  $\Omega$ ;  $C_{L}$  = 100 pF unless otherwise specified; all voltages are defined with respect to ground; positive currents flow into the IC  $^{[2]}$

| Symbol                       | Parameter                                                           | Conditions                                                              | Min                | Тур | Max                  | Unit |

|------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------|-----|----------------------|------|

| Supply; pin V <sub>cc</sub>  |                                                                     |                                                                         |                    |     |                      |      |

| Vcc                          | supply voltage                                                      |                                                                         | 4.5                | -   | 5.5                  | V    |

| V <sub>uvd(stb)(VCC)</sub>   | standby undervoltage                                                | [3]                                                                     | 3.5                | 4   | 4.3                  | v    |

| ▼ uva(stb)(vcc)              | detection voltage on pin V <sub>cc</sub>                            |                                                                         | 3.3                | -   | 4.5                  | L v  |

| V <sub>uvd(swoff)(VCC)</sub> | switch-off undervoltage                                             | TAJ1044T,GT [3]                                                         | 1.3                | 2.4 | 3.4                  | l v  |

| • ava(swon)(vcc)             | detection voltage on pin V <sub>cc</sub>                            | ,                                                                       | 1.0                |     | 5                    |      |

|                              |                                                                     | Standby mode                                                            |                    |     |                      |      |

|                              |                                                                     | TAJ1044T, GT; $V_{TXD} = V_{CC}$                                        | -                  | 10  | 15                   | μΑ   |

| Icc                          | supply current                                                      | variants with a V <sub>IO</sub> pin; V <sub>TXD</sub> = V <sub>IO</sub> | -                  | 0.1 | 1                    | μΑ   |

| icc                          | Supply current                                                      | Normal mode                                                             |                    |     |                      |      |

|                              |                                                                     | recessive; V <sub>TXD</sub> = V <sub>IO</sub> [4]                       | 2                  | 5   | 10                   | mA   |

|                              |                                                                     | dominant; V <sub>TXD</sub> = 0 V                                        | 20                 | 45  | 60                   | mA   |

|                              |                                                                     | dominant; V <sub>TXD</sub> = 0 V;                                       |                    |     |                      |      |

|                              |                                                                     | short circuit on bus lines;                                             | 2                  | 80  | 110                  | mA   |

|                              |                                                                     | -3 V < (V <sub>CANH</sub> = V <sub>CANL</sub> ) < +18 V                 |                    |     |                      |      |

| I/O level adapte             | er supply; pin V <sub>IO</sub> [1]                                  |                                                                         |                    |     |                      |      |

| V <sub>IO</sub>              | supply voltage on pin V <sub>IO</sub>                               |                                                                         | 2.91               | -   | 5.5                  | V    |

|                              | supply current on pin V <sub>IO</sub>                               | Standby mode; V <sub>TXD</sub> = V <sub>IO</sub> [4]                    | -                  | 10  | 16.5                 | μΑ   |

| I <sub>IO</sub>              |                                                                     | Normal mode                                                             |                    |     |                      |      |

| 110                          |                                                                     | recessive; V <sub>TXD</sub> = V <sub>IO</sub> [4]                       | 10                 | 17  | 30                   | μΑ   |

|                              |                                                                     | dominant; V <sub>TXD</sub> = 0 V                                        | -                  | 170 | 300                  | μΑ   |

| $V_{\text{uvd(swoff)(VIO)}}$ | switch-off undervoltage<br>detection voltage on pin V <sub>IO</sub> | variants with a V <sub>IO</sub> pin [3]                                 | 2.4                | 2.6 | 2.8                  | v    |

| Standby mode                 | control input; pin STB                                              |                                                                         |                    |     |                      |      |

| 1/                           | IIIGII lavalia avetualta aa                                         | variants with a V <sub>IO</sub> pin                                     | 0.7V <sub>IO</sub> | -   | V <sub>IO</sub> +0.3 | V    |

| V <sub>IH</sub>              | HIGH-level input voltage                                            | TAJ1044T,GT                                                             | 2                  | -   | V <sub>cc</sub> +0.3 | V    |

| 17                           | 10001                                                               | variants with a V <sub>IO</sub> pin                                     | -0.3               | -   | +0.3V <sub>IO</sub>  | V    |

| $V_{IL}$                     | LOW-level input voltage                                             | TAJ1044T,GT                                                             | -0.3               | -   | +0.8                 | V    |

| I <sub>IH</sub>              | HIGH-level input current                                            | V <sub>STB</sub> = V <sub>IO</sub> [4]                                  | -1                 | -   | +1                   | μΑ   |

| I <sub>IL</sub>              | LOW-level input current                                             | V <sub>STB</sub> = 0 V                                                  | -15                | -   | -1                   | μΑ   |

| CAN transmit d               | ata input; pin TXD                                                  |                                                                         |                    |     |                      |      |

|                              | IIIGII Isaadisaastaaska                                             | variants with a V <sub>IO</sub> pin                                     | 0.7V <sub>IO</sub> | -   | V <sub>IO</sub> +0.3 | V    |

| $V_{IH}$                     | HIGH-level input voltage                                            | TAJ1044T, GT                                                            | 2                  | -   | V <sub>cc</sub> +0.3 | V    |

| 17                           | LOW lavel in motors by                                              | variants with a V <sub>IO</sub> pin                                     | -0.3               | -   | +0.3V <sub>cc</sub>  | V    |

| VIL                          | LOW-level input voltage                                             | TAJ1044T, GT                                                            | -0.3               |     | +0.8                 | V    |

| I <sub>IH</sub>              | HIGH-level input current                                            | V <sub>TXD</sub> = V <sub>IO</sub> [4]                                  | -5                 | -   | +5                   | μА   |

| Symbol                                       | Parameter                             | Conditions                                                                                                                                     | Min                | Тур                    | Max                | Uni      |

|----------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|--------------------|----------|

|                                              |                                       | V <sub>TXD</sub> = 0 V; variants with a V <sub>IO</sub> pin                                                                                    | -270               | -150                   | -60                | μΔ       |

| I <sub>IL</sub>                              | LOW-level input current               | V <sub>TXD</sub> = 0 V;<br>variants without a V <sub>IO</sub> pin                                                                              | -270               | -150                   | -65                | μΔ       |

| Ci                                           | input capacitance                     | [5]                                                                                                                                            | -                  | 5                      | 10                 | pF       |

| AN receive da                                | ta output; pin RXD                    |                                                                                                                                                |                    |                        |                    |          |

| Іон                                          | HIGH-level output current             | $V_{RXD} = V_{IO}^{[4]} - 0.4 \text{ V}$                                                                                                       | -9                 | -3                     | -1                 | m        |

| I <sub>OL</sub>                              | LOW-level output current              | V <sub>RXD</sub> = 0.4 V; bus dominant                                                                                                         | 1                  | -                      | 12                 | m.       |

|                                              | CANH and CANL                         |                                                                                                                                                |                    |                        |                    |          |

|                                              |                                       | $V_{TXD} = 0 \text{ V}; \text{ t} < \text{t}_{to(dom)TXD}$                                                                                     |                    |                        |                    | T        |

| $V_{O(dom)}$                                 | dominant output voltage               | pin C <sub>ANH</sub> ; $R_L = 50 \Omega$ to $65 \Omega$                                                                                        | 2.75               | 3.5                    | 4.5                | ١ ١      |

| . ,                                          |                                       | pin C <sub>ANL</sub> ; $R_L = 50 \Omega$ to $65 \Omega$                                                                                        | 0.5                | 1.5                    | 2.25               | V        |

| V <sub>dom(TX)sym</sub>                      | transmitter dominant voltage symmetry | $V_{dom(TX)sym} = V_{CC} - V_{CANH} - V_{CANL}$                                                                                                | -400               | -                      | +400               | m        |

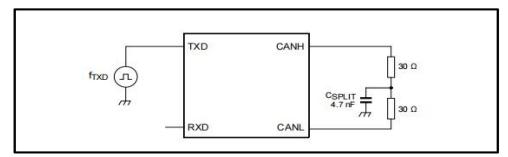

| $V_{TXsym}$                                  | transmitter voltage<br>symmetry       | $V_{TXSym} = V_{CANH} + V_{CANL};$ [5]<br>$f_{TXD} = 250 \text{ kHz}, 1 \text{ MHz and } 2.5 \text{ MHz};$ [6]<br>$C_{SPLIT} = 4.7 \text{ nF}$ | 0.6V <sub>CC</sub> | -                      | 1.1V <sub>CC</sub> | V        |

|                                              |                                       | dominant; Normal mode;<br>$V_{TXD} = 0 \text{ V}; \text{ t} < \text{t}_{to(dom)TXD}$                                                           |                    |                        |                    |          |

|                                              |                                       | $R_L = 50 \Omega$ to $65 \Omega$                                                                                                               | 1.5                | -                      | 3                  | \        |

|                                              | 1:55                                  | R <sub>L</sub> = 45 Ω to 70 Ω                                                                                                                  | 1.4                | -                      | 3.3                | ١ ١      |

| V <sub>O(dif)</sub>                          | differential output                   | R <sub>L</sub> = 2240 Ω                                                                                                                        | 1.5                | -                      | 5                  | ١ ١      |

|                                              | voltage                               | recessive                                                                                                                                      |                    |                        |                    | 1        |

|                                              |                                       | Normal mode: V <sub>TXD</sub> = V <sub>IO</sub> <sup>[4]</sup> ;<br>no load                                                                    | -50                | -                      | +50                | m        |

|                                              |                                       | Standby mode; no load                                                                                                                          | -0.2               | -                      | +0.2               | ١ ١      |

| V <sub>O(rec)</sub> recessive output voltage |                                       | Normal mode; $V_{TXD} = V_{IO}^{[4]}$ ; no load                                                                                                |                    | 0.5<br>V <sub>cc</sub> | 3                  | \        |

| - O(ICC)                                     | ,                                     | Standby mode; no load                                                                                                                          | -0.1               | -                      | +0.1               | 1        |

|                                              |                                       | -12 V ≤ V <sub>CANL</sub> ≤ +12 V;                                                                                                             |                    |                        |                    | $\top$   |

|                                              | differential receiver                 | -12 V ≤ V <sub>CANH</sub> ≤ +12 V                                                                                                              |                    |                        |                    |          |

| $V_{th(RX)dif}$                              | threshold voltage                     | Normal mode                                                                                                                                    | 0.5                | -                      | 0.9                | <u> </u> |

|                                              | am contra t chage                     | Standby mode                                                                                                                                   | 0.4                | -                      | 1.15               |          |

|                                              | receiver recessive                    | $-12 \text{ V} \leq_{\text{VCANL}} \leq +12 \text{ V};$<br>$-12 \text{ V} \leq_{\text{VCANH}} \leq +12 \text{ V}$                              | 0.1                |                        | 1.13               |          |

| $V_{rec(RX)}$                                | voltage                               | Normal mode [5]                                                                                                                                | -4                 | -                      | +0.5               | 1        |

|                                              | 1211262                               | Standby mode [5]                                                                                                                               | -4                 | -                      | +0.4               | 1        |

|                                              | receiver dominant                     | $-12 \text{ V} \leq_{\text{VCANL}} \leq +12 \text{ V};$<br>$-12 \text{ V} \leq_{\text{VCANH}} \leq +12 \text{ V}$                              |                    |                        |                    |          |

| $V_{dom(RX)}$                                | voltage                               | Normal mode [5]                                                                                                                                | 0.9                | -                      | -9.0               | ١ ١      |

|                                              |                                       | Standby mode [5]                                                                                                                               | 1.15               | -                      | 9.0                |          |

|                                              | differential receiver                 | -12 V ≤ V <sub>CANL</sub> ≤ +12 V;                                                                                                             |                    | 1                      |                    |          |

| $V_{hys(RX)dif}$                             | hysteresis voltage                    | -12 V ≤ V <sub>CANH</sub> ≤ +12 V; Normal mode                                                                                                 | 50                 | -                      | 300                | m        |

|                                              |                                       | $V_{TXD} = 0 \text{ V}; \text{ t} < \text{t}_{to(dom)TXD}; \text{ V}_{CC} = 5 \text{ V}$                                                       |                    |                        |                    | T        |

| I <sub>O(sc)dom</sub>                        | dominant short-circuit                | pin C <sub>ANH</sub> ; V <sub>CANH</sub> = -15 V to +40 V                                                                                      | -100               | -70                    | -                  | m        |

| ·O(sc)dom                                    | output current                        | pin Canl; VCANL = -15 V to +40 V                                                                                                               | -                  | 70                     | 100                | m        |

|                                              | recessive short-circuit               | Normal mode; $V_{TXD} = V_{IO}$ [4];                                                                                                           |                    | -                      |                    | +        |

| I <sub>O(sc)rec</sub>                        | output current                        | $V_{CANH} = V_{CANL} = -27 \text{ V to } +32 \text{ V}$                                                                                        | -5                 | -                      | +5                 | m        |

| I <sub>L</sub>                               | leakage current                       | $V_{CC} = V_{IO} = 0 \text{ V or}$<br>$V_{CC} = V_{IO} = \text{shorted to GND via 47 k}\Omega;$<br>$V_{CANH} = V_{CANL} = 5 \text{ V}$         | -5                 | -                      | +5                 | μ        |

| Ri                                           | input resistance                      | $-2 \text{ V} \le \text{V}_{CANL} \le +7 \text{ V};$<br>$-2 \text{ V} \le \text{V}_{CANH} \le +7 \text{ V}$                                    | 9                  | 15                     | 28                 | k        |

| $\Delta R_i$                                 | input resistance<br>deviation         | $0 \text{ V} \le V_{CANL} \le +5 \text{ V};$ [5] $0 \text{ V} \le V_{CANH} \le +5 \text{ V}$                                                   | -3                 | -                      | +3                 | %        |

| R <sub>i(dif)</sub>                          | differential input                    | $ \begin{array}{ll} -2 \text{ V} \le \text{V}_{CANL} \le +7 \text{ V}; \\ -2 \text{ V} \le \text{V}_{CANH} \le +7 \text{ V} \end{array} $ [5]  | 19                 | 30                     | 52                 | k        |

| Symbol              | Parameter                      | Conditions | Min | Тур | Max | Unit |  |

|---------------------|--------------------------------|------------|-----|-----|-----|------|--|

| C <sub>i(cm)</sub>  | common-mode                    | [5]        | -   | -   | 20  | pF   |  |

| C <sub>i(dif)</sub> | differential input capacitance | [5]        | -   | -   | 10  | pF   |  |

| Temperature de      | Temperature detection          |            |     |     |     |      |  |

| T <sub>j(sd)</sub>  | shutdown junction temperature  | [5]        | -   | 185 | -   | °C   |  |

- all circuitry is connected to V<sub>cc</sub> in the other variants.

All parameters are guaranteed over the virtual junction temperature range by design. Factory testing uses correlated test conditions to cover the specified temperature and power supply voltage range.

- (3) Undervoltage is detected between min and max values. Undervoltage is guaranteed to be detected below min value and guaranteed not to be detected above max value.

- $V_{\text{IO}}$  =  $V_{\text{CC}}$  in non- $V_{\text{IO}}$  product variants.

- (5) Not tested in production; guaranteed by design.

- (6) The test circuit used to measure the bus output voltage symmetry and the common-mode voltages (which includes CSPLIT) is shown in Figure 8

#### 10. DYNAMIC CHARACTERISTICS

#### **Table 8. Dynamic characteristics**

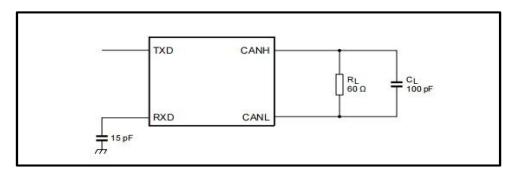

$T_{vj}$  = -40 °C to +125 °C;  $V_{cc}$  = 4.5 V to 5.5 V;  $V_{l0}$  = 2.91 V to 5.5  $V^{[1]}$ ;  $R_L$  = 60  $\Omega$ ;  $C_L$  = 100 pF unless specified otherwise;

| Symbol                                  | Parameter                            | Conditions                          | Min | Тур | Max | Unit |

|-----------------------------------------|--------------------------------------|-------------------------------------|-----|-----|-----|------|

| Transceiver                             | timing; pins CANH, CANL, TXD and RXD | ; see Figure 4, Figure 5 and Figure | 7   |     |     |      |

| t <sub>d(TXD-busdom)</sub>              | delay time from TXD to bus dominant  | other variants; Normal mode         | -   | 65  | 100 | ns   |

| t <sub>d(TXD-busrec)</sub>              | delay time from TXD to bus recessive | other variants; Normal mode         | -   | 90  | 100 | ns   |

| t <sub>d(busdom-RXD)</sub>              | delay time from bus dominant to RXD  | other variants; Normal mode         | -   | 60  | 140 | ns   |

| t <sub>d(busrec-RXD)</sub>              | delay time from bus recessive to RXD | other variants; Normal mode         | -   | 65  | 125 | ns   |

|                                         | delay time from TXD LOW to RXD LOW   | TAJ1044T; Normal mode               | 50  | -   | 230 | ns   |

| t <sub>d(TXDL-RXDL)</sub>               | delay time from TXD LOW to KXD LOW   | all other variants; Normal mode     | 50  | -   | 210 | ns   |

|                                         | delay time from TXD HIGH to RXD      | TAJ1044T; Normal mode               | 50  | -   | 230 | ns   |

| t <sub>d(TXDH-RXDH)</sub>               | HIGH                                 | all other variants; Normal mode     | 50  | -   | 210 | ns   |

|                                         |                                      | all variants except TAJ1044T        |     |     |     |      |

| t <sub>bit(bus)</sub>                   | transmitted recessive bit width      | tbit(TXD) = 500 ns                  | 435 | -   | 530 | ns   |

|                                         |                                      | tbit(TXD) = 200 ns                  | 155 | -   | 210 | ns   |

|                                         |                                      | all variants except TAJ1044T        |     |     |     |      |

| t <sub>bit(RXD</sub> )                  | bit time on pin RXD                  | tbit(TXD) = 500 ns                  | 400 | -   | 550 | ns   |

|                                         |                                      | tbit(TXD) = 200 ns                  | 120 | -   | 220 | ns   |

|                                         |                                      | all variants except TAJ1044T        |     |     |     |      |

| $\Delta t_{rec}$                        | receiver timing symmetry             | tbit(TXD) = 500 ns                  | -65 | -   | +40 | ns   |

|                                         |                                      | tbit(TXD) = 200 ns                  | -45 | -   | +15 | ns   |

| t <sub>to(dom)TXD</sub>                 | TXD dominant time-out time           | VTXD = 0 V; Normal mode             | 0.8 | 3   | 6.5 | ms   |

| t <sub>d(stb-norm)</sub>                | standby to normal mode delay time    |                                     | 7   | 25  | 47  | μs   |

|                                         |                                      | Standby mode                        |     |     |     |      |

| twake(busdom)                           | bus dominant wake-up time            | TAJ1044T, GT                        | 0.5 | -   | 3   | μs   |

|                                         |                                      | all other variants                  | 0.5 | -   | 1.8 | μs   |

|                                         |                                      | Standby mode                        |     |     |     |      |

| twake(busrec)                           | bus recessive wake-up time           | TAJ1044T, GT                        | 0.5 | -   | 3   | μs   |

| (                                       |                                      | all other variants                  | 0.5 | -   | 1.8 | μs   |

| t <sub>to(wake)bus</sub>                | bus wake-up time-out tim             | Standby mode                        | 0.8 | 3   | 6.5 | μs   |

| , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ·                                    | Standby mode                        |     |     |     |      |

| t <sub>fltr(wake)bus</sub>              | bus wake-up filter time              | TAJ1044T, GT                        | 0.5 | 1   | 3   | μs   |

| ,                                       |                                      | all other variants                  | 0.5 | -   | 1.8 | μs   |

#### Note:

- all circuitry is connected to Vcc in the other variants.

All parameters are guaranteed over the junction temperature range by design. Factory testing uses correlated test conditions to cover the

- specified temperature and power supply voltage range.

(3) See Figure 5.

(4) Time-out occurs between the min and max values. Time-out is guaranteed not to occur below the min value; time-out is guaranteed to occur

- (5) Standby-to-Normal mode transition occurs between the min and max values. It is guaranteed not to occur below the min value; it is guaranteed to occur above the max value.

(6) A dominant/recessive phase shorter than the min value is guaranteed not be seen as a dominant/recessive bit; a dominant/recessive phase

- longer than the max value is guaranteed to be seen as a dominant/recessive bit.

(7) Pulses shorter than the min value are guaranteed to be filtered out; pulses longer than the max value are guaranteed to be processed

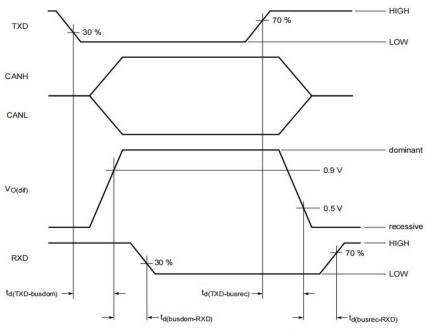

Figure 4. CAN transceiver timing diagram

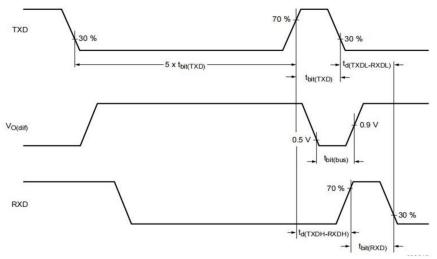

Figure 5. CAN FD timing definitions according to ISO 11898-2:2016

#### 11. APPLICATION INFORMATION

#### 11.1. Application diagrams

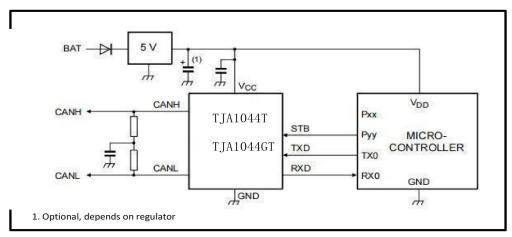

Figure 6. Typical TAJ1044 application with a 5 V microcontroller (non-V 10 variants)

### 12. TEST INFORMATION

Figure 7. CAN transceiver timing test circuit

Figure 8. Test circuit for measuring transceiver transmitter driver symmetry

#### 13. ORDERING INFORMATION

#### **Ordering Information**

| Part<br>Number | Device<br>Making | Package<br>type | Body size<br>(mm) | Temperate<br>(°C) | MSL  | Transpo<br>Rt | Package<br>Quantit |

|----------------|------------------|-----------------|-------------------|-------------------|------|---------------|--------------------|

| TAJ1044T/1     | TAJ1044T1        | SOP-8           | 4.90*3.90         | -40 to +125       | MSL3 | T&R           | 2500               |

| TAJ1044GT      | TAJ1044GT        | SOP-8           | 4.90*3.90         | -40 to +125       | MSL3 | T&R           | 2500               |

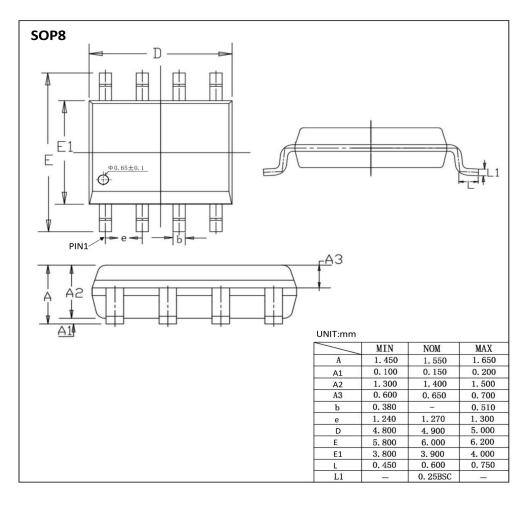

#### 14. DIMENSIONAL DRAWINGS