# **MORNSUN®**

非隔离稳压 40A 单路输出, POL 数字模块电源

专利保护 RoHS

- ASICs、FPGA、ARM

- 网络处理器

- AI 处理器

- 分布式电源

- 通信设备

- 服务器和储存设备

## 产品特点

- 宽输入电压范围: 4.5-14VDC, 含 5V、12V 通用输入

- 输出电压可调: 0.6V-3.3VDC

- 40A 输出电流

- 高精度产品输出电压偏差 3mV

- 输出纹波低至 6 mVp-p, 0.6Vout, 100%lo

- PMBus 数字通信协议

- 工作温度范围: -40 ℃ to +85 ℃

- 效率高达 96.7%, 5Vin, 3.3Vout, 50%lo, 损耗仅 4.5W

- 具备远程控制、PGOOD、远端补偿、时钟同步功能

- 具备输入欠压、输出过/欠压保护功能

- 具备输出过流、短路、过温保护功能

- 通过 PMBus 进行配置和监控

KD12S-40A 是一款非隔离 40A 单路输出的 POL 数字模块电源,它可工作在 4.5-14VDC 的宽输入电压范围,兼容前端 5V/12V 输入系统,并通过外部模拟分压和 PMBus 数字控制,提供精确可调的 0.6-3.3VDC 电压的输出;另外它还具备 PMBus<sup>®</sup>通信协议、远程控制、PGOOD、远端补偿、时钟同步的功能,并具备输入过/欠压、输出过/欠压、输出过流、短路、过温等保护,上位机可实现人机交互,提供大量操作指令去控制和监控模块,同时它拥有高电压精度、低输出纹波、高动态响应等特性。

注:①搭配使用我司上位机,详情见我司官网,技术支持可咨询我司 FAE。

| 选型表        | 表         |                          |                   |              |                |                   |                   |

|------------|-----------|--------------------------|-------------------|--------------|----------------|-------------------|-------------------|

| 认证         | 产品型号      | 输入电压<br>(VDC)            | 输出电压 <sup>①</sup> | 输出电流<br>(A.) | 输出电压偏差<br>(mV) | 效率                | 纹波<br>(Vo=1.0VDC) |

| 7(22 / 782 |           | 标称值<br>(范围值)             | (VDC)             | 最大值          | 标称值            | (标称,满载,典型值)       | 标称满载              |

|            |           | 12<br>(4.5-14) (0.6-1.8) | 40                |              |                |                   |                   |

|            | KD12S-40A | 5-7.5                    |                   | 30           | ±3             | 87.5% (Vo=1.0VDC) | 12mVp-p           |

|            |           | 12<br>(7.5-14)           | 3.3               | 40           |                |                   |                   |

注:

··· ①模块出产设置默认输出 0.6V 输出,阈值微调具体调节见 PMBus 操作指南,模拟调节见 Trim 调节功能。

| 极限额定值 |                                              |      |      |    |

|-------|----------------------------------------------|------|------|----|

|       | 参数                                           | Min. | Max. | 单位 |

|       | VIN                                          | -0.3 | 15   |    |

| 电压    | NC , TRIM , PG , CTRL , SHARE3 , SHARE1      | -0.3 | 7    |    |

|       | VS-、VS+、DATA、SMBALERT#、CLK、SYNC、SHARE、SHARE2 | -0.3 | 5.5  | V  |

|       | ADDRESS 0、ADDRESS 1                          | -0.3 | 3.6  |    |

注:

1.若超出"最大额定值"表内列出的应力值,可能会对器件造成永久损坏。长时间工作在极限额定条件下,器件的可靠性有可能会受到影响。所有电压值都是以大地(GND)为 参考基准。

2.该电源模块可应用于多种应用,从简单的独立供电到复杂的分布式电源架构,为了保持其最大的灵活性,内部不包含保险丝,但是为了实现系统最大的安全性和系统保护,推荐输入端增加保险丝(最大额定值推荐为35A),也可根据实际应用需求,选择适合的保险丝。

| 电气特性                       | 工作友件 1 会 类                        |                     |                  | N 41    | т    | N 4   | <u></u>      |  |

|----------------------------|-----------------------------------|---------------------|------------------|---------|------|-------|--------------|--|

| 项目                         | 工作条件/参数                           |                     |                  | Min.    | Тур. | Max.  | 单位           |  |

| 输入电压范围                     | )7)   (   m     m   )   = 0       |                     |                  | 4.5     | 12   | 14    | VDC          |  |

| 输出电压范围                     | 通过外置电阻分压器                         |                     |                  | 0.6     |      | 3.3   |              |  |

| 最大输入电流                     | 100%负载                            |                     |                  |         | 20.6 |       |              |  |

| 最大输出电流                     |                                   |                     |                  | -       |      | 40    | Α            |  |

| 俞出过流保护阈值<br>(可通过 PMBus 调节) | 0.6-3.3                           | 0.6-3.3             |                  |         | 50   |       |              |  |

| 空载输入电流                     | 标称输入电压、 <b>0%</b> 负载,Vo           | 标称输入电压、0%负载,Vo=0.6V |                  |         | 30   |       |              |  |

| (模块使能)                     | 标称输入电压、0%负载, Vo                   | o=3.3V              |                  |         | 220  |       | mA           |  |

| —————————<br>输出电压偏差        |                                   |                     |                  |         | 3    | 20    |              |  |

|                            |                                   |                     |                  |         | 1    | 6     | mV           |  |

| <br>负载调整偏差                 | 按 10%lo-100%lo 测试                 | 按 10%(0-100%(0 测试   |                  |         | 2    | 10    |              |  |

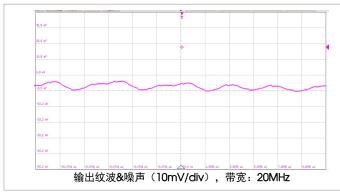

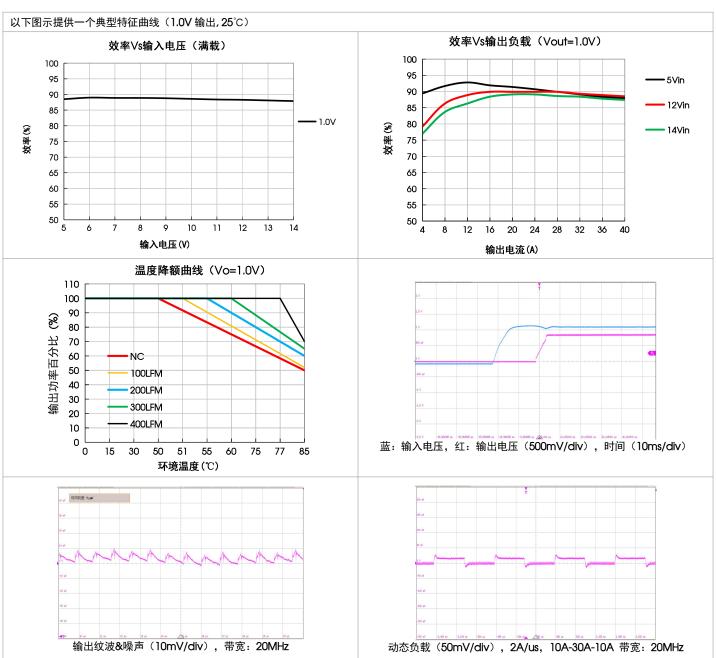

| 74474 Jan 11902            |                                   | 0.6VDC              |                  |         | 6    |       |              |  |

|                            |                                   |                     | 1.0VDC           | <u></u> | 12   |       |              |  |

| 输出电压纹波&噪声                  | 20MHz, 靠测法                        |                     | 1.8VDC           | -       | 18   |       | mVp-         |  |

|                            |                                   |                     |                  |         | 33   |       |              |  |

|                            |                                   |                     | 3.3VDC<br>0.6VDC |         | ±18  | ±85   | mV           |  |

|                            | 20MHz,靠测法<br>25%-75%负载阶跃变化,标称输入电压 |                     | 1.0VDC           |         | ±36  | ±110  |              |  |

| 动态负载                       |                                   |                     |                  |         |      |       |              |  |

|                            | Co=6x47uf+2x680uF+4x100           | DuF                 | 1.8VDC           |         | ±54  | ±150  |              |  |

|                            |                                   | 3.3VDC              |                  | -       | ±99  | ±240  |              |  |

| 温度漂移系数                     |                                   |                     |                  |         | ±0.4 |       | <b>%/</b> °C |  |

| 最大容性负载                     |                                   |                     |                  |         |      | 10000 | μF           |  |

|                            | Vo                                |                     |                  | 79.4    | 81.4 |       | _            |  |

| 效率                         | Vin=12VDC, 100%负载                 | Vo=1.0D             |                  | 85.5    | 87.5 |       | %            |  |

|                            | Vo=                               | Vo=1.8V             | DC               | 89.7    | 91.7 |       |              |  |

|                            | Vo=                               |                     | DC               | 92      | 94.3 |       |              |  |

|                            | Vo=0.6V<br>Vin=12VDC,100%负载       |                     | DC               |         | 5.48 |       | \ <b>\</b>   |  |

| 损耗                         |                                   |                     | DC               | -       | 5.71 |       |              |  |

| ነ <b>火</b> ሉፒ              | VIII—12VDC,100/6以载                | Vo=1.8V             | DC               |         | 6.52 |       | W            |  |

|                            |                                   | Vo=3.3V             | DC               |         | 7.98 |       | 1            |  |

| 模块频率                       |                                   |                     |                  | -       | 540  |       | kHz          |  |

|                            | 同步时钟范围                            |                     |                  | 200     |      | 1500  |              |  |

| 时钟同步/SYNC                  | 高电平 低电平                           |                     |                  | 2.0     |      |       | V            |  |

|                            | 最小脉冲宽度                            |                     |                  |         |      | 0.8   | ns           |  |

|                            | 高电平(模块开)                          |                     |                  | 2.1     |      | 5     | 110          |  |

| 远程控制正逻辑 CTRL               | 低电平(模块关)                          |                     |                  | 0       |      | 0.5   |              |  |

|                            | 高电平(模块关)                          |                     |                  | 2.1     |      | 5     | V            |  |

| 远程控制负逻辑 CTRL               | 低电平(模块开)                          |                     |                  | 0       |      | 0.5   |              |  |

|                            | 开启阈值                              |                     |                  |         | 4.25 |       |              |  |

| 渝入欠压保护                     | 关断阈值                              |                     |                  |         | 4.25 |       | V            |  |

| LUNY VVITT IVER            | PMBus 指令可调范围                      |                     |                  | 4.25    | 4.0  | 14    | -            |  |

| <br>输出过压保护                 |                                   |                     |                  |         |      |       |              |  |

|                            | TRIM 阈值                           |                     |                  |         | 800  |       | mV           |  |

**MORNSUN®**

广州金升田科技有限公司

## DC/DC 数字模块电源

## KD12S-40A 系列

**MORNSUN®**

| 输出过温保护 |  | 130 |    | °C |

|--------|--|-----|----|----|

| 热插拔    |  | 不到  | 支持 |    |

|        |  |     |    |    |

注:

- 1.本模块采用数字控制,数字控制包含一个配置文件,修改配置文件会影响模块的功能和性能。除非另有说明,所有规格均为在默认配置文件下的规格,如需更改配置文件, 可参考以下 PMBus 指令信息,同理上表模块正负逻辑通过数字控制修改;

- 2.除非另有说明,以上规格均在设计参考推荐外围下测试得出;

- 3.除非另有说明,输出电压的测试均在产品输出引脚上进行;

- 4. 除非另有说明,以上规格均适用 1.0V 输出;

- 5.更改开关频率会影响模块性能,更改前请与 FAE 确认;

- 6.外部同步时钟引脚信号必须是占空比为 50%的方波。

- 7.3. 3V 线性调节率低压以 7.5V 为准;

| PMBus 数字                          | -17 IT                |                |                                                                    |                         |      |                          |            |

|-----------------------------------|-----------------------|----------------|--------------------------------------------------------------------|-------------------------|------|--------------------------|------------|

| 项目                                |                       | 工作条            | <u></u>                                                            | Min.                    | Тур. | Max.                     | 单位         |

| 上位机信号特性                           | <u> </u>              |                |                                                                    |                         |      |                          |            |

| 过温保护                              |                       |                |                                                                    | -                       | 130  | -                        | $^{\circ}$ |

| PMBus 温度调 <sup>-</sup>            | 节范围                   |                |                                                                    |                         | -    | 160                      |            |

| 输入欠压保护 F                          | PMBus 可调范围            |                |                                                                    | 4.25                    | _    | 13.8                     | ٧          |

| PGOOD 特性                          |                       |                |                                                                    |                         |      |                          |            |

| PGOOD 阈值料                         | 青度                    |                |                                                                    | -4                      |      | 4                        | %          |

| 上位机测量特性                           | <b>±</b>              |                |                                                                    |                         |      |                          |            |

| 上位机输出电压                           | 玉测量范围                 |                |                                                                    | 0.5                     | _    | 4.5                      |            |

| 上位机输出电压                           | 玉偏置电压                 |                |                                                                    | _                       | 0.1  | _                        | V          |

| 上位机输出电压                           | <br>玉测量精度             | Vo=1V          |                                                                    | -0.8                    |      | 0.8                      | %          |

|                                   | <br>統测量范围             |                |                                                                    | 0                       |      | 50                       | Α          |

|                                   | <br>充测量偏差             | lo≥20 <i>A</i> | A, IOUT_CAL_GAIN=0.503mΩ                                           | -640                    |      | 640                      | mA         |

|                                   | PMBus 数字配置相关          |                |                                                                    |                         |      |                          |            |

| 输入欠压保护                            | <b>4</b>              |                |                                                                    |                         |      |                          |            |

| V <sub>IN(on)</sub>               | 输入欠压开启电               |                | 默认值                                                                |                         | 4.25 | _                        |            |

| V <sub>IN(off)</sub>              | 输入欠压关断电               | <br>B压         | 默认值                                                                |                         | 4    | _                        |            |

| V <sub>INON(rng)</sub>            | 输入欠压开启电               |                |                                                                    | 4.25                    |      | 14                       | V          |

| V <sub>INOFF (rng)</sub>          | 输入欠压关断电               |                |                                                                    |                         |      | 13.75                    |            |

|                                   |                       |                |                                                                    |                         |      |                          |            |

| 输出过压/欠/                           | <br>压保护               |                |                                                                    |                         |      |                          |            |

| V <sub>Trimov</sub>               | Trim 过压阈值             |                | 默认值                                                                |                         | 800  | _                        |            |

| V <sub>TrimUV</sub>               | Trim 欠压阈值             |                | 默认值                                                                |                         | 528  | _                        | mV         |

|                                   |                       | 玉未达到 8         | *******<br>00mV 之前,产品关断驱动,但不进入过压保护状态(锁存关                           | └<br>断〉 <b>,Trim</b> 电压 |      | 」<br><sup>立</sup> 品锁存关断。 |            |

| PG00D                             |                       |                |                                                                    |                         |      |                          |            |

| V <sub>TrimPGH</sub>              | PGOOD 高电平阈            | <br>引值         | 默认值                                                                |                         | 642  | _                        |            |

| V <sub>TrimPGL</sub>              | PGOOD 低电平间            |                | 默认值                                                                |                         | 558  | _                        | mV         |

| V <sub>PG (acc)</sub>             | PG00D 阈值配置            |                |                                                                    | -4                      | -    | 4                        | %          |

| V <sub>PG (hyst)</sub>            | PG00D 回差电压            |                |                                                                    | 15                      | 28   | 45                       | mV         |

| R <sub>PG00D</sub>                | PGOOD 内部下拉            |                | V <sub>Trim</sub> =0V, I <sub>P9000</sub> =5mA                     |                         | 50   |                          | Ω          |

|                                   | PGOOD 引脚漏电            |                | $V_{\text{Trim}} = 600 \text{ mV},  V_{\text{pood}} = 5 \text{ V}$ |                         |      | 20                       |            |

| PGOOD (Ik)                        |                       |                | V <sub>Trim</sub> - 000 IIIV, V <sub>P6000</sub> - 3 V             | <b></b>                 |      | 20                       | μ <b>A</b> |

| $t_{\scriptscriptstyle{PGDELAY}}$ | PGOOD 延迟时间<br>(软启动完成后 | -              | 默认值                                                                |                         | 2    | _                        | ms         |

**MORNSUN®**

广州金升田科技有限公司 MORNSUN GLIANGZHOU SCIENCE & TECHNOLOGY CO LTD

| 通用特性                 |                        |         |                                        |      |         |  |  |

|----------------------|------------------------|---------|----------------------------------------|------|---------|--|--|

| 项目                   | 工作条件                   | Min.    | Тур.                                   | Max. | 单位      |  |  |

| 工作温度                 | 见温度降额曲线图               | -40     |                                        | 85   | °C      |  |  |

| 存储温度                 |                        | -55     |                                        | 125  | C       |  |  |

| 存储湿度                 | 无凝结                    | 5       |                                        | 95   | %RH     |  |  |

| 回流焊温度*               |                        | 峰值温度 Tc | 峰值温度 Tc≤260℃, 217℃以上时间最大为 60 s         |      |         |  |  |

| 平均无故障时间(MTBF)        | MIL-HDBK-217F@25℃      | 18957   |                                        |      | k hours |  |  |

| 海拔高度                 |                        |         |                                        | 2000 | m       |  |  |

| 振动                   |                        | 10-150  | 10-150Hz, 5G, 0.75mm. along X, Y and Z |      |         |  |  |

| 潮敏等级(MSL)            | IPC/JEDEC J-STD-020D.1 |         | MSL 3                                  |      |         |  |  |

| 污染等级                 |                        | PD 3    |                                        |      |         |  |  |

| 注:*实际应用请参考 IPC/JEDEC | J-STD-020D.1 标准。       |         |                                        |      |         |  |  |

| 物理特性 |                         |

|------|-------------------------|

| 外壳材料 | 开板                      |

| 封装尺寸 | 33.00 x 22.10 x 9.05 mm |

| 重量   | 8.8g(Typ)               |

| 冷却方式 | 自然空冷或强制风冷               |

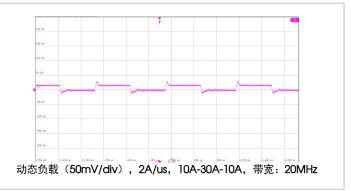

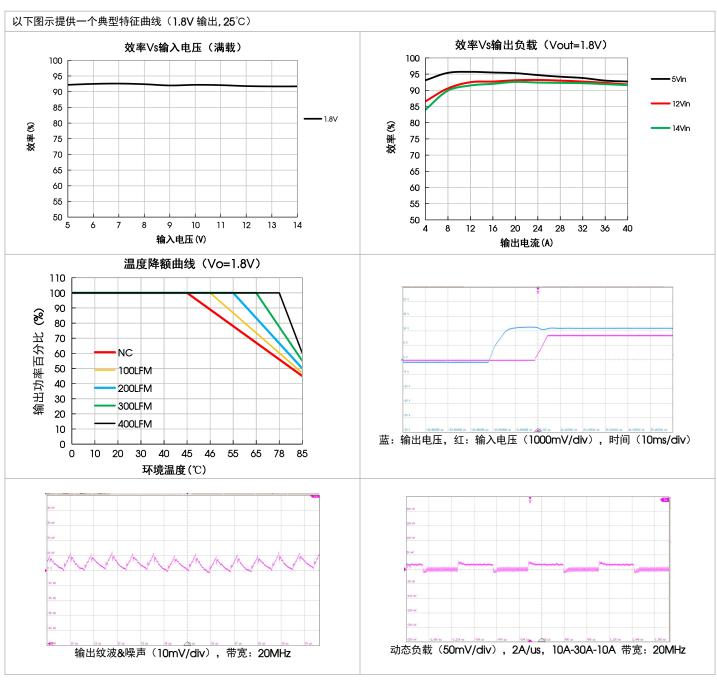

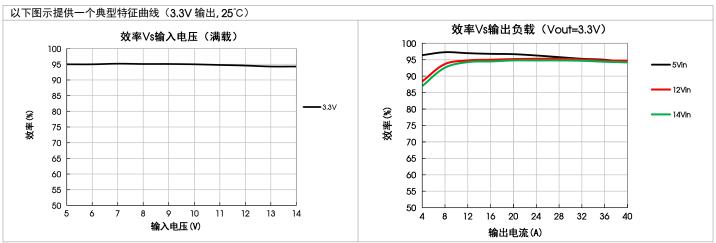

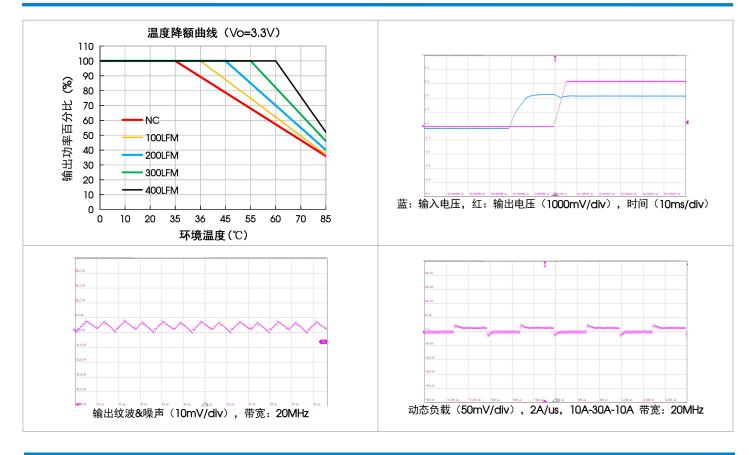

#### 曲线特性 以下图示提供一个典型特征曲线(0.6V输出,25°C) 效率Vs输出负载(Vout=0.6V) 效率Vs输入电压(满载) 100 100 95 95 **-**5Vin 90 90 12Vin 85 85 -0.6V 效率(%) 80 效率(%) 80 - 14Vin 75 75 70 70 65 65 60 60 55 55 50 L 10 11 8 16 20 输入电压(V) 输出电流(A) 温度降额曲线(Vo=0.6V) 110 **○ 触发电平: -8 mV** 100 € 90 80 NC 100LFM 200LFM 300LFM 20 10 400LFM 蓝: 输入电压, 红: 输出电压 (200mV/div), 时间 (10ms/div) 0 10 20 30 40 52 53 59 68 环境温度(℃)

### 输入滤波

该模块应该接入一个低交流阻抗电源,必须保证一个输入电容靠近模块输入引脚附近,确保模块稳定;为了最小化输入电压纹波,推荐使用低 ESR 的陶瓷电容和低 ESR 的电解/聚合物电容。

如应用于 4.5V 输入应用时, 请按以下建议进行:

- a、前级输入必须保证电压≥4.5V;

- B、对于前端 PCB layout 推荐:建议使用至少 4oz,宽度大于 1cm,长度小于 5cm。

#### 输出纹波噪声

默认的环路补偿可以适应大多数的应用需求。另外产品输出会有一部分低频纹波干扰,这种低频纹波与控制环路的不稳定无关,模块总输出纹波 和噪声可以保持在一个较低的幅值。

建议将低 ESR 的陶瓷电容和低 ESR 的电解/聚合物电容放置在尽可能靠近负载的位置,并且并联多个电容以降低其 ESR。为了使电容更有效,建议应用时关注 PCB 布局和布线。

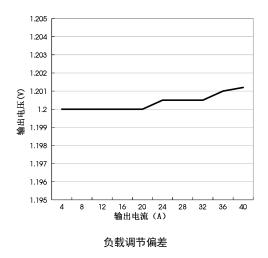

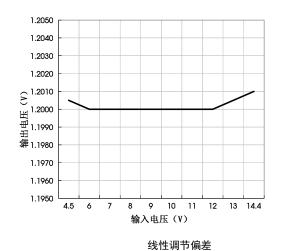

#### 输出精度

该模块为高精度产品,以下为输出电流 0-40A,输出电压 1.0VDC, 4.5-14VDC 输入,典型精度曲线:

## PMBus 数据格式

#### PMBus 数据格式

PMBus 命令(设置阈值、电压或者异常状态)支持三种数据格式,它们需要以文字数字表示作为参数(设置阈值、电压或报告此类命令)。兼容模块只需要支持其中一种格式即可。模块仅支持这些命令的线性数据格式。在这种格式中,data 参数由尾数和指数两部分组成。该参数表示的数字可以表示为:

数值=尾数 x 2 指数

#### PMBus 地址位

在总线上,每个电源模块必须分配唯一的地址,通过 ADDRESS 1 和 ADDRESS 0 引脚可选择 64 个地址(0-63),地址以两个八进制(0-7)数字(以十进制表示的 0 到 63)的形式设置,每个引脚一个数字,ADDRESS 1 是高阶数字,ADDRESS 0 是低阶数字,PMBus 通信时,模块电源的 PMBus 地址位 '0b' +ADDRESS 1+ADDRESS 0,地址设置电阻如下表:

| 数字 | 电阻(kΩ) |

|----|--------|

| 0  | 8.45   |

| 1  | 16.2   |

| 2  | 25.5   |

| 3  | 37.4   |

| 4  | 54.9   |

| 5  | 84.5   |

| 6  | 133    |

| 7  | 200    |

#### 例如:

ADDRESS 1 使用 37.4K 电阻, ADDRESS 0 使用 37.4K 电阻, 八进制数值为 33, 实际上位机显示 27 地址位注意:

- 1、若 ADDRESS 1 和 ADDRESS 1 引脚电阻超出范围值,电源模块不会继续响应 PMBus 指令,上位机不会显示模块被检测;

- 2、使用其他阻值可能会导致 PMBus 地址不正确,建议确保阻值与上表符合。

#### 模块的开机和关机

模块的开机和关机由 PMBus 操作指令、远程控制引脚和输入电压共同控制(可以通过 PMBus 指令设置启机延迟和关机延迟时间)。

#### 注音重顶.

1.如果模块运行在关机延迟时间内,应避免在关机延迟时间之前再开启模块,只有在关机延迟时间结束且模块关闭后,模块才被允许打开,对于两模块并联应用也是如此,两个模块的开关延迟时间必须配置为相同的值。

#### 软启动

模块可配置软启动时间,由 TON\_RISE PMBus 命令从 600 us 到 9 ms 可选配置,详细信息可参阅命令说明。在选择软启动时间时,应考虑输出电容上的充电电流,在有大量输出电容的应用下,这种电流会导致过流保护而关断模块。故为确保这些问题不会发生,在考虑过流阈值设置时,应考虑输出电容的充电电流。输出电容的充电电流由下式可得:

$$I_{CAP} = \frac{V_{OUT} \times C_{OUT}}{t_{SS}}$$

- •ICAP 为输出电容的充电电流,单位为 A

- •VOUT 为模块的输出电压,单位为 V

- •COUT 为输出电容的总容值,单位为 F

- •tSS 为所选的软启动时间,单位为 s

计算出充电电流后,可将过流阈值配置为最大负载电流和输出电容充电电流之和并留一定余量。所需保证的余量可取决于特定的应用场合,但建议为 25%。

注意事项:对于两个模块并联应用时,两个模块的软启动时间必须配置为相同的值。

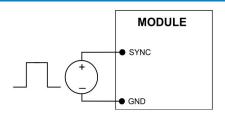

#### 频率设置、时钟同步 SYNC

模块的开关频率可以同步一个在指定范围内具有外部频率的信号。如上图添加外部时钟信号到模块 SYNC 引脚来完成,其中外来时钟需满足电气规格表指定外部 SYNC 信号要求。

如不使用该引脚,模块应在默认开关频率下运行,且将 SYNC 引脚连接至 GND。

开关频率可以通过 SYNC 引脚上的外部时钟同步。在两模块并联工作时,SYNC 信号的频率必须是开关频率的 4 倍,,SYNC 信号必须是占空比为 50%的方形波形。高电平阈值应大于 2V,低电平阈值应小于 0.8 V。SYNC 和 SHARE2 设置的更改仅在电源重启后生效。

#### 开关机延迟

可通过上位机设置开机延迟时间,可设置输出电压上升时间和关机延迟时间,更多信息可在 PMBus 指令处查阅。

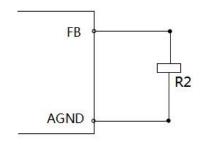

#### 输出电压设置

Trim 引脚连接到内部误差放大器的输入端,内部参考电压为 600 mV ± 0.5%。

$$R2 = R_{FBX}(k\Omega) = \frac{12}{V_O - V_{\rm FB}}$$

| VOCCED  | 电阻(kΩ)          |

|---------|-----------------|

| VO(SET) | 电阻( <b>K</b> Ω) |

| 0.6     | OPEN            |

| 0.9     | 40              |

| 1.0     | 30              |

| 1.2     | 20              |

| 1.5     | 13.33           |

| 1.8     | 10              |

| 3.3     | 4.4444          |

| 4.5     | 3.0791          |

模块的输出电压可以使用 VREF\_TRIM 命令进行调节,该命令的格式详见 MFR\_SPECIFIC\_04 (VREF\_TRIM) (D4h)说明,其调节范围在输出电压的-20% 到 10%之间, VREF\_TRIM 命令通常用于精调模块的输出电压,步进为 2mV。另外 MARGINING 和 VREF\_TRIM 共同限制了输出电压可调范围在-30% 到 10%之间,不建议超过该范围。

KD12S-40A 可以通过以下三种形式确定实际的输出电压:

No output margin

$$V_{FB} = VREF \_TRIM + 0.6$$

Margin High Voltage State

$$V_{FR} = STEP \_ VREF \_ MARGIN \_ HIGH + VREF \_ TRIM + 0.6$$

· Margin Low State

$$V_{FB} = STEP \_ VREF \_ MARGIN \_ LOW + VREF \_ TRIM + 0.6$$

- · VTrim 是 Trim 引脚上的电压

- VREF\_TRIM 是输出电压的偏置电压

- VREF\_MARGIN\_HIGH 是输出电压可调的边际电压上限

- VREF\_MARGIN\_LOW 是输出电压可调的边际电压下限

#### **PGOOD**

模块会检测 Trim 引脚上的电压,用于判断输出电压是否在设定值范围内。在软启动过程,PGOOD 被拉至地,在软启动结束后,如果输出电压在PGOOD 阈值范围内(PG\_LOW 至 PG\_HIGH 之间),PGOOD 引脚会在 2ms 延迟后释放,当输出电压超出 PGOOD 阈值范围内,PGOOD 会立即拉至地。PGOOD 阈值范围(PG\_LOW 和 PG\_HIGH)可通过 PMBus 指令 MFR\_SPECIFIC\_07(PCT\_VOUT\_FAULT)PG\_LIMIT)设置。

PGOOD 为开漏引脚,需外接 10K 电阻。

#### 输出过流保护 OC

输出过流保护上位机可设置两种响应方式,一种为短路自恢复,另一种为短路后模块锁存。短路周期为: 7 个周期计数 (7 × 模块输出电压上升时间),在两模块并联应用下,二路的过流保护响应跟随一路,两个模块需设置在相同的过流保护响应模式下。

#### 输出欠压/过压保护 VOUT UV/OV

模块检测 Trim 引脚上的电压,用于提供输出过压和输出欠压保护,输出过压阈值和输出欠压阈值都可在 PMBus 指令上设置。

输出欠压保护的方式和过流保护一致。

例如若 IOUT\_OC\_FAULT\_RESPONSE 指令设置响应为自恢复重启,那么在欠压保护响应下也为自恢复重启,另外欠压保护只有在软启动结束后才会 开始检测。

当输出过压保护故障发生时,直到电源重启或 CNTL 切换。当输出过压阈值设置为输出电压的百分比时,只有在软启动结束后才会启用输出过压保护,当输出过压阈值设置为固定值时,输出过压保护持续生效。在两项并联应用下,保证两模块 SHARE1 接入 SHARE1 总线只检测模块 1 (主机)的 Trim1的输出欠压/过压故障,其余通道均不会检测。更多信息可查看 MFR\_SPECIFIC\_07 (PCT\_VOUT\_FAULT\_PG\_LIMIT) (D7h) 和 (E0h) MFR\_SPECIFIC\_16 (COMM\_EEPROM\_SPARE) 指令。

#### 输入欠压保护 VIN UV

输入欠压保护也可通过上位机设置,具体可查看 VIN\_ON 和 VIN\_OFF 指令,默认欠压为电气性能表格中描述,这些指令在两模块并联应用时也需要同步设置。

#### 过温保护 OT

模块内部具有保护功能,上位机同步可修改过温保护点,可设置在 120℃到 160℃之间。

当内部控制 IC 过温故障时(160℃),控制 IC 的 PWM 关闭,当温度下降至 140℃后,PWM 重新启动。

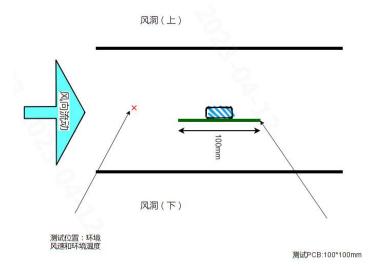

#### 热设计

该产品可工作在不同的热环境下,但必须提供足够的散热以确保模块可靠运行。散热主要通过模块引脚到主板的热传导,以及流经模块的对流风速来实现。该产品有一定程度降额,但不建议过温度使用,温度降额曲线提供了在特定 Vin 下的输出电流与环境温度和风速的关系,具体可见上述表格,测试图见下图。

该模块在 100\*100mm 测试板上测试,垂直安装在截面为 300 x 203 mm 的风洞中。另外请注意模块和主板之间连接的低阻抗可有效减少额外的功率损耗。

#### SHARE1 故障信息

在触发过流、输入欠压、输出过压、输出欠压、过温故障时,SHARE1 引脚会被内部拉低,此外,如果模块的 SHARE1 引脚在外部被拉低,该模块也会关闭。

所以在多相应用下,SHARE1 连接至总线,任何一个通道出现故障 SHARE1 被拉低,其余模块也会跟随关闭,如果故障响应设置为自恢复,则只有在每个通道 SHARE1 均被释放后,才可重新启动。

| 故障信息 | 输入欠压 | 过流        | 输出欠压      | 输出过压                                | 过温           |

|------|------|-----------|-----------|-------------------------------------|--------------|

| 响应模式 | /    | 可设置自恢复或锁存 | 可设置自恢复或锁存 | 锁存                                  | 温度低于开启阈值后自恢复 |

| 软启动前 | 开启   | 关闭        | 关闭        | 阈值为固定值<br>时开启/阈值为<br>输出电压百分<br>比时关闭 | 开启           |

| 软启动中 | 开启   | 逐周期限流     | 关闭        | 阈值为固定值<br>时开启/阈值为<br>输出电压百分<br>比时关闭 | 开启           |

| 软启动后 | 开启   | 开启        | 开启        | 开启                                  | 开启           |

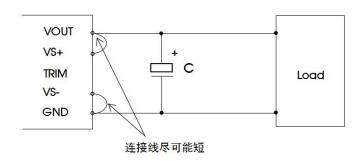

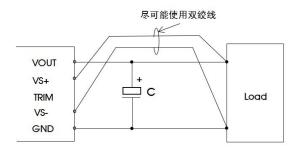

### 远端补偿的使用以及注意事项

1、当不使用远端补偿时:

#### 注意事项:

- 1) 当不使用远端补偿时,确保 VOUT 与 VS+, GND 与 VS-短接;

- 2) VOUT与 VS+, GND与 VS-之间的连线尽可能短,并靠近端子。避免形成一个较大的回路面积,当噪声进入这个回路,可能造成模块的不稳定。

- 2、当使用远端补偿时:

#### 注意事项:

- 1. 如果使用远端补偿的引线比较长时,可能导致输出电压不稳定,如果必须使用较长的远端补偿引线时请联系我司技术人员。

- 2. 如果使用远端补偿,请使用双绞线或者屏蔽线,并使引线尽可能短。

- 3. 在电源模块和负载之间请使用宽 PCB 引线或粗线,并保持线路电压降应低于 0.3V。确保电源模块的输出电压保持在指定的范围内。

- 4. 引线的阻抗可能造成输出电压振荡或者较大纹波,使用之前请做好足够的评估。

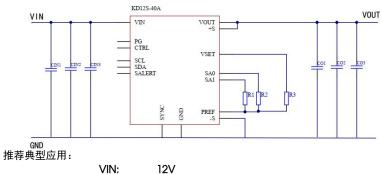

#### 设计参考

#### 典型应用电路

|      | 名称      | 规格                                           |  |  |

|------|---------|----------------------------------------------|--|--|

| CIN1 |         | 2*680uF/35V 电解电容                             |  |  |

|      | CIN2    | 3*22uF/25V 陶瓷电容                              |  |  |

|      | CIN3    | 0.1uF/25V 陶瓷电容                               |  |  |

| СО   | 其他输出    | 0.1uF/6.3V 陶瓷电容                              |  |  |

| 1    | 3.3V 输出 |                                              |  |  |

| СО   | 3.3V 输出 | 6*47uF/6.3V+1*22uF/10V 陶瓷电容                  |  |  |

| 2    | 其他输出    | 5*47uF/6.3V+2*22uF/10V 陶瓷电容                  |  |  |

| СО   | 0.6V 输出 | 1*100uF/25V+3*220uF/25V+1*680uF/3<br>5V 电解电容 |  |  |

| 3    | 3.3V 输出 | 2*680uF/35V 电解电容                             |  |  |

|      | 其他输出    | 2*220uF/25V+1*680uF/35V 电解电容                 |  |  |

|      | R1      | ODEN                                         |  |  |

|      | R2      | OPEN                                         |  |  |

|      | R3      | 30K                                          |  |  |

VIN: 12V VOUT: 1.0V IOUT: 40A

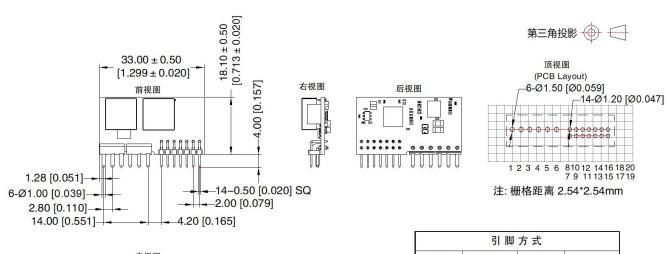

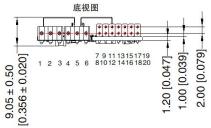

### 外观尺寸图

注:

尺寸单位: mm[inch]

端子直径公差: ±0.10[±0.004] 未标注公差: ±0.25[±0.010] 器件布局仅供参考,具体以实物为准

|    | 引 脚 方 式 |    |        |  |  |  |  |

|----|---------|----|--------|--|--|--|--|

| 引脚 | 功能      | 引脚 | 功能     |  |  |  |  |

| 1  | Vin     | 11 | SDA    |  |  |  |  |

| 2  | Vin     | 12 | SALERT |  |  |  |  |

| 3  | GND     | 13 | SA1    |  |  |  |  |

| 4  | GND     | 14 | SCL    |  |  |  |  |

| 5  | Vo      | 15 | SYNC   |  |  |  |  |

| 6  | Vo      | 16 | SA0    |  |  |  |  |

| 7  | -S      | 17 | CTRL   |  |  |  |  |

| 8  | +S      | 18 | PG     |  |  |  |  |

| 9  | NC      | 19 | PREF   |  |  |  |  |

| 10 | VSET    | 20 | NC     |  |  |  |  |

| PMBusg 关键寄                | 存器详情                                                                                                                                                       |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | 该指令用于操作 CNTL(CTRL)来开启或关闭模块,也可用于设置输出电压的精调。                                                                                                                  |

| OPERATION(01h)            | 为了访问模块通道 1 的 OPERATION 寄存器,PAGE 必须设置为 0,若为了访问模块通道 2 的 OPERATION 寄存器,PAGE 必须设置为 1,如果要同时访问通道 1 和通道 2,PAGE 必须设置为 11。                                          |

|                           | 如果通道被配置为从机,则该通道无法访问该指令,该指令的任何写入都将被忽略,尝试读写从机通道的任何指令都会报告<br>故障并触发 SMBALERT。                                                                                  |

| IOUT_CAL_GAIN             | IOUT_CAL_GAIN 必须等于实际电感器 DCR 值,以实现精确的电流读数和 OC 故障保护。                                                                                                         |

| Enable and UVLO           | ON_OFF_CONFIG 命令用于选择转换器的开启行为。在本示例中,只要输入电压存在且高于 UVLO 阈值,无论操作状态如 何,都使用 CTRL 端子来启用或禁用转换器。如果 CTRL 端子悬空,则通过内部 6 µ A 电流源将其拉至 5V。                                 |

|                           | 软启动时间命令可设置软启动时间,选择软启动时间时需要考虑输出电容器的充电电流。在某些 应用 (例如具有大量输出<br>电容的应用)中,如果未正确选择软启动时间,那么该电流可能导致错误的过流保护电路跳变。为避免误的跳变,在选择软                                          |

| TON_RISE                  | 启动时间和过流阈值时应包括输出电容器充电电流。可以使用公式计算电容器充电电流: $I_{\mathit{CAP}} = \dfrac{V_{\mathit{OUT}} 	imes C_{\mathit{O}}}{t_{\mathit{ss}}}$ 。                              |

| IOUT_OC_FAULT_LIMIT       | 过流阈值和响应令可设置过流阈值。模块使用电感器峰值电流值进行过流检测。应将电流限制设置为最大电感器峰值电流,加上启动期间的输出电容器充电电流,再加上一些负载瞬态和元件变化余量。所需的余量大小取决于各个应用,对于该应用,最大电感器峰值电流为,该设计允许一些额外的余量,因此选择了 50A(峰值电流)的过流阈值。 |

| IOUT_OC_FAULT_RESP<br>ONE | IOUT_OC_FAULT_RESPONE 命令可设置所需的过流事件响应。在该示例中,转换器配置为在发生过流情况时进入间断模式。模块还可以配置为在发生过流情况时锁存。                                                                        |

| <b>PMBus</b> | 详细寄存器            |           |                                                                                                                                                                        |                  |                       |

|--------------|------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|

| CODE         | COMMAND NAME     | WORD/BYTE | DESCRIPTION: PMBus Command                                                                                                                                             | USER<br>WRITABLE | FACTORY DEFAULT VALUE |

| 00h          | PAGE             | Byte      | Locates separate PMBus<br>command lists in multiple output<br>environments                                                                                             | YES              | 0XXX XXX0             |

| 01h          | OPERATION        | Byte      | Turn the unit on and off in conjunction with the input from the CONTROL pin. Set the output voltage to the upper or lower MARGIN VOLTAGES.                             | YES              | 0X00 00XX             |

| 02h          | ON_OFF_CONFIG    | Byte      | Configures the combination of CONTROL pin input and serial bus commands needed to turn the unit on and off. This includes how the unit responds when power is applied. | YES              | XXX1 0110             |

| 03h          | CLEAR_FAULTS     | Byte      | Clears all fault status registers to 0x00. The "Unit is Off" bit in the status byte is not cleared when this command is issued.                                        | YES <sup>1</sup> | NONE                  |

| 10h          | WRITE_PROTECT    | Byte      | Prevents unwanted writes to the device.                                                                                                                                | YES              | 000X XXXX             |

| 15h          | STORE_USER_ALL   | Byte      | Saves the current configuration into the User Store. Note: This command writes to Non-Volatile Memory.                                                                 | YES <sup>1</sup> | NONE                  |

| 16h          | RESTORE_USER_ALL | Byte      | Restores Store. all parameters to the settings saved in the User                                                                                                       | YES <sup>1</sup> | NONE                  |

| 19h          | CAPABILITY       | Byte      | PEC,SPD,ALRT                                                                                                                                                           | No               | 1011 0000             |

| 20h          | VOUT_MODE        | Byte      | Read-Only Mode Indicator. The<br>data format is linear with an<br>exponent of -9                                                                                       | No               | 0001 0111             |

| 35h          | VIN_ON           | Word      | Sets the value of the input voltage<br>at which the unit should<br>start power conversion                                                                              | YES              | 1111 0000 0001 0001   |

| 36h          | VIN_OFF          | Word      | Sets the value of the input voltage at which the unit should stop power conversion.                                                                                    | YES              | 1111 0000 0001 0000   |

# **MORNSUN®**

|     |                        |      | Sets the ratio of the voltage at the                                            |     |                     |

|-----|------------------------|------|---------------------------------------------------------------------------------|-----|---------------------|

| 38h | IOUT_CAL_GAIN          | Word | current sense pins to the sensed current.                                       | YES | 1000 0000 0010 0001 |

| 39h | IOUT_CAL_OFFSET        | Word | Nulls any offsets in the output current sensing circuit                         | YES | 1110 0000 0000 0000 |

|     |                        |      | Sets the value of the output current, in amperes, that causes                   |     |                     |

| 46h | IOUT_OC_FAULT_LIMIT    | Word | the over-current detector to indicate an over-current fault condition.          | YES | 1111 1000 0001 1110 |

|     |                        |      | Instructs the device on what                                                    |     |                     |

| 47h | IOUT_OC_FAULT_RESPONSE | Byte | action to take in response to an output over-current fault.                     | YES | 0000 0111           |

| 4Ah | IOUT_OC_WARN_LIMIT     | Word | Sets the value of the output current that causes an output Over-current warning | YES | 1111 1000 0011 0010 |

| 4Fh | OT_FAULT_LIMIT         | Word | over-temperature fault threshold                                                | YES | 0000 0000 1000 0010 |

| 5lh | OT_WARN_LIMIT          | Word | over-temperature warning threshold                                              | YES | 0000 0000 01111000  |

| 61h | TON_RISE               | Word | Target soft-start rise time                                                     | YES | 1110 0000 0010 1011 |

| 78h | STATUS_BYTE            | Byte | Single byte status indicator                                                    | No  | 0x00 0000           |

| 79h | STATUS_WORD            | Word | Full 2-byte status indicator                                                    | No  | 0000 0000 0x00 0000 |

| 7Ah | STATUS_VOUT            | Byte | Output voltage fault status detail                                              | No  | 0000 0000           |

| 7Bh | STATUS_IOUT            | Byte | Output current fault status detail                                              | No  | 0000 0000           |

| 7Dh | STATUS_TEMPERATURE     | Byte | Temperature fault status detail                                                 | No  | 0000 0000           |

| 7Eh | STATUS_CML             | Byte | Communication, memory, and logic fault status detail                            | No  | 0000 0000           |

| 80h | STATUS_MFR_SPECIFIC    | Byte | Manufacturer specific fault status<br>detail                                    | No  | 0000 0000           |

| 8Bh | READ_VOUT              | Word | Read output voltage                                                             | No  | 0000 0000 0000 0000 |

| 8Ch | READ_IOUT              | Word | Read output current                                                             | No  | 1110 0000 0000 0000 |

| 8Eh | READ_TEMPERATURE_2     | Word | Read off-chip temp sensor                                                       | No  | 1111 0000 0110 0100 |

| 98h | PMBUS_REVISION         | Byte | PMBus Revision Information                                                      | No  | 0001 0001           |

| D0h | MFR_SPECIFIC_00        | Word | User scratch pad                                                                | YES | 0000 0000 0000 0000 |

| D4h | MFR_SPECIFIC_04        | Word | VREF_TRIM                                                                       | YES | 0000 0000 0000 0000 |

| D5h | MFR_SPECIFIC_05        | Word | STEP_VREF_MARGIN_HIGH                                                           | YES | 0000 0000 0001 1110 |

| D6h | MFR_SPECIFIC_06        | Word | STEP_VREF_MARGIN_LOW                                                            | YES | 1111 1111 1110 0010 |

| D7h | MFR_SPECIFIC_07        | Byte | PCT_VOUT_FAULT_PG_LIMIT                                                         | YES | XXXX XX10           |

| D8h | MFR_SPECIFIC_08        | Byte | SWQUENCE_TON_TOFF_DELAY                                                         | YES | 111X 000X           |

| E0h | MFR_SPECIFIC_16        | Word | COMM_EEPROM_SPARE                                                               | YES | 1011 0001 xxxx x011 |

| E5h | MFR_SPECIFIC_21        | Word | IC options                                                                      | YES | 0111 1111 0000 0000 |

| E6h | MFR_SPECIFIC_22        | Word | PWM_OSC_SELECT                                                                  | YES | 0000 0000 0000 0001 |

| E7h | MFR_SPECIFIC_23        | Word | Paged and Common<br>MASK_SMBALERT                                               | YES | 0000 0000 0000 0000 |

| EFh | MFR_SPECIFIC_30        | Word | Temperature offset                                                              | YES | 1111 1000 0000 0000 |

| F0h | MFR_SPECIFIC_32        | Word | API options                                                                     | YES | 0000 0000 0000 0000 |

| FCh | MFR_SPECIFIC_44        | Word | Device code, unique code to id part number                                      | No  | 0000 0001 1110 0000 |

NOTE 1: No data bytes are sent, only the command code is sent.

### PAGE(00h)

| Format      | Unsigned binary integer                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Description | The PAGE command provides the ability to configure, control, and monitor through only one physical address both channels (outputs) of the device. |

| Default     | 0XXX XXX0 (binary)                                                                                                                                |

|     |   |   | P/ | AGE |   |   |     |

|-----|---|---|----|-----|---|---|-----|

| r/w | r | r | r  | r   | r | r | r/w |

| 7   | 6 | 5 | 4  | 3   | 2 | 1 | 0   |

| PA  | X | Х | Х  | X   | Х | Х | P0  |

| Bits | Field Name | Description                                                                                            |

|------|------------|--------------------------------------------------------------------------------------------------------|

|      |            | 00: (Default) All commands address the first channel.                                                  |

|      |            | 01: All commands address the second channel.                                                           |

| 7,0  | PA,P0      | 10: Illegal input-ignore this write, take no action.                                                   |

|      |            | 11: All commands address both channels.                                                                |

|      |            | If PAGE = 11, any then read commands point to PAGEO always.                                            |

| 6:1  | Х          | X indicates writes are ignored and reads are 0. Any values written to read-only registers are ignored. |

#### OPERATION (01h)

| Format      | Unsigned binary integer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description | The OPERATION command is used to turn the device output on or off in conjunction with the input from the CNTLx pin (where x = 1 for channel 1 and x = 2 for channel 2). It is also used to set the output voltage to the upper or lower MARGIN levels.  OPERATION is a paged register. In order to access OPERATION register for channel 1 of the device, PAGE must be set to 0. In order to access OPERATION register for channel 2 of the device, PAGE must be set to 1. For simultaneous access of channels 1 and 2, PAGE command must be set to 11. If the channel is configured as a SLAVE, this command can not be accessed for that channel. Any writes to the SLAVE channel for this command are ignored. An attempt to read and write the SLAVE channel command results in a NACK'd command and the reporting of an IVC fault and triggering of SMB_ALERT. |

| Default     | 0X0000XX (binary)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r/w | r | r/w    | r/w | r/w | r/w | r | r |

|-----|---|--------|-----|-----|-----|---|---|

| 7   | 6 | 5      | 4   | 3   | 2   | 1 | 0 |

| On  | 0 | Margin |     |     |     | Х | Х |

| Bits | Field Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | On         | The On bit is used to enable to IC via PMBus. The necessary condition for this bit to be effective is that the cmd bit in the ON_OFF CONFIG register is set high. However, the cmd bit being high is not a sufficient condition to enable the IC via the On bit, as specified below:  0: (Default) The device output is not enabled via PMBus.  1: The device output is enabled if:  a. The supply voltage VIN is greater than the VIN_UVLO threshold, the cmd bit is high, and b. The bit cpr in the ON_OFF CONFIG register is low, or  c. The bit cpr is high and the CNTL_EN pin is enabled (high or low). |

| 6    | 0          | X: Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5:2  | Margin     | If Margin Low is enabled, load the value from the STEP_VREF_MARGIN_LOW command. If Margin High is enabled, load the value from the STEP_VREF_MARGIN_HIGH command. (See PMBus specification for more information)  0000: (Default) Margin Off  0101: Margin Low (Ignore Fault)  0110: Margin Low (Act On Fault)  1001: Margin High (Ignore Fault)  1010: Margin High (Act On Fault)  Note: Any values written to read-only registers are ignored.                                                                                                                                                              |

| 1:0  | Х          | XX: Default X indicates writes are ignored and reads are 0. Any values written to read-only registers are ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## ON\_OFF\_CONFIG (02h)

| Format      | Unsigned binary integer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | The ON_OFF_CONFIG command configures the combination of CONTROL pin input and serial bus commands needed to turn the unit on and off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Description | ON_OFF_CONFIG is a paged register. In order to access this register for channel 1 of the device, PAGE must be set to 0. In order to access this register for channel 2 of the device, PAGE must be set to 1. For simultaneous access of channels 1 and 2, PAGE command must be set to 11. If the channel is configured as a SLAVE, this command can not be accessed for that channel. Any writes to the SLAVE channel for this command are ignored. An attempt to read and write the SLAVE channel command results in a NACK'd command and the reporting of an IVC fault and triggering of SMB_ALERT. |

|             | However, note that page 0 (channel 1) fault status bits (and associated smbalert state) should be capable of being                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Description | cleared by toggling CNTL1 pin even if channel 1 is a slave. If channel 2 is a slave, then CNTL2 pin is disabled but toggling the CNTL1 pin should also clear page 1 (channel 2) fault status bits and related smbalert state. (The is recommendation is to tie together CNTL1 pins of both devices in a multi-phase configuration).                                                                                                                                                                                                                                                                   |

| Default     | XXX10110 (binary) The default power-up state can be changed using the STORE_USER_ALL command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |   |   | r/w <sup>E</sup> | r/w <sup>E</sup> | r/w <sup>E</sup> | r/w <sup>E</sup> | r   |

|---|---|---|------------------|------------------|------------------|------------------|-----|

| 7 | 6 | 5 | 4                | 3                | 2                | 1                | 0   |

| X | X | Х | pu               | cmd              | cpr              | pol              | сра |

| Bits | Field Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5  | X          | X indicates writes are ignored and reads are 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4    | pu         | (Format: binary) Sets the default to either operate any time power is present or for the CTRL to be controlled by CONTROL pin and/or PMBus commands. This bit is used in conjunction with the 'cp', 'cmd', and 'on' bits to determine start up.  0: Device powers up any time power is present regardless of state of the CONTROL pin.  1: (Default) Device does not power up until commanded by the CNTL_EN pin and/or OPERATION command as programmed in bits (3:0) of the ON_OFF_CONFIG register.                                                                                                                                                |

| 3    | cmd        | (Format: binary) The cmd bit controls how the device responds to commands received via the serial PMBus. This bit is used in conjunction with the 'cpr', 'pu', and 'on' bits to determine start up. 0: (Default) Device ignores the on bit in the OPERATION command. 1: Device responds to the on bit in the OPERATION command, as explained above.                                                                                                                                                                                                                                                                                                 |

| 2    | cpr        | (Format: binary) Set the CNTL_EN pin response. This bit is used in conjunction with the 'cmd', 'pu', and 'on' bits to determine start up. The cpr bit being high is a necessary but not sufficient condition to enable the IC via the CNTL_EN pin:  0: Device ignores the CNTL_EN pin, i.e., CTRL is controlled only by the OPERATION command  1: (Default) The device output is enabled if:  a. The supply voltage VIN is greater than the VIN_UVLO threshold, and the CNTL_EN pin is active (high or low), and  b. The bit cmd in the ON_OFF CONFIG register is low, or  c. The bit cmd is high and the bit on in the OPERATION register is high. |

| 1    | pol        | (Format: binary) Polarity of the CONTROL pin 1: (Default) CONTROL pin is active high 0: CONTROL pin is active low To change this value, the user must change this value in the register, save it to the EEPROM and then reboot the device via power down for the new value to take effect.                                                                                                                                                                                                                                                                                                                                                          |

| 0    | cpa        | (Format: binary) Sets CONTROL pin action when commanding the unit to turn off. 0: (Default) Use the programmed turn-off delay. Note: Any values written to read-only registers are ignored on write and returns a '0' when read.                                                                                                                                                                                                                                                                                                                                                                                                                    |

### CLEAR\_FAULTS (03h)

| Format      | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description | CLEAR_FAULTS is a paged command. In order to issue this command for channel 1 of the device, PAGE must be set to 0. In order to issue this command for channel 2 of the device, PAGE must be set to 1. For simultaneous access of channels 1 and 2, PAGE command must be set to 11. The CLEAR_FAULTS command is used to clear any fault bits that have been set. This command simultaneously clears all bits in all status registers in the selected PAGE. At the same time, the device negates (clears, releases) its SMB_ALERT signal output if the device is asserting the SMB_ALERT signal. The CLEAR_FAULTS command does not cause a unit that has latched off for a fault condition to restart. If the fault is still present when the bit is cleared, the fault bit shall immediately be set again and the host notified by the usual means. |

| Bits | Field Name | Description                                            |  |

|------|------------|--------------------------------------------------------|--|

| 7:0  |            | No data bytes are sent, only the command code is sent. |  |

### WRITE\_PROTECT (10h)

| Format      | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | The WRITE_PROTECT command is used to control writing to the PMBus device. The intent of this command is to provide protection against accidental changes. This command is not intended to provide protection against deliberate or malicious changes to a device's configuration or operation. All supported commands may have their parameters read, regardless of the WRITE_PROTECT settings.                                                                                                                                                                             |

| Description | Note: Valid setting of WRITE_PROTECT(7:5) bits disables the RESTORE_USER_ALL command's ability to restore EEPROM data to protected PMBus Control/Status Registers (CSRs). However, an EEPROM (via the RESTORE_USER_ALL execution) restores the data to any registers the remain unprotected (either by a valid WRITE_PROTECT(7:5) setting, or by any invalid setting of these bits). No WRITE_PROTECT(7:5) bit setting affects the Reset-Restore operation. All registers having EEPROM support get updated. Likewise, STORE_USER_ALL command operation remains unaffected. |

| Default     | 000XXXXX (binary)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | The default power-up state can be changed using the STORE_USER_ALL command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| r/w <sup>E</sup> | r/w <sup>E</sup> | r/w <sup>E</sup> |   |   |   |   |   |

|------------------|------------------|------------------|---|---|---|---|---|

| 7                | 6                | 5                | 4 | 3 | 2 | 1 | 0 |

| bit7             | bit6             | bit5             | X | X | Х | X | Χ |

|     | Field Name | Description                                                                                                                                 |  |  |  |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|     | bit7       | (Format: binary)                                                                                                                            |  |  |  |

| 7   |            | 0: (Default) See table below.                                                                                                               |  |  |  |

| ,   |            | 1: Disable all writes except for the WRITE_PROTECT command. (bit5 and bit6 must be 0 to be valid data)                                      |  |  |  |

|     |            | (Format: binary)                                                                                                                            |  |  |  |

| 6   | Bit6       | 0: (Default) See table below.                                                                                                               |  |  |  |

| O   |            | 1: Disable all writes except for the WRITE_PROTECT, OPERATION, and PAGE commands. (bit5 and bit7 must be 0 to be valid data)                |  |  |  |

|     | Bit5       | (Format: binary)                                                                                                                            |  |  |  |

| 5   |            | 0: (Default) See table below.                                                                                                               |  |  |  |

| 3   |            | 1: Disable all writes except for the WRITE_PROTECT, OPERATION, PAGE, and ON_OFF_CONFIG commands. (bit6 and bit7 must be 0 to be valid data) |  |  |  |

| 4.0 | х          | X indicates writes are ignored and reads are 0.                                                                                             |  |  |  |

| 4:0 |            | Note: Any values written to read-only registers are ignored.                                                                                |  |  |  |

Invalid data written to WRITE\_PROTECT(7:5) causes the cml bit in the STATUS\_BYTE and the ivd bit in the STATUS\_CML registers to be set. INVALID DATA ALSO RESULTS IN NO WRITE PROTECTION (WRITE\_PROTECT = 00h)!

| Data Byte Value | Action                                                                                        |

|-----------------|-----------------------------------------------------------------------------------------------|

| 1000 0000       | Disables all WRITES except to the WRITE_PROTECT command.                                      |

| 0100 0000       | Disables all WRITES except to the WRITE_PROTECT, OPERATION, and PAGE commands.                |

| 0010 0000       | Disables all WRITES except to the WRITE_PROTECT, OPERATION, PAGE, and ON_OFF_CONFIG commands. |

# **MORNSUN®**

### STORE\_USER\_ALL (15h)

| Format      | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description | Store all of the current storable register settings in the EEPROM memory as the new defaults on power up. It is permitted to use the STORE_USER_ALL command while the device is operating. However, the device may be unresponsive during the write operation with unpredictable memory storage results. It is recommended to turn the device output off before issuing this command.  EEPROM programming faults set the cml bit in the STATUS_BYTE and the oth bit in the STATUS_CML registers. |

#### RESTORE\_USER\_ALL (16h)

|        | Format      | N/A                                                                                                                                                                                                                                                                                             |

|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |             | Write EEPROM data to those registers which: (1) have EEPROM support, and; (2) are unprotected according to current setting of the WRITE_PROTECT(7:5) bits.                                                                                                                                      |

| Descri | Description | It is permitted to use the RESTORE_USER_ALL command while the device is operating. However, the device may be unresponsive during the copy operation with unpredictable, undesirable or even catastrophic results. It is recommended to turn the device output off before issuing this command. |

| Bits | Field Name | Description                                            |  |

|------|------------|--------------------------------------------------------|--|

| 7:0  |            | No data bytes are sent, only the command code is sent. |  |

#### CAPABILITY (19h)

| Format N/A                                                                                                         |  |

|--------------------------------------------------------------------------------------------------------------------|--|

| Description This command provides a way for a host system to determine some key capabilities of this PMBus device. |  |

| Default 10110000 (binary)                                                                                          |  |

| r   | r  | r  | r    | r | r    | r     | r |

|-----|----|----|------|---|------|-------|---|

| 7   | 6  | 5  | 4    | 3 | 2    | 1     | 0 |

| PEC | SI | PD | ALRT |   | Rese | erved |   |

| Bits | Field Name | Description                                                                               |  |  |  |

|------|------------|-------------------------------------------------------------------------------------------|--|--|--|

|      | DEO        | (Format: binary)                                                                          |  |  |  |

| 7    |            | Packet Error Checking is supported.                                                       |  |  |  |

| /    | PEC        | 1: Default                                                                                |  |  |  |

|      |            | Note: Any values written to read-only registers are ignored.                              |  |  |  |

|      |            | (Format: binary)                                                                          |  |  |  |

| 4.5  | SPD        | Maximum supported bus speed is 400 kHz.                                                   |  |  |  |

| 6:5  |            | 01: Default                                                                               |  |  |  |

|      |            | Note: Any values written to read-only registers are ignored.                              |  |  |  |

|      | ALRT       | (Format: binary)                                                                          |  |  |  |

| 4    |            | This device does have a SMB_ALERT pin and does support the SMBus Alert Response Protocol. |  |  |  |

| 4    |            | 1: Default                                                                                |  |  |  |

|      |            | Note: Any values written to read-only registers are ignored.                              |  |  |  |

| 2.0  | Reserved   | Reserved bits.                                                                            |  |  |  |

| 3:0  |            | 0000: Default                                                                             |  |  |  |

### VOUT\_MODE (20h)

|             | . ,                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Format      | N/A                                                                                                                                                                                                                                                                                                                                                                   |

| Description | The PMBus specification dictates that the data word for the VOUT_MODE command is one byte that consists of a 3-bit Mode and 5-bit parameter, as shown below.  If a host sends a VOUT_MODE writer command, the device rejects the VOUT_MODE command, declare a communication fault for invalid data and respond as described in PMBus specification II section 10.2.2. |

| Default     | 00010111 (binary)                                                                                                                                                                                                                                                                                                                                                     |

## DC/DC 数字模块电源

## KD12S-40A 系列

| r | r    | r | r        | r | r | r | r |  |  |

|---|------|---|----------|---|---|---|---|--|--|

| 7 | 6    | 5 | 4        | 3 | 2 | 1 | 0 |  |  |

|   | Mode |   | Exponent |   |   |   |   |  |  |

| Bits | Field Name | Description                                                  |

|------|------------|--------------------------------------------------------------|

| 7.5  | N 4l -     | (Format: binary)                                             |

| 7:5  | Mode       | 000: (Default) Linear Format                                 |

|      | Exponent   | (Format: two's SHARE3lement binary)                          |

| 4:0  |            | 10111: (Default) Exponent value = - 9                        |

|      |            | Note: Any values written to read-only registers are ignored. |

#### VIN\_ON (35h)

The VIN\_ON command sets the value of the input voltage at which the unit should start power conversion assuming all other conditions are met.

Values written within the supported VIN range are mapped to the nearest supported increment.

The supported VIN\_ON values are:

| 4.25(default) | 4.5  | 4.75 | 5    | 5.25 | 5.5  | 5.75 |

|---------------|------|------|------|------|------|------|

| 6             | 6.25 | 6.5  | 6.75 | 7    | 7.25 | 7.5  |

| 7.75          | 8    | 8.25 | 8.5  | 8.75 | 9    | 9.25 |

| 9.5           | 10   | 10.5 | 11   | 11.5 | 12   | 12.5 |

| 13            | 14   | 15   | 16   |      |      |      |

| Format      | Linear                                                                                                                                                                                                                                                                                                 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|