# **CMOS PROGRAMMABLE PERIPHERAL INTERFACE**

### **FEATURES**

- High speed and low power consumption due to 3µ silicon gate CMOS technology

- 3 V to 6 V single power supply

- Full static operation

- Programmable 24-bit I/O ports

- Bidirectional bus operation (Port A)

- Bit set/reset function (Port C)

- TTL compatible

- Compatible with 8255A-5

- 40-pin Plastic DIP (DIP-40-P-600-2.54)

### ORDERING INFORMATION

| DEVICE    | Package Type | MARKING  | Packing | Packing Qty |

|-----------|--------------|----------|---------|-------------|

| HG82C55AN | DIP-40       | HG82C55A | TUBE    | 220pcs/Box  |

### **GENERAL DESCRIPTION**

The HG82C55A is a programmable universal I/O interface device which operates as high speed and on low power consumption due to 3 msilicon gate CMOS technology. It is the best fit as an I/O port in a system which employs the 8-bit parallel processing HG80C85 CPU.

This device has 24-bit I/O pins equivalent to three 8-bit I/O ports and all inputs/outputs are TTL interface compatible.

# **PIN CONFIGURATION**

|                 | DI | P-40 (TOP VIE | W)                 |

|-----------------|----|---------------|--------------------|

| PA <sub>3</sub> | 1  | $\bigcup$     | 40 PA <sub>4</sub> |

| PA <sub>2</sub> | 2  |               | 39 PA <sub>5</sub> |

| PA <sub>1</sub> | 3  |               | 38 PA <sub>6</sub> |

| PA <sub>0</sub> | 4  |               | 37 PA <sub>7</sub> |

| $\overline{RD}$ | 5  |               | 36 WR              |

| CS              | 6  |               | 35 RESET           |

| GND             | 7  |               | 34 D <sub>0</sub>  |

| $A_1$           | 8  |               | 33 D <sub>1</sub>  |

| $A_0$           | 9  |               | 32 D <sub>2</sub>  |

| PC <sub>7</sub> | 10 |               | 31 D <sub>3</sub>  |

| $PC_6$          | 11 |               | 30 D <sub>4</sub>  |

| PC <sub>5</sub> | 12 |               | 29 D <sub>5</sub>  |

| PC <sub>4</sub> | 13 |               | 28 D <sub>6</sub>  |

| $PC_0$          | 14 |               | 27 D <sub>7</sub>  |

| PC <sub>1</sub> | 15 |               | 26 V <sub>CC</sub> |

| $PC_2$          | 16 |               | 25 PB <sub>7</sub> |

| PC <sub>3</sub> | 17 |               | 24 PB <sub>6</sub> |

| $PB_0$          | 18 |               | 23 PB <sub>5</sub> |

| DD              | 10 |               | 22 DD              |

PB<sub>1</sub> 19

PB<sub>2</sub> 20

22 PB<sub>4</sub>

21 PB<sub>3</sub>

# **PIN DESCRIPTION**

| Pin No.                         | Item                           | Input/Output    | Function                                                                                                                                                                                                                                                                                                                        |

|---------------------------------|--------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7 - D0                         | Bidirectional Data Bus         | Input andOutput | These are three-state 8-bit bidirectional buses used to write and read data upon receipt of the WR and RD signals from CPU and alsoused when control words and bit set/reset data are transferred from CPU to HG82C55A.                                                                                                         |

| RESET                           | Reset Input                    | Input           | This signal is used to reset the control register and all internal registers when it is in high level. At this time, ports are all made into the input mode (high impedance status).  all port latches are cleared to 0. and all ports groups are set to mode 0.                                                                |

| CS                              | Chip SelectInput               | Input           | When the CS is in low level, data transmission is enabled with CPU. When it is in high level, the data bus is made into the high impedancestatus where no write nor read operation is performed. Internal registers hold their previous status, however.                                                                        |

| RD                              | Read Input                     | Input           | When RD is in low level, data is transferred from HG82C55A toCPU.                                                                                                                                                                                                                                                               |

| WR                              | Write Input                    | Input           | When WR is in low level, data or control words are transferred fromCPU to HG82C55A.                                                                                                                                                                                                                                             |

| A <sub>0</sub> , A <sub>1</sub> | Port Select Input<br>(Address) | Input           | By combination of $A_0$ and $A_1$ , either one is selected from among port A, port B, port C, and control register. These pins are usually connected to low order 2 bits of the address bus.                                                                                                                                    |

| PA7 - PA0                       | Port A                         | Input andOutput | These are universal 8-bit I/O ports. The direction of inputs/ outputscan be determined by writing a control word. Especially, port A can be used as a bidirectional port when it is set to mode 2.                                                                                                                              |

| PB7 - PB0                       | Port B                         | Input andOutput | These are universal 8-bit I/O ports. The direction of inputs/outputsports can be determined by writing a control word.                                                                                                                                                                                                          |

| PC7 - PC0                       | Port C                         | Input andOutput | These are universal 8-bit I/O ports. The direction of inputs/outputscan be determined by writing a control word as 2 ports with 4 bits each. When port A or port B is used in mode 1 or mode 2 (port A only), they become control pins. Especially, when port C is used asan output port, each bit can set/reset independently. |

| V <sub>cc</sub>                 | _                              | _               | +5V power supply.                                                                                                                                                                                                                                                                                                               |

| GND                             | _                              | _               | GND                                                                                                                                                                                                                                                                                                                             |

# **CIRCUIT CONFIGURATION**

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                | Symbol           | Conditions                      | Rating           | Unit |

|------------------------------------------|------------------|---------------------------------|------------------|------|

| Supply Voltage                           | V <sub>cc</sub>  | T 0500                          | -0.5 to +7       | V    |

| Input Voltage                            | V <sub>IN</sub>  | Ta = 25°C<br>with respectto GND | -0.5 to VCC +0.5 | V    |

| Output Voltage                           | V <sub>out</sub> | with respectito GND             | -0.5 to VCC +0.5 | V    |

| Storage Temperature                      | T <sub>STG</sub> | _                               | -55 to +150      | °C   |

| Power Dissipation                        | P <sub>D</sub>   | Ta = 25°C                       | 1.0              | W    |

| Lead Temperature (Soldering, 10 seconds) | TL               |                                 | 260              | °C   |

Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured.

# **OPERATING RANGE**

| Parameter             | Symbol          | Range     | Unit |

|-----------------------|-----------------|-----------|------|

| Supply Voltage        | V <sub>cc</sub> | 3 to 6    | V    |

| Operating Temperature | T <sub>op</sub> | -40 to 85 | °C   |

# **RECOMMENDED OPERATING RANGE**

| Parameter             | Symbol          | Min. | Тур. | Max.      | Unit |

|-----------------------|-----------------|------|------|-----------|------|

| Supply Voltage        | V <sub>CC</sub> | 4.5  | 5    | 5.5       | V    |

| Operating Temperature | T <sub>op</sub> | -40  | +25  | +85       | °C   |

| "L" Input Voltage     | V <sub>IL</sub> | -0.3 | _    | +0.8      | V    |

| "H" Input Voltage     | V <sub>IH</sub> | 2.2  | _    | VCC + 0.3 | V    |

# **DC CHARACTERISTICS**

| Parameter                          | Symbol           | Conditio                                                                                       | ne                                | Н    | Unit |      |       |

|------------------------------------|------------------|------------------------------------------------------------------------------------------------|-----------------------------------|------|------|------|-------|

| Parameter                          | Syllibol         | Conditio                                                                                       | 115                               | Min. | Тур. | Max. | Offic |

| "L" Output Voltage                 | V <sub>OL</sub>  | I <sub>OL</sub> = 2.5 μA                                                                       |                                   | _    |      | 0.4  | V     |

| "H" Output Voltage                 | V <sub>OH</sub>  | $I_{OH} = -40 \mu A$                                                                           |                                   | 4.2  | _    |      | V     |

| 11 Output voitage                  | ▼ OH             | $I_{OH} = -2.5 \text{ mA}$                                                                     |                                   | 3.7  | _    | 1    | V     |

| Input Leak Current                 | I <sub>LI</sub>  | $0 \le V_{IN} \le VCC$                                                                         |                                   | -1   | _    | 1    | μA    |

| Output Leak Current                | lLO              | 0 ≤ V <sub>OUT</sub> ≤ VCC                                                                     | VCC = 4.5V to 5.5V                | -10  | _    | 10   | μΑ    |

| Supply Current<br>(Standby)        | I <sub>ccs</sub> | $CS \ge V_{CC} - 0.2 \text{ V}$ $V_{IH} \ge V_{CC} - 0.2 \text{ V}$ $V_{IL} \le 0.2 \text{ V}$ | Ta =-40°C to +85°C<br>(CL = 0 pF) | _    | 0.1  | 10   | μА    |

| Average Supply<br>Current (Active) | I <sub>cc</sub>  | I/O Wire Cycle<br>82C55AA-2<br>8 MHzCPU Timing                                                 |                                   | _    | _    | 8    | mA    |

# **AC CHARACTERISTICS**

$(V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$

|                                                                                                                               |                  | HG8  | 2C55A |      | Domonto    |  |

|-------------------------------------------------------------------------------------------------------------------------------|------------------|------|-------|------|------------|--|

| Parameter                                                                                                                     | Symbol           | Min. | Max.  | Unit | Remarks    |  |

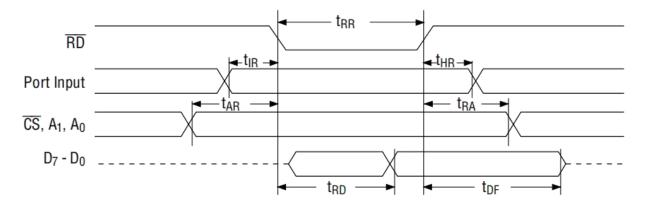

| Setup Time of Address to the Falling Edge of $\overline{RD}$                                                                  | t <sub>AR</sub>  | 20   | _     | ns   |            |  |

| Hold Time of Address to the Rising Edge of $\overline{RD}$                                                                    | t <sub>RA</sub>  | 0    | _     | ns   |            |  |

| RD Pulse Width                                                                                                                | t <sub>RR</sub>  | 100  | _     | ns   |            |  |

| Delay Time from the Falling Edge of RD to the Output ofDefined Data                                                           | t <sub>RD</sub>  | _    | 120   | ns   |            |  |

| Delay Time from the Rising Edge of $\overline{RD}$ to the Floating ofData Bus                                                 | t <sub>DF</sub>  | 10   | 75    | ns   |            |  |

| Time from the Rising Edge of $\overline{RD}$ or $\overline{WR}$ to the Next FallingEdge of $\overline{RD}$ or $\overline{WR}$ | t <sub>RV</sub>  | 200  | _     | ns   |            |  |

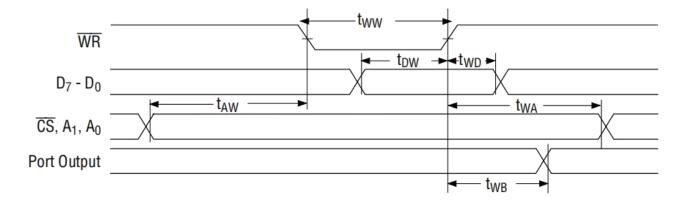

| Setup Time of Address before the Falling Edge of \$\overline{WR}\$                                                            | t <sub>AW</sub>  | 0    | _     | ns   |            |  |

| Hold Time of Address after the Rising Edge of WR                                                                              | t <sub>wA</sub>  | 20   | _     | ns   | 1          |  |

| WR Pulse Width                                                                                                                | t <sub>ww</sub>  | 150  | _     | ns   |            |  |

| Setup Time of Bus Data before the Rising Edge of WR                                                                           | t <sub>DW</sub>  | 50   | _     | ns   |            |  |

| Hold Time of Bus Data after the Rising Edge of $\overline{WR}$                                                                | t <sub>WD</sub>  | 30   | _     | ns   |            |  |

| Delay Time from the rising Edge of WR to the Output ofDefined Data                                                            | t <sub>WB</sub>  | _    | 200   | ns   |            |  |

| Setup Time of Port Data before the Falling Edge of RD                                                                         | t <sub>IR</sub>  | 20   | _     | ns   | 1          |  |

| Hold Time of Port Data after the Rising Edge of $\overline{\text{RD}}$                                                        | t <sub>HR</sub>  | 10   | _     | ns   | 1 4450 = 5 |  |

| ACK Pulse Width                                                                                                               | t <sub>AK</sub>  | 100  | _     | ns   | Load150 pF |  |

| STB Pulse Width                                                                                                               | t <sub>ST</sub>  | 100  | _     | ns   |            |  |

| Setup Time of Port Data before the rising Edge of STB                                                                         | t <sub>PS</sub>  | 20   | _     | ns   |            |  |

| Hold Time of Port Bus Data after the rising Edge of STB                                                                       | t <sub>PH</sub>  | 50   | _     | ns   |            |  |

| Delay Time from the Falling Edge of $\overline{\text{ACK}}$ to the Output ofDefined Data                                      | t <sub>AD</sub>  | _    | 150   | ns   |            |  |

| Delay Time from the Rising Edge of $\overline{ACK}$ to the Floating ofPort (Port A in Mode 2)                                 | t <sub>KD</sub>  | 20   | 250   | ns   |            |  |

| Delay Time from the Rising Edge of $\overline{\mathrm{WR}}$ to the Falling Edge of OBF                                        | t <sub>wob</sub> | _    | 150   | ns   |            |  |

| Delay Time from the Falling Edge of $\overline{\text{ACK}}$ to the Rising Edge of OBF                                         | t <sub>AOB</sub> | _    | 150   | ns   |            |  |

| Delay Time from the Falling Edge of $\overline{\text{STB}}$ to the Rising Edge of IBF                                         | t <sub>SIB</sub> | _    | 150   | ns   |            |  |

| Delay Time from the Rising Edge of $\overline{RD}$ to the Falling Edge of IBF                                                 | t <sub>RIB</sub> | _    | 150   | ns   |            |  |

| Delay Time from the the Falling Edge of $\ensuremath{\overline{R}} \overline{D}$ to the Falling Edgeof INTR                   | t <sub>RIT</sub> | _    | 200   | ns   | 1          |  |

| Delay Time from the Rising Edge of \$\overline{STB}\$ to the Rising Edge of INTR                                              | t <sub>SIT</sub> | _    | 150   | ns   | 1          |  |

| Delay Time from the Rising Edge of $\overline{\text{ACK}}$ to the Rising Edge of INTR                                         | t <sub>AIT</sub> | _    | 150   | ns   |            |  |

| Delay Time from the Falling Edge of $\overline{\mathrm{WR}}$ to the Falling Edge of INTR                                      | t <sub>wit</sub> | _    | 250   | ns   | 1          |  |

Note: Timing measured at  $V_L$  = 0.8 V and  $V_H$  = 2.2 V for both inputs and outputs.

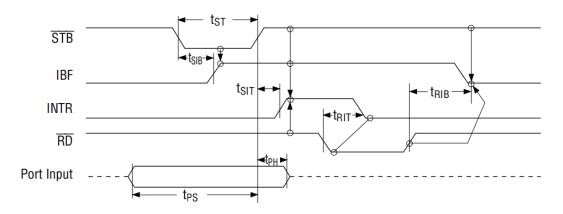

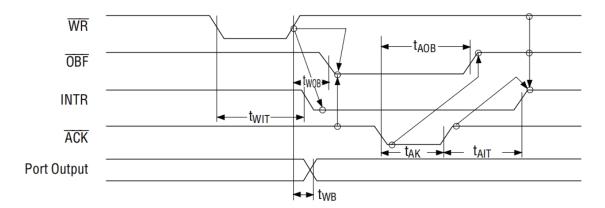

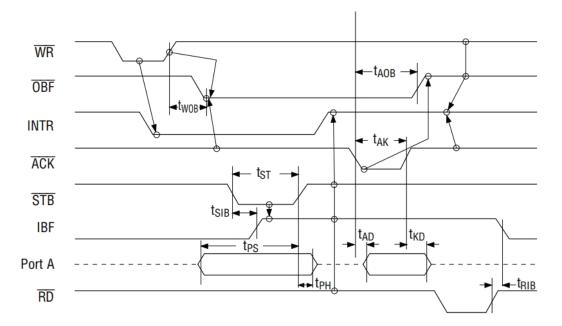

# **TIMING DIAGRAM**

# **Basic Input Operation (Mode 0)**

# **Basic Output Operation (Mode 0)**

# **Strobe Input Operation (Mode 1)**

# **Strobe Output Operation (Mode 1)**

# **Bidirectional Bus Operation (Mode 2)**

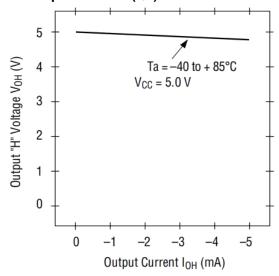

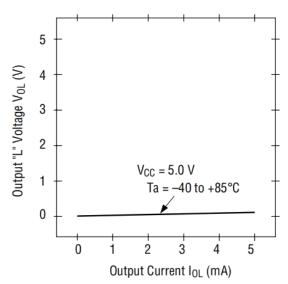

# **OUTPUT CHARACTERISTICS (REFERENCE VALUE)**

# 1 Output "H" Voltage (VOH) vs. Output Current (I<sub>OH</sub>)

# 2 Output "L" Voltage (VOL) vs. Output Current ( $I_{OL}$ )

Note: The direction of flowing into the device is taken as positive for the output current.

### **BASIC FUNCTIONAL DESCRIPTION**

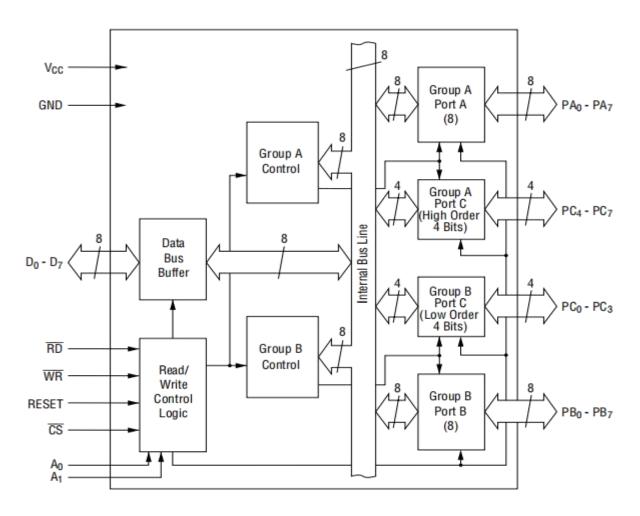

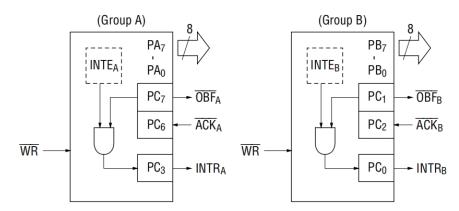

#### Group A and Group B

When setting a mode to a port having 24 bits, set it by dividing it into two groups of 12 bits each.

Group A: Port A (8 bits) and high order 4 bits of port C (PC7~PC4)

Group B: Port B (8 bits) and low order 4 bits of port C (PC3~PC0)

#### Mode 0, 1, 2

There are 3 types of modes to be set by grouping as follows:

Mode 0: Basic input operation/output operation (Available for both groups A and B)

Mode 1: Strobe input operation/output operation (Available for both groups A and B)

Mode 2: Bidirectional bus operation (Available for group A only)

When used in mode 1 or mode 2, however, port C has bits to be defined as ports for control signal for operation ports (port A for group A and port B for group B) of their respective groups.

#### Port A, B, C

The internal structure of 3 ports is as follows:

Port A: One 8-bit data output latch/buffer and one 8-bit data input latch

Port B: One 8-bit data input/output latch/buffer and one 8-bit data input buffer

Port C: One 8-bit data output latch/buffer and one 8-bit data input buffer (no latch for input)

#### Single bit set/reset function for port C

When port C is defined as an output port, it is possible to set (to turn to high level) or reset (to turn to low level) any one of 8 bits individually without affecting other bits.

### **OPERATIONAL DESCRIPTION**

#### **Control Logic**

Operations by addresses and control signals, e.g., read and write, etc. are as shown in the table below:

| Operaiton | <b>A</b> <sub>1</sub> | A <sub>0</sub> | CS | WR | RD | Operation                                 |

|-----------|-----------------------|----------------|----|----|----|-------------------------------------------|

|           | 0                     | 0              | 0  | 1  | 0  | Port A → Data Bus                         |

| Input     | 0                     | 1              | 0  | 1  | 0  | Port B → Data Bus                         |

|           | 1                     | 0              | 0  | 1  | 0  | Port C → Data Bus                         |

|           | 0                     | 0              | 0  | 0  | 1  | Data Bus → Port A                         |

| Output    | 0                     | 1              | 0  | 0  | 1  | Data Bus → Port B                         |

|           | 1                     | 0              | 0  | 0  | 1  | Data Bus → Port C                         |

| Control   | 1                     | 1              | 0  | 0  | 1  | Data Bus → Control Register               |

| Otherna   | 1                     | 1              | 0  | 1  | 0  | Illegal Condition                         |

| Others    | ×                     | ×              | 1  | ×  | ×  | Data bus is in the high impedance status. |

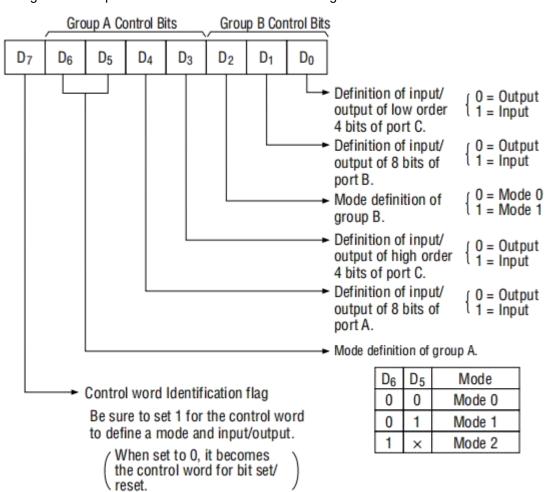

# **SETTING OF CONTROL WORD**

The control register is composed of 7-bit latch circuit and 1-bit flag as shown below.

#### **Precaution for Mode Selection**

The output registers for ports A and C are cleared to f each time data is written in the command register and the mode is changed, but the port B state is undefined.

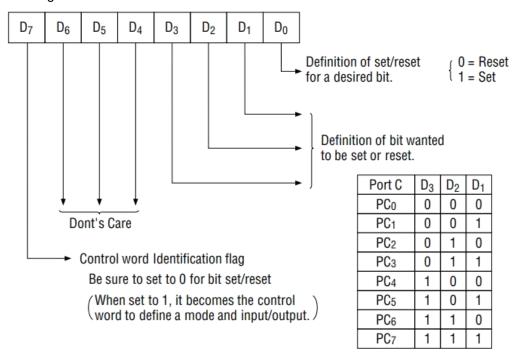

#### **Bit Set/Reset Function**

When port C is defined as output port, it is possible to set (set output to 1) or reset (set output to 0) any one of 8 bits without affecting other bits as shown below.

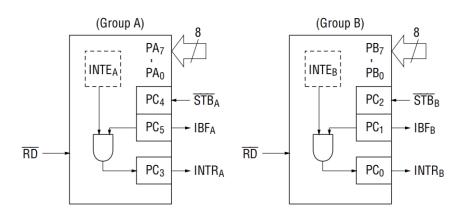

#### **Interrupt Control Function**

When the HG82C55A is used in mode 1 or mode 2, the interrupt signal for the CPU is provided. The interrupt request signal is output from port C. When the internal flip-flop INTE is set beforehand at this time, the desired interrupt request signal is output. When it is reset beforehand, however, the interrupt request signal is not output. The set/reset of the internal flip-flop is made by the bit set/reset operation for port C virtually.

Bit set → INTE is set → Interrupt allowed

Bit reset  $\rightarrow$  INTE is reset  $\rightarrow$  Interrupt inhibited

### **OPERATIONAL DESCRIPTION BY MODE**

#### 1. Mode 0 (Basic input/output operation)

Mode 0 makes the HG82C55A operate as a basic input port or output port. No control signals such as interrupt request, etc. are required in this mode. All 24 bits can be used as two-8-bit ports and two 4-bit ports. Sixteen combinations are then possible for inputs/ outputs. The inputs are not latched, but the outputs are.

|      | Control Word |                |                |    |    | rd             |                |                |        | Group A                     | Group B |                            |  |

|------|--------------|----------------|----------------|----|----|----------------|----------------|----------------|--------|-----------------------------|---------|----------------------------|--|

| Туре | D7           | D <sub>6</sub> | D <sub>5</sub> | D4 | D3 | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | Port A | High Order 4 Bits of Port C | Port B  | Low Order 4 Bits of Port C |  |

| 1    | 1            | 0              | 0              | 0  | 0  | 0              | 0              | 0              | Output | Output                      | Output  | Output                     |  |

| 2    | 1            | 0              | 0              | 0  | 0  | 0              | 0              | 1              | Output | Output                      | Output  | Input                      |  |

| 3    | 1            | 0              | 0              | 0  | 0  | 0              | 1              | 0              | Output | Output                      | Input   | Output                     |  |

| 4    | 1            | 0              | 0              | 0  | 0  | 0              | 1              | 1              | Output | Output                      | Input   | Input                      |  |

| 5    | 1            | 0              | 0              | 0  | 1  | 0              | 0              | 0              | Output | Input                       | Output  | Output                     |  |

| 6    | 1            | 0              | 0              | 0  | 1  | 0              | 0              | 1              | Output | Input                       | Output  | Input                      |  |

| 7    | 1            | 0              | 0              | 0  | 1  | 0              | 1              | 0              | Output | Input                       | Input   | Ouput                      |  |

| 8    | 1            | 0              | 0              | 0  | 1  | 0              | 1              | 1              | Output | Input                       | Input   | Input                      |  |

| 9    | 1            | 0              | 0              | 1  | 0  | 0              | 0              | 0              | Input  | Output                      | Output  | Output                     |  |

| 10   | 1            | 0              | 0              | 1  | 0  | 0              | 0              | 1              | Input  | Output                      | Output  | Input                      |  |

| 11   | 1            | 0              | 0              | 1  | 0  | 0              | 1              | 0              | Input  | Output                      | Input   | Output                     |  |

| 12   | 1            | 0              | 0              | 1  | 0  | 0              | 1              | 1              | Input  | Output                      | Input   | Input                      |  |

| 13   | 1            | 0              | 0              | 1  | 1  | 0              | 0              | 0              | Input  | Input                       | Output  | Output                     |  |

| 14   | 1            | 0              | 0              | 1  | 1  | 0              | 0              | 1              | Input  | Input                       | Output  | Input                      |  |

| 15   | 1            | 0              | 0              | 1  | 1  | 0              | 1              | 0              | Input  | Input                       | Input   | Output                     |  |

| 16   | 1            | 0              | 0              | 1  | 1  | 0              | 1              | 1              | Input  | Input                       | Input   | Input                      |  |

Notes: When used in mode 0 for both groups A and B

#### 2. Mode 1 (Strobe input/output operation)

In mode 1, the strobe, interrupt and other control signals are used when input/output operations are made from a specified port. This mode is available for both groups A and B. In group A at this time, port A is used as the data line and port C as the control signal.

Following is a description of the input operation in mode 1.

#### **STB** (Strobe input)

When this signal is low level, the data output from terminal to port is fetched into the internal latch of the port. This can be made independent from the CPU, and the data is not output to the data bus until the RD signal arrives from the CPU.

### IBF (Input buffer full flag output)

This is the response signal for the  $\overline{STB}$ . This signal when turned to high level indicates that data is fetched into the input latch. This signal turns to high level at the falling edge of  $\overline{STB}$  and to low level at the rising edge of  $\overline{RD}$ .

#### **INTR** (Interrupt request output)

This is the interrupt request signal for the CPU of the data fetched into the input latch. It is indicated by high level only when the internal INTE flip-flop is set. This signal turns to high level at the rising edge of the  $\overline{\text{STB}}$  (IBF = 1 at this time) and low level at the falling edge of the  $\overline{\text{RD}}$  when the INTE is set.

INTE A of group A is set when the bit for PC4 is set, while INTE B of group B is set when the bit for PC2 is set. Following is a description of the output operation of mode 1.

#### **OBF** (Output buffer full flag output)

This signal when turned to low level indicates that data is written to the specified port upon receipt of the  $\overline{WR}$  signal from the CPU. This signal turns to low level at the rising edge of the  $\overline{WR}$  and high level at the falling edge of the ACK.

#### **ACK** (Acknowledge input)

This signal when turned to low level indicates that the terminal has received data.

#### **INTR** (Interrupt request output)

This is the signal used to interrupt the CPU when a terminal receives data from the CPU via the HG82C55A. It indicates the occurrence of the interrupt in high level only when the internal INTE flip-flop is set. This signal turns to high level at the rising edge of the  $\overline{ACK}$  (OBF = 1 at this time) and low level at the falling edge of  $\overline{WR}$  when the INTE B is set.

INTE A of group A is set when the bit for PC6 is set, while INTE B of group B is set when the bit for PC2 is set.

#### **Mode 1 Input**

Note: Although belonging to group B, PC3 operates as the control signal of group A functionally.

### **Mode 1 Output**

### **Port C Function Allocation in Mode 1**

| Combination ofInput/Output Port C | Group A: Input<br>Group B: Input | Group A: Input Group<br>B: Output | Group A: Output<br>Group B: Input | Group A: Output<br>Group B: Output |

|-----------------------------------|----------------------------------|-----------------------------------|-----------------------------------|------------------------------------|

| PC0                               | INTRB                            | INTRB                             | INTRB                             | INTRB                              |

| PC1                               | IBFB                             | OBFB                              | IBFB                              | OBFB                               |

| PC <sub>2</sub>                   | STBB                             | ACKB                              | STBB                              | ACKB                               |

| PC3                               | INTRA                            | INTRA                             | INTRA                             | INTRA                              |

| PC4                               | STBA                             | STBA                              | I/O                               | I/O                                |

| PC5                               | IBFA                             | IBFA                              | I/O                               | I/O                                |

| PC6                               | I/O                              | I/O                               | ACKA                              | ACKA                               |

| PC7                               | I/O                              | I/O                               | OBFA                              | OBFA                               |

Note: I/O is a bit not used as the control signal, but it is available as a port of mode 0.

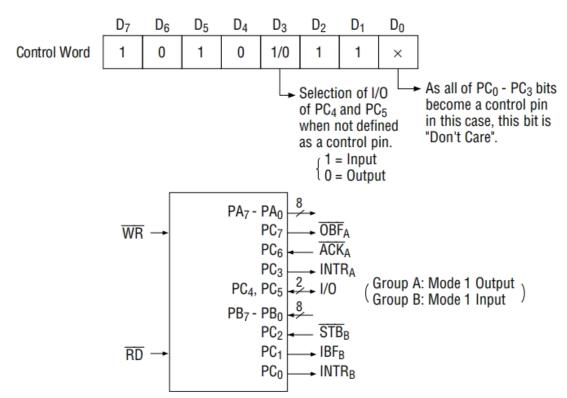

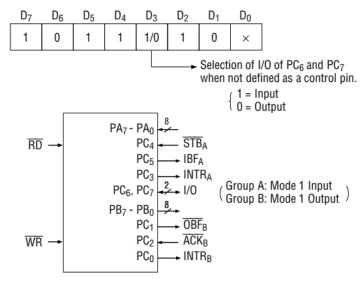

Examples of the relation between the control words and pins when used in mode 1 are shown below:

### (a) When group A is mode 1 output and group B is mode 1 input.

#### (b) When group A is mode 1 input and group B is mode 1 output.

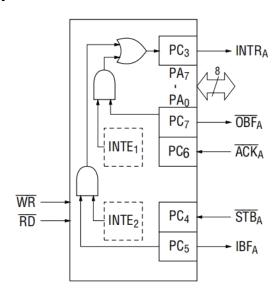

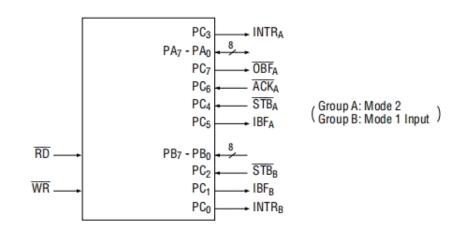

### 3. Mode 2 (Strobe bidirectional bus I/O operation)

In mode 2, it is possible to transfer data in 2 directions through a single 8-bit port. This operation is akin to a combination between input and output operations. Port C waits for the control signal in this case, too. Mode 2 is available only for group A, however.

Next, a description is made on mode 2.

#### **OBF** (Output buffer full flag output)

This signal when turned to low level indicates that data has been written to the internal output latch upon receipt of the WR signal from the CPU. At this time, port A is still in the high impedance status and the data is not yet output to the outside. This signal turns to low level at the rising edge of the WR and high level at the falling edge of the  $\overline{ACK}$ .

#### **ACK** (Acknowledge input)

When a low level signal is input to this pin, the high impedance status of port A is cleared, the buffer is enabled, and the data written to the internal output latch is output to port A. When the input returns to high level, port A is made into the high impedance status.

#### **STB** (Strobe input)

When this signal turns to low level, the data output to the port from the pin is fetched into the internal input latch. The data is output to the data bus upon receipt of the RD signal from the CPU, but it remains in the high impedance status until then.

#### IBF (Input buffer full flag output)

This signal when turned to high level indicates that data from the pin has been fetched into the input latch. This signal turns to high level at the falling edge of the STB and low level at the rising edge of the  $\overline{\text{RD}}$ .

### **INTR** (Interrupt request output)

This signal is used to interrupt the CPU and its operation in the same as in mode 1. There are two INTE flip-flops internally available for input and output to select either interrupt of input or output operation. The INTE1 is used to control the interrupt request for output operation and it can be reset by the bit set for PC6. INTE2 is used to control the interrupt request for the input operation and it can be set by the bit set for PC4.

# Mode 2 I/O Operation

Port C Function Allocation in Mode 2

| Port C          | Function                      |

|-----------------|-------------------------------|

| PC <sub>0</sub> |                               |

| PC <sub>1</sub> | Confirmed to the Group B Mode |

| PC <sub>2</sub> |                               |

| PC <sub>3</sub> | INTR <sub>A</sub>             |

| PC <sub>4</sub> | STBA                          |

| PC <sub>5</sub> | IBF <sub>A</sub>              |

| PC <sub>6</sub> | ACK <sub>A</sub>              |

| PC <sub>7</sub> | OBF <sub>A</sub>              |

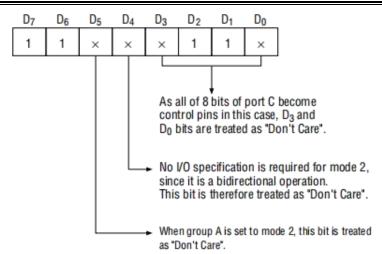

Following is an example of the relation between the control word and the pin when used in mode 2. When input in mode 2 for group A and in mode 1 for group B.

# 4. When Group A is Different in Mode from Group B

Group A and group B can be used by setting them in different modes each other at the same time. When either group is set to mode 1 or mode 2, it is possible to set the one not defined as a control pin in port C to both input and output as port which operates in mode 0 at the 3rd and 0th bits of the control word.

# (Mode combinations that define no control bit at port C)

|   | Croup A          | Croup B          | Port C                        |                  |                  |                         |                   |                         |                                         |                   |  |  |

|---|------------------|------------------|-------------------------------|------------------|------------------|-------------------------|-------------------|-------------------------|-----------------------------------------|-------------------|--|--|

|   | Group A          | Group B          | PC7                           | PC6              | PC5              | PC4                     | PC3               | PC2                     | PC1                                     | PC0               |  |  |

| 1 | Mode 1input      | Mode 0           | I/O                           | I/O              | IBF <sub>A</sub> | <u>STB</u> <sub>A</sub> | INTR <sub>A</sub> | I/O                     | I/O                                     | I/O               |  |  |

| 2 | Mode 0<br>Output | Mode 0           | OBFA                          | ĀCK <sub>A</sub> | I/O              | I/O                     | INTR <sub>A</sub> | I/O                     | I/O                                     | I/O               |  |  |

| 3 | Mode 0           | Mode 1<br>Input  | I/O                           | I/O              | I/O              | I/O                     | I/O               | <u>STB</u> <sub>B</sub> | IBF <sub>B</sub>                        | INTR <sub>B</sub> |  |  |

| 4 | Mode 0           | Mode 1<br>Output | I/O                           | I/O              | I/O              | I/O                     | I/O               | ĀCK <sub>B</sub>        | <del>OBF</del> <sub>B</sub>             | INTR <sub>B</sub> |  |  |

| 5 | Mode 1<br>Input  | Mode 1<br>Input  | I/O                           | I/O              | IBF <sub>A</sub> | <u>STB</u> <sub>A</sub> | INTR <sub>A</sub> | <u>STB</u> <sub>B</sub> | IBF <sub>B</sub>                        | INTR <sub>B</sub> |  |  |

| 6 | Mode 1<br>Input  | Mode 1<br>Output | I/O                           | I/O              | IBF <sub>A</sub> | <u>STB</u> <sub>A</sub> | INTR <sub>A</sub> | ĀCK <sub>B</sub>        | <del></del> <del>OBF</del> <sub>B</sub> | INTR <sub>B</sub> |  |  |

| 7 | Mode 1<br>Output | Mode 1<br>Input  | $\overline{\mathrm{OBF}}_{A}$ | ACK <sub>A</sub> | I/O              | I/O                     | INTR <sub>A</sub> | <u>STB</u> <sub>B</sub> | IBF <sub>B</sub>                        | INTR <sub>B</sub> |  |  |

| 8 | Mode 1<br>Output | Mode 1<br>Output | <del>OBF</del> <sub>A</sub>   | ĀCK <sub>A</sub> | I/O              | I/O                     | INTR <sub>A</sub> | ĀCK <sub>B</sub>        | ŌBF <sub>B</sub>                        | INTR <sub>B</sub> |  |  |

| 9 | Mode 2           | Mode 0           | OBFA                          | ĀCK <sub>A</sub> | IBF <sub>A</sub> | STBA                    | INTR <sub>A</sub> | I/O                     | I/O                                     | I/O               |  |  |

Controlled at the 3rd bit (D3) of the Control Word

Controlled at the 0th bit (D0) of the Control Word

When the I/O bit is set to input in this case, it is possible to access data by the normal port C read operation. When set to output, PC<sub>7</sub>-PC<sub>4</sub> bits can be accessed by the bit set/reset function only.

Meanwhile, 3 bits from PC<sub>2</sub> to PC<sub>0</sub> can be accessed by normal write operation.

The bit set/reset function can be used for all of PC<sub>3</sub>-PC<sub>0</sub> bits. Note that the status of port C varies according to the combination of modes like this.

# 5. Port C Status Read

When port C is used for the control signal, that is, in either mode 1 or mode 2, each control signal and bus status signal can be read out by reading the content of port C.

The status read out is as follows:

|    | Group A          | Group P          | Status Read on the Data Bus |                   |                  |                   |                   |                   |                  |                   |  |  |

|----|------------------|------------------|-----------------------------|-------------------|------------------|-------------------|-------------------|-------------------|------------------|-------------------|--|--|

|    | Group A          | Group B          | D <sub>7</sub>              | D <sub>6</sub>    | D <sub>5</sub>   | D <sub>4</sub>    | D <sub>3</sub>    | D <sub>2</sub>    | D <sub>1</sub>   | D <sub>0</sub>    |  |  |

| 1  | Mode 1Input      | Mode 0           | I/O                         | I/O               | IBFA             | INTEA             | INTRA             | I/O               | I/O              | I/O               |  |  |

| 2  | Mode 1<br>Output | Mode 0           | OBFA                        | INTEA             | I/O              | I/O               | INTR <sub>A</sub> | I/O               | I/O              | I/O               |  |  |

| 3  | Mode 0           | Mode 1<br>Input  | I/O                         | I/O               | I/O              | I/O               | I/O               | INTE <sub>B</sub> | IBF <sub>B</sub> | INTR <sub>B</sub> |  |  |

| 4  | Mode 0           | Mode 1<br>Output | I/O                         | I/O               | I/O              | I/O               | I/O               | INTEB             | OBF <sub>B</sub> | INTR <sub>B</sub> |  |  |

| 5  | Mode 1<br>Input  | Mode 1<br>Input  | I/O                         | I/O               | IBF <sub>A</sub> | INTE <sub>A</sub> | INTR <sub>A</sub> | INTE <sub>B</sub> | IBF <sub>B</sub> | INTR <sub>B</sub> |  |  |

| 6  | Mode 1<br>Input  | Mode 1<br>Output | I/O                         | I/O               | IBF <sub>A</sub> | INTE <sub>A</sub> | INTR <sub>A</sub> | INTE <sub>B</sub> | OBF <sub>B</sub> | INTR <sub>B</sub> |  |  |

| 7  | Mode 1<br>Output | Mode 1<br>Input  | <del>OBF</del> A            | INTEA             | I/O              | I/O               | INTRA             | INTEB             | IBF <sub>B</sub> | INTR <sub>B</sub> |  |  |

| 8  | Mode 1<br>Output | Mode 1<br>Output | OBFA                        | INTE <sub>A</sub> | I/O              | I/O               | INTR <sub>A</sub> | INTE <sub>B</sub> | OBF <sub>B</sub> | INTR <sub>B</sub> |  |  |

| 9  | Mode 2           | Mode 0           | OBFA                        | INTE <sub>1</sub> | IBF <sub>A</sub> | INTE <sub>2</sub> | INTR <sub>A</sub> | I/O               | I/O              | I/O               |  |  |

| 10 | Mode 2           | Mode 1<br>Input  | <del>OBF</del> A            | INTE <sub>1</sub> | IBF <sub>A</sub> | INTE <sub>2</sub> | INTRA             | INTE <sub>B</sub> | IBF <sub>B</sub> | INTR <sub>B</sub> |  |  |

| 11 | Mode 2           | Mode 1<br>Output | <del>OBF</del> A            | INTE <sub>1</sub> | IBF <sub>A</sub> | INTE <sub>2</sub> | INTR <sub>A</sub> | INTE <sub>B</sub> | OBF <sub>B</sub> | INTR <sub>B</sub> |  |  |

# 6. Reset of HG82C55A

Be sure to keep the RESET signal at power ON in the high level at least for 50  $\mu$ s. Subsequently, it becomes the input mode at a high level pulse above 500 ns.

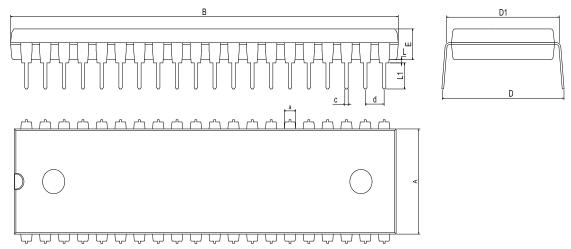

# **Physical Dimensions**

# DIP-40

| Dimensions In Millimeters(DIP-40) |       |       |       |       |      |      |      |      |      |          |  |

|-----------------------------------|-------|-------|-------|-------|------|------|------|------|------|----------|--|

| Symbol:                           | Α     | В     | D     | D1    | Е    | L    | L1   | а    | С    | d        |  |

| Min:                              | 13.21 | 51.82 | 16.00 | 14.99 | 3.71 | 0.38 | 3.00 | 1.45 | 0.38 | 2.54 BSC |  |

| Max:                              | 14.22 | 53.09 | 17.28 | 15.49 | 3.91 | 0.55 | 3.60 | 1.65 | 0.53 |          |  |

# **Revision History**

| REVISION<br>NUMBER | DATE    | REVISION                                                      | PAGE |

|--------------------|---------|---------------------------------------------------------------|------|

| V1.0               | 2016-8  | New                                                           | 1-22 |

| V1.1               | 2019-9  | Update encapsulation type、Add annotation for Maximum Ratings. | 1、4  |

| V1.2               | 2024-11 | RESET signal time at power ON 、Update Lead Temperature        | 4、19 |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.