# Dual Channel PWM Controller with I<sup>2</sup>C Interface Control for IMVP9.1 CPU Core Power Supply

### **General Description**

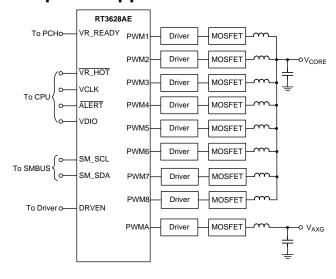

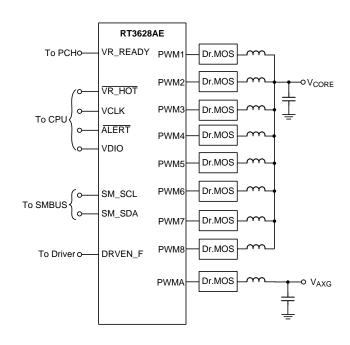

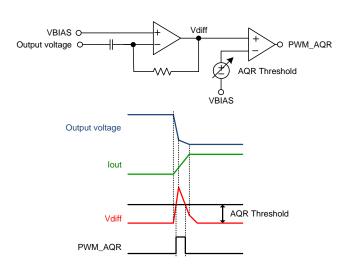

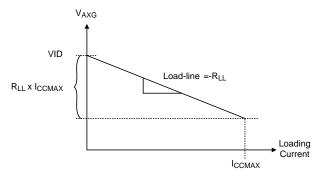

The RT3628AE is a synchronous buck controller which supports 2 output rails and can fully meet Intel IMVP9.1 requirements. The RT3628AE adopts G-NAVP<sup>TM</sup> (Green Native AVP) which is Richtek's proprietary topology derived from finite DC gain of EA amplifier with current mode control, making it easy to set the droop to meet all Intel CPU requirements of AVP (Adaptive Voltage Positioning). Based on the G-NAVP<sup>TM</sup> topology, the RT3628AE features a new generation of quick response mechanism (Adaptive Quick Response, AQR) to optimize AVP performance during load transient and reduce output capacitors. The RT3628AE integrates a high accuracy ADC for platform and function settings, such as ICCMAX, switching frequency, over-current threshold and AQR trigger level. The RT3628AE provides VR Ready and thermal indicators. It also features complete fault protection functions, including over-voltage (OV), under-voltage (UV), over-current (OC) and under-voltage lockout (UVLO). The RT3628AE supports several functions which can be set by I<sup>2</sup>C interface, like thermal balance adjustment, dynamic load line, voltage offset setting, fix VID setting, protection report, protection disable and Current/PSYS/Temperature report.

### **Applications**

- IMVP9.1 Intel Core/AXG Supply

- Desktop and Notebook Computer

- AVP Step-Down Converter

### **Features**

- Intel IMVP9.1 Compliant

- 8/7/6/5/4 Phase (CORE VR) + 1 Phase (AXG VR)

PWM Controller

- G-NAVP<sup>TM</sup> (Green Native Adaptive Voltage Positioning) Topology

- 0.5% DAC Accuracy

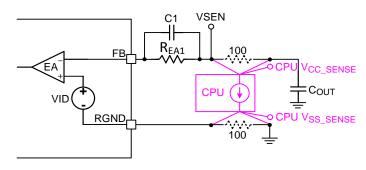

- Differential Remote Voltage Sensing

- Built-in ADC for Platform Programming and Reporting

- Accurate Current Balance

- Diode Emulation Mode at Light Load Condition

- Fast Transient Response : Adaptive Quick Response (AQR)

- VR Ready Indicator

- OVP, OCP, UVP with Flag

- . Switching Frequency Setting

- Slew Rate Setting

- DVID Enhancement

- Acoustic Noise Suppression

- Zero Load-line

- Rail Disable

- Standard I<sup>2</sup>C Protocol Interface

- ▶ Thermal Balance Adjustment

- **▶** Dynamic Load Line Setting

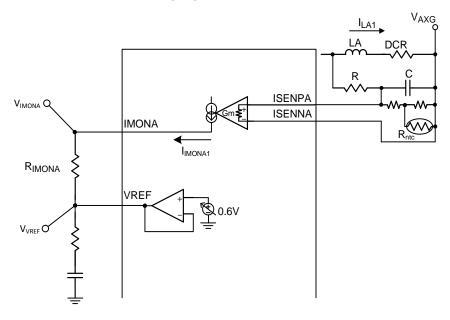

- ▶ Voltage Offset Setting

- ► Fixed VID Setting

- ▶ Protection Report and Protection Disable

- ► Current/PSYS/Temperature Report

- Soldering Good Detection

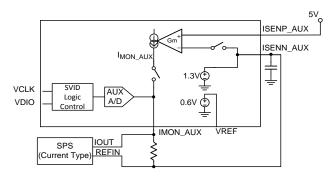

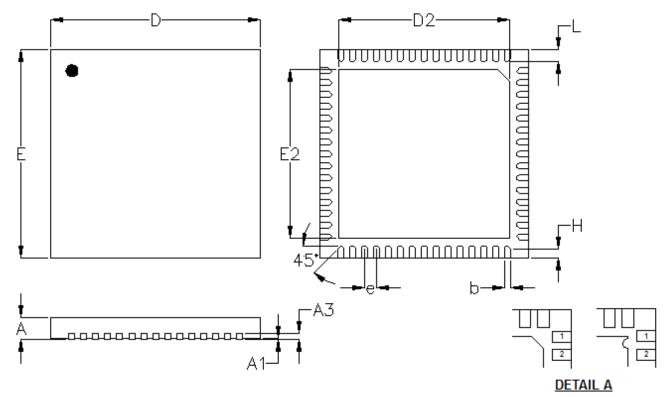

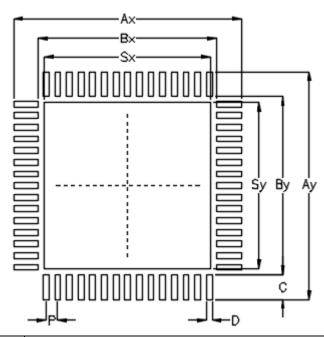

- Small 60-Lead WQFN Package

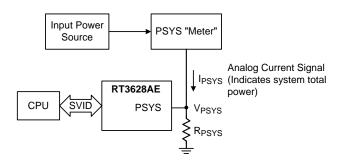

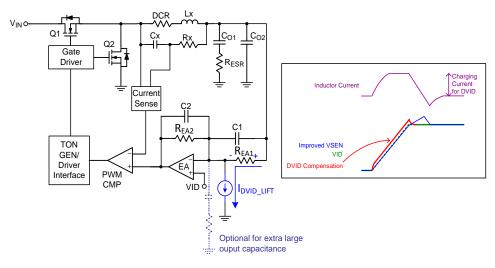

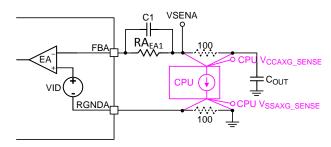

### **Simplified Application Circuit**

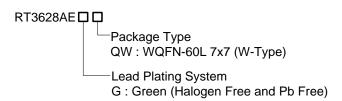

### **Ordering Information**

### Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

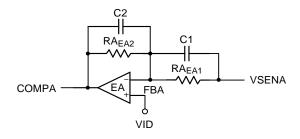

### **Marking Information**

RT3628AEGQW: Product Number YMDNN: Date Code

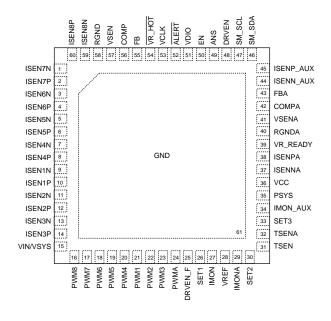

### **Pin Configuration**

(TOP VIEW)

WQFN-60L7x7

**Functional Pin Description**

| Pin No.                           | Pin Name   | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 11, 13, 7, 5,<br>3, 1, 59      | ISEN[1:8]N | Negative inputs of current-sense amplifier of multi-phase CORE rail VR channel 1, 2, 3, 4, 5, 6, 7 and 8.                                                                                                                                                                                                                                                                                                        |

| 10, 12, 14, 8, 6,<br>4, 2, 60     | ISEN[1:8]P | Positive inputs of current-sense amplifier of multi-phase CORE rail VR channel 1, 2, 3, 4, 5, 6, 7 and 8.                                                                                                                                                                                                                                                                                                        |

| 15                                | VIN/VSYS   | Input voltage pin. Connect a low pass filter which time constant is at the switching frequency to this pin for setting on-time.                                                                                                                                                                                                                                                                                  |

| 21, 22, 23, 20,<br>19, 18, 17, 16 | PWM[1:8]   | PWM output for CORE rail VR channel 1, 2, 3, 4, 5, 6, 7 and 8. The tri-state window = 1.6V to 2.2V.                                                                                                                                                                                                                                                                                                              |

| 24                                | PWMA       | PWM output for AXG rail VR. The tri-state window = 1.6V to 2.2V.                                                                                                                                                                                                                                                                                                                                                 |

| 25                                | DRVEN_F    | External driver mode control and the output high level is VCC. As received PS4 command, this pin is in floating state. For discrete power MOSFET driver application, connecting $100k\Omega$ resister to GND is required.                                                                                                                                                                                        |

| 26                                | SET1       | Function setting for DVID slew rate, I <sup>2</sup> C address, CORE rail on-time (switch frequency), VR_HOT assertion during DVID current limiting, and AUX rail ICCMAX. Connect the SET1 to 5V and turn on the EN pin, if the soldering is good, both rails outputs are VBOOT.                                                                                                                                  |

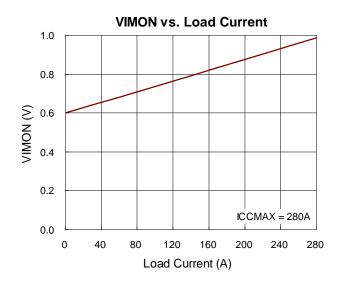

| 27                                | IMON       | CORE rail VR current monitor output for controller. This pin outputs a current proportional to the output current.                                                                                                                                                                                                                                                                                               |

| 28                                | VREF       | Voltage source output. During Controller internal setting period, it outputs 3.2V. In normal operation, it outputs 0.6V to offset IMON, IMONA and IMON_AUX signal. While controller shuts down or sets all rail in PS4, voltage source shuts down. An exact $0.47\mu F$ capacitor and $3.9\Omega$ resistor from this pin to GND are required for stability.                                                      |

| 29                                | IMONA      | AXG rail VR current monitor output for controller. This pin outputs a current proportional to the output current.                                                                                                                                                                                                                                                                                                |

| 30                                | SET2       | Function setting for CORE rail adaptive ramp trigger level, ICCMAX of AXG rail, dual phases function and AXG rail on-time (switch frequency).                                                                                                                                                                                                                                                                    |

| 31                                | TSEN       | Thermal sense input for CORE rail. Function setting for CORE rail ZCD threshold, CORE and AXG rail current gain (Ai).                                                                                                                                                                                                                                                                                            |

| 32                                | TSENA      | Thermal sense input for AXG rail. Function setting for CORE and AXG rail sum-OC threshold, AXG rail ZCD threshold and CORE rail adaptive quick response threshold.                                                                                                                                                                                                                                               |

| 33                                | SET3       | Function setting for CORE and AXG rail DAC step, CORE rail ICCMAX, CORE and AXG rail VBOOT (boot voltage depends on SET3 VID table setting), and AXG rail adaptive ramp trigger level.                                                                                                                                                                                                                           |

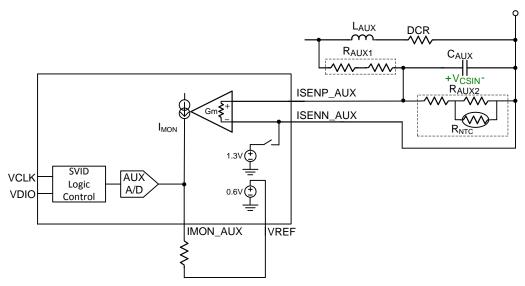

| 34                                | IMON_AUX   | AUX rail VR current monitor output for controller. This pin outputs a current proportional to the output current.                                                                                                                                                                                                                                                                                                |

| 35                                | PSYS       | System input power monitor. Place the PSYS resistor as close to the IC as possible. The input power domain (SVID Address 0x0Dh) rail can be disabled by pulling the voltage at the PSYS pin > (VCC – 0.5V). RT3628AE will reject any commands to the input power domain rail. If the platform doesn't support PSYS function, It is recommended to connect PSYS pin to GND to avoid affecting system performance. |

| 36                                | VCC        | Controller power supply. Connect this pin to 5V and place an RC filter, R = $1\Omega$ and C = $2.2\mu$ F. The decoupling capacitor should be placed as close to PWM controller as possible. The R is recommended as 0603 size.                                                                                                                                                                                   |

Copyright © 2021 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation

| Pin No.             | Pin Name  | Pin Function                                                                                                                            |

|---------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

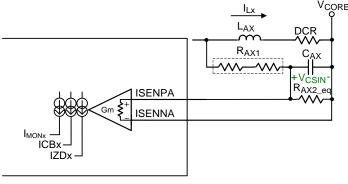

| 37                  | ISENNA    | Negative inputs of current-sense amplifier of AXG rail VR.                                                                              |

| 38                  | ISENPA    | Positive inputs of current-sense amplifier of AXG rail VR.                                                                              |

| 39                  | VR_READY  | VR ready indicator.                                                                                                                     |

| 40                  | RGNDA     | Return ground for AXG rail VR. This pin is the negative node of the differential remote sense.                                          |

| 41                  | VSENA     | AXG rail VR voltage sense input. This pin is connected to the terminal of AXG rail VR output voltage.                                   |

| 42                  | СОМРА     | AXG rail VR error amplifier output pin.                                                                                                 |

| 43                  | FBA       | Negative input of the error amplifier. This pin is for AXG rail VR output voltage feedback to controller.                               |

| 44                  | ISENN_AUX | Negative inputs of current-sense amplifier of AUX rail VR.                                                                              |

| 45                  | ISENP_AUX | Positive inputs of current-sense amplifier of AUX rail VR.                                                                              |

| 46                  | SM_SDA    | Data line for the I <sup>2</sup> C interface.                                                                                           |

| 47                  | SM_SCL    | Clock input for the I <sup>2</sup> C interface.                                                                                         |

| 48                  | DRVEN     | External driver mode control and the output high level is VCC. As the PS4 command is received, this pin is in low state.                |

| 49                  | ANS       | Acoustic noise suppression function setting. When pulling to VCC, this function can be enabled. This pin is not allowed to be floating. |

| 50                  | EN        | Controller enable pin. A logic high signal enables the controller. Don't drive this pin voltage higher than $V_{CC}-1.2V$ at any time.  |

| 51                  | VDIO      | VR and CPU data transmission interface.                                                                                                 |

| 52                  | ALERT     | SVID alert. (Active low)                                                                                                                |

| 53                  | VCLK      | Synchronous clock from the CPU.                                                                                                         |

| 54                  | VR_HOT    | Thermal monitor output. (Active low).                                                                                                   |

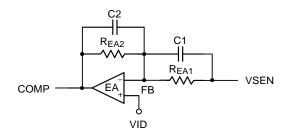

| 55                  | FB        | Negative input of the error amplifier. This pin is for CORE rail VR output voltage feedback to controller.                              |

| 56                  | COMP      | CORE rail VR error amplifier output pin.                                                                                                |

| 57                  | VSEN      | CORE rail VR voltage sense input. This pin is connected to the terminal of CORE rail VR output voltage.                                 |

| 58                  | RGND      | Return ground for CORE rail VR. This pin is the negative node of the differential remote sense.                                         |

| 61<br>(Exposed Pad) | GND       | Ground. The exposed pad must be soldered to a large PCB and connected to GND with enough VIA numbers for maximum power dissipation.     |

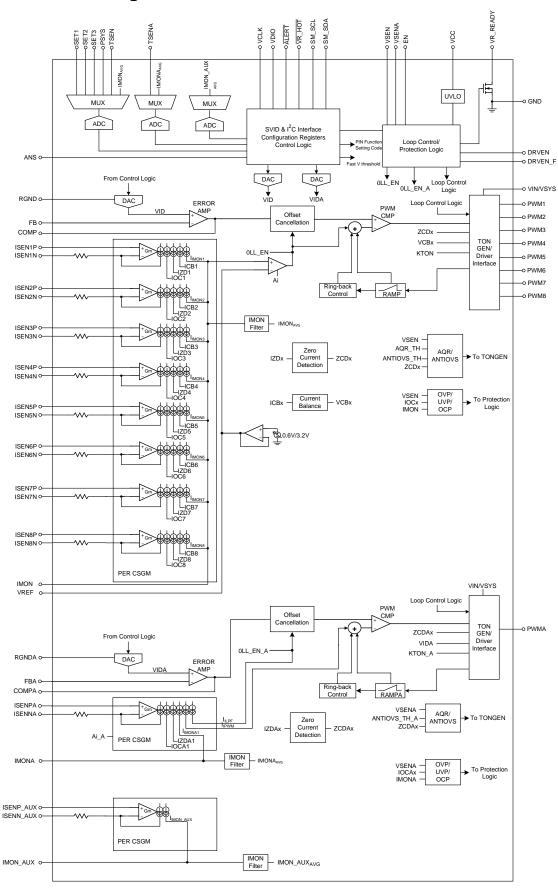

### **Functional Block Diagram**

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

### **Operation**

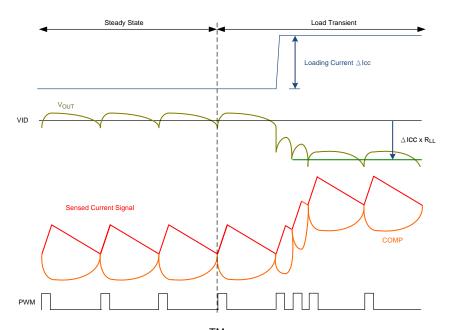

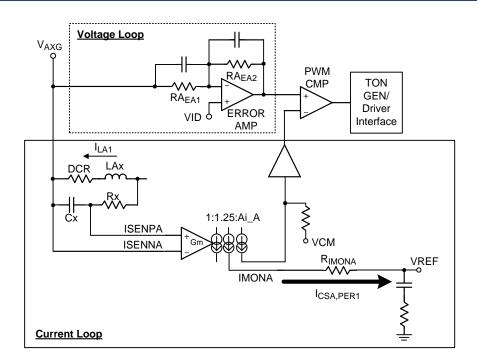

### **G-NAVP**<sup>TM</sup> Control Mode

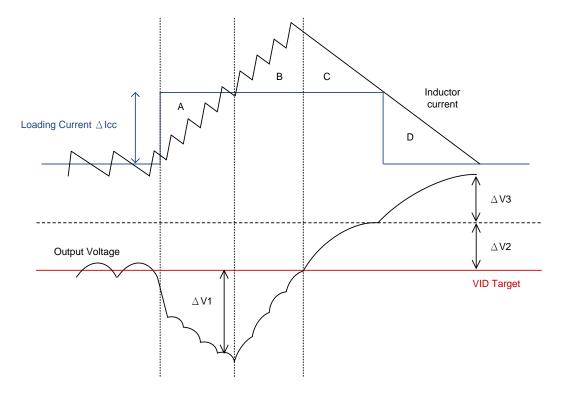

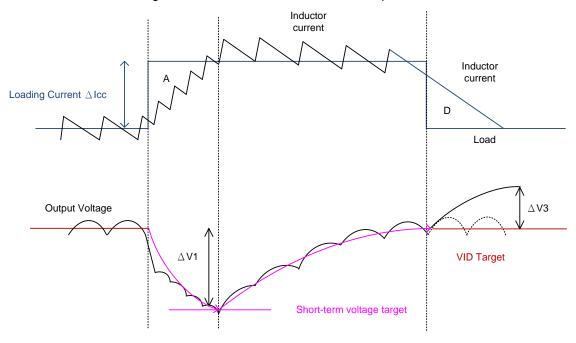

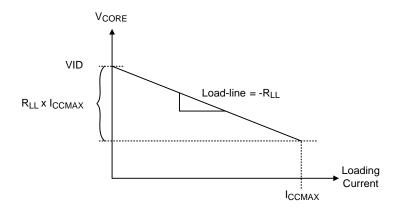

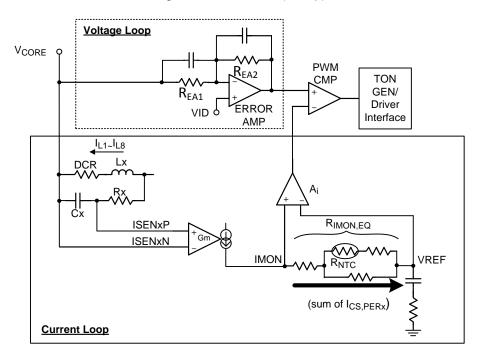

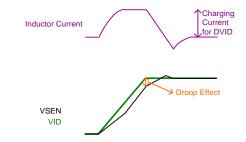

The RT3628AE adopts G-NAVPTM (Green Native AVP) which is Richtek's proprietary topology. It is derived from current mode constant on-time control with finite DC gain of error amplifier and DC offset cancellation. The topology can achieve easy load-line design and provide high DC accuracy and fast transient response. When the sensed current signal reaches the sensed voltage signal, the RT3628AE generates a PWM pulse to achieve loop modulation. The left part of Figure 1 shows the basic G-NAVP<sup>TM</sup> behavior waveforms. The COMP signal is the sensed voltage, that is inverted and amplified signal of output voltage. While current loading is increasing, referring to the right part of Figure 1, the CCOMP rises due to output voltage droop. Then, the rising COMP forces PWM to turn-on earlier and closer. While inductor current reaches loading current, the COMP enters another steady state of higher voltage and the corresponding output voltage is in the steady state of lower voltage. The loadline, voltage drooping which is proportional to loading current, is achieved.

Figure 1. G-NAVP<sup>TM</sup> Behavior Waveform

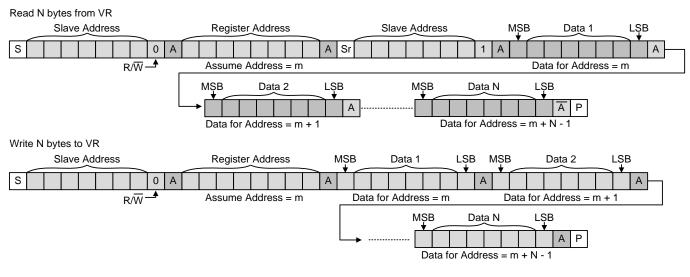

### I<sup>2</sup>C and SVID Interface/Control **Logic/Configuration Registers**

The SVID Interface receives or transmits SVID signal with CPU. The I<sup>2</sup>C Interface receives or transmits I<sup>2</sup>C signal with SMBus. The control logic executes command (Read/Write registers, SetVID, SetPS) and sends related signals to control VR. The configuration registers include function setting registers and CPU required registers.

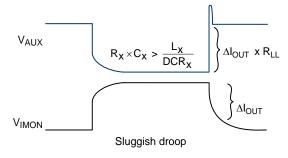

### **IMON Filter**

The IMON Filter is used to average current signal by analog low-pass filter. It outputs IMON<sub>AVG</sub>, IMONAAVG and IMON\_AUXAVG to the MUX of ADC for current reporting.

### **MUX and ADC**

The MUX supports the inputs for SET1, SET2, SET3, TSEN, TSENA , PSYS, IMONAVG, IMONAVG and IMON\_AUXAVG. The ADC converts these analog signals to digital codes for reporting or function settings.

### **UVLO**

The UVLO Detects the VCC voltage. As VCC exceeds the threshold, the controller issues POR = high and waits EN. After both POR and for EN are ready, the controller is enabled.

### **Loop Control/Protection Logic**

It controls power-on/off sequence, protections, power state transition and PWM sequence.

#### DAC

The DAC generates a reference VID voltage according to the VID code sent by Control Logic. According to SetVID command, Control Logic dynamically changes VID voltage to the target voltage with required slew rate.

### **ERROR AMP**

The ERROR AMP inverts and amplifies the difference between output voltage and VID with externally set finite DC gain. The output signal is COMP for PWM triggers.

### **PER CSGM**

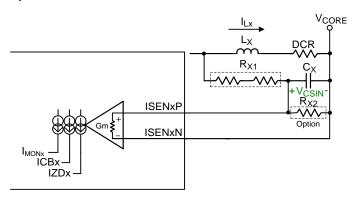

The PER CSGM senses per-phase inductor current. The outputs are used for loop response, current balance, zero current detection, current reporting and over-current protection.

### **SUM CSGM**

The SUM CSGM senses total inductor current with RIMON gain adjustment. SUM CSGM output current ratio can also be set by PIN-SETTING(Ai/Ai\_A). It helps wide application range of DCR and load-line. SUM CSGM output is used for PWM trigger.

### **RAMP**

The RAMP helps loop stability and transient response.

### **PWM CMP**

The PWM comparator compares COMP signal and sum current signal based on RAMP to trigger PWM.

#### **Offset Cancellation**

The offset cancellation cancels the current signal/comp voltage ripple issue to control output voltage accuracy.

### **Current Balance**

Per-phase current sense signal is compared with sensed average current. The comparison result adjusts each phase PWM width to optimize current and thermal balance.

#### **Zero Current Detection**

The Zero Current Detection detects whether each phase current crosses zero current. The result is used for DEM power saving and overshoot reduction (anti-overshoot function).

### **AQR/ANTIOVS**

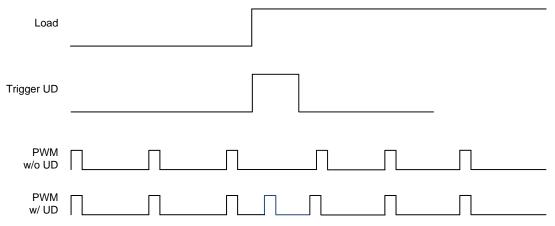

The AQR is a new generation of quick response mechanism (Adaptive Quick Response, AQR) which detects loading rising edge and allows all PWMs to turn on. The PWM pulse width triggered by AQR is adaptive to loading level. The AQR trigger level can be set by PIN-SETTING. ANTIOVS can help overshoot reduction which detects loading falling edge and forces all PWMs in tri-state until the zero current is detected.

#### **TONGEN/Driver Interface**

The PWM comparator output signal triggers TONGEN to generate PWM pulse. The PWM sequence is controlled by Loop Control. The PWM pulse width is determined by frequency setting, current balance output and Adaptive Quick Response (AQR) settings. Once AQR is triggered, VR allows all PWMs to turn on at the same time. Driver interface provides high/low/tri-state to drive external driver. In power saving mode, driver interface force PWM in tri-state to turn off high-side and low-side power MOSFETs according to zero current detection output. In addition, the PWM state is controlled by protection logic. Different protections force required PWM state.

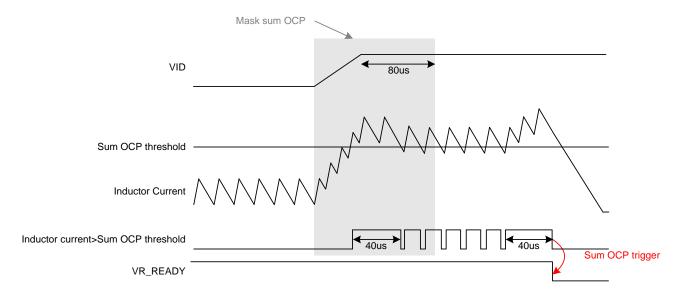

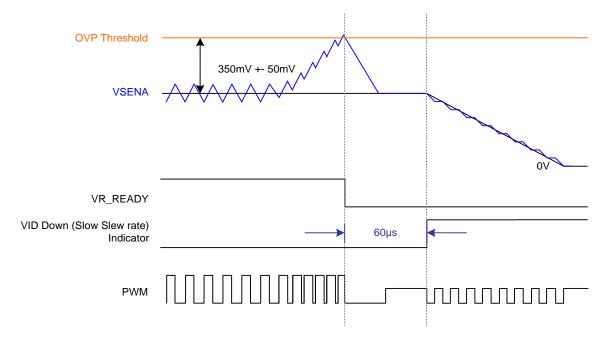

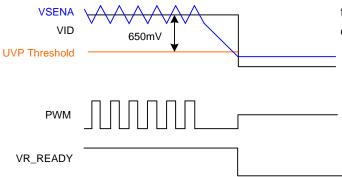

### OVP/UVP/OCP

Over-voltage protection / under-voltage protection / over-current protection.

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

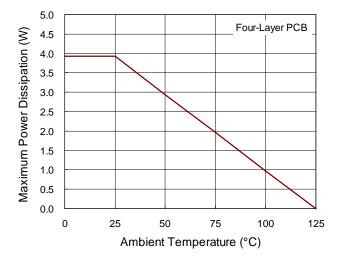

### Absolute Maximum Ratings (Note 1)

| • VIN/VSYS to GND                                                           | 0.3V to 28V    |

|-----------------------------------------------------------------------------|----------------|

| • VCC to GND                                                                | 0.3V to 6.5V   |

| • RGND to GND                                                               | 0.3V to 0.3V   |

| • Other Pins                                                                | 0.3V to 6.8V   |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| WQFN-60L 7x7                                                                | 3.92W          |

| Package Thermal Resistance (Note 2)                                         |                |

| WQFN-60L 7x7, $\theta$ JA                                                   | 25.5°C/W       |

| WQFN-60L 7x7, $\theta$ JC                                                   | 6.5°C/W        |

| Lead Temperature (Soldering, 10 sec.)                                       | 260°C          |

| Junction Temperature                                                        | 150°C          |

| Storage Temperature Range                                                   | 65°C to 150°C  |

| • ESD Susceptibility (Note 3)                                               |                |

| HBM (Human Body Model)                                                      | 2kV            |

| Recommended Operating Conditions (Note 4)                                   |                |

| VIN/VSYS to GND                                                             | 4.5V to 24V    |

| Supply Input Voltage, VCC                                                   | 4.75V to 5.25V |

| Junction Temperature Range                                                  | 10°C to 105°C  |

### **Electrical Characteristics**

$(VCC = 5V, typical values are referenced to T_J = 25^{\circ}C, Min and Max values are referenced to T_J from <math>-10^{\circ}C$  to  $105^{\circ}C$ , unless otherwise specified)

| Parameter                                            | Symbol           | Symbol Test Conditions                          |      | Тур | Max  | Unit |  |

|------------------------------------------------------|------------------|-------------------------------------------------|------|-----|------|------|--|

| Supply Input                                         |                  |                                                 |      |     |      |      |  |

| Controller Supply Current                            | Ivcc             | VCC = 5V, EN = H, no switching                  |      | 13  |      | mA   |  |

| Controller Supply Current under PS4 all call         | IVCC_PS4         | VCC = 5V, EN = H, PS4<br>all call               |      | 85  |      | μΑ   |  |

| VR Shutdown Current                                  | Ishdn            | VCC = 5V, EN = L                                |      |     | 15   | μΑ   |  |

| Per Phase Current Sense An                           | nplifier         |                                                 |      |     |      |      |  |

| Recommended Input Voltage<br>Range for High Accuracy | VIN_PCS          | Recommend Input Voltage Range for High Accuracy | -10  |     | 80   | mV   |  |

| Current Sense Gain                                   | GAIN_PCS         |                                                 | 0.97 | 1   | 1.03 | V/V  |  |

| Current Sense Resistor                               | R <sub>INT</sub> |                                                 |      | 1   |      | kΩ   |  |

| TON Setting                                          |                  |                                                 |      |     |      |      |  |

| ON-Time Setting                                      | Ton              | VIN = 12V, VID = 1.8V,<br>freq. = 350kHz        |      | 428 |      | ns   |  |

| Parameter                           |                   | Symbol                 | Test Conditions                                               | Min          | Тур          | Max          | Unit |

|-------------------------------------|-------------------|------------------------|---------------------------------------------------------------|--------------|--------------|--------------|------|

| Protections                         |                   |                        | •                                                             |              |              |              |      |

| VCC POR                             |                   | V <sub>POR</sub>       |                                                               |              |              | 4.45         | V    |

| VCC Under-Voltage Lockout<br>(UVLO) |                   | Vuvlo                  |                                                               |              |              | 4.3          | V    |

| Over-Voltage P                      | roduction         | V <sub>ROVP</sub>      | Respect to VID voltage<br>VID > 1V                            | VID<br>+ 300 | VID<br>+ 350 | VID<br>+ 400 | mV   |

| Triresnoid                          |                   | V <sub>AOVP</sub>      | VID ≤ 1V                                                      | 1.325        | 1.35         | 1.375        | V    |

| \ / - It                            | for DAC =<br>VID1 | VPRE-OVP               | Active while VRON recycle or PS4 exit and                     | 2.42         | 2.45         | 2.48         | V    |

| Threshold                           | for DAC =<br>VID2 | TREOVI                 | until PWM turn-on                                             | 2.62         | 2.65         | 2.68         | V    |

| Debounce Time                       | of all OVP        | DT <sub>OVP</sub>      |                                                               |              | 0.5          |              | μS   |

| Under Voltage I<br>Threshold (UVF   |                   | V <sub>U</sub> VP      | Active while VID settle and non-DACOFF                        | -700         | -650         | -600         | mV   |

| Debounce Time                       | of UVP            | DT <sub>UVP</sub>      |                                                               |              | 3            |              | μS   |

| EN and VR_RE                        | ADY               |                        |                                                               |              |              |              |      |

| VR Enable Thre                      | eshold            | V <sub>IH</sub> _EN    |                                                               | 0.7          |              |              | V    |

| VR Disable Thre                     | eshold            | VIL_EN                 |                                                               |              |              | 0.3          | V    |

| Leakage Current of EN               |                   | ILEAK_EN               |                                                               | -1           |              | 1            | μΑ   |

| Output Voltage Low of VR_READY      |                   | Vol_vr_ready           | I <sub>VR_READY</sub> = 10mA                                  |              | 1            | 0.13         | V    |

| Acoustic Noise                      | e Suppression     | (ANS)                  |                                                               |              |              |              |      |

| ANS Enable Th                       | reshold           | V <sub>TH</sub> _H_ANS | VCC-V <sub>ANS</sub> < 0.5V, ANS is enabled                   |              |              | 0.5          | V    |

| ANS Disable Th                      | nreshold          | V <sub>TH_L_</sub> ANS | VCC-V <sub>ANS</sub> > 1V, ANS is disabled                    | 1            |              |              | V    |

| Serial VID and                      | VR_HOT            |                        |                                                               |              |              |              |      |

| SVID VCLK / VI<br>High Threshold    | •                 | VIH_SVID               |                                                               | 0.65         |              |              | V    |

| SVID VCLK / VI<br>Threshold         | DIO Logic Low     | VIL_SVID               |                                                               |              |              | 0.45         | V    |

| Leakage Currer<br>VDIO / ALERT      |                   | ILEAK_SVID             | $ VDIO = H, \overline{ALERT} = H, \\ \overline{VR\_HOT} = H $ | -1           | 1            | 1            | μΑ   |

|                                     |                   | Vol_vdio               | I <sub>VDIO</sub> = 10mA                                      |              |              |              |      |

| Output Voltage                      |                   | Vol_alert              | I <sub>ALERT</sub> = 10mA                                     | 0.04         |              | 0.13         | V    |

| ALEKI/ VR_F                         | ALERT/ VR_HOT     |                        | $I_{\overline{VR}\_{HOT}} = 10\text{mA}$                      |              |              |              |      |

| I <sup>2</sup> C Interface          |                   | ı                      |                                                               | 1            |              |              |      |

| SM_SCL / SM_<br>High Threshold      |                   | V <sub>IH</sub> _I2C   |                                                               | 1            |              |              | V    |

| SM_SCL / SM_<br>Low Threshold       | SDA Logic         | VIL_I2C                |                                                               |              |              | 0.6          | V    |

| Leakage Currer<br>/ SM_SDA          | nt of SM_SCL      | I <sub>LEAK_I2C</sub>  | SM_SDA = H                                                    | -1           |              | 1            | μΑ   |

Copyright © 2021 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation

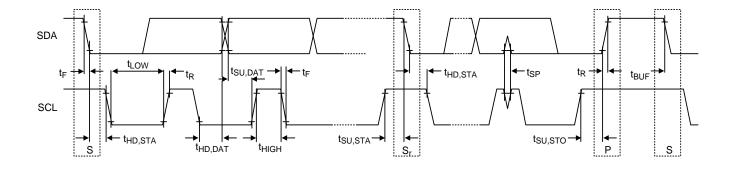

| Parameter                                                                                             | Symbol               | Test Conditions                                                | Min   | Тур   | Max   | Unit    |

|-------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------|-------|-------|-------|---------|

| Active Low Voltage of SM_SDA                                                                          | V <sub>SM_SDA</sub>  | I <sub>SM_SDA</sub> = 10mA                                     | 0.04  |       | 0.13  | V       |

| SCL Clock Rate                                                                                        | f <sub>SCL</sub>     |                                                                |       |       | 400   | kHz     |

| Hold Time (Repeated) Start<br>Condition. After this Period,<br>the First Clock Pulse is<br>Generated  | thd;sta              |                                                                | 0.6   |       |       | μS      |

| Low Period of the SCL Clock                                                                           | t <sub>LOW</sub>     |                                                                | 1.3   |       |       | μS      |

| High Period of the SCL Clock                                                                          | thigh                |                                                                | 0.6   |       |       | μS      |

| Set-Up Time for a Repeated START Condition                                                            | t <sub>SU;STA</sub>  |                                                                | 0.6   |       |       | μS      |

| Data Hold Time                                                                                        | t <sub>HD;DAT</sub>  |                                                                | 0     |       | 0.9   | μS      |

| Data Set-Up Time                                                                                      | t <sub>SU;DAT</sub>  |                                                                | 100   |       |       | μS      |

| Set-Up Time for STOP<br>Condition                                                                     | tsu;sto              |                                                                | 0.6   |       |       | μS      |

| Bus Free Time Between a STOP and START Condition                                                      | t <sub>BUF</sub>     |                                                                | 1.3   |       |       | μS      |

| Rising Time of both SDA and SCL Signals                                                               | t <sub>R</sub>       |                                                                | 20    |       | 300   | μS      |

| Falling Time of both SDA and SCL Signals                                                              | t <sub>F</sub>       |                                                                | 20    |       | 300   | μS      |

| DIMON                                                                                                 |                      |                                                                | •     |       |       |         |

|                                                                                                       | dvimon iccmax        | VIMON – VREF = 0.4V ;<br>VREF = 0.6V                           |       | 255   |       | Decimal |

| Digital IMON Set                                                                                      | dvimona iccmax       | VIMONA – VREF = 0.4V ;<br>VREF = 0.6V                          |       | 255   |       | Decimal |

|                                                                                                       | dvimon_aux<br>iccmax | VIMON_AUX - VREF<br>=1.6V; VREF = 0.6V                         |       | 255   |       | Decimal |

| Thermal Monitor                                                                                       |                      |                                                                |       |       |       |         |

| TSEN Voltage Threshold to Pull Low $\overline{\text{VR\_HOT}}$ (Asserts $\overline{\text{VR\_HOT}}$ ) | VTSEN_VR_HOT_L       | Within the range,  VR_HOT = L.  (R 1% variation is considered) |       | 0.600 | 0.620 | V       |

| TSEN Voltage Threshold to Pull High VR_HOT (De-Asserts VR_HOT)                                        | VTSEN_VR_HOT_H       | Within the range,  VR_HOT = H  (R 1% variation is considered)  | 0.608 | 0.628 | 0.649 | V       |

| TSEN Rises to Pull Low<br>ALERT                                                                       | VTSEN_<br>Status_H   | ALERT = L                                                      | 0.608 | 0.628 | 0.649 | V       |

| TSEN Down to Pull Low ALERT                                                                           | VTSEN_<br>Status_L   | ALERT = L                                                      | 0.637 | 0.658 | 0.680 | V       |

| I <sub>TSEN</sub>                                                                                     | 1                    | 1                                                              |       | 1     |       |         |

| Current Source from TSEN                                                                              | I <sub>TSEN</sub>    | V <sub>TSEN</sub> = 1.6V                                       | 78.8  | 80    | 81.2  | μА      |

| Parameter                            | Symbol Test Conditions |                          | Min  | Тур | Max  | Unit    |  |

|--------------------------------------|------------------------|--------------------------|------|-----|------|---------|--|

| PSYS                                 |                        |                          |      |     |      |         |  |

| Digital IMON Reporting Code for PMAX | D <sub>PSYS_PMAX</sub> | V <sub>PSYS</sub> = 1.6V |      | 255 |      | Decimal |  |

| VSYS                                 |                        |                          |      |     |      |         |  |

| \(\O\)\(\O\)                         | Vova zu                | As V <sub>IN</sub> = 24V |      | 255 |      | Dooimal |  |

| VSYS Input Voltage                   | Vsys_th                | As V <sub>IN</sub> = 12V |      | 128 |      | Decimal |  |

| PWM Driving Capability               |                        |                          |      |     |      |         |  |

| PWM Source Resistance                | RPWM_SRC               |                          |      | 30  |      | Ω       |  |

| PWM Sink Resistance                  | RPWM_SNK               |                          |      | 10  |      | Ω       |  |

| osc                                  |                        |                          |      |     |      |         |  |

| Oscillator Frequency 20kHz           |                        |                          | -5   |     | 5    | %       |  |

| V <sub>REF</sub>                     |                        |                          |      |     |      |         |  |

| VREF Voltage                         | Vvref                  | Normal operation         | 0.59 | 0.6 | 0.61 | V       |  |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}\text{C}$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

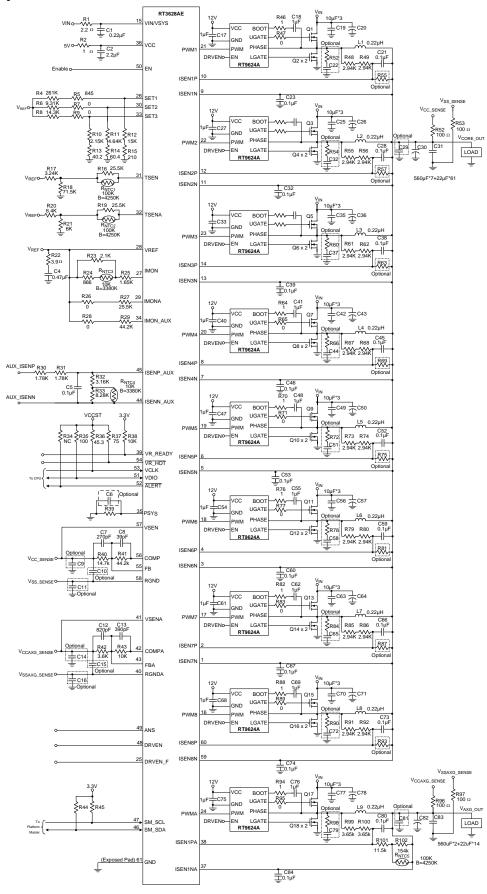

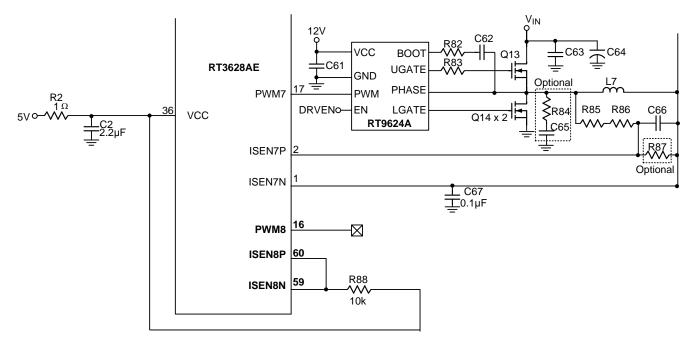

### **Typical Application Circuit**

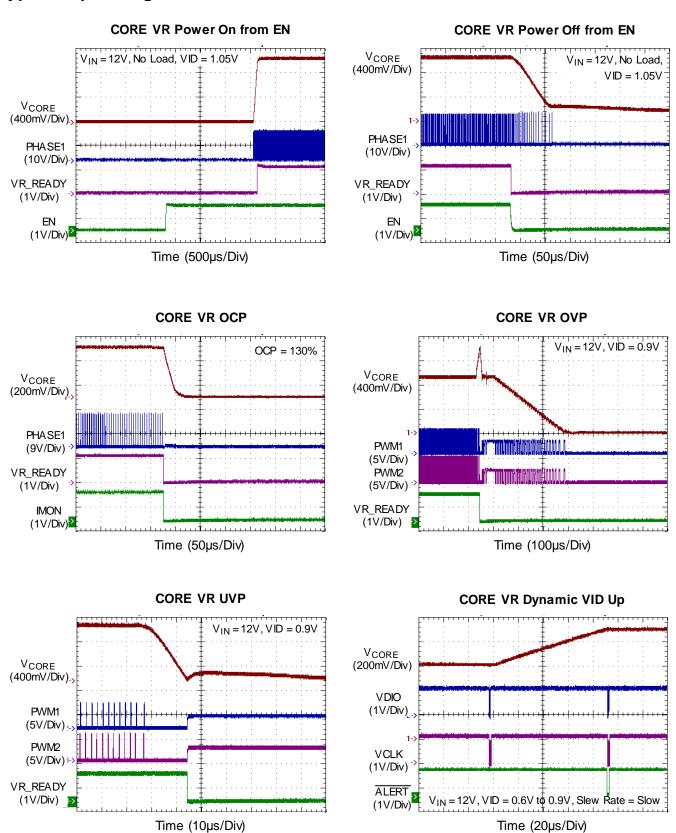

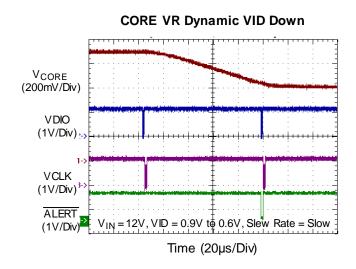

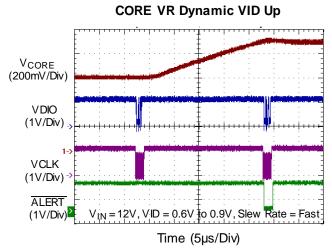

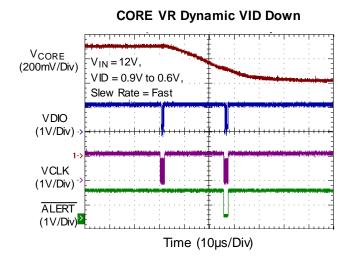

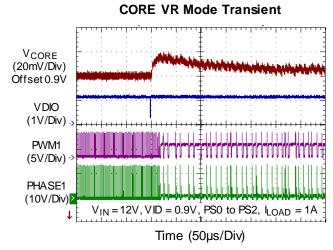

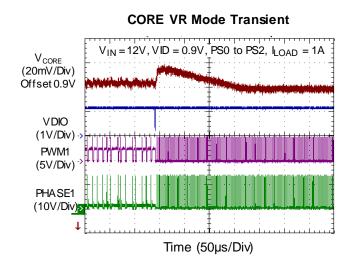

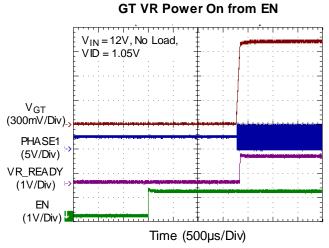

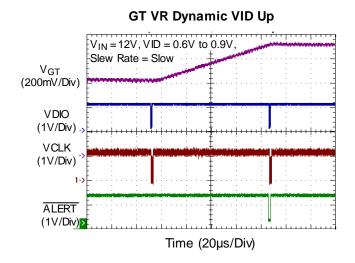

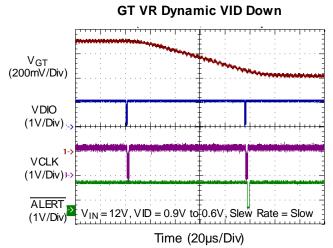

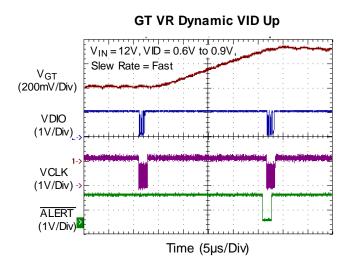

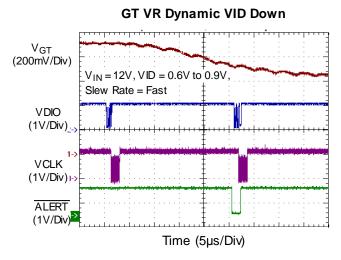

### **Typical Operating Characteristics**

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation

### **Application Information**

The RT3628AE includes two voltage rails: an 8/7/6/5/4 phase synchronous buck controller, the CORE VR and a 1 phase synchronous buck controller. **AXG** VR. designed the to meet Intel IMVP9.1compatible CPUs specification with a serial SVID control interface. The controller uses an ADC to implement all kinds of settings to save total pin number for easy use and increasing PCB space utilization. The RT3628AE is used in desktop computers or notebook computers.

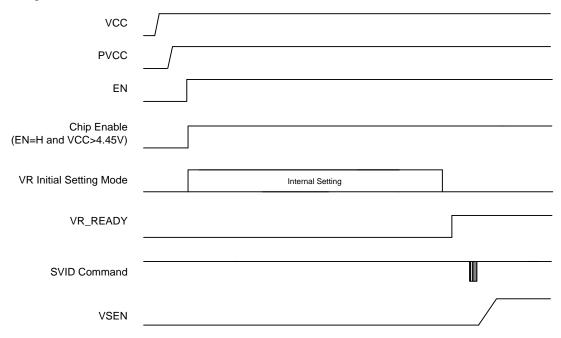

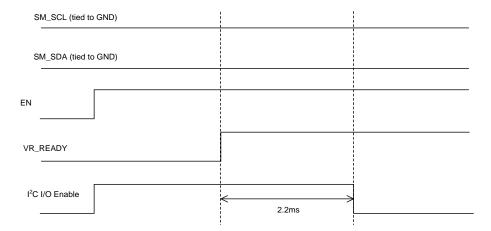

### **Power-ON Sequence**

In order to confirm sufficient power supply for proper operation, the VR triggers UVLO if VCC voltage drops below 4.3V (max). The UVLO protection shuts down controller and forces high-side MOSFET and low-side

MOSFET off. When VCC > 4.45, the RT3628AE issues POR=high and waits for EN signal. After POR = high and EN > 0.7V, the controller powers on (Chip Enable = H) and starts VR internal settings, which include internal circuit offset correction and function (PIN-SETTING). Users multi-functions through SETx, TSEN and TSENA pins. Figure 2 shows the typical timing of controller power-on. The pull-high power of EN pin is recommended as 1.05V, the same power as SVID interface. That can ensure the SVID power is ready while EN=H. Driver power (PVCC) is strongly suggested to be ready after VCC. This can prevent current flow back to VCC from PVCC through PWMx pin or DRVEN pin.

Figure 2. Typical Timing of Controller Power-ON

### **Maximum Active Phases Number Setting**

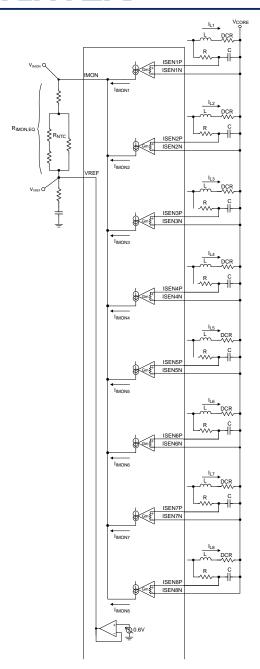

The number of active phases is determined by the ISENxP voltages. The detection is only active and latched at Chip Enable rising edge (EN = H and VCC > 4.45V). While Voltage at ISENxP > (VCC - 0.5V), maximum active phase number is (x-1). For example, pulling ISEN8P to VCC programs a 7-phase operation, while pulling ISEN8P and ISEN7P to VCC programs a

6-phase operation. The unused ISENxN pins are recommended to connect to VCC and the unused PWM pins can be floating. Figure 3 is a 7-phase operation voltage example, the pull-up ISEN8P/ISEN8N should be connected together with VCC of RT3628AE and the pull-up resistor should be 10kΩ.

DS3628AE-00

Figure 3. 7-Phase Operation Setting

### Rail Disable

Pulling ISEN1P > (VCC – 0.5V) to programs CORE rail disabled. The unused ISENxN pins are recommended to connect to VCC and the unused PWM pins can be floating. Pulling ISENPA > (VCC – 0.5V) to programs AXG rail disabled. The unused ISENNA pins are recommended to connect to VCC and the unused PWMA pins can be floating. Pulling the PSYS pin to VCC programs input power domain rail disable. The RT3628AE will reject any commands to the input power domain rail. The unused ISENP\_AUX pin and ISENN\_AUX pin are recommended to connect to GND.

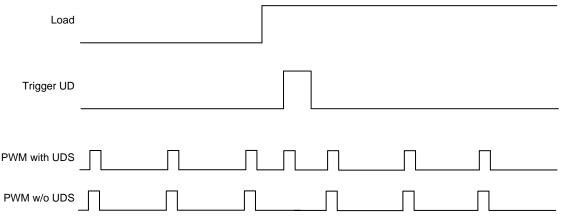

### **Acoustic Noise Suppression**

The RT3628AE supports acoustic noise suppression function for reducing acoustic noise induced by piezoelectric effect from MLCC. As output voltage transition occurs, especially in dynamic VID, the vibrating MLCC produces acoustic noise if the vibrating frequency falls into audible band and the noise level is related to the output voltage transition amplitude  $\Delta V.$  Therefore, the RT3628AE adapts acoustic noise suppression function which is enabled by pulling ANS pin to VCC to reduce  $\Delta V$  when SetVID down and SetVID Decay down in DEM mode.

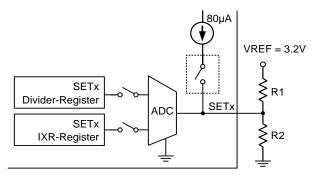

### **PIN-SETTING Mechanism**

The RT3628AE provides multiple parameters for platform setting and BOM optimization. These parameters can be set through SETx and TSEN pins. The RT3628AE adopts two-step PIN-SETTING mechanism to maximize IC pin utilization. Figure 4 illustrates this operating mechanism for SETx.

The Vdivider and V<sub>IXR</sub> can be represented as follows:

$$\begin{aligned} &V_{divider} = \frac{R2}{R1 + R2} \times 3.2V \\ &V_{IXR} = \frac{R2}{R1 + R2} \times 3.2V + 80\mu A \times \frac{R1 \times R2}{R1 + R2} \end{aligned}$$

Figure 4. Operating Mechanism for SETx

The Divider-Register and the IXR-Register set the specified functions. All setting functions are summarized in Table 1.

**Table 1. Summary of Pin Setting Functions**

| Pin   | Register                                           | Function Setting                                      | y of Pin Setting Ful<br>Symbol | Description                                                                                                     |

|-------|----------------------------------------------------|-------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------|

|       | Divider<br>Register[4]                             | DVID Fast slew rate                                   | DVID fast_SR[4]                | DVID fast_SR[4] = 0 : Fast_S<br>DVID fast_SR[4] = 1 : Fast_P                                                    |

|       | Divider<br>Register[3]                             | I <sup>2</sup> C Address setting                      | I2C_ADDR[3]                    | I2C_ADDR[3] = 0 : 0x20h<br>I2C_ADDR[3] = 1 : 0x21h                                                              |

| SET1  | Divider<br>Register[2:0]                           | CORE VR TON width setting (Switching frequency)       | KTON[2:0]                      | According to required frequency, select adaptive KTON parameter.                                                |

|       | IXR<br>Register[4]                                 | VR_HOT assertion during DVID current limit            | VR_HOT _DVID[4]                | $\frac{\overline{VR\_HOT}\_DVID[4] = 0, Disable}{VR\_HOT\_DVID[4] = 1, Enable}$                                 |

|       | IXR<br>Register[3:1]                               | AUX VR ICCMAX                                         | ICCMAX_AUX[3:1]                | According to Platform, set AUX VR's corrsponding ICCMAX                                                         |

|       | Divider<br>Register[4:3]                           | CORE VR Adaptive<br>RAMP(AR) Trigger level in<br>PS1  | AR_TH[4:3]                     | AR for loop response speed-up of loading rising edge, set trigger level in PS1.                                 |

|       | Divider<br>Register[2:0]                           | AXG VR ICCMAX                                         | ICCMAX_A[2:0]                  | According to Platform, set AXG VR's corrsponding ICCMAX                                                         |

| SET2  | IXR<br>Register[4]                                 | Dual phases function                                  | Dual_Phases[4]                 | Dual_Phases[4] = 0 : Each PWM output drives one phase.  Dual_Phases[4] = 1 : Each PWM output drives two phases. |

|       | IXR AXG VR TON width setting (switching frequency) |                                                       | KTON_A[3:1]                    | According to required frequency, select adaptive KTON_A parameter.                                              |

|       | Divider<br>Register[4]                             | Selectable VID table                                  | VIDT[4]                        | VIDT[4] = 0 : VID1 (0V ~ 1.52V)<br>VIDT[4] = 1 : VID2 (0V ~ 2.74V)                                              |

|       | Divider<br>Register[3:0]                           | Core VR ICCMAX                                        | ICCMAX[3:0]                    | According to Platform, set CORE VR's corresponding ICCMAX                                                       |

| SET3  | IXR<br>Register[4]                                 | Setting VBOOT of CORE rail                            | VBOOT[4]                       | VBOOT[4] = 0 : 0V<br>VBOOT[4] = 1 : non-zero                                                                    |

|       | IXR<br>Register[3]                                 | Setting VBOOT of AXG rail                             | VBOOT_A[3]                     | VBOOT_A[3] = 0 : 0V<br>VBOOT_A[3] = 1 : non-zero                                                                |

|       | IXR<br>Register[2:1]                               | AXG VR Adaptive<br>RAMP(AR) Trigger level             | AR_TH_A[2:1]                   | AR for loop response speed-up of loading rising edge, set trigger level.                                        |

|       | Divider<br>Register[5]                             | CORE VR Zero Current Detection Threshold              | ZCD_TH[5]                      | Detect whether each phase current crosses zero current. Set trigger level.                                      |

| TSEN  | Divider<br>Register[4:3]                           | AXG VR Current Gain                                   | Ai_A[4:3]                      | Current gain setting                                                                                            |

|       | Divider<br>Register[2:1]                           | CORE VR Current Gain                                  | Ai[2:1]                        | Current gain setting                                                                                            |

|       | Divider<br>Register[5]                             | Core & AXG VR sum OCP ratio                           | SUM_OC[5]                      | SUM_OC[5] = 0 : 130% x ICCMAX<br>SUM_OC[5] = 1 : 150% x ICCMAX                                                  |

| TSENA | Divider<br>Register[4]                             | AXG VR Zero Current<br>Detection Threshold            | ZCD_TH_A[4]                    | Detect whether each phase current crosses zero current. Set trigger level.                                      |

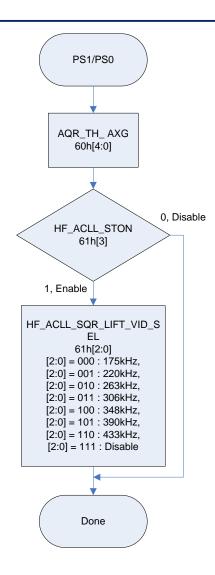

|       | Divider<br>Register[3:1]                           | CORE VR Adaptive Quick<br>Response(AQR) trigger level | AQR_TH[3:1]                    | AQR for loop response speed-up of loading rising edge. Set trigger level.                                       |

Referring to PIN-SETTING tables Table 2 to 6, users can search corresponding Vdivider or  $V_{IXR}$  according to the desired function setting combinations. Then SETx external resistors can be calculated as follows:

$$R1 = \frac{3.2V \times V_{IXR}}{80\mu A \times V_{divider}}$$

$$R1 \times V_{...}$$

Richtek provides a Microsoft Excel-based design tool to calculate the desired PIN-SETTING resisters.

The TSEN and TSENA pin also have function settings except for thermal monitoring function. It only utilizes divider part of PIN-SETTING mechanism. The detailed operation is described in Thermal Monitoring and Indicator section.

Table 2. SET1 Pin Setting for DVID Fast SR, I2C ADDR, KTON, VR\_HOT\_DVID and ICCMAX\_AUX

| V <sub>divider_SET1</sub><br>(mV) | DVID Fast SR                        | I2C ADDR | KTON | V <sub>IXR_SET1</sub> (mV) | VR_HOT_DVID                                    | ICCMAX_AUX |

|-----------------------------------|-------------------------------------|----------|------|----------------------------|------------------------------------------------|------------|

| 25                                |                                     |          | 0.50 | 50                         |                                                | 25A        |

| 75                                |                                     |          | 0.60 | 150                        |                                                | 30A        |

| 125                               | Past_S (mv) (mv) (N_not_bulk)  0.50 |          |      | 35A                        |                                                |            |

| 175                               | Fast_S                              | 0001-    | 0.80 | 350                        | Disable                                        | 40A        |

| 225                               |                                     | UX∠UN    | 0.90 | 450                        | Disable                                        | 45A        |

| 275                               |                                     |          | 1.00 | 550                        |                                                | 50A        |

| 325                               |                                     |          | 1.10 | 650                        |                                                | 55A        |

| 375                               | Foot C                              |          | 1.20 | 750                        |                                                | 60A        |

| 425                               | Fast_S                              |          | 0.50 | 850                        |                                                | 25A        |

| 475                               |                                     |          | 0.60 | 950                        | ]                                              | 30A        |

| 525                               |                                     |          | 0.70 | 1050                       | ]                                              | 35A        |

| 575                               |                                     | 0041     | 0.80 | 1150                       | Enable                                         | 40A        |

| 625                               |                                     | UXZIN    | 0.90 | 1250                       |                                                | 45A        |

| 675                               |                                     |          | 1.00 | 1350                       |                                                | 50A        |

| 725                               |                                     |          | 1.10 | 1450                       |                                                | 55A        |

| 775                               |                                     |          | 1.20 | 1550                       |                                                | 60A        |

| 825                               |                                     |          | 0.50 | 50                         |                                                | 25A        |

| 875                               |                                     |          | 0.60 | 150                        |                                                | 30A        |

| 925                               |                                     |          | 0.70 | 250                        |                                                | 35A        |

| 975                               |                                     | 0v20h    | 0.80 | 350                        | Diaghla                                        | 40A        |

| 1025                              |                                     | UXZUN    | 0.90 | 450                        | Disable                                        | 45A        |

| 1075                              |                                     |          | 1.00 | 550                        |                                                | 50A        |

| 1125                              |                                     |          | 1.10 | 650                        |                                                | 55A        |

| 1175                              | Foot D                              |          | 1.20 | 750                        | <u>                                       </u> | 60A        |

| 1225                              | rasi_P                              |          | 0.50 | 850                        |                                                | 25A        |

| 1275                              |                                     |          | 0.60 | 950                        | ]                                              | 30A        |

| 1325                              |                                     |          | 0.70 | 1050                       |                                                | 35A        |

| 1375                              |                                     | 0,045    | 0.80 | 1150                       | Fachie                                         | 40A        |

| 1425                              |                                     | 0x21h    | 0.90 | 1250                       | Enable                                         | 45A        |

| 1475                              |                                     |          | 1.00 | 1350                       |                                                | 50A        |

| 1525                              |                                     |          | 1.10 | 1450                       | ]                                              | 55A        |

| 1575                              |                                     |          | 1.20 | 1550                       |                                                | 60A        |

Table 3. SET2 Pin Setting for AR\_TH, ICCMAX\_A, Dual Phases Function and KTON\_A

| V <sub>divider_SET2</sub> (mV) | AR_TH   | ICCMAX_A       | SSOCP_A      | V <sub>IXR_SET2</sub> (mV) | Dual<br>Phases | KTON_A |

|--------------------------------|---------|----------------|--------------|----------------------------|----------------|--------|

| 25                             |         | 22A            | ICCMAV*2     | 50                         |                | 0.82   |

| 75                             |         | 26A            | ICCMAX*3     | 150                        |                | 0.91   |

| 125                            |         | 30A            | 1008487/40.5 | 250                        |                | 1.00   |

| 175                            | 475 \/  | 34A ICCMAX*2.5 | 350          | D'artite                   | 1.09           |        |

| 225                            | 175mV   | 38A            | 1001441/*0   | 450                        | Disable        | 1.18   |

| 275                            |         | 42A            | ICCMAX*2     | 550                        |                | 1.27   |

| 325                            |         | 46A            | 10000000     | 650                        |                | 1.36   |

| 375                            |         | 50A            | ICCMAX*1.6   | 750                        |                | 1.55   |

| 425                            |         | 22A            | ICCNANV*O    | 850                        |                | 0.82   |

| 475                            |         | 26A            | ICCMAX*3     | 950                        |                | 0.91   |

| 525                            |         | 30A            | ICCMAX*2.5   | 1050                       |                | 1.00   |

| 575                            | 150mV   | 34A            | ICCIVIAX 2.5 | 1150                       | Enoble         | 1.09   |

| 625                            |         | 38A            | ICCMAX*2     | 1250                       | Enable         | 1.18   |

| 675                            |         | 42A            | ICCIVIAX 2   | 1350                       |                | 1.27   |

| 725                            |         | 46A            | ICCMAX*1.6   | 1450                       |                | 1.36   |

| 775                            |         | 50A            |              | 1550                       |                | 1.55   |

| 825                            |         | 22A            | ICCMAX*3     | 50                         |                | 0.82   |

| 875                            |         | 26A 150        |              | 0.91                       |                |        |

| 925                            |         | 30A            | ICCMAX*2.5   | 250                        |                | 1.00   |

| 975                            | 125mV   | 34A            | TOOMAX 2.5   | 350                        | Disable        | 1.09   |

| 1025                           | 1231114 | 38A            | ICCMAX*2     | 450                        | Disable        | 1.18   |

| 1075                           |         | 42A            | IOOWAX 2     | 550                        |                | 1.27   |

| 1125                           |         | 46A            | ICCMAX*1.6   | 650                        |                | 1.36   |

| 1175                           |         | 50A            | TOOMAX 1.0   | 750                        |                | 1.55   |

| 1225                           |         | 22A            | ICCMAX*3     | 850                        |                | 0.82   |

| 1275                           |         | 26A            | ICCIVIAX 3   | 950                        |                | 0.91   |

| 1325                           |         | 30A            | ICCMAX*2.5   | 1050                       |                | 1.00   |

| 1375                           | Disable | 34A            | ICCIVIAN 2.5 | 1150                       | Enable         | 1.09   |

| 1425                           | Disable | 38A            | ICCM^ V*2    | 1250                       | Enable         | 1.18   |

| 1475                           |         | 42A            | ICCMAX*2     | 1350                       |                | 1.27   |

| 1525                           |         | 46A            | 10014414     | 1450                       |                | 1.36   |

| 1575                           |         | 50A            | ICCMAX*1.6   | 1550                       |                | 1.55   |

Table 4. SET3 Pin Setting for VBOOT, VBOOT\_A and AR\_TH\_A

| V <sub>IXR_SET3</sub> (mV) | vвоот    | VBOOT_A  | AR_TH_A |

|----------------------------|----------|----------|---------|

| 50                         |          |          | Disable |

| 150                        |          | 0.0V     | 125mV   |

| 250                        |          | 0.00     | 175mV   |

| 350                        | 0.01/    |          | 225mV   |

| 450                        | 0.0V     |          | Disable |

| 550                        |          | non-zero | 125mV   |

| 650                        |          |          | 175mV   |

| 750                        |          |          | 225mV   |

| 850                        |          |          | Disable |

| 950                        |          | 0.0V     | 125mV   |

| 1050                       |          | 0.00     | 175mV   |

| 1150                       | non 70ro |          | 225mV   |

| 1250                       | non-zero |          | Disable |

| 1350                       |          | non zoro | 125mV   |

| 1450                       |          | non-zero | 175mV   |

| 1550                       |          |          | 225mV   |

Table 5. SET3 Pin Setting for VIDT and ICCMAX

| ICCMAX                             |       |         |                                                                                           |         |         |         |         |                      |               |  |

|------------------------------------|-------|---------|-------------------------------------------------------------------------------------------|---------|---------|---------|---------|----------------------|---------------|--|

| V <sub>divider_</sub> SET3<br>(mV) | VIDT  | Each    | 83[4] = 0 Each PWM output drives one phase.  83[4] = 1 Each PWM output drives two phases. |         |         |         |         | SSOCP                |               |  |

|                                    |       | 4 phase | 5 phase                                                                                   | 6 phase | 7 phase | 8 phase | 8 phase | 10/12/14/16<br>phase |               |  |

| 25                                 |       | 93A     | 134A                                                                                      | 170A    | 206A    | 232A    | 232A    | 233A                 |               |  |

| 75                                 |       | 100A    | 140A                                                                                      | 176A    | 212A    | 238A    | 238A    | 240A                 | ICCMAX*2.5    |  |

| 125                                |       | 107A    | 146A                                                                                      | 182A    | 218A    | 244A    | 244A    | 247A                 | 1001/17/7 2.5 |  |

| 175                                |       | 114A    | 152A                                                                                      | 188A    | 224A    | 250A    | 250A    | 254A                 |               |  |

| 225                                |       | 121A    | 158A                                                                                      | 194A    | 230A    | 256A    | 256A    | 260A                 |               |  |

| 275                                |       | 128A    | 164A                                                                                      | 200A    | 236A    | 262A    | 262A    | 268A                 | ICCMANY*2 25  |  |

| 325                                |       | 135A    | 170A                                                                                      | 206A    | 242A    | 268A    | 268A    | 274A                 | ICCMAX*2.25   |  |

| 375                                | VID1  | 142A    | 176A                                                                                      | 212A    | 248A    | 274A    | 274A    | 282A                 |               |  |

| 425                                | וטויי | 149A    | 182A                                                                                      | 218A    | 254A    | 280A    | 280A    | 288A                 |               |  |

| 475                                |       | 156A    | 188A                                                                                      | 224A    | 260A    | 286A    | 286A    | 296A                 | ICCMAX*2      |  |

| 525                                |       | 163A    | 194A                                                                                      | 230A    | 266A    | 292A    | 292A    | 302A                 |               |  |

| 575                                |       | 170A    | 200A                                                                                      | 236A    | 272A    | 298A    | 298A    | 310A                 |               |  |

| 625                                |       | 177A    | 206A                                                                                      | 242A    | 278A    | 304A    | 304A    | 316A                 |               |  |

| 675                                |       | 184A    | 212A                                                                                      | 248A    | 284A    | 310A    | 310A    | 324A                 | ICCMAX*1.75   |  |

| 725                                |       | 191A    | 218A                                                                                      | 254A    | 290A    | 316A    | 316A    | 330A                 | ICCIVIAX 1.75 |  |

| 775                                |       | 198A    | 224A                                                                                      | 260A    | 296A    | 322A    | 322A    | 338A                 |               |  |

| 825                                |       | 93A     | 134A                                                                                      | 170A    | 206A    | 232A    | 232A    | 233A                 |               |  |

| 875                                |       | 100A    | 140A                                                                                      | 176A    | 212A    | 238A    | 238A    | 240A                 | ICCMAX*2.5    |  |

| 925                                |       | 107A    | 146A                                                                                      | 182A    | 218A    | 244A    | 244A    | 247A                 | ICCIVIAX 2.5  |  |

| 975                                |       | 114A    | 152A                                                                                      | 188A    | 224A    | 250A    | 250A    | 254A                 |               |  |

| 1025                               |       | 121A    | 158A                                                                                      | 194A    | 230A    | 256A    | 256A    | 260A                 |               |  |

| 1075                               |       | 128A    | 164A                                                                                      | 200A    | 236A    | 262A    | 262A    | 268A                 | ICCMAY*2.25   |  |

| 1125                               |       | 135A    | 170A                                                                                      | 206A    | 242A    | 268A    | 268A    | 274A                 | ICCMAX*2.25   |  |

| 1175                               | VIDO  | 142A    | 176A                                                                                      | 212A    | 248A    | 274A    | 274A    | 282A                 |               |  |

| 1225                               | VID2  | 149A    | 182A                                                                                      | 218A    | 254A    | 280A    | 280A    | 288A                 |               |  |

| 1275                               |       | 156A    | 188A                                                                                      | 224A    | 260A    | 286A    | 286A    | 296A                 | ICCNAAV*0     |  |

| 1325                               |       | 163A    | 194A                                                                                      | 230A    | 266A    | 292A    | 292A    | 302A                 | ICCMAX*2      |  |

| 1375                               |       | 170A    | 200A                                                                                      | 236A    | 272A    | 298A    | 298A    | 310A                 |               |  |

| 1425                               |       | 177A    | 206A                                                                                      | 242A    | 278A    | 304A    | 304A    | 316A                 |               |  |

| 1475                               |       | 184A    | 212A                                                                                      | 248A    | 284A    | 310A    | 310A    | 324A                 | ICCMAV*4 75   |  |

| 1525                               |       | 191A    | 218A                                                                                      | 254A    | 290A    | 316A    | 316A    | 330A                 | ICCMAX*1.75   |  |

| 1575                               |       | 198A    | 224A                                                                                      | 260A    | 296A    | 322A    | 322A    | 338A                 |               |  |

Table 6. TSEN Pin Setting for ZCD\_TH, Ai\_A and Ai

| V <sub>TSEN</sub><br>(mV) | ZCD_TH  | Ai_A | Ai   |

|---------------------------|---------|------|------|

| 50                        |         |      | 0.25 |

| 150                       |         | 0.75 | 0.50 |

| 250                       |         | 0.73 | 0.75 |

| 350                       |         |      | 1.00 |

| 450                       |         |      | 0.25 |

| 550                       |         | 1.13 | 0.50 |

| 650                       |         | 1.10 | 0.75 |

| 750                       | 0.417mV |      | 1.00 |

| 850                       |         |      | 0.25 |

| 950                       |         | 1.50 | 0.50 |

| 1050                      |         | 1.50 | 0.75 |

| 1150                      |         |      | 1.00 |

| 1250                      |         |      | 0.25 |

| 1350                      |         | 1.88 | 0.50 |

| 1450                      |         | 1.00 | 0.75 |

| 1550                      |         |      | 1.00 |

| 1650                      |         |      | 0.25 |

| 1750                      |         | 0.75 | 0.50 |

| 1850                      |         | 0.73 | 0.75 |

| 1950                      |         |      | 1.00 |

| 2050                      |         |      | 0.25 |

| 2150                      |         | 1 12 | 0.50 |

| 2250                      |         | 1.13 | 0.75 |

| 2350                      |         |      | 1.00 |

| 2450                      | 0.208mV |      | 0.25 |

| 2550                      |         | 4.50 | 0.50 |

| 2650                      |         | 1.50 | 0.75 |

| 2750                      |         |      | 1.00 |

| 2850                      |         |      | 0.25 |

| 2950                      |         | 4.00 | 0.50 |

| 3050                      |         | 1.88 | 0.75 |

| 3150                      |         |      | 1.00 |

Table 7. TSENA Pin Setting for SUM\_OC, ZCD\_TH\_A and AQR\_TH

| V <sub>TSENA</sub> (mV) | SUM_OC | ZCD_TH_A   | AQR_TH  |

|-------------------------|--------|------------|---------|

| 50                      |        |            | 240mV   |

| 150                     |        |            | 400mV   |

| 250                     |        |            | 560mV   |

| 350                     |        | 0.063mV    | 800mV   |

| 450                     |        | 0.003111   | 880mV   |

| 550                     |        |            | 1040mV  |

| 650                     |        |            | 1200mV  |

| 750                     | 130%   |            | Disable |

| 850                     |        |            | 240mV   |

| 950                     |        |            | 400mV   |

| 1050                    |        |            | 560mV   |

| 1150                    |        | 0.188mV    | 800mV   |

| 1250                    |        | 0.1001117  | 880mV   |

| 1350                    |        |            | 1040mV  |

| 1450                    |        |            | 1200mV  |

| 1550                    |        |            | Disable |

| 1650                    |        |            | 240mV   |

| 1750                    |        |            | 400mV   |

| 1850                    |        |            | 560mV   |

| 1950                    |        | 0.063mV    | 800mV   |

| 2050                    |        | 0.003111   | 880mV   |

| 2150                    |        |            | 1040mV  |

| 2250                    |        |            | 1200mV  |

| 2350                    | 4500/  |            | Disable |

| 2450                    | 150%   |            | 240mV   |

| 2550                    |        |            | 400mV   |

| 2650                    |        |            | 560mV   |

| 2750                    |        | 0.188mV    | 800mV   |

| 2850                    |        | U. IOOIIIV | 880mV   |

| 2950                    |        |            | 1040mV  |

| 3050                    |        |            | 1200mV  |

| 3150                    |        |            | Disable |

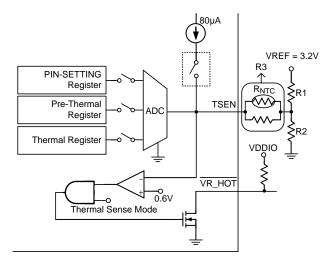

### **Thermal Monitoring and Indicator**

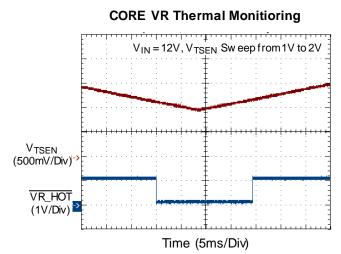

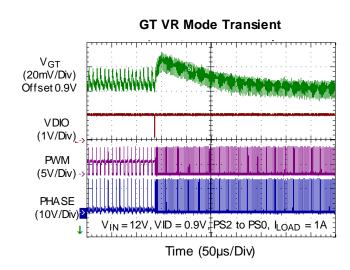

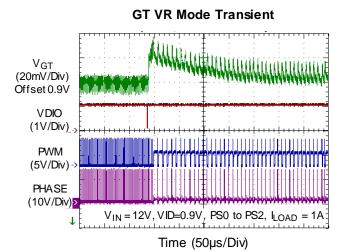

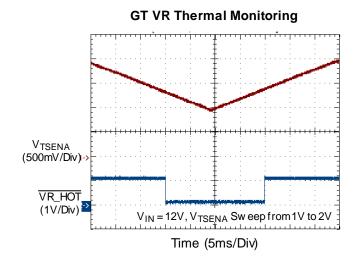

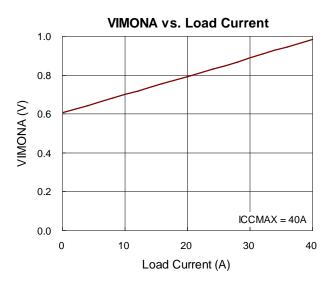

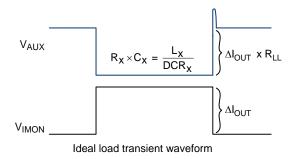

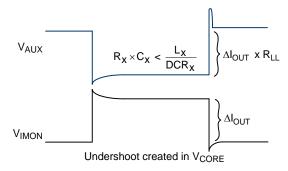

TSEN pin processes two functions of PIN-SETTING (function setting) and thermal monitoring. After power on, TSEN has three operation modes: PIN-SETTING, Pre-Thermal Sense and Thermal Sense Mode. The corresponding function blocks of the three modes are shown in Figure 5. In PIN-SETTING Mode, the TSEN pin voltage = 3.2V x R2 / (R1+R2) with VREF = 3.2V and is coded by ADC and stored in PIN-SETTING register. In Pre-Thermal Sense Mode, the TSEN pin voltage = 0.6V x R2 / (R1+R2) with VREF = 0.6V and is coded and stored in Pre-Thermal Register. This part helps Thermal Sense Mode calculation. In Thermal Sense Mode, the TSEN pin voltage =  $0.6V \times R2 / (R1+R2) + 80\mu A \times$ [(R1//R2)+R3] with VREF = 0.6V and is coded. Subtracting Pre-Thermal Register code, the result is stored in Thermal Register (The corresponding TSEN voltage =  $80uA \times [(R1//R2)+R3]$  which is defined as Thermal Voltage. The R3 is the NTC thermistor network to sense temperature.) The NTC thermistor is recommended to be placed near the MOSFET, the hottest area in the PCB. Higher temperature causes smaller R3 and lower TSEN. According to NTC thermistor temperature curve, design Thermal Voltage vs Temperature with proper R3 network to meet Table 8. The  $R_{NTC} = 100k\Omega$  with Beta = 4250 is recommended. The 100°C Thermal Voltage = 80µA x  $[(R1//R2)+R3(100^{\circ}C)] = 0.6V$  must be meet. The controller processes the TSEN pin voltage to report temperature zone register. While the TSEN pin voltage is less than 0.6V, the VR\_HOT is pulled low. The Thermal Register data is update every 75us and the averaging interval is 600 µs. The resistance accuracy of TSEN network is recommended to be less than 1% error.