#### 1. DESCRIPTION

The XLN7392 is a monolithic high– and low–side gate drive IC, that can drive high–speed MOSFETs and IGBTs that operate up to +600 V. It has a buffered output stage with all NMOS transistors designed for high pulse current driving capability and minimum cross–conduction,An a dvanced.

level–shift circuit offers high–side gate driver operation up to  $V_S = -9.8 \text{ V}$  (typical) for  $V_{BS} = 15 \text{ V}$ . Logic inputs are compatible with standard CMOS or LSTTL output, down to 3.3 V logic. The UVLO circuit prevents malfunction when VCC and VBS are lower than the specified threshold voltage. The high–current and low–output voltage drop feature makes this device suitable for half– and full–bridge inverters, like switching–mode power supply and high–power DC–DC converter applications.

#### 2. FEATURES

- Floating Channel for Bootstrap Operation to +600 V

- 3 A/3 A Sourcing/Sinking Current Driving Capability

- Common-Mode dv/dt Noise Canceling Circuit

- 3.3 V Logic Compatible

- Separate Logic Supply (VDD) Range from 3.3 V to 20 V

- Under-Voltage Lockout for VCC and VBS

- Cycle-by-Cycle Edge-Triggered Shutdown Logic

- Matched Propagation Delay for Both Channels

- Outputs In-phase with Input Signals

- Available in 14-DIP and 16-SOP (Wide) Packages

- This is a Pb-Free Device

#### 3. APPLICATIONS

- High-Speed Power MOSFET and IGBT Gate Driver

- Server Power Supply

- Uninterrupted Power Supply (UPS)

- Telecom System Power Supply

- Distributed Power Supply

- Motor Drive Inverter

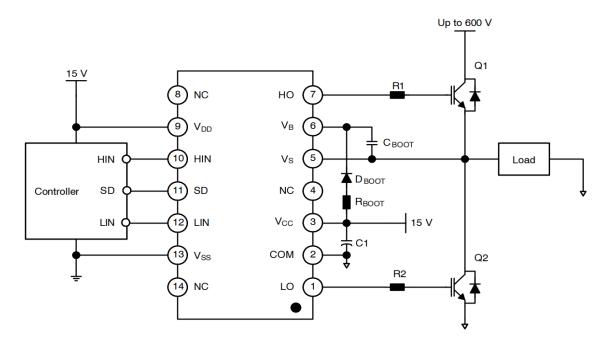

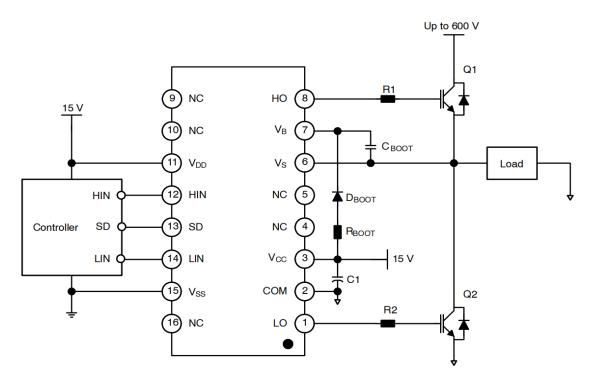

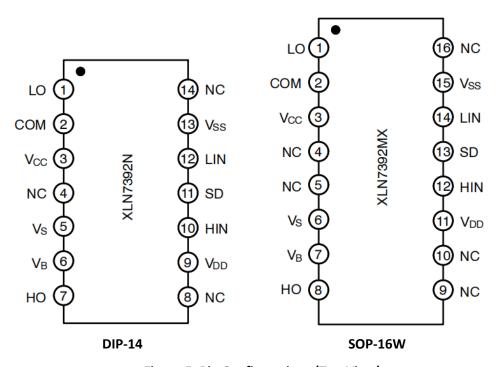

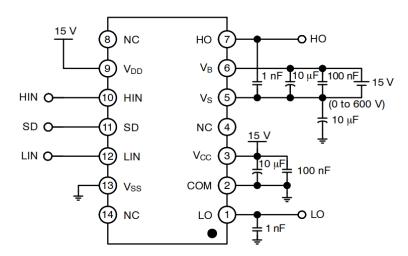

### 4. TYPICAL APPLICATION DIAGRAMS

Figure 1. Typical Application Circuit (Referenced 14-DIP)

Figure 2. Application Circuit for Half-Bridge (Referenced 16-SOP)

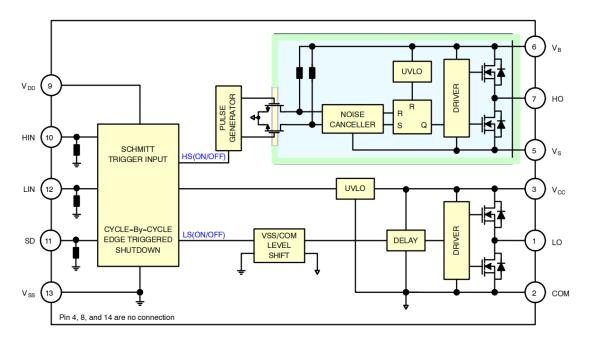

# 5. INTERNAL BLOCK DIAGRAM

Figure 3. Functional Block Diagram (Referenced 14-Pin)

Figure 4. Functional Block Diagram (Referenced 16-SOP)

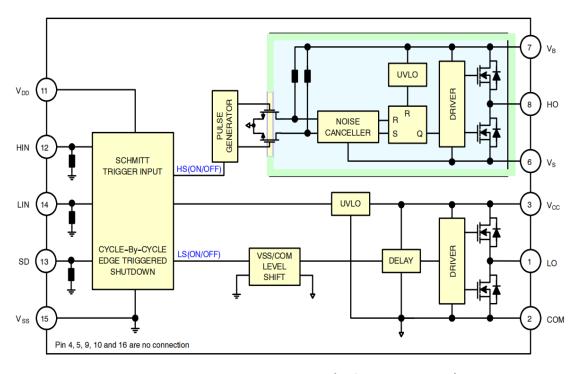

# 6. PIN CONFIGURATION

Figure 5. Pin Configurations (Top View)

# **PIN DEFINITIONS**

| 14-PIN | 16-PIN      | Name            | Descripion                                   |

|--------|-------------|-----------------|----------------------------------------------|

| 1      | 1           | LO              | Low-Side Driver Output                       |

| 2      | 2           | СОМ             | Low-Side Return                              |

| 3      | 3           | V <sub>cc</sub> | Low-Side Supply Voltage                      |

| 5      | 6           | Vs              | High-Voltage Floating Supply Return          |

| 6      | 7           | V <sub>B</sub>  | High-Side Floating Supply                    |

| 7      | 8           | НО              | High-Side Driver Output                      |

| 9      | 11          | $V_{DD}$        | Logic Supply Voltage                         |

| 10     | 12          | HIN             | Logic Input for High-Side Gate Driver Output |

| 11     | 13          | SD              | Logic Input for Shutdown Function            |

| 12     | 14          | LIN             | Logic Input for Low-Side Gate Driver Output  |

| 13     | 15          | V <sub>SS</sub> | Logic Ground                                 |

| 4,8,14 | 4,5,9,10,16 | NC              | No Connect                                   |

www.xinluda.com 4 / 17 Rev 1.0

### 7. ABSOLUTE MAXIMUM RATINGS

(TA = 25°C, unless otherwise noted)

| Symbol           | Characteristics                   | Min                    | Max                   | Unit                    |        |

|------------------|-----------------------------------|------------------------|-----------------------|-------------------------|--------|

| V <sub>B</sub>   | High-Side Floating Supply Voltage | -0.3                   | 625.0                 | V                       |        |

| Vs               | High-Side Floating Offset Voltag  | V <sub>B</sub> - 25.0  | V <sub>B</sub> + 0.3  | V                       |        |

| V <sub>HO</sub>  | High-Side Floating Output Voltag  | ge                     | V <sub>S</sub> - 0.3  | V <sub>B</sub> + 0.3    | V      |

| V <sub>cc</sub>  | Low-Side Supply Voltage           |                        | -0.3                  | 25.0                    | V      |

| V <sub>LO</sub>  | Low-Side Floating Output Voltage  | ge                     | -0.3                  | V <sub>CC</sub> + 0.3   | V      |

| $V_{DD}$         | Logic Supply Voltage              |                        | -0.3                  | V <sub>S S</sub> + 25.0 | V      |

| V <sub>SS</sub>  | Logic Supply Offset Voltage       | V <sub>CC</sub> - 25.0 | V <sub>CC</sub> + 0.3 | V                       |        |

| V <sub>IN</sub>  | Logic Input Voltage (HIN, LIN and | V <sub>SS</sub> - 0.3  | V <sub>DD</sub> + 0.3 | V                       |        |

| Dvs/dt           | Allowable Offset Voltage Slew R   | -                      | ±50                   | V/ns                    |        |

| D                | Power Dissipation (Note 1, 2)     | DIP-14                 | -                     | 1.6                     | 14/    |

| P <sub>D</sub>   |                                   | SOP-16W                | -                     | 1.3                     | W      |

| 0                | The word Desistance               | DIP-14                 | -                     | 75                      | °C /\\ |

| $\theta_{JA}$    | Thermal Resistance SOP-16W        |                        | -                     | 95                      | °C/W   |

| TJ               | Maximum Junction Temperature      | -                      | +150                  | °C                      |        |

| T <sub>STG</sub> | Storage Temperature               | -55                    | +150                  | °C                      |        |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

JESD51-2: Integral circuits thermal test method environmental conditions - natural convection; and JESD51-3: Low effective thermal conductivity test board for leaded surface-mount packages.

### 8. RECOMMENDED OPERATING CONDITIONS

| Symbol          | Characteristics                          | Min                 | Max                  | Unit |

|-----------------|------------------------------------------|---------------------|----------------------|------|

| V <sub>B</sub>  | High-Side Floating Supply Voltage        | V <sub>S</sub> + 10 | V <sub>S</sub> + 20  | V    |

| Vs              | High-Side Floating Supply Offset Voltage | 6 -V <sub>SS</sub>  | 600                  | V    |

| V <sub>HO</sub> | High-Side Output Voltage                 | Vs                  | V <sub>B</sub>       | V    |

| V <sub>CC</sub> | Low-Side Supply Voltage                  | 10                  | 20                   | V    |

| V <sub>LO</sub> | Low-Side Output Voltage                  | 0                   | V <sub>CC</sub>      | V    |

| $V_{DD}$        | Logic Supply Voltage                     | V <sub>SS</sub> + 3 | V <sub>SS</sub> + 20 | V    |

| V <sub>SS</sub> | Logic Supply Offset Voltage              | -5                  | 5                    | V    |

| V <sub>IN</sub> | Logic Input Voltage                      | V <sub>SS</sub>     | $V_{DD}$             | V    |

| T <sub>A</sub>  | Operating Ambient Temperature            | -40                 | +85                  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability

<u>www.xinluda.com</u> 5 / 17 Rev 1.0

<sup>1.</sup> Refer to the following standards:

<sup>2.</sup> Do not exceed power dissipation (PD) under any circumstances.

### 9. ELECTRICAL CHARACTERISTICS

$(V_{BIAS}\ (V_{CC},\ V_{BS},\ V_{DD})=15.0\ V$ , VSS = COM = 0 V and  $T_A=25\ ^{\circ}$  C, unless otherwise specified. The  $V_{IH}$ ,  $V_{IL}$  and  $I_{IN}$  parameters are referenced to  $V_{SS}$  and are applicable to the respective input leads: HIN, LIN, and SD. The  $V_O$  and  $I_O$  parameters are referenced to  $V_S$  and COM and are applicable to the respective output leads: HO and LO.)

| Symbol               | Characteristics                                                           | Test Condition                                 | Min  | Тур  | Max  | Unit |

|----------------------|---------------------------------------------------------------------------|------------------------------------------------|------|------|------|------|

| LOW-SIDE             | POWER SUPPLY SECTION                                                      |                                                |      |      |      |      |

| I <sub>QCC</sub>     | Quiescent V <sub>CC</sub> Supply Current                                  | V <sub>IN</sub> = 0 V or V <sub>DD</sub>       | -    | 40   | 80   | μΑ   |

| I <sub>QDD</sub>     | Quiescent V <sub>DD</sub> Supply Curren                                   | V <sub>IN</sub> = 0 V or V <sub>DD</sub>       | -    | -    | 10   | μΑ   |

| I <sub>PCC</sub>     | Operating V <sub>CC</sub> Supply Current                                  | $f_{IN}$ = 20 kHz, rms, $V_{IN}$ = 15 $V_{PP}$ | -    | 430  | -    | μΑ   |

| I <sub>PDD</sub>     | Operating V <sub>DD</sub> Supply Current                                  | $f_{IN}$ = 20 kHz, rms, $V_{IN}$ = 15 $V_{PP}$ | -    | 300  | -    | μΑ   |

| I <sub>SD</sub>      | Shutdown Supply Current                                                   | $S_D = V_{DD}$                                 | -    | 120  | -    | μΑ   |

| V <sub>CCUV+</sub>   | V <sub>CC</sub> Supply Under-Voltage Positive-<br>Going Threshold Voltage | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = Sweep | 7.7  | 8.8  | 9.9  | V    |

| $V_{\text{CCUV-}}$   | V <sub>CC</sub> Supply Under-Voltage Negative-<br>Going Threshold Voltage | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = Sweep | 7.3  | 8.4  | 9.5  | V    |

| $V_{\text{CCUVH}}$   | V <sub>CC</sub> Supply Under-Voltage Lockout<br>Hysteresis Voltage        | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = Sweep | -    | 0.4  | -    | V    |

| BOOTSTRA             | APPED SUPPLY SECTION                                                      |                                                |      |      |      |      |

| I <sub>QBS</sub>     | Quiescent VBS Supply Current                                              | V <sub>IN</sub> = 0 V or V <sub>DD</sub>       | -    | 60   | 130  | μΑ   |

| I <sub>PBS</sub>     | Operating VBS Supply Current                                              | f <sub>IN</sub> = 20 kHz, rms value            | -    | 500  | -    | μΑ   |

| V <sub>BSUV+</sub>   | V <sub>BS</sub> Supply Under-Voltage Positive-<br>Going Threshold Voltage | V <sub>IN</sub> = 0 V, V <sub>BS</sub> = Sweep | 7.7  | 8.8  | 9.9  | V    |

| $V_{BSUV}$           | V <sub>BS</sub> Supply Under-Voltage Negative-<br>Going Threshold Voltage | V <sub>IN</sub> = 0 V, V <sub>BS</sub> = Sweep | 7.3  | 8.4  | 9.5  | V    |

| $V_{BSUVH}$          | V <sub>BS</sub> Supply Under-Voltage Lockout<br>Hysteresis Voltage        | VI <sub>N</sub> = 0 V, V <sub>BS</sub> = Sweep | -    | 0.4  | -    | V    |

| I <sub>LK</sub>      | Offset Supply Leakage Current                                             | V <sub>B</sub> = V <sub>S</sub> = 600 V        | -    | -    | 50   | μА   |

| INPUT LO             | CIC SECTION (HIN, LIN, AND SD)                                            |                                                |      |      |      |      |

| .,                   | Lasia ((4)) Lagrada Thanasha Id Malkana                                   | V <sub>DD</sub> = 3 V                          | 2.4  | -    | -    | V    |

| $V_{IH}$             | Logic "1" Input Threshold Voltage                                         | V <sub>DD</sub> = 15 V                         | 9.5  | -    | -    | V    |

|                      | Landa ((O)) Langua Thomas In a lal Maltana                                | V <sub>DD</sub> = 3 V                          | -    | -    | 0.8  | V    |

| $V_{IL}$             | Logic "0" Input Threshold Voltage                                         | V <sub>DD</sub> = 15 V                         | -    | -    | 4.5  | V    |

| I <sub>IN+</sub>     | Logic Input High Bias Current                                             | V <sub>IN</sub> = V <sub>DD</sub>              | -    | 20   | 40   | μΑ   |

| I <sub>IN-</sub>     | Logic Input Low Bias Current                                              | V <sub>IN</sub> = 0 V                          | -    | -    | 3    | μΑ   |

| R <sub>IN</sub>      | Logic Input Pull-Down Resistance                                          |                                                | 375  | 750  | -    | kΩ   |

| GATE DRIV            | /ER OUTPUT SECTION                                                        |                                                |      |      |      |      |

| V <sub>OH</sub>      | High-Level Output Voltage (V <sub>BIAS</sub> - V <sub>O</sub> )           | No Load (I <sub>O</sub> = 0 A)                 | -    | -    | 1.5  | V    |

| V <sub>OL</sub>      | Low-Level Output Voltage                                                  | No Load (I <sub>O</sub> = 0 A)                 | -    | -    | 200  | mA   |

| I <sub>O+</sub>      | Output High, Short-Circuit Pulsed<br>Current (Note 4)                     | $V_0 = 0 \text{ V, PW} \le 10  \mu\text{s}$    | 2.5  | 3.0  | -    | А    |

| 10-                  | Output Low, Short-Circuit Pulsed<br>Current (Note 4)                      | $V_0 = 15 \text{ V, PW} \le 10  \mu\text{s}$   | 2.5  | 3.0  | -    | Α    |

| V <sub>ss</sub> /COM | VSS-COM/COM-VSS Voltage<br>Endurability                                   |                                                | -5.0 | -    | 5.0  | V    |

| -V <sub>S</sub>      | Allowable Negative VS Pin Voltage for HIN Signal Propagation to HO        |                                                | -    | -9.8 | -7.0 | V    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>4.</sup> This parameter guaranteed by design.

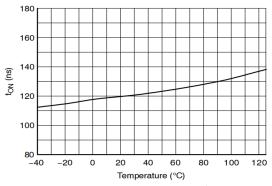

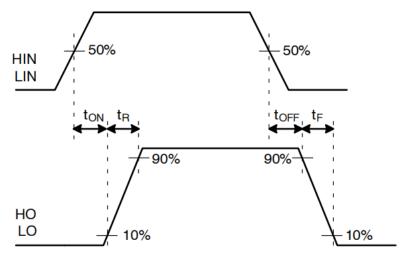

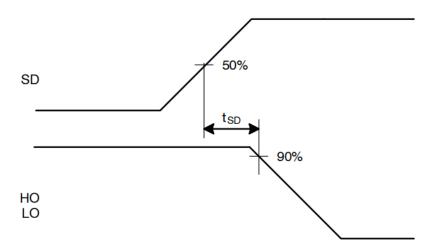

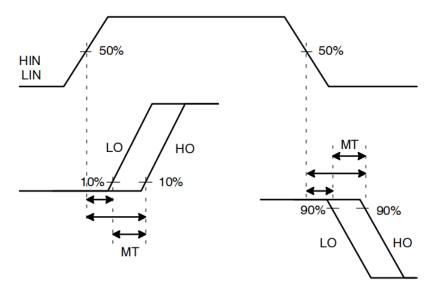

# 10. DYNAMIC ELECTRICAL CHARACTERISTICS

$(V_{BIAS}(V_{CC}, V_{BS}, V_{DD}) = 15.0 \text{ V}, V_{SS} = COM = 0V, C_{LOAD} = 1000 \text{ pF}, T_A = 25^{\circ}C, unless otherwise specified.)$

| Symbol           | Characteristics                          | Test Condition       | Min | Тур | Max | Unit |

|------------------|------------------------------------------|----------------------|-----|-----|-----|------|

| ton              | Turn-On Propagation Delay Time           | V <sub>S</sub> = 0 V | -   | 130 | 180 | ns   |

| t <sub>off</sub> | Turn-Off Propagation Delay Time          | V <sub>S</sub> = 0 V | -   | 150 | 200 |      |

| t <sub>sd</sub>  | Shutdown Propagation Delay Time (Note 5) |                      | -   | 130 | 180 |      |

| t <sub>r</sub>   | Turn-On Rise Time                        |                      | -   | 25  | 50  | ns   |

| t <sub>f</sub>   | Turn-Off Fall Time                       |                      | -   | 20  | 45  |      |

| MT               | Delay Matching, HO & LO Turn-On/Off      |                      | -   | -   | 35  |      |

<sup>5.</sup> This parameter guaranteed by design.

# 11. TYPICAL CHARACTERISTICS

Figure 6. Turn-On Propagation Delay vs.

Temperature

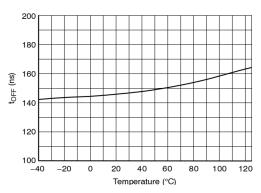

Figure 7. Turn-Off Propagation Delay vs.

Temperature

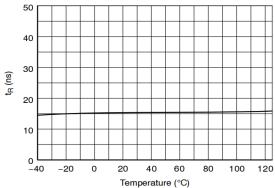

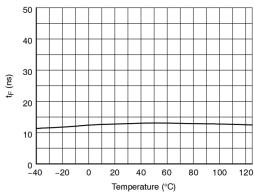

Figure 8. Turn-On Rise Time vs. Temperature

Figure 9. Turn-Off Fall Time vs. Temperature

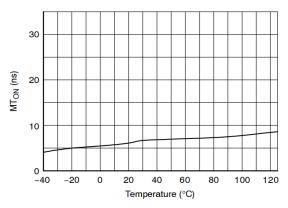

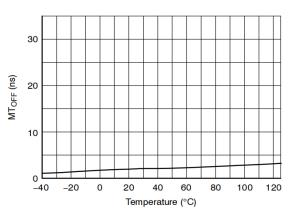

Figure 10. Turn-On Delay Matching vs. Temperature

Figure 11. Turn-Off Delay Matching vs. Temperature

www.xinluda.com 8 / 17 Rev 1.0

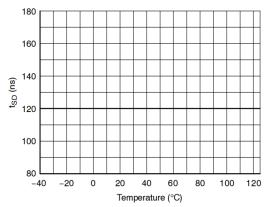

Figure 12. Shutdown Propagation Delay vs. Temperature

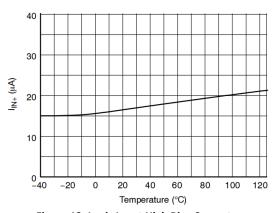

Figure 13. Logic Input High Bias Current vs.

Temperature

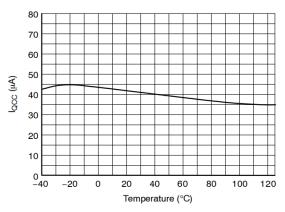

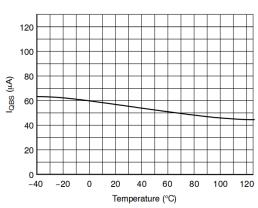

Figure 14. Quiescent  $V_{\text{CC}}$  Supply Current vs. Temperature

Figure 15. Quiescent  $V_{\text{BS}}$  Supply Current vs. Temperature

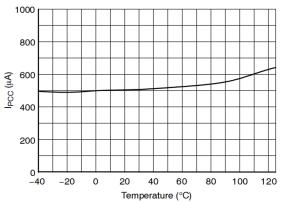

Figure 16. Operating  $V_{\text{CC}}$  Supply Current vs. Temperature

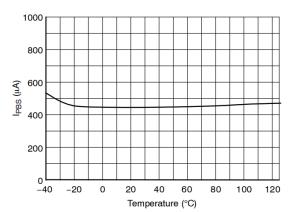

Figure 17. Operating  $V_{\text{BS}}$  Supply Current vs. Temperature

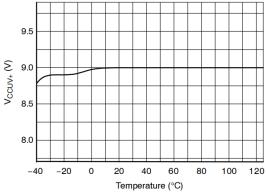

Figure 18. V<sub>CC</sub> UVLO+ vs. Temperature

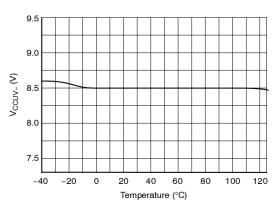

Figure 19. V<sub>cc</sub> UVLO- vs. Temperature

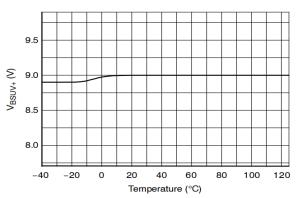

Figure 20. V<sub>BS</sub> UVLO+ vs. Temperature

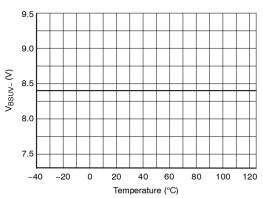

Figure 21.  $V_{\text{BS}}$  UVLO- vs. Temperature

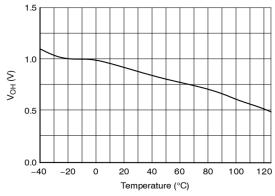

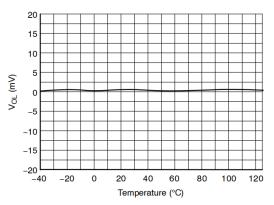

Figure 22. High-Level Output Voltage vs. Temperature

Figure 23. Low-Level Output Voltage vs. Temperature

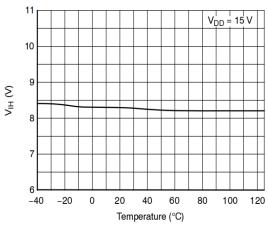

Figure 24. Logic High Input Voltage vs. Temperature

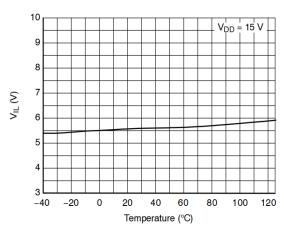

Figure 25. Logic Low Input Voltage vs. Temperature

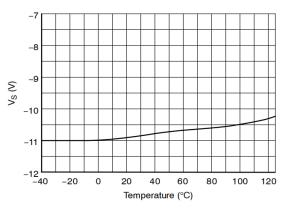

Figure 26. Allowable Negative  $V_{\text{S}}$  Voltage vs. Temperature

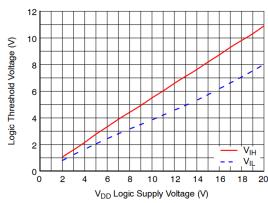

Figure 27. Input Logic (HIN & LIN) Threshold Voltagevs. V<sub>DD</sub> Supply Voltage

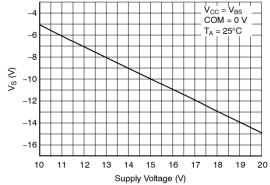

Figure 28. Allowable Negative Vs Voltage for HIN Signal Propagation to High Side vs. Supply Voltage

# 12. SWITCHING TIME DEFINITIONS

Figure 29. Switching Time Test Circuit (Referenced 14-DIP)

Figure 30. Input/Output Timing Diagram

Figure 31. Switching Time Waveform Definitions

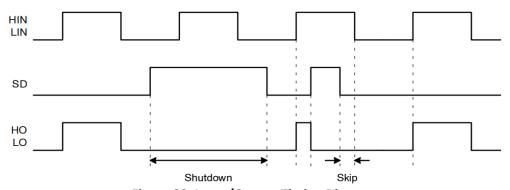

**Figure 32. Shutdown Waveform Definition**

Figure 33. Delay Matching Waveform Definitions

<u>www.xinluda.com</u> 13 / 17 Rev 1.0

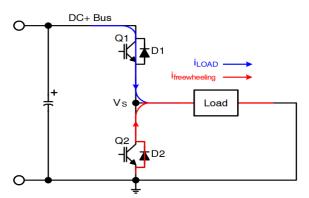

# 13. APPLICATION INFORMATION

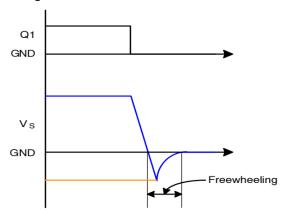

#### Negative V<sub>S</sub> Transient

The bootstrap circuit has the advantage of being simple and low cost, but has some limitations. The biggest difficulty with this circuit is the negative voltage present at the emitter of the high-side switching device when high-side switch is turned-off in half-bridge application.

If the high-side switch, Q1, turns-off while the load current is flowing to an inductive load, a current commutation occurs from high-side switch, Q1, to the diode, D2, in parallel with the low-side switch of the same inverter leg. Then the negative voltage present at the emitter of the high-side switching device, just before the freewheeling diode, D2, starts clamping, causes load current to suddenly flow to the low-side freewheeling diode, D2, as shown in Figure 34.

Figure 34. Half-Bridge Application Circuits

This negative voltage can be trouble for the gate driver's output stage, there is the possibility to develop an over-voltage condition of the bootstrap capacitor, input signal missing and latch-up problems because it directly affects the source Vs pin of the gate driver, as shown in Figure 35. This undershoot voltage is called "negative Vs transient".

Figure 35. V= Waveforms During Q1 Turn-Off

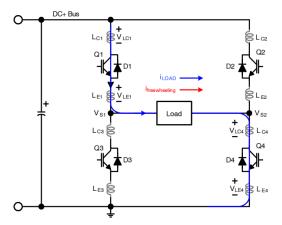

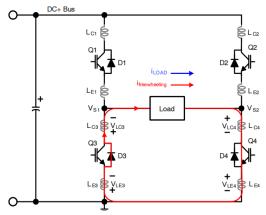

Figure 36 and Figure 37 show the commutation of the load current between high-side switch, Q1, and low-side freewheelling diode, D3, in same inverter leg. The parasitic inductances in the inverter circuit from the die wire bonding to the PCB tracks are jumped together in LC and LE for each IGBT. When the high-side switch, Q1, and low-side switch, Q4, are turned on, the Vs1 node is below DC+ voltage by the voltage drops associated with the power switch and the parasitic inductances of the circuit due to load current is flows from Q1 and Q4, as shown in Figure 36. When the high-side switch, Q1, is turned off and Q4, remained turned on, the load current to flows the low-side freewheeling diode, D3, due to the inductive load connected to VS1 as shown in Figure 37. The current flows from ground (which is connected to the COM pin of the gate driver) to the load and the negative voltage present at the emitter of the high-side switching device.

<u>www.xinluda.com</u> 14 / 17 Rev 1.0

In this case, the COM pin of the gate driver is at a higher potential than the Vs pin due to the voltage drops associated with freewheeling diode, D3, and parasitic elements, LC3 and LE3.

Figure 36. Q1 and Q4 Turn-On

Figure 37. Q1 Turn-Off and D3 Conducting

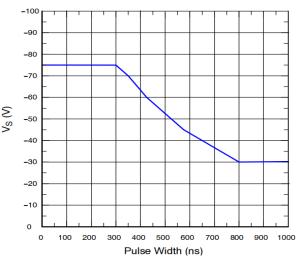

The XLN7392 has a negative Vs transient performance curve, as shown in Figure 38.

Figure 38. Negative VS Transient Characteristic

Even though the XLN7392 has been shown able to handle these negative Vs transient conditions, it is strongly recommended that the circuit designer limit the negative Vs transient as much as possible by careful PCB layout to minimized the value of parasitic elements and component use. The amplitude of negative Vs voltage is proportional to the parasitic inductances and the turn-off speed, di/dt, of the switching device.

www.xinluda.com 15 / 17 Rev 1.0

### 14. GENERAL GUIDELINES

#### 14.1. Printed Circuit Board Layout

The relayout recommended for minimized parasitic elements is as follows:

- Direct tracks between switches with no loops or deviation.

- Avoid interconnect links. These can add significant inductance.

- Reduce the effect of lead-inductance by lowering package height above the PCB.

- Consider co-locating both power switches to reduce track length.

- To minimize noise coupling, the ground plane should not be placed under or near the high-voltage floating side.

- To reduce the EM coupling and improve the power switch turn-on/off performance, the gate drive loops must be reduced as much as possible.

#### 14.2. Placement of Components

The recommended placement and selection of component as follows:

- Place a bypass capacitor between the V<sub>DD</sub> and VSS pins. A ceramic 1 μF capacitor is suitable for most applications. This component should be placed as close as possible to the pins to reduce parasitic elements.

- The bypass capacitor from V<sub>CC</sub> to COM supports both the low-side driver and bootstrap capacitor recharge. A value at least ten times higher than the bootstrap capacitor is recommended.

- The bootstrap resistor, RBOOT, must be considered in sizing the bootstrap resistance and the current developed during initial bootstrap charge. If the resistor is needed in series with the bootstrap diode, verify that VBdoes not fall below COM (ground). Recommended use is typically  $5^{\sim}10~\Omega$  that increase the VBS time constant. If the voltage drop of of bootstrap resistor and diode is too high or the circuit topology does not allow a sufficient charging time, a fast recovery or ultra-fast recovery diode can be used.

- The bootstrap capacitor, CBOOT, uses a low-ESR capacitor, such as ceramic capacitor.

It is strongly recommended that the placement of components is as follows:

- Place components tied to the floating voltage pins (VB and VS) near the respective high-voltage portions of the device and the XLN7392. NC (not connected) pins in this package maximize the distance between the high-voltage and low-voltage pins (see Figure 5).

- Place and route for bypass capacitors and gate resistors as close as possible to gate drive IC.

- Locate the bootstrap diode, DBOOT, as close as possible to bootstrap capacitor, CBOOT.

- The bootstrap diode must use a lower forward voltage drop and minimal switching time as soon as possible for fast recovery or ultra-fast diode.

## 15. ORDERING INFORMATION

### **Ordering Information**

| Part<br>Number | Device<br>Making | Package<br>type | Body size<br>(mm) | Temperate<br>(°C) | MSL  | Transpo<br>Rt | Package<br>Quantit |

|----------------|------------------|-----------------|-------------------|-------------------|------|---------------|--------------------|

| XLN7392N       | XL7392N          | DIP14           | 19.05*6.35        | -40 to +85        | MSL3 | Tube 25       | 1000               |

| XLN7392MX      | XL7392M          | SOP16(W)        | 10.45*7.5         | -40 to +85        | MSL3 | T&R           | 1000               |

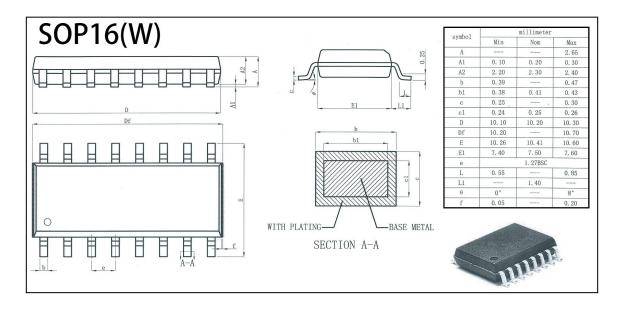

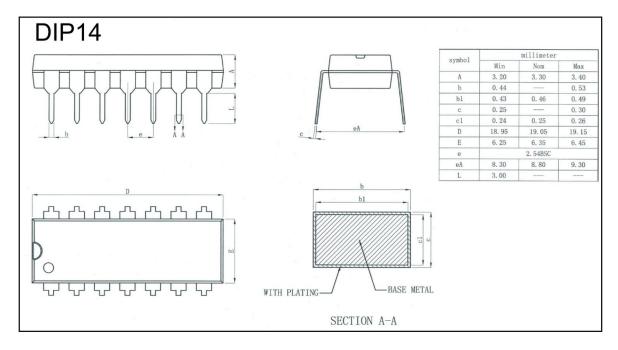

### 16. DIMENSIONAL DRAWINGS