## 1. DESCRIPTION

The XL65HVD230 and XL65HVD231 controller area network (CAN) transceivers are compatible to the specifications of the ISO 11898-2 High Speed CAN Physical Layer standard (transceiver). These devices are designed for data rates up to 1 megabit per second (Mbps), and include many protection features providing device and CAN network robustness. The XL65HVD23x transceivers are designed for use with the 3.3 V  $\mu$ Ps, MCUs and DSPs with CAN controllers, or with equivalent protocol controller devices. The devices are intended for use in applications employing the CAN serial communication physical layer in accordance with the ISO 11898 standard.

Designed for operation in especially harsh environments, these devices feature cross wire protection, loss of ground and overvoltage protection, overtemperature protection, as well as wide common mode range of operation.

The CAN transceiver is the CAN physical layer and interfaces the single ended host CAN protocol controller with the differential CAN bus found in industrial, building automation, and automotive applications. These devices operate over a -2 V to 7 V common mode range on the bus, and can withstand common mode transients of  $\pm 25$  V.

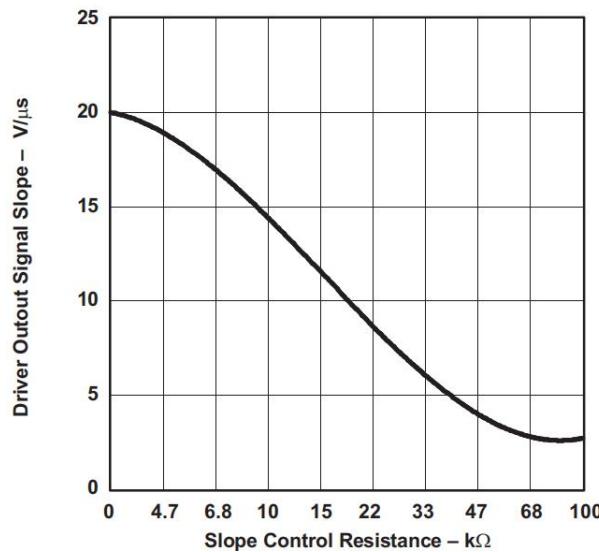

The RS pin (pin 8) on the XL65HVD230 and XL65HVD231 provides three different modes of operation: high speed mode, slope control mode, and low-power mode. The high speed mode of operation is selected by connecting the RS pin to ground, allowing the transmitter output transistors to switch on and off as fast as possible with no limitation on the rise and fall slopes. The rise and fall slopes can also be adjusted by connecting a resistor in series between the RS pin and ground. The slope will be proportional to the pin's output current. With a resistor value of 10 k $\Omega$  the device will have a slew rate of  $\sim 15$  V/ $\mu$ s, and with a resistor value of 100 k $\Omega$  the device will have a slew rate of  $\sim 2$  V/ $\mu$ s. See [Application Information](#) for more information.

The XL65HVD230 enters a low current standby mode (listen only) during which the driver is switched off and the receiver remains active if a high logic level is applied to the RS pin. This mode provides a lower power consumption mode than normal mode while still allowing the CAN controller to monitor the bus for activity indicating it should return the transceiver to normal mode or slope control mode. The host controller (MCU, DSP) returns the device to a transmitting mode (high speed or slope control) when it wants to transmit a message to the bus or if during standby mode it received bus traffic indicating the need to once again be ready to transmit.

The difference between the XL65HVD230 and the XL65HVD231 is that both the driver and the receiver are switched off in the XL65HVD231 when a high logic level is applied to the RS pin. In this sleep mode the device will not be able to transmit messages to the bus or receive messages from the bus. The device will remain in sleep mode until it is reactivated by applying a low logic level on the RS pin.

## 2. FEATURES

- Operates with a single 3.3 V Supply

- Compatible With ISO 11898-2 Standard

- Bus Pin ESD Protection Exceeds  $\pm 16$  kV HBM

- High Input Impedance Allows for Up to 120 Nodes on a Bus

- Adjustable Driver Transition Times for Improved Emissions Performance

- XL65HVD230 and XL65HVD231

- XL65HVD230: Low Current Standby Mode

- 370  $\mu$ A Typical

- XL65HVD231: Ultra Low Current Sleep Mode

- 40 nA Typical

- Designed for Data Rates<sup>(1)</sup> up to 1 Mbps

- Thermal Shutdown Protection

- Open Circuit Fail-Safe Design

- Glitch Free Power Up and Power Down Protection

- for Hot Plugging Applications

(1) The signaling rate of a line is the number of voltage transitions that are made per second expressed in the units bps (bits per second).

### 3. APPLICATIONS

- Industrial Automation, Control, Sensors and Drive Systems

- Motor and Robotic Control

- Building and Climate Control (HVAC)

- Telecom and Basestation Control and Status

- CAN Bus Standards Such as CANopen, DeviceNet, and CAN Kingdom

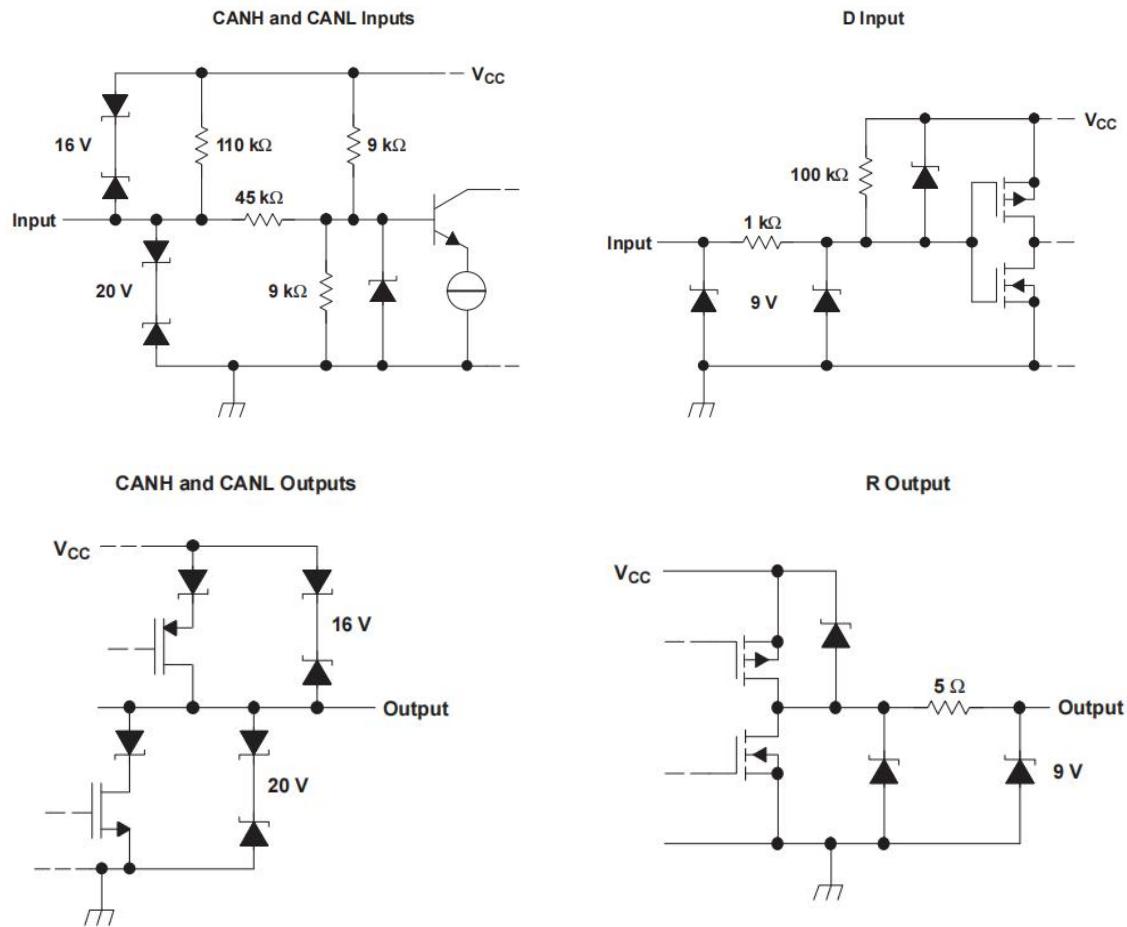

## Equivalent Input and Output Schematic Diagrams

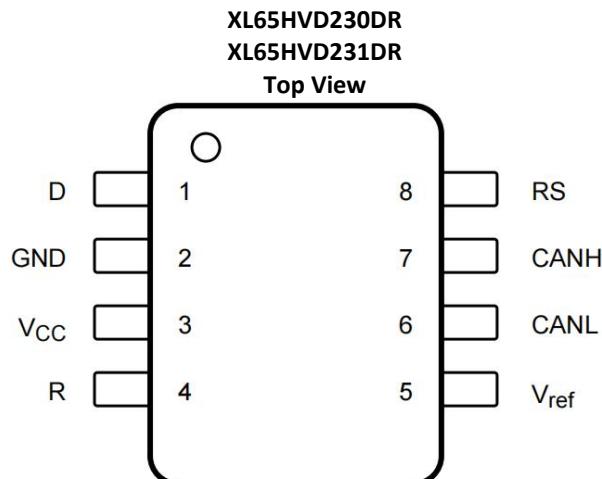

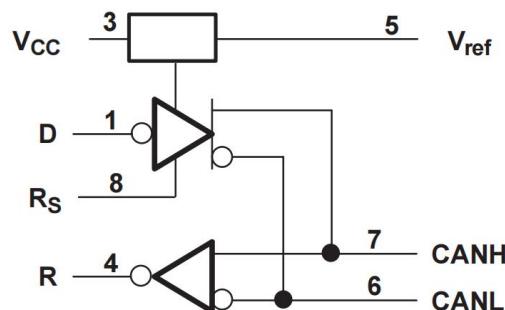

#### 4. PIN CONFIGURATION AND FUNCTIONS

**Pin Functions**

| PIN              |     | TYPE   | DESCRIPTION                                                                                                                                                                                    |

|------------------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO. |        |                                                                                                                                                                                                |

| D                | 1   | I      | CAN transmit data input (LOW for dominant and HIGH for recessive bus states), also called TXD, driver input                                                                                    |

| GND              | 2   | GND    | Ground connection                                                                                                                                                                              |

| V <sub>CC</sub>  | 3   | Supply | Transceiver 3.3V supply voltage                                                                                                                                                                |

| R                | 4   | O      | CAN receive data output (LOW for dominant and HIGH for recessive bus states), also called RXD, receiver output                                                                                 |

| V <sub>ref</sub> | 5   | O      | XL65HVD230 and XL65HVD231: V <sub>CC</sub> / 2 reference output pin                                                                                                                            |

| CANL             | 6   | I/O    | Low level CAN bus line                                                                                                                                                                         |

| CANH             | 7   | I/O    | High level CAN bus line                                                                                                                                                                        |

| R <sub>S</sub>   | 8   | I      | XL65HVD230 and XL65HVD231: Mode select pin: strong pull down to GND = high speed mode, strong pull up to V <sub>CC</sub> = low power mode, 10kΩ to 100kΩ pull down to GND = slope control mode |

#### 5. SPECIFICATIONS

##### 5.1. Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                                                              | MIN                                     | MAX                  | UNIT |

|------------------------------------------------------------------------------|-----------------------------------------|----------------------|------|

| Supply voltage, V <sub>CC</sub>                                              | -0.3                                    | 6                    | V    |

| Voltage at any bus terminal (CANH or CANL)                                   | -4                                      | 16                   | V    |

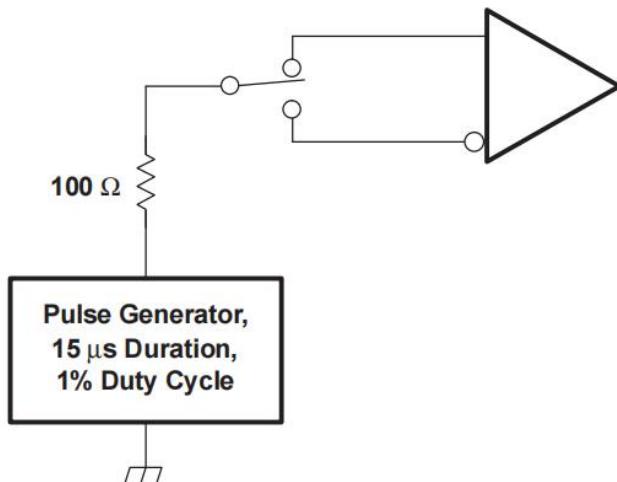

| Voltage input, transient pulse, CANH and CANL, through 100 Ω (see Figure 24) | -25                                     | 25                   | V    |

| Digital Input and Output voltage, V <sub>I</sub> (D or R)                    | -0.5                                    | V <sub>CC</sub> +0.5 | V    |

| Receiver output current, I <sub>O</sub>                                      | -11                                     | 11                   | mA   |

| Continuous total power dissipation                                           | See <a href="#">Thermal Information</a> |                      |      |

| Storage temperature, T <sub>stg</sub>                                        | -40                                     | 85                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under [Recommended Operating Conditions](#) is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential I/O bus voltages, are with respect to network ground terminal

## 5.2. ESD Ratings

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              |       | All pins | ±16000 | V |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|----------|--------|---|

|                    |                         | CANH, CANL and GND                                                             | ±4000 |          |        |   |

|                    |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 |          |        |   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 5.3. Recommended Operating Conditions

|                                                             |          | MIN               | NOM | MAX             | NOTE |

|-------------------------------------------------------------|----------|-------------------|-----|-----------------|------|

| Supply voltage, V <sub>CC</sub>                             |          | 3                 |     | 3.6             | V    |

| Voltage at any bus terminal (common mode) V <sub>IC</sub>   |          | -2 <sup>(1)</sup> |     | 7               | V    |

| Voltage at any bus terminal (separately) V <sub>I</sub>     |          | -2.5              |     | 7.5             | V    |

| High-level input voltage, V <sub>IH</sub>                   | D, R     | 2                 |     |                 | V    |

| Low-level input voltage, V <sub>IL</sub>                    | D, R     |                   |     | 0.8             | V    |

| Differential input voltage, V <sub>ID</sub> (see Figure 22) |          | -6                |     | 6               | V    |

| Input voltage, V <sub>(RS)</sub>                            |          | 0                 |     | V <sub>CC</sub> | V    |

| Input voltage for standby or sleep, V <sub>(RS)</sub>       |          | 0.7VCC            |     | V <sub>CC</sub> | V    |

| Wave-shaping resistance, R <sub>S</sub>                     |          | 0                 |     | 100             | kΩ   |

| High-level output current, I <sub>OH</sub>                  | Driver   | -40               |     |                 | mA   |

|                                                             | Receiver | -8                |     |                 |      |

| Low-level output current, I <sub>OL</sub>                   | Driver   |                   |     | 48              | mA   |

|                                                             | Receiver |                   |     | 8               |      |

| Thermal shutdown temperature                                |          |                   | 165 |                 | °C   |

| Thermal shutdown hysteresis                                 |          |                   | 10  |                 |      |

| Operating free-air temperature, T <sub>A</sub>              |          | -40               |     | 85              |      |

(1) The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

## 5.4. Thermal Information

| THERMAL METRIC        |                                              | 65HVD230 | 65HVD231 | UNIT |  |

|-----------------------|----------------------------------------------|----------|----------|------|--|

|                       |                                              | D        |          |      |  |

|                       |                                              | 8 PINS   |          |      |  |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 76.8     | 101.5    | °CW  |  |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 33.4     | 43.3     | °CW  |  |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 15.3     | 42.2     | °CW  |  |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 1.4      | 4.8      | °CW  |  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 14.9     | 41.8     | °CW  |  |

## 5.5. Electrical Characteristics: Driver

over recommended operating conditions (unless otherwise noted)

| PARAMETER   |                              | TEST CONDITIONS |                                                                                   | MIN       | TYP <sup>(1)</sup> | MAX  | UNIT          |

|-------------|------------------------------|-----------------|-----------------------------------------------------------------------------------|-----------|--------------------|------|---------------|

| $V_{OH}$    | Bus output voltage           | Dominant        | $V_i = 0 \text{ V}$ , See <a href="#">Figure 18</a> and <a href="#">Figure 20</a> | CANH      | 2.45               |      | $V_{CC}$      |

|             |                              |                 |                                                                                   | CANL      | 0.5                |      | 125           |

| $V_{OL}$    |                              | Recessive       | $V_i = 3 \text{ V}$ , See <a href="#">Figure 18</a> and <a href="#">Figure 20</a> | CANH      |                    | 2.3  |               |

|             |                              |                 |                                                                                   | CANL      |                    | 2.3  |               |

| $V_{OD(D)}$ | Differential output voltage  | Dominant        | $V_i = 0 \text{ V}$ , See <a href="#">Figure 18</a>                               |           | 1.5                | 2    | 3             |

|             |                              |                 | $V_i = 0 \text{ V}$ , See <a href="#">Figure 19</a>                               |           | 1.2                | 2    | 3             |

| $V_{OD(R)}$ |                              | Recessive       | $V_i = 3 \text{ V}$ , See <a href="#">Figure 18</a>                               |           | -120               | 0    | 12            |

|             |                              |                 | $V_i = 3 \text{ V}$ , No load                                                     |           | -0.5               | 0.2  | 0.05          |

| $I_{IH}$    | High-level input current     |                 | $V_i = 2 \text{ V}$                                                               |           | -30                |      | $\mu\text{A}$ |

| $I_{IL}$    | Low-level input current      |                 | $V_i = 0.8 \text{ V}$                                                             |           | -30                |      | $\mu\text{A}$ |

| $I_{OS}$    | Short-circuit output current |                 | $V_{CANH} = -2 \text{ V}$                                                         |           | -250               |      | 250           |

|             |                              |                 | $V_{CANL} = 7 \text{ V}$                                                          |           | -250               |      | 250           |

| $C_o$       | Output capacitance           |                 | See receiver                                                                      |           |                    |      |               |

| $I_{CC}$    | Standby                      | XL65HVD230      | $V_{(RS)} = V_{CC}$                                                               |           |                    | 370  | 600           |

|             | Sleep                        | XL65HVD231      | $V_{(RS)} = V_{CC}$ , D at $V_{CC}$                                               |           |                    | 0.04 | 1             |

|             | Dominant                     |                 | $V_i = 0 \text{ V}$ , No load                                                     | Dominant  |                    | 10   | 17            |

|             | Recessive                    |                 | $V_i = V_{CC}$ , No load                                                          | Recessive |                    | 10   | 17            |

(1) All typical values are at 25°C and with a 3.3-V supply

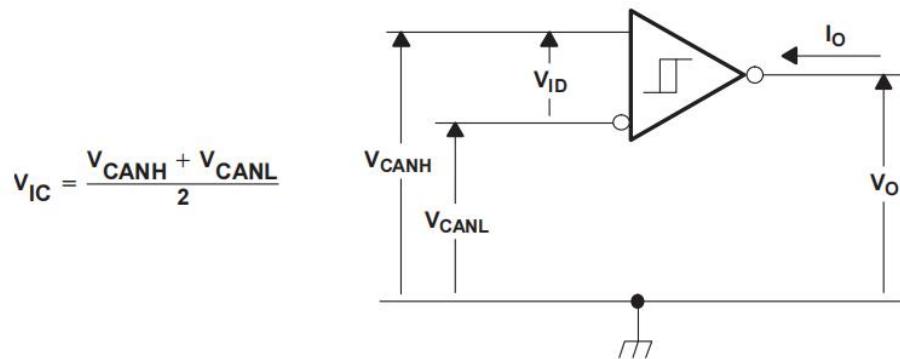

## 5.6. Electrical Characteristics: Receiver

over recommended operating conditions (unless otherwise noted)

| PARAMETER  |                                            | TEST CONDITIONS                                                                                        |                             | MIN  | TYP <sup>(1)</sup> | MAX | UNIT          |

|------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------|------|--------------------|-----|---------------|

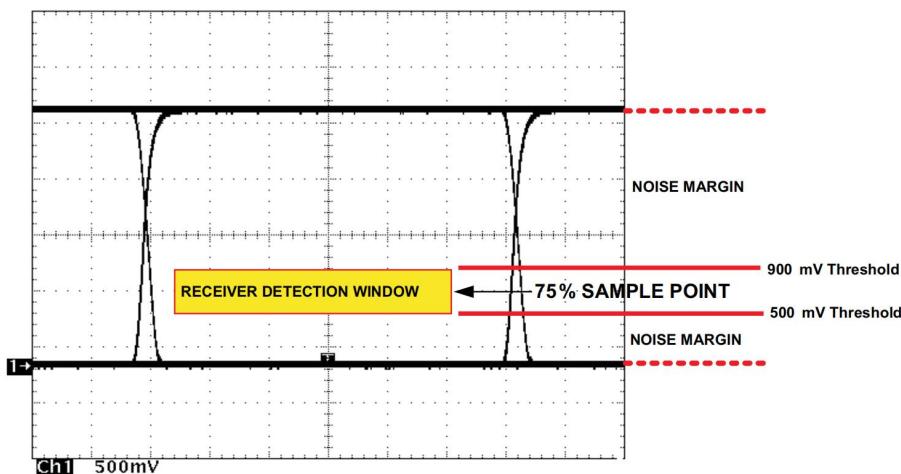

| $V_{IT+}$  | Positive-going input threshold voltage     | See <a href="#">Table 1</a>                                                                            |                             |      | 750                | 900 | mV            |

| $V_{IT-}$  | Negative-going input threshold voltage     |                                                                                                        |                             | 500  | 650                |     | mV            |

| $V_{HYS}$  | Hysteresis voltage ( $V_{IT+} - V_{IT-}$ ) | $-6 \text{ V} \leq V_{ID} \leq 500 \text{ mV}$ , $I_o = -8 \text{ mA}$ , See <a href="#">Figure 22</a> |                             |      | 100                |     |               |

| $V_{OH}$   | High-level output voltage                  |                                                                                                        |                             | 2.4  |                    |     | V             |

| $V_{OL}$   | Low-level output voltage                   | $900 \text{ mV} \leq V_{ID} \leq 6 \text{ V}$ , $I_o = 8 \text{ mA}$ , See <a href="#">Figure 22</a>   |                             |      |                    | 0.4 |               |

| $I_i$      | Bus input current                          | $V_{IH} = 7 \text{ V}$                                                                                 | Other input at 0 V, D = 3 V | 100  |                    | 250 | $\mu\text{A}$ |

|            |                                            | $V_{IH} = 7 \text{ V}$ , $V_{CC} = 0 \text{ V}$                                                        |                             | 100  |                    | 350 |               |

|            |                                            | $V_{IH} = -2 \text{ V}$                                                                                |                             | -200 |                    | -30 |               |

|            |                                            | $V_{IH} = -2 \text{ V}$ , $V_{CC} = 0 \text{ V}$                                                       |                             | -100 |                    | -20 | $\mu\text{A}$ |

| $C_i$      | CANH, CANL input capacitance               | Pin-to-ground, $V_{(D)} = 3 \text{ V}$ , $V_i = 0.4 \sin(4E6\pi t) + 0.5 \text{ V}$                    |                             |      | 32                 |     | pF            |

| $C_{Diff}$ | Differential input capacitance             | Pin-to-pin, $V_{(D)} = 3 \text{ V}$ , $V_i = 0.4 \sin(4E6\pi t) + 0.5 \text{ V}$                       |                             |      | 16                 |     | pF            |

| $R_{Diff}$ | Differential input resistance              | Pin-to-pin, $V_{(D)} = 3 \text{ V}$                                                                    |                             | 40   | 70                 | 100 | k $\Omega$    |

| $R_i$      | CANH, CANL input resistance                |                                                                                                        |                             | 20   | 35                 | 50  | k $\Omega$    |

| $I_{CC}$   | Supply current                             | See driver                                                                                             |                             |      |                    |     |               |

(1) All typical values are at 25°C and with a 3.3-V supply

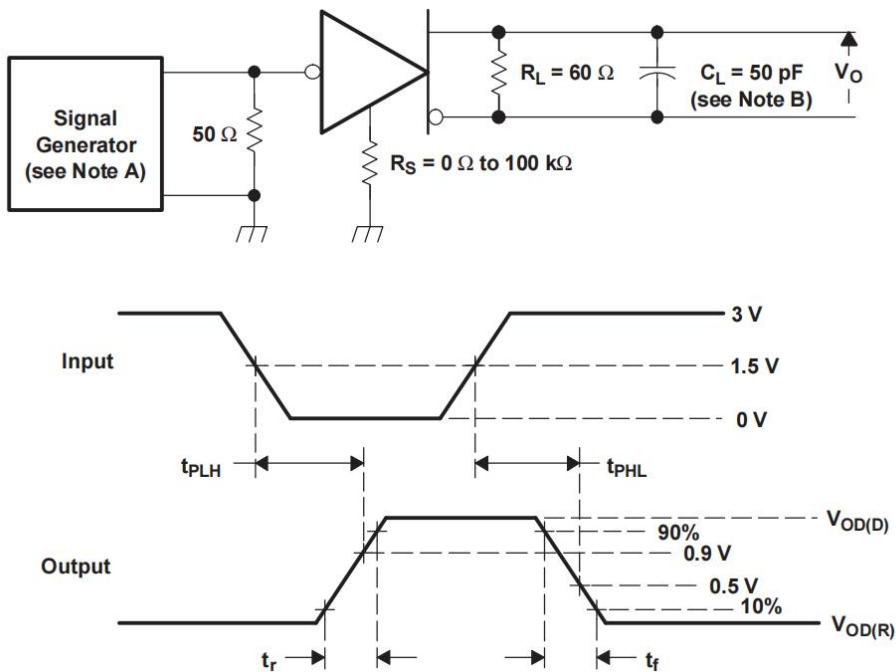

## 5.7. Switching Characteristics: Driver

over recommended operating conditions (unless otherwise noted)

| PARAMETER   |                                                  |                                     | TEST CONDITIONS                                 | MIN | TYP | MAX  | UNIT |  |

|-------------|--------------------------------------------------|-------------------------------------|-------------------------------------------------|-----|-----|------|------|--|

| $t_{PLH}$   | Propagation delay time, low-to-high-level output | $V_{(RS)} = 0$ V                    | $C_L = 50$ pF,<br>See <a href="#">Figure 21</a> |     | 35  | 85   | ns   |  |

|             |                                                  | $R_S$ with 10 k $\Omega$ to ground  |                                                 |     | 70  | 125  |      |  |

|             |                                                  | $R_S$ with 100 k $\Omega$ to ground |                                                 |     | 500 | 870  |      |  |

| $t_{PHL}$   | Propagation delay time, high-to-low-level output | $V_{(RS)} = 0$ V                    | $C_L = 50$ pF,<br>See <a href="#">Figure 21</a> |     | 70  | 120  | ns   |  |

|             |                                                  | $R_S$ with 10 k $\Omega$ to ground  |                                                 |     | 130 | 180  |      |  |

|             |                                                  | $R_S$ with 100 k $\Omega$ to ground |                                                 |     | 870 | 1200 |      |  |

| $t_{sk(p)}$ | Pulse skew ( $ t_{PHL} - t_{PLH} $ )             | $V_{(RS)} = 0$ V                    | $C_L = 50$ pF,<br>See <a href="#">Figure 21</a> |     | 35  |      | ns   |  |

|             |                                                  | $R_S$ with 10 k $\Omega$ to ground  |                                                 |     | 60  |      |      |  |

|             |                                                  | $R_S$ with 100 k $\Omega$ to ground |                                                 |     | 370 |      |      |  |

| $t_r$       | Differential output signal rise time             | $V_{(RS)} = 0$ V                    | $R_S$ with 10 k $\Omega$ to ground              | 25  | 50  | 100  | ns   |  |

| $t_f$       | Differential output signal fall time             |                                     |                                                 | 40  | 55  | 80   | ns   |  |

| $t_r$       | Differential output signal rise time             | $R_S$ with 10 k $\Omega$ to ground  |                                                 | 80  | 120 | 160  | ns   |  |

| $t_f$       | Differential output signal fall time             |                                     |                                                 | 80  | 125 | 150  | ns   |  |

| $t_r$       | Differential output signal rise time             | $R_S$ with 100 k $\Omega$ to ground |                                                 | 600 | 800 | 1200 | ns   |  |

| $t_f$       | Differential output signal fall time             |                                     |                                                 | 600 | 825 | 1000 | ns   |  |

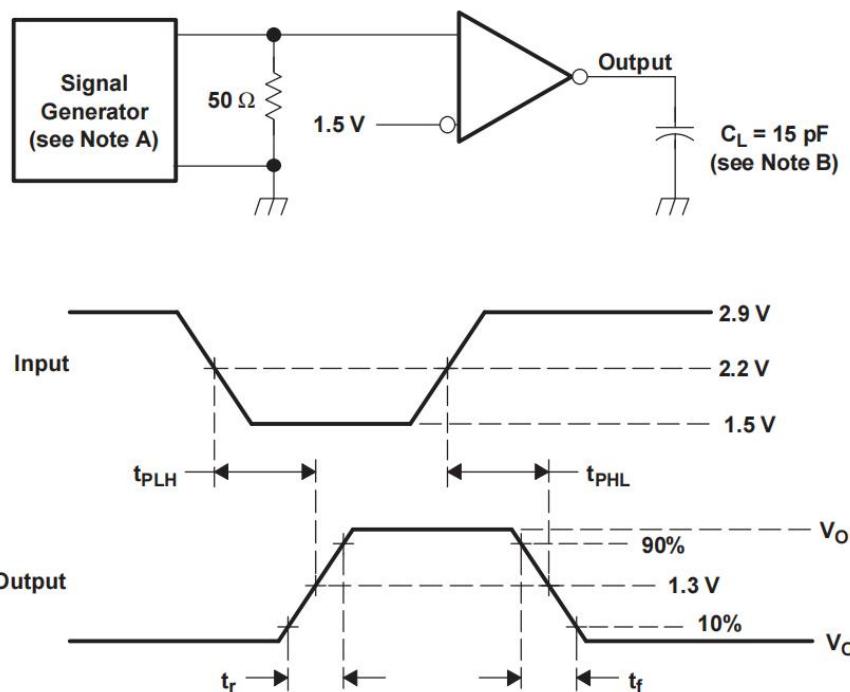

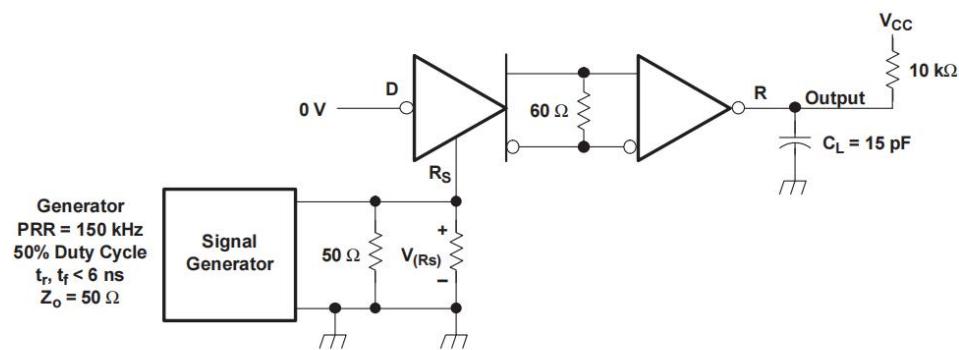

## 5.8. Switching Characteristics: Receiver

over recommended operating conditions (unless otherwise noted)

| PARAMETER   |                                                  | TEST CONDITIONS               | MIN | TYP | MAX | UNIT |

|-------------|--------------------------------------------------|-------------------------------|-----|-----|-----|------|

| $t_{PLH}$   | Propagation delay time, low-to-high-level output | See <a href="#">Figure 23</a> |     | 35  | 50  | ns   |

| $t_{PHL}$   | Propagation delay time, high-to-low-level output |                               |     | 35  | 50  | ns   |

| $t_{sk(p)}$ | Pulse skew ( $ t_{PHL} - t_{PLH} $ )             |                               |     |     | 10  | ns   |

| $t_r$       | Output signal rise time                          | See <a href="#">Figure 23</a> |     | 1.5 |     | ns   |

| $t_f$       | Output signal fall time                          |                               |     | 1.5 |     | ns   |

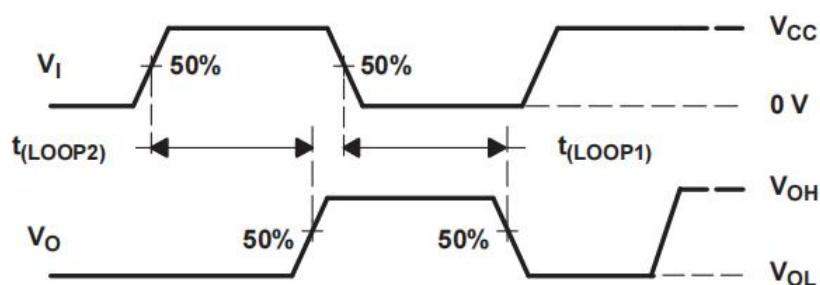

## 5.9. Switching Characteristics: Device

over recommended operating conditions (unless otherwise noted)

| PARAMETER     |                                                                          | TEST CONDITIONS                                                    | MIN | TYP | MAX | UNIT |

|---------------|--------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|-----|------|

| $t_{(LOOP1)}$ | Total loop delay, driver input to receiver output, recessive to dominant | $V_{(RS)} = 0$ V, See <a href="#">Figure 26</a>                    |     | 70  | 115 | ns   |

|               |                                                                          | $R_S$ with 10 k $\Omega$ to ground, See <a href="#">Figure 26</a>  |     | 105 | 175 |      |

|               |                                                                          | $R_S$ with 100 k $\Omega$ to ground, See <a href="#">Figure 26</a> |     | 535 | 920 |      |

| $t_{(LOOP2)}$ | Total loop delay, driver input to receiver output, dominant to recessive | $V_{(RS)} = 0$ V, See <a href="#">Figure 26</a>                    |     | 100 | 135 | ns   |

|               |                                                                          | $R_S$ with 10 k $\Omega$ to ground, See <a href="#">Figure 26</a>  |     | 155 | 185 |      |

|               |                                                                          | $R_S$ with 100 k $\Omega$ to ground, See <a href="#">Figure 26</a> |     | 830 | 990 |      |

## 5.10. Device Control-Pin Characteristics

over recommended operating conditions (unless otherwise noted)

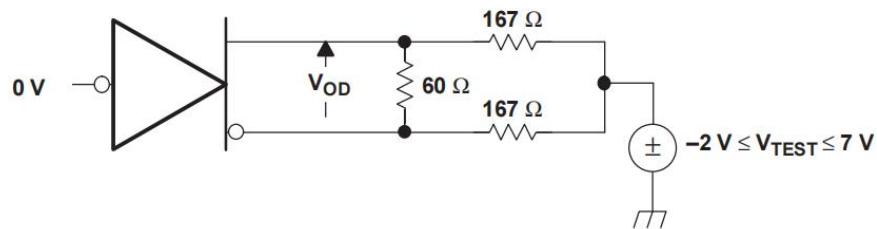

| PARAMETER    |                                                      | TEST CONDITIONS                         | MIN                 | TYP <sup>(1)</sup> | MAX                 | UNIT    |

|--------------|------------------------------------------------------|-----------------------------------------|---------------------|--------------------|---------------------|---------|

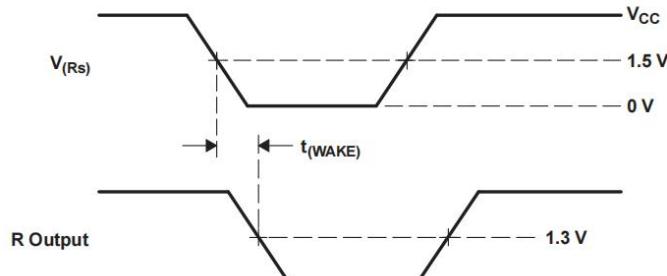

| $t_{(WAKE)}$ | XL65HVD230 wake-up time from standby mode with $R_S$ | See <a href="#">Figure 25</a>           |                     | 0.55               | 1.5                 | $\mu$ s |

|              | XL65HVD231 wake-up time from sleep mode with $R_S$   |                                         |                     | 3                  | 5                   | $\mu$ s |

| $V_{ref}$    | Reference output voltage                             | $-5 \mu$ A < $I_{(Vref)}$ < 5 $\mu$ A   | 0.45V <sub>CC</sub> |                    | 0.55V <sub>CC</sub> | V       |

|              |                                                      | $-50 \mu$ A < $I_{(Vref)}$ < 50 $\mu$ A | 0.4V <sub>CC</sub>  |                    | 0.6V <sub>CC</sub>  |         |

| $I_{(RS)}$   | Input current for high-speed                         | $V_{(RS)} < 1$ V                        | -450                |                    | 0                   | $\mu$ A |

(1) All typical values are at 25°C and with a 3.3-V supply.

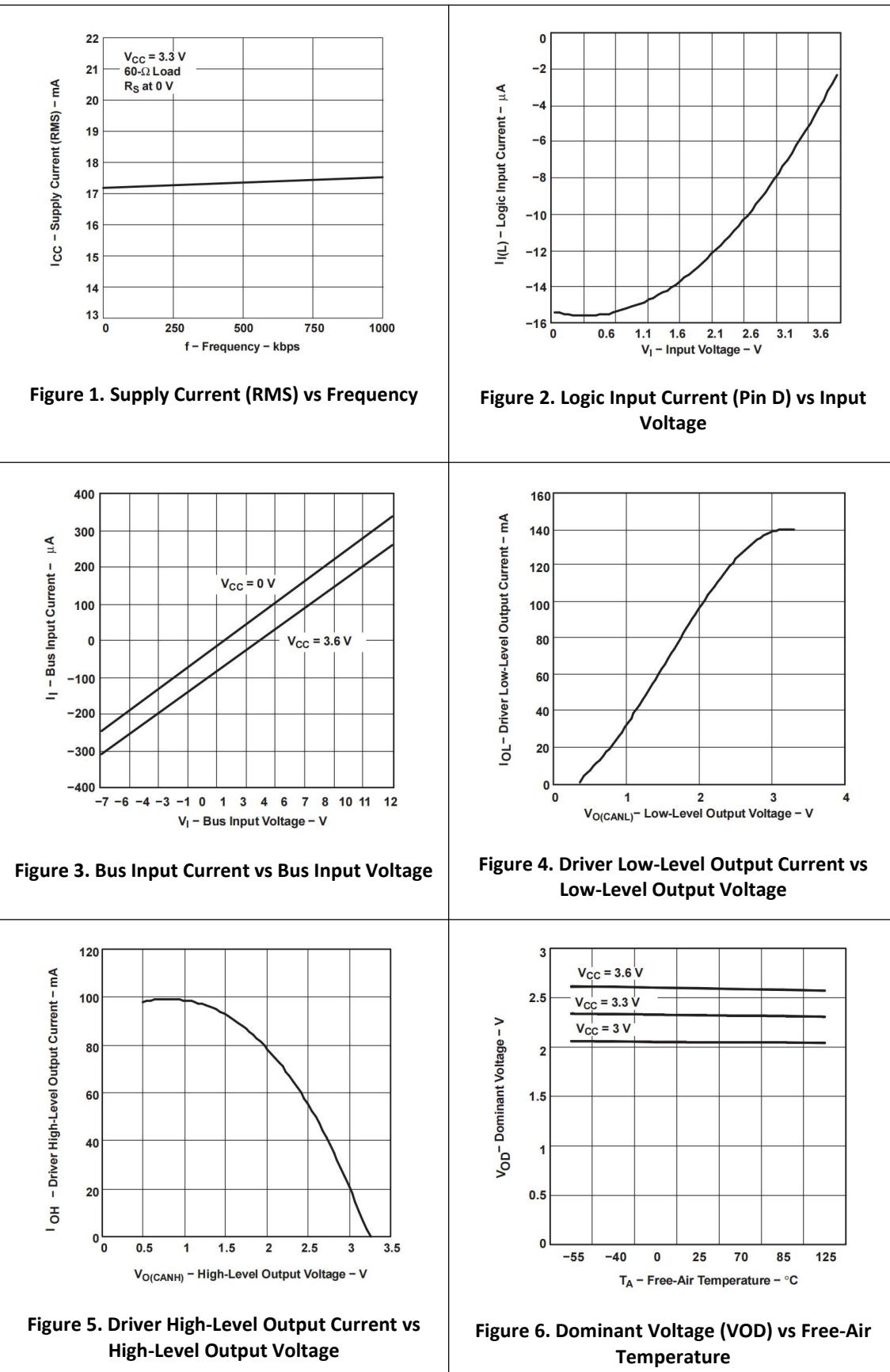

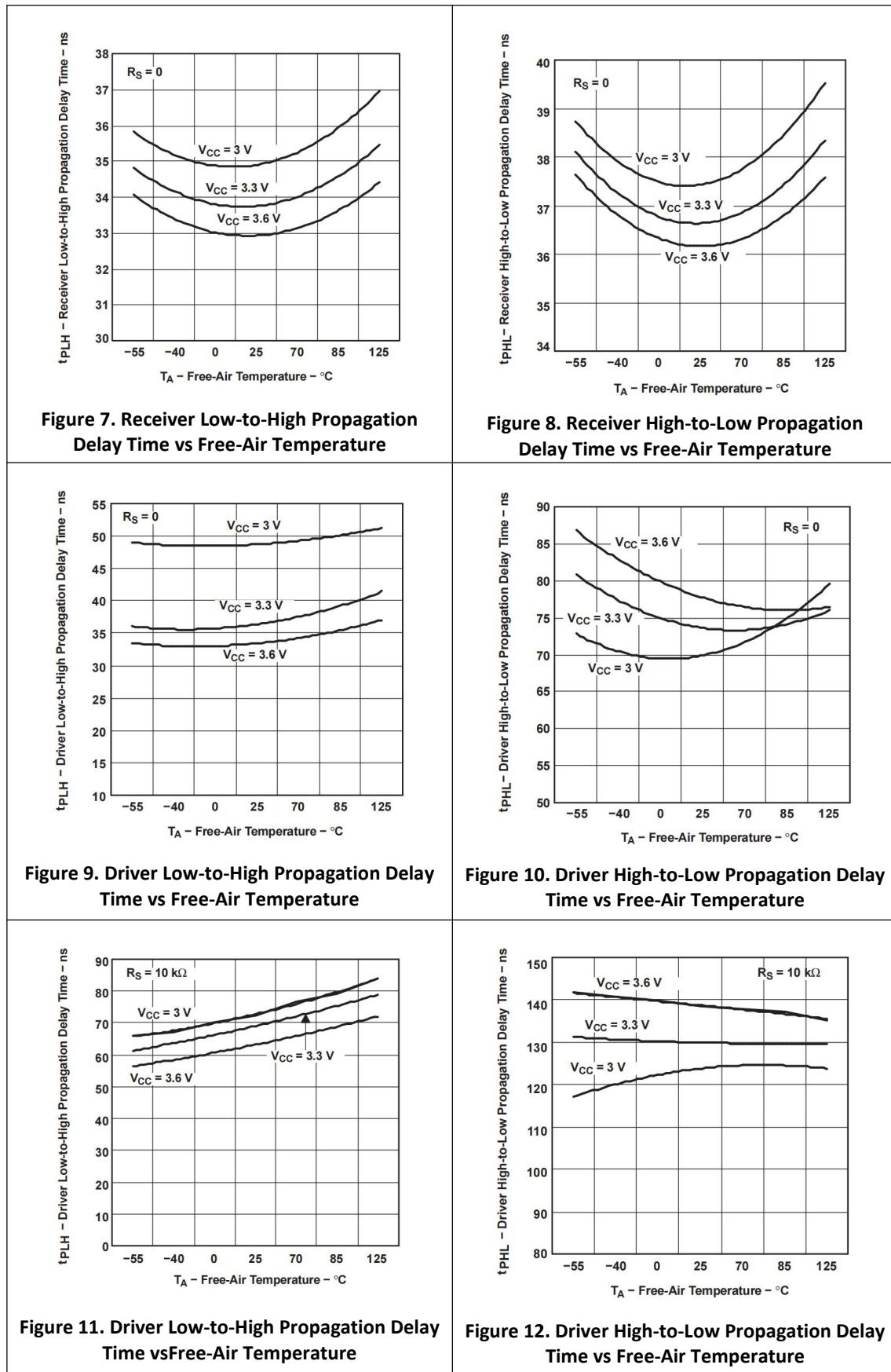

### 5.11. Typical Characteristics

**Typical Characteristics (continued)**

**Typical Characteristics (continued)**

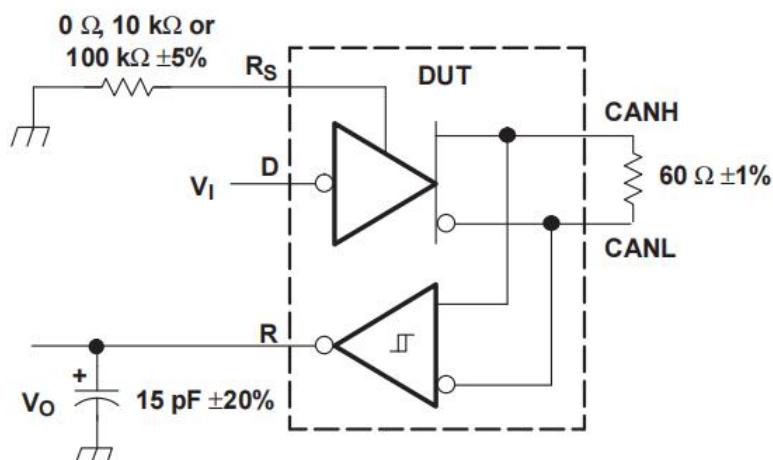

## 6. PARAMETER MEASUREMENT INFORMATION

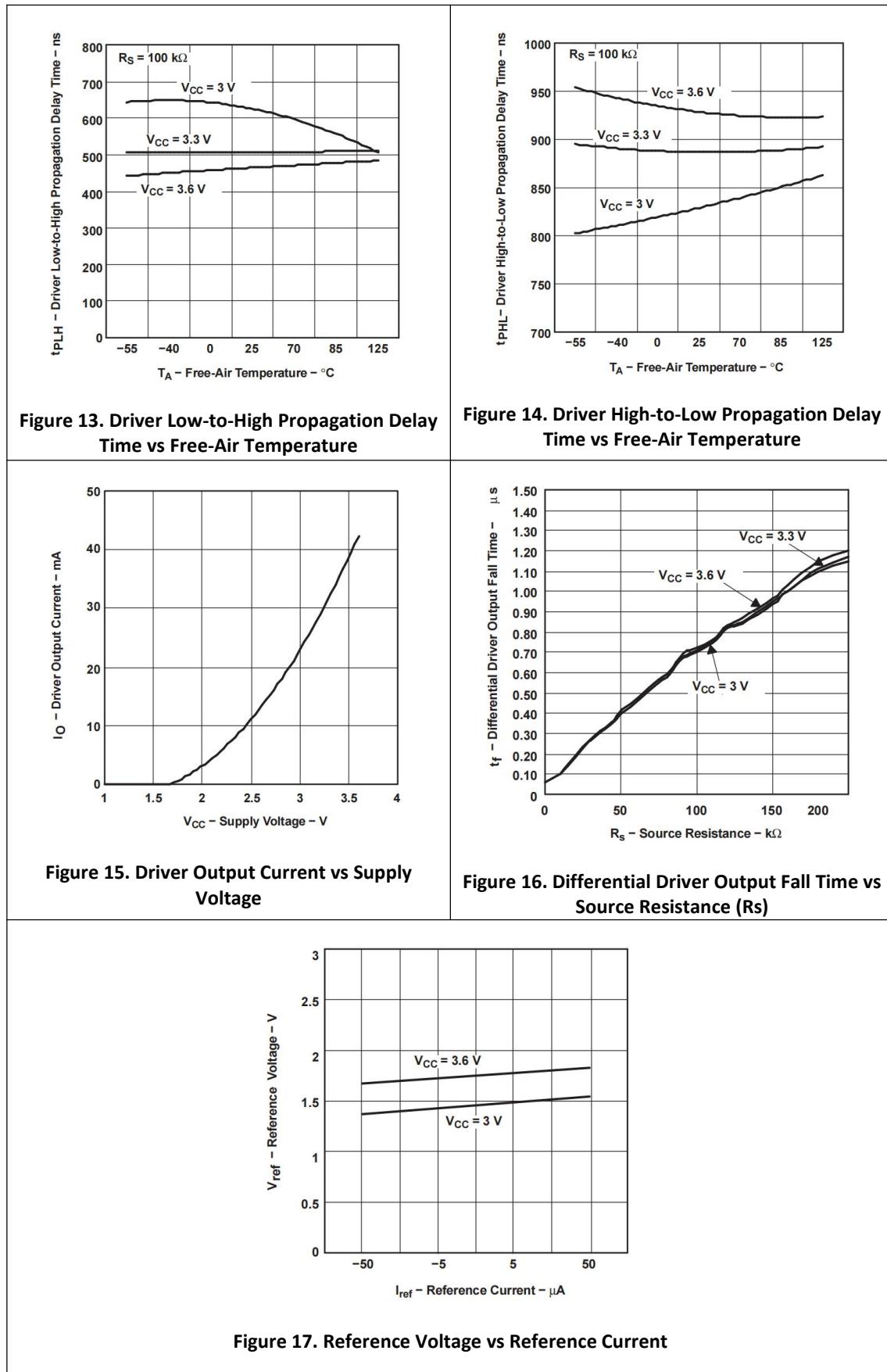

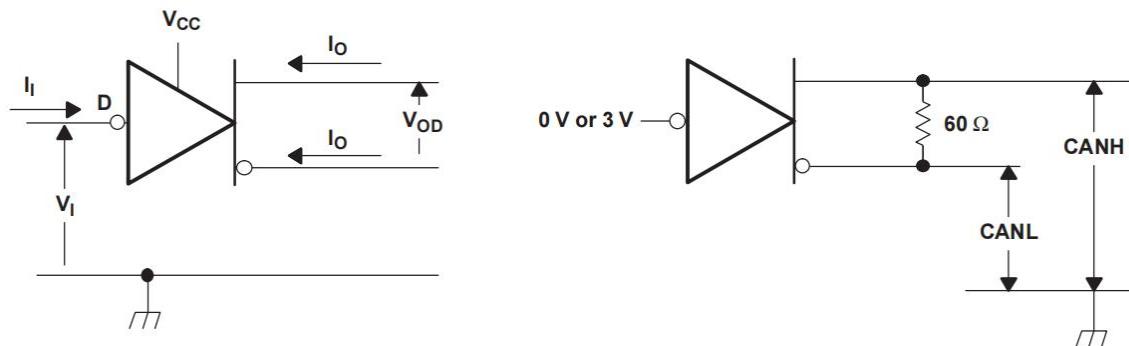

Figure 18. Driver Voltage and Current Definitions

Figure 19. Driver  $V_{OD}$

Figure 20. Driver Output Voltage Definitions

A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  500 kHz, 50% duty cycle,  $t_r \leq 6$  ns,  $t_f \leq 6$  ns,  $Z_o = 50 \Omega$ .

B.  $C_L$  includes probe and jig capacitance.

**Figure 21. Driver Test Circuit and Voltage Waveforms**

**Figure 22. Receiver Voltage and Current Definitions**

A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  500 kHz, 50% duty cycle,  $t_r \leq 6$  ns,  $t_f \leq 6$  ns,  $Z_0 = 50 \Omega$ .

B. CL includes probe and jig capacitance.

**Figure 23. Receiver Test Circuit and Voltage Waveforms**

**Figure 24. Overvoltage Protection**

Table 1. Receiver Characteristics Over Common Mode With  $V_{(Rs)} = 1.2$  V

| $V_{IC}$ | $V_{ID}$ | $V_{CANH}$ | $V_{CANL}$ | R OUTPUT |          |

|----------|----------|------------|------------|----------|----------|

| -2 V     | 900 mV   | -1.55 V    | -2.45 V    | L        | $V_{OL}$ |

| 7 V      | 900 mV   | 8.45 V     | 6.55 V     | L        |          |

| 1 V      | 6 V      | 4 V        | -2 V       | L        |          |

| 4 V      | 6 V      | 7 V        | 1 V        | L        |          |

| -2 V     | 500 mV   | -1.75 V    | -2.25 V    | H        | $V_{OH}$ |

| 7 V      | 500 mV   | 7.25 V     | 6.75 V     | H        |          |

| 1 V      | -6 V     | -2 V       | 4 V        | H        |          |

| 4 V      | -6 V     | 1 V        | 7 V        | H        |          |

| X        | X        | Open       | Open       | H        |          |

Figure 25.  $t_{(WAKE)}$  Test Circuit and Voltage Waveforms

A. All  $V_I$  input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \leq 6$  ns, Pulse Repetition Rate (PRR) = 125 kHz, 50% duty cycle.

**Figure 26.  $t_{\text{LOOP}}$  Test Circuit and Voltage Waveforms**

Figure 27. Equivalent Input and Output Schematic Diagrams

## 7. DETAILED DESCRIPTION

### 7.1. Overview

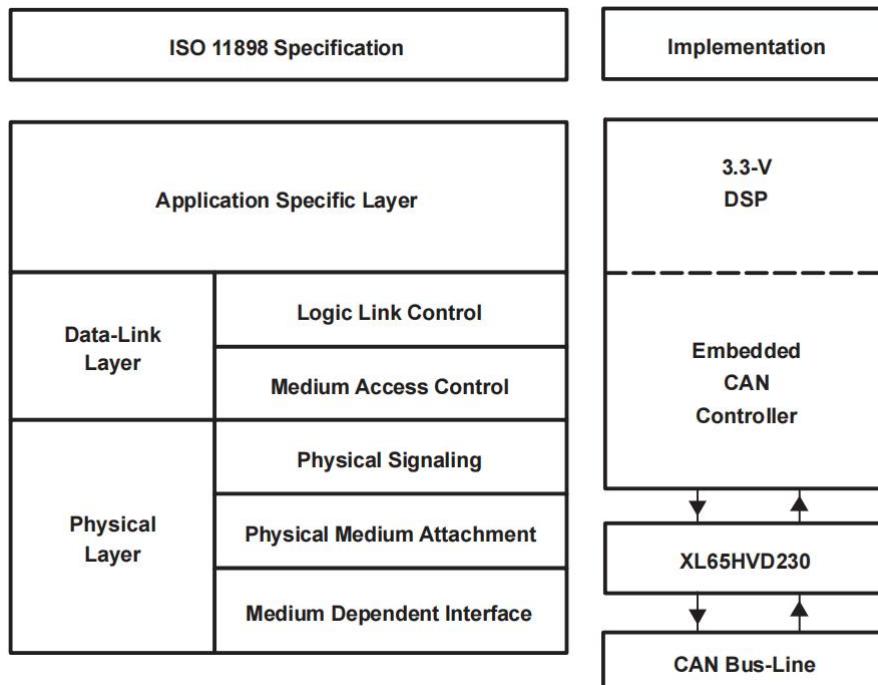

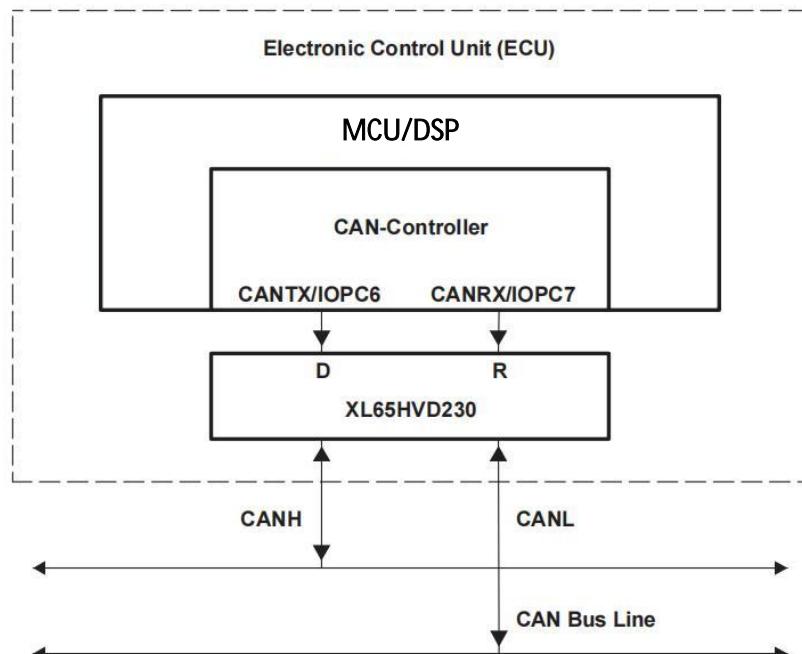

ISO 11898 family of standards are the international standard for high speed serial communication using the controller area network (CAN) bus protocol and physical layers (transceivers). It supports multimaster operation, real time control, programmable data rates up to 1 Mbps, and powerful redundant error checking procedures that provide reliable data transmission. It is suited for networking *intelligent* devices as well as sensors and actuators within the rugged electrical environment of a machine chassis or factory floor. The XL65HVD23x family of 3.3 V CAN transceivers implement the lowest layers of the ISO/OSI reference model, the ISO11898-2 standard. This is the interface with the physical signaling output of the CAN controller of the  $\mu$ Ps, MCUs and DSPs as illustrated in [Figure 28](#).

Figure 28. Layered ISO 11898 Standard Architecture

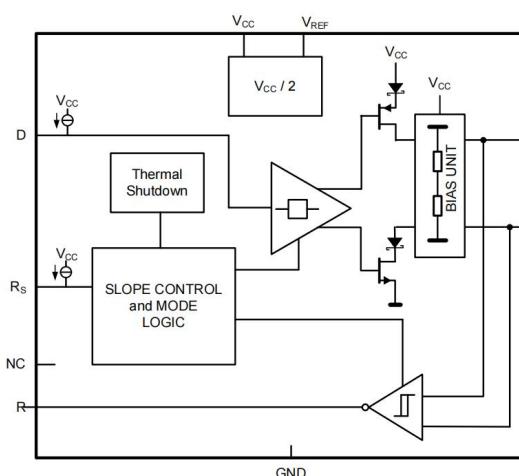

### 7.2. Functional Block Diagram

**XL65HVD230, XL65HVD231**

Logic Diagram (Positive Logic)

Figure 29. Logic Diagram (Positive Logic)

### 7.3. Feature Description

The XL65HVD230/231 are pin-compatible (but not functionally identical) with one another and, depending upon the application, may be used with identical circuit boards.

These transceivers feature single 3.3 V supply operation and standard compatibility with signaling rates up to 1 Mbps,  $\pm 16$  kV HBM ESD protection on the bus pins, thermal shutdown protection, bus fault protection, and open circuit receiver failsafe. The fail-safe design of the receiver assures a logic high at the receiver output if the bus wires become open circuited.

The bus pins are also maintained in a high-impedance state during low  $V_{CC}$  conditions to ensure glitch-free power-up and power-down bus protection for hot-plugging applications. This high-impedance condition also means that an unpowered node does not disturb the bus. Transceivers without this feature usually have a very low output impedance. This results in a high current demand when the transceiver is unpowered, a condition that could affect the entire bus.

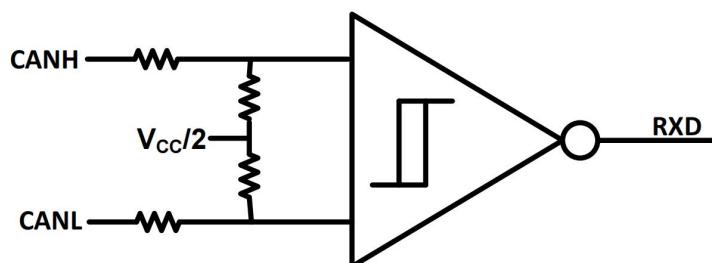

#### 7.3.1. $V_{ref}$ Voltage Reference

The  $V_{ref}$  pin (pin 5) on the XL65HVD230 and XL65HVD231 is available as a  $V_{CC}/2$  voltage reference. This pin can be connected to the common mode point of a split termination to help further stabilize the common mode voltage of the bus. If the  $V_{ref}$  pin is not used it may be left floating.

#### 7.3.2. Thermal Shutdown

If a high ambient temperature or excessive output currents result in thermal shutdown, the driver will be disabled and the bus pins become high impedance. During thermal shutdown the D pin to bus transmission path is blocked and the CAN bus pins are high impedance and biased to a recessive level. Once the thermal shutdown condition is cleared and the junction temperature drops below the thermal shutdown temperature the driver will be reactivated and resume normal operation. During a thermal shutdown the receiver to R pin path remains operational.

### 7.4. Device Functional Modes

The Rs pin (Pin 8) of the XL65HVD230 and XL65HVD231 provides three different modes of operation: high speed mode, slope-control mode, and low-power mode.

#### 7.4.1. High-Speed Mode

The high-speed mode can be selected by applying a logic low to the Rs pin (pin 8). The high-speed mode of operation is commonly employed in industrial applications. High-speed allows the output to switch as fast as possible with no internal limitation on the output rise and fall slopes. If the high speed transitions are a concern for emissions performance slope control mode can be used.

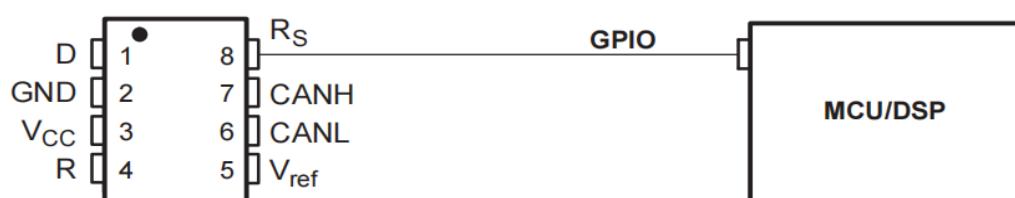

If both high speed mode and the low-power standby mode is to be used in the application, direct connection to a  $\mu$ P, MCU or DSP general purpose output pin can be used to switch between a logic-low level ( $< 1.2$  V) for high speed operation, and the logic-high level ( $> 0.75$   $V_{CC}$ ) for standby. [Figure 30](#) shows a typical DSP connection, and [Figure 31](#) shows the HVD230 driver output signal in high-speed mode on the CAN bus.

**Figure 30. RS (Pin 8) Connection to a MCU/DSP for High Speed/Standby Operation**

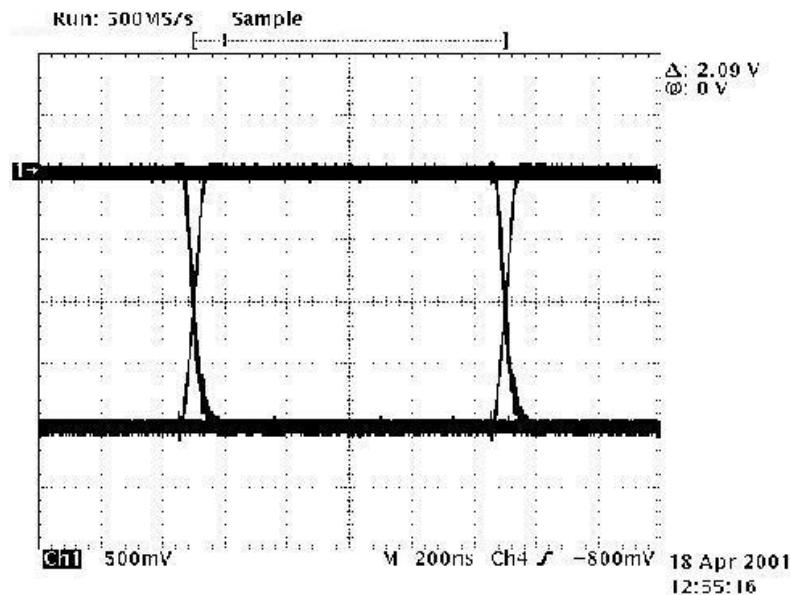

Figure 31. Typical High Speed XL65HVD230 Output Waveform into a 60-Ω Load

#### 7.4.2. Slope Control Mode

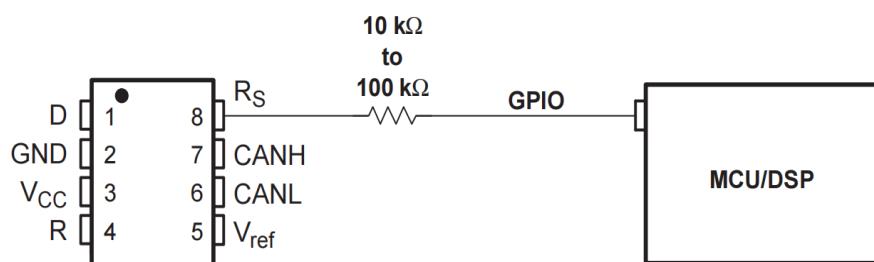

Electromagnetic compatibility is essential in many applications while still making use of unshielded twisted pair bus cable to reduce system cost. Slope control mode was added to the XL65HVD230 and XL65HVD231 devices to reduce the electromagnetic interference produced by the rise and fall times of the driver and resulting harmonics. These rise and fall slopes of the driver outputs can be adjusted by connecting a resistor from  $R_s$  (pin 8) to ground or to a logic low voltage, as shown in Figure 32. The slope of the driver output signal is proportional to the pin's output current. This slope control is implemented with an external resistor value of  $10\text{ k}\Omega$  to achieve a  $\sim 15\text{ V}/\mu\text{s}$  slew rate, and up to  $100\text{ k}\Omega$  to achieve a  $\sim 2.0\text{ V}/\mu\text{s}$  slew rate as displayed in Figure 33.

Figure 32. Slope Control/Standby Connection to a DSP

Figure 33. HVD230 Driver Output Signal Slope vs Slope Control Resistance Value

#### 7.4.3. Standby Mode (Listen Only Mode) of the HVD230

If a logic high ( $> 0.75$  VCC) is applied to RS (pin 8) in Figure 30 and Figure 32, the circuit of the XL65HVD230 enters a low-current, *listen only* standby mode, during which the driver is switched off and the receiver remains active. In this *listen only* state, the transceiver is completely passive to the bus. It makes no difference if a slope control resistor is in place as shown in Figure 32. The  $\mu P$  can reverse this low-power standby mode when the rising edge of a dominant state (bus differential voltage  $> 900$  mV typical) occurs on the bus. The  $\mu P$ , sensing bus activity, reactivates the driver circuit by placing a logic low ( $< 1.2$  V) on RS (pin 8).

#### 7.4.4. The Babbling Idiot Protection of the HVD230

Occasionally, a runaway CAN controller unintentionally sends messages that completely tie up the bus (what is referred to in CAN jargon as a babbling idiot). When this occurs, the  $\mu P$ , MCU or DSP can engage the *listen-only* standby mode of the transceiver to disable the driver and release the bus, even when access to the CAN controller has been lost. When the driver circuit is deactivated, its outputs default to a high impedance state (recessive).

#### 7.4.5. Sleep Mode of the HVD231

The unique difference between the XL65HVD230 and the XL65HVD231 is that both driver and receiver are switched off in the XL65HVD231 when a logic high is applied to RS (pin 8). The device remains in a very low power-sleep mode until the circuit is reactivated with a logic low applied to RS (pin 8). While in this sleep mode, the bus-pins are in a high-impedance state, while the D and R pins default to a logic high.

#### 7.4.6. Summary of Device Operating Modes

Table 2 shows a summary of the operating modes for the XL65HVD230 and XL65HVD231.

**Table 2. XL65HVD230 and XL65HVD231 Operating Modes**

| RS Pin                                                                          | MODE                |                             | DRIVER                             | RECEIVER       | RXD Pin                             |

|---------------------------------------------------------------------------------|---------------------|-----------------------------|------------------------------------|----------------|-------------------------------------|

| LOW, $V_{(RS)} < 1.2$ V,<br>strong pull down to<br>GND                          | High Speed Mode     |                             | Enabled (ON) High<br>Speed         | Enabled (ON)   | Mirrors Bus<br>State <sup>(1)</sup> |

| LOW, $V_{(RS)} < 1.2$ V, 10<br>k $\Omega$ to 100 k $\Omega$ pull down<br>to GND | Slope Control Mode  |                             | Enabled (ON) with<br>Slope Control | Enabled (ON)   | Mirrors Bus<br>State                |

| HIGH, $V_{(RS)} > 0.75$ V <sub>CC</sub>                                         | Low Current<br>Mode | XL65HVD230:<br>Standby Mode | Disabled (OFF)                     | Enabled (ON)   | Mirrors Bus<br>State                |

|                                                                                 |                     | XL65HVD231:<br>Sleep Mode   |                                    | Disabled (OFF) | High                                |

(1) Mirrors bus state: low if CAN bus is dominant, high if CAN bus is recessive.

**Table 3. XL65HVD230 and XL65HVD231 Driver Functions**

| DRIVER (XL65HVD230, XL65HVD231) <sup>(1)</sup> |                                                                                    |         |      |           |

|------------------------------------------------|------------------------------------------------------------------------------------|---------|------|-----------|

| INPUT D                                        | RS                                                                                 | OUTPUTS |      | BUS STATE |

|                                                |                                                                                    | CANH    | CANL |           |

| L                                              | $V_{(RS)} < 1.2$ V (including 10 k $\Omega$ to 100<br>k $\Omega$ pull down to GND) | H       | L    | Dominant  |

| H                                              |                                                                                    | Z       | Z    | Recessive |

| Open                                           | X                                                                                  | Z       | Z    | Recessive |

| X                                              | $V_{(RS)} > 0.75$ V <sub>CC</sub>                                                  | Z       | Z    | Recessive |

(1) H = high level; L = low level; X = irrelevant; ? = indeterminate; Z = high impedance

**Table 4. XL65HVD230 Receiver Functions**

| RECEIVER (XL65HVD230) <sup>(1)</sup> |    |          |

|--------------------------------------|----|----------|

| DIFFERENTIAL INPUTS                  | RS | OUTPUT R |

| $V_{ID} \geq 0.9$ V                  | X  | L        |

| $0.5$ V < $V_{ID} < 0.9$ V           | X  | ?        |

| $V_{ID} \leq 0.5$ V                  | X  | H        |

| Open                                 | X  | H        |

(1) H = high level; L = low level; X = irrelevant; ? = indeterminate

**Table 5. XL65HVD231 Receiver Functions**

| RECEIVER (XL65HVD231) <sup>(1)</sup> |                                                                                    |          |

|--------------------------------------|------------------------------------------------------------------------------------|----------|

| DIFFERENTIAL INPUTS                  | RS                                                                                 | OUTPUT R |

| $V_{ID} \geq 0.9$ V                  | $V_{(RS)} < 1.2$ V (including 10 k $\Omega$ to<br>100 k $\Omega$ pull down to GND) | L        |

| $0.5$ V < $V_{ID} < 0.9$ V           |                                                                                    | ?        |

| $V_{ID} \leq 0.5$ V                  |                                                                                    | H        |

| X                                    | $V_{(RS)} > 0.75$ V <sub>CC</sub>                                                  | H        |

| X                                    | $1.2$ V < $V_{(RS)} < 0.75$ V <sub>CC</sub>                                        | ?        |

| Open                                 | X                                                                                  | H        |

(1) H = high level; L = low level; X = irrelevant; ? = indeterminate

## 8. APPLICATION AND IMPLEMENTATION

**NOTE:** Information in the following applications sections is not part of the component specification, Does not warrant its accuracy or completeness. Customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1. Application Information

This application section provides information concerning the implementation of the physical medium attachment layer in a CAN network according to the ISO 11898 standard. It presents a typical application circuit and test results, as well as discussions on slope control, total loop delay, and interoperability in 5-V CAN systems.

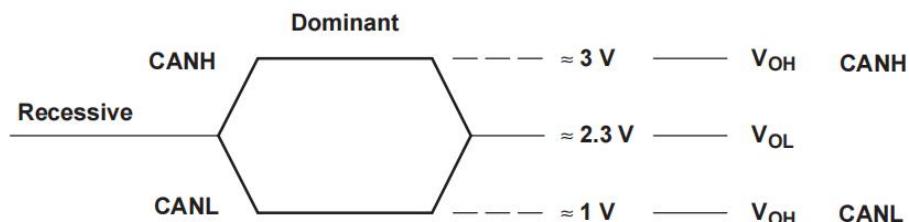

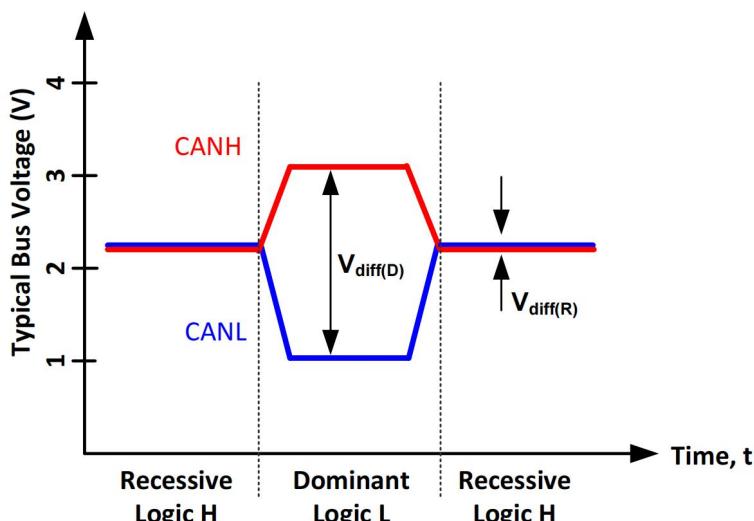

#### 8.1.1. CAN Bus States

The CAN bus has two states during powered operation of the device; dominant and recessive. A dominant bus state is when the bus is driven differentially, corresponding to a logic low on the D and R pin. A recessive bus state is when the bus is biased to  $V_{CC}/2$  via the high-resistance internal resistors  $R_I$  and  $R_{Diff}$  of the receiver, corresponding to a logic high on the D and R pins. See [Figure 34](#) and [Figure 35](#).

Figure 34. CAN Bus States (Physical Bit Representation)

Figure 35. Simplified Recessive Common Mode Bias and Receiver

## 8.2. Typical Application

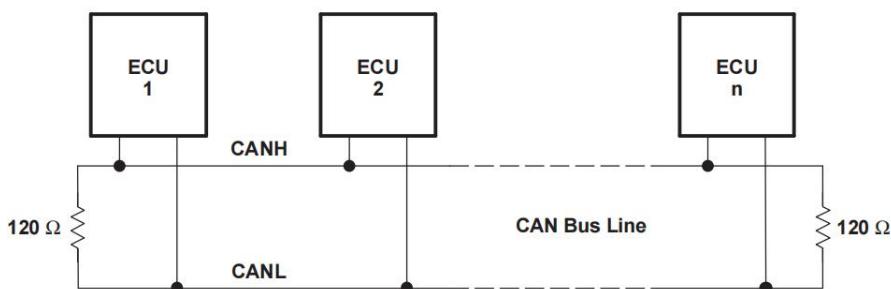

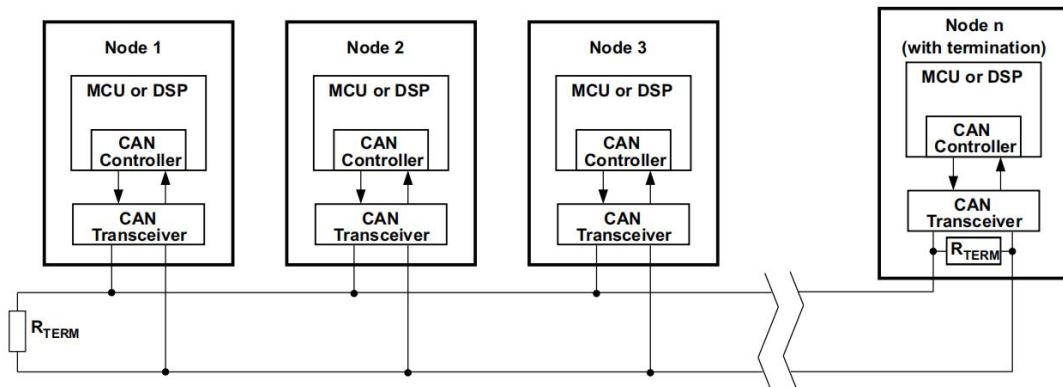

Figure 36 illustrates a typical application of the XL65HVD23x family. The output of the host  $\mu$ P's CAN controller (TXD) is connected to the transceivers driver input, pin D, and the transceivers receiver output, pin R, is connected to the input of the CAN controller (RXD). The transceiver is attached to the differential bus lines at pins CANH and CANL. Typically, the bus is a twisted pair of wires with a characteristic impedance of  $120 \Omega$ , in the standard half-duplex multipoint topology of Figure 37. Each end of the bus is terminated with  $120 \Omega$  resistors in compliance with the standard to minimize signal reflections on the bus.

Figure 36. Details of a Typical CAN Node

Figure 37. Typical CAN Network

### 8.2.1. Design Requirements

#### 8.2.1.1. CAN Termination

The ISO11898 standard specifies the interconnect to be a single twisted pair cable (shielded or unshielded) with  $120 \Omega$  characteristic impedance ( $Z_0$ ). Resistors equal to the characteristic impedance of the line should be used to terminate both ends of the cable to prevent signal reflections. Unterminated drop lines (stubs) connecting nodes to the bus should be kept as short as possible to minimize signal reflections. The termination may be on the cable or in a node, but if nodes may be removed from the bus the termination must be carefully placed so that it is not removed from the bus.

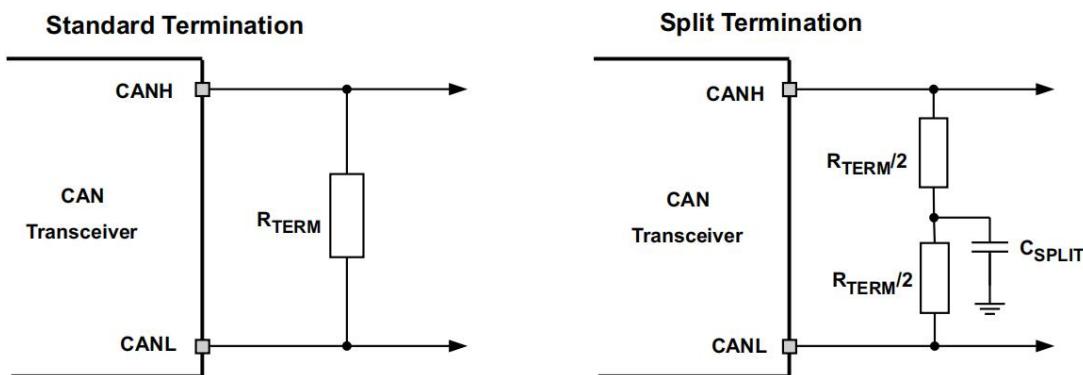

Figure 38. Typical CAN Bus

Termination is typically a  $120\ \Omega$  resistor at each end of the bus. If filtering and stabilization of the common mode voltage of the bus is desired, then split termination may be used (see [Figure 39](#)). Split termination utilizes two  $60\Omega$  resistors with a capacitor in the middle of these resistors to ground. Split termination improves the electromagnetic emissions behavior of the network by eliminating fluctuations in the bus common mode voltages at the start and end of message transmissions.

Care should be taken in the power ratings of the termination resistors used. Typically the worst case condition would be if the system power supply was shorted across the termination resistance to ground. In most cases the current flow through the resistor in this condition would be much higher than the transceiver's current limit.

Figure 39. CAN Bus Termination Concepts

#### 8.2.1.2. Loop Propagation Delay

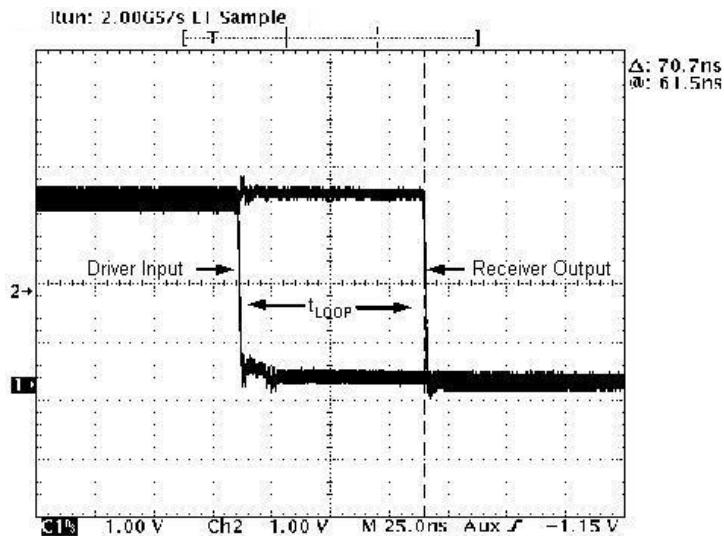

Transceiver loop delay is a measure of the overall device propagation delay, consisting of the delay from the driver input (D pin) to the differential outputs (CANH and CANL pins), plus the delay from the receiver inputs (CANH and CANL) to its output (R pin).

A typical loop delay for the XL65HVD230 transceiver is displayed in [Figure 40](#). This loop delay will increase as the slope of the driver output is slowed during slope control mode. This increased loop delay means that there is a tradeoff between the total bus length able to be used and the driver's output slope used via the slope control pin of the device. For example, the loop delay for a  $10\text{-k}\Omega$  resistor from the RS pin to ground is  $\sim 100\ \text{ns}$ , and the loop delay for a  $100\text{-k}\Omega$  resistor is  $\sim 500\ \text{ns}$ . Therefore, if we use the following rule-of-thumb that the propagation delay of typical twisted pair bus cable is  $5\ \text{ns/m}$ , we can calculate an approximate cable length trade-off between normal high-speed mode and slope control mode with a  $100\text{-k}\Omega$  resistor. Using typical values, the loop delay for a recessive to dominant bit with RS tied directly to ground is  $70\text{ns}$ , and with a  $100\text{-k}\Omega$  resistor is  $535\ \text{ns}$ . At  $5\text{ns/m}$  of propagation delay, which you have to count in both directions the difference is  $46.5\ \text{meters}$   $(535-70)/(2*5)$ .

Another option to improving the electromagnetic emissions of the device besides slowing down the edge rates of the driver in slope control mode is using quality shielded bus cabling

Figure 40. 70.7-ns Loop Delay Through the HVD230 With  $R_s = 0$

#### 8.2.1.3. Bus Loading, Length and Number of Nodes

The ISO11898 Standard specifies up to 1 Mbps data rate, maximum bus length of 40 meters, maximum drop line (stub) length of 0.3 meters and a maximum of 30 nodes. However, with careful network design, the system may have longer cables, longer stub lengths, and many more nodes. Many CAN organizations and standards have scaled the use of CAN for applications outside the original ISO11898 standard. They have made system level trade-offs for data rate, cable length, and parasitic loading of the bus. Examples of some of these specifications are ARINC825, CANopen, CAN Kingdom, DeviceNet and NMEA200.

A high number of nodes requires a transceiver with high input impedance and wide common mode range such as the XL65HVD23x CAN family. ISO11898-2 specifies the driver differential output with a  $60\ \Omega$  load (two  $120\ \Omega$  termination resistors in parallel) and the differential output must be greater than 1.5 V. The XL65HVD23x devices are specified to meet the 1.5 V requirement with a  $60\ \Omega$  load, and additionally specified with a differential output voltage minimum of 1.2 V across a common mode range of -2 V to 7 V via a  $167\ \Omega$  coupling network. This network represents the bus loading of 120 XL65HVD23x transceivers based on their minimum differential input resistance of  $40\ k\Omega$ . Therefore, the XL65HVD23x supports up to 120 transceivers on a single bus segment with margin to the 1.2 V minimum differential input voltage requirement at each node. For CAN network design, margin must be given for signal loss across the system and cabling, parasitic loadings, network imbalances, ground offsets and signal integrity thus a practical maximum number of nodes may be lower. Bus length may also be extended beyond the original ISO11898 standard of 40 meters by careful system design and data rate tradeoffs. For example, CANopen network design guidelines allow the network to be up to 1 km with changes in the termination resistance, cabling, less than 64 nodes and significantly lowered data rate.

This flexibility in CAN network design is one of the key strengths of the various extensions and additional standards that have been built on the original ISO11898 CAN standard. In using this flexibility comes the responsibility of good network design.

### 8.2.2. Detailed Design Procedure

The following system level considerations should be looked at when designing your application. There are trade offs between the total number of nodes, the length of the bus, and the slope of the driver output that need to be evaluated when building up a system

#### 8.2.2.1. Transient Protection

Typical applications that use CAN will sometime require some form of ESD, burst, or surge protection performance at the system level. If these requirements are higher than those of the device some form of external protection may be needed to shield the transceiver against these high power transients that can cause damage. Transient voltage suppressor (TVS) are very commonly used and can help clamp the amount of energy that reaches the transceiver.

#### 8.2.2.2. Transient Voltage Suppressors

Transient voltage suppressors are the preferred protection components for CAN bus applications due to their low capacitance, fast response times and high peak power dissipation limits. The low bus capacitance allows these devices to be used at many, if not all, nodes on the network without having to reduce the data rate. The quick response times in the order of a few picoseconds enable these devices to clamp the energy of very fast transients like ESD and EFT. Lastly, the high peak power ratings enable these devices to handle high energy surge pulses without being damaged.

### 8.2.3. Application Curve

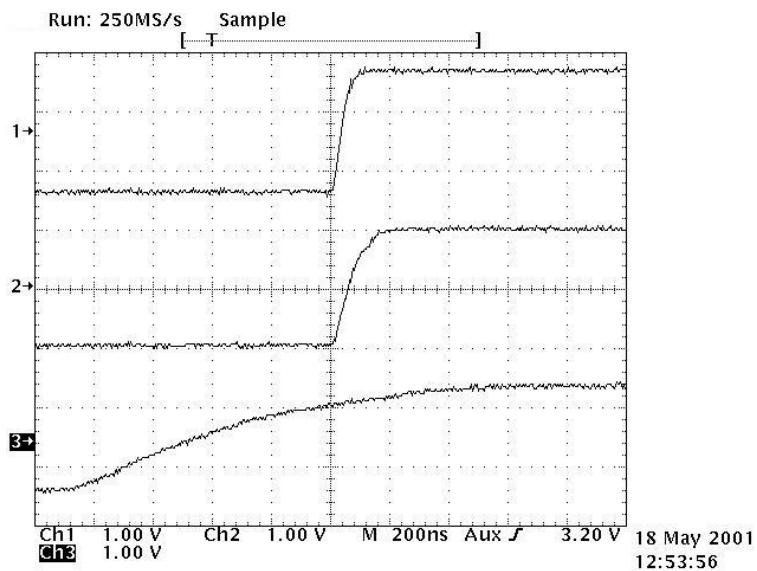

Typical driver output waveforms from a pulse input signal with different slope control resistances are displayed in [Figure 41](#). The top waveform show the typical differential signal when transitioning from a recessive level to a dominant level on the CAN bus with RS tied to GND through a zero ohm resistor. The second waveform shows the same signal for the condition with a 10k ohm resistor tied from RS to ground. The bottom waveform shows the typical differential signal for the case where a 100k ohm resistor is tied from the RS pin to ground.

Figure 41. Typical XL65HVD230 250-kbps Output Pulse Waveforms With Slope Control

### 8.3. System Example

#### 8.3.1. ISO 11898 Compliance of XL65HVD23x Family of 3.3 V CAN Transceivers

##### 8.3.1.1. Introduction

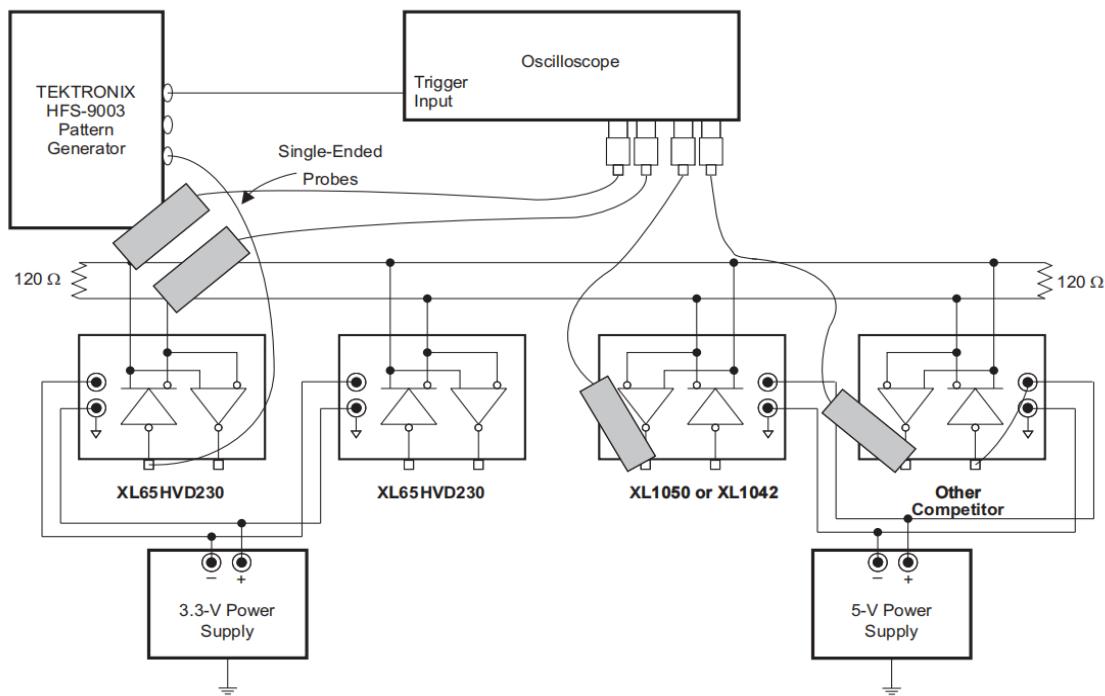

Many users value the low power consumption of operating their CAN transceivers from a 3.3 V supply. However, some are concerned about the interoperability with 5 V supplied transceivers on the same bus. This report analyzes this situation to address those concerns.

##### 8.3.1.2. Differential Signal

CAN is a differential bus where complementary signals are sent over two wires and the voltage difference between the two wires defines the logical state of the bus. The differential CAN receiver monitors this voltage difference and outputs the bus state with a single-ended output signal.

Figure 42. Typical XL65HVD230 Differential Output Voltage Waveform

The CAN driver creates the differential voltage between CANH and CANL in the dominant state. The dominant differential output of the XL65HVD23x is greater than 1.5 V and less than 3 V across a 60 ohm load as defined by the ISO 11898 standard. These are the same limiting values for 5 V supplied CAN transceivers. Typically, the bus termination resistors drive the bus back to the recessive bus state and not the CAN driver. A CAN receiver is required to output a recessive state when less than 500 mV of differential voltage exists on the bus, and a dominant state when more than 900 mV of differential voltage exists on the bus. The CAN receiver must do this with common-mode input voltages from -2 V to 7 volts per the ISO 11898-2 standard. The XL65HVD23x family receivers meet these same input specifications as 5 V supplied receivers.

#### 8.3.1.2.1. Common Mode Signal

A common-mode signal is an average voltage of the two signal wires that the differential receiver rejects. The common-mode signal comes from the CAN driver, ground noise, and coupled bus noise. Since the bias voltage of the recessive state of the device is dependent on VCC, any noise present or variation of VCC will have an effect on this bias voltage seen by the bus. The XL65HVD23x family has the recessive bias voltage set higher than  $0.5 \times VCC$  to comply with the ISO 11898-2 CAN standard which states that the recessive bias voltage must be between 2 V and 3 V. The caveat to this is that the common mode voltage will drop by a couple hundred millivolts when driving a dominant bit on the bus. This means that there is a common mode shift between the dominant bit and recessive bit states of the device. While this is not ideal, this small variation in the driver common-mode output is rejected by differential receivers and does not effect data, signal noise margins or error rates

#### 8.3.1.3. Interoperability of 3.3-V CAN in 5-V CAN Systems

The 3.3 V supplied XL65HVD23x family of CAN transceivers are fully compatible with 5 V CAN transceivers. The differential output voltage is the same, the recessive common mode output bias is the same, and the receivers have the same input specifications. The only difference is in the dominant common mode output voltage is lower in 3.3 V CAN transceivers than with 5 V supplied transceiver (by a few hundred millivolts).

To help ensure the widest interoperability possible, the XL65HVD23x family has successfully passed the internationally recognized GIFT ICT conformance and interoperability testing for CAN transceivers which is shown in . Electrical interoperability does not always assure interchangeability however. Most implementers of CAN buses recognize that ISO 11898 does not sufficiently specify the electrical layer and that strict standard compliance alone does not ensure full interchangeability. This comes only with thorough equipment testing.

Figure 43. 3.3-V and 5-V CAN Transceiver System Testing

## 9. Power Supply Recommendations

The XL65HVD23x 3.3 V CAN transceivers provide the interface between the 3.3 V  $\mu$ Ps, MCUs and DSPs and the differential bus lines, and are designed to transmit data at signaling rates up to 1 Mbps as defined by the ISO 11898 standard.

To ensure reliable operation at all data rates and supply voltages, the VCC supply pin of each CAN transceiver should be decoupled with a 100-nF ceramic capacitor located as close to the VCC and GND pins as possible. The 76333 is a linear voltage regulator suitable for supplying the 3.3-V supply

## 10. LAYOUT

### 10.1. Layout Guidelines

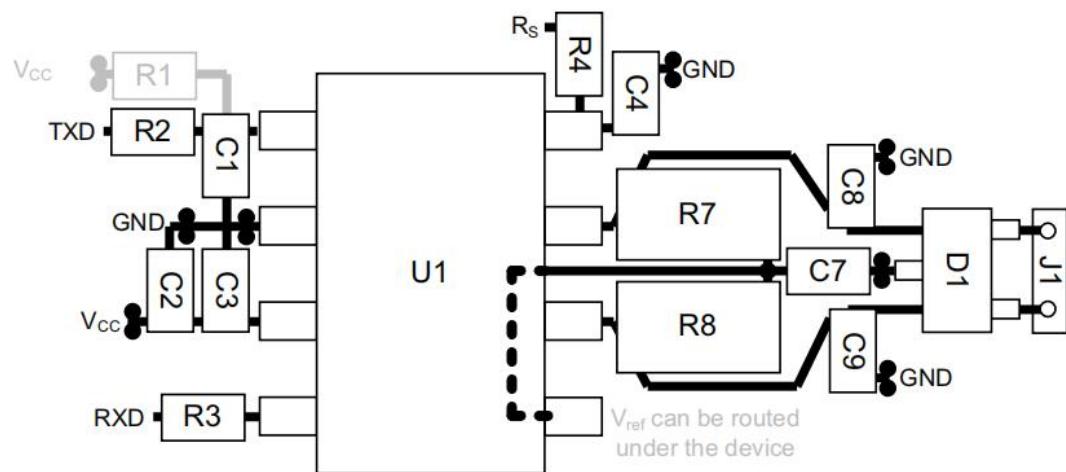

In order for the PCB design to be successful, start with design of the protection and filtering circuitry. Because ESD and EFT transients have a wide frequency bandwidth from approximately 3 MHz to 3 GHz, high frequency layout techniques must be applied during PCB design. On chip IEC ESD protection is good for laboratory and portable equipment but is usually not sufficient for EFT and surge transients occurring in industrial environments. Therefore robust and reliable bus node design requires the use of external transient protection devices at the bus connectors. Placement at the connector also prevents these harsh transient events from propagating further into the PCB and system.

Use Vcc and ground planes to provide low inductance. Note: high frequency current follows the path of least inductance and not the path of least resistance.

Design the bus protection components in the direction of the signal path. Do not force the transient current to divert from the signal path to reach the protection device.

An example placement of the Transient Voltage Suppression (TVS) device indicated as D1 (either bi-directional diode or varistor solution) and bus filter capacitors C8 and C9 are shown in .

The bus transient protection and filtering components should be placed as close to the bus connector, J1, as possible. This prevents transients, ESD and noise from penetrating onto the board and disturbing other devices.

Bus termination: [Figure 44](#) shows split termination. This is where the termination is split into two resistors, R7 and R8, with the center or split tap of the termination connected to ground via capacitor C7. Split termination provides common mode filtering for the bus. When termination is placed on the board instead of directly on the bus, care must be taken to ensure the terminating node is not removed from the bus as this will cause signal integrity issues of the bus is not properly terminated on both ends. See the application section for information on power ratings needed for the termination resistor(s).

Bypass and bulk capacitors should be placed as close as possible to the supply pins of transceiver, examples C2, C3 (Vcc).

Use at least two vias for Vcc and ground connections of bypass capacitors and protection devices to minimize trace and via inductance.

To limit current of digital lines, serial resistors may be used. Examples are R1, R2, R3 and R4.

To filter noise on the digital IO lines, a capacitor may be used close to the input side of the IO as shown by C1 and C4.

Since the internal pull up and pull down biasing of the device is weak for floating pins, an external 1k to 10k ohm pull-up or down resistor should be used to bias the state of the pin more strongly against noise during transient events.

Pin 1: If an open drain host processor is used to drive the D pin of the device an external pull-up resistor between 1k and 10k ohms should be used to drive the recessive input state of the device (R1).

Pin 8: is shown assuming the mode pin, RS, will be used. If the device will only be used in normal mode or slope control mode, R3 is not needed and the pads of C4 could be used for the pull down resistor to GND.

Pin 5 in is shown for the XL65HVD230 and XL65HVD231 devices which have a V<sub>ref</sub> output voltage reference. If used, this pin should be tied to the common mode point of the split termination. If this feature is not used, the pin can be left floating.

## 10.2. Layout Example

Figure 44. XL65HVD23x Board Layout

## 11. ORDERING INFORMATION

Ordering Information

| Part Number  | Device Making | Package type | Body size (mm) | Temperate (°C) | MSL  | Transport Media | Package Quantit |

|--------------|---------------|--------------|----------------|----------------|------|-----------------|-----------------|

| XL65HVD230DR | 65HVD230      | SOP-8        | 4.90*3.90      | -40 to +85     | MSL3 | T&R             | 2500            |

| XL65HVD231DR | 65HVD231      | SOP-8        | 4.90*3.90      | -40 to +85     | MSL3 | T&R             | 2500            |

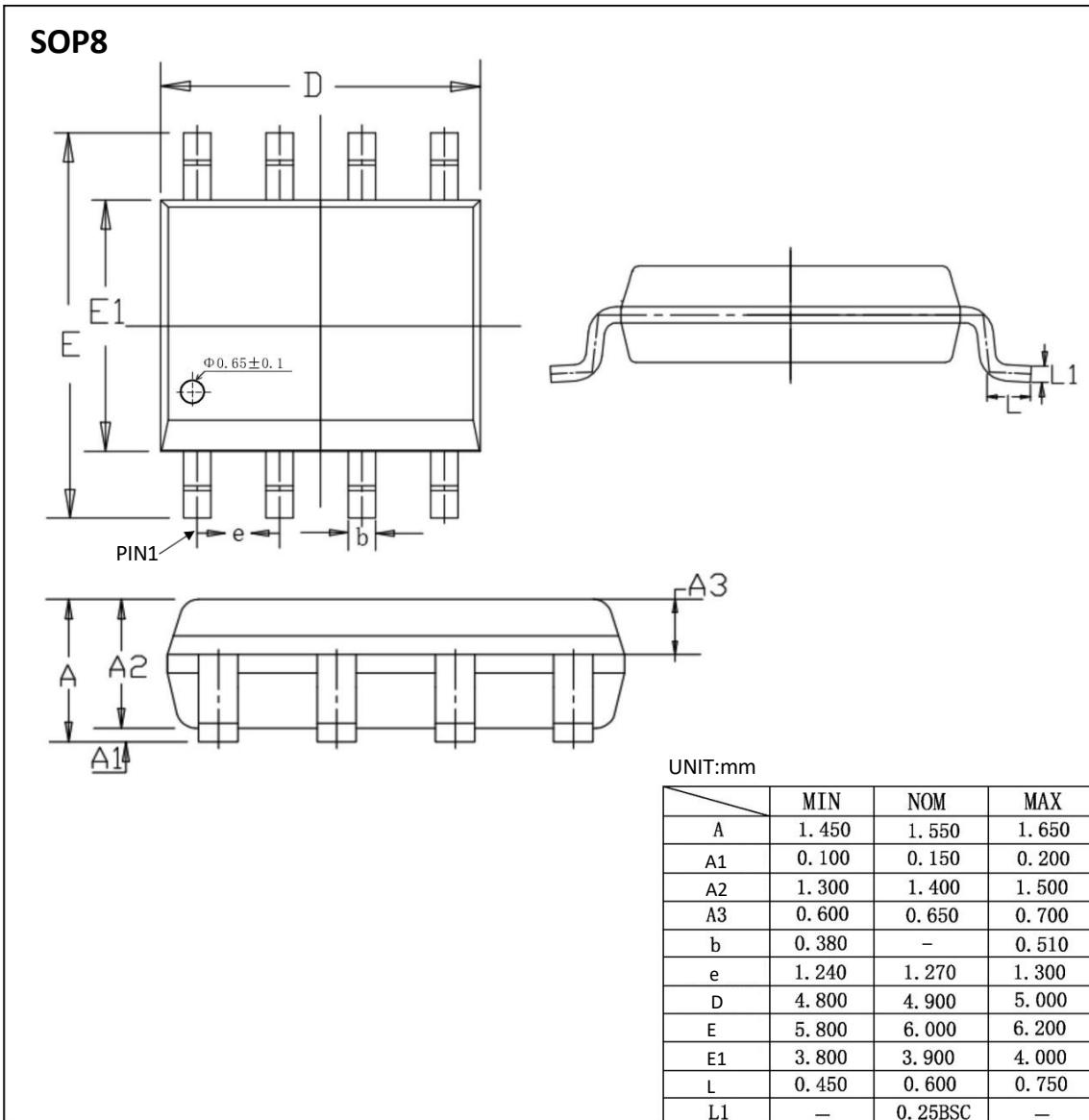

## 12. DIMENSIONAL DRAWINGS