# MP9931 100V Input, Synchronous Step-Down Controller

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## DESCRIPTION

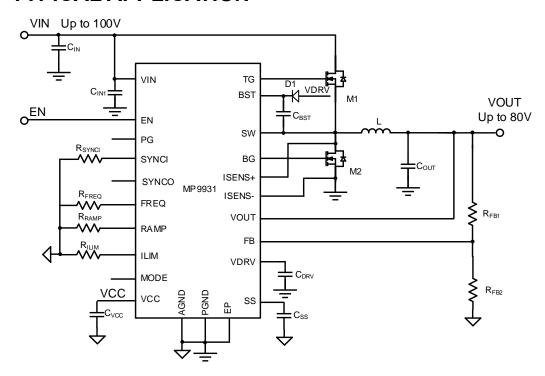

The MP9931 is a high-voltage, synchronous step-down switching regulator controller that can directly step-down voltages from up to 100V. It has capable of driving dual N-channel MOSFET switches.

The MP9931 Adaptive Constant-On-Time (COT) control architecture provides fast transient response and eases loop stabilization. The DC auto tune loop provides good load and line regulation.

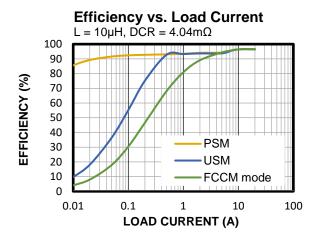

PSM Mode and USM Mode enables nonsynchronous operation to optimize light load efficiency.

The operating frequency of MP9931 can be programmed by an external resistor or synchronized to an external clock for noise-sensitive applications.

Fault protections are available including a precision input over voltage protection (OVP), output over current protection (OCP), and thermal shutdown.

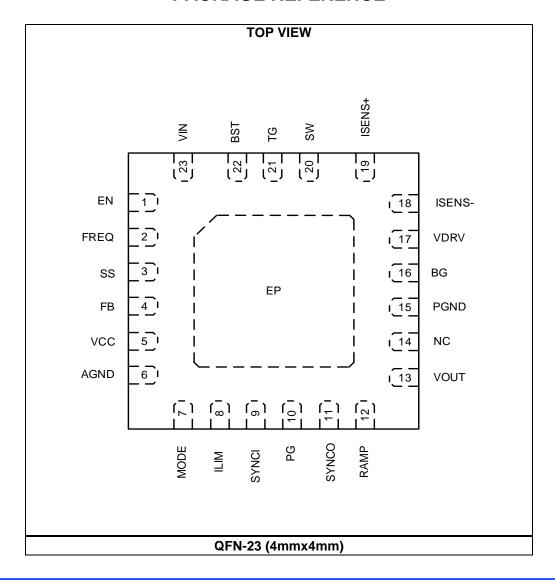

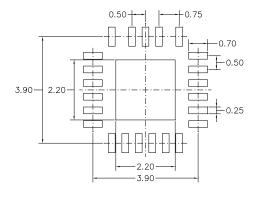

The MP9931 is available in a QFN-23(4.0mmx4.0mm) package.

## **FEATURES**

## **Basic Function**

- Lossless R<sub>DS (on)</sub> or shunt current sense

- COT Control offers Fast Load Transient Response

- 7V-to-100V Input Voltage Range

- Output adjusts from 0.8V to 80V

- 450µA Quiescent Current

- 4µA EN Shutdown Current

- 60ns Min-on-time

- Low Dropout Operation: max duty up to 99%

- USM/PSM/FCCM Selectable by Mode Pin

- Selectable Frequency by FREQ Resistor: 100kHz -1000kHz

- Power Good Indicator

- Ramp selectable by RAMP pin

- Selectable current limit by ILIM Resistor

- V<sub>DRV</sub> Power from V<sub>OUT</sub> when V<sub>OUT</sub>>8.4V

- External V<sub>DRV</sub>: bias V<sub>DRV</sub> with external voltage source which is higher than internal V<sub>DRV</sub>

#### **Drive Ability**

10V N-Channel MOS Gate Driver with 4.2A Source and 5.2A Sink Capability

#### SYNCI/SYNCO

- SYNCI with external clock

- 180° Out-of-Phase SYNCO

#### **APPLICATIONS**

- Energy Storage System

- USB PD Charger

- POE System Power Supply

- Industrial Power Supplies

- E-bike Auxiliary Power Supplies

- General-Purpose Power Supplies

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

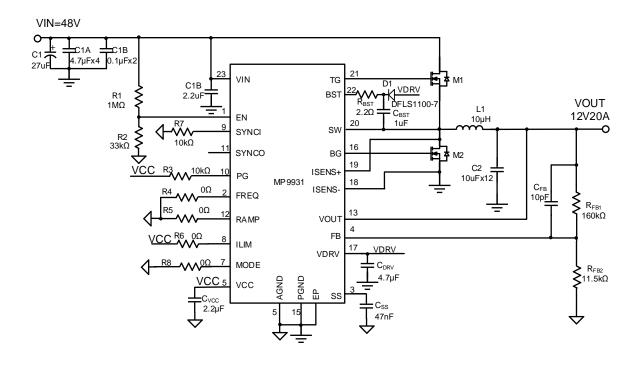

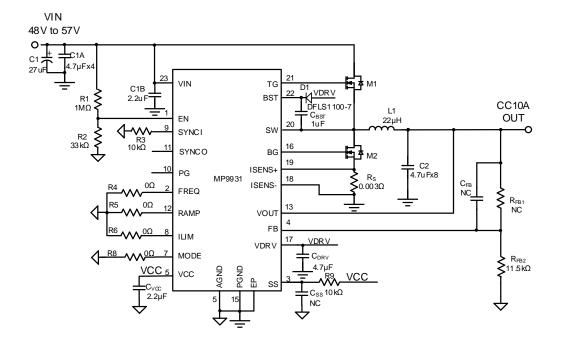

# **TYPICAL APPLICATION**

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

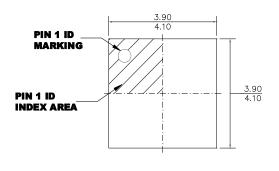

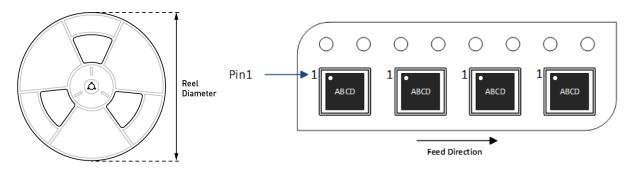

## ORDERING INFORMATION

| Part Number* | Package          | Top Marking | MSL Rating |

|--------------|------------------|-------------|------------|

| MP9931GR     | QFN-23 (4mmx4mm) | See Below   | 1          |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP9931GR-Z)

## **TOP MARKING**

**MPSYWW** MP9931 LLLLLL

MPS: MPS prefix Y: Year code WW: Week code MP9931: Part number LLLLL: Lot number

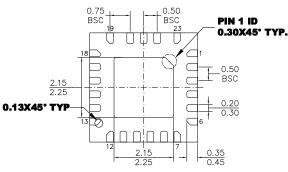

## PACKAGE REFERENCE

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# **PIN FUNCTIONS**

| Pin# | Name  | Description                                                                                                                                                                                                                                                                                                        | n                                                                                                                                                                                                                                                                         |                              |             |                  |            |         |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------|------------------|------------|---------|

| 1    | EN    | <b>Enable control pin.</b> When EN is pull low, the controller is in the shutdown mode with all functions disabled. When EN voltage is pull high to above 1.2 V, the SS voltage can ramp up and pulse-width modulated gate-drive signals are delivered to the TG and BG pins.                                      |                                                                                                                                                                                                                                                                           |                              |             |                  |            |         |

|      |       | switching f                                                                                                                                                                                                                                                                                                        | <b>Switching frequency select.</b> Connect a resistor between FREQ and AGND to set the switching frequency. It cannot be adjusted on-line, suggest Vin/EN off then on again after FREQ pin setup is changed. 1% tolerance resistor is recommended for it's good accuracy. |                              |             |                  |            |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | FREQ pin                                                                                                                                                                                                                                                                  |                              | Switch      | Frequency        | ]          |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | GND                                                                                                                                                                                                                                                                       |                              | 100kHz      |                  |            |         |

| 2    | FREQ  |                                                                                                                                                                                                                                                                                                                    | 20kΩ to GNI                                                                                                                                                                                                                                                               | )                            | 150kHz      |                  |            |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | 45.3kΩ to G                                                                                                                                                                                                                                                               | ND                           | 200kHz      |                  |            |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | 80.6kΩ to G                                                                                                                                                                                                                                                               |                              | 250kHz      |                  | ]          |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | 124kΩ to GN                                                                                                                                                                                                                                                               |                              | 300kHz      |                  | ]          |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | 180kΩ to GN                                                                                                                                                                                                                                                               |                              | 400kHz      |                  | ]          |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | 243kΩ to GN                                                                                                                                                                                                                                                               | 1D                           | 600kHz      |                  | ]          |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | VCC                                                                                                                                                                                                                                                                       |                              | 1MHz        |                  | ]          |         |

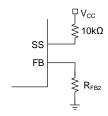

| 3    | SS    |                                                                                                                                                                                                                                                                                                                    | control input.<br>apacitor between                                                                                                                                                                                                                                        | This pin is usen SS to AGND. | ed to pro   | gram the soft-st | art period | with an |

| 4    | FB    | sets the ou                                                                                                                                                                                                                                                                                                        | Output feedback. An external resistor divider from the output to AGND tapped to FB sets the output voltage. It is recommended to place the resistor divider as close to FB as possible. Vias should be avoided on the FB traces.                                          |                              |             |                  |            |         |

| 5    | VCC   | Internal 5V LDO output. The most control circuits are powered from the VCC voltage. Decouple VCC with a ceramic capacitor at least 1µF placed as close to it as possible. 2.2uF X7R or X5R grade dielectric ceramic capacitors are recommended for their stable temperature characteristics.                       |                                                                                                                                                                                                                                                                           |                              |             |                  |            |         |

| 6    | AGND  | Analog gr                                                                                                                                                                                                                                                                                                          | ound. Select A                                                                                                                                                                                                                                                            | GND as the cont              | rol circuit | reference point. |            |         |

| 7    | MODE  | Analog ground. Select AGND as the control circuit reference point.  Operation mode selection. Pull MODE to VCC to operate in forced CCM mode. Float MODE to operate in PSM mode with ultrasonic mode (USM) at light load. Connect MODE to ground to operate in PSM mode without USM. Mode can be adjusted on-line. |                                                                                                                                                                                                                                                                           |                              |             |                  |            |         |

|      |       | Current limit adjust. Connect a resistor between ILIM and GND to set the valley current limit. Current limit can be adjusted on-line.                                                                                                                                                                              |                                                                                                                                                                                                                                                                           |                              |             |                  |            |         |

|      |       | IL                                                                                                                                                                                                                                                                                                                 | .IM pin                                                                                                                                                                                                                                                                   | Valley Current               | t Limit     | Negative Curr    | ent limit  |         |

| 8    | ILIM  |                                                                                                                                                                                                                                                                                                                    | ND                                                                                                                                                                                                                                                                        | 25mV                         |             | 25mV             |            |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | 1kΩ to GND                                                                                                                                                                                                                                                                | 50mV                         |             | 25mV             |            |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | 20kΩ to GND                                                                                                                                                                                                                                                               | 75mV                         |             | 50mV             |            |         |

|      |       |                                                                                                                                                                                                                                                                                                                    | CC                                                                                                                                                                                                                                                                        | 100mV                        |             | 50mV             |            |         |

| 9    | SYNCI | Sync signal input. If an external sync clock is applied to this pin, internal clock will follow the sync frequency.                                                                                                                                                                                                |                                                                                                                                                                                                                                                                           |                              |             |                  |            |         |

| 10   | PG    |                                                                                                                                                                                                                                                                                                                    | Power good output. The output of this pin is open drain.                                                                                                                                                                                                                  |                              |             |                  |            |         |

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# PIN FUNCTIONS (continued)

| Pin# | Name   | Description                                                                                                                                                                                                                                                                                                                                                       |                        |                      |  |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|--|

| 11   | SYNCO  | Sync signal output. Outputs a clock which are 180° out-of-phase with internal Oscillator Clock or external Synchronize Clock when part works in CCM mode, DCM or USM. SYNCO outputs 0V in other cases (Sleep mode, Fault protections, etc.).                                                                                                                      |                        |                      |  |

| 12   | RAMP   | Internal ramp selection. Connect a resistor internal ramp. A large ramp will make the chip was bring better load transient response performance                                                                                                                                                                                                                   | vork more stable, whil | le a small ramp will |  |

| 13   | VOUT   | VOUT sense and bias supply. VOUT will supply this pin. It will disable the power from VIN as lo pin must be connected to output for internal tor                                                                                                                                                                                                                  | ng as VOUT is highe    |                      |  |

| 14   | NC     | Not connected. NC pin need to be floating.                                                                                                                                                                                                                                                                                                                        |                        |                      |  |

| 15   | PGND   | <b>System ground.</b> Power ground reference for the internal low side switch driver and the VDRV regulator circuit. Connect this pin directly to the negative terminal of the VDRV decoupling capacitor.                                                                                                                                                         |                        |                      |  |

| 16   | BG     | <b>Bottom gate driver.</b> Connect this pin to the gate of the synchronous N-channel MOSFET.                                                                                                                                                                                                                                                                      |                        |                      |  |

| 17   | VDRV   | <b>Decoupling Input Pin for Driver Power supply</b> . Decouple with a minimum 4.7μF ceramic capacitor as close to the pin as possible. X7R or X5R grade dielectric ceramic capacitors are recommended.                                                                                                                                                            |                        |                      |  |

| 18   | ISENS- | <b>Negative input for the current sense.</b> ISENS+ and ISENS- should be layout with differential pair lines.                                                                                                                                                                                                                                                     |                        |                      |  |

| 19   | ISENS+ | <b>Positive input for the current sense.</b> ISENS+ can be connected to either the drain of the low-side MOSFET for lossless R <sub>DS</sub> (on) sensing or a current sense resistor connected to the source of the low-side MOSFET for accurate current limit and ZCD(zero current detection). ISENS+ and ISENS- should be layout with differential pair lines. |                        |                      |  |

| 20   | SW     | <b>Switch node.</b> Reference for the V <sub>BST</sub> supply and high current returns for bootstrapped switch.                                                                                                                                                                                                                                                   |                        |                      |  |

| 21   | TG     | <b>Top gate drive.</b> The TG pin drives the gate of the top N-channel MOSFET. The TG driver draws power from the BST capacitor and returns to SW pin, providing a true floating drive to the top N-channel MOSFET.                                                                                                                                               |                        |                      |  |

| 22   | BST    | <b>Bootstrap.</b> This pin is the positive power supply for the internal floating high side MOSFET driver. Connect a bypass capacitor between this pin and SW pin.                                                                                                                                                                                                |                        |                      |  |

| 23   | VIN    | <b>Input voltage.</b> Operates from a 7V to 100V input. Ceramic capacitor is needed to prevent large voltage spikes from appearing at the input.                                                                                                                                                                                                                  |                        |                      |  |

| EP   | -      | Exposed Pad. Connect it to ground.                                                                                                                                                                                                                                                                                                                                |                        |                      |  |

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

| ABSOLUTE MAXIMUM RATINGS (1) Input supply voltage (V <sub>IN</sub> )0.3V to 110V                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW0.3V (-5V for <20ns) to 110V ISENS+0.3V (-5V for <20ns) to 110V BST - SW0.3V to 14V $V_{DRV}$ 0.3V to 14V $V_{OUT}$ 0.3V (-5V for <10 $\mu$ s) to 85V TG - SW0.3V to $V_{BST}$ + 0.3V BG0.3V to +6.5V(<100 $\mu$ A when >6V) All other pins0.3V to +6.5V |

| Continuous power dissipation (TA = $+25^{\circ}$ C) (2) QFN-23 (4.0mmx4.0mm)                                                                                                                                                                               |

| <b>ESD Ratings</b> Human body model (HBM) ±2000V                                                                                                                                                                                                           |

| Charged device model (CDM) ±750V                                                                                                                                                                                                                           |

| Recommended Operating Conditions (3)                                                                                                                                                                                                                       |

| Input voltage VIN                                                                                                                                                                                                                                          |

Thermal Resistance  $\theta_{JA}$   $\theta_{JC}$  QFN-23(4.0mmx4.0mm)

JESD51-7 (4) ...... TBD ... TBD °C/W

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) The value of θ<sub>JA</sub> given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

6

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# **ELECTRICAL CHARACTERISTICS**

VIN= 48V, EN = 2V,  $T_J$  = -40°C to 125°C  $^{(5)}$ , typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameters                                                  | Symbol                   | Condition                                            | Min   | Тур   | Max   | Units            |

|-------------------------------------------------------------|--------------------------|------------------------------------------------------|-------|-------|-------|------------------|

| VDRV Regulator                                              |                          |                                                      |       |       |       |                  |

| VDRV UVLO rising threshold                                  | V <sub>DRV_UV_R</sub>    |                                                      |       | 6.5   |       | V                |

| VDRV UVLO hysteresis                                        | V <sub>DRV_UV_</sub>     |                                                      |       | 600   |       | mV               |

| VDRV Voltage                                                | $V_{DRV}$                | $I_{DRV} = 0mA$                                      |       | 10    |       | V                |

| VDRV Regulation                                             |                          | I <sub>DRV</sub> = 20mA                              |       | 2     |       | %                |

| VOUT rising threshold, override $V_{\text{IN}}$ supply VDRV | VO_VDRV_R                |                                                      |       | 8.4   |       | V                |

| VOUT falling threshold, V <sub>IN</sub> supply VDRV         | Vo_V <sub>DRV_F</sub>    |                                                      |       | 7.4   |       | V                |

| VCC Regulator                                               |                          |                                                      |       |       |       |                  |

| VCC Voltage                                                 | VCC                      | Icc=0mA                                              |       | 5     |       | V                |

| VCC Regulation                                              |                          | I <sub>CC</sub> =20mA                                |       | 2     |       | %                |

| Supply Current                                              |                          |                                                      |       |       |       |                  |

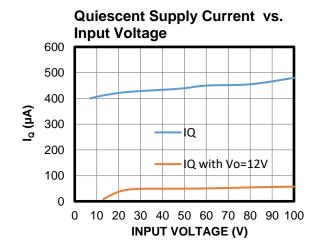

|                                                             |                          | V <sub>FB</sub> =0.88V, V <sub>OUT</sub> =0V, PSM    |       | 450   |       | μA               |

| VIN quiescent current                                       | lα                       | V <sub>FB</sub> =0.88V,V <sub>OUT</sub> =12V,<br>PSM |       | 50    |       | μA               |

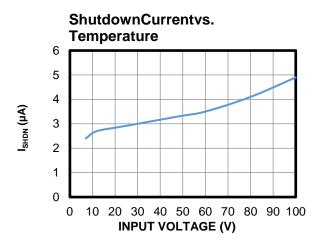

| VIN shutdown current                                        | I <sub>SHDN</sub>        | V <sub>EN</sub> = 0V                                 |       | 4     |       | μA               |

| VIN OVP                                                     |                          |                                                      |       |       |       |                  |

| VIN over voltage rising threshold                           | V <sub>IN_OV_R</sub>     |                                                      |       | 105   |       | V                |

| VIN over voltage hysteresis                                 | VIN_OV_HYS               |                                                      |       | 2     |       | V                |

| Enable Control                                              |                          |                                                      |       |       |       |                  |

| EN UVLO rising threshold                                    | V <sub>EN_UVLO_R</sub>   |                                                      |       | 1.2   |       | V                |

| EN UVLO hysteresis                                          | V <sub>EN_UVLO_HYS</sub> |                                                      |       | 200   |       | mV               |

| EN input current                                            | I <sub>EN</sub>          | V <sub>EN</sub> =2V                                  |       | 0     | 1     | μΑ               |

| Feedback (FB)                                               |                          |                                                      |       | •     | •     | •                |

| ED Defenses Velters                                         | 1/                       | T <sub>J</sub> =25°C                                 | 0.792 | 0.800 | 0.808 | V                |

| FB Reference Voltage                                        | V <sub>REF</sub>         | T <sub>J</sub> =-40°C to 125°C                       | 0.788 | 0.800 | 0.812 | V                |

| Feedback current                                            | I <sub>FB</sub>          | V <sub>FB</sub> = 1.05V                              |       | -50   |       | nA               |

| FB under voltage threshold                                  | V <sub>FB_UV</sub>       |                                                      |       | 30%   |       | V <sub>REF</sub> |

| FB under voltage hysteresis                                 | V <sub>FB_UV_HYS</sub>   |                                                      |       | 20%   |       | $V_{REF}$        |

| FB over voltage threshold                                   | V <sub>FB_OV</sub>       |                                                      |       | 108%  |       | V <sub>REF</sub> |

| FB over voltage recover hysteresis                          | V <sub>FB_OV_HYS</sub>   |                                                      |       | 3%    |       | $V_{REF}$        |

| Soft start                                                  |                          |                                                      |       |       |       |                  |

| SS capacitor charging current                               | Iss                      | Vss=0V                                               |       | 4     |       | μΑ               |

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# **ELECTRICAL CHARACTERISTICS** (continued)

VIN= 48V, EN = 2V,  $T_J$  = -40°C to 125°C <sup>(5)</sup>, typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameters                                                 | Symbol                | Condition                                                                      | Min  | Тур  | Max   | Units      |

|------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------|------|------|-------|------------|

| Switching Frequency                                        | -                     |                                                                                |      |      |       |            |

|                                                            |                       | Connect FREQ to GND                                                            |      | 100  |       | kHz        |

|                                                            |                       | $R_{FREQ}=20k\Omega$                                                           |      | 150  |       | kHz        |

| Cuitabina Francisco                                        |                       | $R_{FREQ}=45.3k\Omega$                                                         |      | 200  |       | kHz        |

| Switching Frequency                                        | fsw                   | $R_{FREQ}=80.6k\Omega$                                                         |      | 250  |       | kHz        |

|                                                            | ISW                   | R <sub>FREQ</sub> =124kΩ                                                       |      | 300  |       | kHz        |

|                                                            |                       | $R_{FREQ}=180k\Omega$                                                          |      | 400  |       | kHz        |

|                                                            |                       | $R_{FREQ}=243k\Omega$                                                          |      | 600  |       | kHz        |

|                                                            |                       | Connect FREQ to VCC                                                            |      | 1000 |       | kHz        |

| Min TG on time                                             | ttg_min_on            |                                                                                |      | 60   |       | ns         |

| Min BG on time                                             | tbg_min_on            |                                                                                |      | 200  |       | ns         |

| Max TG on time                                             | ttg_max_on            | Vin-Vout<3V                                                                    |      | 20   |       | μs         |

|                                                            |                       | 3V <vin-vout<6v< td=""><td></td><td>10</td><td></td><td>μs</td></vin-vout<6v<> |      | 10   |       | μs         |

| Max Duty Cycle                                             | D <sub>MAX</sub>      |                                                                                |      | 99.0 |       | %          |

| Minimum switching frequency in USM                         | f <sub>SW_USM</sub>   | USM                                                                            | 20   |      |       | kHz        |

| Dead Time                                                  |                       |                                                                                |      |      |       |            |

| Dead time from TG falling to BG rising                     | t <sub>DT_BG_R</sub>  | trigger point 5V to 5V                                                         |      | 35   |       | ns         |

| Dead time from BG falling to TG rising                     | t <sub>DT BG_F</sub>  | trigger point 5V to 5V                                                         |      | 35   |       | ns         |

| SYNCHRONICATION INPUT AND OU                               | TPUT                  |                                                                                |      |      |       |            |

| SYNCI external clock frequency                             | ,                     |                                                                                | 000/ |      | 4000/ | <b>-</b> - |

| range                                                      | fsynci                |                                                                                | 80%  |      | 120%  | Fsw        |

| SYNCI voltage rising threshold                             | V <sub>SYNC_R</sub>   |                                                                                | 2    |      |       | V          |

| SYNCI voltage falling threshold                            | V <sub>SYNC_F</sub>   |                                                                                |      |      | 0.8   | V          |

| Minimum SYNCI pulse-width (6)                              | tsync_min             |                                                                                | 50   |      |       | ns         |

| SYNCO output HIGH logic                                    | V <sub>SYNCO_H</sub>  | ISYNCO = -1mA source                                                           | 4.7  |      |       | V          |

| SYNCO output LOW logic                                     | V <sub>SYNCO_L</sub>  | ISYNCO = 1mA sink                                                              |      |      | 0.3   | >          |

| SYNCO pulse duty cycle                                     | D <sub>SYNCO</sub>    |                                                                                |      | 50%  |       |            |

| Phase from PLL clock rising to SYNCO rising <sup>(6)</sup> | P <sub>DLY</sub>      | 50% to 50%                                                                     |      | 180° |       |            |

| BST Power                                                  |                       |                                                                                |      | •    |       |            |

| BST Forward Voltage                                        | V <sub>DROP_BST</sub> | VDRV to BST, BST pin sourcing 20mA                                             |      | 0    | 1     | V          |

| BST to SW quiescent current, not switching                 | I <sub>BST_LKG</sub>  | No switching, Vsw=48V, Vbst=58V                                                |      | 27   |       | μΑ         |

| Mode Selection                                             |                       |                                                                                |      |      |       |            |

| PSM mode with USM                                          | V_usm                 |                                                                                |      |      | 0.4   | V          |

| PSM mode without USM                                       | V_ <sub>PSM</sub>     |                                                                                | 1    |      | 1.6   | ٧          |

| FCCM mode                                                  | V_FCCM                |                                                                                | 2.5  |      |       | ٧          |

| Power Good (PG)                                            |                       |                                                                                |      |      |       |            |

| Power Good rising threshold                                | PG <sub>TH_R</sub>    | FB rising                                                                      |      | 95%  |       | $V_{REF}$  |

| Tower Good Hally theatlold                                 | F G IH_R              | FB falling                                                                     |      | 105% |       | $V_{REF}$  |

| Power Good falling threshold                               | PG <sub>TH_F</sub>    | FB falling                                                                     |      | 90%  |       | $V_{REF}$  |

| rower Good failing threshold                               | FGIH_F                | FB rising                                                                      |      | 108% |       | $V_{REF}$  |

8

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# **ELECTRICAL CHARACTERISTICS** (continued)

VIN= 48V, EN = 2V,  $T_J$  = -40°C to 125°C<sup>(5)</sup>, typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameters                          | Symbol                 | Condition                                                                                        | Min | Тур  | Max | Units |

|-------------------------------------|------------------------|--------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Dawar Cood dalay                    | 4                      | Low to high                                                                                      |     | 300  |     | μs    |

| Power Good delay                    | t <sub>PG_DLY</sub>    | High to low                                                                                      |     | 150  |     | μs    |

| Power Good sink current capability  | $V_{PG}$               | IC enabled, Sink 4mA                                                                             |     |      | 0.4 | V     |

| Power Good leakage current          | I <sub>PG_LKG</sub>    | PG High state, VPG=5V                                                                            |     | 1.5  |     | μA    |

| Gate Drivers                        |                        |                                                                                                  |     |      |     |       |

| TG pull-up resistor (7)             | R <sub>TG_UP</sub>     | V <sub>BST</sub> -V <sub>SW</sub> =10V, TG high state, I <sub>TG</sub> =-100mA                   |     | 1.2  |     | Ω     |

| TG pull-down resistor (7)           | R <sub>TG_DN</sub>     | V <sub>BST</sub> -V <sub>SW</sub> =10V, TG low state, I <sub>TG</sub> =100mA                     |     | 0.7  |     | Ω     |

| BG pull-up resistor (7)             | R <sub>BG_UP</sub>     | V <sub>DRV</sub> =10V, BG high state, I <sub>BG</sub> =-100mA                                    |     | 1.2  |     | Ω     |

| BG pull-down resistor (7)           | R <sub>BG_DN</sub>     | $V_{DRV}$ =10V, BG low state, $I_{BG}$ =100mA                                                    |     | 0.7  |     | Ω     |

| TG, BG source current (7)           | Іон                    | V <sub>BST</sub> -V <sub>SW</sub> =10V, V <sub>DRV</sub> =10V, TG=SW, BG=PGND<br>Not test in ATE |     | 4.2  |     | А     |

| TG, BG sink current (7)             | loL                    | V <sub>BST</sub> -V <sub>SW</sub> =10V, V <sub>DRV</sub> =10V, TG=BST, BG=VDRV                   |     | 5.2  |     | А     |

| Over Current Protection             |                        |                                                                                                  |     |      |     |       |

|                                     | Vval_limit             | ILIM connect to GND                                                                              |     | 25   |     | mV    |

| Valley augreent limit valtage       |                        | $R_{ILIM} = 51k\Omega$                                                                           |     | 50   |     | mV    |

| Valley current limit voltage        |                        | $R_{ILIM} = 120k\Omega$                                                                          |     | 75   |     | mV    |

|                                     |                        | ILIM connect to VCC                                                                              |     | 100  |     | mV    |

| Negative Current Limit              |                        |                                                                                                  |     |      |     |       |

|                                     |                        | ILIM connect to GND                                                                              |     | 25   |     | mV    |

| Nicolation of Park State            | .,                     | $R_{ILIM} = 51k\Omega$                                                                           |     | 25   |     | mV    |

| Negative current limit voltage      | V <sub>NCL_LIMIT</sub> | $R_{ILIM} = 120k\Omega$                                                                          |     | 50   |     | mV    |

|                                     |                        | ILIM connect to VCC                                                                              |     | 50   |     | mV    |

| ZCD                                 |                        |                                                                                                  |     |      |     |       |

| ZCD detect voltage                  | V <sub>ZCD</sub>       |                                                                                                  |     | 1    |     | mV    |

| Current temperature coefficient     |                        |                                                                                                  |     |      |     |       |

| Current temperature coefficient (7) | тс                     | R <sub>DS_ON</sub> mode                                                                          |     | 4500 |     | ppm/℃ |

| Current temperature coefficient (7) | 10                     | R <sub>SENSE</sub> mode                                                                          |     | 0    |     | ppm/℃ |

| Thermal Protection                  |                        |                                                                                                  |     |      |     |       |

| Thermal shutdown (7)                | T <sub>SD</sub>        |                                                                                                  |     | 150  |     | °C    |

| Thermal shutdown hysteresis (7)     | T <sub>SD_HYS</sub>    |                                                                                                  |     | 20   |     | °C    |

#### Note:

- 5) Not tested in production. Guaranteed by over-temperature correlation.

- 6) Not tested in production. Derived by design.

- 7) Not tested in production. Derived by sample characterization.

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

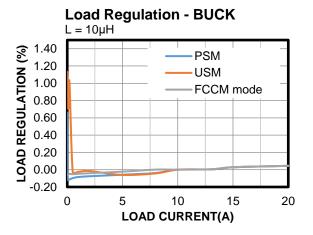

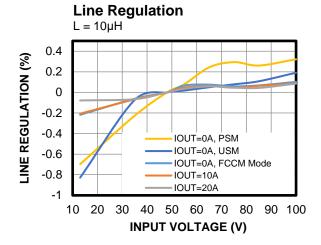

## TYPICAL CHARACTERISTICS

$V_{IN} = 48V$ ,  $V_{OUT} = 12V$ , Freq = 100kHz, L=10 $\mu$ H, EN=2V, PSM,  $T_A = +25$ °C, unless otherwise noted.

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## TYPICAL PERFORMANCE CHARACTERISTICS

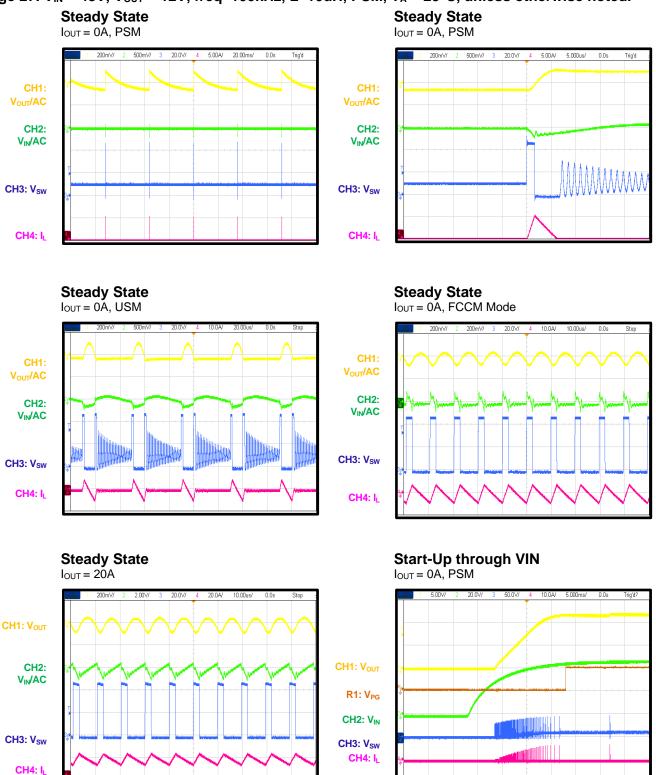

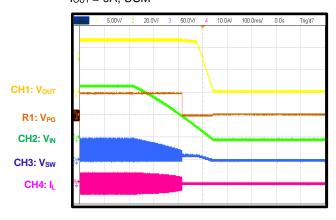

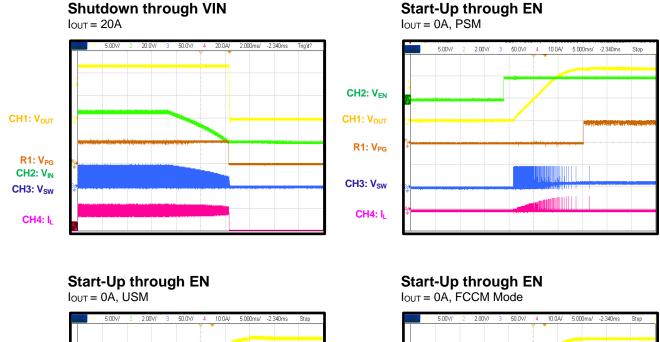

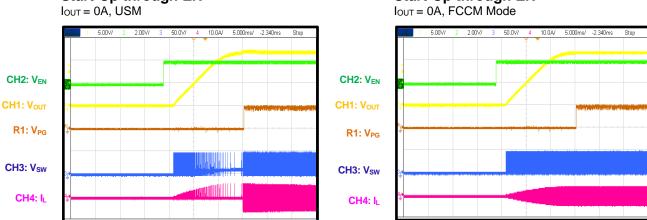

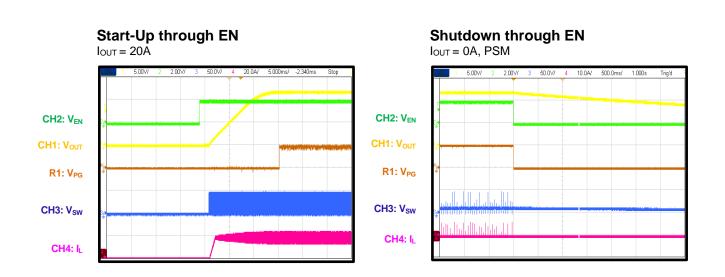

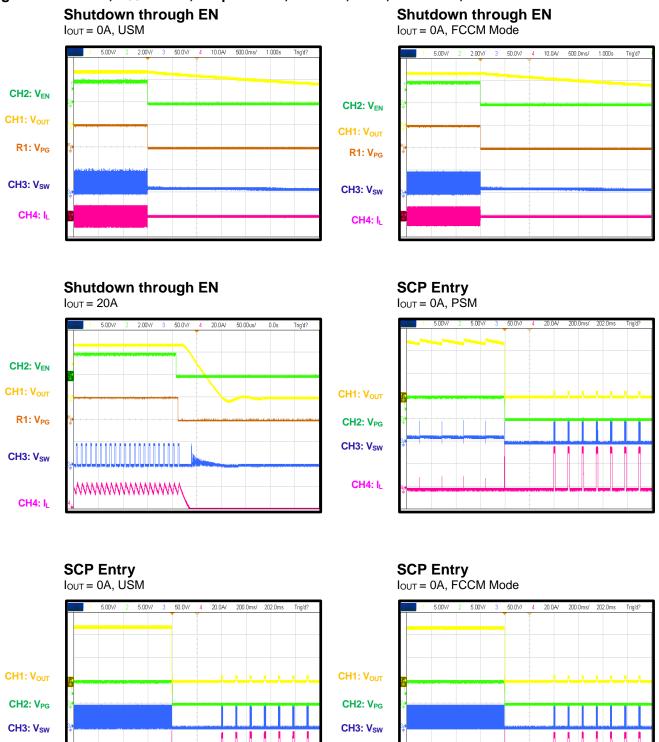

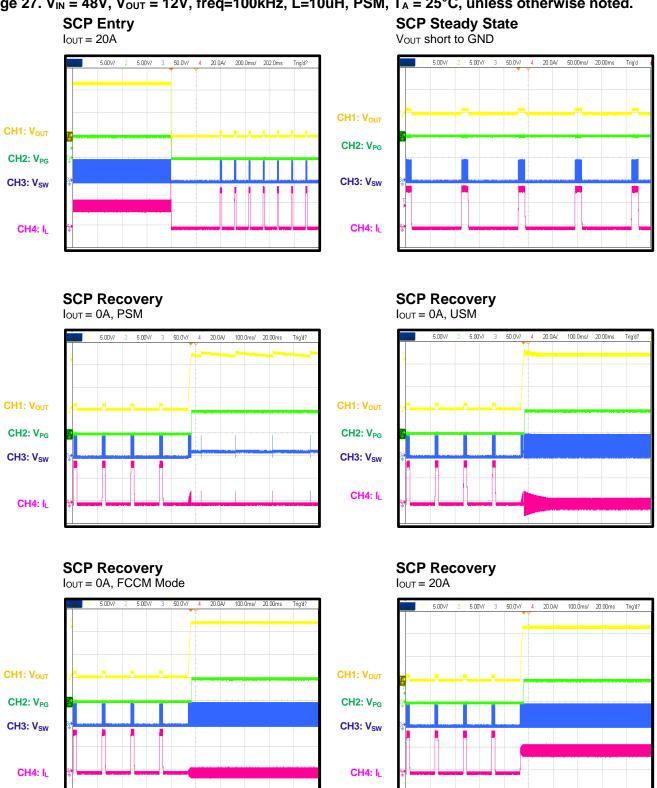

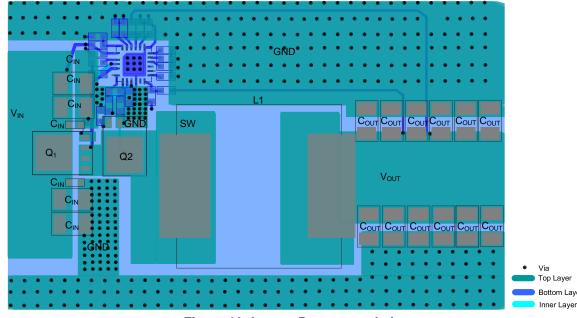

Performance waveforms are tested on the evaluation board in the Design Example section on page 27.  $V_{IN} = 48V$ ,  $V_{OUT} = 12V$ , freq=100kHz, L=10uH, PSM,  $T_A = 25^{\circ}$ C, unless otherwise noted.

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

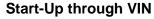

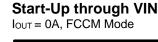

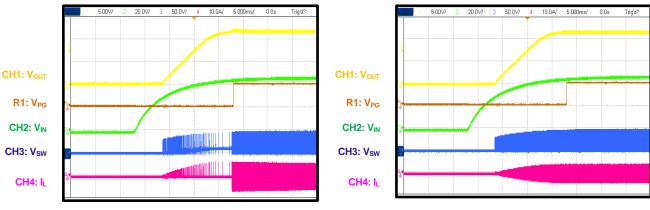

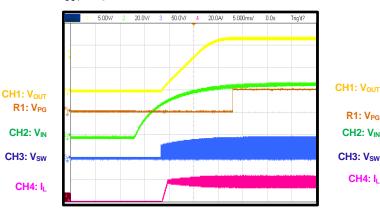

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board in the Design Example section on page 27.  $V_{IN} = 48V$ ,  $V_{OUT} = 12V$ , freq=100kHz, L=10uH, PSM,  $T_A = 25$ °C, unless otherwise noted.

I<sub>OUT</sub> = 0A, USM

# Start-Up through VIN

$I_{OUT} = 20A$

## Shutdown through VIN

I<sub>OUT</sub> = 0A, PSM

## Shutdown through VIN

I<sub>OUT</sub> = 0A, USM

#### Shutdown through VIN

Iout = 0A, FCCM Mode

CH1: Vout

R1: V<sub>PG</sub> CH2: V<sub>IN</sub>

CH3: V<sub>SW</sub>

CH4: IL

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board in the Design Example section on page 27.  $V_{IN} = 48V$ ,  $V_{OUT} = 12V$ , freq=100kHz, L=10uH, PSM,  $T_A = 25^{\circ}$ C, unless otherwise noted.

CH4: IL

#### MP9931—7V to 100V SYNCHRONOUS STEP-DOWN CONTROLLER

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board in the Design Example section on page 27.  $V_{IN} = 48V$ ,  $V_{OUT} = 12V$ , freq=100kHz, L=10uH, PSM,  $T_A = 25^{\circ}$ C, unless otherwise noted.

CH4: IL

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board in the Design Example section on page 27.  $V_{IN} = 48V$ ,  $V_{OUT} = 12V$ , freq=100kHz, L=10uH, PSM,  $T_A = 25^{\circ}$ C, unless otherwise noted.

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

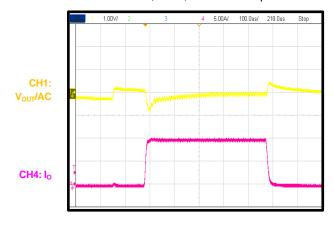

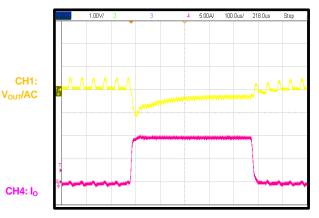

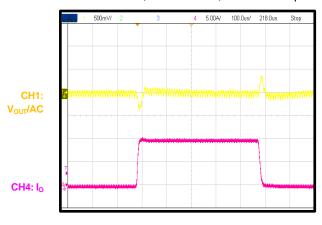

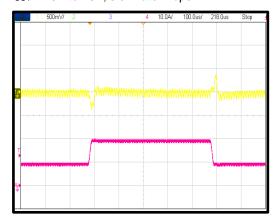

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board in the Design Example section on page 27.  $V_{IN} = 48V$ ,  $V_{OUT} = 12V$ , freq=100kHz, L=10uH, PSM,  $T_A = 25^{\circ}$ C, unless otherwise noted.

#### **Load Transient**

IOUT = 0A to 10A, PSM, slew rate 1A/µs

## **Load Transient**

I<sub>OUT</sub> = 0A to 10A, USM, slew rate 1A/µs

#### **Load Transient**

$I_{OUT} = 0A$  to 10A, FCCM Mode, slew rate 1A/ $\mu$ s

#### **Load Transient**

CH1:

V<sub>OUT</sub>/AC

CH4: Io

I<sub>OUT</sub> = 10A to 20A, slew rate 1A/µs

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

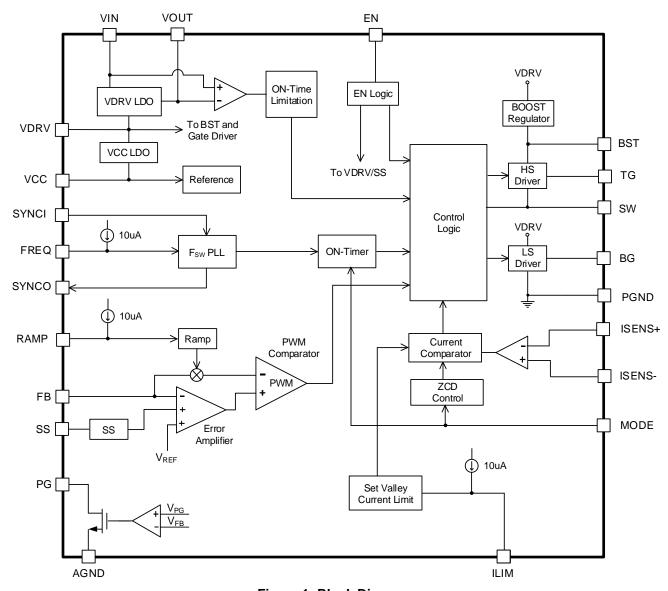

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: Block Diagram

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## **OPERATION**

#### Overview

The MP9931 is a high-performance, step down, synchronous converter controller IC with a wide input range. It implements COT control mode, switching frequency programmable control architecture to regulate the output voltage with external N-channel MOSFET switches.

Adaptive Constant-On-Time (COT) control mode provides fast transient response and eases loop stabilization. The DC auto tune loop provides good load and line regulation.

Under normal load condition, the controller operates in full PWM mode. At the beginning of each cycle, the high-side MOSFET (HS-FET) is turned ON when the feedback voltage ( $V_{FB}$ ) is below the reference voltage ( $V_{REF}$ ), which indicates insufficient output voltage. The ON period is determined by the output voltage and input voltage to make the switching frequency fairly constant over input voltage range.

An internal compensation is applied for COT control to make a more stable operation even when ceramic capacitors are used as output capacitors, this internal compensation will then improve the jitter performance without affect the line or load regulation.

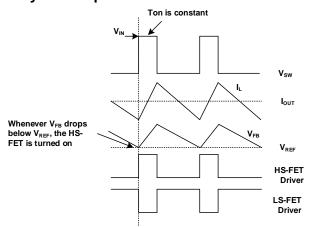

#### **Heavy-Load Operation**

Figure 2: Heavy Load Operation

When the output current is high and the inductor current is always above zero amps, it is called continuous-conduction-mode (CCM). The CCM mode operation is shown in Figure 2. When  $V_{\text{FB}}$  is below  $V_{\text{REF}}$ , HS-MOSFET is turned on for a fixed

interval. When the HS-MOSFET is turned off, the LS-MOSFET is turned on until next period.

There is a dead short between the input and GND if both the HS-FET and LS-FET are turned on at the same time. This is called shoot-through. To prevent shoot-through, a dead time is generated internally between the HS-FET off and LS-FET on, or LS-FET off and HS-FET on.

In CCM mode operation, the switching frequency is fairly constant and it is also called PWM mode.

In light load condition, MP9931 can be set in different MODE, refer to next section for detail.

## **Operation Mode**

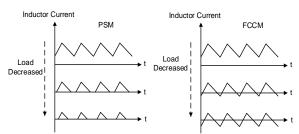

MP9931 works with fix frequency in heavy load condition. When load current decreases, MP9931 can work in forced continuous conduction mode (FCCM), pulse skip mode (PSM), or Ultrasonic Mode (USM) based on MODE pin setting. Refer to Table 1 for MODE pin setting. The operation mode can be change on-line.

**Table 1: MODE Setting**

| MODE pin | Light Load Mode |

|----------|-----------------|

| GND      | PSM without USM |

| FLOAT    | PSM with USM    |

| VCC      | FCCM mode       |

#### Pulse-Skip Mode (PSM)

With the load decrease, the inductor current decrease too. Once the inductor current touch zero, the operation is transition from continuous-conduction-mode (CCM) to discontinuous-conduction-mode (DCM).

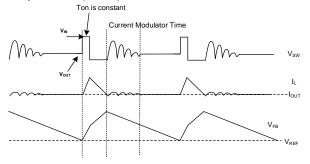

The light load operation is shown in Figure 3. When  $V_{FB}$  is below  $V_{REF}$ , HS-MOSFET is turned on for a fixed interval. When the HS-MOSFET is turned off, the LS-MOSFET is turned on until the inductor current reaches zero. In DCM operation, the  $V_{FB}$  does not reach  $V_{REF}$  when the inductor current is approaching zero. Both the BG and TG will be pull LOW whenever the inductor current reaches zero. At light load or no load condition, the output drops very slowly and the MP9931 reduces the switching frequency naturally. As a result, the efficiency at light load condition is greatly improved. At light load condition, the HS-MOSFET is not turned ON as frequently as at heavy load condition. This is also called Pulse-

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## Skip Mode (PSM).

**Figure 3: Light Load Operation**

As the output current increases from the light load condition, the time period within which the current modulator regulates becomes shorter. The HS-MOSFET is turned ON more frequently. Hence, the switching frequency increases correspondingly. The output current reaches the critical level when the current modulator time is zero. The critical level of the output current is determined as equation 1:

$$I_{OUT\_Critical} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times L \times F_{SW} \times V_{IN}}$$

(1)

It turns into CCM mode once the output current exceeds the critical level. After that, the switching frequency fairly constant over the output current range.

## Forced Continuous Conduction Mode (FCCM)

When the MP9931 sets in FCCM mode, if load is light, low-side FET doesn't turn off when inductor current touch ZCD. The inductor current goes negatively flowing from Vout to GND when LS-FET is on. This forces the inductor current to work in continuous conduction mode (CCM) with a fixed frequency, producing a lower  $V_{\text{OUT}}$  ripple than in PSM mode.

The FCCM mode operation is shown in Figure 4. HS-FET is turned on for a fixed interval. When the HS-FET is turned off, the LS-FET is turned on until next period.

Figure 4: PSM Mode and Forced CCM Mode

## **Ultrasonic Mode (USM)**

Ultrasonic mode (USM) is used to keep the switching frequency above audible frequency areas during light-load conditions. Once part goes into light load, Ton shrinks and ZCD drops to avoid IC switching frequency go below 20kHz.

#### **Low Dropout Operation**

Low dropout mode is designed to improve dropout when VIN is close to VOUT by further increase HS-FET on time after min-off-time is reached. At low dropout mode, the MP9931 is designed to operate at Ton extended mode as long as the voltage across BST - SW is greater than BST under-voltage lockout (UVLO). When the voltage from BST to SW drops below BST UVLO, the BST UVLO circuit turns off the high-side MOSFET (HS-FET), After the BST capacitor voltage is recharged above BST UVLO, the HS-FET turns on again to regulate the output. Since the BST regulation voltage is far greater than BST UVLO, the HS-FET can remain on for a long time without requirement to refresh the BST capacitor, thus increasing the effective duty cycle of the switching regulator. The low dropout operation makes the MP9931 suitable for application where VIN is close with VOUT. The max extend on time is limited by VIN-VOUT, when 3V<VIN-VOUT<6V, it's 10µs, when VIN-VOUT <3V, it's 20µs. When ss is pulled up to vcc the low drop out mode is disabled.

#### **Constant Current (CC) Mode**

MP9931 provide a CC mode operation for battery charge. Pull up SS to VCC via  $10k\Omega$  to enable CC Mode. At this condition, output UV protection and low drop out mode is disabled. FB pull down to GND or divide from VCC to set FB to lower than 0.8V are both ok for this condition. Figure 5 shows SS and FB typical connection for CC mode application.

Figure 5: CC Mode

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

The CC average current is set by valley current limit and inductor current ripple, can be calculate by equation 2 as below.

$$I_{CC} = \frac{V_{ILIM}}{R_S} + \frac{V_{OUT}}{2 \times f_{SW} \times L} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

(2)

Recommend use shunt resistor current sensing for CC mode to achieve better accuracy at full temperature range.

#### **Synchronization**

MP9931 frequency (internal oscillator set by FREQ pin) can be synchronized to an external clock with range ±20% of programmed switching frequency through SYNCI pin. When add one clock signal to SYNCI pin, the internal clock rising edge is synchronized to the external clock rising edge.

#### Floating Driver and Bootstrap Charging

The floating top gate driver is powered by an external bootstrap capacitor (CBST), which is normally refreshed when the high-side MOSFET (HS-FET) turns off. This floating driver has its own UVLO protection.

## **VDRV Power Supply and VCC Regulator**

Both high-side BST and low-side MOSFET drivers are powered from V<sub>DRV</sub>, usually a 4.7µF ceramic capacitor is needed at V<sub>DRV</sub> Pin to prevent large voltage spikes.

An internal low dropout linear regulator supplies VCC power from V<sub>DRV</sub>, most of the internal circuit are powered from the VCC regulator, a 2.2µF ceramic capacitor is recommended from VCC to AGND. All VIN, VDRV and VCC have their own UVLO circuit to protect the chip from operating at an insufficient supply voltage.

When VIN power is supplied and EN is high, MP9931 regulate  $V_{DRV}$  from VIN first. If  $V_{OUT}$ voltage >8.4V, MP9931 will slowly scale down the  $V_{DRV}$  and make it approximately equal to  $V_{OUT}$ , then, disable the VIN to VDRV LDO1 and enable the V<sub>OUT</sub> to V<sub>DRV</sub> LDO2. When V<sub>OUT</sub> drop below 7.4V, the source to V<sub>DRV</sub> will be change back to VIN and V<sub>DRV</sub> voltage will be scaled accordingly.

If 8.4V<V<sub>OUT</sub><10V, the V<sub>DRV</sub> LDO2 is in low dropout mode and  $V_{DRV}$  is approximately equal to  $V_{OUT}$ . When VOUT is greater than 10V, VDRV is regulated to 10V, so that MP9931 can get higher efficiency for internal driver loss.

V<sub>DRV</sub> can also be power from external voltage source.

Figure 6: Internal LDO Structure

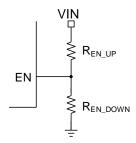

#### **Enable (EN) and Programmable UVLO**

EN pin enables and disables the MP9931. When applying a voltage lower than 0.4V, MP9931 is shutdown. After the voltage rise to the EN high threshold (1.2V typically), the MP9931 enables starts switching operation. Switching operation is disabled when EN voltage falls below its falling threshold.

Tie EN to VIN through a resistor divider R<sub>EN UP</sub> and R<sub>EN DOWN</sub> to program the VIN start up threshold (see Figure 7).

Figure 7: EN Divider Resistors

EN pin can be directly connect to VIN via a pull-up resistor limits the EN input current below 100µA. which prevents damage to the EN circuit internal.

For example, when connecting 100V to VIN, then the pull up resistor should be larger than  $935k\Omega$ .

$R_{PULL\_UP} \ge (100V - 6.5V) / 100\mu A = 935k\Omega$ .

#### **Switching Frequency**

The selection of switching frequency is a tradeoff between efficiency and component size. Low frequency operation increases efficiency by

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

reducing MOSFET switching loss, but requires larger inductance and capacitance to maintain low output voltage ripple. The switching frequency of MP9931 can be set by the R<sub>FREQ</sub> connected to FREQ and AGND pin as below table.

**Table 2: Switching Frequency Selection**

| FREQ pin      | Switching Frequency |

|---------------|---------------------|

| Ω0            | 100kHz              |

| 20kΩ to GND   | 150kHz              |

| 45.3kΩ to GND | 200kHz              |

| 80.6kΩ to GND | 250kHz              |

| 124kΩ to GND  | 300kHz              |

| 180kΩ to GND  | 400kHz              |

| 243kΩ to GND  | 600kHz              |

| VCC           | 1MHz                |

When EN is high and VCC rising above its UVLO, MP9931 starts work by source a current pulse to FREQ pin to detect FREQ setting. This detection set the switching frequency and latch the setting after MP9931 startup.

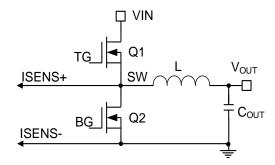

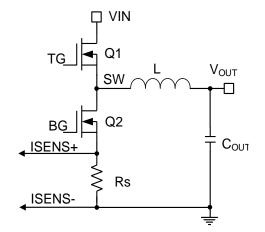

#### **Current Sense**

The MP9931 implements a lossless current sense scheme designed to limit the inductor current during an overload or short-circuit condition. Figure 8 portrays the current sense method using the on-state resistance of the low-side MOSFET. Meanwhile, Figure 9 shows an alternative implementation with current shunt resistor R<sub>S</sub>. The MP9931 senses the inductor current during the PWM off-time.

Figure 8: MOSFET R<sub>DS (on)</sub> Current Sensing

Figure 9: Shunt Resistor Current Sensing

The MP9931 has four fixed options for current limit setting as shown in table 3.

When use lossless current sense, MP9931 monitors the inductor current by on-state resistance of the low-side MOSFET. The current limit can be calculate by equation 3.

$$I_{ILIM} = \frac{V_{ILIM}}{R_{DS\ ON}} \tag{3}$$

When use shunt resistor current sensing, the current sense resistor  $R_{\text{S}}$  monitors the inductor current. Its value is chosen based on the current limit threshold. The relationship between the inductor valley current  $I_{\text{ILIM}}$  and  $R_{\text{S}}$  is:

$$I_{ILIM} = \frac{V_{ILIM}}{R_S} \tag{4}$$

The typical values for  $R_S$  are in the range of  $2m\Omega$  to  $10m\Omega$ .

#### **Valley Current Limit set**

The ILIM pin of the MP9931 sources a reference current that flows to external resistor  $R_{\text{ILIM}}$ , to program the current limit sense voltage. TG is not allowed to pull high when voltage of ISENS+ and ISENS- fall below the sense voltage limit set by ILIM pin.

Connect ILIM pin to AGND through resistor R<sub>ILIM</sub> to program the current limit sense voltage between ISENS+ and ISENS- pin as below table.

## PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

Table 3: Valley Current Limit Threshold

| ILIM pin     | Valley Current Limit<br>Threshold |  |

|--------------|-----------------------------------|--|

| GND          | 25mV                              |  |

| 51kΩ to GND  | 50mV                              |  |

| 120kΩ to GND | 75mV                              |  |

| VCC          | 100mV                             |  |

The MP9931 detects the appropriate mode at start-up and sets the temperature coefficient (TC) accordingly. MP9931 provide a TC of +4500 generally ppm/°C track the R<sub>DS</sub>(on) temperature variation of the low-side MOSFET. Conversely, MP9931 have no TC in R<sub>SENSE</sub> mode. This controls the valley of inductor current during a steady state overload at the output.

## **Over-Current Protection (OCP)**

The MP9931 has a hiccup, cycle-by-cycle, overcurrent limiting control. The MP9931 limited the voltage between ISENS+ and ISENS- pin for the valley current. PWM is not allowed to initiate a new cycle before the inductor current falls to the valley threshold.

After the cycle-by-cycle over-current limit occurs, the output voltage drops until V<sub>FB</sub> is below the under-voltage (UV) threshold (typically 30% of the V<sub>REF</sub>). Once UV is triggered, the MP9931 enters hiccup mode to restart the part periodically. This protection mode is especially useful when the output is dead shorted to ground. The average short-circuit current is reduced greatly to alleviate thermal issues and protect the regulator. The MP9931 exits hiccup mode once the over-current condition is removed.

#### **RAMP Set**

The RAMP pin of the MP9931 can be used to select the internal ramp for stability. With different R<sub>RAMP</sub> to GND, can set different ramp value. Below table 4 shows the relationship of ramp pin pull down resistor R<sub>RAMP</sub> and internal R value for RAMP calculate.

Table 4: RAMP vs. Internal R

| RAMP pin     | RAMP  | R (kΩ) |

|--------------|-------|--------|

| GND          | 1X    | 2077   |

| 51kΩ to GND  | 0.5X  | 4077   |

| 120kΩ to GND | 0.33X | 6077   |

| 180kΩ to GND | 2X    | 1077   |

| VCC          | 4X    | 577    |

RAMP can be calculate by equation 5 as below:

$$RAMP(mV) = K_{DIV} \times \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times R(k\Omega)}$$

(5)

$K_{DIV}$  is fixed to  $0.44 \times 10^4$ .

For example, select 1X ramp for 48V input, 12V output, RAMP is about 21mV.

Note: Larger RAMP set is better for stability, but transient performance will be worse at the same time.

#### **Power Good Function**

The MP9931 includes an open-drain power good output that indicates whether the regulator's output is within the range of its nominal value. When the output voltage is out of this range, the PG output is pulled to low. It should be pull up to a voltage source through a resistor (e.g.,  $100k\Omega$ ).

PG pin has self-driving capability, if MP9931 is off and PG pin is pulled up to another DC power source through a resistor, the PG pin can also be pulled low by self-driving circuit.

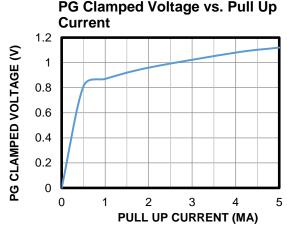

The relationship between the PG clamped voltage and the pull-up current is shown in Figure 10.

Figure 10: PG Clamped Voltage vs. Pull Up Current

#### **Soft Start**

The soft start (SS) is implemented to prevent the converter output voltage from overshooting during startup. When the chip starts, the internal circuitry generates a soft-start voltage ramping up from 0V to VCC. When it is lower than the internal V<sub>REF</sub>, SS

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

voltage overrides  $V_{\text{REF}}$ , so the error amplifier uses SS voltage as the reference. When SS voltage is higher than  $V_{\text{REF}}$ ,  $V_{\text{REF}}$  regains control.

An external capacitor connected from SS to AGND is charged by an internal current source, producing a ramped voltage. The soft-start time (t<sub>SS</sub>) is set by the external SS capacitor and can be calculated by equation 6 as below:

$$t_{SS}(ms) = \frac{C_{SS}(nF) \times V_{REF}(V)}{I_{SS}(\mu A)}$$

(6)

Where  $C_{SS}$  is the value of external SS capacitor,  $V_{REF}$  is the internal reference voltage, and  $I_{SS}$  is the SS charge current. Typical value of Iss is 4uA. SS will be reset when a protection happened except for output over voltage protection.

With Css=47nF, t<sub>SS</sub> is about 9.4ms.

#### **Pre-bias Startup**

The MP9931 is designed for monotonic startup into pre-biased loads. If the output is pre-biased to a certain voltage during startup, MP9931 won't switch until SS ramps up to the value reference to the V<sub>OUT</sub> bias voltage. The BST voltage will be refreshed in this condition.

#### **Output Over-Voltage Protection**

MP9931 output voltage is monitored by FB voltage. If FB voltage is typically 108% of the reference, it'll trigger OVP. Once it triggers OVP, MP9931 will stop switching, MP9931 recover to normal loop control when  $V_{\text{OUT}}$  drops to 105% of regulation voltage.

#### **Thermal Protection**

The MP9931 has thermal protection by monitoring the IC temperature internally. This function prevents the chip from operating at exceedingly high temperature. If the junction temperature exceeds the OTP rising threshold, the whole chip shuts down. It is a non-latch protection and once the junction temperature drops below with the hysteresis threshold, the device resumes operation by initiating a soft-start.

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

#### APPLICATION INFORMATION

## **Setting the Output Voltage**

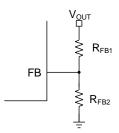

The external resistor divider is used to set the output voltage.

Figure 11: Vout Setting Resistor

If R<sub>FB1</sub> is determined, then R<sub>FB2</sub> can be calculated with below formula:

$$R_{FB2} = \frac{R_{FB1}}{\frac{V_{OUT}}{0.8V} - 1}$$

(7)

Table 5: Resistor Selection for Common Output Voltages

| V <sub>OUT</sub> (V) | R1 (kΩ)  | R2 (kΩ)   |

|----------------------|----------|-----------|

| 12                   | 160 (1%) | 11.5 (1%) |

| 33                   | 324(1%)  | 8.06(1%)  |

#### Selecting the Input Capacitor (C<sub>IN</sub>)

The step-down converter has a discontinuous input current ( $I_{\text{IN}}$ ), and requires a capacitor to supply AC current to the step-down converter while maintaining the DC  $V_{\text{IN}}$ . Use ceramic capacitors for the best performance. Place the input capacitors as close to the VIN pin as possible.

The capacitance can vary significantly with the temperature. Capacitors with X5R and X7R dielectrics are recommended due to their stable temperature characteristics and low ESR.

The input capacitors should have a ripple current rating that exceeds the converter's maximum input ripple current (I<sub>CIN\_MAX</sub>). The input ripple current (I<sub>CIN</sub>) can be estimated with Equation (8):

$$I_{CIN} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}})}$$

(8)

The worst-case condition occurs at  $V_{IN} = 2 \times V_{OUT}$ , which can be calculated with Equation (9):

$$I_{CIN} = \frac{I_{OUT}}{2} \tag{9}$$

For simplification, choose an input capacitor ( $C_{IN}$ ) with an RMS current rating that exceeds half the maximum load current ( $I_{LOAD\ MAX}$ ).

The input capacitance value determines converter's  $V_{\text{IN}}$  ripple ( $\Delta V_{\text{IN}}$ ). If there is a  $\Delta V_{\text{IN}}$  requirement in the system, then select  $C_{\text{IN}}$  to meet the system's specification.

$\Delta V_{IN}$  can be estimated with Equation (10):

$$\Delta V_{IN} = \frac{I_{OUT}}{f_{SW} \times C_{IN}} \times \frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}}) \tag{10}$$

The worst-case condition occurs at  $V_{IN} = 2 \times V_{OUT}$ , which can be calculated with Equation (11):

$$\Delta V_{IN} = \frac{1}{4} \times \frac{I_{OUT}}{f_{SW} \times C_{IN}}$$

(11)

## Selecting the Output Capacitor (C<sub>OUT</sub>)

The output capacitor ( $C_{OUT}$ ) maintains the DC  $V_{OUT}$ . The  $V_{OUT}$  ripple ( $\Delta V_{OUT}$ ) can be estimated with Equation (12):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{SW}} \times L} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \times (R_{\text{ESR}} + \frac{1}{8 \times f_{\text{SW}} \times C_{\text{OUT}}}) \text{ (12)}$$

When using ceramic capacitors, the capacitance dominates the impedance at  $f_{SW}$ . The capacitance also dominates  $\Delta V_{OUT}$ . For simplification,  $\Delta V_{OUT}$  can be estimated with Equation (13):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{8 \times f_{\text{SW}}^2 \times L \times C_{\text{OUT}}} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) (13)$$

When using POSCAP capacitors, the ESR dominates the impedance at  $f_{SW}$ . For simplification,  $\Delta V_{OUT}$  can be estimated with Equation (14):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{SW}} \times L} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \times R_{\text{ESR}} \qquad (14)$$

#### Selecting the Inductor

The inductor supplies a constant current to the output load while being driven by the switching  $V_{\text{IN}}$ . A larger-value inductor results in less ripple current and a lower  $\Delta V_{\text{OUT}}$ ; however, a larger-value inductor has a larger physical size, a higher series resistance, and a lower saturation current. Recommend to choose an inductor so that the peak-to-peak inductor ripple current  $(\Delta I_{\text{L}})$  is between 20% and 50% of the maximum output

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

current ( $I_{OUT\_MAX}$ ). The peak inductor current ( $I_{L\_PEAK}$ ) should be below the saturation current. The inductance (L) can be calculated with Equation (15):