# **MK SD NAND Product Datasheet**

# **Product List**

MKDN032GCL-AD MKDN064GCL-AD

For the SD NAND reference design and precautions, please click the following official website link to download the attachement:

https://www.mkfounder.com/zlxz/

1

# **Revision History**

| Version | Date       | Description      |

|---------|------------|------------------|

| Rev 1.0 | 2024/06/27 | Original version |

### Notice:

The datasheet is prepared and approved by MK Founder semiconductor co., LTD.

MK Founder reserves the right to change products or specifications without notice. ©2024 MK Founder semiconductor co., LTD. All rights reserved.

# **Table Of Contents**

| 1 Introduction                       | 4  |

|--------------------------------------|----|

| 2 Product List                       | 5  |

| 3 Features                           | 5  |

| 4 Physical Characteristics           |    |

| 4.1 Temperature                      | 5  |

| 5 Pin Assignments(SD Mode& SPI Mode) | 6  |

| 6 Usage                              | 7  |

| 6.1 SD Bus Mode protocol             | 7  |

| 6.2 Card Initialize                  | 8  |

| 6.3 Electrical Characteristics       | 13 |

| 7 Internal Information               | 14 |

| 7.1 Registers                        | 14 |

| 7.1.1 OCR Register                   |    |

| 7.1.2 CID Register                   | 16 |

| 7.1.3 CSD Register                   | 17 |

| 7.1.4 RCA Register                   | 18 |

| 7.1.5 DSR Register                   |    |

| 8 Power Scheme                       |    |

| 8.1 Power Up                         |    |

| 8.2 Power Up Time                    |    |

| 8.2.1 Power On or Power Cycle        |    |

| 8.2.2 Power Supply Ramp Up           | 20 |

| 8.2.3 Power Supply Ramp Up           | 20 |

| 9 Package Dimensions                 |    |

| 10 Reference Design                  | 22 |

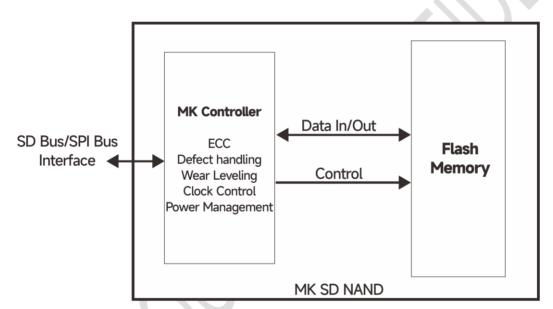

### 1 Introduction

MK Nano SD NAND is an embedded storage solution designed in a LGA package form. The operation of SD is similar to an SD card which is an Commercial Grade.

Nano SD NAND consists of NAND flash and a high performance controller. 3.3V supply voltage is required for the NAND area (VCC).

Nano SD NAND is fully compliant with SD3.0 interface, which allows most of general CPU to utilize.

Nano SD NAND has high performance, high quality and low power consumption.

MK's SD NAND family includes an on-board intelligent controller which manages interface protocols; security algorithms for content protection; data storage and retrieval, as well as Error Correction Code (ECC) algorithms; defect handling; power management; wear leveling and clock control.

ECC:Error Correction code algorithms

### 2 Product List

| Part Number   | Flash<br>Type | Capacity | Actual<br>Capacity | Read/Write (MByte/s) | Package | Size     |

|---------------|---------------|----------|--------------------|----------------------|---------|----------|

| MKDN032GCL-AD | MLC           | 32Gbit   | 3688MB             | 80/20                | LGA-16  | 9x12.5mm |

| MKDN064GCL-AD | MLC           | 64Gbit   | 7374MB             | 80/20                | LGA-16  | 9x12.5mm |

### 3 Features

- Support up to 208MHz clock frequency

- Support SPI Mode

- Built-in HW ECC Engine and highly reliable NAND management mechanism

- Advanced thermal management features to maximize performance and data protection at extended temperatures Static, dynamic, and global wear leveling

- Bad block management, intelligent garbage collection and support for interleaving, cache, and multi-plane programming

- Read disturb management and dynamic data refresh

- Best-in-class power fail management

## 4 Physical Characteristics

### 4.1 Temperature

1) Operation Conditions

Temperature Range: -25°C to +85°C

2) Storage Conditions

Temperature Range: -40°C to +85°C

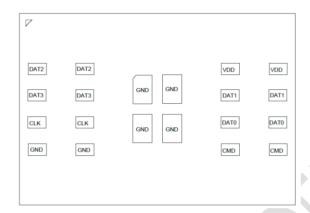

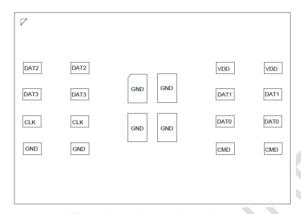

### 5 Pin Assignments(SD Mode& SPI Mode)

#### Top view through package

|      |        | SD Mode               |            | SPI Mode               |

|------|--------|-----------------------|------------|------------------------|

| Name | Tyte   | Description           | Tyte       | Description            |

| DAT2 | I/O/PP | Data Line [Bit 2]     | RSV        | Reserved               |

| DAT3 | I/O/PP | Data Line [Bit 3]     | <b>I</b> 3 | Chip Select (neg true) |

| CLK  | I      | Clock                 | I          | Clock                  |

| GND  | S      | Supply voltage ground | S          | Supply voltage ground  |

| VDD  | S      | Supply voltage        | S          | Supply voltage         |

| DAT1 | I/O/PP | Data Line [Bit 1]     | RSV        | Reserved               |

| DAT0 | I/O/PP | Data Line [Bit 0]     | O/PP       | Data Out               |

| CMD  | PP     | Command/Response      | I          | Data In                |

- a. Type Key: S=power supply; I= input; O=output using push-pull drivers; PP=I/O using push-pull drivers.

- b. The extended DAT lines (DAT1-DAT3) are input on power up. They start to operate as DAT lines after the SET\_BUS\_WIDTH Type Key: S=power supply; I=input; O=output using push-pull drivers; PP=I/O using push-pull drivers.

- c. At power up this line has a 50 kilohm pull-up enabled in the card. This resistor serves two functions: Card detection and Mode Selection. For Mode Selection, the host can drive the line high or let it be pulled high to select SD mode. If the host wants to select SPI mode it should drive the line low. For Card detection, the host detects that the line is pulled high. This pull-up should be disconnected by the user, during regular data transfer, with SET\_CLR\_CARD\_DETECT (ACMD42) command.

6

### 6 Usage

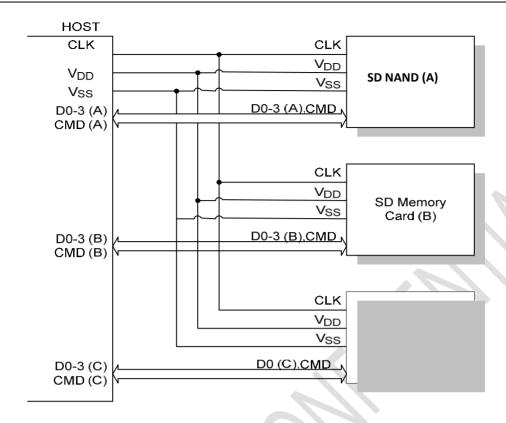

### 6.1 SD Bus Mode protocol

The SD bus allows the dynamic configuration of the number of data line from 1 to 4 Bi-directional data signal. After power up by default, the SD card will use only DAT0. After initialization, host can change the bus width.

Multiplied SD cards connections are available to the host. Common VDD, VSS and CLK signal connections are available in the multiple connections. However, Command, Respond and Data lined (DAT0-DAT3) shall be divided for each device from host.

This feature allows easy trade off between hardware cost and system performance. Communication over the SD bus is based on command and data bit stream initiated by a start bit and terminated by stop bit.

#### Command

Commands are transferred serially on the CMD line. A command is a token to starts an operation from host to the device. Commands are sent to an addressed single card (addressed Command) or to all connected cards (Broad cast command).

#### Response

Responses are transferred serially on the CMD line.

A response is a token to answer to a previous received command. Responses are sent from an addressed single card or from all connected cards.

#### **Data**

Data can be transfer from the card to the host or vice versa. Data is transferred via the data lines.

| CLK       | Host card Clock signal                  |  |  |

|-----------|-----------------------------------------|--|--|

| CMD       | Bi-directional Command/ Response Signal |  |  |

| DATO-DAT3 | 4 Bi-directional data signal            |  |  |

| VDD       | Power supply                            |  |  |

| VSS       | GND                                     |  |  |

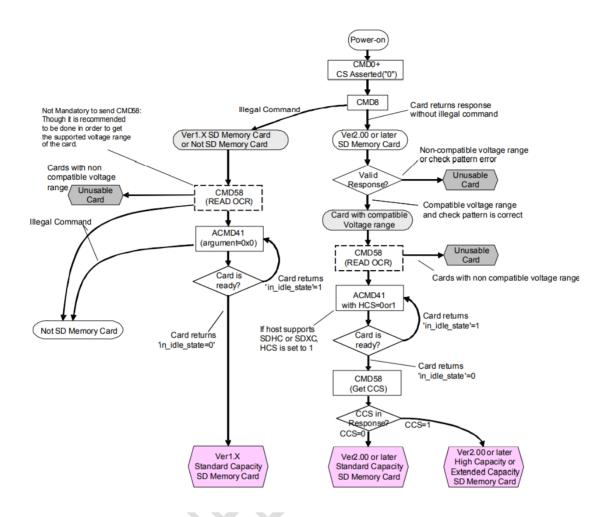

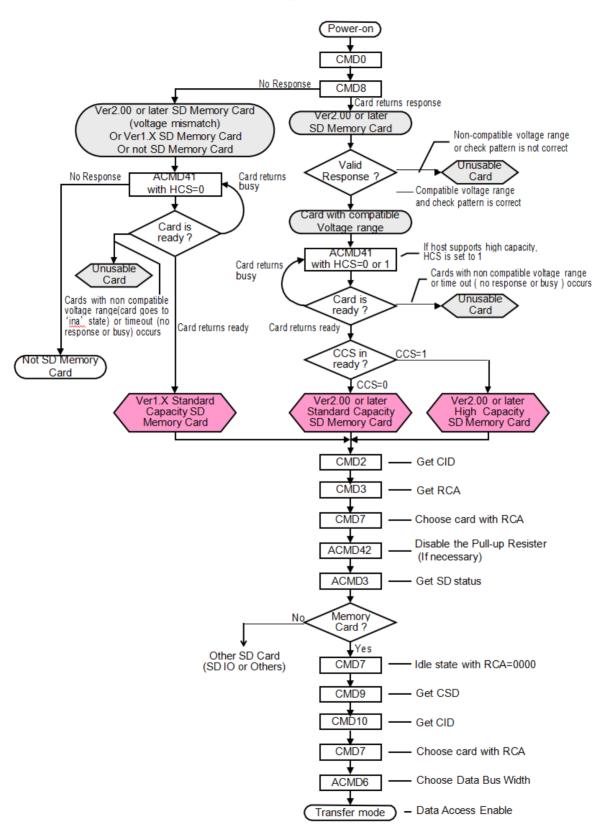

#### 6.2 Card Initialize

To initialize the SD NAND, follow the following procedure is recommended example.

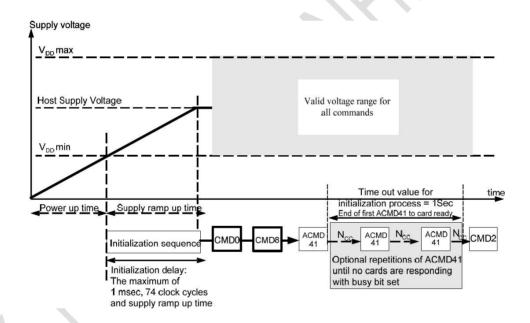

### 1) Supply Voltage for initialization

Host System can apply the Operating Voltage from initialization to the card. Apply more than 74 cycles of Dummy-clock to the SD card.

### 2) Select operation mode (SD mode or SPI mode)

In case of SPI mode operation, host should drive 1 pin (CD/DAT3) of SD Card I/F to "Low" level. Then, issue CMD0. In case of SD mode operation, host should drive or detect 1 pin of SD Card I/F (Pull up register of 1 pin is pull up to "High" normally).

Card maintain selected operation mode except re-issue of CMD0 or power on below is SD mode initialization procedure.

- 3) Send the ACMD41 with Arg = 0 and identify the operating voltage range of the Card.

- 4) Apply the indicated operating voltage to the card.

Reissue ACMD41 with apply voltage storing and repeat ACMD41 until the busy bit is cleared. (Bit 31 Busy = 1) If response time out occurred, host can recognize not SD Card.

- 5) Issue the CMD2 and get the Card ID (CID).

- 6) Issue the CMD3 and get the RCA. (RCA value is randomly changed by access, not equal zero)

- 7) Issue the CMD7 and move to the transfer state.

If necessary, Host may issue the ACMD42 and disabled the pull up resistor for Card detect.

- 8) Issue the ACMD13 and poll the Card status as SD Memory Card.Check SD\_CARD\_TYPE value. If significant 8 bits are "all zero", that means SD Card. If it is not, stop initialization.

- 9) Issue CMD7 and move to standby state. Issue CMD9 and get CSD. Issue CMD10 and get CID.

- 10) Back to the Transfer state with CMD7.

- 11) Issue ACMD6 and choose the appropriate bus-width.

Then the Host can access the Data between the SD card as a storage device.

#### **SPI Mode Initialization Flow**

#### Normal SD initial flow

### **SD card Initialize Procedure**

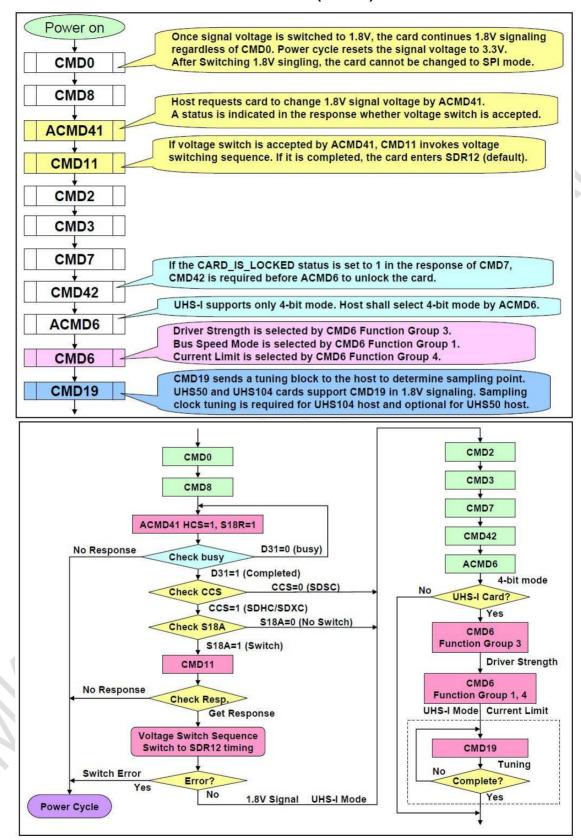

#### SD3.0 initial flow for UHS-I(IO 1.8v) switch

### **6.3** Electrical Characteristics

### **Absolute Maximum Rating**

| Item                        | Symbol | CONDITION        | MIN. | Тур. | MAX. | Unit |

|-----------------------------|--------|------------------|------|------|------|------|

| Supply Voltage              | VDD    |                  | 2.7  | 3.3  | 3.6  | V    |

| Input Leakage<br>Current    | IIL    |                  | -10  |      | 10   | uA   |

| Output Leakage<br>Current   | ILO    |                  | -10  |      | 10   | uA   |

| Input Voltage Setup<br>Time | Ts     | VIN = 0 V to VDD | 0    | -    | 250  | ms   |

### **Current Consumption**

| ltem            | Symbol | CONDITION | MIN. | Тур. | MAX. | Unit |

|-----------------|--------|-----------|------|------|------|------|

| Read Current    | ICCO1  | CLK=50MHZ | -    | 53   | -    | mA   |

| Write Current   | ICCO2  | CLK=50MHZ | -    | 40   | -    | mA   |

| Standby Current | ICCS   |           | -    | 80   | -    | uA   |

### Note:

<sup>1)</sup>Full speed test

<sup>2)</sup>The SD NAND mode was four-wire during the test

### 7 Internal Information

### 7.1 Registers

The Nano SD NAND has six registers and SD Status information: OCR, CID, CSD, RCA, DSR, SCR and SD Status. DSR IS NOT SUPPORTED in this card.

There are two types of register groups.

MMC compatible registers: OCR, CID, CSD, RCA, DSR, and SCR SD card Specific: SD Status

### **SD** card Registers

| Resister Name | Bit Width | Description                                                       |  |  |

|---------------|-----------|-------------------------------------------------------------------|--|--|

| OCR           | 32        | Operation Conditions (VDU Voltage Profile and Busy Status)        |  |  |

| CID           | 128       | Card Identification information                                   |  |  |

| CSD           | 128       | Card specific information                                         |  |  |

| RCA           | 16        | Relative Card Address                                             |  |  |

| DSR           | 16        | Not Implemented (Programmable Card Driver): Driver Stage Register |  |  |

| SCR           | 64        | SD Memory Card's special features                                 |  |  |

| SD Status     | 512       | Status bits and Card features                                     |  |  |

### 7.1.1 OCR Register

This 32-bit register describes operating voltage range and status bit in the power supply.

**OCR** register definition

|         | OOK register defini              |                     |

|---------|----------------------------------|---------------------|

| OCR bit | VDD voltage window               | Initial             |

| 31      | Card power up status bit(busy)   | "0" = busy          |

| 30      | Card Capacity Status             | "0"= SD Memory Card |

| 29-25   | reserved                         | All 0               |

| 24      | Switching to 1.8V Accepted(S18A) | 0                   |

| 23      | 3.6 - 3.5                        | 1                   |

| 22      | 3.5 - 3.4                        | 1                   |

| 21      | 3.4 - 3.3                        | 1                   |

| 20      | 3.3 - 3.2                        | 1                   |

| 19      | 3.2 - 3.1                        | 1                   |

| 18      | 3.1 - 3.0                        | 1                   |

| 17      | 3.0 - 2.9                        | 1                   |

| 16      | 2.9 - 2.8                        | 1                   |

| 15      | 2.8 - 2.7                        | 1                   |

| 14      | Reserved                         | 0                   |

| 13      | Reserved                         | 0                   |

| 12      | Reserved                         | 0                   |

| 11      | Reserved                         | 0                   |

| 10      | Reserved                         | 0                   |

| 9       | Reserved                         | 0                   |

| 8       | Reserved                         | 0                   |

| 7       | Reserved for Low Voltage Range   | 0                   |

| 6       | Reserved                         | 0                   |

| 5       | Reserved                         | 0                   |

| 4       | Reserved                         | 0                   |

| 3-0     | reserved                         | All 0               |

bit 23-4: Describes the SD Card Voltage

bit 31 indicates the card power up status. Value "1" is set after power up and initialization procedurehas been completed.

### 7.1.2 CID Register

The CID (Card Identification) register is 128-bit width. It contains the card identification information. (Refer Appendix 3. for the detail)

The Value of CID Register is vender specific.

### **CID Register**

| Field    | Width | CID-slice | Initial Value |

|----------|-------|-----------|---------------|

| MID      | 8     | [127:120] | 0xF2          |

| OID      | 16    | [119:104] | 0x2345        |

| PNM      | 40    | [103:64]  | MK            |

| PRV      | 8     | [63:56]   | 0x06          |

| PSN      | 32    | [55:24]   | 150C0415      |

| reserved | 4     | [23:20]   | 0x0           |

| MDT      | 12    | [19:8]    | 0x21C         |

| CRC      | 7     | [7:1]     | CRC7          |

| reserved | 1     | [0:0]     | 0x1           |

### 7.1.3 CSD Register

CSD is Card-Specific Data register provides information on 128bit width. Some field of this register can writable by PROGRAM\_CSD (CMD27).

**CSD** Register

|                     |       |           | CSD Register |               |

|---------------------|-------|-----------|--------------|---------------|

| Field               | Width | Cell Type | CSD Slice    | Initial Value |

| CSD_STRUCTURE       | 2     | R         | [127:126]    | 01b           |

| reserved            | 6     | R         | [125:120]    | 000000b       |

| TAAC                | 8     | R         | [119:112]    | 00001110b     |

| NSAC                | 8     | R         | [111:104]    | 0000000b      |

| TRAN_SPEED          | 8     | R         | [103:96]     | 00110010b     |

| CCC                 | 12    | R         | [95:84]      | 010110110101b |

| READ_BL_LEN         | 4     | R         | [83:80]      | 1001b         |

| READ_BL_PARTIAL     | 1     | R         | [79:79]      | 0b            |

| WRITE_BLK_MISALIG   | 1     | R         | [78:78]      | 0b            |

| READ_BLK_MISALIGN   | 1     | R         | [77:77]      | 0b            |

| DSR_IMP             | 1     | R         | [76:76]      | 0b            |

| reserved            | 6     | R         | [75:70]      | 000000b       |

| C_SIZE              | 22    | R         | [69:48]      | xxxxxxxxb     |

| reserved            | 1     | R         | [47:47]      | 0b            |

| ERASE_BLK_EN        | 1     | R         | [46:46]      | 1b            |

| SECTOR_SIZE         | 7     | R         | [45:39]      | 1111111b      |

| WP_GRP_SIZE         | 7     | R         | [38:32]      | 000000b       |

| WP_GRP_ENABLE       | 1     | R         | [31:31]      | 0b            |

| reserved            | 2     | R         | [30:29]      | 00b           |

| R2W_FACTOR          | 3     | R         | [28:26]      | 010b          |

| WRITE_BL_LEN        | 4     | R         | [25:22]      | 1001b         |

| WRITE_BL_PARTIAL    | 1     | R         | [21:21]      | 0b            |

| reserved            | 5     | R         | [20:16]      | 00000b        |

| FILE_FORMAT_GRP     | 1     | R/W(1)    | [15:15]      | 0b            |

| COPY                | _1    | R/W(1)    | [14:14]      | 0b            |

| PERM_WRITE_PROTE    | 1     | R/W(1)    | [13:13]      | 0b            |

| FILE_FORMAT         | 2     | R         | [11:10]      | 00b           |

| reserved            | 2     | R         | [9:8]        | 00b           |

| CRC                 | 7     | R/W       | [7:1]        | 0101101b      |

| not used, always'1' | 1     | -         | [0:0]        | 1b            |

Cell Type:R: Read Only, R/W: Writable and Readable, R/W(1): One-time Writable / Readable Note: Erase of one data block is not allowed in this card. This information is indicated by "ERASE\_BLK\_EN".

Host System should refer this value before one data block size erase.

#### 7.1.4 RCA Register

The writable 16bit relative card address register carries the card address in SD Card mode.

#### 7.1.5 DSR Register

This register is not implemented on this card.

### 8 Power Scheme

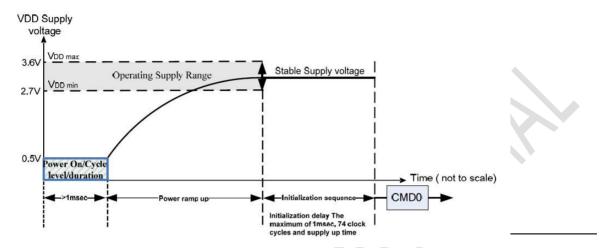

### 8.1 Power Up

'Power up time' is defined as voltage rising time from 0 volt to VDD min.

'Supply ramp up time' provides the time that the power is built up to the operating level (Host Supply Voltage) and the time to wait until the Nano SD NAND can accept the first command,

The host shall supply power to the card so that the voltage is reached to Vdd\_min within 250ms and start to supply at least 74 SD clocks to the Nano SD NAND with keeping CMD line to high.

### 8.2 Power Up Time

Host needs to keep power line level less than 0.5V and more than 1ms before power ramp up.

### 8.2.1 Power On or Power Cycle

Followings are requirements for Power on and Power cycle to assure a reliable Tailor™ SD hard reset.

- (1) Voltage level shall be below 0.5V

- (2) Duration shall be at least 1ms.

### 8.2.2 Power Supply Ramp Up

The power ramp up time is defined from 0.5V threshold level up to the operating supply voltage which is stable between VDD(min.) and VDD(max.) and host can supply SDCLK.

Followings are recommendation of Power ramp up:

- (1) Voltage of power ramp up should be monotonic as much as possible.

- (2) The minimum ramp up time should be 0.1ms.

- (3) The maximum ramp up time should be 35ms for 2.7-3.6V power supply.

### 8.2.3 Power Supply Ramp Up

When the host shuts down the power, the VDD shall be lowered to less than 0.5Volt for a minimum period of 1ms. During power down, DAT, CMD, and CLK should be disconnected or driven to logical 0 by the host to avoid a situation that the operating current is drawn through the signal lines.

If the host needs to change the operating voltage, a power cycle is required. Power cycle means the power is turned off and supplied again. Power cycle is also needed for accessing cards that are already in Inactive State. To create a power cycle the host shall follow the power down description before power up the card (i.e. the VDD shall be once lowered to less than 0.5Volt for a minimum period of 1ms).

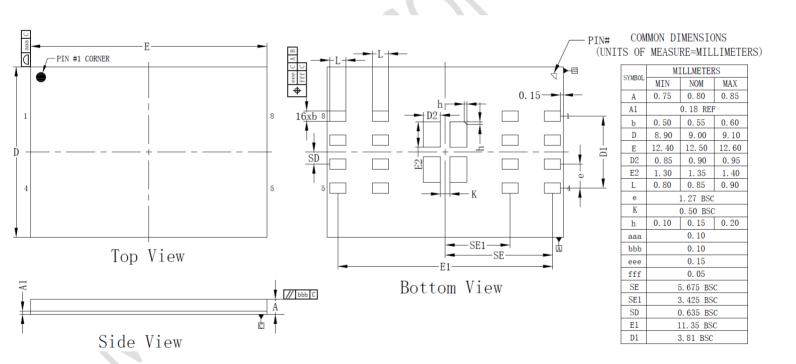

## 9 Package Dimensions

Top view through package

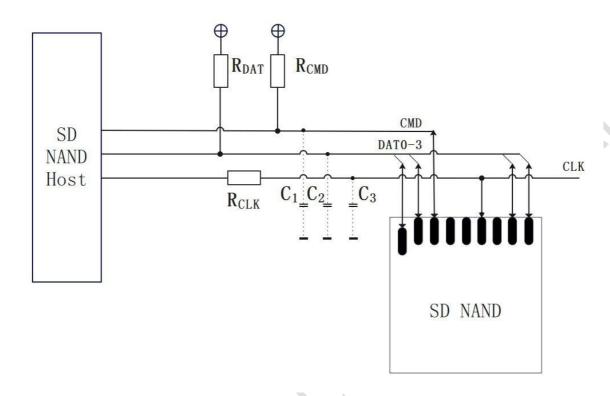

## 10 Reference Design

RDAT and RCMD (10K $\sim$ 100 k $\Omega$ ) are pull-up resistors protecting the CMD and the DAT lines against bus floating when Nano SD NAND is in a high-impedance mode.

The host shall pull-up all DAT0-3 lines by RDAT, even if the host uses the Nano SD NAND as 1 bit mode-only in SD mode. It is recommended to have 2.2uF capacitance on VDD. Rclk reference  $0\sim120~\Omega$ .