## 特点

- 2 端口 EtherCAT 从站控制器

- 内部集成 2 个以太网 PHY 芯片

- I/O 电压 3.3V

- 内部集成 1.2V 稳压器

- 8/16 bit 异步并口

- SPI/QSPI 接口

- 16 个 Digital I/O

- 16 个 GPIO

- LGA-64 封装

## 功能特性

- 集成式高性能 100 Mbps 以太网收发器

- 符合 IEEE 802.3/802.3u 标准

- 自动极性检测与校正

- 自动线序自适应(Auto-MDIX)

- EtherCAT 从站控制器

- 3 个现场总线内存管理单元(FMMU)

- 4 个同步管理器(SM)

- 64-bit 分布式时钟(DC)

- 8K Bytes SRAM

- 8/16 bit 异步并口模式

- 索引寄存器访问模式(Index)

- 地址数据复用访问模式(Multiplex)

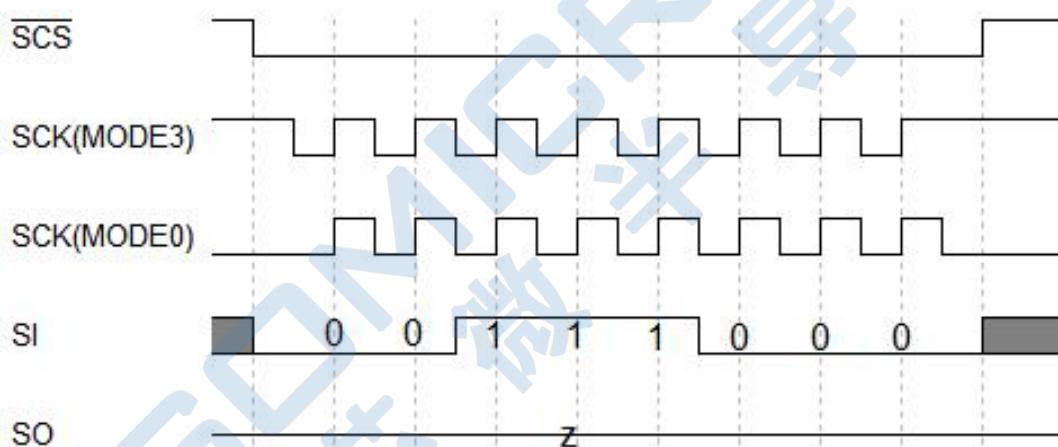

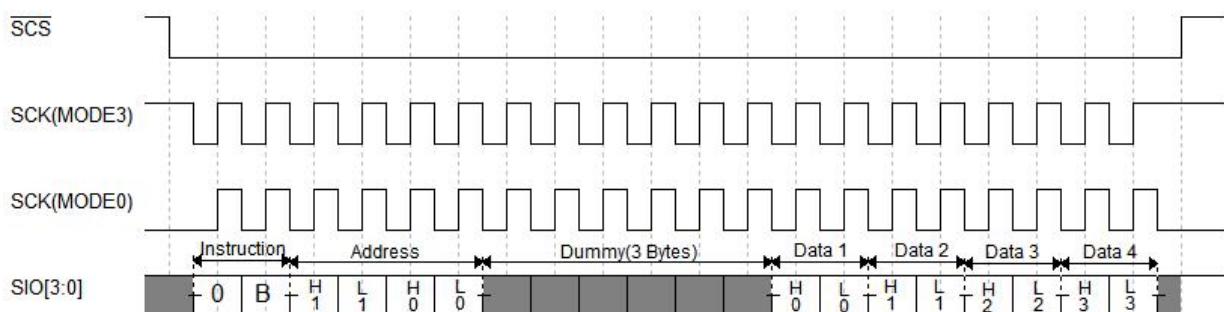

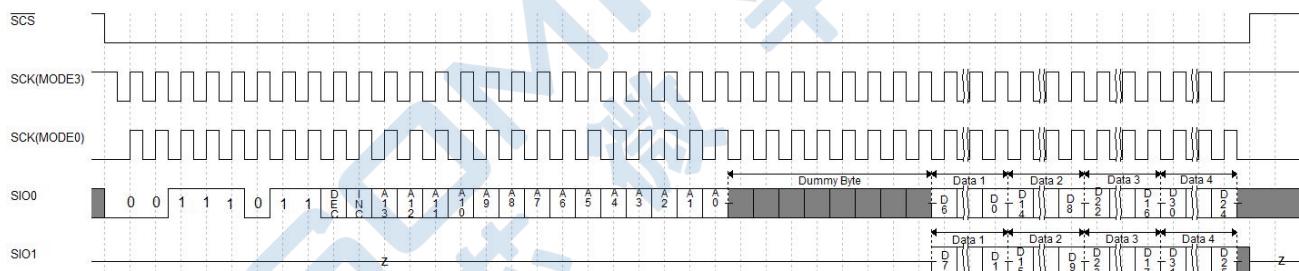

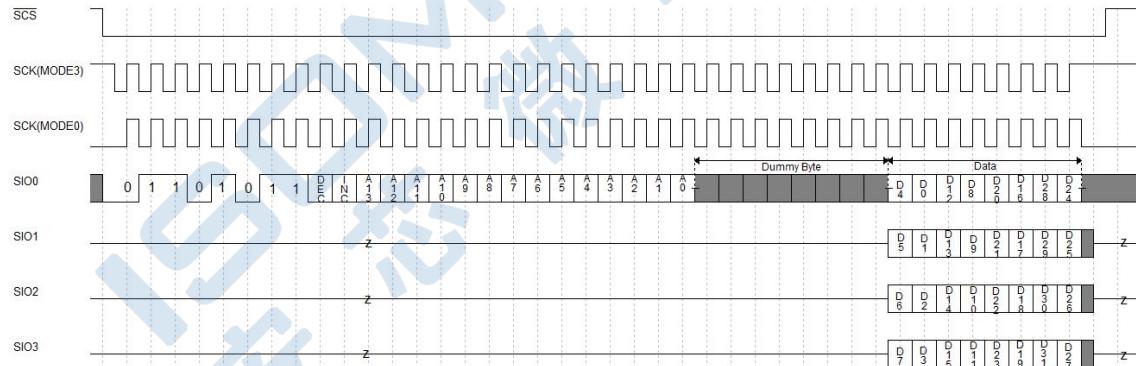

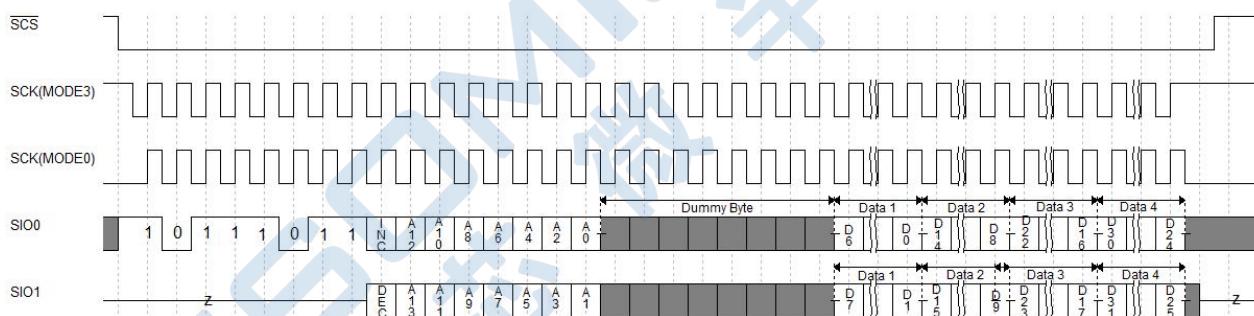

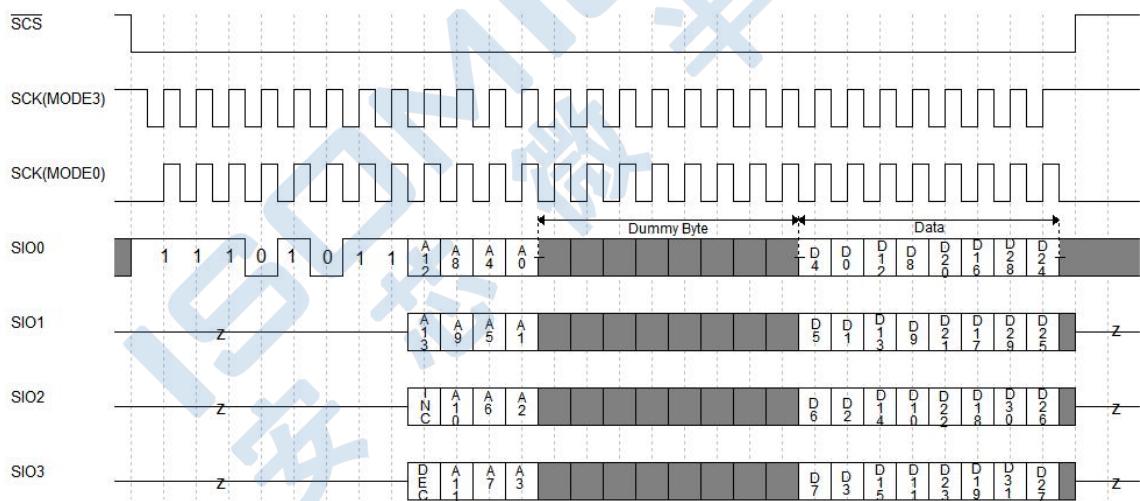

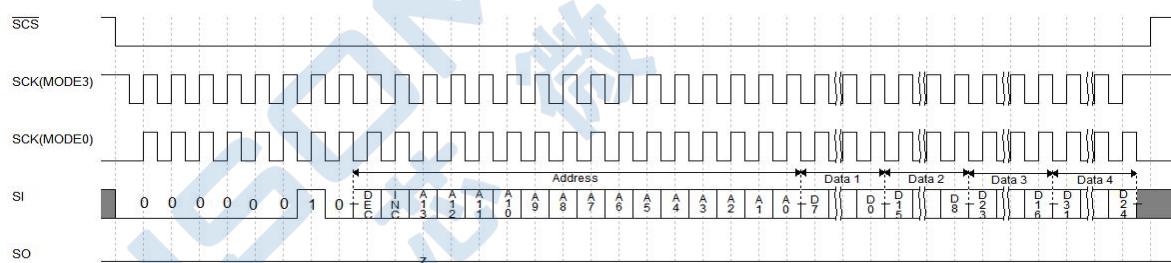

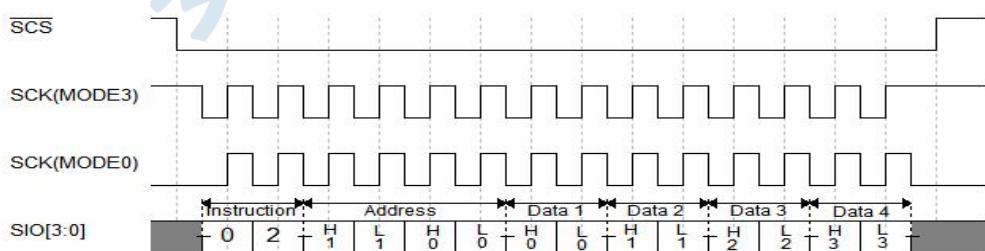

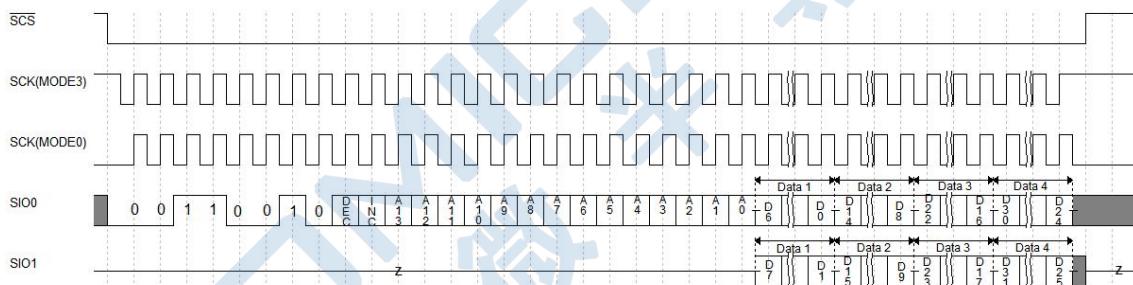

- SPI 接口模式

- 支持 SPI Mode0/Mode3

- 最高 42MHz

- 支持 SPI/DPI/QPI

- 支持 16 个 GPIO

- Digital IO 模式

- 支持 16 个 Digital I/O

- EEPROM 配置 Digital IO 方向

- EEPROM 配置输出/输入触发事件

- 支持 Push-Pull 和 Open-Drain

## 应用场景

- 电机运动控制

- 过程/工厂自动化

- 通信模块

- 传感器接口卡

- 液压与气动阀门系统

## 订购信息

| 外形                                                                                  | 产品型号         | 封装        | 字印                        | 包装 | 数量  |

|-------------------------------------------------------------------------------------|--------------|-----------|---------------------------|----|-----|

|  | ISN8221-GMIT | LGA-64pin | ISN8221<br>/YYWW<br>(二维码) | 盘装 | 260 |

## 1. 概述

ISN8221 是一款带有双集成以太网 PHY 的 2 端口 EtherCAT 从站控制器, 每个 PHY 包含一个全双工 100BASE-TX 收发器, 并支持 100Mbps 的通信速率。ISN8221 包括一个 8K Byte 双端口 RAM、4 个同步管理器 (SM) 和 3 个现场总线内存管理单元 (FMMU) 。

现场总线内存管理单元 (FMMU) 实现了逻辑地址到物理地址的映射功能, 从而 EtherCAT 主站可以通过逻辑地址访问不同 EtherCAT 从站的寄存器和过程数据。

同步管理器 (SM) 实现了 EtherCAT 主站和从站之间的数据交换功能, 并由 EtherCAT 主站控制数据交换的方向和操作模式。同步管理器 (SM) 支持的操作模式包括: 缓冲 (Buffered) 模式和邮箱 (Mailbox) 模式。

- **缓冲 (Buffered) 模式**

在缓冲 (Buffered) 模式下, 本地微控制器 (MCU) 和 EtherCAT 主站可以直接访问缓冲区的数据, 主要用于周期性过程数据的交换。

- **邮箱 (Mailbox) 模式**

在邮箱 (Mailbox) 模式下, 本地微控制器 (MCU) 和 EtherCAT 主站需要通过握手机制来访问缓冲区的数据, 确保不会丢失数据。

ISN8221 包含一个 64 位分布式时钟, 以实现高精度时间同步, 并为定时采集本地数据提供准确的计时信息。

ISN8221 实现了 8/16 bit 主机总线接口(HBI) 和 SPI 接口。本地微控制器 (MCU) 无法直接访问 EtherCAT 从站寄存器, 需通过以上控制接口操作 ISN8221 的系统控制寄存器和两个过程数据 FIFO 来间接访问 EtherCAT 从站寄存器。

主机总线接口(HBI) 支持以下模式:

- 索引寄存器访问模式(HBI Index): 该模式实现了 3 组索引/数据寄存器, 微控制器 (MCU) 需要先往索引寄存器写入目标寄存器的地址, 然后通过读写相应的数据寄存器来访问目标寄存器。

- 地址数据复用访问模式(HBI Multiplexed): 该模式支持接口的地址与数据复用, 微控制器 (MCU) 可直接访问目标寄存器。

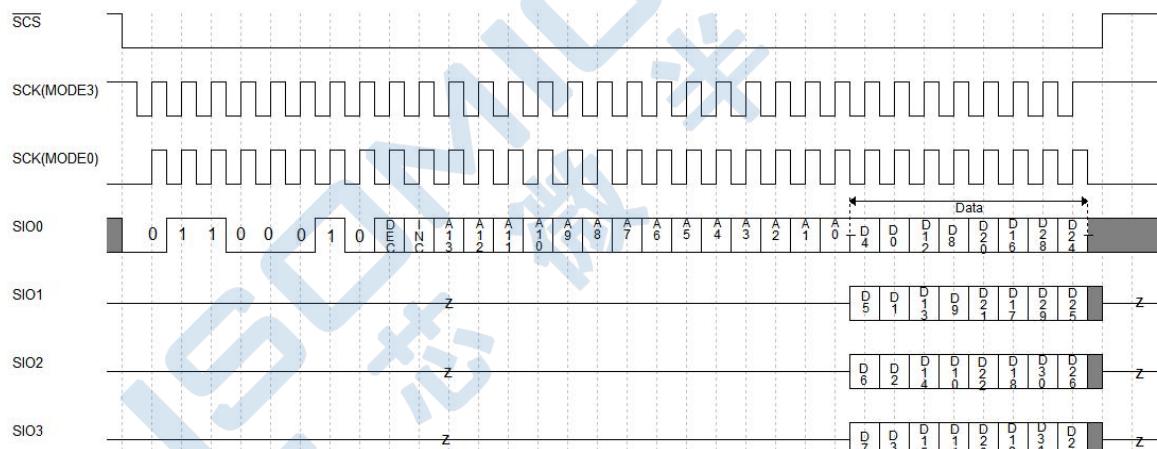

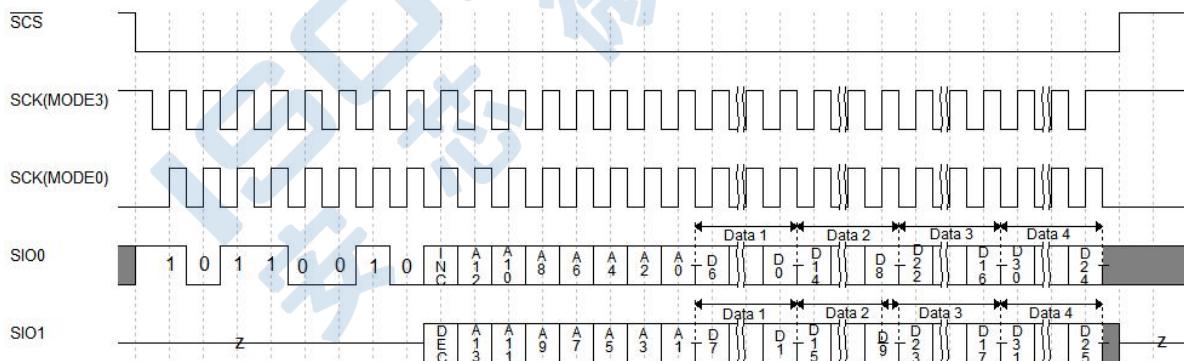

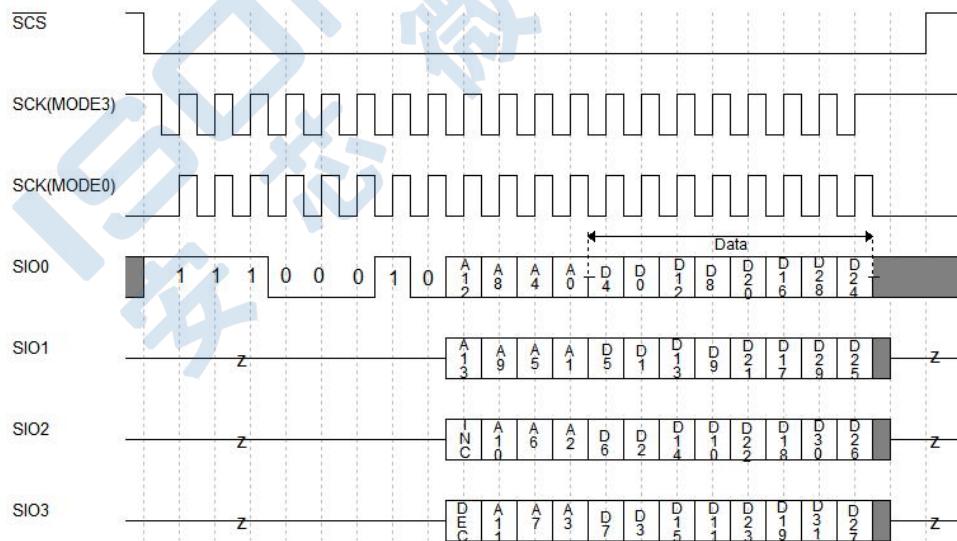

SPI 接口支持一次性读写单个或多个寄存器。当一次性读写多个寄存器时, 寄存器的地址可配置为递增、递减或固定模式, 当寄存器的地址处于固定模式时, 将多次读写同一个寄存器。SPI 接口支持单线、双线和四线通信, 通信时钟频率高达 42 MHz。

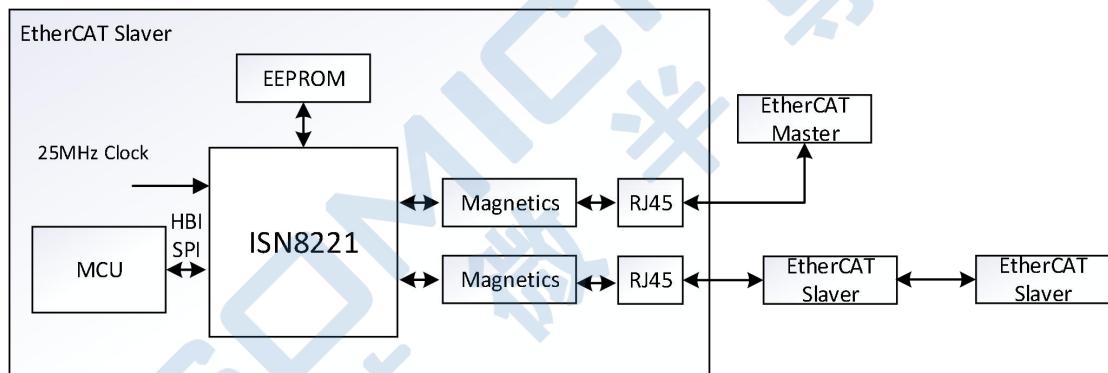

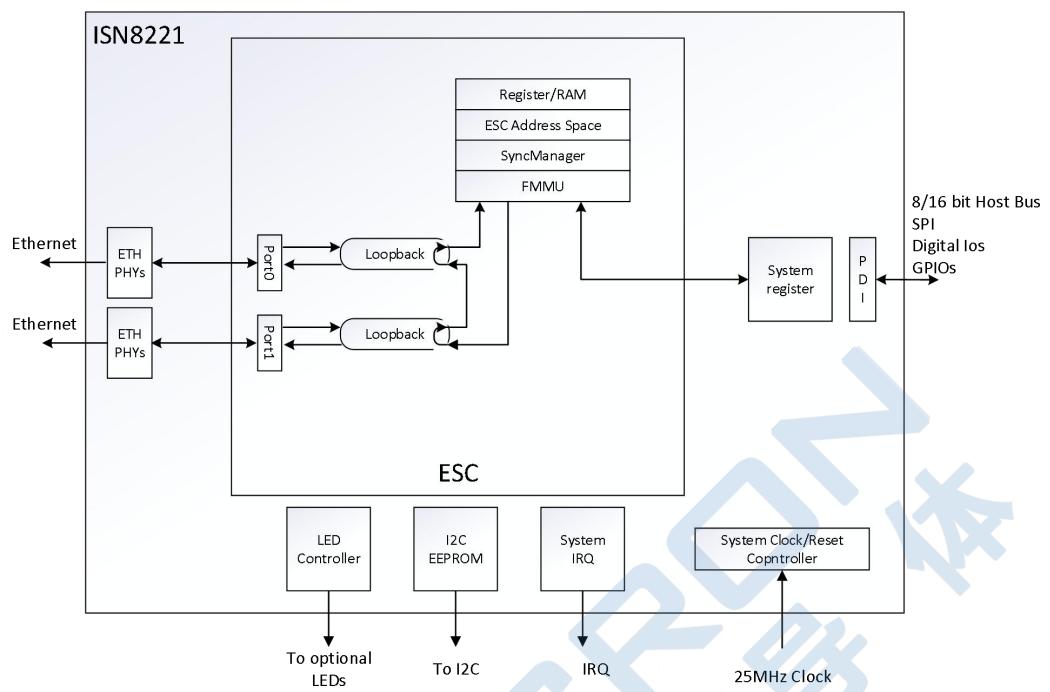

图 1-1 详细说明了一个典型系统应用, 而图 1-2 提供了 ISN8221 的内部框图。

图 1-1 系统模块框图

图 1-2 内部模块框图

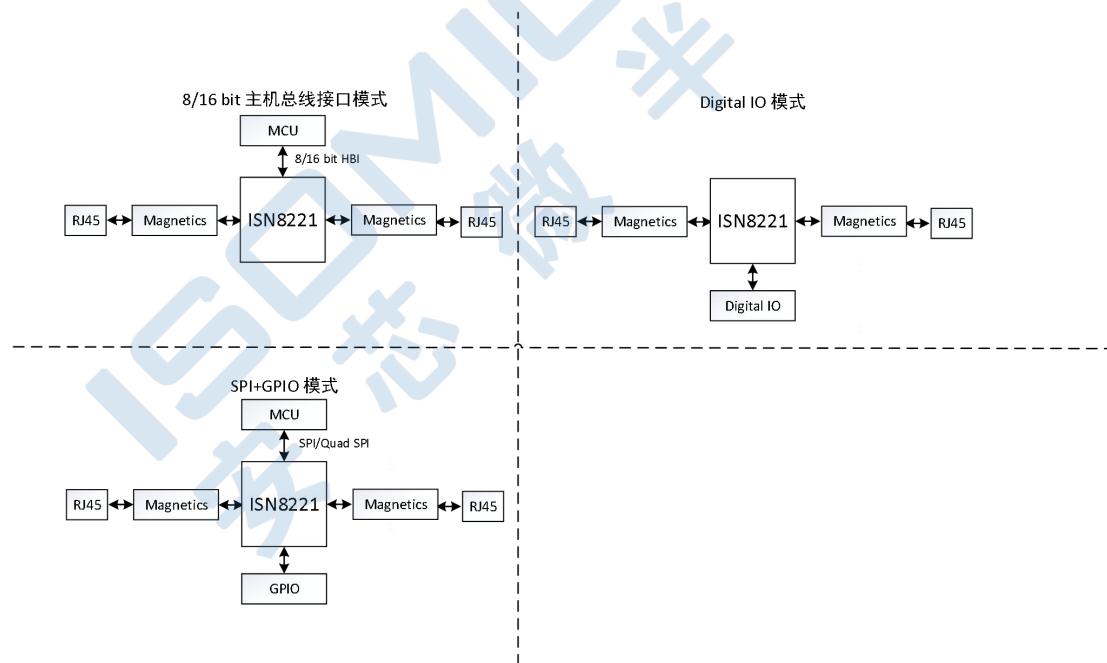

ISN8221 包含 3 种工作模式：8/16 bit 主机总线接口(HBI)模式、SPI+GPIO 模式、Digital I/O 模式，其中 Digital I/O 模式无需额外的微控制器(MCU)，如图 1-3：

- 8/16 bit 主机总线接口(HBI)模式：该模式下，微控制器可通过 8/16 bit 主机总线接口(HBI) 访问 ISN8221 内部寄存器，该模式提供了并行的数据访问模式，提高了数据访问效率。

- SPI+GPIO 模式：该模式下，微控制器可通过单线/双线/四线 SPI 接口访问 ISN8221 内部寄存器，该模式适用于没有并行接口的微控制器(MCU)，节省了微控制器 MCU 的接口。

- Digital I/O 模式：该模式下，无需额外的微控制器(MCU)，可实现成简单的数字 I/O 模块，模块可包含 16 个 Digital IO，每个 Digital IO 都可以单独配置成输入/输出模式下运行；16 个 Digital IO 可由 EtherCAT 主站控制；ISN8221 还提供了 6 个 Digital IO 的控制信号。

图 1-3 ISN8221 操作模式

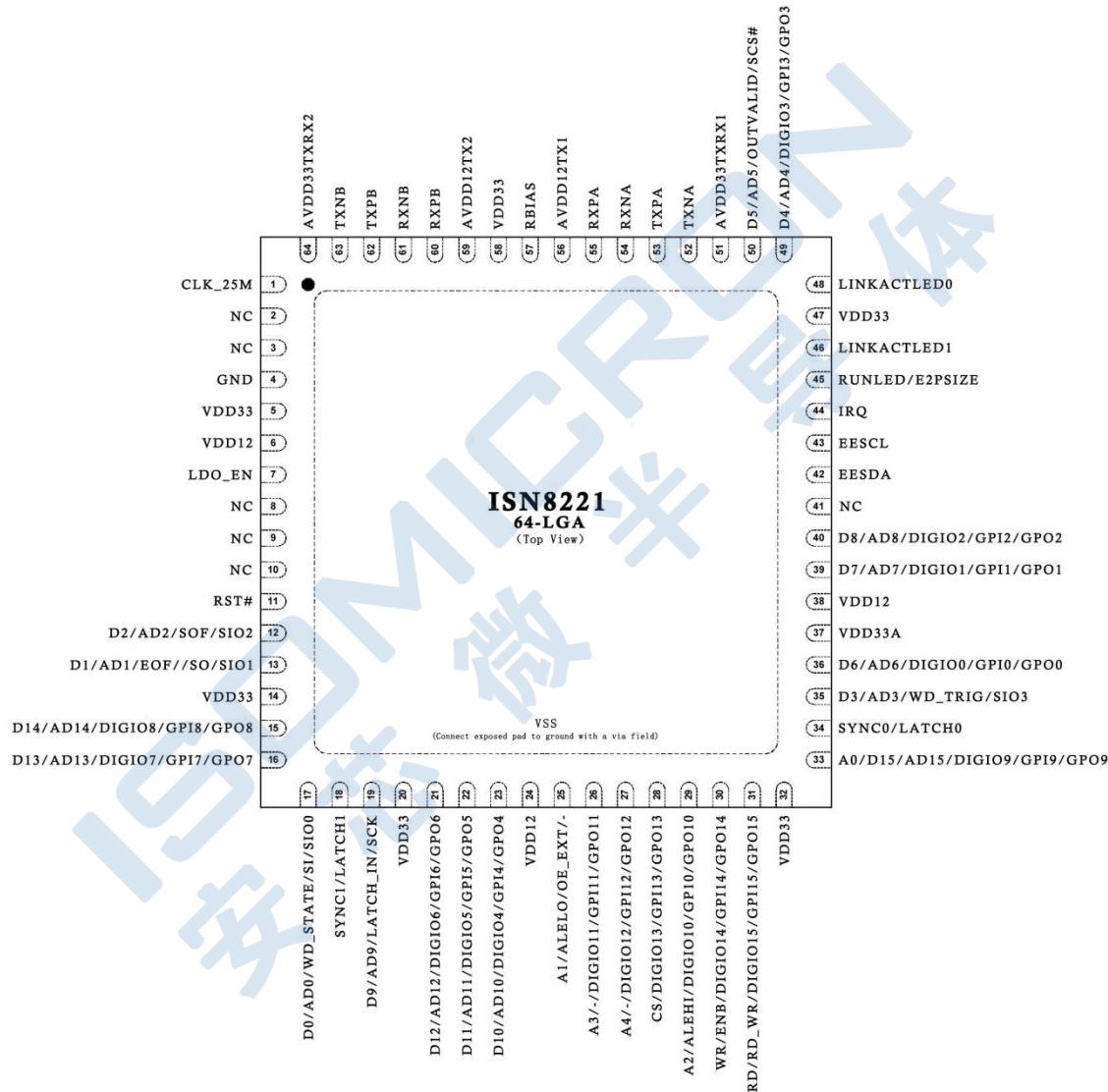

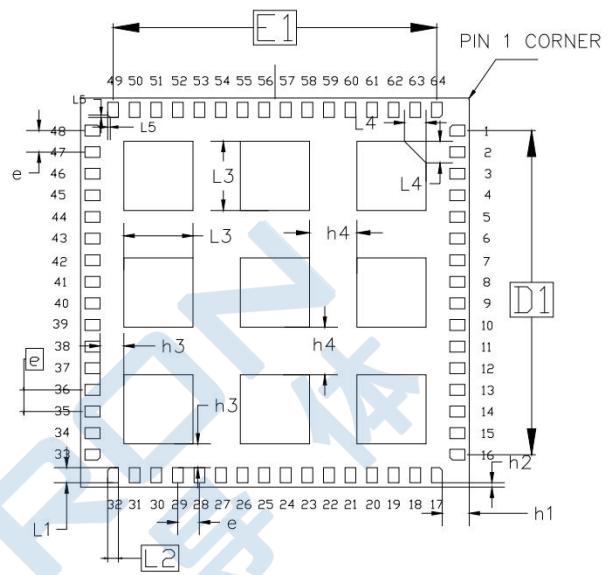

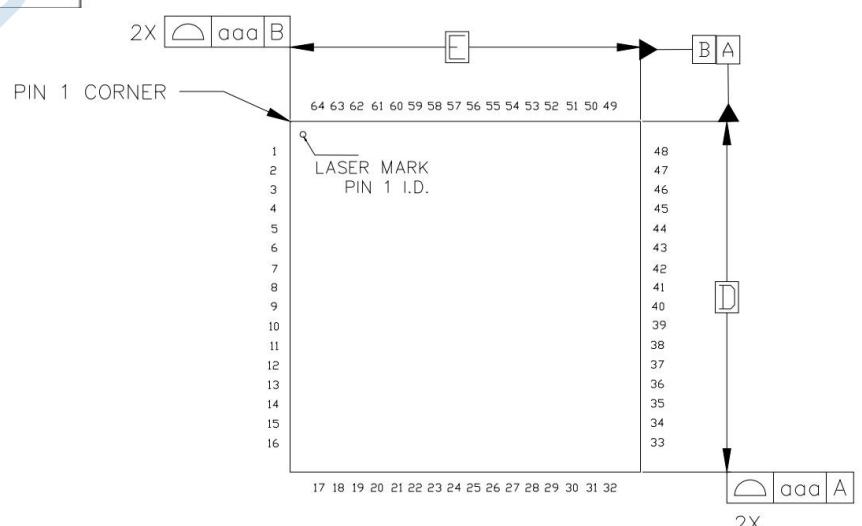

## 2 管脚描述

### 2.1 LGA-64 封装管脚

图 2-1 ISN8221 LGA-64 封装管脚

表 2-1 以表格形式详细列出了 ISN8221 64-LGA 封装的管脚分配。某些管脚的功能可能会根据芯片的运行模式而改变。对于某个特定管脚在某些模式下无功能的情况，表格单元格将标记为 “-”。

表 2-1 ISN8221 管脚分配

| 管脚号 | 寄存器索引 | 地址数据复用  | Digital IO | SPI       |

|-----|-------|---------|------------|-----------|

| 1   |       | CLK_25M |            |           |

| 2   |       |         | -          |           |

| 3   |       |         | -          |           |

| 4   |       | GND     |            |           |

| 5   |       | VDD33   |            |           |

| 6   |       | VDD12   |            |           |

| 7   |       | LDO_EN  |            |           |

| 8   |       |         | -          |           |

| 9   |       |         | -          |           |

| 10  |       |         | -          |           |

| 11  |       | RST#    |            |           |

| 12  | D2    | AD2     | SOF        | SIO2      |

| 13  | D1    | AD1     | EOF        | SO/SIO1   |

| 14  |       | VDD33   |            |           |

| 15  | D14   | AD14    | DGPIO8     | GPI8/GPO8 |

| 16  | D13   | AD13    | DGPIO7     | GPI7/GPO7 |

| 17  | D0    | AD0     | WD_STATE   | SI/SIO0   |

| 18  |       |         | -          |           |

| 19  | D9    | AD9     | LATCH_IN   | SCK       |

| 20  |       | VDD33   |            |           |

| 21  | D12   | AD12    | DGPIO6     | GPI6/GPO6 |

| 22  | D11   | AD11    | DGPIO5     | GPI5/GPO5 |

| 23  | D10   | AD10    | DGPIO4     | GPI4/GPO4 |

| 24  |       | VDD12   |            |           |

| 25  | A1    | ALELO   | OE_EXT     | -         |

|    |                |       |          |             |

|----|----------------|-------|----------|-------------|

| 26 | A3             | -     | DIGIO11  | GPI11/GPO11 |

| 27 | A4             | -     | DIGIO12  | GPI12/GPO12 |

| 28 | CS             |       | DIGIO13  | GPI13/GPO13 |

| 29 | A2             | ALEHI | DIGIO10  | GPI10/GPO10 |

| 30 | WR/ENB         |       | DIGIO14  | GPI14/GPO14 |

| 31 | RD/RD_WR       |       | DIGIO15  | GPI15/GPO15 |

| 32 | VDD33          |       |          |             |

| 33 | A0/D15         | AD15  | DIGIO9   | GPI9/GPO9   |

| 34 | SYNC0          |       |          |             |

| 35 | D3             | AD3   | WD_TRIG  | SIO3        |

| 36 | D6             | AD6   | DIGIO0   | GPI0/GPO0   |

| 37 | VDD33A         |       |          |             |

| 38 | VDD12          |       |          |             |

| 39 | D7             | AD7   | DIGIO1   | GPI1/GPO1   |

| 40 | D8             | AD8   | DIGIO2   | GPI2/GPO2   |

| 41 | -              |       |          |             |

| 42 | EESDA          |       |          |             |

| 43 | EESCL          |       |          |             |

| 44 | IRQ            |       |          |             |

| 45 | RUNLED/E2PSIZE |       |          |             |

| 46 | LINKACTLED1    |       |          |             |

| 47 | VDD33          |       |          |             |

| 48 | LINKACTLED0    |       |          |             |

| 49 | D4             | AD4   | DIGIO3   | GPI3/GPO3   |

| 50 | D5             | AD5   | OUTVALID | SCS#        |

| 51 | AVDD33TXRX1    |       |          |             |

| 52 | TXNA           |       |          |             |

| 53 | TXPA           |       |          |             |

| 54 | RXNA           |       |          |             |

|                |             |

|----------------|-------------|

| 55             | RXPA        |

| 56             | AVDD12TX1   |

| 57             | RBIAS       |

| 58             | VDD33       |

| 59             | AVDD12TX2   |

| 60             | RXPB        |

| 61             | RXNB        |

| 62             | TXPB        |

| 63             | TXNB        |

| 64             | AVDD33TXRX2 |

| Exposed<br>PAD | GND         |

## 2.2 管脚描述

本节包含对 ISN8221 各个管脚的描述。管脚描述已按功能组分类，如下所示：

- 网口 Port 0 管脚描述

- 网口 Port 1 管脚描述

- 网口 Port 0 和 Port 1 电源及公共管脚描述

- 主机总线接口(HBI)管脚描述

- SPI 管脚描述

- EtherCAT 分布式时钟管脚描述

- EtherCAT Digital I/O 和 GPIO 管脚描述

- EEPROM 管脚描述

- LED 和配置管脚描述

- 通用管脚描述

- 核心和 I/O 电源管脚描述

表 2.2 网口 Port 0 管脚描述

| 管脚数 | 管脚名  | IO 类型 | 描述                            |

|-----|------|-------|-------------------------------|

| 1   | TXPA | AIO   | 网口 Port 0 双绞线发送/接收差分对 通道 1 正极 |

| 1   | TXNA | AIO   | 网口 Port 0 双绞线发送/接收差分对 通道 1 负极 |

| 1   | RXPA | AIO   | 网口 Port 0 双绞线发送/接收差分对 通道 2 正极 |

| 1   | RXNA | AIO   | 网口 Port 0 双绞线发送/接收差分对 通道 2 负极 |

表 2.3 网口 Port 1 管脚描述

| 管脚数 | 管脚名  | IO 类型 | 描述                            |

|-----|------|-------|-------------------------------|

| 1   | TXPB | AIO   | 网口 Port 1 双绞线发送/接收差分对 通道 1 正极 |

| 1   | TXNB | AIO   | 网口 Port 1 双绞线发送/接收差分对 通道 1 负极 |

| 1   | RXPB | AIO   | 网口 Port 1 双绞线发送/接收差分对 通道 2 正极 |

| 1   | RXNB | AIO   | 网口 Port 1 双绞线发送/接收差分对 通道 2 负极 |

表 2.4 网口 Port 0 和 Port 1 电源及公共管脚描述

| 管脚数 | 管脚名         | IO 类型 | 描述                                                           |

|-----|-------------|-------|--------------------------------------------------------------|

| 1   | RBIAS       | AI    | 用于内部偏置电路。外部连接 $6.19\text{ k}\Omega\pm1\%$ 的电阻到地              |

| 1   | AVDD33TXRX1 | P     | 详细细节参考 <b>第3章 电源连接</b>                                       |

| 1   | AVDD33TXRX2 | P     | 详细细节参考 <b>第3章 电源连接</b>                                       |

| 1   | AVDD12TX1   | P     | 此管脚由外部 1.2V 电源或通过 PCB 从芯片的内部稳压器供电。<br>详细细节参考 <b>第3章 电源连接</b> |

| 1   | AVDD12TX2   | P     | 此管脚由外部 1.2V 电源或通过 PCB 从芯片的内部稳压器供电。<br>详细细节参考 <b>第3章 电源连接</b> |

表 2.5 主机总线接口(HBI)管脚描述

| 管脚数 | 管脚名     | IO 类型 | 描述                                                                                                                                                                |

|-----|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RD      | DI    | 该管脚是主机总线读取选通，通常为低电平有效；极性可以通过 EtherCAT 从站寄存器 <b>PDI Configuration Register(HBI Modes)</b> 的 <b>HBI Read, Read/Write Polarity</b> 位改变                               |

|     | RD_WR   | DI    | 该管脚为主机总线方向控制管脚。与 ENB 管脚配合使用时，可指示读或写操作。常规极性为：1 时表示读取，0 时表示写入 (R/nW)；极性可以通过 <b>PDI Configuration Register(HBI Modes)</b> 的 <b>HBI Read, Read/Write Polarity</b> 位改变 |

| 1   | WR      | DI    | 该管脚为主机总线写入选通。通常为低电平有效；极性可以通过 EtherCAT 从站寄存器 <b>PDI Configuration Register(HBI Modes)</b> 的 <b>HBI Write, Enable Polarity</b> 位改变                                  |

|     | ENB     | DI    | 该管脚是主机总线数据使能选通。与 RD_WR 管脚配合使用时，它表示操作的数据阶段。通常为低电平有效<br>极性可以通过 EtherCAT 从站寄存器 <b>PDI Configuration Register(HBI Modes)</b> 的 <b>HBI Write, Enable Polarity</b> 位改变  |

| 1   | CS      | DI    | 该管脚是主机总线片选信号，表示芯片已被选中进行当前的数据传输，通常为低电平有效。极性可以通过 EtherCAT 从站寄存器 <b>PDI Configuration Register(HBI Modes)</b> 的 <b>HBI Chip Select Polarity</b> 位改变                  |

| 5   | A[4:0]  | DI    | 这些管脚在索引寄存器模式下提供地址信号。在 16 位数据模式下，Bit 0 不被使用。                                                                                                                       |

| 16  | D[15:0] | DIO   | 这些管脚是在索引寄存器模式下的主机总线接口的数据信号。                                                                                                                                       |

|   |          |     |                                                                                                                                                                                                 |

|---|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |          |     | 在 8 位数据模式下, 不使用 Bit 15-8                                                                                                                                                                        |

|   | AD[15:0] | DIO | 这些管脚是用于地址数据复用模式的主机总线接口的地址/数据信号。在单相地址复用模式下, 位 15-8 提供地址的高字节。位 7-0 提供地址的低字节; 在双相地址复用模式下 位 7-0 提供地址的高字节和低字节; 在 8 位数据双相地址复用模式下, 不使用 Bit 15-8                                                        |

| 1 | ALEHI    | DI  | 该管脚用于地址数据复用模式下的地址锁存。在双相复用地址模式中, 它用于加载高地址字节。通常为低电平有效 (地址在上升沿保存) 极性可以通过 EtherCAT 从站寄存器 <b>PDI Configuration Register(HBI Modes)</b> 的 <b>HBI ALE Polarity</b> 位改变                                 |

| 1 | ALELO    | DI  | 该管脚用于地址数据复用模式下的地址锁存。在单阶段复用地址模式下, 它用于加载两个地址字节; 在双阶段复用地址模式下, 它用于加载低地址字节。<br>通常为低电平有效 (地址在上升沿保存), 极性可以通过 EtherCAT 从站寄存器 <b>PDI Configuration Register(HBI Modes)</b> 的 <b>HBI ALE Polarity</b> 位改变 |

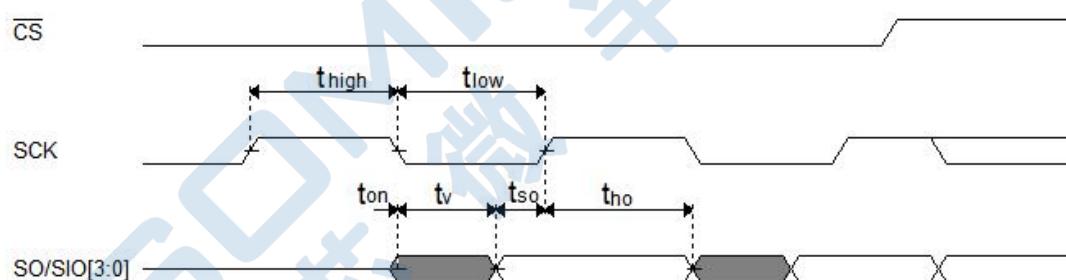

表 2.6 SPI 管脚描述

| 管脚数 | 管脚名      | IO 类型   | 描述                                                     |

|-----|----------|---------|--------------------------------------------------------|

| 1   | SCS      | DI(PU)  | SPI 片选输入。当为低电平时，选择 SPI 进行 SPI 传输。当为高电平时，SPI 串行数据输出为三态。 |

| 1   | SCK      | DI(PU)  | SPI 串行时钟输入                                             |

| 4   | SIO[3:0] | DIO(PU) | 多比特 I/O 的 SPI 数据输入和输出。                                 |

|     | SI       | DI(PU)  | SPI 串行数据输入，与 SIO[0] 管脚复用                               |

|     | SO       | DO(PU)  | SPI 串行数据输出，与 SIO[1] 管脚复用                               |

表 2.7 EtherCAT 分布式时钟管脚描述

| 管脚数 | 管脚名   | IO 类型 | 描述                 |

|-----|-------|-------|--------------------|

| 1   | SYNC0 | DO    | 分布式时钟同步信号输出(Sync0) |

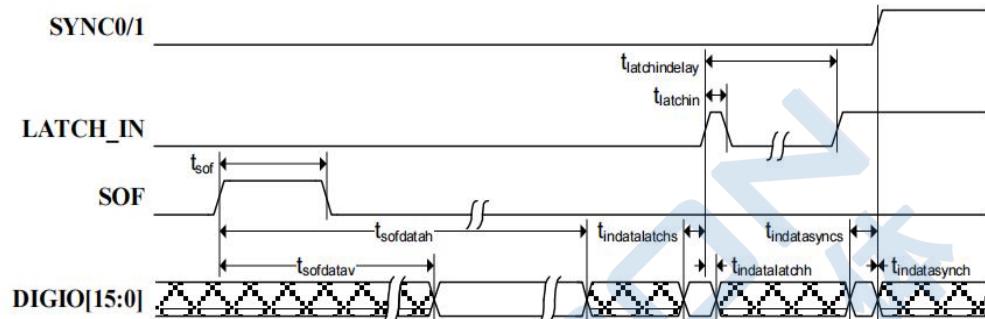

表 2.8 EtherCAT Digital I/O 和 GPIO 管脚描述

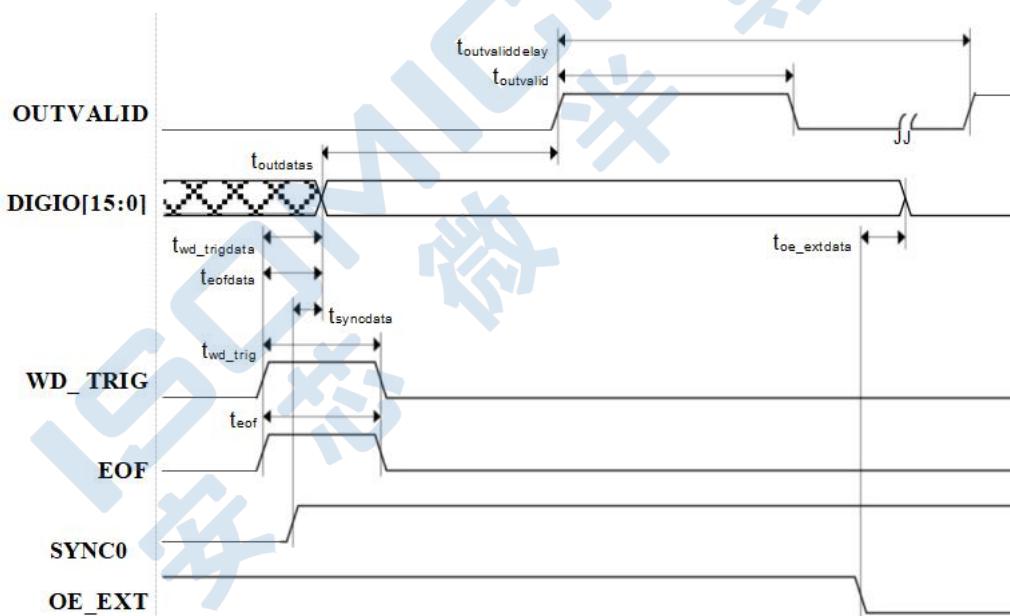

| 管脚数 | 管脚名         | IO 类型 | 描述                                                                                      |

|-----|-------------|-------|-----------------------------------------------------------------------------------------|

| 16  | GPI[15:0]   | DI    | 这些管脚是通用输入管脚，直接映射到 EtherCAT 从站寄存器 <b>General Purpose Inputs Register</b> 中。GPI 的一致性无法保证。 |

| 16  | GPO[15:0]   | DO    | 这些管脚是通用输出管脚，由 EtherCAT 从站寄存器 <b>General Purpose Outputs Register</b> 驱动，且不带看门狗保护。       |

| 16  | DIGIO[15:0] | DIO   | 这些管脚是输入/输出或者双向数据                                                                        |

| 1   | OUTVALID    | DO    | 此管脚表示输出数据有效，可以捕获到外部寄存器中。                                                                |

| 1   | LATCH_IN    | DI    | 该管脚为外部数据锁存信号。每当识别到 LATCH_IN 的上升沿                                                        |

|   |            |    |                                  |

|---|------------|----|----------------------------------|

|   |            |    | 时, 将对输入数据进行采样。                   |

| 1 | WD_TRIGGER | DO | 此管脚为同步管理器(SM)看门狗触发输出。            |

| 1 | WD_STATE   | DO | 此管脚为同步管理器(SM)看门狗状态输出。0 表示看门狗已过期。 |

| 1 | SOF        | DO | 此管脚为帧起始输出, 指示以太网/EtherCAT 帧的开始。  |

| 1 | EOF        | DO | 此管脚为帧结束输出, 表示以太网/EtherCAT 帧的结束。  |

| 1 | OE_EXT     | DI | 该管脚为输出使能输入管脚。当为低电平时, 它会清除输出数据。   |

表 2.9 EEPROM 管脚描述

| 管脚数 | 管脚名   | IO 类型 | 描述                                   |

|-----|-------|-------|--------------------------------------|

| 1   | EESDA | DIO   | 当芯片访问外部 EEPROM 时, 此管脚为 I2C 串行数据输入输出。 |

| 1   | EESCL | DO    | 当芯片访问外部 EEPROM 时, 此管脚为 I2C 串行时钟输出    |

表 2.10 LED 和配置管脚描述

| 管脚数 | 管脚名             | IO 类型 | 描述                                                            |

|-----|-----------------|-------|---------------------------------------------------------------|

| 1   | LINKACTL<br>ED0 | DO    | 此管脚是网口 Port 0 的链路/活动 LED 输出 (熄灭=无链路, 常亮=有链路但无活动, 闪烁=有链路且有活动)。 |

| 1   | LINKACTL<br>ED1 | DO    | 此管脚是网口 Port 1 的链路/活动 LED 输出 (熄灭=无链路, 常亮=有链路但无活动, 闪烁=有链路且有活动)。 |

|   |         |    |                                                                                                                                                                           |

|---|---------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | RUNLED  | DO | 此管脚为运行 LED 输出,由 EtherCAT 从站寄存器 <b>AL Status Register</b> 控制。                                                                                                              |

| 1 | E2PSIZE | DI | <p>该管脚用于配置 EEPROM 的容量大小, 在 POR 复位激活时锁定配置值。</p> <p>当管脚为低电平时, 选择 1K bit (128 x 8) 至 16K bit (2K x 8) 的容量。</p> <p>当管脚为高电平时, 选择 32K bit (4K x 8) 至 4M bit (512K x 8) 的容量。</p> |

表 2.11 通用管脚描述

| 管脚数 | 管脚名     | IO 类型 | 描述                                                                    |

|-----|---------|-------|-----------------------------------------------------------------------|

| 1   | IRQ     | DO    | 中断请求输出。该信号的极性、来源和缓冲区类型可通过系统寄存器 <b>IRQ_CFG</b> 来配置调整。                  |

| 1   | RST#    | DI    | 作为输入, 此管脚低电平复位芯片。                                                     |

| 1   | LDO_EN  | AI    | 连接到 3.3V 时, 使能内部 1.2V 稳压器。连接到 GN 时 D, 禁用内部 1.2V 稳压器, 采用外部 1.2V 直接供电模式 |

| 1   | CLK_25M | ICLK  | 外部 25 MHz 晶振时钟输入。该信号一般由外部有源晶振输出的单端时钟驱动。                               |

表 2.12 核心和 I/O 电源管脚描述

| 管脚数 | 管脚名    | IO 类型 | 描述                                                      |

|-----|--------|-------|---------------------------------------------------------|

| 6   | VDD33  | P     | 3.3 V 电源输入管脚, 为内部 1.2V 稳压器提供 3.3V 输入电压, 以及芯片的 3.3V 电源供电 |

| 1   | VDD33A | P     | 3.3V 电源输入管脚, 为片内 PLL 以及模拟电路提供 3.3V 电源供电                 |

|   |       |   |                                                                                                                      |

|---|-------|---|----------------------------------------------------------------------------------------------------------------------|

| 3 | VDD12 | P | 当 REG_EN 接 3.3V 电源时, 使能片内 1.2V 稳压器, 此管脚应通过去耦电容接低;<br>当 REG_EN 接地时, 禁用片内 1.2V 稳压器, 此管脚应与外部 1.2V 电源相连, 为芯片的 1.2V 提供电源。 |

| 1 | GND   | P | 公共接地。此裸露焊盘必须通过过孔阵列连接到地                                                                                               |

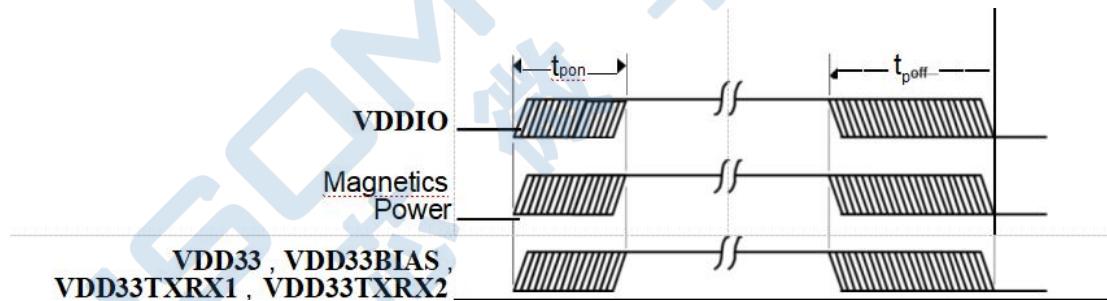

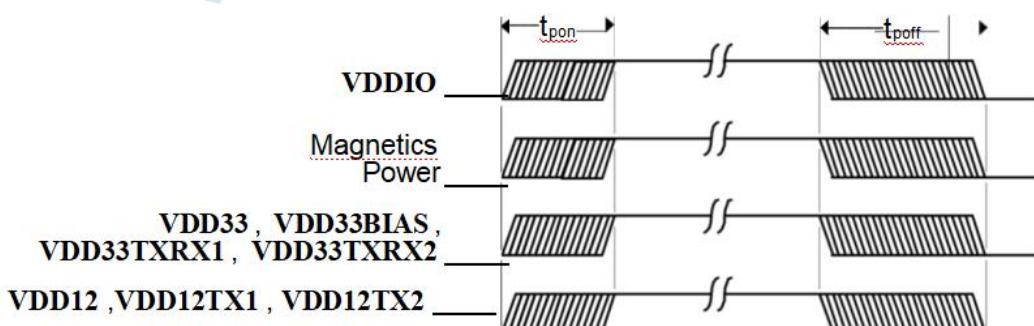

### 3 电源连接

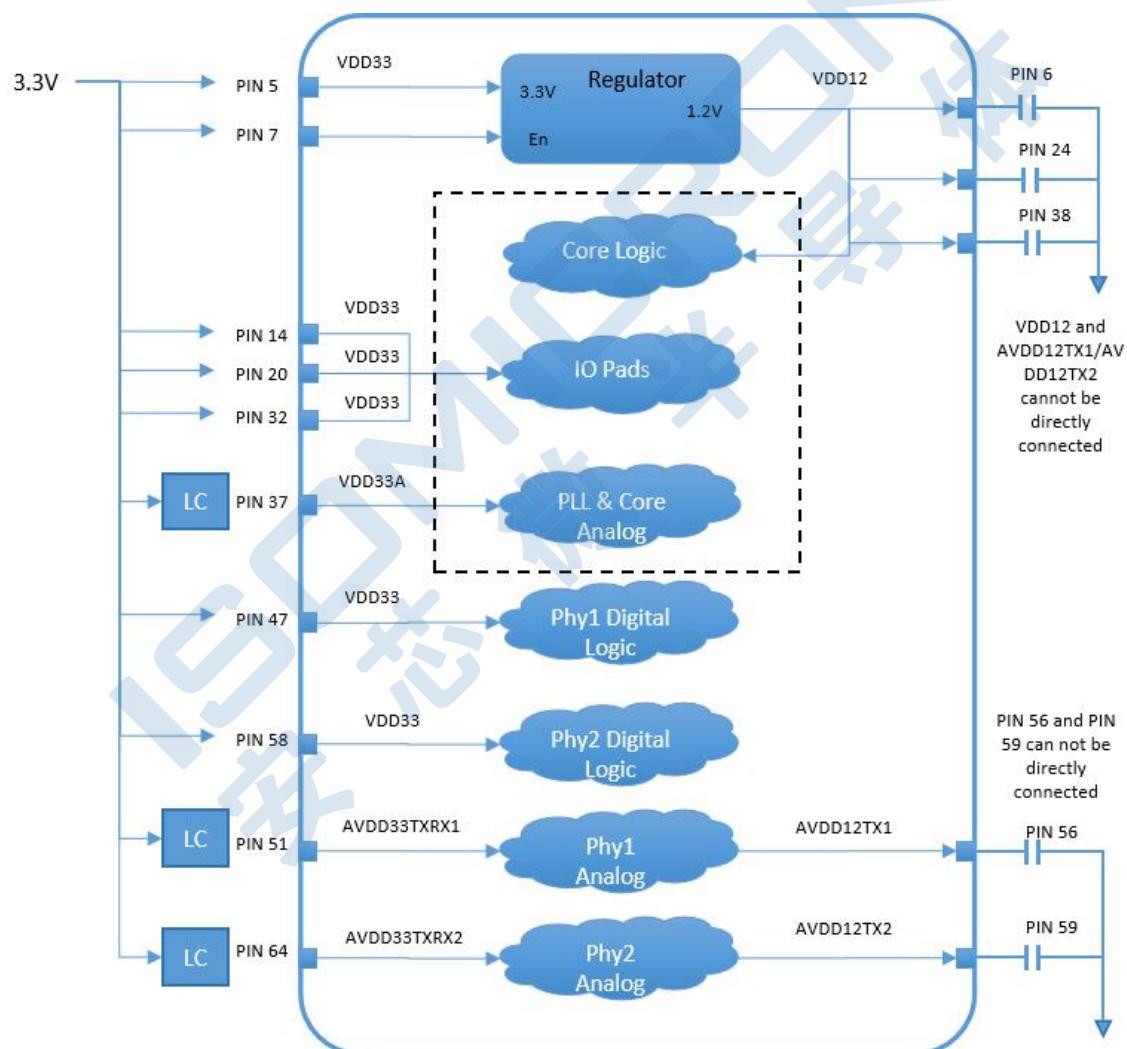

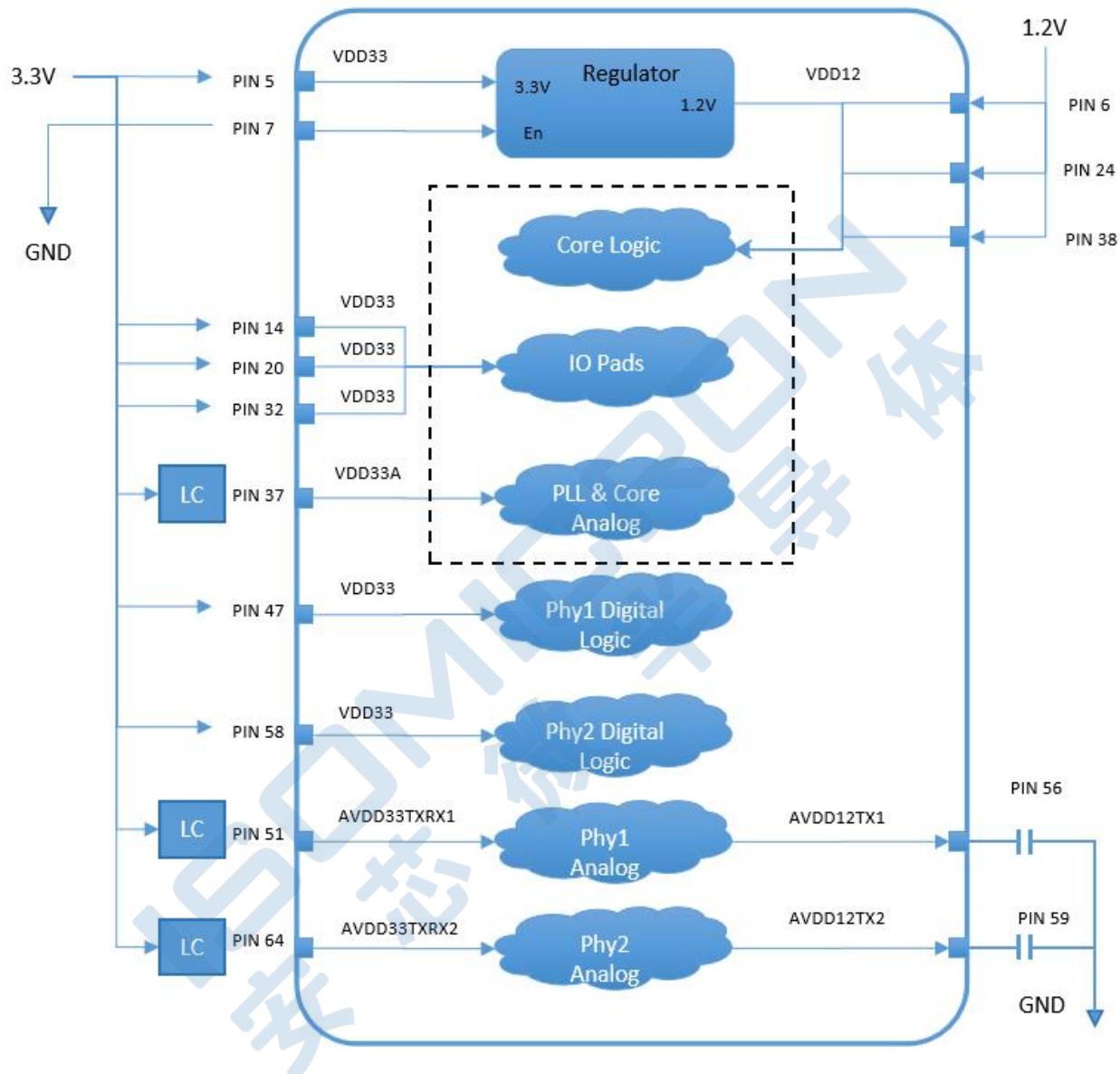

图 3-1 和图 3-2 分别显示了内部稳压器启用和禁用情况下的芯片电源连接关系。第 3.1 节提供了有关芯片内部稳压器的更多信息。

图 3-1 启用稳压器的电源连接

图 3-2 禁用稳压器的电源连接

### 3.1 内部稳压器

ISN8221 包含三个内部的 1.2V 稳压器：

- 1.2V 核心电压稳压器

- 1.2V PHY1 稳压器

- 1.2V PHY2 稳压器

#### 3.1.1 1.2 V 核心稳压器

核心电压稳压器为芯片提供 1.2V 电压。

当 REG\_EN 输入管脚连接到 3.3V 时, 开启片内 1.2V 核心电压稳压器, 并且在 VDD33 管脚上接收 3.3V 电压。

稳压器相关的 VDD12 管脚需对地并联 1 颗 0.1  $\mu$ F 的电容。

当 REG\_EN 输入管脚连接到 VSS 时, 禁用片内 1.2V 核心电压稳压器。并且在 VDD33 管脚上接收 3.3V 电压。

此时, 芯片内部的 1.2V 核心电压必须由 VDD12 管脚接到板上的 1.2V 来供电。

#### 3.1.2 1.2 V PHY1 稳压器

PHY1 稳压器为 PHY1 的模拟电路提供 1.2V 电压。

#### 3.1.3 1.2 V PHY2 稳压器

PHY2 稳压器为 PHY2 的模拟电路提供 1.2V 电压。

## 4. 时钟复位

### 4.1 时钟

ISN8221 通过芯片管脚 CLK\_25M 提供单端的系统时钟输入，通过 PLL 为系统提供 100MHz 的主时钟，以及内部 Phy 的时钟。

芯片的 CLK\_25M 管脚需外接 1 个固定频率 25MHz 有源晶振，给芯片提供时钟输入。目前暂不支持外部无源晶振的时钟输入。

## 4.2 复位

ISN8221 提供多种硬件和软件复位源, 允许对芯片的不同层级进行复位。所有复位可以分为以下三个复位类型, 具体描述见以下章节:

- 芯片级复位

- 上电复位 (POR)

- RST# 管脚复位

- 多模块复位

- 数字复位 (DIGITAL\_RST)

- 单模块复位

- 端口 A PHY 复位 (PHY\_A\_RST)

- 端口 B PHY 复位 (PHY\_B\_RST)

- EtherCAT 控制器复位 (ETHERCAT\_RST)

表 4-1 总结了各种复位源对 ISN8221 各个模块的影响。有关这些复位类型的详细信息, 请参阅以下章节。

本章节主要介绍芯片级复位, 关于多模块和单模块复位控制, 可参考 **第 5.4 章节复位控制**

| 模块          | POR | RST# | DIGITAL_RST | ETHERCAT_RST |

|-------------|-----|------|-------------|--------------|

| EtherCAT 从站 | √   | √    | √           | √            |

| PHYA        | √   | √    |             |              |

| PHYB        | √   | √    |             |              |

| SPI/SQI 接口  | √   | √    | √           |              |

|        |   |   |   |  |

|--------|---|---|---|--|

| HBI 接口 | √ | √ | √ |  |

| GPT    | √ | √ | √ |  |

| 系统寄存器  | √ | √ | √ |  |

#### 4.2.1 芯片级复位

芯片级复位会激活所有内部功能的复位，从而复位整个芯片。芯片级复位可以通过以下几种方式来触发：

- **上电复位 (POR)**

当芯片首次上电，或掉电后重新上电时，将发生上电复位。此操作将复位芯片内的所有电路。复位后，ISN8221 将重新执行 EEPROM 的加载。

- **RST# 管脚复位**

将 RST# 管脚拉低会触发芯片级复位。此事件会复位芯片内的所有电路。复位后，ISN8221 将重新执行 EEPROM 的加载。

RST# 管脚复位通常大约需要 760 us。

## 5. 系统寄存器

本章着重阐述了 ISN8221 的系统寄存器。系统寄存器主要具备芯片版本信息呈现、系统配置、中断控制以及间接访问 EtherCAT 从站寄存器等功能。微控制器（MCU）可借助主机总线接口（HBI）或 SPI 接口对系统寄存器进行直接访问。系统寄存器的地址映射详见表 5 - 1：

表 5-1 ISN8221 系统寄存器

| 地址           | 符号                | 寄存器名                      |

|--------------|-------------------|---------------------------|

| 000h-01Ch    | ECAT_PRAM_RD_DATA | EtherCAT 过程 RAM 读取数据 FIFO |

| 020h-03Ch    | ECAT_PRAM_WR_DATA | EtherCAT 过程 RAM 写入数据 FIFO |

| 050h         | ID_REV            | 芯片 ID 和 版本                |

| 054h         | IRQ_CFG           | 中断配置寄存器                   |

| 058h         | INT_STS           | 中断状态寄存器                   |

| 05Ch         | INT_EN            | 中断使能寄存器                   |

| 064h         | BYTE_TEST         | 字节顺序测试寄存器                 |

| 074h         | HW_CFG            | 硬件配置寄存器                   |

| 08Ch         | GTP_CFG           | 通用定时器配置寄存器                |

| 090h         | GPT_CNT           | 通用定时器计数寄存器                |

| 复位寄存器        |                   |                           |

| 1F8H         | RESET_CTRL        | 复位控制寄存器                   |

| EtherCAT 寄存器 |                   |                           |

| 300H         | ECAT_CSR_DATA     | EtherCAT CSR 接口数据寄存器      |

|      |                       |                            |

|------|-----------------------|----------------------------|

| 304H | ECAT_CSR_CMD          | EtherCAT CSR 接口命令寄存器       |

| 308H | ECAT_PRAM_RD_ADDR_LEN | EtherCAT 过程 RAM 读取地址与长度寄存器 |

| 30CH | ECAT_PRAM_RD_CMD      | EtherCAT 过程 RAM 读取命令寄存器    |

| 310H | ECAT_PRAM_WR_ADDR_LEN | EtherCAT 过程 RAM 写入地址与长度寄存器 |

| 314H | ECAT_PRAM_WR_CMD      | EtherCAT 过程 RAM 写入命令寄存器    |

## 5.1 系统配置

本节将描述系统配置寄存器，如表 5-2 所示

表 5-2 ISN8221 系统配置寄存器

| 地址   | 符号        | 寄存器名      |

|------|-----------|-----------|

| 050h | ID_REV    | 芯片 ID 和版本 |

| 064h | BYTE_TEST | 字节顺序测试寄存器 |

| 074h | HW_CFG    | 硬件配置寄存器   |

### 5.1.1 芯片 ID 和版本寄存器(ID\_REV)

寄存器 ID\_REV 是 32-bit 只读寄存器，包含芯片 ID 与芯片版本信息，地址偏移为 050h。寄存器格式如下：

| Bits  | 描述    | 权限 | 默认值   |

|-------|-------|----|-------|

| 31:16 | 芯片 ID | RO | 8221h |

| 15:0  | 芯片版本  | RO | -     |

### 5.1.2 字节顺序测试寄存器(BYTE\_ORDER)

寄存器 BYTE\_ORDER 是 32-bit 只读寄存器，地址偏移为 064h，用于确定字节顺序。寄存器格式如下：

| Bits | 描述        | 权限 | 默认值       |

|------|-----------|----|-----------|

| 31:0 | Byte Test | RO | 87654321h |

### 5.1.3 硬件配置寄存器(HW\_CFG)

寄存器 HW\_CFG 是 32-bit 只读寄存器，地址偏移为 074h，用于指示芯片是否就绪。寄存器格式如下：

| Bits  | 描述                                                                                                          | 权限 | 默认值 |

|-------|-------------------------------------------------------------------------------------------------------------|----|-----|

| 31:28 | 保留                                                                                                          | RO | -   |

| 27    | <b>芯片就绪 (READY)</b><br><br>1: 表明芯片已完成上电复位，并且 EtherCAT 从站从 EEPROM 加载完配置信息。<br><br>0: 表明芯片还未就绪，此时微控制器无法访问寄存器。 | RO | 0b  |

| 26:0  | 保留                                                                                                          | RO | -   |

## 5.2 通用计时器

ISN8221 实现了一个可编程的 16-bit 通用计时器，计时器的计时单位时间为 100us，可用于产生周期性的定时中断。通用计时器寄存器如表 5-3 所示：

表 5-3 ISN8221 通用计时器寄存器

| 地址   | 符号      | 寄存器名       |

|------|---------|------------|

| 08Ch | GTP_CFG | 通用计时器配置寄存器 |

| 090h | GPT_CNT | 通用计时器计数寄存器 |

通用计时器采用 16-bit 的计数器进行计时，当通用计时器启用时，计数器开始每隔 100us 递减计数，当计数值达到 0000h 时，产生计时中断，计数器将回绕到 FFFFh 继续计数。

通用计时器的计数器初始值可由寄存器 **GPT\_CFG** 的 **GPT\_LOAD** 字段设置，并在寄存器 **GPT\_CFG** 中的 **TIMER\_EN** 位被置为 1 时，被加载到计数器中。而寄存器 **GPT\_CNT** 的 **GPT\_CNT** 字段则显示当前计数器的值。

如果 **TIMER\_EN** 使能时，微控制器（MCU）每次往寄存器 **GPT\_CFG** 的 **GPT\_LOAD** 字段写新的数值，都会立刻更新到计数器中，计数器将基于更新值继续递减计数。

### 5.2.1 通用计时器配置寄存器(GPT\_CFG)

寄存器 GPT\_CFG 用于配置芯片的通用计时器 (GPT)。地址偏移为 08Ch, 寄存器格式如下：

| Bits  | 描述                                                                                                    | 权限  | 默认值   |

|-------|-------------------------------------------------------------------------------------------------------|-----|-------|

| 31:30 | 保留                                                                                                    | RO  | -     |

| 29    | <b>TIMER_EN</b><br>0: 禁用通用计时器<br>1: 启用通用计时器                                                           | R/W | 0b    |

| 28:16 | 保留                                                                                                    | RO  | -     |

| 15:0  | <b>GPT_LOAD</b><br>通用计时器预加载值, 在启用通用计时器时, 作为通用计时器的计数器初始值。<br>当 TIMER_EN 位从 1 到 0 转变时, 该字段将重置位<br>FFFFh | R/W | FFFFh |

### 5.2.2 通用计时器计数寄存器(GPT\_CNT)

寄存器 GPT\_CNT 反映通用计时器的计数器值, 地址偏移位 090h, 寄存器格式如下:

| Bits  | 描述                            | 权限 | 默认值   |

|-------|-------------------------------|----|-------|

| 31:16 | 保留                            | RO | -     |

| 15:0  | <b>GPT_CNT</b><br>通用计时器的当前计数值 | RO | FFFFh |

## 5.3 中断

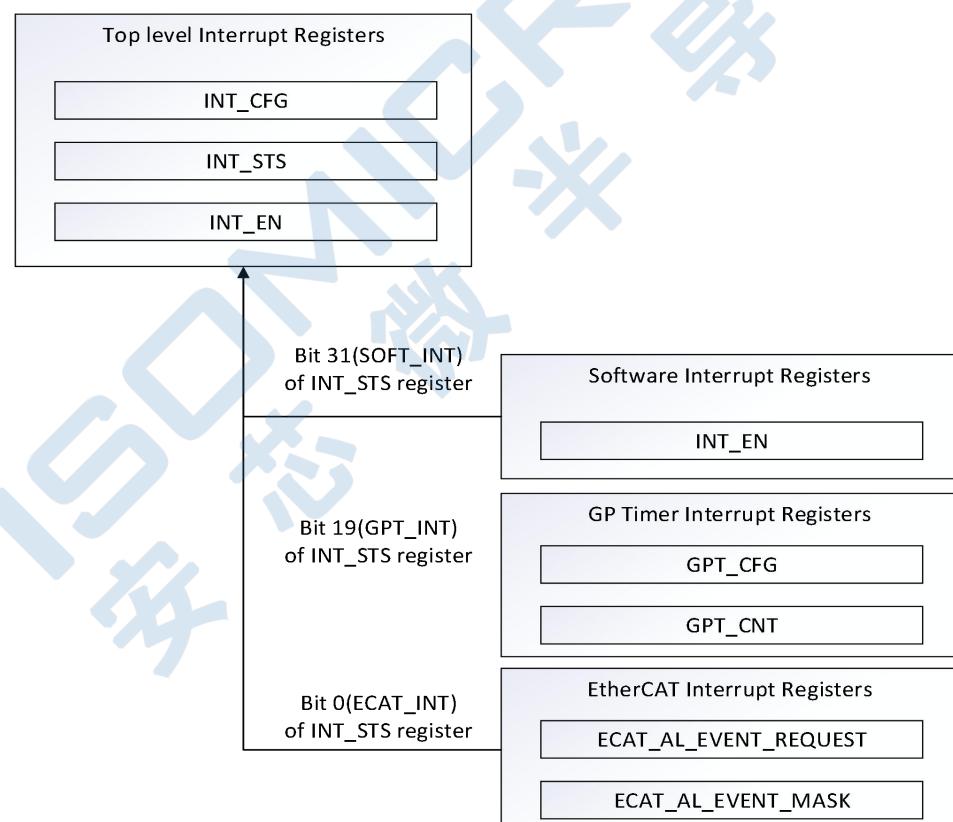

ISN8221 实现了一种可编程中断管理单元，可通过寄存器配置实现对系统各子模块中断源的收集，并将中断信号输出至 IRQ 引脚。IRQ 引脚的有效极性支持可配置，并采用推挽输出结构。该中断管理单元具备全局中断屏蔽功能，可对所有内部中断源进行使能控制。内部中断源涵盖以下类型：通用定时器中断（GPT）、EtherCAT 中断、软件触发中断及芯片就绪中断。

所有中断都通过多层分支的结构，逐层进行访问和配置，如图 5-1 所示。芯片中断结构的顶层是中断状态（INT\_STS）寄存器、中断使能（INT\_EN）寄存器和中断配置（IRQ\_CFG）寄存器。

图 5-1 中断层次结构

ISN8221 中断管理单元相关的寄存器如表 5-4 所示：

表 5-4：中断控制寄存器

| 地址   | 符号      | 寄存器名    |

|------|---------|---------|

| 054h | IRQ_CFG | 中断配置寄存器 |

| 058h | INT_STS | 中断状态寄存器 |

| 05Ch | INT_EN  | 中断使能寄存器 |

ISN8221 的中断源包括软件中断、通用计时器中断和 EtherCAT 从站中断，其中：

- 软件中断：通过往中断使能 (INT\_EN) 寄存器的 **SW\_INT\_EN** 位写 1 产生软件中断。

- 通用计时器中断：在启用通用计时器后，当通用计时器的计数器计数到 0 时产生通用计时器中断。

- EtherCAT 从站中断：表明在 EtherCAT 从站寄存器 **AL 事件请求寄存器(ECAT\_AL\_EVENT\_REQUEST)** 中发生了 EtherCAT 中断事件。

中断管理单元实现了中断状态 (INT\_STS) 寄存器用于显示软件、通用计时器以及 EtherCAT 从站等中断源的中断状态。而中断使能寄存器 (INT\_EN) 用于控制这些中断源的中断能否输出到 IRQ 管脚上。中断配置 (IRQ\_CFG) 寄存器则配置 IRQ 管脚的输出使能和有效极性，以及控制有效中断输出的间隔时间。

### 5.3.1 中断配置 (IRQ\_CFG) 寄存器

中断配置 (IRQ\_CFG) 寄存器主要配置中断管脚信息，以及中断间隔控制，地址偏移为 054h，寄存器格式如下：

| Bits  | 描述                                                                                                                                                                    | 权限     | 默认值 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|

| 31:24 | <b>INT_DEAS (中断时间间隔)</b><br><br>如果数值为 0，禁用中断间隔机制。当 IRQ 输出管脚信号从有效变为无效时，启用中断间隔机制，并开始计时，计数器每个 10us 递增计数，当计数器数值等于 INT_DEAS 时，退出中断间隔机制。处于中断间隔机制期间，IRQ 管脚不会输出有效电平，所有中断都被屏蔽。 | R/W    | 00h |

| 23-15 | 保留                                                                                                                                                                    | RO     | -   |

| 14    | <b>INT_DEAS_CLR</b><br><br>软件写 1 后将清除中断间隔机制的计数器，如果处于中断间隔机制期间，将计数器将重新计时。                                                                                               | R/W SC | 0h  |

| 13    | <b>INT_DEAS_STS (中断间隔状态)</b><br><br>0: 不处于中断间隔机制期间<br>1: 处于中断间隔机制期间                                                                                                   | RO     | 0b  |

| 12    | <b>IRQ_INT (IRQ 管脚中断)</b><br><br>0: 没有有效中断请求                                                                                                                          | RO     | 0b  |

|      |                                              |     |    |

|------|----------------------------------------------|-----|----|

|      | 1: 存在一个或多个已使能的有效中断请求                         |     |    |

| 11-9 | 保留                                           | RO  | -  |

|      | <b>IRQ_EN (中断使能)</b>                         |     |    |

| 8    | 0: 禁止中断状态输出到 IRQ 管脚<br>1: 允许中断状态输出到 IRQ 管脚   | R/W | 0b |

| 7:5  | 保留                                           | RO  | -  |

|      | <b>IRQ_POL (IRQ 极性)</b>                      |     |    |

| 4    | 0: IRQ 管脚的有效中断电平是低电平<br>1: IRQ 管脚的有效中断电平是高电平 | R/W | 0b |

| 3:0  | 保留                                           | RO  | -  |

### 5.3.2 中断状态(INT\_STS)寄存器

中断状态 (INT\_STS) 寄存器的位反映了中断源的中断状态, 地址偏移为 058h, 寄存器格式如下:

| Bits  | 描述                                                               | 权限   | 默认值 |

|-------|------------------------------------------------------------------|------|-----|

| 31    | <b>SW_INT (软件中断状态)</b><br>1: 软件中断请求有效; 软件往该字段写 1, 清除软件中断请求       | R/WC | 0b  |

| 30:20 | 保留                                                               | RO   | -   |

| 19    | <b>GPT_INT (通用计时器中断)</b><br>1: 通用计时器中断请求有效; 软件往该字段写 1, 清除通用计时器中断 | R/WC | 0b  |

| 18:1  | 保留                                                               | RO   | -   |

| 0     | <b>ECAT_INT (EtherCAT 中断事件)</b><br>1: EtherCAT 从站中断请求有效          | RO   | 0b  |

### 5.3.3 中断使能寄存器(INT\_EN)

中断使能 (INT\_EN) 寄存器用于控制中断源的中断请求是否允许通过 IRQ 管脚输出, 地址偏移为 05Ch, 寄存器格式如下:

| Bits  | 描述                                                                                                     | 权限  | 默认值 |

|-------|--------------------------------------------------------------------------------------------------------|-----|-----|

| 31    | <b>SW_INT_EN (软件中断使能)</b><br>0: 禁止软件中断请求输出到 IRQ 管脚<br>1: 允许软件中断请求输出到 IRQ 管脚                            | R/W | 0b  |

| 30:20 | 保留                                                                                                     | RO  | -   |

| 19    | <b>GPT_INT_EN (通用计时器中断使能)</b><br>0: 禁止通用计时器中断请求输出到 IRQ 管脚<br>1: 允许通用计时器中断请求输出到 IRQ 管脚                  | R/W | 0b  |

| 18:1  | 保留                                                                                                     | RO  | -   |

| 0     | <b>ECAT_INT_EN (EtherCAT 中断事件使能)</b><br>0: 禁止 EtherCAT 中断请求输出到 IRQ 管脚<br>1: 允许 EtherCAT 中断请求输出到 IRQ 管脚 | R/W | 0b  |

## 5.4 复位控制

ISN8221 实现复位控制寄存器 (RESET\_CTRL) 对系统子模块进行单独复位, 地址偏移为 1F8h, 寄存器格式如下:

| Bits | 描述                                                                                                          | 权限     | 默认值 |

|------|-------------------------------------------------------------------------------------------------------------|--------|-----|

| 31:7 | 保留                                                                                                          | RO     | -   |

| 6    | <b>ETHERCAT_RST (EtherCAT 复位)</b><br>写 1 将复位 EtherCAT 从站, 复位完成后, 硬件自动清除此位                                   | R/W SC | 0b  |

| 5:3  | 保留                                                                                                          | RO     | -   |

| 2    | <b>PHY_B_RST (网口 Port B PHY 复位)</b><br>写 1 将复位网口 Port B 的 PHY 芯片, 内部逻辑会自动保持 PHY 复位至少 20 ms, 复位完成后, 硬件自动清除此位 | R/W SC | 0b  |

| 1    | <b>PHY_A_RST (网口 Port A PHY 复位)</b><br>写 1 将复位网口 Port A 的 PHY 芯片, 内部逻辑会自动保持 PHY 复位至少 20 ms, 复位完成后, 硬件自动清除此位 | R/W SC | 0b  |

| 0    | <b>DIGITAL_RST (数字复位)</b><br>写 1 将执行全局复位, 除网口 Port B PHY 和网口 Port A PHY 除外, 所有的电路都将复位, 复位完成后, 硬件自动清除此位      | R/W SC | 0b  |

## 6. 访问 EtherCAT 从站寄存器

在 ISN8221 的实现中，微控制器（MCU）无法通过主机总线接口（HBI）或 SPI 接口直接访问 EtherCAT 从站寄存器，需要通过对应的**系统寄存器**来间接访问，间接访问 EtherCAT 从站寄存器相关的系统寄存器如表 6-1 所示：

表 6-1：间接访问 EtherCAT 从站寄存器的寄存器列表

| 地址        | 符号                    | 寄存器名                       |

|-----------|-----------------------|----------------------------|

| 000h-01Ch | ECAT_PRAM_RD_DATA     | EtherCAT 过程 RAM 读取数据 FIFO  |

| 020h-03Ch | ECAT_PRAM_WR_DATA     | EtherCAT 过程 RAM 写入数据 FIFO  |

| 300h      | ECAT_CSR_DATA         | EtherCAT CSR 接口数据寄存器       |

| 304h      | ECAT_CSR_CMD          | EtherCAT CSR 接口命令寄存器       |

| 308h      | ECAT_PRAM_RD_ADDR_LEN | EtherCAT 过程 RAM 读取地址与长度寄存器 |

| 30Ch      | ECAT_PRAM_RD_CMD      | EtherCAT 过程 RAM 读取命令寄存器    |

| 310h      | ECAT_PRAM_WR_ADDR_LEN | EtherCAT 过程 RAM 写入地址与长度寄存器 |

| 314h      | ECAT_PRAM_WR_CMD      | EtherCAT 过程 RAM 写入命令寄存器    |

ISN8221 支持以下访问方式来间接访问 EtherCAT 从站寄存器：

- 单次读写：支持字节(8-Bit)/字(16-Bit)/双字(32-Bit)读写

- 突发读：支持 1~65535 字节的连续读

- 突发写：支持 1~65535 字节的连续写

## 6.1 单次读写

微控制器 (MCU) 可通过配置 **EtherCAT CSR 接口数据 (ECAT\_CSR\_DATA)** 寄存器和 **EtherCAT CSR 接口命令 (ECAT\_CSR\_CMD)** 寄存器来实现对 EtherCAT 从站寄存器的单次读写。

微控制器 (MCU) 读 EtherCAT 从站寄存器的步骤如下：

1. 配置 **EtherCAT CSR 接口命令 (ECAT\_CSR\_CMD)** 寄存器， 其中：

- (1) **CSR\_ADDR** 字段设置为从站寄存器地址。

- (2) **CSR\_SIZE** 字段设置为所需的数据大小， 1: 字节 (8-Bit) , 2: 字 (16-Bit) , 4: 双字 (32-Bit)。

- (3) **R\_nW** 位设置为 1, 将操作设置为读操作。

- (4) **CSR\_BUSY** 位设置为 1, 启动读操作请求。

2. 等待 **EtherCAT CSR 接口命令 (ECAT\_CSR\_CMD)** 寄存器的 **CSR\_BUSY** 位清零。

3. 从 **EtherCAT CSR 接口数据 (ECAT\_CSR\_DATA)** 寄存器中读取到有效数据。

微控制器 (MCU) 写 EtherCAT 从站寄存器的步骤如下：

1. 将数据写入 **EtherCAT CSR 接口数据 (ECAT\_CSR\_DATA)** 寄存器。

2. 配置 **EtherCAT CSR 接口命令 (ECAT\_CSR\_CMD)** 寄存器， 其中：

- (1) **CSR\_ADDR** 字段设置为从站寄存器地址。

- (2) **CSR\_SIZE** 字段设置为所需的数据大小， 1: 字节 (8-Bit) , 2: 字 (16-Bit) , 4: 双字 (32-Bit)。

- (3) **R\_nW** 位设置为 0, 将操作设置为写操作。

- (4) **CSR\_BUSY** 位设置为 1, 启动写操作请求。

3. 等待 **EtherCAT CSR 接口命令 (ECAT\_CSR\_CMD)** 寄存器的 **CSR\_BUSY** 位清零。

注意： 读和写操作的有效数据始终对齐到 **EtherCAT CSR 接口数据 (ECAT\_CSR\_DATA)** 寄存器的最低位。

**EtherCAT CSR 接口数据 (ECAT\_CSR\_DATA)** 寄存器主要存放 EtherCAT 从站寄存器的读写数据，地址偏移为 300h，寄存器格式如下：

| Bits | 描述                                                                                                                                                                                                                                                                                                                                                                                             | 权限  | 默认值       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 31:0 | <p><b>EtherCAT CSR 数据 (CSR_DATA)</b></p> <p>此字段包含从 EtherCAT 从站寄存器读取或写入的值。</p> <p>通过 <b>EtherCAT CSR 接口命令寄存器 (ECAT_CSR_CMD)</b> 的 CSR 地址 (CSR_ADDR) 位选择 EtherCAT 从站寄存器地址。</p> <p>有效数据始终写入或读取自该字段的低位。芯片会处理任何所需的字节对齐。</p> <p>读取该寄存器时，返回的值取决于 <b>EtherCAT CSR 接口命令寄存器 (ECAT_CSR_CMD)</b> 中的读/写 (R_nW) 位。</p> <p>如果读/写 (R_nW) 被置位，则数据来自 EtherCAT 从站寄存器。</p> <p>如果读/写 (R_nW) 被清除，则数据是上次写入该寄存器的值。</p> | R/W | 00000000h |

EtherCAT CSR 接口命令 (ECAT\_CSR\_CMD) 寄存器 用于配置从站寄存器地址、字节数、读写命令以及启动读写请求，地址偏移为 304h，寄存器格式如下：

| Bits  | 描述                                                                                                                                 | 权限     | 默认值 |

|-------|------------------------------------------------------------------------------------------------------------------------------------|--------|-----|

| 31    | <b>CSR_BUSY (CSR 繁忙)</b><br>软件写 1 时，启动 EtherCAT 从站寄存器的读写操作，读写操作完成后，硬件自动清零。                                                         | R/W SC | 0b  |

| 30    | <b>R_nW (读/写)</b><br>0: 执行写 EtherCAT 从站寄存器操作。<br>1: 执行读 EtherCAT 从站寄存器操作。                                                          | R/W    | 0b  |

| 29:19 | 保留                                                                                                                                 | RO     | -   |

| 18:16 | <b>CSR_SIZE (CSR 大小)</b><br>该字段指定访问 EtherCAT 从站寄存器的大小，以字节为单位。<br>有效值为 1、2 和 4。<br>1: 字节 (8-Bit)<br>2: 字 (16-Bit)<br>4: 双字 (32-Bit) | R/W    | 0h  |

| 15:0  | <b>CSR_ADDR (CSR 地址)</b><br>访问的 EtherCAT 从站寄存器                                                                                     | R/W    | 00h |

需要注意的是：字 (16Bit) 和双字 (32Bit) 访问必须根据以下表格对齐到正确的地址边界。

| CSR_SIZE[2:0] | CSR_ADDR[1:0]   |

|---------------|-----------------|

| 1             | 00b,01b,10b,11b |

| 2             | 00b,10b         |

| 4             | 00b             |

## 6.2 突发读

微控制器 (MCU) 可以通过配置 **EtherCAT 过程 RAM 读地址和长度 (ECAT\_PRAM\_RD\_ADDR\_LEN)** 寄存器和 **EtherCAT 过程 RAM 读命令 (ECAT\_PRAM\_RD\_CMD)** 寄存器实现对 EtherCAT 从站寄存器的突发读访问。ISN8221 实现了一个深度为 16、位宽位 32-bit 的 FIFO，用于暂存突发读访问过程中，从 EtherCAT 从站寄存器读的数据，FIFO 的基地址为 00h。

微控制器 (MCU) 突发读 EtherCAT 从站寄存器的步骤如下：

1. 往 **EtherCAT 过程 RAM 读命令 (ECAT\_PRAM\_RD\_CMD)** 寄存器的 **PRAM\_READ\_ABORT** 位写 1，重置突发读操作。

2. 往 **EtherCAT 过程 RAM 读地址和长度 (ECAT\_PRAM\_RD\_ADDR\_LEN)** 寄存器写入寄存器的地址和读取长度 (以字节为单位)。

3. 往 **EtherCAT 过程 RAM 读命令 (ECAT\_PRAM\_RD\_CMD)** 寄存器的 **PRAM\_READ\_BUSY** 位来启动突发读操作。

4. 读取 **EtherCAT 过程 RAM 读命令 (ECAT\_PRAM\_RD\_CMD)** 寄存器，根据 **PRAM\_READ\_AVAIL** 位确认 FIFO 中，是否存放有效的 EtherCAT 从站寄存器数据，如果 **PRAM\_READ\_AVAIL** 位为 1，执行第 5 步。

5. **EtherCAT 过程 RAM 读命令 (ECAT\_PRAM\_RD\_CMD)** 寄存器 **PRAM\_READ\_AVAIL\_CNT** 字段表示允许微控制器 (MCU) 以双字 (32-Bit) 为单位，读取 FIFO 的次数，微控制器 (MCU) 根据读取长度，读取 FIFO 内的数据。

6. 如需继续读取数据，继续执行第 4 步。

基于起始地址，第一次 FIFO 读取中的有效字节数如下：

| 起始地址 ADDR[1:0] |                  |

|----------------|------------------|

| 00b            | Bytes 3, 2, 1, 0 |

| 01b            | Bytes 3, 2, 1    |

| 10b            | Bytes 3, 2       |

| 11b            | Bytes 3          |

根据起始地址和长度，最后一次 FIFO 读取中的有效字节如下：

| 起始地址<br>Addr[1:0] | 起始长度 Len[1:0]   |                 |                 |                 |  |

|-------------------|-----------------|-----------------|-----------------|-----------------|--|

|                   | 01b             | 10b             | 11b             | 00b             |  |

| 00b               | Byte 0          | Byte 1, 0       | Byte 2, 1, 0    | Byte 3, 2, 1, 0 |  |

| 01b               | Byte 1, 0       | Byte 2, 1, 0    | Byte 3, 2, 1, 0 | Byte 0          |  |

| 10b               | Byte 2, 1, 0    | Byte 3, 2, 1, 0 | Byte 0          | Byte 1, 0       |  |

| 11b               | Byte 3, 2, 1, 0 | Byte 0          | Byte 1, 0       | Byte 2, 1, 0    |  |

EtherCAT 过程 RAM 读地址和长度 (ECAT\_PRAM\_RD\_ADDR\_LEN) 寄存器存放初始地址和读取长度, 地址偏移为 305h, 寄存器格式如下:

| Bits  | 描述                                                                                                        | 权限  | 默认值   |

|-------|-----------------------------------------------------------------------------------------------------------|-----|-------|

| 31:16 | <b>PRAM_READ_LEN (PRAM 读长度)</b><br>该字段存放要读取的 EtherCAT 从站寄存器的字节数。当数据从 EtherCAT 从站读取并放入 FIFO 时, 该字段的值会递减。   | R/W | 0000h |

| 15:0  | <b>PRAM_READ_ADDR (PRAM 读地址)</b><br>该字段存放要读取的 EtherCAT 从站寄存器的起始地址。当数据从 EtherCAT 从站读取并放入 FIFO 时, 该地址会自动递增。 | R/W | 0000h |

EtherCAT 过程 RAM 读命令 (ECAT\_PRAM\_RD\_CMD) 寄存器控制突发读操作的进度, 地址偏移为 30Ch,

寄存器格式如下:

| Bits  | 描述                                                                                                                                                                                                                                    | 权限     | 默认值    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| 31    | <b>PRAM_READ_BUSY (PRAM 读繁忙)</b><br>写 1 将启动突发读 EtherCAT 从站寄存器的操作, 执行完突发读操作后, 硬件会自动清零                                                                                                                                                  | R/W SC | 0b     |

| 30    | <b>PRAM_READ_ABORT (PRAM 读中止)</b><br>写 1 将结束正在进行的读取操作, 并将 FIFO 清空, 执行完成后, 硬件自动清零。                                                                                                                                                     | R/W SC | 0b     |

| 29:13 | 保留                                                                                                                                                                                                                                    | RO     | -      |

| 12:8  | <b>PRAM_READ_AVAIL_CNT (PRAM 读数据可用计数)</b><br>该字段表示在无需进一步检查状态的情况下, 可以读取 EtherCAT 过程 RAM 读取数据 FIFO (ECAT_PRAM_RD_DATA) 的次数。<br>当数据从 EtherCAT 从站寄存器读取并放入 FIFO 时, 该字段会递增。当从 RAM 读取数据 FIFO (ECAT_PRAM_RD_DATA) 中读取完整的一个 DWORD 数据时, 该字段会递减。 | RO     | 00000b |

| 7:1   | 保留                                                                                                                                                                                                                                    | RO     | -      |

| 0     | <b>PRAM_READ_AVAIL (PRAM 读数据可用)</b><br>1: 表明 FIFO 存放有有效的 EtherCAT 从站寄存器数据。                                                                                                                                                            | RO     | 0b     |

**EtherCAT 过程 RAM 读数据 FIFO (ECAT\_PRAM\_RD\_DATA)** 寄存器存放突发读操作的数据，地址偏移

为 000h-01Ch，寄存器格式如下：

| Bits | 描述                                                                                                          | 权限 | 默认值 |

|------|-------------------------------------------------------------------------------------------------------------|----|-----|

| 31:0 | <b>EtherCAT 过程 RAM 读数据 (PRAM_RD_DATA)</b><br>此字段包含从 EtherCAT 从站寄存器中读的数据。<br><b>注意：根据起始地址和传输长度，某些字节可能无效。</b> | RO | -   |

注:000h-003h、004h-007h、008h-00Bh、00Ch-00Fh、010h-013h、014h-017h、018h-01Bh 和 01Ch-01Fh

均为 **EtherCAT 过程 RAM 读数据 FIFO (ECAT\_PRAM\_RD\_DATA)** 寄存器的地址别名，微控制器 (MCU)

从这些地址读取数据的操作等价。

## 6.3 突发写

微控制器 (MCU) 可以通过配置 **EtherCAT 过程 RAM 写地址和长度 (ECAT\_PRAM\_WR\_ADDR\_LEN)** 寄存器和 **EtherCAT 过程 RAM 写命令 (ECAT\_PRAM\_WR\_CMD)** 寄存器实现对 EtherCAT 从站寄存器的突发写访问。ISN8221 实现了一个深度为 16、位宽位 32-bit 的 FIFO，用于暂存突发写访问过程中，往 EtherCAT 从站寄存器写入的数据，FIFO 的基地址为 20h。

微控制器 (MCU) 突发读 EtherCAT 从站寄存器的步骤如下：

1. 往 **EtherCAT 过程 RAM 写命令 (ECAT\_PRAM\_WR\_CMD)** 寄存器的 **PRAM\_WRITE\_ABORT** 位写 1，重置突发写操作。

2. 往 **EtherCAT 过程 RAM 写地址和长度 (ECAT\_PRAM\_WR\_ADDR\_LEN)** 寄存器写入寄存器的地址和写长度 (以字节为单位)。

3. 往 **EtherCAT 过程 RAM 写命令 (ECAT\_PRAM\_WR\_CMD)** 寄存器的 **PRAM\_WRITE\_BUSY** 位来启动突发写操作。

4. 读取 **EtherCAT 过程 RAM 写命令 (ECAT\_PRAM\_WR\_CMD)** 寄存器，根据 **PRAM\_WRITE\_AVAIL** 位确认 FIFO 中，是否有空间用于存放写 EtherCAT 从站寄存器的数据，如果 **PRAM\_WRITE\_AVAIL** 位为 1，执行第 5 步。

5. **EtherCAT 过程 RAM 写命令 (ECAT\_PRAM\_WR\_CMD)** 寄存器 **PRAM\_WRITE\_AVAIL\_CNT** 字段表示允许微控制器 (MCU) 以双字 (32-Bit) 为单位，写 FIFO 的次数，微控制器 (MCU) 根据写长度，将数据写入到 FIFO 内。

6. 如需要继续写入数据，继续执行第 4 步。

基于起始地址，第一次 FIFO 写的有效字节数如下：

| 起始地址 ADDR[1:0] |                  |

|----------------|------------------|

| 00b            | Bytes 3, 2, 1, 0 |

| 01b            | Bytes 3, 2, 1    |

| 10b            | Bytes 3, 2       |

| 11b            | Bytes 3          |

根据起始地址和长度，最后一次 FIFO 写的有效字节如下：

| 起始地址<br>Addr[1:0] | 起始长度 Len[1:0]   |                 |                 |                 |  |

|-------------------|-----------------|-----------------|-----------------|-----------------|--|

|                   | 01b             | 10b             | 11b             | 00b             |  |

| 00b               | Byte 0          | Byte 1, 0       | Byte 2, 1, 0    | Byte 3, 2, 1, 0 |  |

| 01b               | Byte 1, 0       | Byte 2, 1, 0    | Byte 3, 2, 1, 0 | Byte 0          |  |

| 10b               | Byte 2, 1, 0    | Byte 3, 2, 1, 0 | Byte 0          | Byte 1, 0       |  |

| 11b               | Byte 3, 2, 1, 0 | Byte 0          | Byte 1, 0       | Byte 2, 1, 0    |  |

**EtherCAT 过程 RAM 写地址和长度 (ECAT\_PRAM\_WR\_ADDR\_LEN)** 寄存器存放初始地址和写长度，地址偏移为 310h，寄存器格式如下：

| Bits  | 描述                                                                                                   | 权限  | 默认值   |

|-------|------------------------------------------------------------------------------------------------------|-----|-------|

| 31:16 | <b>PRAM 写入长度 (PRAM_WRITE_LEN)</b><br>该字段存放写 EtherCAT 从站寄存器的字节数。当数据从 FIFO 传输到 EtherCAT 从站时，该字段的值会递减。  | R/W | 0000h |

| 15:0  | <b>PRAM 写入地址 (PRAM_READ_ADDR)</b><br>该字段存放写 EtherCAT 从站寄存器的起始地址。当数据从 FIFO 传输到 EtherCAT 从站时，该地址会自动递增。 | R/W | 0000h |

EtherCAT 过程 RAM 写命令 (ECAT\_PRAM\_WR\_CMD) 寄存器控制突发写操作的进度, 地址偏移为 314h,

寄存器格式如下:

| Bits  | 描述                                                                                                                                                                                                                                      | 权限     | 默认值    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| 31    | <b>PRAM_WRITE_BUSY (PRAM 写入繁忙)</b><br>写 1 将启动突发写 EtherCAT 从站寄存器的操作, 执行完突发写操作后, 硬件自动清零                                                                                                                                                   | R/W SC | 0b     |

| 30    | <b>PRAM_WRITE_ABORT (PRAM 写入中止)</b><br>写 1 将重置正在进行的突发写操作, 并将 FIFO 清空, 执行完操作后, 硬件自动清零。                                                                                                                                                   | R/W SC | 0b     |

| 29:13 | 保留                                                                                                                                                                                                                                      | RO     | -      |

| 12:8  | <b>PRAM_WRITE_AVAIL_CNT (PRAM 可写数据计数)</b><br>该字段表示无需进一步检查状态即可写入 EtherCAT 过程 RAM 写数据 FIFO (ECAT_PRAM_WR_DATA) 的次数。<br>当一个完整的双字 (DWORD) 数据写入 EtherCAT 过程 RAM 写数据 FIFO (ECAT_PRAM_WR_DATA) 时, 该字段会递减。当数据从 FIFO 读取并放入 EtherCAT 核心时, 该字段会递增。 | RO     | 00000b |

| 7:1   | 保留                                                                                                                                                                                                                                      | RO     | -      |

| 0     | <b>PRAM 可写数据 (PRAM_WRITE_AVAIL)</b><br>1: 表示 FIFO 中有可用的空间供微控制器 (MCU) 写入数据。                                                                                                                                                              | RO     | 10000b |

**EtherCAT 过程 RAM 写数据 FIFO (ECAT\_PRAM\_WR\_DATA)** 寄存器存放突发写 EtherCAT 从站寄存器的写数据，地址偏移为 020h-03Fh，寄存器格式如下：

| Bits | 描述                                                                                                      | 权限 | 默认值 |

|------|---------------------------------------------------------------------------------------------------------|----|-----|

| 31:0 | <b>EtherCAT 过程 RAM 写数据 (PRAM_WR_DATA)</b><br>此字段包往 EtherCAT 从站中传输的值。<br><b>注意：根据起始地址和传输长度，某些字节可能无效。</b> | WO | -   |

注:020h-023h、024h-027h、028h-02Bh、02Ch-02Fh、030h-033h、034h-037h、038h-03Bh 和 03Ch-03Fh

均为的 **EtherCAT 过程 RAM 写数据 FIFO (ECAT\_PRAM\_WR\_DATA)** 寄存的地址别名，微控制器 (MCU) 往这些地址写入数据的操作等价。

## 7. PDI 接口配置

ISN8221 实现了 8/16 Bit 主机总线接 (HBI) 和 SPI 接口作为与微控制器 (MCU) 通信的 PDI 接口，也实现了 Digital IO 模式来获取简单的数字量。这些 PDI 接口的选择，由 EtherCAT 从站寄存器 **PDI Control** 来控制，寄存器 **PDI Control** 的寄存器格式如下：

地址偏移：0140h-0141h

| Bits | 描述                                                                                                                                                                                                                                                                               | ECAT<br>权限 | PDI<br>权限 | 默认<br>值 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|---------|

| 7:0  | 编程数据接口：<br>04h: Digital I/O<br>80h: SPI<br>88h: 8Bit 单相地址/数据复用主机总线接口 (HBI Mul)<br>89h: 16Bit 单相地址/数据复用主机总线接口 (HBI Mul)<br>8Ah: 8Bit 双相地址/数据复用主机总线接口 (HBI Mul)<br>8Bh: 16Bit 双相地址/数据复用主机总线接口 (HBI Mul)<br>8Ch: 8Bit 寄存器索引主机总线接口 (HBI Index)<br>8Dh: 16Bit 寄存器索引主机总线接口 (HBI Index) | RO         | RO        | 00h     |

此外，在不同的 PDI 接口模式下，EtherCAT 从站寄存器 **PDI Configuration** 和 **Extended PDI Configuration** 提供了编程接口相关的配置。

EtherCAT 从站寄存器 PDI Control、PDI Configuration 和 Extended PDI Configuration 的初始值均可以通过 EEPROM 配置；更多信息请参阅第 10.6 节“EEPROM 可配置寄存器”。

ISOMICRON 安芯微半导体

## 7.1 Digital IO 接口配置

当 EtherCAT 从站寄存器 **PDI Control** 配置为 Digital I/O 接口时, EtherCAT 从站寄存器 **PDI Configuration** 和 **Extended PDI Configuration** 为 Digital IO 提供了相关的配置。

Digital IO 接口模式下的寄存器 **PDI Configuration** 的寄存器格式如下:

地址偏移: 0150h

| Bits | 描述                                                                                                                                                           | ECAT<br>权限 | PDI<br>权限 | 默认<br>值 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|---------|

| 7:6  | Output Data Sample Selection (输出数据采样选择)<br>00: 帧结束<br>01: 保留<br>10: DC SYNC0 事件<br>11: 保留<br><br>注意: 如果 OUTVALID 模式 = 1, 输出数据将在过程数据看门狗触发事件时更新 (输出数据采样选择位被忽略) | RO         | RO        | 00b     |

| 5:4  | Input Data Sample Selection (输入数据采样选择)<br>00: 帧起始<br>01: LATCH_IN 上升沿<br>10: DC SYNC0 事件<br>11: 保留                                                           | RO         | RO        | 00b     |

| 3    | Watchdog Behavior (看门狗行为)                                                                                                                                    | RO         | RO        | 0b      |

|   |                                                                                                                                        |    |    |    |

|---|----------------------------------------------------------------------------------------------------------------------------------------|----|----|----|

|   | 0: 看门狗超时后, 输出立即复位<br><br>1: 看门狗超时后, 输出在下一个输出事件中复位                                                                                      |    |    |    |

| 2 | Unidirectional/Bidirectional Mode (单向/双向模式)<br><br>0: 单向模式: 管脚的输入/输出方向单独配置<br><br>1: 双向模式: 所有 I/O 管脚均为双向<br><br>注意: 双向模式下, 方向控制必须设置为输入 | RO | RO | 0b |

| 1 | OUTVALID Mode (OUTVALID 模式)<br><br>0: 输出事件信号<br><br>1: 在 OUTVALID 上触发过程数据看门狗 (WD_TRIGGER) 信号。<br><br>如果触发看门狗, 输出数据将更新。覆盖输出数据样本选择位。     | RO | RO | 0b |

| 0 | OUTVALID Polarity (OUTVALID 电平极性)<br><br>0: 高电平有效<br><br>1: 低电平有效                                                                      | RO | RO | 0b |

Digital I/O 接口模式下寄存器的 **Extended PDI Configuration** 的寄存器格式如下:

地址偏移: 0152h-0153h

| Bits | 描述                                                                           | ECAT<br>权限 | PDI<br>权限 | 默认值   |

|------|------------------------------------------------------------------------------|------------|-----------|-------|

| 15:8 | 保留                                                                           | RO         | RO        | 0000h |

| 7    | I/O[15:14] Direction (I/O[15:14] 方向)<br>0: 输入<br>1: 输出<br>注意: 在双向模式下必须清零为 0。 | RO         | RO        | 0b    |

| 6    | I/O[13:12] Direction (I/O[13:12] 方向)<br>0: 输入<br>1: 输出<br>注意: 在双向模式下必须清零为 0。 | RO         | RO        | 0b    |

| 5    | I/O[11:10] Direction (I/O[11:10] 方向)<br>0: 输入<br>1: 输出<br>注意: 在双向模式下必须清零为 0。 | RO         | RO        | 0b    |

| 4    | I/O[9:8] Direction (I/O[9:8] 方向)<br>0: 输入<br>1: 输出                           | RO         | RO        | 0b    |

|   |                                                                                 |    |    |    |

|---|---------------------------------------------------------------------------------|----|----|----|

|   | 注意：在双向模式下必须清零为 0。                                                               |    |    |    |

| 3 | I/O[7:6] Direction (I/O[7:6] 方向)<br><br>0: 输入<br>1: 输出<br><br>注意：在双向模式下必须清零为 0。 | RO | RO | 0b |

| 2 | I/O[5:4] Direction (I/O[5:4] 方向)<br><br>0: 输入<br>1: 输出<br><br>注意：在双向模式下必须清零为 0。 | RO | RO | 0b |

| 1 | I/O[3:2] Direction (I/O[3:2] 方向)<br><br>0: 输入<br>1: 输出<br><br>注意：在双向模式下必须清零为 0。 | RO | RO | 0b |

| 0 | I/O[1:0] Direction (I/O[1:0] 方向)<br><br>0: 输入<br>1: 输出<br><br>注意：在双向模式下必须清零为 0。 | RO | RO | 0b |

## 7.2 HBI 接口配置

当 EtherCAT 从站寄存器 **PDI Control** 配置为主机总线 (HBI) 接口时, EtherCAT 从站寄存器 **PDI Configuration** 为 HBI 接口提供了相关的配置。

HBI 接口模式下的 EtherCAT 从站寄存器 **PDI Configuration** 的寄存器格式如下:

地址偏移: 0150h

| Bits | 描述                                                                                                           | ECAT<br>权限 | PDI<br>权限 | 默认<br>值 |

|------|--------------------------------------------------------------------------------------------------------------|------------|-----------|---------|

| 7    | HBI ALE Qualification (HBI 地址锁存信号的限制)<br>0: 地址输入使用 ALEHI 和 ALELO 锁存<br>1: 地址输入仅在 CS 有效时, 使用 ALEHI 和 ALELO 锁存 | RO         | RO        | 0b      |

| 6    | HBI Read/Write Mode (HBI 读写模式)<br>0: 读和写模式<br>1: 方向和使能模式                                                     | RO         | RO        | 0b      |

| 5    | HBI Chip Select Polarity (HBI 片选信号极性)<br>配置 HBI 接口片选信号 CS 的极性。<br>0: 低电平有效<br>1: 高电平有效                       | RO         | RO        | 0b      |

| 4    | HBI Read, Read/Write Polarity (HBI 读、读/写信号极性)<br>读和写模式<br>0: 低电平有效读取                                         | RO         | RO        | 0b      |

|     |                                                                                                                                               |    |    |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|

|     | 1: 高电平有效读取<br><br>方向和使能模式<br><br>0: 为 1 时读取, 为 0 时写入 (R/nW)<br><br>1: 为 1 时写入, 为 0 时读取 (W/nR)                                                 |    |    |    |

| 3   | HBI Write, Enable Polarity (HBI 写、使能信号极性)<br><br>读和写模式<br><br>0: 低电平有效写入<br><br>1: 高电平有效写入<br><br>方向和使能模式<br><br>0: 低电平有效使能<br><br>1: 高电平有效使能 | RO | RO | 0b |

| 2   | HBI ALE Polarity (HBI 地址锁存信号极性)<br><br>0: 低电平有效选通 (地址在上升沿锁存)<br><br>1: 高电平有效选通 (地址在下降沿锁存)                                                     | RO | RO | 0b |

| 1:0 | 保留                                                                                                                                            | RO | RO | -  |

## 7.3 SPI 接口配置

当 EtherCAT 从站寄存器 **PDI Control** 配置为 SPI 接口时，EtherCAT 从站寄存器 **Extended PDI Configuration** 为 GPI/GPO 提供了相关的配置。

SPI 接口模式下的 EtherCAT 从站寄存器 **Extended PDI Configuration** 的寄存器格式如下：

地址偏移：0152h-0153h

| Bits | 描述                                                                                       | ECAT<br>权限 | PDI<br>权限 | 默认<br>值 |

|------|------------------------------------------------------------------------------------------|------------|-----------|---------|

| 15   | I/O[15:14] Buffer Type (I/O[15:14] Buffer 类型)<br>0: 推挽 (Push-Pull)<br>1: 开漏 (Open Drain) | RO         | RO        | 0b      |

| 14   | I/O[13:12] Buffer Type (I/O[13:12] Buffer 类型)<br>0: 推挽 (Push-Pull)<br>1: 开漏 (Open Drain) | RO         | RO        | 0b      |

| 13   | I/O[11:10] Buffer Type (I/O[11:10] Buffer 类型)<br>0: 推挽 (Push-Pull)<br>1: 开漏 (Open Drain) | RO         | RO        | 0b      |

| 12   | I/O[9:8] Buffer Type (I/O[9:8] Buffer 类型)<br>0: 推挽 (Push-Pull)<br>1: 开漏 (Open Drain)     | RO         | RO        | 0b      |

| 11   | I/O[7:6] Buffer Type (I/O[7:6] Buffer 类型)                                                | RO         | RO        | 0b      |

|    |                                                                                      |    |    |    |

|----|--------------------------------------------------------------------------------------|----|----|----|

|    | 0: 推挽 (Push-Pull)<br>1: 开漏 (Open Drain)                                              |    |    |    |

| 10 | I/O[5:4] Buffer Type (I/O[5:4] Buffer 类型)<br>0: 推挽 (Push-Pull)<br>1: 开漏 (Open Drain) | RO | RO | 0b |

| 9  | I/O[3:2] Buffer Type (I/O[3:2] Buffer 类型)<br>0: 推挽 (Push-Pull)<br>1: 开漏 (Open Drain) | RO | RO | 0b |

| 8  | I/O[1:0] Buffer Type (I/O[1:0] Buffer 类型)<br>0: 推挽 (Push-Pull)<br>1: 开漏 (Open Drain) | RO | RO | 0b |

| 7  | I/O[15:14] Direction (I/O[15:14] 方向)<br>0: 输入<br>1: 输出                               | RO | RO | 0b |

| 6  | I/O[13:12] Direction (I/O[13:12] 方向)<br>0: 输入<br>1: 输出                               | RO | RO | 0b |

| 5  | I/O[11:10] Direction (I/O[11:10] 方向)<br>0: 输入<br>1: 输出                               | RO | RO | 0b |

|   |                                                     |    |    |    |

|---|-----------------------------------------------------|----|----|----|

| 4 | I/O[9:8] Direction (I/O[9:8] 方向)<br>0: 输入<br>1: 输出。 | RO | RO | 0b |

| 3 | I/O[7:6] Direction (I/O[7:6] 方向)<br>0: 输入<br>1: 输出  | RO | RO | 0b |

| 2 | I/O[5:4] Direction (I/O[5:4] 方向)<br>0: 输入<br>1: 输出  | RO | RO | 0b |

| 1 | I/O[3:2]Direction (I/O[3:2] 方向)<br>0: 输入<br>1: 输出   | RO | RO | 0b |

| 0 | I/O[1:0] Direction (I/O[1:0] 方向)<br>0: 输入<br>1: 输出  | RO | RO | 0b |

## 8. 主机总线接口 (HBI)

### 8.1 功能概述

主机总线接口 (HBI) 模块提供了一个高速异步并行接口，可用于 ISN8221 与微控制器(MCU)之间的通信。主机总线接口 (HBI) 基于小端字节序来访问系统寄存器，并通过系统寄存器间接访问 EtherCAT 从站寄存器。关于主机总线接口 (HBI) 的配置可参考 **7.2 HBI 接口配置**。以下是主机总线接口 (HBI) 的功能概述

- 支持两种寻址模式：复用地址/数据模式、以及寄存器索引模式。

- 可选数据总线宽度：支持 16 Bit 和 8 Bit 数据模式。在 16Bit 模式下，不支持字节 (8Bit) 访问。

- 支持两种读/写控制模式：读写独立使能、以及使能/方向控制。

- 控制信号的极性可配：可配置片选、读/写和地址锁存等信号的极性。

- 复用地址/数据模式下，支持直接 FIFO 访问，通过 FIFO 直接选择输入信号，将写操作定向到写 **EtherCAT 过程 RAM 写数据 FIFO**，并将所有读操作定向到读 **EtherCAT 过程 RAM 读数据 FIFO 读取**。

- 复用地址/数据模式下，支持单相/双相地址锁存。

## 8.2 控制逻辑

### 8.2.1 读/写控制信号

芯片支持两种不同的读/写模式：

- 读写使能：RD\_WR 管脚(RD)控制读操作，WR\_ENB 管脚 (ENB) 控制写操作。

- 使能/方向控制： RD\_WR 管脚 (RD\_WR) 控制读和写方向，WR\_ENB 管脚 (ENB) 控制读写使能。

### 8.2.2 控制信号极性

芯片支持以下信号的极性控制：

- CS: 片选输入

- RD\_WR: 读/方向

- WR\_ENB: 写/使能

- ALELO/ALEHI: 地址锁存

## 8.3 地址/数据复用模式

在地址/数据复用模式下，地址、FIFO 直接选择与数据总线复用。地址锁存支持两种方式：

- 单相地址锁存：使用 16 Bit 地址/数据管脚

- 双相地址锁存：仅使用低 8 Bit 地址/数据管脚

### 8.3.1 地址锁存周期

#### 8.3.1.1 单相地址锁存

在单相地址锁存模式下，所有地址位和 FIFO 直接选择信号都在 **ALELO** 信号的无效边沿时被锁存到芯片中。

地址通过所有 16 个地址/数据管脚进行锁存。在 8 位数据模式下，管脚 AD[15:8]专门用于地址锁存，读写数据值使用 AD[7:0]。可以通过配置选择限定 **ALELO** 信号仅在 CS 信号有效时才能锁存地址，或者仅使用 **ALELO** 信号就能锁存地址。地址锁存后，将用于所有后续的读写操作，锁存的地址将一直保持，直到复位或者下一次地址锁存。这允许多次针对相同地址进行读写请求，而无需多次执行地址锁存操作。

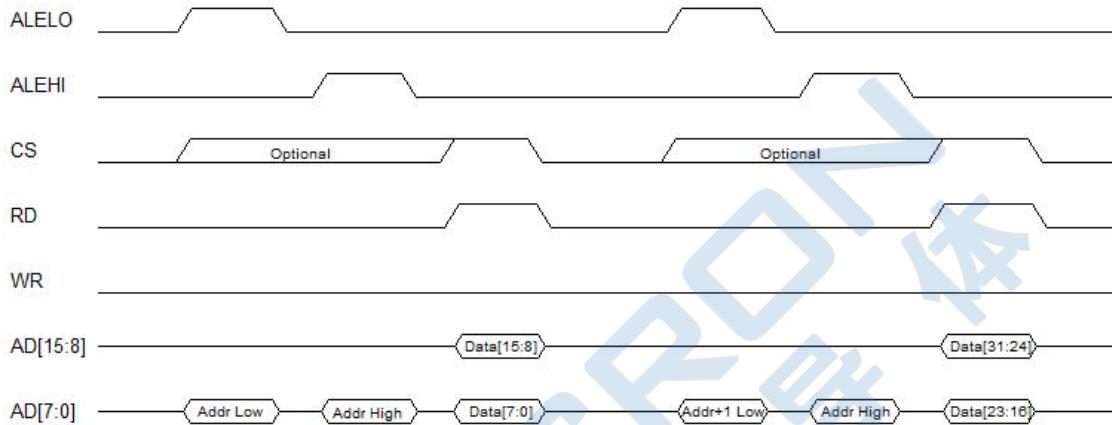

#### 8.3.1.2 双相地址锁存

在双相地址锁存模式下，地址的低 8 Bit 在 **ALELO** 信号的无效边沿时被锁存到芯片中，而地址的高位与 FIFO 直接选择信号则在 **ALEHI** 信号的无效边沿时被锁存到芯片中；两者的锁存顺序可以任意。在 8 位数据模式下，不使用管脚 AD[15:8]。在 16 位数据模式下，管脚 D[15:8]仅用于读写数据。可以通过配置选择限定 **ALELO** 和 **ALEHI** 信号仅在 CS 信号有效时才能锁存地址，或者仅使用 **ALELO** 和 **ALEHI** 信号就能锁存地址。地址锁存后，将用于所有后续的读写操作，锁存的地址将一直保持，直到复位或者下一次地址锁存。这允许多次针对相同地址进行读写请求，而无需多次执行地址锁存操作。

### 8.3.1.3 地址位到地址/数据管脚映射

在 8 Bit 数据模式下，地址 Bit 0 复用到 AD[0]管脚，地址 Bit 1 复用到 AD[1]管脚，依此类推。地址的最高位为第 9 位，在单相地址锁存模式下，复用到 AD[9]；在双相地址锁存模式下，复用到 AD[1]。锁存的地址被视为字节地址，覆盖范围为 1K Byte (0~3FFh)。

在 16Bit 数据模式下，地址 Bit 1 复用到 AD[0]管脚，地址 Bit 2 复用到 AD[1]管脚，依此类推。地址的最高位为第 9 位，在单相地址锁存模式下，复用到 AD[8]；在双相地址锁存模式下，复用到 AD[0]。锁存的地址被视为字 (16 Bit) 地址，覆盖范围为 512 字 (0 至 1FFh)。在内部访问中会将字 (16 Bit) 地址转换为字节 (8 Bit) 地址。

### 8.3.1.4 FIFO 直接选择到地址/数据管脚映射

FIFO 直接选择信号与地址一起被锁存，以允许微控制器(MCU)直接访问 **EtherCAT 过程 RAM 数据 FIFO**。FIFO 直接选择信号被复用到地址/数据管脚上，如表 8-1 所示。

表 8-1：FIFO 直接选择到地址/数据管脚映射

| 数据模式   | 单相地址锁存模式 | 双相地址锁存模式 |

|--------|----------|----------|

| 8 Bit  | AD11     | AD3      |

| 16 Bit | AD10     | AD2      |

### 8.3.2 数据访问周期

主机总线接口 (HBI) 的数据总线可以是 16 Bit 或 8 Bit, 而所有系统寄存器都是 32 Bit; 因此, 主机总线接口 (HBI) 在 8 Bit 或 16 Bit 数据模式下执行从字节 (8 Bit) 或字 (16 Bit) 到双字 (32 Bit) 的转换过程中, 分别需要在同一双字 (32 Bit) 内进行 4 次或 2 次连续访问才能完成一次读或写系统寄存器操作。

#### 8.3.2.1 写周期

当片选信号 CS 和写信号 WR 有效时 (或者当使能信号 ENB 有效且 RD\_WR 指示为写时), 发生写周期。在写周期的后沿 (WR、CS 或 ENB 变为无效时), 根据数据总线宽度, 8Bit 或 16 Bit 的写数据被锁存, 并根据锁存的地址, 将数据写入到系统寄存器。在 8 Bit 或 16 Bit 数据模式下, 微控制器 (MCU) 需要进行 4 次 8 Bit 或 2 次 16 Bit 的写操作才能完成一次双字 (32 Bit) 传输。

**注意: 写入双字 (32 Bit) 内的最高位字 (16 Bit) 或字节 (8 Bit) 会改变系统寄存器的状态, 例如 FIFO 的写指针。**

#### 8.3.2.2 读周期

当片选信号 CS 和读信号 RD 有效时 (或者当使能信号 ENB 有效且 RD\_WR 指示为读时), 发生读周期。在读周期开始时, 内部电路在锁存的地址译码下, 读取对应的寄存器并将其数值驱动到数据管脚上。根据总线宽度, 读取一个字 (16 Bit) 或一个字节 (8 Bit)。在 8 Bit 或 16 Bit 数据模式下, 微控制器 (MCU) 需要进行 4 次 8 Bit 或 2 次 16 Bit 的读操作才能完成一次双字 (32 Bit) 传输。

**注意: 读取双字 (32 Bit) 内的最高位字 (16 Bit) 或字节 (8 Bit) 会改变系统寄存器的状态, 例如 FIFO 的读指针。**

### 8.3.3 ETHERCAT 进程 RAM 数据 FIFO 访问

#### 8.3.3.1 FIFO 直接选择访问

主机总线接口(HBI) 地址/数据复用模式在地址信号中提供了一个 FIFO 直接选择信号，允许微控制器 (MCU) 直接访问 **EtherCAT 进程 RAM 数据 FIFO**。当在地址锁存周期期间锁存的 FIFO 直接选择信号处于活动状态时，所有写操作都指向 **EtherCAT 进程 RAM 写数据 FIFO**，所有读操作都来自 **EtherCAT 进程 RAM 读数据 FIFO**。并通过锁存的地址低位来选择正确的字节 (8 Bit) 或字 (16 Byte)。而其他的地址被忽略。

### 8.3.4 复用地址/数据模式功能时序图

以下时序图展示了复用地址/数据模式下，基于不同总线位宽的地址锁存、读和写周期的示例。对于本节中的时序图，应注意以下几点：

- 本节中的时序图中，ALEHI/ALELO、CS、RD 和 WR 信号的有效电平是高电平。这些信号的极性可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI ALE Polarity**、**HBI Chip Select Polarity**、**HBI Read Read/Write Polarity** 和 **HBI Write Enable Polarity** 位分别进行选择。

- 第 8.3.4.1 节 “双相地址锁存” 和第 8.3.4.2 节 “单相地址锁存” 中的时序图利用了 RD 和 WR 信号。还支持替代的 RD\_WR 和 ENB 信号，如第 8.3.4.3 节 “RD\_WR/ENB 控制模式示例” 所示。HBI 读/写模式可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI Read/Write Mode** 位进行选择。RD\_WR 和 ENB 信号的极性可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI Read Read/Write Polarity** 和 **HBI Write Enable Polarity** 位进行选择。

- ALELO/ALEHI 是否限定在 CS 信号使能时有效可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI ALE Qualification** 位进行选择。

- 在双相地址锁存模式下，ALEHI 和 ALELO 之间的锁存可以是任何顺序。

- 在单相地址锁存模式下，可以跳过 ALELO 周期，并且芯片保留最后锁存的地址。

- 对于 16 Bit 和 8Bit 模式，连续的地址周期必须在同一个双字 (32 Bit) 内，直到完全访问该双字 (32 Bit)。并且首先访问较低地址的字节 (8 Bit) 或字 (16 Bit)。

**注意：在 8 Bit 和 16 Bit 模式下，通常不会跳过 ALELO 周期，因为为了满足完整的双字周期，会按顺序访问连续的字节或字。**

#### 8.3.4.1 双相地址锁存

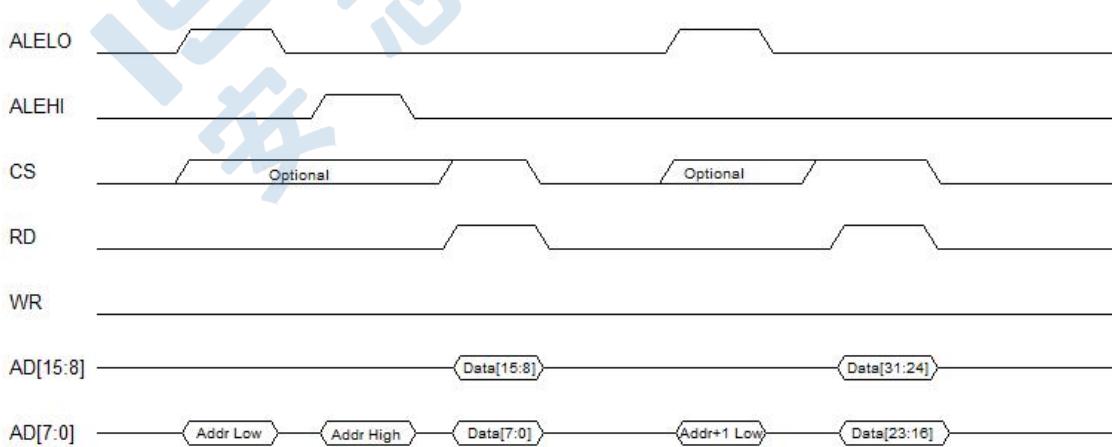

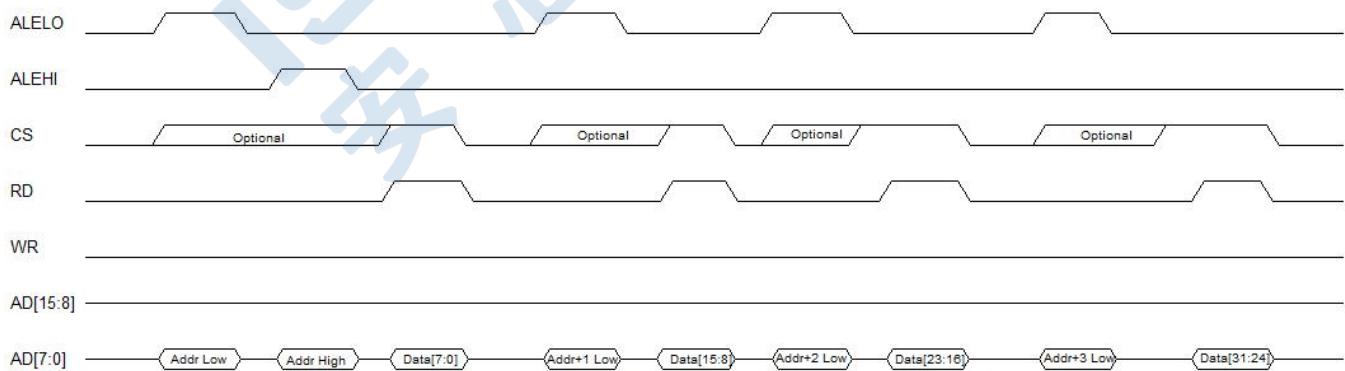

本节的时序图详细说明了在双相地址锁存的地址/数据复用模式下，16 Bit 和 8 Bit 模式的读写操作。

ISOMICRON 安芯微半导体

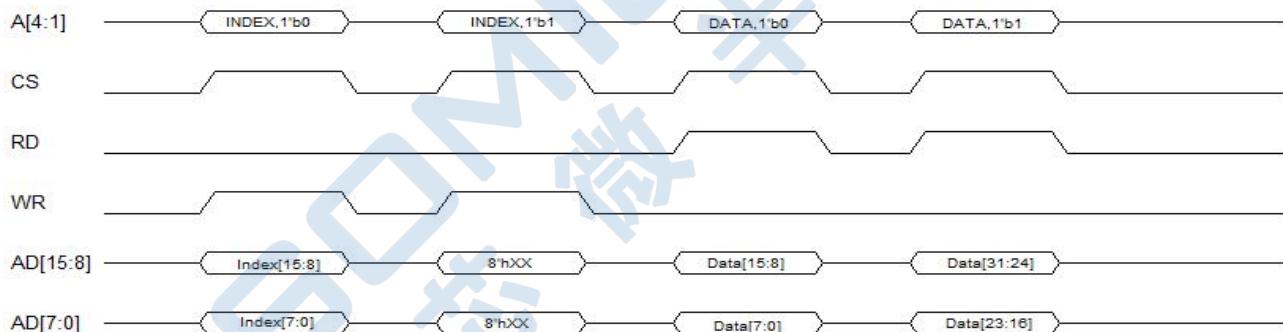

## 16 Bit 读取

地址的高低字节依次从管脚 AD[7:0]中锁存, 在地址锁存阶段, 不使用或驱动 AD[15:8]。随后在 AD[15:0]上进行读取操作。随后锁存下一个字 (16 Bit) 地址, 读取下一个字 (16 Bit) 数据, 完成双字 (32 Bit) 的读取。

图 8 - 1: 采用双相锁存的复用寻址 - 16 Bit 读取

## 16 Bit 读取并抑制 ALEHI

地址的高低字节依次从管脚 AD[7:0]中依次锁存, 在地址锁存阶段, 不使用或驱动 AD[15:8]。随后在 AD[15:0]上进行读取操作。随后仅锁存下一个字 (16 Bit) 地址的低位, 读取下一个字 (16 Bit) 数据, 完成双字 (32 Bit) 的读取。

图 8-2: 采用双相锁存的复用寻址 - 无 ALEHI 的 16 Bit 读取

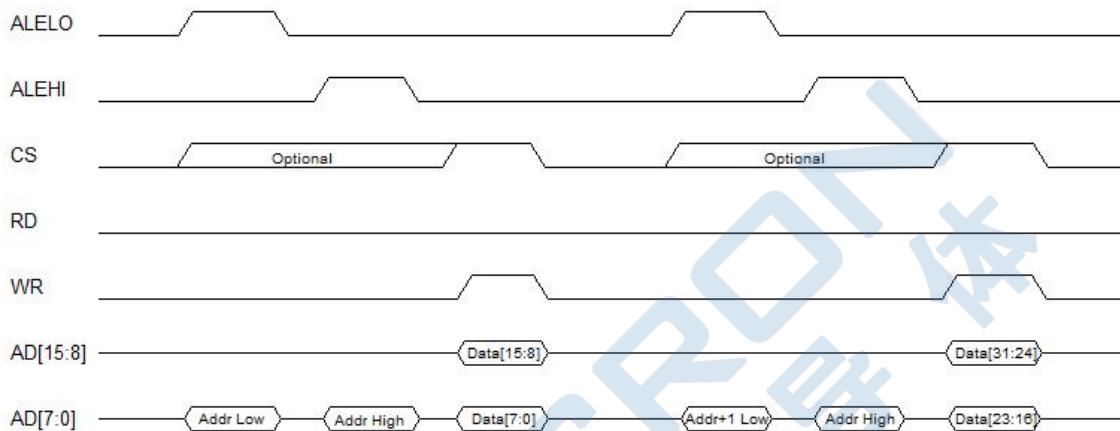

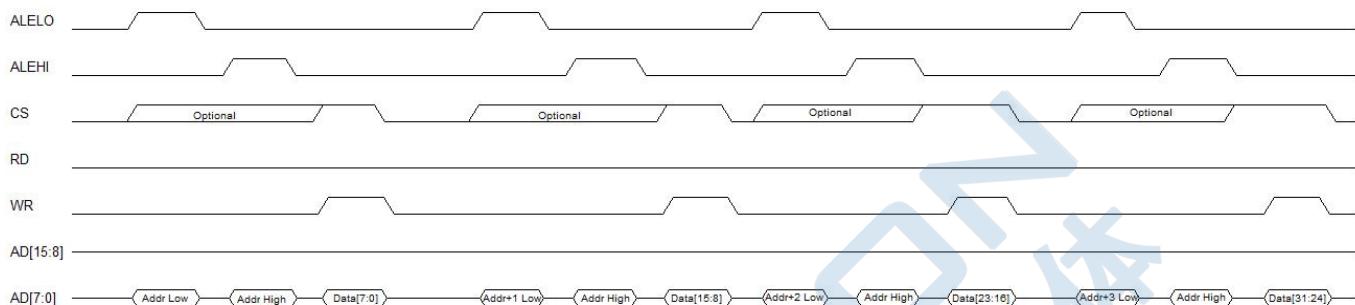

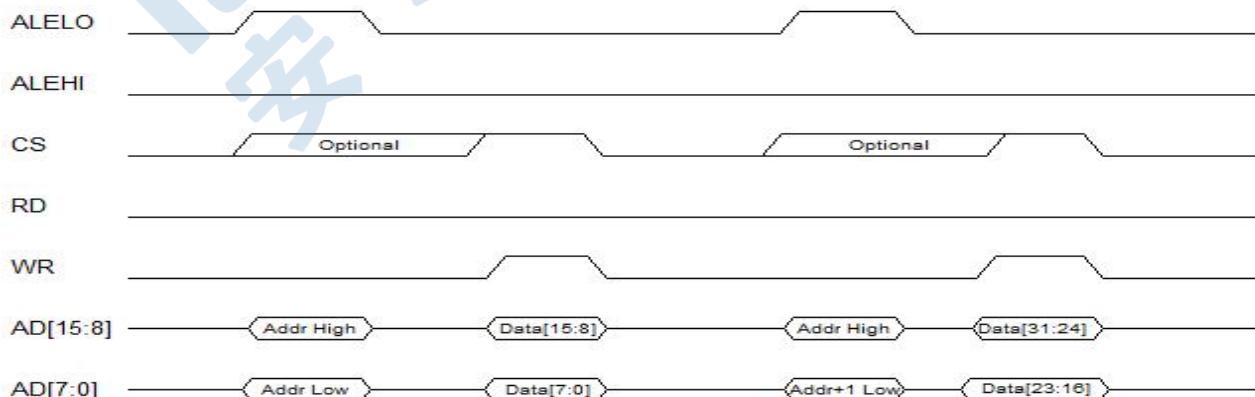

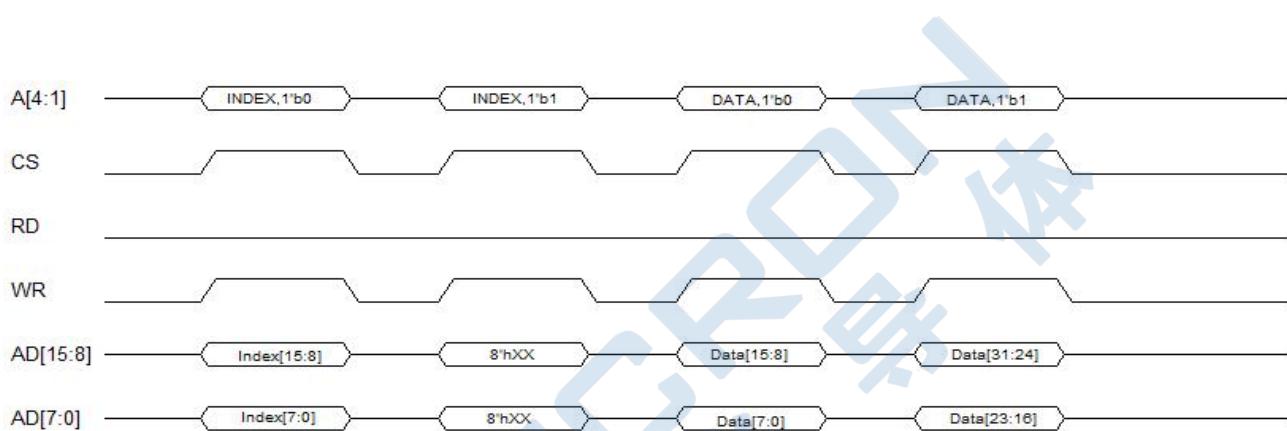

## 16 Bit 写操作

地址的高低字节依次从管脚 AD[7:0]中锁存，在地址锁存阶段，不使用或驱动 AD[15:8]。随后在 AD[15:0]上进行写操作。随后锁存下一个字（16 Bit）地址，写下下一个字（16 Bit）数据，完成双字（32 Bit）的写操作。

图 8-3: 采用双相锁存的复用寻址 - 16 Bit 写操作

## 16 Bit 写并抑制 ALEHI

地址的高低字节依次从管脚 AD[7:0]中锁存，在地址锁存阶段，不使用或驱动 AD[15:8]。随后在 AD[15:0]上进行写操作。随后仅锁存下一个字（16 Bit）地址的低位，写下下一个字（16 Bit）数据，完成双字（32 Bit）的写操作。

图 8-4: 采用双相锁存的复用寻址 - 无 ALEHI 的 16 Bit 写

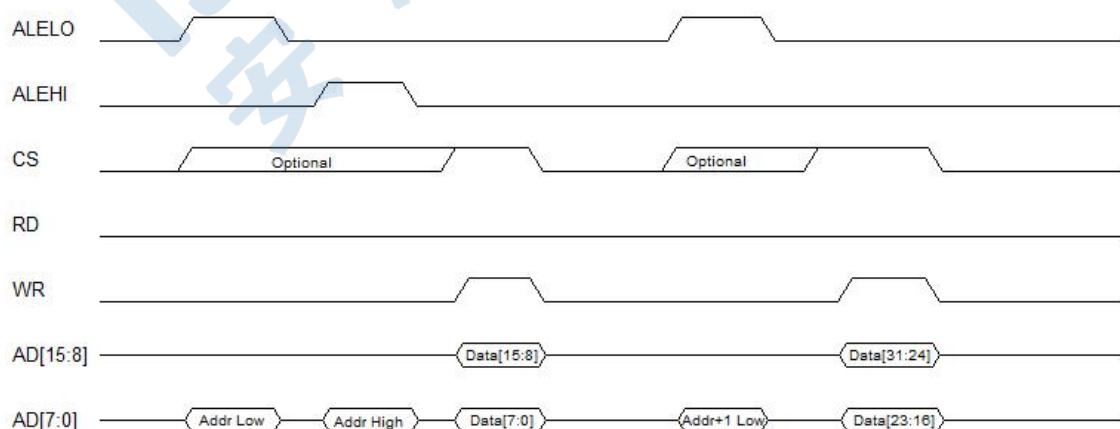

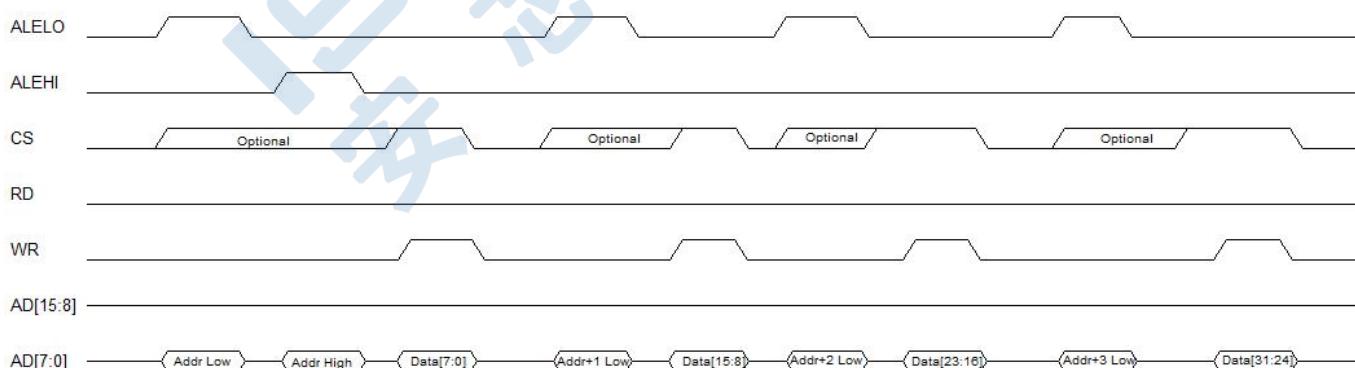

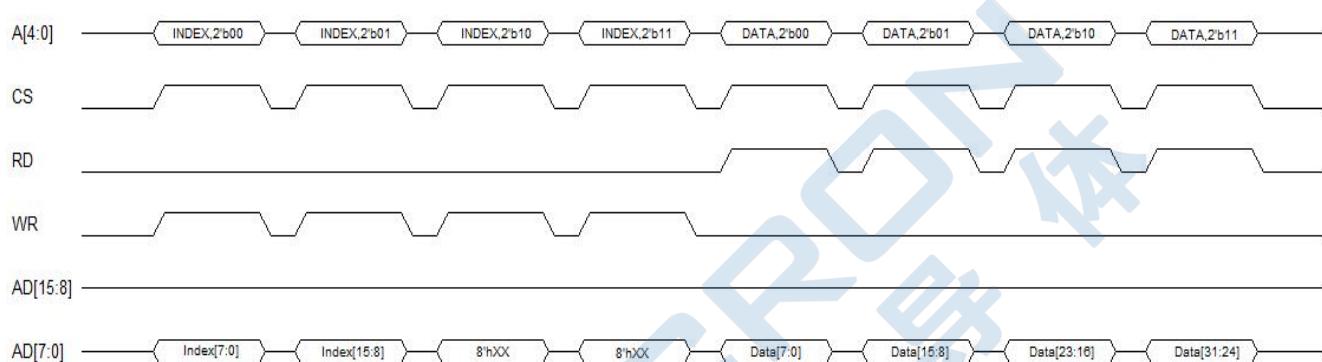

## 8 Bit 读取

地址的高低字节依次从管脚 AD[7:0]中锁存，在地址锁存阶段，不使用或驱动 AD[15:8]。随后在 AD[7:0]上进行读取操作。随后锁存下一个字节（8 Bit）地址，读取下个字节数据，连续 4 次，完成双字（32 Bit）的读取操作。

图 8-5：采用双相锁存的复用寻址 - 8 Bit 读取

## 8 Bit 读取并抑制 ALEHI 信号

地址的高低字节依次从管脚 AD[7:0]中锁存，在地址锁存阶段，不使用或驱动 AD[15:8]。随后在 AD[7:0]上进行读取操作。随后仅使用 ALELO 锁存下一个字节（8 Bit）地址低位，读取下个字节数据，连续 4 次，完成双字（32 Bit）的读取操作。

图 8-6：采用双相锁存的复用寻址 - 无 ALEHI 信号的 8 Bit 读取操作

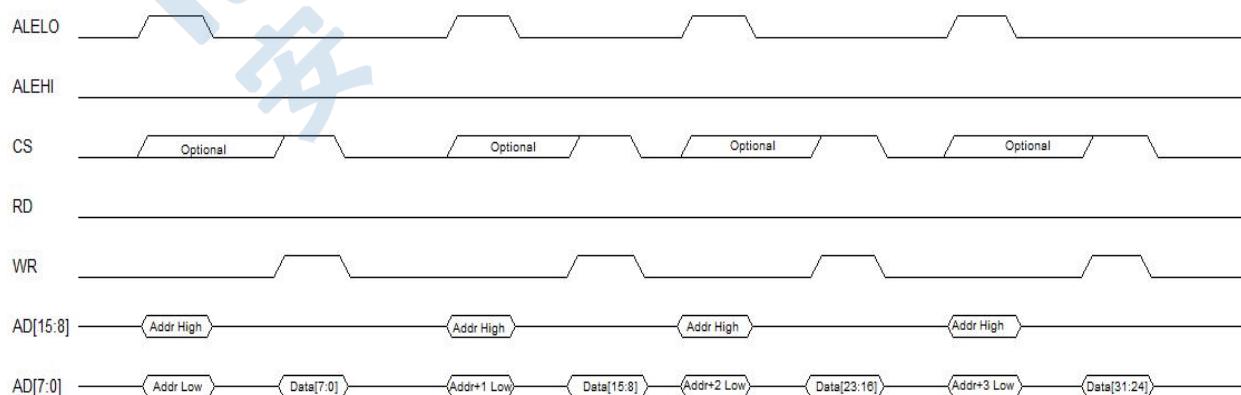

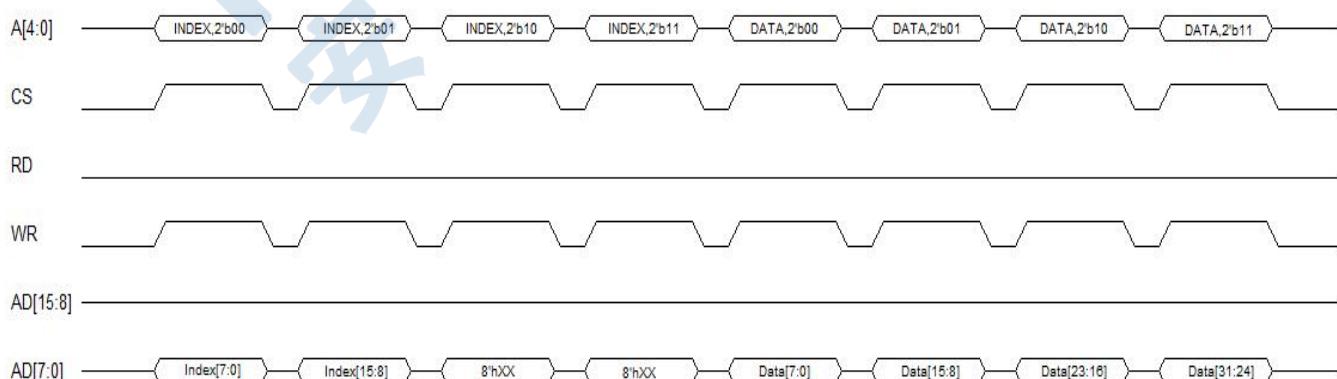

## 8 Bit 写

地址的高低字节依次从管脚 AD[7:0]中锁存，在地址锁存阶段，不使用或驱动 AD[15:8]。随后在 AD[7:0]上进行写操作。随后锁存下一个字节 (8 Bit) 地址，写下个字节数据，连续 4 次，完成双字 (32 Bit) 的写操作。

图 8-7：采用双相锁存的复用寻址-8 Bit 写

## 8 Bit 写并抑制 ALEHI 信号

地址的高低字节依次从管脚 AD[7:0]中锁存。在地址锁存阶段，不使用或驱动 AD[15:8]。随后在 AD[7:0]上进行写操作。随后仅使用 ALELO 锁存下一个字节 (8 Bit) 地址低位，写下个字节数据，连续 4 次，完成双字 (32 Bit) 的写操作。

图 8-8：采用双相锁存的复用寻址 - 不带 ALEHI 的 8 Bit 写操作

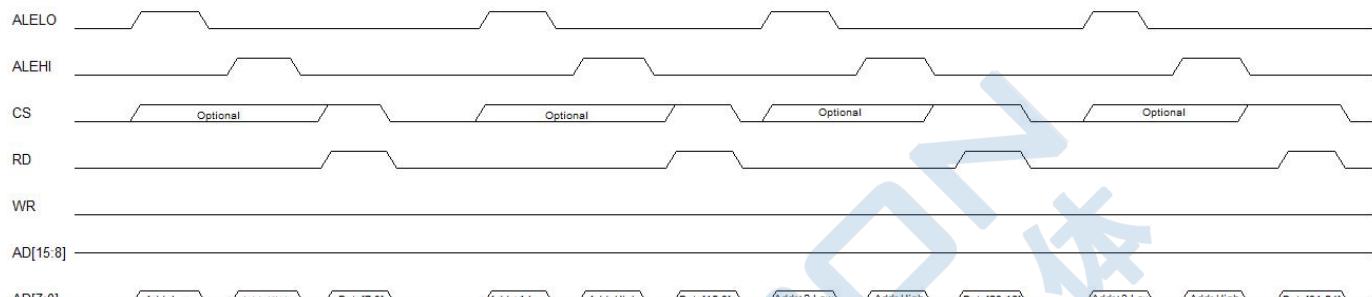

#### 8.3.4.2 单相地址锁存

本节的时序图详细说明了在 16 位和 8 位操作模式下使用单相地址锁存的地址/数据复用模式。

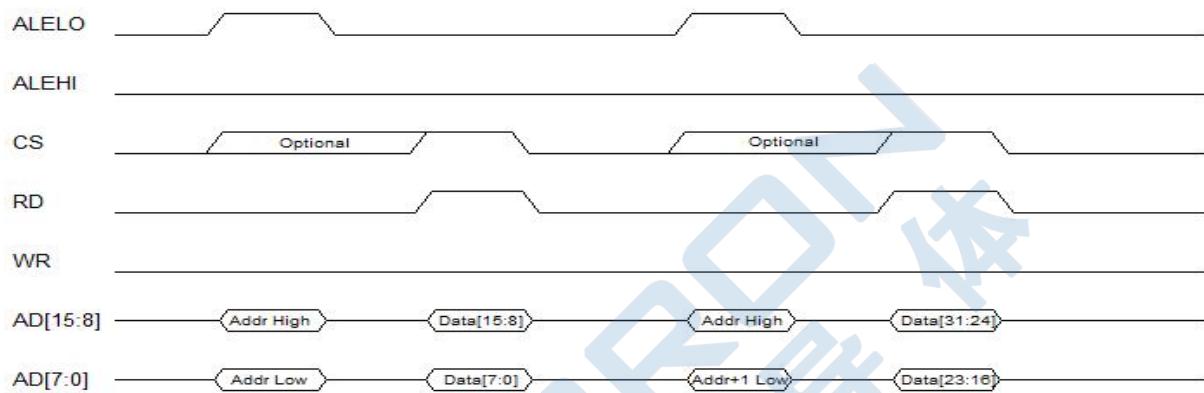

## 16 Bit 读取

地址同时从 AD[7:0]和 AD[15:8]锁存。随后在 AD[15:0]上进行读取。随后锁存下一个字 (16 Bit) 地址，读取下一个字 (16 Bit) 数据，完成双字 (32 Bit) 的读取操作。

图 8-9: 使用单相锁存的复用寻址 - 16 Bit 读取

## 16 Bit 写

地址同时从 AD[7:0]和 AD[15:8]锁存。随后在 AD[15:0]上进行写。随后锁存下一个字 (16 Bit) 地址，写下一个字 (16 Bit) 数据，完成双字 (32 Bit) 的写操作。

图 8-10: 使用单相锁存的复用寻址 - 16 Bit 写入操作

## 8 Bit 读操作

地址同时从 AD[7:0]和 AD[15:8]锁存。随后在 AD[7:0]上进行读取操作。在数据阶段不使用或驱动 AD[15:8]管脚，随后锁存下一个字节 (8 Bit) 地址，读取下一个字节 (8 Bit) 数据，连续重复 4 次，完成双字 (32 Bit) 的读取操作。

图 8-11：使用单相锁存的复用寻址 - 8 Bit 读操作

## 8 Bit 写操作

地址同时从 AD[7:0]和 AD[15:8]锁存。随后在 AD[7:0]上进行写操作。在数据阶段不使用或驱动 AD[15:8]管脚，随后锁存下一个字节 (8 Bit) 地址，写下下一个字节 (8 Bit) 数据，连续重复 4 次，完成双字 (32 Bit) 的写操作。

图 8-12：使用单相锁存的复用寻址 - 8 Bit 写操作

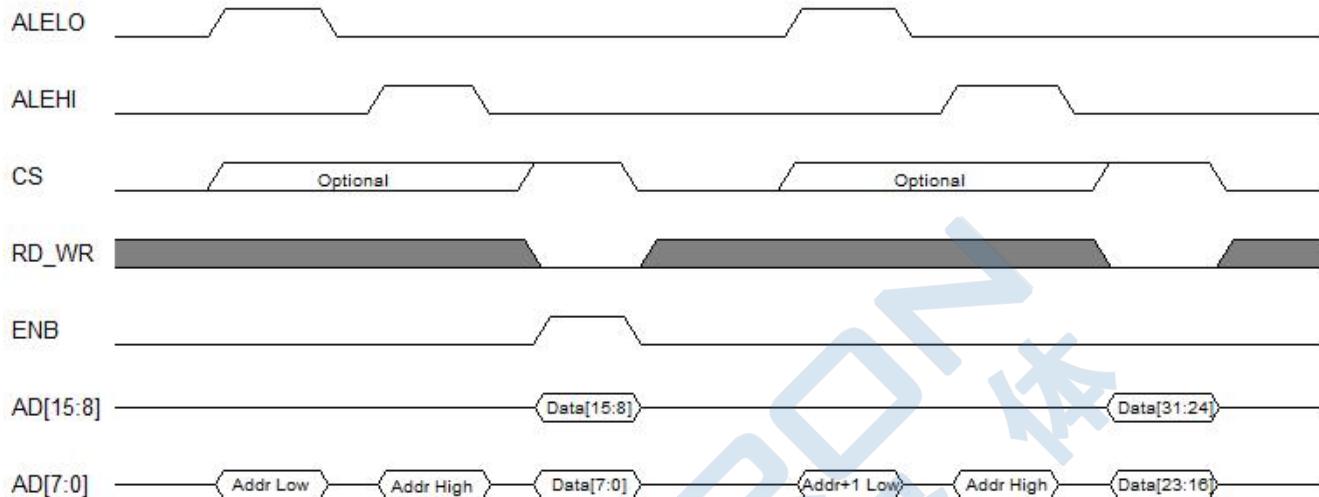

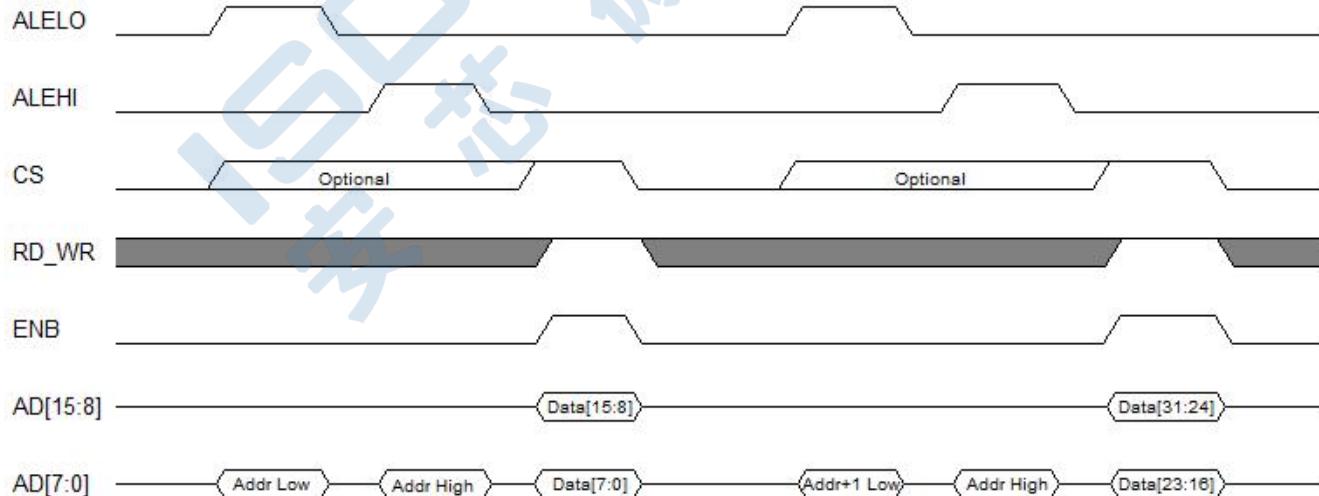

### 8.3.4.3 使能/方向控制模式示例

本节的时序图详细展示了使用使能/方向控制模式的 RD\_WR 和 ENB 信号进行读写操作。HBI 读/写模式可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI Read/Write Mode** 位选择。

本节的时序图中，ENB 信号为高电平有效，RD\_WR 信号在读取时为低电平，在写入时为高电平。RD\_WR 和 ENB 信号的极性可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI Read、Read/Write Polarity** 和 **HBI Write Enable Polarity** 位选择。

**使能/方向控制模式 16 Bit 读取：**

图 8-13: RD\_WR / ENB 控制模式示例 - 16 Bit 读取

**使能/方向控制模式 16 Bit 写：**

图 8-14: RD\_WR / ENB 控制模式示例 - 16 Bit 写入

### 8.3.5 复用寻址模式时序要求

以下图表和表格描述在地址/数据复用模式下的时序规范。对于本节中的时序规范，应注意以下几点：

- 本节中的图表描绘了高电平有效的 ALEHI、ALELO、CS、RD、WR、RD\_WR 和 ENB 信号。这些信号的极性可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI ALE Polarity**、**HBI Chip Select Polarity**、**HBI Read Read/Write Polarity** 和 **HBI Write Enable Polarity** 位分别选择。

- ALELO 和/或 ALEHI 与 CS 信号的限定可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI ALE Qualification** 位选择。这在图中以虚线表示。仅当此模式处于活动状态时，ALELO/ALEHI 与 CS 之间的时序要求才适用。

- 在双相地址锁存模式下，ALEHI 和 ALELO 周期可以是任意顺序。图中实线表示先 ALEHI，虚线表示先 ALELO。

- 一个读取周期之后可能跟随一个地址周期、一个写入周期或者另一个读取周期。一个写入周期之后可能跟随一个读取周期或者另一个写入周期。这些在图中以虚线表示。

### 8.3.5.1 读取时序要求

有效极性为高电平时：

- 如果使用 RD 和 WR 信号，当 RD 在 CS 为 1 时被置 1，主机读取周期开始，读周期在 RD 被置 0 时结束。CS 可以与 RD 同时被置 1 和置 0。

- 如果使用 RD\_WR 和 ENB 信号，当 ENB 为 1、CS 为 1 且 RD\_WR 指示读取时，主机读取周期开始。该周期在 ENB 被置 0 时结束。CS 可以与 ENB 同时设置

有效极性为低电平时：

- 如果使用 RD 和 WR 信号，当 RD 在 CS 为 0 时被置 0，主机读取周期开始，读周期在 RD 被置 1 时结束。CS 可以与 RD 同时被置 0 和置 1。

- 如果使用 RD\_WR 和 ENB 信号，当 ENB 为 0、CS 为 0 且 RD\_WR 指示读取时，主机读取周期开始。该周期在 ENB 被置 1 时结束。CS 可以与 ENB 同时设置

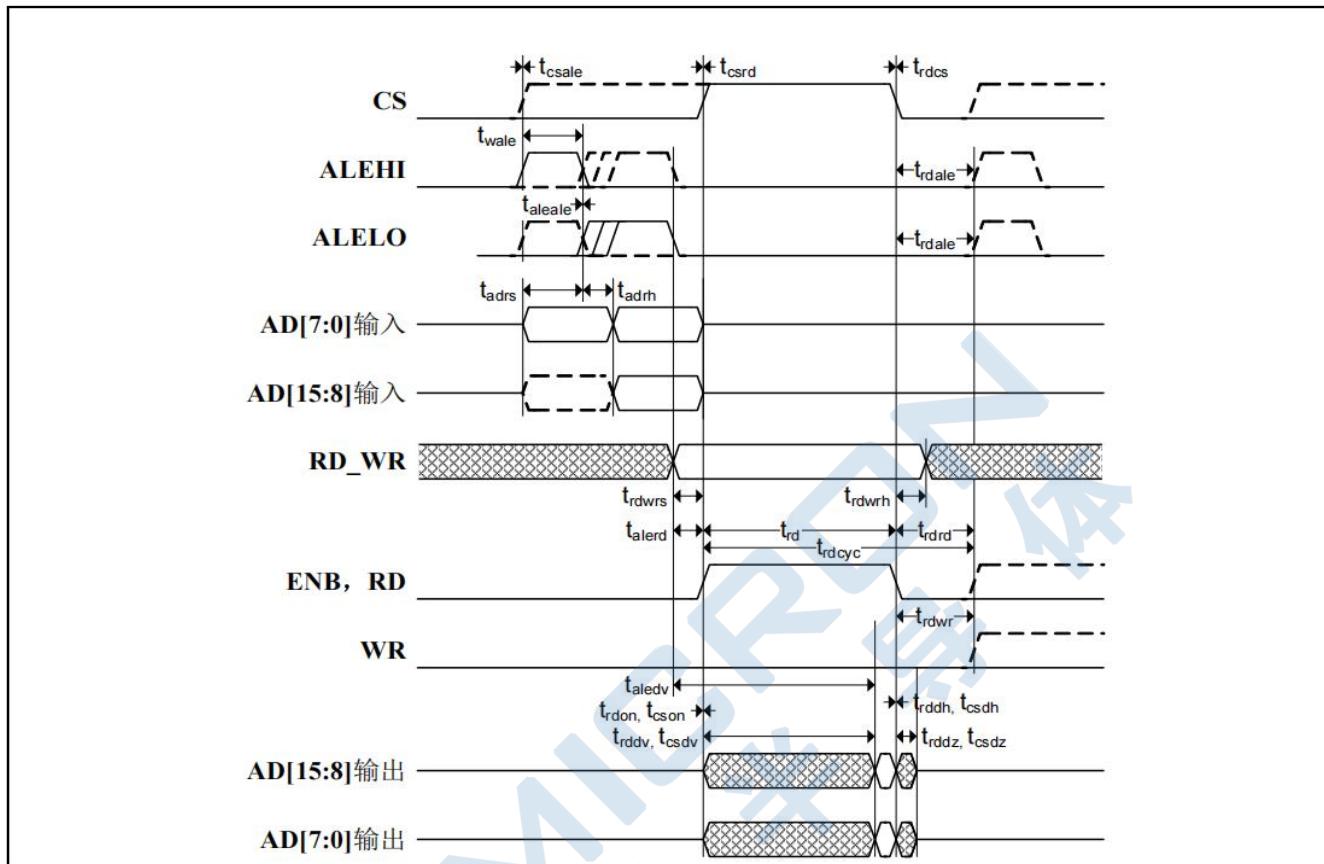

图 8-15: 复用寻址读周期时序

表 8-2: 复用寻址读周期时序值

| 符号          | 描述                              | Min | Typ | Max | units |

|-------------|---------------------------------|-----|-----|-----|-------|

| $t_{csale}$ | ALELO/ALEHI 有效前 CS 有效的建立时间      | 0   |     |     | ns    |

| $t_{csrd}$  | RD/ENB 有效前 CS 有效的建立时间           | 0   |     |     | ns    |

| $t_{rdcs}$  | RD/ENB 无效后 CS 有效的保持时间           | 0   |     |     | ns    |

| $t_{wale}$  | ALELO/ALEHI 有效脉冲宽度时间            | 10  |     |     | ns    |

| $t_{adrs}$  | ALELO/ALEHI 无效前 Address 有效的建立时间 | 10  |     |     | ns    |

| $t_{adrh}$  | ALELO/ALEHI 无效后 Address 有效的保持时间 | 5   |     |     | ns    |

| $t_{alerd}$ | ALELO/ALEHI 无效后到 RD/ENB 有效的时间   | 10  |     |     | ns    |

| $t_{rdwrs}$ | ENB 有效前 RD_WR 有效的建立时间           | 5   |     |     | ns    |

| $t_{rdwrh}$ | ENB 无效后 RD_WR 有效的保持时间           | 5   |     |     | ns    |

| $t_{rdon}$  | RD/ENB 有效后, 到数据缓存输出开启的时间        | 0   |     |     | ns    |

| $t_{rddv}$  | RD/ENB 有效后, 到数据输出有效的时间          |     |     | 65  | ns    |

| $t_{rddh}$  | RD/ENB 无效后, 数据输出有效的保持时间         | 0   |     |     | ns    |

| $t_{rddz}$  | RD/ENB 无效后, 到数据缓存输出关闭的时间        |     |     | 30  | ns    |

| $t_{cs0n}$  | CS 有效后, 到数据输出有效的时间              | 0   |     |     | ns    |

| $t_{csdv}$  | CS 有效后, 到数据输出有效的时间              |     |     | 65  | ns    |

| $t_{csdh}$  | CS 无效后, 数据输出有效的保持时间             | 0   |     |     | ns    |

| $t_{csdz}$  | CS 无效后, 到数据缓存输出关闭的时间            |     |     | 30  | ns    |

| $t_{aledv}$ | ALELO/ALEHI 无效后, 到数据输出有效的时间     |     |     | 75  | ns    |

| $t_{rd}$    | RD/ENB 的有效时间                    | 65  |     |     | ns    |

| $t_{rdcyc}$ | RD/ENB 的周期时间                    | 95  |     |     | ns    |

| $t_{rdale}$ | 下次地址锁存之前, RD/ENB 保持无效的时间        | 30  |     |     | ns    |

| 符号         | 描述                     | Min | Typ | Max | units |

|------------|------------------------|-----|-----|-----|-------|

| $t_{rdrd}$ | 下次读周期前, RD/ENB 保持无效的时间 | 30  |     |     | ns    |

| $t_{rdwr}$ | 下次写周期前, RD 保持无效的时间     | 30  |     |     | ns    |

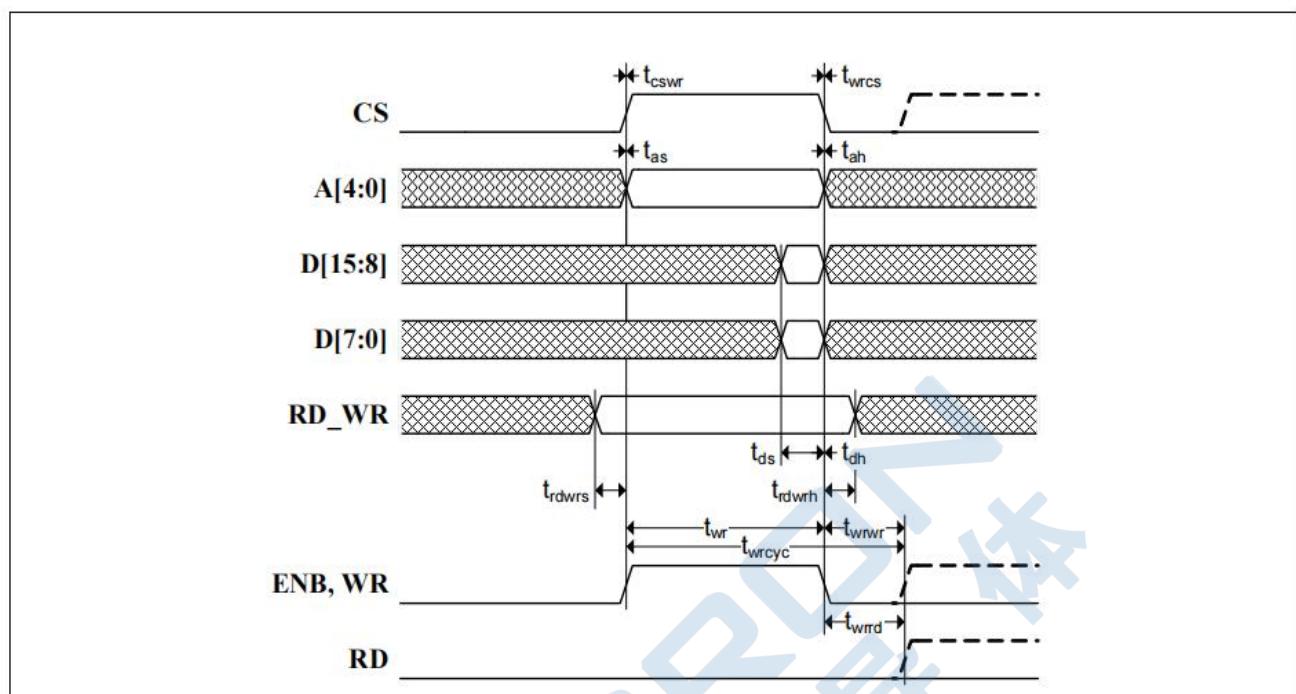

### 8.3.5.2 写入时序要求

有效极性为高电平时：

- 如果使用 RD 和 WR 信号，主机写入周期在 WR 置 1 且 CS 置 1 时开始。写周期在 WR 被置 0 时结束。CS 可以与 WR 同时设置。

- 如果使用 RD\_WR 和 ENB 信号，主机写入周期在 ENB 为 1、CS 为 1 且 RD\_WR 指示写入时开始。该周期在 ENB 置 0 时结束。CS 可以与 ENB 同时设置。

有效极性为低电平时：

- 如果使用 RD 和 WR 信号，主机写入周期在 WR 置 0 且 CS 置 0 时开始。写周期在 WR 被置 1 时结束。CS 可以与 WR 同时设置。

- 如果使用 RD\_WR 和 ENB 信号，主机写入周期在 ENB 为 0、CS 为 0 且 RD\_WR 指示写入时开始。该周期在 ENB 置 1 时结束。CS 可以与 ENB 同时设置。

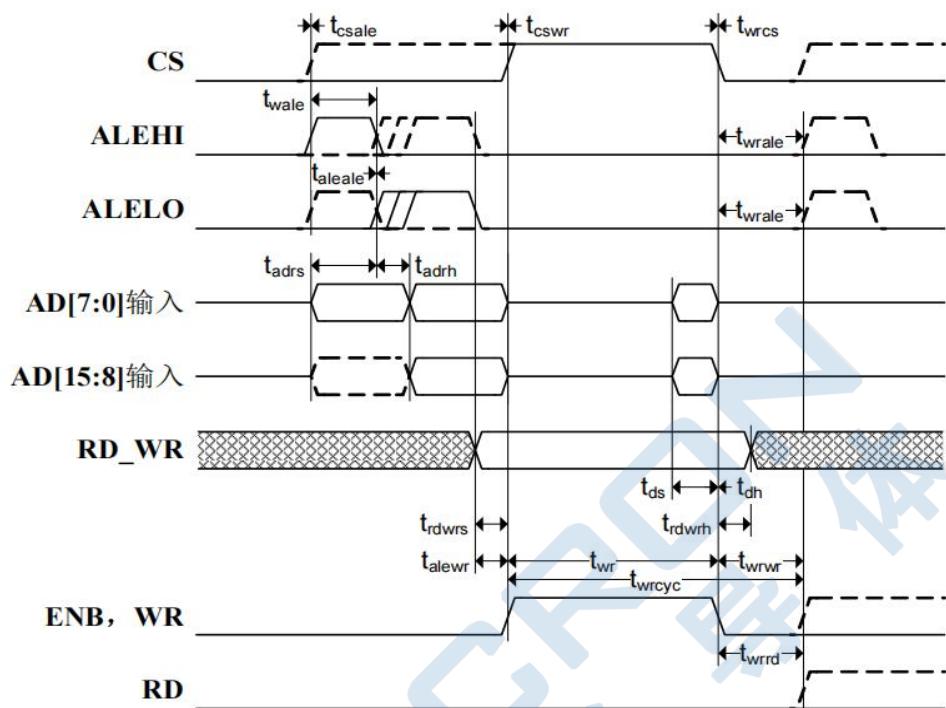

图 8 - 16: 复用寻址写周期时序

表 8-2: 复用寻址写周期时序值

| 符号           | 描述                                         | Min | Typ | Max | Units |

|--------------|--------------------------------------------|-----|-----|-----|-------|

| $t_{csale}$  | ALELO/ALEHI 有效前CS有效的建立时间                   | 0   |     |     | ns    |

| $t_{cswr}$   | WR/ENB 有效前CS有效的建立时间                        | 0   |     |     | ns    |

| $t_{wrCS}$   | WR/ENV 无效后CS有效的保持时间                        | 0   |     |     | ns    |

| $t_{wale}$   | ALELO/ALEHI有效的脉冲宽度时间                       | 10  |     |     | ns    |

| $t_{adrs}$   | ALELO/ALEHI 无效前Address有效的建立时间              | 10  |     |     | ns    |

| $t_{adrh}$   | ALELO/ALEHI 无效后Address有效的保持时间              | 5   |     |     | ns    |

| $t_{aleale}$ | 从ALELO无效到ALEHI有效的时间<br>从ALEHI无效到ALELO有效的时间 | 0   |     |     | ns    |

| $t_{alewr}$  | 从ALELO/ALEHI无效到WR/ENB有效的时间                 | 10  |     |     | ns    |

| $t_{rdwrs}$  | ENB有效前RD_WR有效的建立时间                         | 5   |     |     | ns    |

| $t_{rdwrh}$  | ENB无效后, RD_WR有效的保持时间                       | 5   |     |     | ns    |

| $t_{ds}$     | WR/ENB 无效前Data有效的建立时间                      | 7   |     |     | ns    |

| $t_{dh}$     | WR/ENB 无效后Data有效的保持时间                      | 0   |     |     | ns    |

| $t_{wr}$     | WR/ENB的有效时间                                | 65  |     |     | ns    |

| $t_{wrcyc}$  | WR/ENB的周期时间                                | 95  |     |     | ns    |

| $t_{wrale}$  | 下次地址锁存之前, WR/ENB保持无效的时间                    | 30  |     |     | ns    |

| $t_{wrwr}$   | 下次写周期前, WR/ENB保持无效的时间                      | 30  |     |     | ns    |

| $t_{wrrd}$   | 下次读周期前, WR保持无效的时间                          | 30  |     |     | ns    |

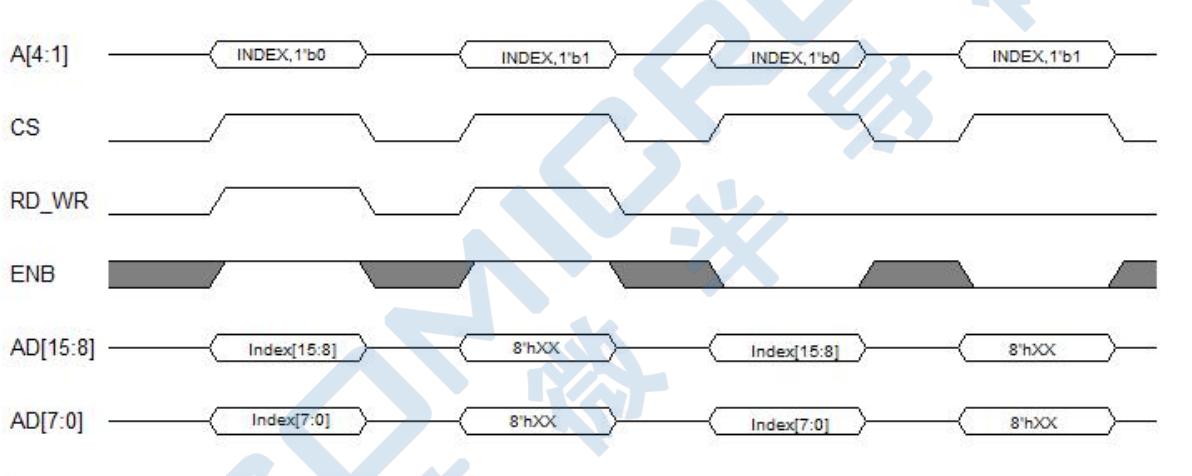

## 8.4 寄存器索引模式

在寄存器索引模式下，通过索引寄存器和数据寄存器的间接映射来访问系统寄存器。系统寄存器的地址写入到索引寄存器中，然后访问相关联的数据寄存器等价于访问索引寄存器所指向的系统寄存器。寄存器索引模式实现了3组索引/数据寄存器，允许在多线程操作中避免一个线程覆盖另一个线程设置的索引值。此外，还实现了一个额外的数据寄存器用于直接访问 FIFO。主机总线接口的地址信号映射如下：

- 在8位数据模式下，主机地址输入(ADDR[4:0])为字节地址。

- 在16位数据模式下，ADDR0未提供，主机地址输入(ADDR[4:1])为字地址。

如第8.4.4.1节“索引寄存器直接访问 FIFO”所述，当在地址18h-1Bh进行读写操作时，将访问EtherCAT过程RAM数据FIFO。

表8-3：主机总线接口寄存器索模式的寄存器映射

| 字节地址      | 符号               | 寄存器名称                                                |

|-----------|------------------|------------------------------------------------------|

| 00h - 03h | HBI_IDX_0        | 主机总线接口索引寄存器0                                         |

| 04h - 07h | HBI_DATA_0       | 主机总线接口数据寄存器0                                         |

| 08h - 0Bh | HBI_IDX_1        | 主机总线接口索引寄存器1                                         |

| 0Ch - 0Fh | HBI_DATA_1       | 主机总线接口数据寄存器1                                         |

| 10h - 13h | HBI_IDX_2        | 主机总线接口索引寄存器2                                         |

| 14h - 17h | HBI_DATA_2       | 主机总线接口数据寄存器2                                         |

| 18h - 1Bh | PROCESS_RAM_FIFO | EtherCAT 过程 RAM 写数据 FIFO<br>EtherCAT 过程 RAM 读数据 FIFO |

### 8.4.1 主机总线接口索引寄存器

索引寄存器可按字 (16 Bit) 或字节 (8 Bit) 进行写入, 具体取决于数据位宽模式。索引寄存器的格式如下:

| Bits  | 描述                                                                                                                                                                                                                                               | 权限  | 默认值   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 31:16 | 保留                                                                                                                                                                                                                                               | RO  | -     |

| 15:0  | <p>内部地址</p> <p>访问相应数据寄存器时使用的地址。</p> <p><b>注意: 每个索引寄存器提供的内部地址始终被视为字节地址。</b></p> <p>在 16 Bit 数据位宽下, 在访问对应的数据寄存器时, 通过索引寄存器存放的地址加地址信号的 A[1]访问寄存器的字 (16 Bit) 偏移</p> <p>在 8 Bit 数据位宽下, 在访问对应的数据寄存器时, 通过索引寄存器存放的地址加地址信号的 A[1:0]来访问寄存器的字节 (8 Bit) 偏移</p> | R/W | 1234h |

## 8.4.2 索引寄存器访问

主机总线接口 (HBI) 的数据信号可以是 16 Bit 或 8 Bit 宽。HBI 索引寄存器为 32 位宽，可根据数据位宽模式以字 (16 Bit) 或字节 (8 Bit) 的形式写入。

### 8.4.2.1 写周期

当片选信号 CS 和写信号 WR 同时有效时 (或当使能信号 ENB 有效且 RD\_WR 指示为写操作时)，启动写周期。在写周期的无效沿 (即 WR、CS 或 ENB 变为无效时)，根据地址信号的译码，将数据信号锁存，并写入到对应的索引寄存器中。根据数据总线位宽，写入内容可以是一个字 (16 Bit) 或一个字节 (8 Bit)。在 16 Bit 数据模式下，不支持单独的字节 (8 Bit) 访问。

### 8.4.2.2 读周期

当片选信号 CS 和读信号 RD 同时有效时 (或当使能信号 ENB 有效且 RD\_WR 指示为读操作时)，发生读周期。在读周期开始时，根据地址信号的译码，从对应的索引寄存器读取数据，并将通过数据管脚将数据输出。根据总线宽度，读取内容可以是一个字 (16 Bit) 或一个字节 (8 Bit)。

### 8.4.3 系统寄存器访问

主机总线接口可以通过访问与索引寄存器相关联的数据寄存器访问内部的系统寄存器，索引寄存器提供了内部系统寄存器的字节(8 Bit)地址，并通过地址信号 A[1:0] 或者 A[1] 选择寄存器对应的字节 (8 Bit) 或字 (16 Bit)。主机总线接口 (HBI) 的数据总线位宽可以是 16Bit 或 8 Bit，而所有的系统寄存器均为 32 Bit。如果要完成系统寄存器的双字(32 Bit)访问，需要在 8 Bit 或 16 Bit 数据位宽模式下，进行 4 次或 2 次访问才能完成。

**注意：访问数据寄存器或 FIFO 直接地址访问寄存器的高位字 (16 Bit) 或字节 (8 Bit) 会改变内部系统寄存器的状态，例如 FIFO 的写指针、FIFO 的读指针。**

#### 8.4.3.1 写周期

当 CS 和 WR 有效时（或者当 ENB 有效且 RD\_WR 指示写操作时），发生一个写周期。主机总线接口上的地址信号选择一个索引寄存器相关联的数据寄存器。在写周期的后沿（WR、CS 或 ENB 变为无效），数据信号被锁存，并根据数据总线位宽、索引寄存器存放的地址、以及地址信号的译码，将数据写入到索引寄存器指向的系统寄存器中。

#### 8.4.3.2 读取周期

当 CS 和 RD 有效时（或者当 ENB 有效且 RD\_WR 指示读取时），发生读取周期。主机总线接口上的地址信号选择一个索引寄存器相关联的数据寄存器。在读周期的前沿，根据数据总线位宽、索引寄存器存放的地址、以及地址信号的译码，读取索引寄存器指向的系统寄存器，并将通过数据管脚将数据输出。

#### 8.4.4 直接访问 FIFO

除了通过索引寄存器访问系统寄存器之外，还可以绕过索引寄存器，并在地址 18h-1Bh 处直接访问 FIFO。在此地址上，主机写操作将写入 **EtherCAT 过程 RAM 写数据 FIFO**，而主机读操作则从 **EtherCAT 过程 RAM 读数据 FIFO** 中读取数据。此访问方式不涉及相关的索引寄存器。可以通过地址信号 A[1:0] 或者 A[1] 选择 FIFO 对应的字节 (8 Bit) 或字 (16 Bit)。

#### 8.4.5 寄存器索引模式功能时序图

本节的时序图展示了在各种配置和总线位宽下，寄存器索引模式读取和写入操作的示例。对于本节中的时序图，需要注意以下几点：

- 本节中的图表的片选 (CS)、读取 (RD) 和写入 (WR) 信号是高电平有效的。这些信号的极性可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI Chip Select Polarity**、**HBI Read Read/Write Polarity** 和 **HBI Write Enable Polarity** 位分别进行选择。

- 本节中的图表使用了 RD 和 WR 信号。也支持替代的 RD\_WR 和 ENB 信号，类似于第 8.4.5.3 节“**RD\_WR / ENB 控制模式示例**”中的复用示例。HBI 读/写模式可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI Read/Write Mode** 位进行选择。RD\_WR 和 ENB 信号的极性可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI Read Read/Write Polarity** 和 **HBI Write Enable Polarity** 位进行选择。

#### 8.4.5.1 索引寄存器访问

本节的时序图表详细说明了在寄存器索引模式下，基于 16 Bit 和 8 Bit 数据位宽的索引寄存器读写操作。

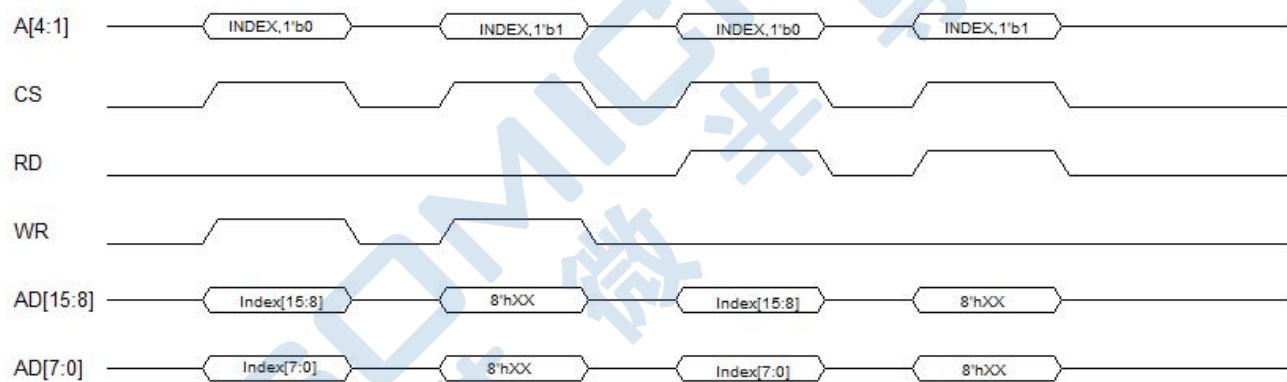

##### 16 Bit 读写操作

对于写操作，地址 A[4:2] 选择某个索引寄存器，地址 A[1]设置为 0b 时，写索引寄存器的低 16 Bit。数据在 WR 信号下降沿通过 D[15:0]写入。将地址 A[1]设置为 1b 时，写索引寄存器的高 16 Bit。

对于读操作，地址 A[4:2] 选择某个索引寄存器，地址 A[1]设置为 0b 时，读索引寄存器的低 16 Bit。在 RD 信号有效期间，读取的数据通过 D[15:0]输出。地址 A[1]设置为 1b 时，读索引寄存器的高 16 Bit。

图8-17: 访问索引寄存器 - 16 Bit 写/读

## 8 Bit 读写操作

对于写操作，地址 A[4:2] 选择某个索引寄存器，地址 A[1:0] 设置为 00b 时，写索引寄存器的低 8 Bit，在 WR 信号的下降沿将数据通过 D[7:0] 写入。D[15:8] 管脚不使用或驱动。将地址 A[1:0] 设置为 01b, 10b, 11b 时，写索引寄存器的其余字节。

对于读操作，地址 A[4:2] 选择某个索引寄存器，地址 A[1:0] 设置为 00b 时，读索引寄存器的低 8 Bit，在 RD 信号有效期间，读取的数据会通过 D[7:0] 输出。D[15:8] 管脚不使用或驱动。将地址 A[1:0] 设置为 01b, 10b, 11b 时，读索引寄存器的其余字节。

图 8-18：访问索引寄存器 - 8 Bit 写/读

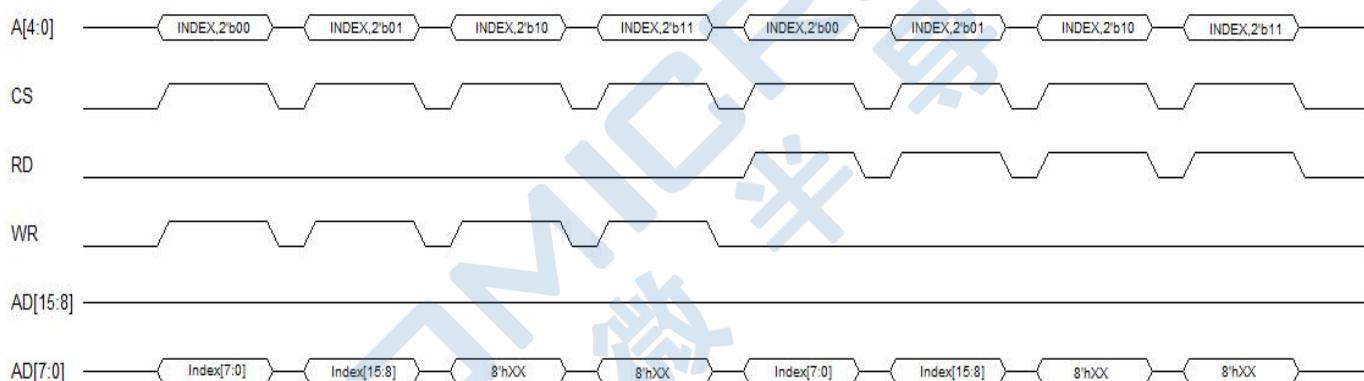

#### 8.4.5.2 系统寄存器访问

本节的时序图表详细说明了在寄存器索引模式下，基于 16 Bit 和 8 Bit 数据位宽的系统寄存器读写周期。这包括一个索引寄存器写入，随后是数据寄存器的读取或写入。

#### 16 Bit 读取

根据 8.4.5.1 描述的方法将系统寄存器的地址写入到其中一个索引寄存器中。然后地址 A[4:2] 选择对应的数据寄存器，设置地址 A[1] 为 0b 时，读相应系统寄存器的低 16 Bit。在 RD 有效期间，读取的数据会在 D[15:0] 上输出。将地址 A[1] 设置为 1b 时，读相应系统寄存器的高 16 Bit。

图 8-19：访问系统寄存器 - 16 位读取

## 16 Bit 写入

根据 8.4.5.1 描述的方法将系统寄存器的地址写入到其中一个索引寄存器中。然后地址 A[4:2] 选择对应的数据寄存器，地址 A[1] 设置为 0b 时，写相应系统寄存器的低 16 Bit。在 WR 的后沿，D[15:0] 上的数据被写入。地址 A[1] 设置为 1b 时，写相应系统寄存器的高 16 Bit。

图 8 - 20: 访问系统寄存器 - 16 位写入

## 8 Bit 读操作

根据 8.4.5.1 描述的方法将系统寄存器的地址写入到其中一个索引寄存器中。然后地址 A[4:2] 选择对应的数据寄存器，地址 A[1:0] 设置为 00b 时，读取系统寄存器的低 8 Bit。在读取 (RD) 有效期间，读取的数据会在 D[7:0] 上输出。D[15:8] 管脚未被使用或驱动。地址 A[1:0] 设置为 01b, 10b, 11b 时，读取系统寄存器的其余字节。

图 8 - 21: 访问系统寄存器 - 8 位读操作

## 8 位写操作

根据 8.4.5.1 描述的方法将系统寄存器的地址写入到其中一个索引寄存器中。然后地址 A[4:2] 选择数据寄存器，地址 A[1:0] 设置为 00b 时，写系统寄存器的低 8 Bit。在写入 (WR) 信号的后沿，D[7:0] 上的数据被写入。D[15:8] 管脚未被使用或驱动。地址 A[1:0] 设置为 01b, 10b, 11b 时，写入系统寄存器的其余字节。

图 8 - 22: 访问系统寄存器 - 8 位写操作

### 8.5.5.3 使能/方向控制模式示例

本节中的时序图详细说明了使用替代的 RD\_WR 和 ENB 信号进行的读写操作。HBI 读/写模式可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI Read/Write Mode** 位进行选择。

本节中的 ENB 信号为高电平有效，RD\_WR 信号在读取时为低电平，在写入时为高电平。RD\_WR 和 ENB 信号的极性可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI Read Read/Write Polarity** 和 **HBI Write Enable Polarity** 位进行选择。

图 8-23：读写/使能控制模式示例 - 16 位写/读操作

### 8.4.6 寄存器索引模式时序要求

以下图表和表格描述在寄存器索引模式下的时序规范。对于本节中的时序规范，应注意以下几点：

- 本节中的图表描绘了高电平有效的片选 (CS)、读 (RD)、写 (WR)、读/写 (RD\_WR) 和使能 (ENB) 信号。这些信号的极性可通过 **PDI 配置寄存器 (HBI 模式)** 中的 **HBI Chip Select Polarity**、**HBI Read Read/Write Polarity** 和 **HBI Write Enable Polarity** 位分别选择。

- 一个读周期可能后面跟着一个写周期或者另一个读周期。一个写周期可能后面跟着一个读周期或者另一个写周期。这些情况以虚线表示。

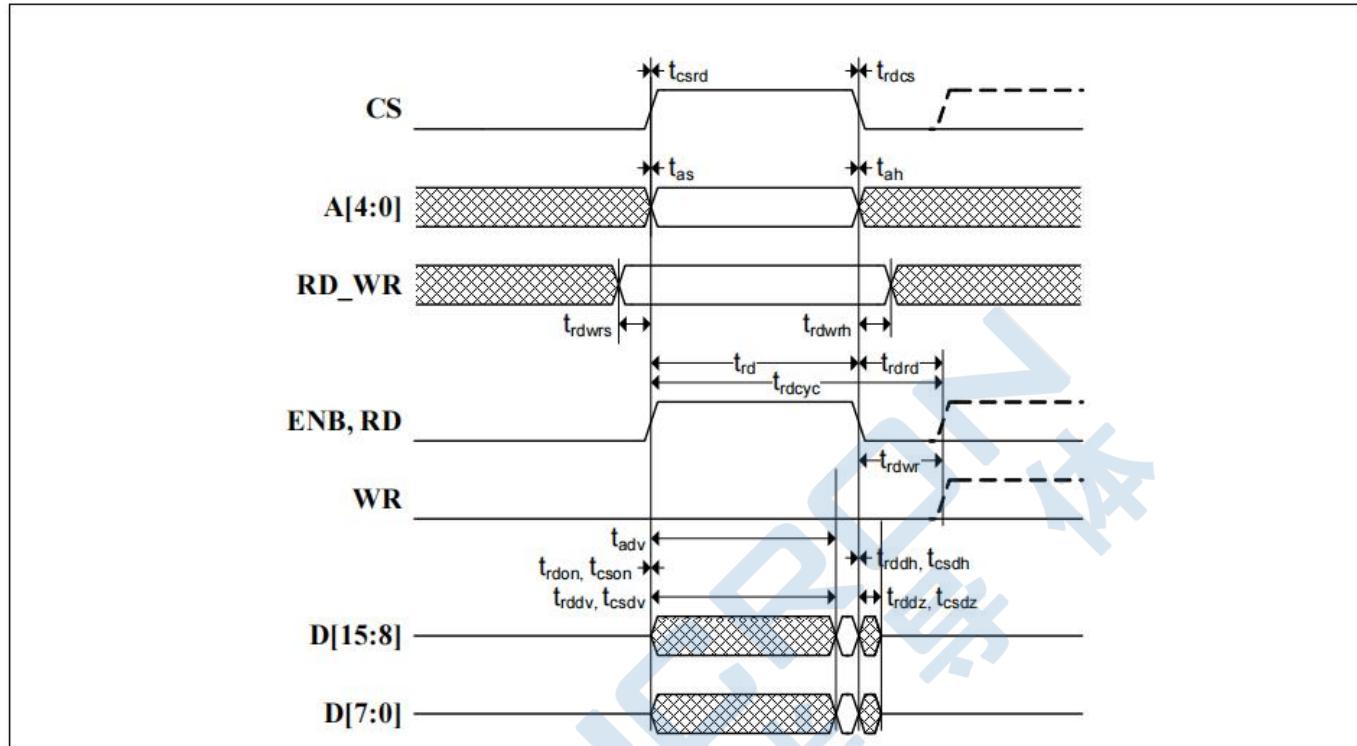

#### 8.4.6.1 读时序要求

有效极性为高电平时：

- 如果使用 RD 和 WR 信号，当 RD 在 CS 为 1 时被置 1，主机读取周期开始，读周期在 RD 被置 0 时结束。CS 可以与 RD 同时被置 1 和置 0。

- 如果使用 RD\_WR 和 ENB 信号，当 ENB 为 1、CS 为 1 且 RD\_WR 指示读取时，主机读取周期开始。该周期在 ENB 被置 0 时结束。CS 可以与 ENB 同时设置

有效极性为低电平时：

- 如果使用 RD 和 WR 信号，当 RD 在 CS 为 0 时被置 0，主机读取周期开始，读周期在 RD 被置 1 时结束。CS 可以与 RD 同时被置 0 和置 1。

- 如果使用 RD\_WR 和 ENB 信号，当 ENB 为 0、CS 为 0 且 RD\_WR 指示读取时，主机读取周期开始。该周期在 ENB 被置 1 时结束。CS 可以与 ENB 同时设置

图 8-24: 索引寻址读周期时序图

表 8-3: 索引寻址读取周期时序值

| 符号          | 描述                         | Min | Typ | Max | units |

|-------------|----------------------------|-----|-----|-----|-------|

| $t_{csrd}$  | RD/ENB 有效前 CS 有效的建立时间      | 0   |     |     | ns    |

| $t_{rdcs}$  | RD/ENB 无效后 CS 有效的保持时间      | 0   |     |     | ns    |

| $t_{as}$    | RD/ENB 有效前 Address 有效的建立时间 | 0   |     |     | ns    |

| $t_{ah}$    | RD/ENB 无效后 Address 有效的保持时间 | 0   |     |     | ns    |

| $t_{rdwrs}$ | ENB 有效前, RD_WR 有效的建立时间     | 5   |     |     | ns    |

| $t_{rdwrh}$ | ENB 无效后, RD_WR 有效的保持时间     | 5   |     |     | ns    |

| $t_{rdon}$  | RD/ENB 有效后, 到数据缓存输出开启的时间   | 0   |     |     | ns    |

| $t_{rddv}$  | RD/ENB 有效后, 到数据有效的时间       |     |     | 65  | ns    |

| $t_{rddh}$  | RD/ENB 无效后, 数据输出有效的保持时间    | 0   |     |     | ns    |

| $t_{rddz}$  | RD/ENB 无效后, 到数据缓存输出关闭的时间   |     |     | 30  | ns    |

| $t_{cs0n}$  | CS 有效后, 到数据缓存输出开启的时间       | 0   |     |     | ns    |

| $t_{csdv}$  | CS 有效后, 到数据有效的时间           |     |     | 65  | ns    |

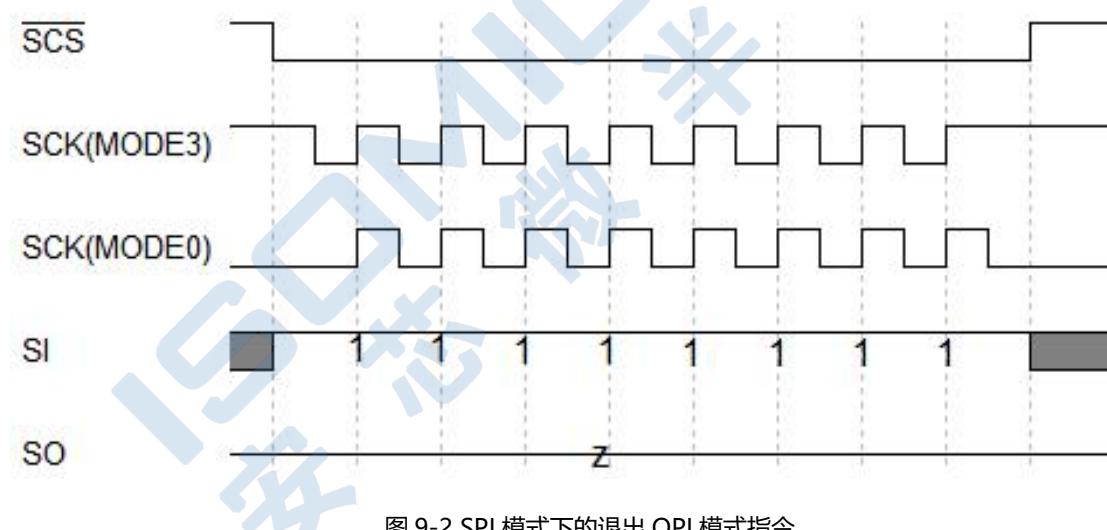

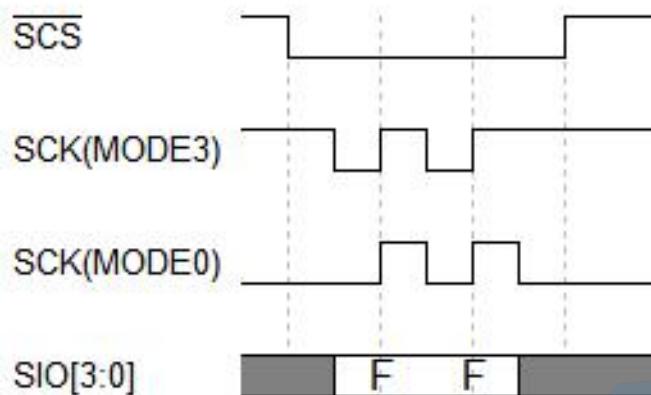

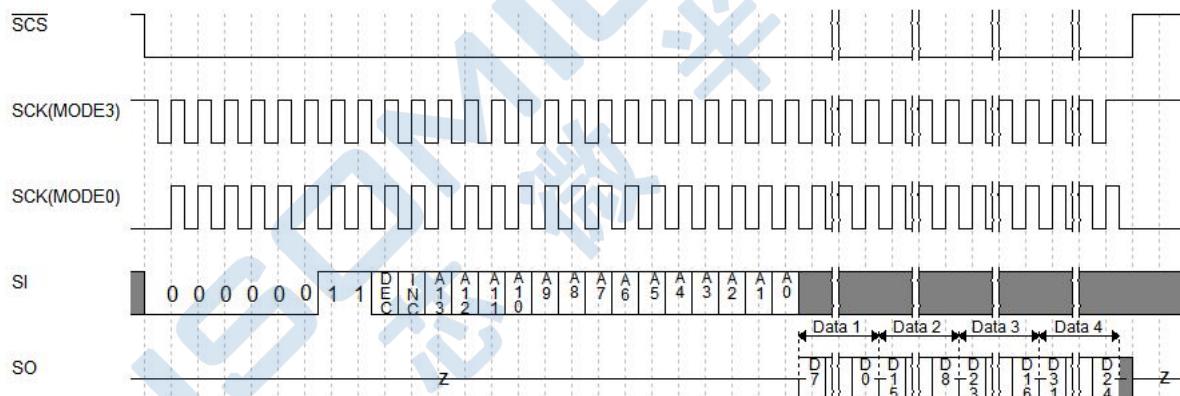

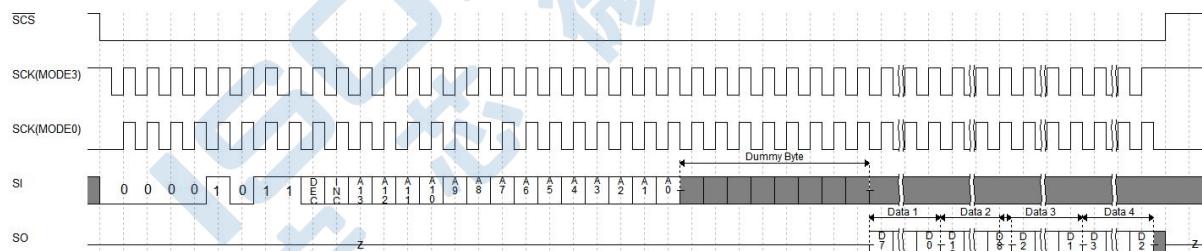

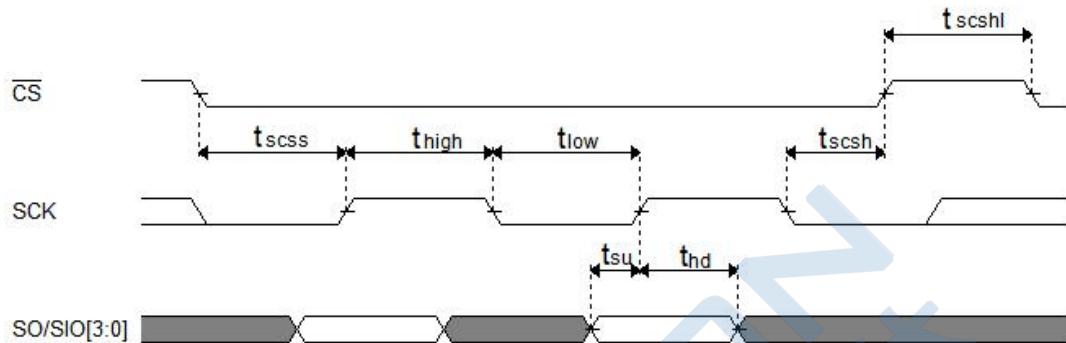

| $t_{csdh}$  | CS 无效后, 数据输出有效的保持时间        | 0   |     |     | ns    |