## LOW IQ REVERSE BATTERY POLARITY AND OVERVOLTAGE PROTECTION CONTROLLER

## **Description**

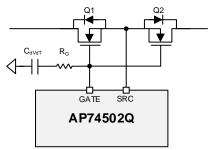

The AP74502Q, AP74502HQ is an automotive AEC-Q100 qualified reverse battery polarity and overvoltage protection controller, which operates with 2 of external N-channel MOSFETs.

The AP74502Q, AP74502HQ is for input protection of 12V/24V/48V automotive systems. The input voltage support as low as 3.2V is particularly for severe cold crank requirements in automotive systems and up to 75V.

The AP74502Q, AP74502HQ controller provides a charge pump gate drive for an external Back to Back N-channel MOSFETs with the enable pin low, the controller is off and draws approximately  $1\mu A$  of current.

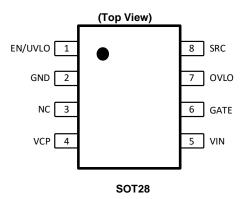

The AP74502Q, AP74502HQ is available in SOT28 package.

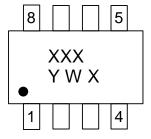

# **Pin Assignments**

## **Applications**

- Automotive body control units

- Automotive infotainment systems head units, telematics control units

- Automotive ADAS systems cameras

- Power of industrial automation such as PLC

- Enterprise power supply

## **Features**

- Input Voltage Ranges from 3.2V to 80V (3.9V Start-Up)

- -80V Reverse Battery Voltage

- Charge Pump for External N-ch Power MOSFETs

- Drives External Back to Back N-ch MOSFETs

- Gate Driver Strength Option

- AP74502Q: 60µA Peak Gate Source

- AP74502HQ: 11mA Peak Gate Source

- Low Shutdown Current of 0.9µA When Disabled

- Low Quiescent Current of 62µA When Enabled

- 2.3A Peak Gate Turn-Off Current

- ESD Protection: 2kV of HBM and 750V of CDM

- AEC-Q100 Qualification Compliance with Device Temperature Grade 1 (-40°C to +125°C Ambient Operating Temperature Range)

- 8-Pin SOT28 Package

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- The AP74502Q, AP74502HQ are suitable for automotive applications requiring specific change control; these parts are AEC-Q100 qualified, PPAP capable, and manufactured in IATF16949 certified facilities.

https://www.diodes.com/quality/product-definitions/

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

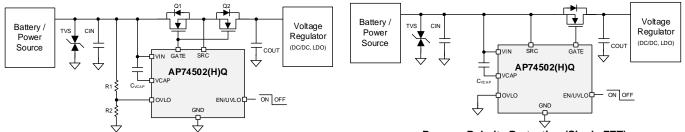

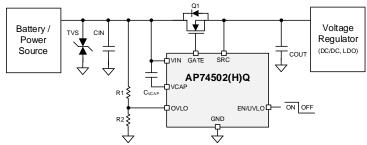

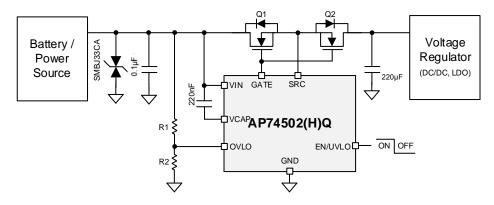

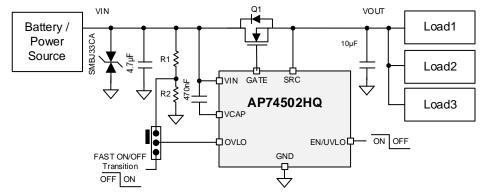

# **Typical Applications Circuit**

Reverse Polarity/Overvoltage Protection with Load Disconnect (Dual FETs)

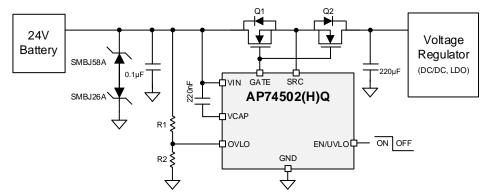

**Reverse Polarity Protection (Single FET)**

Load Switch Controller with Overvotlage Protection (Single FET)

# **Pin Descriptions**

| Pin Name | Pin Number | Function                                                                                                                                               |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN/UVLO  | 1          | EN/ UVLO Control pin. Enable/ Shutdown can be controlled IO control from processor. This pin also support UVLO feature with external resistor divider. |

| GND      | 2          | Ground Pin                                                                                                                                             |

| NC       | 3          | No Connection                                                                                                                                          |

| VCAP     | 4          | Charge pump output pin. Connect external Capacitor (minimum 0.1µF) between VIN and VCAP.                                                               |

| VIN      | 5          | Input power supply to the device. Connect CIN (> 0.1µF) between VIN and GND.                                                                           |

| GATE     | 6          | GATE driver output. Connect to the gate of external NMOS FET.                                                                                          |

| OVLO     | 7          | OVLO input pin. Connect external resistor divider to adjust OVLO threshold. Connect to GND if OVLO feature is not used.                                |

| SRC      | 8          | Power input for gate driver. Connect to the source of external NMOS FET.                                                                               |

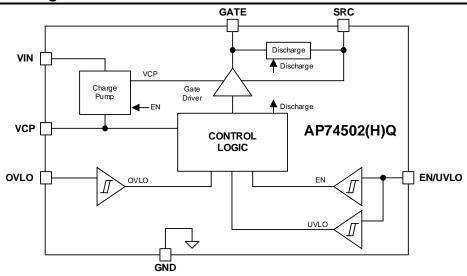

# **Functional Block Diagram**

# Absolute Maximum Ratings (@TA = +25°C, unless otherwise specified.) (Note 4)

| Symbol               | Parameter                              | Rating                | Unit |

|----------------------|----------------------------------------|-----------------------|------|

| ESD HBM              | Human Body ESD Protection              | ±2                    | kV   |

| ESD CDM              | Charged Device Model ESD Protection    | ±750                  | ٧    |

| VIN to GND           | Input Voltage at VIN                   | -80 to +80            | ٧    |

|                      | V <sub>VIN</sub> > 0V                  | -0.3 to +80           | V    |

| EN/UVLO, OVLO to GND | V <sub>VIN</sub> ≤ 0V                  | Vvin to (Vvin +80)    | V    |

| SRC to GND           | Vvin > 0V                              | -(80-Vvin) to Vvin    | V    |

| SRC to GND           | V <sub>VIN</sub> ≤ 0V                  | V <sub>VIN</sub> +0.3 | V    |

| GATE to SRC          | _                                      | 0 to 15               | V    |

| VCAP to VIN          | _                                      | -0.3 to 15            | V    |

| TJ(MAX)              | Maximum Operating Junction Temperature | -40 to +150           | °C   |

| T <sub>STG</sub>     | Storage Temperature                    | -40 to +150           | °C   |

Note:

# Package Thermal Information (Notes 5 & 6)

| Symbol            | Parameter                                    | Value | Unit |

|-------------------|----------------------------------------------|-------|------|

| Reja              | Junction-to-Ambient Thermal Resistance       | 176.9 | °C/W |

| ReJC(top)         | Junction-to-Case (Top) Thermal Resistance    | 122.0 | °C/W |

| R <sub>θ</sub> ЈВ | Junction-to-Board Thermal Resistance         | 46.0  | °C/W |

| ΨJT               | Junction-to-Top Characterization Parameter   | 10.1  | °C/W |

| ΨЈВ               | Junction-to-Board Characterization Parameter | 44.9  | °C/W |

| RθJC(bot)         | Junction-to-Case (Bottom) Thermal Resistance | 50.0  | °C/W |

Notes:

- 5.  $R_{\theta JA}$  and  $R_{\theta JC}$  are measured at  $T_A$  = +25°C on a high effective thermal conductivity four-layer test board per JEDEC 51-7.

- 6. Device mounted on the JEDEC High-K 2S2P board.

# Recommended Operating Conditions (@TA = +25°C, unless otherwise specified.)

| Symbol                            | Parameter                                | Min | Max  | Unit |

|-----------------------------------|------------------------------------------|-----|------|------|

| VIN, EN/UVLO,<br>OVLO, SRC to GND | Input Voltage at VIN, EN/UVLO, OVLO, SRC | -75 | +75  | V    |

| VIN Capacitance                   | Input Capacitor at VIN (Note 7)          | 0.1 | _    | μF   |

| VIN to VCAP Capacitance           | Charge pump Capacitor (Note 7)           | 0.1 | _    | μF   |

| External MOSFET VGS Max           | Gate to SRC (Note 7)                     | 15  | _    | V    |

| TJ                                | Operating Junction Temperature Range     | -40 | +150 | °C   |

Note:

7. Refer to the typical application circuit.

<sup>4.</sup> Stresses greater than the 'Absolute Maximum Ratings' specified above can cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions exceeding those indicated in this specification is not implied. Device reliability can be affected by exposure to absolute maximum rating conditions for extended periods of time.

# **Electrical Characteristics**

$(T_J = -40^{\circ}C \text{ to } +125^{\circ}C, \ V_{IN} = 12\text{V}, \ C_{VCAP} = 0.1 \mu\text{F}, \ V_{EN} = 3.3\text{V}, \ typical \ values \ are \ at \ T_J = +25^{\circ}C, \ unless \ otherwise \ specified.)$

| Symbol             | Parameter                                                      | Conditions                                            |          | Min   | Тур   | Max   | Unit |

|--------------------|----------------------------------------------------------------|-------------------------------------------------------|----------|-------|-------|-------|------|

| VIN Supply         |                                                                | <u> </u>                                              |          |       |       |       |      |

| Vvin               | Operating Input Voltage                                        | _                                                     |          | 4     | _     | 75    | V    |

| Vvin_por_rising    | VIN UVLO Rising Threshold                                      | _                                                     |          | _     | _     | 3.9   | V    |

| Vvin_por_falling   | VIN UVLO Falling Threshold                                     | _                                                     |          | 2.2   | 2.8   | 3.1   | V    |

| VVIN_POR_HYS       | VIN UVLO Hysteresis                                            | _                                                     |          | 0.44  | _     | 0.67  | V    |

| Ishdn              | Shutdown Supply Current                                        | VEN_UVLO = 0V                                         |          | _     | 0.9   | 1.5   | μA   |

| lq                 | Operating Quiescent Current                                    | VEN_UVLO = High                                       |          | 1     | 62    | 84    | μΑ   |

| IREV               | Leakage Current During Reverse Polarity Condition              | 0V < V <sub>VIN</sub> ≤ -65V                          |          | -     | 140   | 200   | μA   |

| EN/UVLO Input      |                                                                |                                                       |          |       |       |       |      |

| VEN_UVLO_RISING    | EN/UVLO Rising Threshold                                       | _                                                     |          | 1.16  | 1.24  | 1.32  | V    |

| VEN_UVLO_FALLING   | EN/UVLO Falling Threshold                                      | _                                                     |          | 1.027 | 1.14  | 1.235 | V    |

| VEN_UVLO_HYS       | EN/UVLO Hysteresis                                             | _                                                     |          | 38    | 90    | 132   | mV   |

| Venf               | EN Threshold Voltage for Ishdn                                 | _                                                     |          | 0.32  | 0.64  | 0.94  | V    |

| len                | EN/UVLO Sink Current                                           | _                                                     |          | _     | 3     | 5     | μA   |

| GATE Drive         |                                                                |                                                       |          |       |       |       |      |

| 1                  | Dook Course Current                                            | \\\\\\\\\\\\\\\\\\\\\\\\\\                            | AP74502Q | 40    | 60    | 77    | μA   |

| IGATE_SOURCE       | Peak Source Current                                            | V <sub>GATE</sub> – V <sub>SRC</sub> = 5.0V AP74502HQ | 3        | 11    | _     | mA    |      |

| IGATE_SINK         | Peak Sink Current                                              | EN/UVLO = High to Low,<br>VGATE - VSRC = 5.0V         | ,        |       | 2370  | _     | mA   |

| RDS_ON             | GATE Discharge Switch R <sub>DS_ON</sub>                       | EN/UVLO = High to Low<br>VGATE - VSRC = 100mV         |          | 0.4   | _     | 2     | Ω    |

| Charge Pump        |                                                                |                                                       |          |       | •     | •     | •    |

|                    | Charge Pump Voltage at VsRc = 3.2V                             | Ivcap ≤ 30µA                                          |          | 8     | _     | _     | V    |

| Vvcap – Vsrc       | Charge Pump Turn-On Voltage                                    | _                                                     |          | 10.3  | 11.6  | 13    | V    |

| VVCAP - VSRC       | Charge Pump Turn-Off Voltage                                   | _                                                     |          | 11    | 12.4  | 13.9  | V    |

|                    | Charge Pump Turn-On/Off<br>Hysteresis                          | _                                                     |          | 0.45  | 0.8   | 1.6   | V    |

| IVCAP_SOURCE       | Charge Pump Source Current                                     | VVCAP - VSRC = 7V                                     |          | 162   | 250   | 600   | μΑ   |

| IVCAP_SINK         | Charge Pump Sink Current                                       | V <sub>VCAP</sub> – V <sub>SRC</sub> = 14V            |          | 1     | 5     | 10    | μA   |

| VVCAP_UVLO_RISING  | V <sub>VCAP</sub> – V <sub>SRC</sub> UVLO Rising<br>Threshold  | _                                                     |          | 5.7   | 6.5   | 7.5   | V    |

| VVCAP_UVLO_FALLING | V <sub>VCAP</sub> – V <sub>SRC</sub> UVLO Falling<br>Threshold | _                                                     |          | 5.05  | 5.4   | 6.5   | V    |

| OVERVOLTAGE PR     | OTECTION                                                       |                                                       |          |       | •     | -     | -    |

| Vov_rising         | Overvoltage Input Rising<br>Threshold                          | _                                                     |          | 1.165 | 1.25  | 1.333 | V    |

| Vov_falling        | Overvoltage Input Falling<br>Threshold                         | _                                                     |          | 1.063 | 1.143 | 1.222 | V    |

| Vov_HYS            | Overvoltage Hysteresis                                         | _                                                     |          | _     | 100   | _     | mV   |

| lov                | Overvoltage Input Leakage<br>Current                           | _                                                     |          | 12    | 50    | 110   | nA   |

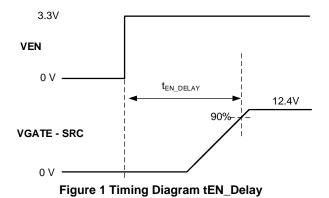

**Switching Characteristics** (T<sub>J</sub> = -40°C to +125°C, V<sub>IN</sub> = 12V, C<sub>VCAP</sub> =  $0.1\mu$ F, V<sub>EN</sub> = 3.3V, typical values are at T<sub>J</sub> = +25°C, unless otherwise specified.)

| Symbol                     | Parameter                                                                        | Conditions                                                                                                                    | Min | Тур | Max | Unit |

|----------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Switching Characteri       | Switching Characteristics                                                        |                                                                                                                               |     |     |     |      |

| ten_delay                  | Delay from Enable Switching High to Gate Turn-On                                 | V <sub>VCP</sub> > V <sub>VCP_UVLO</sub> , VEN/UVLO Step from<br>0V to > VEN_UVLORISING, VGATE-SRC > 5V,<br>CGATE-SRC = 4.7nF | _   | 75  | 110 | μs   |

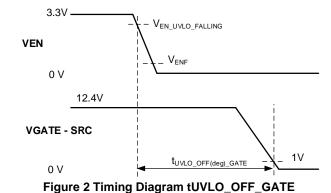

| t <sub>UVLO_OFF_GATE</sub> | Gate Turn-Off Delay by EN/UVLO                                                   | V <sub>EN/UVLO</sub> falling to V <sub>GATE_SRC</sub> < 1V,<br>C <sub>GATE-SRC</sub> = 4.7nF                                  |     | 2   | _   | μs   |

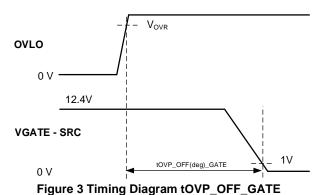

| t <sub>OVP_OFF_</sub> GATE | Gate Turn-Off Delay by Vov Rising > Vov_RISING (Note 8)                          | Vov Rising > Vov_RISINNG to VGATE-SRC < 1V, CGATE-SRC = 4.7nF                                                                 | _   | 0.6 | 1   | μs   |

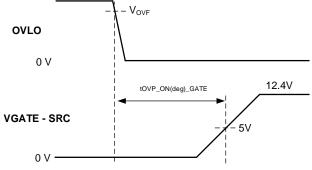

| tovp_on_gate               | Gate Turn-On Delay by V <sub>OV</sub> Falling < V <sub>OV_FALLING</sub> (Note 8) | Vov Falling < Vov_Falling to Vgate-<br>src > 5V, Cgate-src = 4.7nF                                                            | _   | 7   | 10  | μs   |

Note:

8. Parameter guaranteed by Bench characterization.

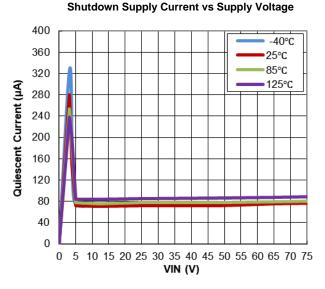

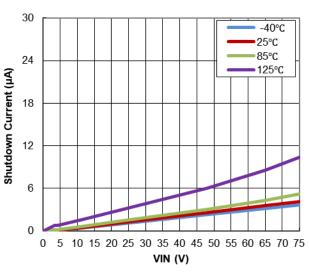

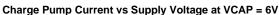

# Typical Performance Characteristics ( $V_{IN} = 12V$ , $V_{EN} = 3.3V$ , $C_{VCAP} = 0.1 \mu F$ , $T_J = +25 ^{\circ}C$ , unless otherwise specified.)

## **Operating Quiescent Current vs Supply Voltage**

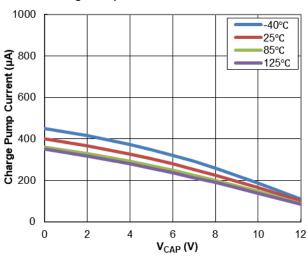

Charge Pump V-I Characteristics at VIN > = 12V

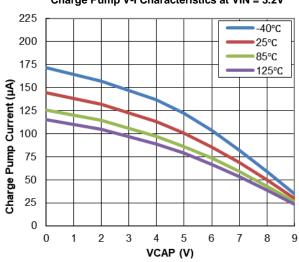

## Charge Pump V-I Characteristics at VIN = 3.2V

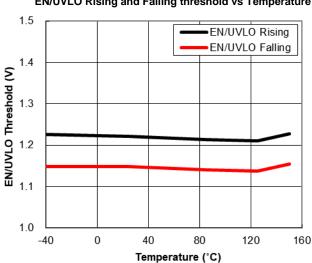

EN/UVLO Rising and Falling threshold vs Temperature

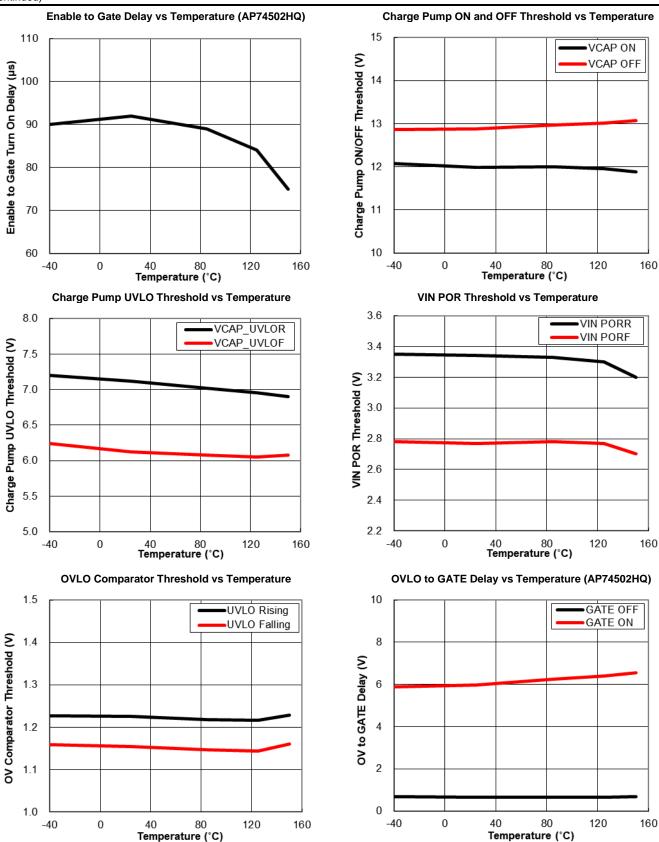

# Typical Performance Characteristics ( $V_{IN} = 12V$ , $V_{EN} = 3.3V$ , $C_{VCAP} = 0.1 \mu F$ , $T_J = +25 ^{\circ}C$ , unless otherwise specified.) (continued)

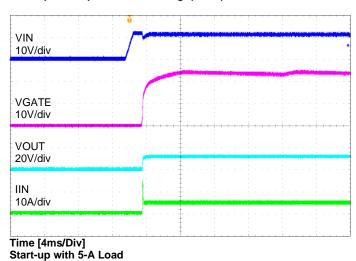

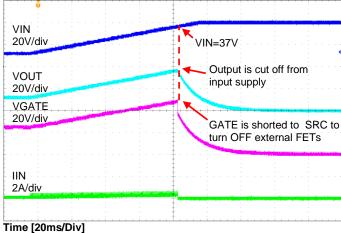

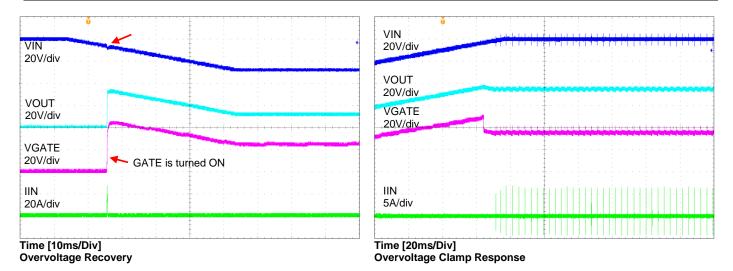

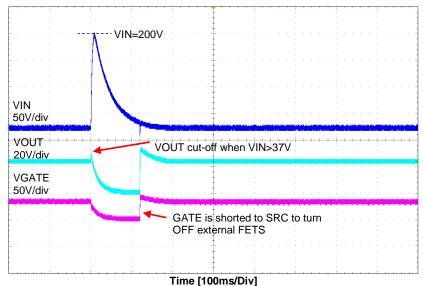

# **Application Curves**

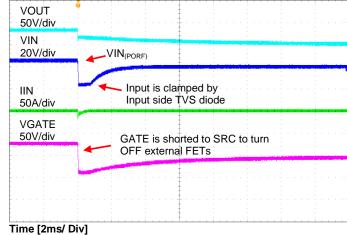

ISO 7637-2 Pulse 1

Response to ISO 7637-2 Pulse 1(–150V)

Time [20ms/Div]

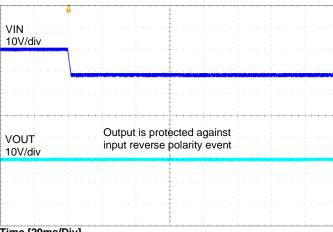

Start-up with Input Reverse Voltage(-12 V)

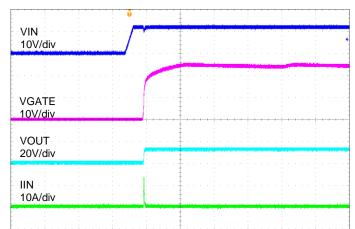

Time [4ms/Div] Start-up with No Load

Overvoltage Cutoff Response (37V)

# **Application Curves** (continued)

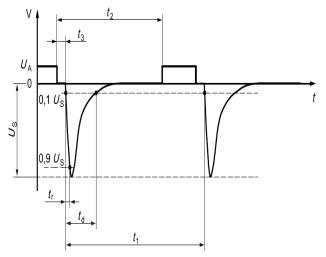

# Switching Waveforms

Figure 4 Timing Diagram tOVP\_ON\_GATE

# **Detailed Description**

### Overview

The AP74502Q, AP74502HQ controller has all the features necessary to implement an efficient and fast reverse polarity protection circuit with load disconnect function. This easy-to-use reverse polarity protection controller is paired with an external back-to-back connected N-channel MOSFETs to replace other reverse polarity schemes such as a P-channel MOSFETs. The wide input supply of 4V to 80V allows protection and control of 12V, 24V and 48V automotive battery powered ECUs. The device can withstand and protect the loads from negative supply voltages down to -65V. An integrated charge pump drives external back-to-back connected N-channel MOSFETs with gate drive voltage of approximately 12.4V to realize reverse polarity protection and load disconnect function in case of overvoltage and under voltage event. The AP74502Q with its typical gate drive strength of 60µA provides smooth start-up with inherent inrush current control due to its lower gate drive strength. The AP74502HQ with its 11mA typical peak gate drive strength is suitable for applications which need faster turn on such as load switch applications. The AP74502Q, AP74502HQ features an adjustable overvoltage cutoff protection feature using a programming resistor divider to OVLO terminal. The AP74502Q, AP74502HQ features enable control. With the enable pin low during the standby mode, both the external MOSFETs and controller is off and draws a very low 0.9µA of current.

#### Input Voltage

The VIN pin is used to power the AP74502Q, AP74502HQ internal circuitry, typically drawing 62µA when enabled and 0.9µA when disabled. If the VIN pin voltage is greater than the POR Rising threshold, then the AP74502Q, AP74502HQ operates in either shutdown mode or conduction mode in accordance with the EN/UVLO pin voltage. The voltage from VIN to GND is designed to vary from 80V to -80V, allowing the AP74502Q, AP74502HQ to withstand negative voltage transients.

## **Built-in Charge Pump with External Capacitor**

The charge pump supplies the voltage necessary to drive the external N-channel MOSFET. An external charge pump capacitor is placed between VCAP and VIN pin to provide power to turn on the external MOSFET. For the charge pump to supply current to the external capacitor the EN/UVLO pin, voltage must be > VENF. When EN/UVLO > VENF the charge pump sources a charging current of 300µA typically. If EN/UVLO < VENF then the charge pump remains disabled. To ensure that the external N-channel MOSFET can be driven above its specified VTH, the VCAP to VIN voltage must be above the undervoltage lockout threshold, typically 6.5V, before the internal gate driver is enabled. Use below equation to calculate the initial gate driver enable delay.

$$T_{DRV\_EN} = 75\mu s + C_{VCAP} \times \frac{V_{VCAP\_UVLO\_RISING}}{300\mu A}$$

Where,

CVCAP is the charge pump capacitance connected across ANODE and VCP pins VVCAP UVLO RISING = 6.5V (typical)

Typical 1V hysteresis of VCP UVLO threshold enhances linearity of gate driver. The charge pump remains enabled until the VCP to ANODE voltage reaches 12.4V, typically, at which point the charge pump is disabled, decreasing the current draw on the ANODE pin. The charge pump remains disabled until the VCP to ANODE voltage is below 11.6V typically, at which point the charge pump is enabled. The voltage between VCP and ANODE continues to charge and discharge between 11.6V and 12.4V. By enabling and disabling the charge pump, the operating quiescent current of the AP74502Q is reduced. When the charge pump is disabled, it sinks 5µA typical.

#### **Gate Driver**

The gate driver is used to control the external N-Channel MOSFET by setting the appropriate GATE to SRC voltage. Before the gate driver is enabled following three conditions must be achieved:

- The EN/UVLO pin voltage must be greater than the specified input high voltage.

- The VCAP to VIN voltage must be greater than the undervoltage lockout voltage.

- The VIN voltage must be greater than VIN POR Rising threshold.

If any of above is not met, the GATE pin is internally connected to the SRC pin, external MOSFET is disabled. After these conditions are met the gate driver operates for enhancing the external MOSFET. The controller offers two gate drive variants. The AP74502Q with typical peak gate drive strength of 60µA is suitable to achieve smooth start-up with inherent inrush current control due to its lower gate drive strength. The AP74502HQ with its 11mA typical peak gate drive strength is suitable for applications, which need faster turn-on such as load switch applications.

The AP74502Q, AP74502HQ SRC pin is capable of handling negative voltage which also makes it suitable for load disconnect switch applications with loads which are inductive in nature.

## **Detailed Description** (continued)

#### **Inrush Current Control**

An external circuit can be added on the GATE pin of the AP74502Q to have additional inrush current control for the applications, which have large capacitive loads.

Inrush Current Limiting with External Components (AP74502Q Only)

The  $C_{dVdT}$  capacitor can control GATE voltage ramping up rate upon external NMOS FET turn on. Use below equation 2 to calculate  $C_{dVdT}$  capacitance value.

$$C_{dVdT} = \frac{I_{GATESource} \times C_{OUT}}{I_{INRUSH}}$$

Whereas Igate\_source is 60µA for the AP74502Q, Inrush is proportional to ratio of Cout over CdvdT. The series resistor of Rg increases isolation between GATE driver to CdvdT which helps to decrease turn off time. This inrush control circuit with external components is only applicable to the AP74502Q and AP74502HQ is designed to have a strong GATE driver for quickly turn on for load switch applications.

## Enable and Undervoltage Lockout (EN/UVLO)

The AP74502Q, AP74502HQ has an enable pin, EN/UVLO. The enable pin allows for the gate driver to be either enabled or disabled by an external signal. If the EN/UVLO pin voltage is greater than the rising threshold, the gate driver and charge pump operate as described in Gate Driver and Charge Pump sections. If the enable pin voltage is less than the input low threshold, the charge pump and gate driver are disabled placing the AP74502Q, AP74502HQ in shutdown mode. The EN/UVLO pin can withstand a voltage as large as 80V and as low as -80V. This feature allows for the EN/UVLO pin to be connected directly to the VS pin if enable functionality is not needed. In conditions where EN/UVLO is left floating, the internal sink current of 3µA pulls EN/UVLO pin low and disables the device. An external resistor divider connected from input to EN/UVLO to ground can be used to implement the input Undervoltage Lockout (UVLO) functionality. When EN/UVLO pin voltage is lower than UVLO comparator rising threshold (VEN\_UVLO\_RISING) but higher than enable falling threshold (VENF), the device disables gate drive voltage, however, charge pump is kept on. This action ensures quick recovery of gate drive when UVLO condition is removed. If UVLO functionality is not required, connect EN/UVLO pin to VS.

## Overvoltage Protection (OVLO)

The AP74502Q, AP74502HQ provides programmable overvoltage protection feature with OVLO pin. A resistor divider can be connected from input source to OVLO pin to ground to set overvoltage threshold. An internal comparator compares the input voltage against fixed reference (1.25V) and disables the gate drive as soon as OVLO pin voltage goes above the OVLO comparator reference. When the resistor divider is referred from input supply side, the device is configured for overvoltage cutoff functionality. When the resistor divider is referred from output side (VOUT), the device is configured for overvoltage clamp functionality. When OVLO pin voltage goes above OVLO comparator Vov\_RISING threshold (1.24V typical), the device disables gate drive, however, charge pump remains active. When OVLO pin voltage falls below Vov\_FALLING threshold (1.14V typical), the gate is quickly turned on as charge pump is kept on and the device does not go through the device start-up process. When OV pin is not used, it can be connected to ground.

## **Detailed Description** (continued)

## **Device Operation Mode**

| VIN        | EN/UVLO            | OVLO              | Gate Driver<br>(GATE) | Charge Pump<br>(VCP) | Device Operation Mode |

|------------|--------------------|-------------------|-----------------------|----------------------|-----------------------|

| < VVIN_POR | Don't Care         | Don't Care        | N/A                   | N/A                  | Power Off (No Power)  |

|            | < VENF             | Don't Care        | Connect to SRC        | Disabled             | Shutdown Mode         |

| V          | > VENF, < VEN_UVLO | < V <sub>OV</sub> | Connect to SRC        | Enabled              | UVLO Mode             |

| > VVIN_POR |                    | < Vov             | Enabled               | Enabled              | Conduction Mode       |

|            | > VEN_UVLO         | > Vov             | Connect to SRC        | Enabled              | OVP Mode              |

#### **Shutdown Mode**

The AP74502Q, AP74502HQ enters shutdown mode when the EN/UVLO pin voltage is below V<sub>EN\_UVLO</sub>. In this mode, both the gate driver and the charge pump are disabled in shutdown mode and the AP74502Q consume minimum power by I<sub>SHDN</sub> (typ 0.9μA) at VIN pin.

#### **Conduction Mode**

The AP74502Q, AP74502HQ enters conduction mode driving external NMOS FET to be in enhancement mode only if all of below conditions are met.

- VIN > VVIN\_POR

- EN/UVLO > VEN\_UVLO

- OVLO < Vov</li>

In this mode, Gate pin will drive external NMOSFET to be in conduction state. The AP74502Q and AP74502HQ drive Gate pin in 2 different methods.

- The AP74502Q drives Gate pin through 60µA current source for slow turning on external NMOS FET.

- The AP74502HQ connects Gate to VCP for fast turning external NMOS FET.

## **UVLO Mode and OVP Mode**

To protect downstream application circuit, In UVLO mode or OVP mode, the AP74502Q, AP74502HQ turn off external NMOS FET by routing Gate pin to SRC and keeps enabled Charge pump for being ready to go back to conduction mode whenever UVLO or OVLO condition is removed.

The AP74502Q, AP74502HQ enter UVLO or OVP mode.

If EN/UVLO < VEN\_UVLO or OVLO > Vov

# **Application Information**

The AP74502Q, AP74502HQ is used with N-Channel MOSFET controller in a typical reverse polarity protection application. The schematic for the 12V battery protection application is shown below where the AP74502Q, AP74502HQ is used to drive back-to-back connected MOSFETs Q1 and Q2 in series with a battery for reverse polarity protection and load disconnection. The TVS is required for protection for the AP74502Q, AP74502HQ and its downstream application against positive and negative voltage surges and ESD event. Output Capacitor is recommended for filtering out supply upon dynamic load condition.

### **Typical Application**

## **Design Example**

| Design Example            |                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------|

| Design Parameter          | Example Value                                                                     |

| VIN Range                 | 12V Vehicle Battery, 12V nominal with 3.2V cold crank and 35V load dump condition |

| VOUT                      | 3.2V during cold crank to 35V load dump                                           |

| IOUT                      | 3A nominal and 5A maximum                                                         |

| COUT                      | 220µF typical hold up Capacitor                                                   |

| Overvotlage Protection    | Typical 37V for 12V battery system                                                |

| Automotive EMC Compliance | ISO 7637-2 and ISO 16750-2                                                        |

#### **MOSFET Selection**

The important MOSFET electrical parameters are the maximum continuous drain current,  $I_D$ , the maximum drain-to-source voltage,  $V_{DS(MAX)}$ , the maximum source current through body diode, and the drain-to-source on resistance,  $R_{DS(ON)}$ .

The maximum continuous drain current, I<sub>D</sub>, rating must exceed the maximum continuous load current. The maximum drain-to-source voltage, V<sub>DS(MAX)</sub>, must be high enough to withstand the highest differential voltage seen in the application. This would include any anticipated fault conditions. It is recommended to use MOSFETs with voltage rating up to 75V maximum with the AP74502(H)Q. The maximum V<sub>GS</sub> the AP74502Q, AP74502HQ can drive is 13.9V, so a MOSFET with 15V minimum V<sub>GS</sub> rating must be selected. If a MOSFET with V<sub>GS</sub> rating < 15V is selected, a Zener diode can be used to clamp V<sub>GS</sub> to safe level within Max V<sub>GS</sub> of the MOSFET.

To reduce the MOSFET conduction losses, lowest possible  $R_{DS(ON)}$  is preferred. Selecting a MOSFET with  $R_{DS(ON)}$  that gives  $V_{DS}$  drop 20mV to 50 mV at full load provides good trade off in terms of power dissipation and cost. Thermal resistance of the MOSFET must be considered against the expected maximum power dissipation in the MOSFET to ensure that the junction temperature  $(T_J)$  is well controlled.

#### Overvoltage Protection Threshold

Resistors R1 and R2 voltage divider can be used to adjust the overvoltage threshold. Connecting R1 to VIN provides overvoltage cutoff and switching the connection to VOUT provides overvoltage clamp response. The resistor values required for setting the overvoltage threshold Vov to 37V are calculated by below equation.

$$V_{OVProtection\_threshold} = V_{OVR} \cdot \left(1 + \frac{R_1}{R_2}\right) = 1.25V \times \left(1 + \frac{R_1}{R_2}\right)[V]$$

whereas  $V_{OVR}$  is 1.25V.

For minimizing the input current drawn from the supply through resistors R1 and R2, we recommend to use higher value of resistance. Using high value resistors adds error in the calculations because the current through the resistors at higher value becomes comparable to the leakage current into the OVLO pin. Select (R1 + R2) such that current through resistors is around 100 times higher than  $I_{OV}$ , which is the leakage into OVLO pin (Max 110nA). R1 =  $100k\Omega$  and R2 =  $3.5k\Omega$  as a standard resistor value to set overvoltage cutoff of 37V. Based on application use case, overvoltage threshold can be set at the lower voltage as it enables lower rated downstream components, thus providing solution size and lower cost benefit.

### Charge Pump VCAP, Input and Output Capacitance

Minimum required capacitance for charge pump(C\_VCAP), Input capacitance (CIN) and output capacitance are:

- C\_VCAP: Minimum recommended value of C\_VCAP [μF] ≥ 10 × C<sub>ISS(MOSFET\_effective)</sub> [μF], C\_VCAP of 0.22 [μF] is selected

- CIN: Typical input capacitor of 0.1 [µF]

- COUT: Typical output capacitor 220 [µF]

#### Appropriate TVS Diodes for 12V Battery Applications

TVS diodes are used in automotive systems for protection against transients. In the 12V battery protection application circuit shown below, a bidirectional TVS diode is used to protect from positive and negative transient voltages that occur during normal operation of the car and these transient voltage levels and pulses are specified in ISO 7637-2 and ISO 16750-2 standards.

There are two important specifications, breakdown voltage and clamping voltage of the TVS. Breakdown voltage is the voltage at which the TVS diode goes into avalanche similar to a Zener diode and is specified at a low current value typical 1mA, and the breakdown voltage should be higher than worst case steady state voltages seen in the system. The breakdown voltage of the TVS+ should be higher than 24V jump start voltage and 35V suppressed load dump voltage and less than the maximum ratings of the AP74502Q(80V). The breakdown voltage of TVS- should be beyond maximum reverse battery voltage -16V, so that the TVS- is not damaged due to long time exposure to reverse connected battery.

Clamping voltage is the voltage the TVS diode clamps in high current pulse situations and this voltage is much higher than the breakdown voltage. TVS diodes are meant to clamp transient pulses and should not interfere with steady state operation. In the case of ISO 7637-2 Pulse 1, the input voltage goes up to -150V with a generator impedance of  $10\Omega$ . This translates to 15A flowing through the TVS- and the voltage across the TVS would be close to its clamping voltage.

The next criterion is that the absolute minimum rating of VIN voltage of the AP74502Q (-80V) and the maximum VDS rating MOSFET are not exceeded. In the design example, 60V rated MOSFET is selected. SMBJ series of TVS are rated up to 600W peak pulse power levels. This rating is sufficient for ISO 7637-2 pulses and suppressed load dump (ISO-16750-2 pulse B).

## Appropriate TVS Diodes and MOSFET for 24V Battery Applications

Typical 24V battery protection application circuit shown in below diagram that uses two uni-directional TVS diodes to protect from positive and negative transient voltages.

The breakdown voltage of the TVS+ must be higher than 48V jump start voltage, less than the absolute maximum ratings of source and enable pin of the AP74502Q, AP74502HQ (80V) and must withstand 65V suppressed load dump. The breakdown voltage of TVS- must be lower than maximum reverse battery voltage -32V, so that the TVS- is not damaged due to long time exposure to reverse connected battery.

During ISO 7637-2 pulse 1, the input voltage goes up to -600V with a generator impedance of  $50\Omega$ . Single bi-directional TVS cannot be used for 24V battery protection because breakdown voltage for TVS+  $\geq$  48V, maximum negative clamping voltage is  $\leq$  65V. Two uni-directional TVS connected back-to-back must be used at the input. For positive side TVS+, We recommend SMBJ58A with the breakdown voltage of 64.4V (minimum), 67.8 (typical). For the negative side TVS-, We recommend SMBJ26A with breakdown voltage close to 32V (to withstand maximum reverse battery voltage -32V) and maximum clamping voltage of 42V.

For 24V battery protection, we recommend a 75V rated MOSFET to be used along with SMBJ26A and SMBJ58A connected back-to-back at the input.

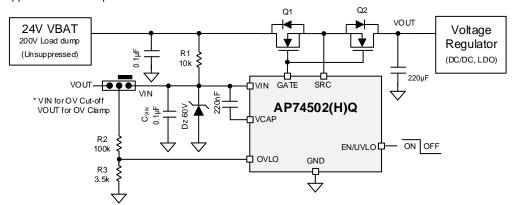

## Surge Stopper Using the AP74502Q, AP74502HQ

Many automotive applications are designed to comply with unsuppressed load dump transients specified by ISO16750-2 Pulse 5A. The AP74502Q, AP74502HQ can be configured as input surge stopper to provide overvoltage along with input reverse supply protection and protect the downstream loads in case of unsuppressed load dump event.

200V Surge Stopper with Overvoltage Cutoff Using AP74502Q

### VIN Capacitance (CVIN), Resistor R1 and Zener Clamp (Dz)

A minimum of  $1\mu F$  C<sub>VIN</sub> capacitance is required. During input overvoltage transient, resistor R1 and Zener diode D<sub>Z</sub>, are used to protect VIN pin from exceeding the maximum ratings by clamping VIN to 60V. Choosing R1 =  $10k\Omega$ , the peak power dissipated in Zener diode D<sub>Z</sub> can be calculated using below equation:

$$P_{DZ} = V_{DZ} \times \frac{(V_{IN_{MAX}} - V_{DZ})}{R_1}$$

Where V<sub>DZ</sub> is the breakdown voltage of Zener diode. Select the Zener diode that can handle peak power requirement.

Peak power dissipated in resistor R1 can be calculated using below equation:

$$P_{R1} = \frac{(V_{IN_{MAX}} - V_{DZ})^2}{R_1}$$

Select a resistor package which can handle peak power and maximum DC voltage.

### **Overvoltage Protection**

For the overvoltage setting, refer to the resistor selection procedure described in Overvoltage Protection. Select  $R_2$  =  $100k\Omega$  and  $R_3$  =  $3.5k\Omega$  as a standard resistor value to set overvoltage cutoff of 37V.

## **MOSFET Selection**

The VDS rating of the MOSFET Q1 must be minimum VIN(max) for designs with output overvoltage cutoff where output can reach 0V with higher loads. For designs with output overvoltage clamp, MOSFET VDS rating must be (VIN(max) – VOUT\_CLAMP). The VGS rating is based on GATE-SRC maximum voltage of 15V. We recommend a 20V VGS rated MOSFET. Power dissipation on MOSFET Q1 on a design where output is clamped is critical and SOA characteristics of the MOSFET must be considered with sufficient design margin for reliable operation. An additional Zener diode from GATE to SRC can be needed to protect the external FET in case output is expected to drop to the level where it can exceed external FET VGS(max) rating.

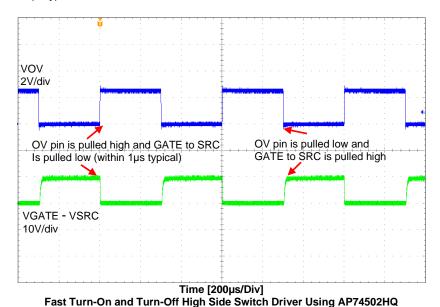

#### Fast Turn-On and Turn-Off High Side Switch Driver Using the AP74502HQ

In automotive load driving applications N-Channel MOSFET based high side switch is very commonly used to disconnect the loads from supply line in case of faults such as overvoltage event. The AP74502Q, AP74502HQ can be used to drive external MOSFET to perform simple high side switch with overvoltage protection. Below diagram shows a typical application circuit where the AP74502HQ is used to drive external MOSFET Q1 as a switch for main power path control. A resistor divider from input to OVLO pin to ground can be used to set the overvoltage threshold.

If VOUT node (SRC pin) of the device is expected to drop in case of events such as overcurrent or short-circuit on load side, then additional Zener diode is required across gate and source pin of external MOSFET to protect it from exceeding its maximum V<sub>GS</sub> rating.

Many safety applications require fast switching off of the MOSFET in case of fault events such as overvoltage or overcurrent fault. Some of the load driving path applications also require PWM operation of high side switch. The AP74502HQ OVLO pin can be used as control input to perform fast turn-on and turn-off mode transition. With OVLO pin pulled above VovR threshold of (1.25V typical), the AP74502HQ turns off the external MOSFET (with C<sub>ISS</sub> = 4.7nF) within 1µs typically. When OVLO pin is pulled low, the AP74502HQ with its peak gate drive strength of 11mA turns on external MOSFET with turn-on speed of 7µs typical.

## **Power Supply Recommendations**

The AP74502Q, AP74502HQ reverse polarity protection controller is designed for the supply voltage range of  $3.2V \le VS \le 80V$ . If the input supply is located more than a few inches from the device, we recommend an input ceramic bypass capacitor higher than  $0.1\mu F$ . Based on system requirements, a higher input bypass capacitor can be needed with the AP74502HQ to avoid supply glitch in case of high inrush current start-up event. To prevent the AP74502Q, AP74502HQ and surrounding components from damage under the conditions of a direct output short circuit, use a power supply having overload and short-circuit protection.

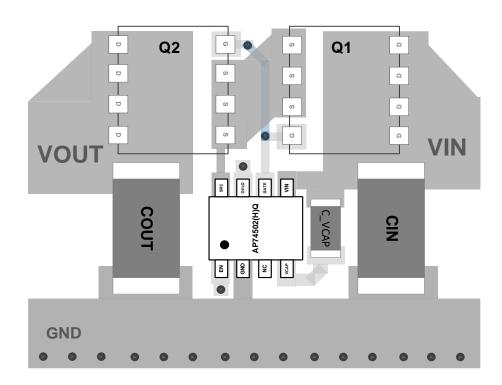

### **Layout Guidelines**

- Connect GATE and SRC pin of the AP74502Q, AP74502HQ close to the MOSFET's gate and source pin.

- Use thick traces or filled plane for source and drain of the MOSFET to minimize resistive losses because the high current path of for this solution is through the MOSFET.

- Keep the charge pump capacitor across VCAP and VIN pin away from the MOSFET to lower the thermal effects on the capacitance value.

- Connect the GATE pin of the AP74502Q, AP74502HQ to the MOSFET gate with short trace. Avoid excessively thin and long running trace to the Gate Drive.

## **Layout Example**

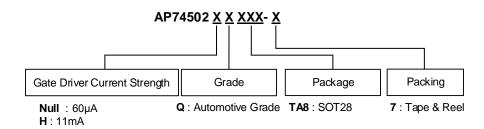

# Ordering Information (Note 9)

| Orderable Part | Gate Driver | Enable Active  | Package Code | Package | Pa   | cking            |

|----------------|-------------|----------------|--------------|---------|------|------------------|

| Number         | Strength    | Eliable Active | Fackage Code | rackage | Qty. | Carrier          |

| AP74502QTA8-7  | 60µA        | HIGH           | TA8          | SOT28   | 3000 | 7" Tape and Reel |

| AP74502HQTA8-7 | 11mA        | HIGH           | TA8          | SOT28   | 3000 | 7" Tape and Reel |

Note: 9. For packaging details, go to our website at https://www.diodes.com/design/support/packaging/diodes-packaging/.

# **Marking Information**

## SOT28

XXX: Identification Code

Y: Year 0 to 9

W: Week: A to Z: week 1 to 26;

a to z : week 27 to 52; z represents

52 and 53 week

X: Internal Code

| Orderable Part Number | Package | Identification Code |

|-----------------------|---------|---------------------|

| AP74502QTA8-7         | SOT28   | T2Q                 |

| AP74502HQTA8-7        | SOT28   | T3Q                 |

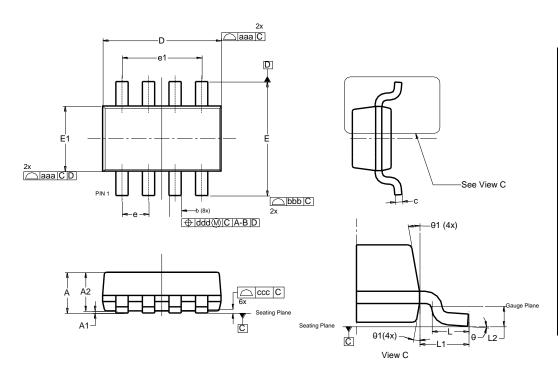

# **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### SOT28

|            | SC    | <b>DT28</b> |       |  |

|------------|-------|-------------|-------|--|

| Dim        | Min   | Max         | Тур   |  |

| Α          | 0.90  | 1.10        | 1.00  |  |

| <b>A</b> 1 | 0.00  | 0.10        |       |  |

| A2         |       |             | 0.95  |  |

| b          | 0.20  | 0.40        | 0.30  |  |

| С          | 0.08  | 0.20        |       |  |

| D          | 2.85  | 2.95        | 2.90  |  |

| Е          | 2.65  | 2.95        | 2.80  |  |

| E1         | 1.55  | 1.65        | 1.60  |  |

| е          |       | 0.65 B      | SC    |  |

| e1         |       | 1.95 B      | SC    |  |

| L          | 0.30  | 0.60        | 0.45  |  |

| L1         |       | 0.60 R      | EF    |  |

| L2         |       | 0.25 B      | SC    |  |

| θ          | 0°    | 8°          |       |  |

| θ1         | 9°    | 11°         | 10°   |  |

| aaa        |       | 0.15        |       |  |

| bbb        | 0.25  |             |       |  |

| CCC        | 0.10  |             |       |  |

| ddd        |       | 0.20        |       |  |

| All        | Dimen | sions       | in mm |  |

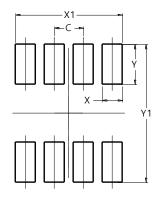

# **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

#### SOT28

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| С          | 0.650            |

| Х          | 0.450            |

| X1         | 2.400            |

| Y          | 0.900            |

| Y1         | 3.100            |

Note: The suggested land pattern dimensions have been provided for reference only, as actual pad layouts may vary depending on application. These dimensions may be modified based on user equipment capability or fabrication criteria. A more robust pattern may be desired for wave soldering and is calculated by adding 0.2 mm to the 'Z' dimension. For further information, please reference document IPC-7351A, Naming Convention for Standard SMT Land Patterns, and for international grid details, please see document IEC, Publication 97.

**Note:** For high voltage applications, the appropriate industry sector guidelines should be considered with regards to creepage and clearance distances between device Terminals and PCB tracking.

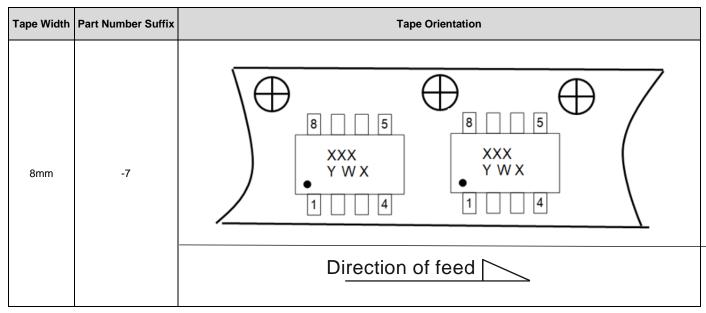

# **Device Taping Orientation**

Package Type: SOT28

For part marking, refer to product datasheet. Note:

Note:

Tape and package drawings are not to scale and are shown for device tape orientation only.

The taping orientation of the other package type can be found on our website at https://www.diodes.com/assets/Packaging-Support-Docs/AP02007.pdf. Note:

## **Mechanical Data**

- Surface-Mount Package

- Moisture Sensitivity: Level 1 per J-STD-020

- Package Material: Molded Plastic, UL Flammability Classification Rating 94V-0

- Terminals: Finish Matte Tin Plated Leads, Solderable per MIL-STD-202, Method 208 (3)

- Weight: 0.016 grams (Approximate)

- Max Soldering Temperature +260°C for 30 secs as per JEDEC J-STD-020

#### IMPORTANT NOTICE

- 1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- 2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their intended applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- 3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- 4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- 5. Diodes' products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- 6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- 7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- 8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

- 9. This Notice may be periodically updated with the most recent version available at <a href="https://www.diodes.com/about/company/terms-and-conditions/important-notice">https://www.diodes.com/about/company/terms-and-conditions/important-notice</a>

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. All other trademarks are the property of their respective owners.

© 2025 Diodes Incorporated. All Rights Reserved.

www.diodes.com