## 1、概述

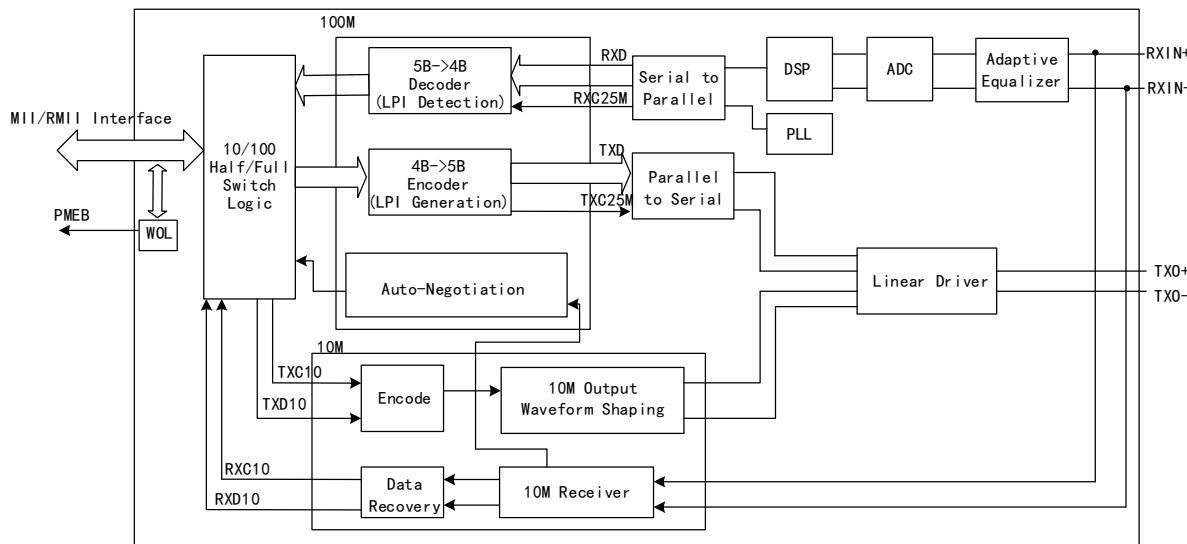

CH182 是一款支持 Auto-MDIX 的工业级 10/100M 以太网 PHY 收发器。CH182 内部包括物理编码子层（PCS）、物理介质接入层（PMA）、双绞线物理介质相关子层（TP-PMD）、10BASE-T 编码器/解码器、双绞线介质连接单元（TPMAU）、MII 和 RMII 接口等以太网 Transceiver 功能所需的模块。

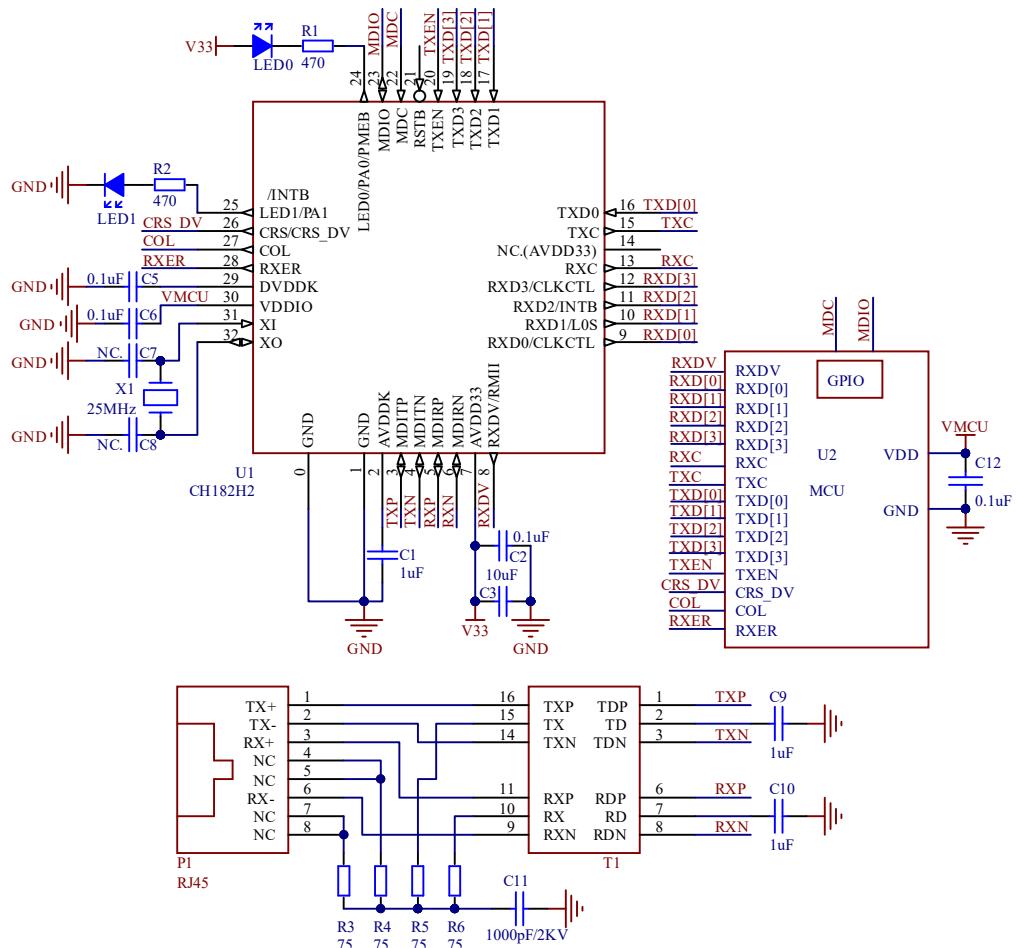

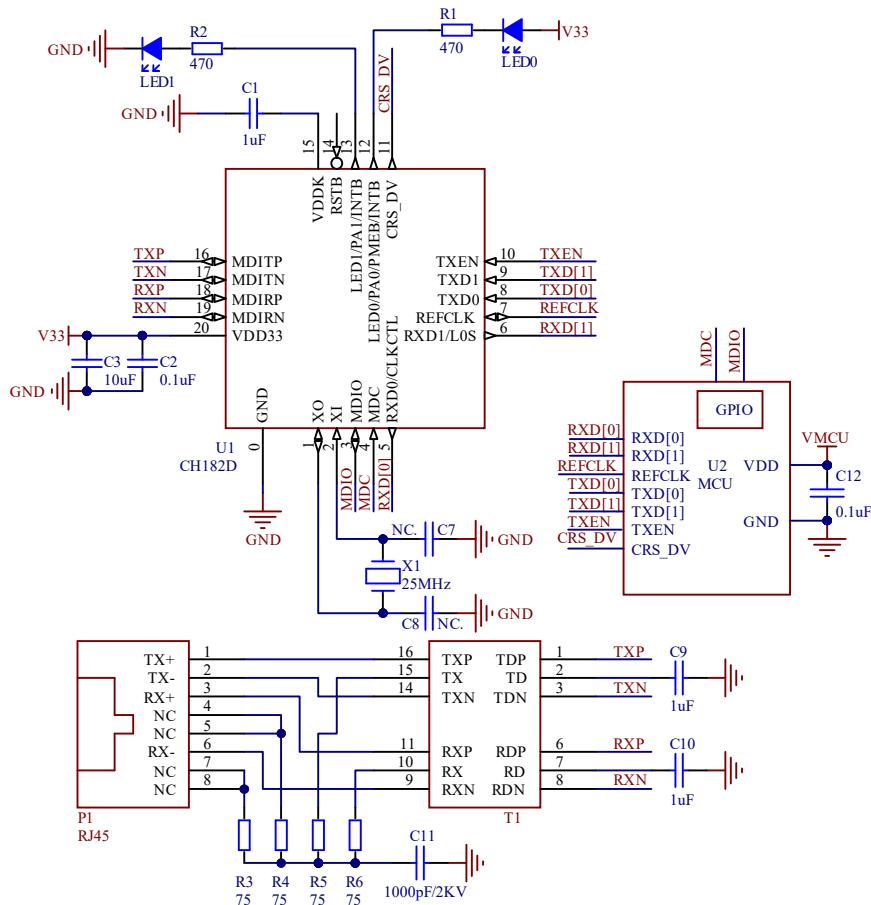

下图为 CH182 的框图。

## 2、特点

- 基于 DSP 算法实现的低功耗以太网物理层收发器 PHYceiver。

- 支持停机模式。

- 支持 Auto-MDIX 交换 TX/RX，自动识别正负信号线。

- 支持 10BASE-T 和 100BASE-TX 及自动协商。

- 支持 MII 和 RMII 两种接口模式。

- 支持全双工和半双工操作。

- 支持 UTP CAT5、CAT6 双绞线，支持 120 米传输距离。

- 内置 LDO 降压器，单一 3.3V 电源供电。

- 独立的 I/O 接口电源，支持 3.3V、2.5V 或 1.8V，以适配不同电压的处理器或 MCU。

- 内置  $50\Omega$  阻抗匹配电阻，内置 25MHz 晶体振荡器所需电容，外围电路精简。

- 可选支持外部 50MHz 时钟输入。

- 支持 WOL 网络唤醒。

- 支持中断功能。

- 支持两种网络状态 LED。

- CH182D 芯片内置唯一的以太网 MAC 地址，无需另外购买或分配。

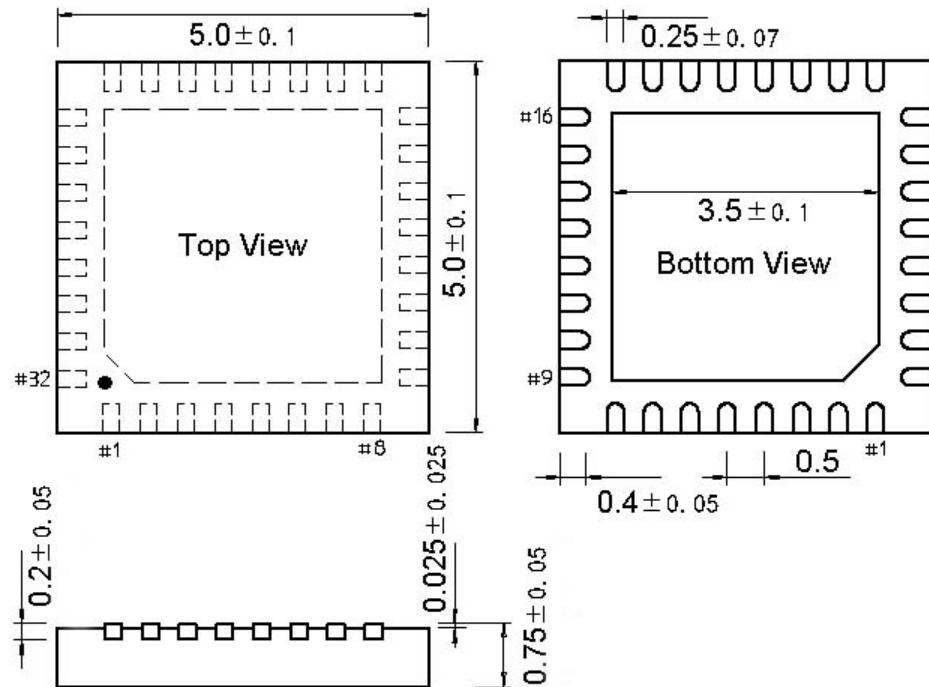

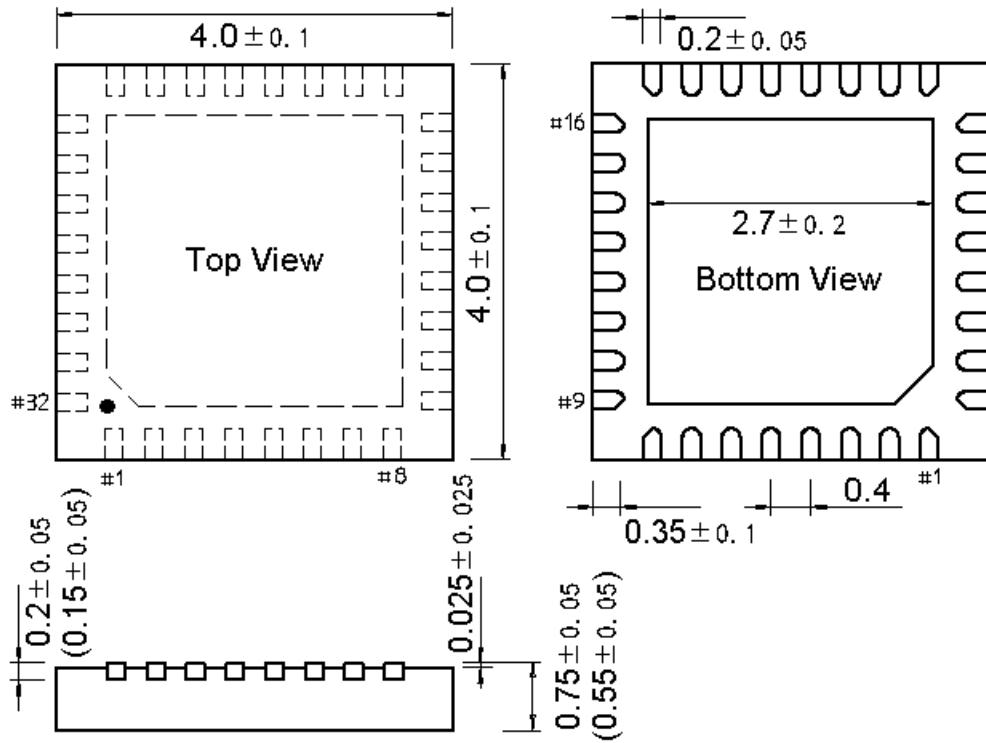

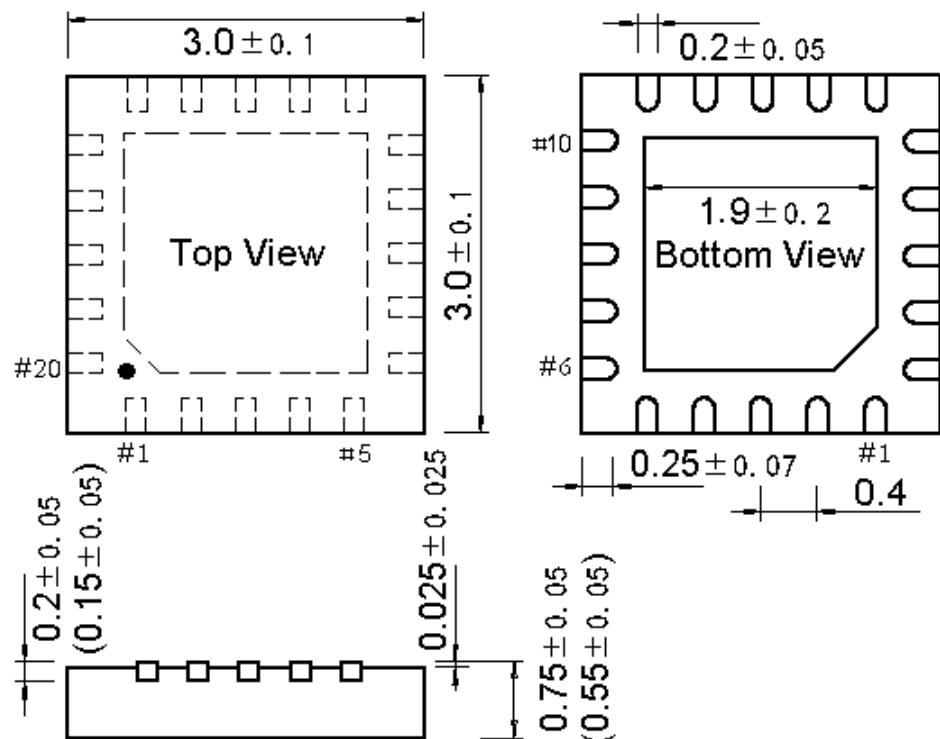

- 提供 QFN32X5、QFN32、QFN20 封装。

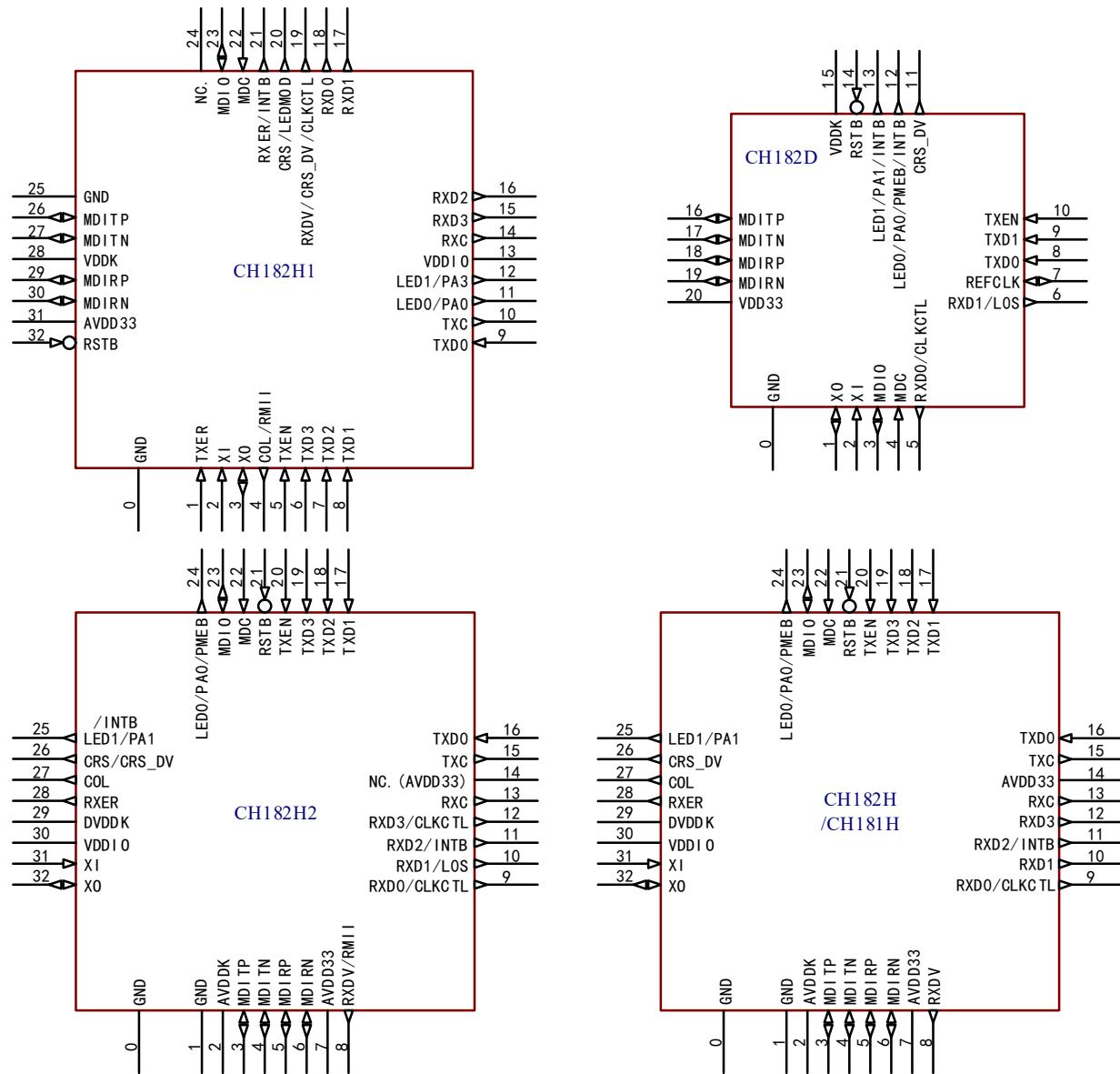

### 3、引脚排列

| 封装形式    | 塑体尺寸      | 引脚节距   | 封装说明       | 订货型号    |

|---------|-----------|--------|------------|---------|

| QFN32   | 4.0*4.0mm | 0.40mm | 四边无引线 32 脚 | CH182H1 |

| QFN20   | 3.0*3.0mm | 0.40mm | 四边无引线 20 脚 | CH182D  |

| QFN32X5 | 5.0*5.0mm | 0.50mm | 四边无引线 32 脚 | CH182H2 |

| QFN32X5 | 5.0*5.0mm | 0.50mm | 四边无引线 32 脚 | CH182H  |

| QFN32X5 | 5.0*5.0mm | 0.50mm | 四边无引线 32 脚 | CH181H  |

注：1、CH182H2 是 CH182H 的升级版本，引脚兼容。

2、新设计可用 CH182D/CH182H1/CH182H2，建议优选小体积的 CH182D 或 CH182H1。

3、客制引脚 CH182H3、CH182H6、CH182H7、CH182H8、CH182F2、CH182F7、CH182F8，仅批量预定，引脚排列和引脚定义请参考《CH182DS3》手册。

## 4、引脚定义

表 4-1 CH182H1 引脚定义

| 引脚号     | 引脚名称                | 类型                                         | 引脚说明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

|---------|---------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----|----|----|----|------|---------------------|--------------------------------------------|-------------------------------------------|--------------------------------------------|

| 0       | GND                 | P                                          | 公共接地端。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

| 1       | TXER                | I, PD                                      | 发送错误指示。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

| 2       | XI                  | I                                          | 晶振输入，需外接 25MHz 晶体一端，可选外部 25MHz 或 50MHz 时钟输入。<br>RMII 从模式下 XI 接 GND, TXC/REFCLKI 接 50MHz 时钟。                                                                                                                                                                                                                                                                                                                                                                                                               |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

| 3       | XO                  | I/O                                        | 晶振反相输出，需外接25MHz晶体另一端。<br>或XI接GND时，XO用于输入外部25MHz或50MHz时钟。                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

| 4       | COL/RMII            | LI,<br>0, PD                               | 碰撞监测 (COL)：<br>当检测到碰撞时，COL 输出高电平。<br><br>RMII 模式选择 (RMII)：<br>上电复位期间，<br>默认由内部下拉电阻置低电平 = MII 接口模式；<br>可选外部 4. 7KΩ 上拉电阻置高电平 = RMII 接口模式。                                                                                                                                                                                                                                                                                                                                                                   |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

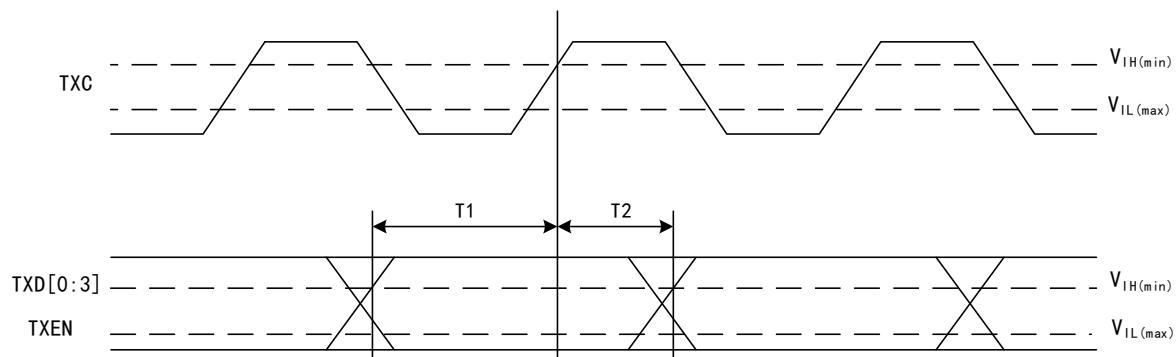

| 5       | TXEN                | I                                          | 发送使能 (TXEN)。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

| 6       | TXD3                | I                                          | 发送数据位 TXD[3:0]：                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

| 7       | TXD2                | I                                          | 由 MAC 驱动，向 PHY 提供并行的发送数据。<br>当 TXEN 使能时：                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

| 8       | TXD1                | I                                          | MII 模式下，TXD[3:0] 数据有效；                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

| 9       | TXD0                | I                                          | RMII 模式下，TXD[1:0] 数据有效。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

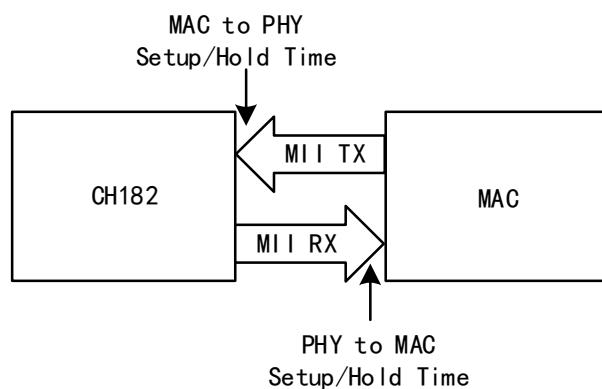

| 10      | TXC<br>/REFCLKI     | I/O                                        | MII 模式发送时钟 (TXC)：<br>在 MII 模式下，该引脚为 TXD[3:0] 和 TXEN 信号提供参考时钟。<br>TXC 在 100Mbps 和 10Mbps 模式下分别是 25MHz 和 2. 5MHz。<br><br>RMII 模式 50MHz 时钟输入 (REFCLKI)：<br>在 RMII 模式下，该模式用于 50MHz 时钟输入。                                                                                                                                                                                                                                                                                                                      |                                            |    |    |    |    |      |                     |                                            |                                           |                                            |

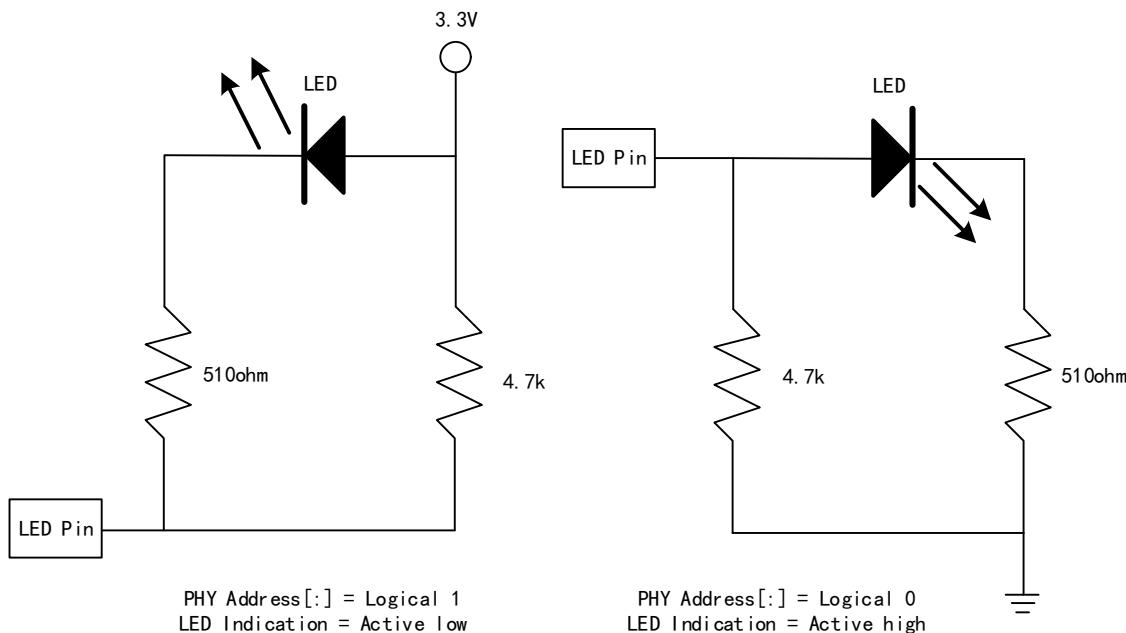

| 11      | LED0/PA0            | LI, 0<br>PD                                | LED0：<br>传统 LED 功能选择， 默认 LED_SEL 为 01：<br><table border="1" style="margin-left: auto; margin-right: auto;"> <tr> <th>LED_SEL</th> <th>00</th> <th>01</th> <th>10</th> <th>11</th> </tr> <tr> <th>LED0</th> <td>ACT<sub>ALL</sub></td> <td>LINK<sub>ALL</sub><br/>/ACT<sub>ALL</sub></td> <td>LINK<sub>10</sub><br/>/ACT<sub>ALL</sub></td> <td>LINK<sub>10</sub><br/>/ACT<sub>10</sub></td> </tr> </table><br>PHY 地址 [0] (PA0)：<br>上电锁存 PHY 地址 [0] 的值，<br>默认由内部下拉电阻置低电平 = 0；<br>可选外部 4. 7KΩ 上拉电阻置高电平 = 1。 | LED_SEL                                    | 00 | 01 | 10 | 11 | LED0 | ACT <sub>ALL</sub>  | LINK <sub>ALL</sub><br>/ACT <sub>ALL</sub> | LINK <sub>10</sub><br>/ACT <sub>ALL</sub> | LINK <sub>10</sub><br>/ACT <sub>10</sub>   |

| LED_SEL | 00                  | 01                                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11                                         |    |    |    |    |      |                     |                                            |                                           |                                            |

| LED0    | ACT <sub>ALL</sub>  | LINK <sub>ALL</sub><br>/ACT <sub>ALL</sub> | LINK <sub>10</sub><br>/ACT <sub>ALL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LINK <sub>10</sub><br>/ACT <sub>10</sub>   |    |    |    |    |      |                     |                                            |                                           |                                            |

| 12      | LED1/PA3            | LI, 0<br>PD                                | LED1：<br>传统 LED 功能选择， 默认 LED_SEL 为 01：<br><table border="1" style="margin-left: auto; margin-right: auto;"> <tr> <th>LED_SEL</th> <th>00</th> <th>01</th> <th>10</th> <th>11</th> </tr> <tr> <th>LED1</th> <td>LINK<sub>100</sub></td> <td>LINK<sub>100</sub></td> <td>LINK<sub>100</sub></td> <td>LINK<sub>100</sub><br/>/ACT<sub>100</sub></td> </tr> </table>                                                                                                                                          | LED_SEL                                    | 00 | 01 | 10 | 11 | LED1 | LINK <sub>100</sub> | LINK <sub>100</sub>                        | LINK <sub>100</sub>                       | LINK <sub>100</sub><br>/ACT <sub>100</sub> |

| LED_SEL | 00                  | 01                                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11                                         |    |    |    |    |      |                     |                                            |                                           |                                            |

| LED1    | LINK <sub>100</sub> | LINK <sub>100</sub>                        | LINK <sub>100</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LINK <sub>100</sub><br>/ACT <sub>100</sub> |    |    |    |    |      |                     |                                            |                                           |                                            |

| 引脚号     | 引脚名称                 | 类型           | 引脚说明                                                                                                                                                                                                                                                                   |

|---------|----------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH182H1 |                      |              |                                                                                                                                                                                                                                                                        |

|         |                      |              | PHY 地址[3] (PA3) :<br>上电锁存 PHY 地址[3]的值，<br>默认由内部下拉电阻置低电平 = 0；<br>可选外部 4. 7KΩ 上拉电阻置高电平 = 1。                                                                                                                                                                              |

| 13      | VDDIO                | P            | I/O 接口的电源输入，外接 0. 1uF 对地电容。                                                                                                                                                                                                                                            |

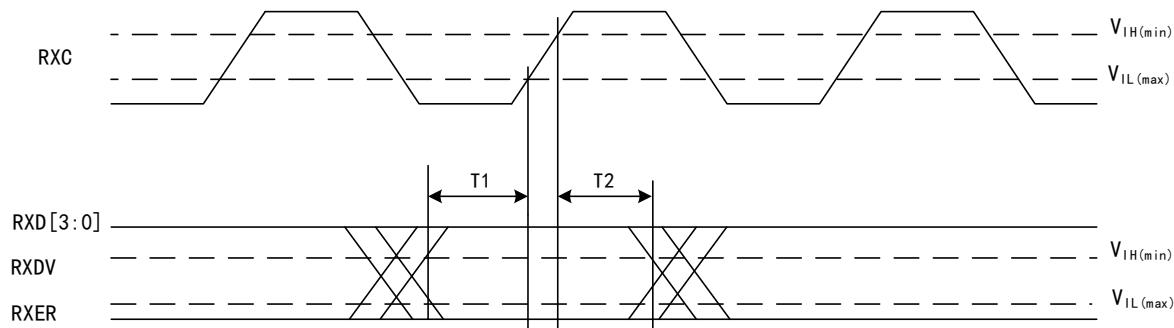

| 14      | RXC /REFCLK0         | 0            | 输出接收时钟 (RXC) :<br>该引脚提供用于 RXD[3:0] 和 RXDV 信号的连续工作时钟。<br>RXC 在 100Mbps 和 10Mbps 模式下分别是 25MHz 和 2. 5MHz。<br><br>RMII 模式 50MHz 时钟输出 (REFCLK0) :<br>在 RMII 模式下，50MHz 时钟输出。                                                                                                 |

| 15      | RXD3                 | 0            | 接收数据位 RXD[3:0] :<br>由 PHY 驱动，向 MAC 提供并行的接收数据。                                                                                                                                                                                                                          |

| 16      | RXD2                 | 0            |                                                                                                                                                                                                                                                                        |

| 17      | RXD1                 | 0            |                                                                                                                                                                                                                                                                        |

| 18      | RXD0                 | 0            |                                                                                                                                                                                                                                                                        |

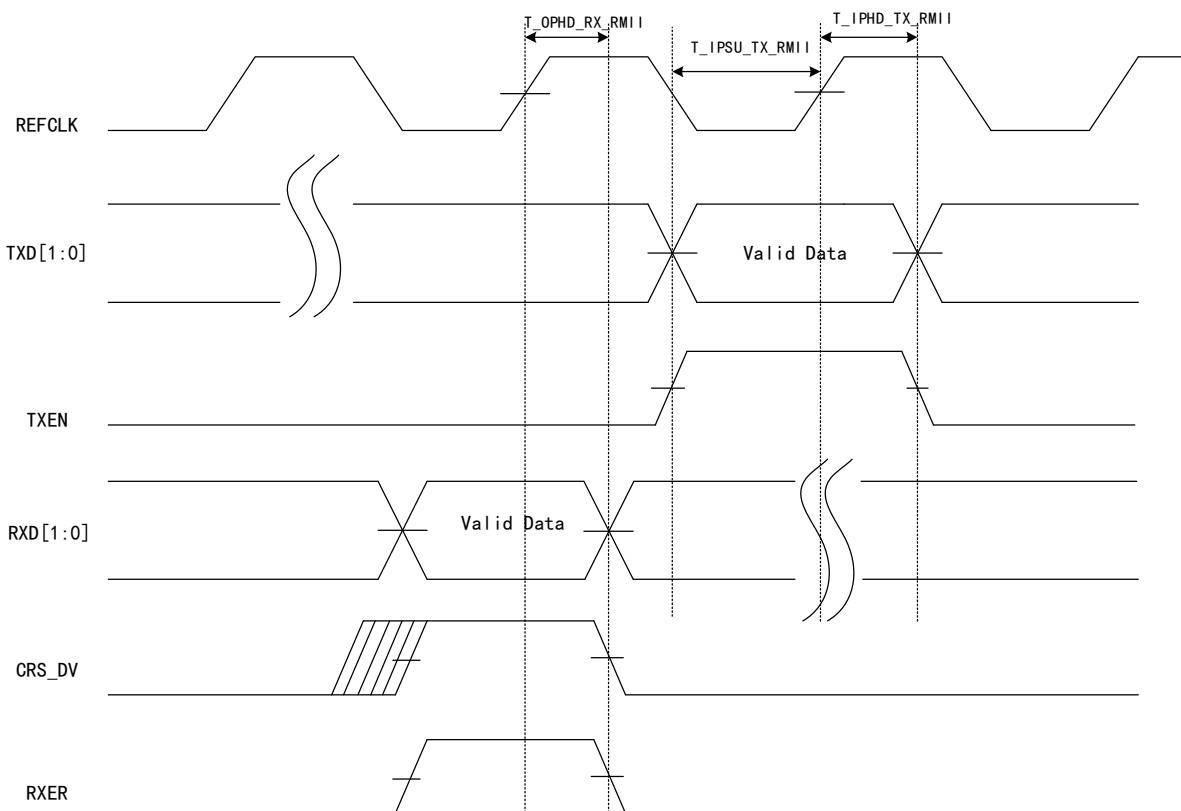

| 19      | RXDV /CRS_DV /CLKCTL | LI,<br>0, PD | 接收数据有效 (RXDV) :<br>MII 模式下，当 RXD[3:0] 接收数据时，该引脚输出高电平；当接收完成时被拉低；在 RXC 的上升沿有效。<br><br>载波检测/接收数据有效 (CRS_DV) :<br>RMII 模式下，如果接收媒介不处于空闲状态，则输出高电平。<br><br>时钟方向选择 (CLKCTL) :<br>RMII 模式下，上电期间根据该引脚的锁存值，用于配置参考时钟的方向：<br>内部下拉电阻置低电平 = RXC 输出时钟；<br>可选外部 4. 7KΩ 上拉电阻 = TXC 输入时钟。 |

| 20      | CRS /LEDMOD          | LI,<br>0, PD | 载波监测 (CRS) :<br>MII 模式下，该引脚输出高电平信号表明正在进行发送或者接收，输出低电平信号则表示正处于空闲状态。<br>而在 RMII 模式下，该引脚输出低电平。<br><br>LED 模式选择 (LEDMOD) :<br>上电复位期间，该引脚的锁存值用来确定 LED_SEL[1] 的值，请参考 LED 引脚的相关描述。                                                                                             |

| 21      | RXER /INTB           | LI,<br>0/OD  | 接收错误指示 (RXER) 。<br><br>INTB：中断输出，开漏输出。<br>注：该引脚功能由页 1 寄存器 28 决定。                                                                                                                                                                                                       |

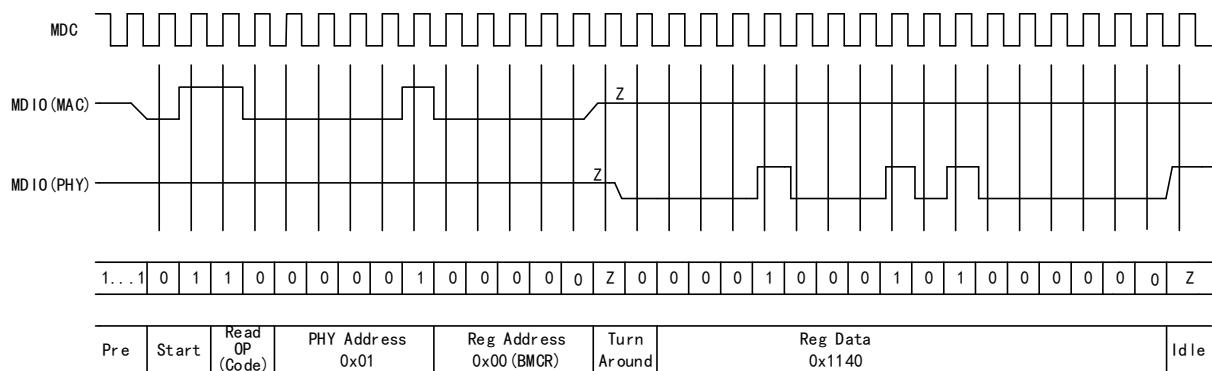

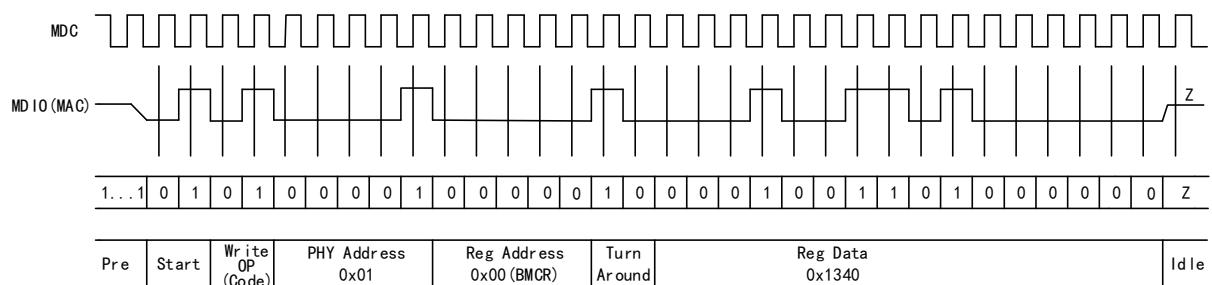

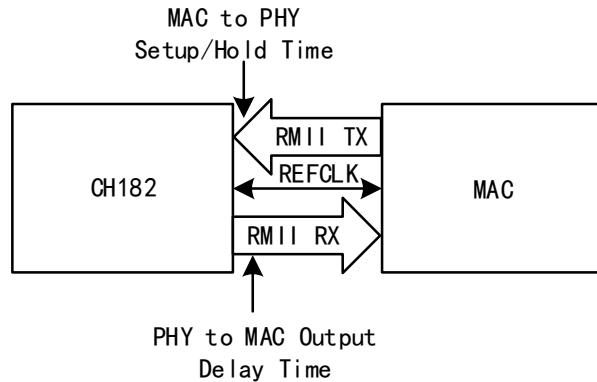

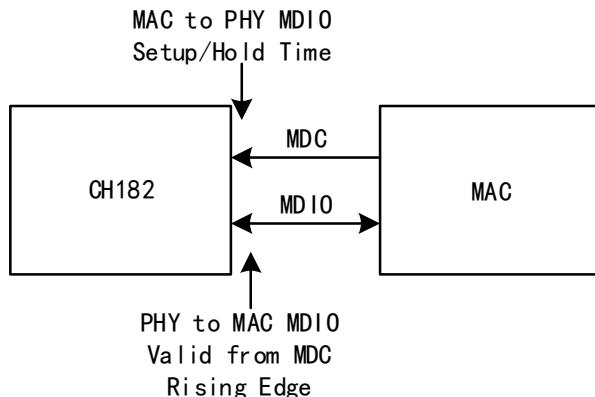

| 22      | MDC                  | I,<br>PU     | SMI 管理接口的时钟输入 (MDC) :<br>该引脚输入与 MDIO 同步的串行时钟，内置上拉电阻防止引脚浮空。                                                                                                                                                                                                             |

| 23      | MDIO                 | I/O,<br>PU   | SMI 管理接口的数据输入和输出 (MDIO) :<br>该引脚用于输入或输出管理信息的双向串行数据。                                                                                                                                                                                                                    |

| 24      | NC.                  | NC.          | 保留引脚，内部未连接。                                                                                                                                                                                                                                                            |

| 25      | GND                  | P            | 可选的公共接地端，建议连接。                                                                                                                                                                                                                                                         |

| 引脚号           | 引脚名称   | 类型    | 引脚说明                                                  |

|---------------|--------|-------|-------------------------------------------------------|

| CH182H1<br>26 | MDITP  | I/O   | 10BASE-T/100BASE-TX MDI 模式下的差分输出；                     |

| 27            | MDITN  | I/O   | 10BASE-T/100BASE-TX MDIX 模式下的差分输入。                    |

| 28            | VDDK   | P     | 外接 1uF 对地电容贴近芯片放置。                                    |

| 29            | MDIRP  | I/O   | 10BASE-T/100BASE-TX MDI 模式下的差分输入；                     |

| 30            | MDIRN  | I/O   | 10BASE-T/100BASE-TX MDIX 模式下的差分输出。                    |

| 31            | AVDD33 | P     | 3.3V 主电源输入，建议 0.1uF 并联 10uF 对地电容贴近芯片放置，或单个 1uF~4.7uF。 |

| 32            | RSTB   | I, PU | 复位输入，低电平有效。                                           |

注： I = 输入； O = 输出； I/O = 输入/输出； P = 电源；

OD = 开漏输出； PD = 上电复位内部拉低； PU = 上电复位内部拉高；

LI = 上电期间检测引脚状态并锁存输入用于功能配置； NC. = 保留引脚。

表 4-2 CH182H2/CH182D 引脚定义

| 引脚号         | 引脚名称 | 类型           | 引脚说明                                                                                                                                                                               |

|-------------|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH182D<br>0 | GND  | P            | 公共接地端。                                                                                                                                                                             |

| -           | 1    | P            | 可选的公共接地端，建议连接。                                                                                                                                                                     |

| -           | 2    | AVDDK        | 外接 1uF 对地电容贴近芯片放置。                                                                                                                                                                 |

| 15          | -    | VDDK         | 外接 1uF 对地电容贴近芯片放置。                                                                                                                                                                 |

| 16          | 3    | MDITP        | I/O 10BASE-T/100BASE-TX MDI 模式下的差分输出；                                                                                                                                              |

| 17          | 4    | MDITN        | I/O 10BASE-T/100BASE-TX MDIX 模式下的差分输入。                                                                                                                                             |

| 18          | 5    | MDIRP        | I/O 10BASE-T/100BASE-TX MDI 模式下的差分输入；                                                                                                                                              |

| 19          | 6    | MDIRN        | I/O 10BASE-T/100BASE-TX MDIX 模式下的差分输出。                                                                                                                                             |

| -           | 7    | AVDD33       | P 3.3V 主电源输入，建议 0.1uF 并联 10uF 对地电容贴近芯片放置，或单个 1uF~4.7uF。                                                                                                                            |

| 20          | -    | VDD33        | P 建议 0.1uF 并联 10uF 对地电容贴近芯片放置，或单个 1uF~4.7uF。                                                                                                                                       |

| -           | 8    | RXDV /RMII   | 接收数据有效 (RXDV)：<br>MII 模式下，当 RXD[3:0] 接收数据时，该引脚输出高电平；<br>当接收完成时被拉低；在 RXC 的上升沿有效。<br><br>RMII 模式选择 (RMII)：<br>上电复位期间，<br>默认由内部下拉电阻置低电平 = MII 接口模式<br>可选外部 4.7KΩ 上拉电阻置高电平 = RMII 接口模式 |

| 5           | 9    | RXD0 /CLKCTL | 接收数据位 [0] (RXD0)。<br><br>时钟方向选择 (CLKCTL)：<br>在 RMII 模式下，上电期间根据该引脚的锁存值，用于配置参考时钟的方向：<br>默认由内部下拉电阻置低电平 = TXC 输出时钟；<br>可选外部 4.7KΩ 上拉电阻置高电平 = TXC 输入时钟。                                 |

| 引脚号    |         | 引脚名称            | 类型                  | 引脚说明                                                                                                                                                                                                                                             |

|--------|---------|-----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH182D | CH182H2 |                 |                     |                                                                                                                                                                                                                                                  |

| 6      | 10      | RXD1 /LOS       | O, PD               | 接收数据位[1] (RXD1)。<br>LED0 功能选择 (LOS)：<br>默认内部由下拉电阻置低电平 = LED0 功能；<br>可选外部 4.7KΩ 上拉电阻置高电平 = WOL 功能。                                                                                                                                                |

| -      | 11      | RXD2 /INTB      | LI,<br>O/OD<br>, PD | 接收数据位[2] (RXD2)。<br><br>INTB：在 RMII 模式下，中断输出，开漏输出。                                                                                                                                                                                               |

| -      | 12      | RXD3 /CLKCTL    | LI,<br>O, PD        | 接收数据位[3] (RXD3)。<br><br>时钟方向选择 (CLKCTL)：<br>在 RMII 模式下，上电期间根据该引脚的锁存值，用于配置参考时钟的方向：<br>默认由内部下拉电阻置低电平 = TXC 输出时钟；<br>可选外部 4.7KΩ 上拉电阻置高电平 = TXC 输入时钟。                                                                                                |

| -      | 13      | RXC             | O, PD               | 输出接收时钟 (RXC)：<br>该引脚提供用于 RXD[3:0] 和 RXDV 信号的连续工作时钟。<br>RXC 在 100Mbps 和 10Mbps 模式下分别是 25MHz 和 2.5MHz。                                                                                                                                             |

| -      | 14      | NC.<br>(AVDD33) | NC.<br>(P)          | 保留引脚，内部未连接。<br>为了兼容 CH182H 的引脚，外部也可以连接到 3.3V 电源。                                                                                                                                                                                                 |

| -      | 15      | TXC<br>/REFCLK  | I/O,<br>PD          | MII 模式发送时钟 (TXC)：<br>在 MII 模式下，该引脚为 TXD[3:0] 和 TXEN 信号提供参考时钟。TXC 在 100Mbps 和 10Mbps 模式下分别是 25MHz 和 2.5MHz。<br><br>50MHz 参考时钟 (REFCLK)：<br>在 RMII 模式下，50MHz 时钟输入或输出，默认为输出。当 RXD0/CLKCTL 引脚、RXD3/CLKCTL 引脚、页 7 寄存器 16 其中之一配置为输入模式时，REFCLK 切换为输入模式。 |

| 7      | -       | REFCLK          | I/O,<br>PD          | 50MHz 参考时钟 (REFCLK)：<br>在 RMII 模式下，该引脚用于输出或者输入 50MHz 参考时钟 REFCLK。方向由 RXD0/CLKCTL 引脚或页 7 寄存器 16 决定。                                                                                                                                               |

| 8      | 16      | TXD0            | I, PD               | 发送数据位 TXD[3:0]：<br>由 MAC 驱动，向 PHY 提供并行的发送数据。                                                                                                                                                                                                     |

| 9      | 17      | TXD1            | I, PD               | 当 TXEN 使能时：                                                                                                                                                                                                                                      |

| -      | 18      | TXD2            | I, PD               | MII 模式下，TXD[3:0] 数据有效；                                                                                                                                                                                                                           |

| -      | 19      | TXD3            | I, PD               | RMII 模式下，TXD[1:0] 数据有效。                                                                                                                                                                                                                          |

| 10     | 20      | TXEN            | I, PD               | 发送使能 (TXEN)。                                                                                                                                                                                                                                     |

| 14     | 21      | RSTB            | I, PU               | 复位输入，低电平有效。                                                                                                                                                                                                                                      |

| 4      | 22      | MDC             | I, PU               | SMI 管理接口的时钟输入 (MDC)：<br>该引脚输入与 MDIO 同步的串行时钟，<br>内置上拉电阻防止引脚浮空。                                                                                                                                                                                    |

| 3      | 23      | MDIO            | I/O,<br>PU          | SMI 管理接口的数据输入和输出 (MDIO)：<br>该引脚用于输入或输出管理信息的双向串行数据。                                                                                                                                                                                               |

| 引脚号     |                     | 引脚名称                                       | 类型                                        | 引脚说明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |    |    |      |                     |                                            |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

|---------|---------------------|--------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----|----|------|---------------------|--------------------------------------------|--------------------|--------------------------------------------|-------------------------------------------|------------------------------------------|----|------|---------------------|---------------------|---------------------|--------------------------------------------|

| CH182D  | CH182H2             |                                            |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |    |    |      |                     |                                            |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

| -       | 24                  | LEDO<br>/PA0<br>/PMEB                      | LI,<br>0/OD<br>, PU                       | <p>LED0:</p> <p>传统 LED 功能选择， 默认 LED_SEL 为 11:</p> <table border="1"> <tr> <td>LED_SEL</td> <td>00</td> <td>01</td> <td>10</td> <td>11</td> </tr> <tr> <td>LEDO</td> <td>ACT<sub>ALL</sub></td> <td>LINK<sub>ALL</sub><br/>/ACT<sub>ALL</sub></td> <td>LINK<sub>10</sub><br/>/ACT<sub>ALL</sub></td> <td>LINK<sub>10</sub><br/>/ACT<sub>10</sub></td> </tr> </table> <p>PHY 地址[0] (PA0) :</p> <p>上电锁存 PHY 地址[0]的值，<br/>默认由内部上拉电阻置高电平 = 1；<br/>可选外部接下拉电阻置低电平 = 0。</p> <p>电源管理事件输出 (PMEB) :</p> <p>WOL 电源管理事件输出，低电平有效。<br/>如果接收到魔法包或唤醒帧，则输出低电平。<br/>注：该引脚功能由页 1 寄存器 28 决定。</p> | LED_SEL | 00 | 01 | 10   | 11                  | LEDO                                       | ACT <sub>ALL</sub> | LINK <sub>ALL</sub><br>/ACT <sub>ALL</sub> | LINK <sub>10</sub><br>/ACT <sub>ALL</sub> | LINK <sub>10</sub><br>/ACT <sub>10</sub> |    |      |                     |                     |                     |                                            |

| LED_SEL | 00                  | 01                                         | 10                                        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |    |    |      |                     |                                            |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

| LEDO    | ACT <sub>ALL</sub>  | LINK <sub>ALL</sub><br>/ACT <sub>ALL</sub> | LINK <sub>10</sub><br>/ACT <sub>ALL</sub> | LINK <sub>10</sub><br>/ACT <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |    |    |      |                     |                                            |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

| 12      | -                   | LEDO/PA0<br>/PMEB<br>/INTB                 | LI,<br>0/OD<br>, PU                       | <p>LED0:</p> <p>传统 LED 功能选择， 默认 LED_SEL 为 01:</p> <table border="1"> <tr> <td>LED_SEL</td> <td>00</td> <td>01</td> </tr> <tr> <td>LEDO</td> <td>ACT<sub>ALL</sub></td> <td>LINK<sub>ALL</sub><br/>/ACT<sub>ALL</sub></td> </tr> </table> <p>PHY 地址[0] (PA0) :</p> <p>上电锁存 PHY 地址[0]的值，<br/>默认由内部上拉电阻置高电平 = 1；<br/>可选外部接下拉电阻置低电平 = 0。</p> <p>电源管理事件输出 (PMEB) :</p> <p>WOL 电源管理事件输出，低电平有效。<br/>如果接收到魔法包或唤醒帧，则输出低电平。</p> <p>INTB: 中断输出，开漏输出。<br/>注：该引脚功能由页 1 寄存器 28 决定。</p>                                                                                                    | LED_SEL | 00 | 01 | LEDO | ACT <sub>ALL</sub>  | LINK <sub>ALL</sub><br>/ACT <sub>ALL</sub> |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

| LED_SEL | 00                  | 01                                         |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |    |    |      |                     |                                            |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

| LEDO    | ACT <sub>ALL</sub>  | LINK <sub>ALL</sub><br>/ACT <sub>ALL</sub> |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |    |    |      |                     |                                            |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

| 13      | 25                  | LED1<br>/PA1<br>/INTB                      | LI,<br>0/OD<br>, PD                       | <p>LED1:</p> <p>对于 CH182D 芯片， 默认 LED_SEL 为 01:</p> <table border="1"> <tr> <td>LED_SEL</td> <td>00</td> <td>01</td> </tr> <tr> <td>LED1</td> <td>LINK<sub>100</sub></td> <td>LINK<sub>100</sub></td> </tr> </table> <p>对于 CH182H2 芯片， 默认 LED_SEL 为 11:</p> <table border="1"> <tr> <td>LED_SEL</td> <td>00</td> <td>01</td> <td>10</td> <td>11</td> </tr> <tr> <td>LED1</td> <td>LINK<sub>100</sub></td> <td>LINK<sub>100</sub></td> <td>LINK<sub>100</sub></td> <td>LINK<sub>100</sub><br/>/ACT<sub>100</sub></td> </tr> </table> <p>PHY 地址[1] (PA1) :</p>                 | LED_SEL | 00 | 01 | LED1 | LINK <sub>100</sub> | LINK <sub>100</sub>                        | LED_SEL            | 00                                         | 01                                        | 10                                       | 11 | LED1 | LINK <sub>100</sub> | LINK <sub>100</sub> | LINK <sub>100</sub> | LINK <sub>100</sub><br>/ACT <sub>100</sub> |

| LED_SEL | 00                  | 01                                         |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |    |    |      |                     |                                            |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

| LED1    | LINK <sub>100</sub> | LINK <sub>100</sub>                        |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |    |    |      |                     |                                            |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

| LED_SEL | 00                  | 01                                         | 10                                        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |    |    |      |                     |                                            |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

| LED1    | LINK <sub>100</sub> | LINK <sub>100</sub>                        | LINK <sub>100</sub>                       | LINK <sub>100</sub><br>/ACT <sub>100</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |    |    |      |                     |                                            |                    |                                            |                                           |                                          |    |      |                     |                     |                     |                                            |

| 引脚号    |        | 引脚名称        | 类型    | 引脚说明                                                                                                                                           |

|--------|--------|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| CH182D | CH182H |             |       |                                                                                                                                                |

|        |        |             |       | 上电锁存 PHY 地址[1]的值，<br>默认由内部下拉电阻置低电平 = 0；<br>可选外部 4.7KΩ 上拉电阻置高电平 = 1。<br><br>INTB：中断输出，开漏输出。<br>注：该引脚功能由页 1 寄存器 28 决定。                           |

| -      | 26     | CRS /CRS_DV | 0, PD | 载波检测（CRS）：<br>MII 模式下，该引脚输出高电平信号表示正在进行发送或者接收，低电平信号则表示正处于空闲状态。<br><br>载波检测/接收数据有效（CRS_DV）：<br>RMII 模式下，如果接收媒介不处于空闲状态，则输出高电平。                    |

| 11     | -      | CRS_DV      | 0, PD | 载波检测/接收数据有效（CRS_DV）：<br>如果接收媒介不处于空闲状态，则输出高电平。                                                                                                  |

| -      | 27     | COL         | 0, PD | 碰撞监测（COL）：当检测到碰撞时，COL 输出高电平。                                                                                                                   |

| -      | 28     | RXER        | 0, PD | 接收错误指示（RXER）。                                                                                                                                  |

| -      | 29     | DVDDK       | P     | 外接 0.1uF (0.1uF~1uF) 对地电容贴近芯片放置。                                                                                                               |

| -      | 30     | VDDIO       | P     | I/O 接口的电源输入，外接 0.1uF 对地电容。                                                                                                                     |

| 2      | 31     | XI          | I     | 晶振输入，需外接 25MHz 晶体一端，可选外部 25MHz 或 50MHz 时钟输入。                                                                                                   |

| 1      | 32     | XO          | I/O   | 晶振反相输出，需外接 25MHz 晶体另一端。<br>或在 XI 接 GND 时，XO 用于输入外部 25MHz 或 50MHz 时钟。<br>注：RMII 模式下，当 XO 设置为输入时钟时，需设置 REFCLK 为输出，或设置 REFCLK 为输入且需外部提供 50MHz 时钟。 |

注：I = 输入； O = 输出； I/O = 输入/输出； P = 电源；

OD = 开漏输出； PD = 上电复位内部拉低； PU = 上电复位内部拉高；

LI = 上电期间检测引脚状态并锁存输入用于功能配置； NC. = 保留引脚。

表 4-3 CH182H/CH181H 引脚定义

| 引脚号    |        | 引脚名称  | 类型  | 引脚说明                               |

|--------|--------|-------|-----|------------------------------------|

| CH181H | CH182H |       |     |                                    |

| 0      | 0      | GND   | P   | 公共接地端。                             |

| 1      | 1      | GND   | P   | 可选的公共接地端，建议连接。                     |

| 2      | 2      | AVDDK | P   | 外接 1uF 对地电容贴近芯片放置。                 |

| 3      | 3      | MDITP | I/O | 10BASE-T/100BASE-TX MDI 模式下的差分输出；  |

| 4      | 4      | MDITN | I/O | 10BASE-T/100BASE-TX MDIX 模式下的差分输入。 |

| 5      | 5      | MDIRP | I/O | 10BASE-T/100BASE-TX MDI 模式下的差分输入；  |

| 6      | 6      | MDIRN | I/O | 10BASE-T/100BASE-TX MDIX 模式下的差分输出。 |

| 引脚号    |        | 引脚名称                  | 类型                  | 引脚说明                                                                                                                                                                                                      |

|--------|--------|-----------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH181H | CH182H |                       |                     |                                                                                                                                                                                                           |

| 7      | 7      | AVDD33                | P                   | 3.3V 主电源输入，建议 0.1uF 并联 10uF 对地电容贴近芯片放置，或单个 1uF~4.7uF。                                                                                                                                                     |

| 8      | 8      | RXDV                  | L1,<br>0, PD        | 接收数据有效 (RXDV)。<br>当 RXD[3:0] 接收数据时，该引脚输出高电平；当接收完成时被拉低；在 RXC 的上升沿有效。上电复位期间 PHY 检测该引脚配置 MAC 接口模式：<br>默认由内部下拉电阻置低电平 = MII 接口模式；<br>可选外部 4.7KΩ 上拉电阻置高电平 = RMII 接口模式。                                          |

| 9      | 9      | RXDO<br>/CLKCTL       | L1,<br>0, PD        | 接收数据位 [0] (RXDO)。<br><br>时钟方向选择 (CLKCTL)：<br>在 RMII 模式下，上电期间根据该引脚的锁存值，用于配置参考时钟的方向：<br>默认由内部下拉电阻置低电平 = TXC 输出时钟；<br>可选外部 4.7KΩ 上拉电阻置高电平 = TXC 输入时钟。                                                        |

| 10     | 10     | RXD1                  | 0, PD               | 接收数据位 [1] (RXD1)。                                                                                                                                                                                         |

| 11     | 11     | RXD2<br>/INTB         | L1,<br>0, PD        | 接收数据位 [2] (RXD2)。<br><br>INTB：在 RMII 模式下，中断输出，开漏输出。                                                                                                                                                       |

| 12     | 12     | RXD3                  | 0, PD               | 接收数据位 [3] (RXD3)。                                                                                                                                                                                         |

| 13     | 13     | RXC                   | 0, PD               | 输出接收时钟 (RXC)。<br>该引脚提供用于 RXD[3:0] 和 RXDV 信号的连续工作时钟。<br>RXC 在 100Mbps 和 10Mbps 模式下分别是 25MHz 和 2.5MHz。                                                                                                      |

| 14     | 14     | AVDD33                | P                   | 可选的 3.3V 电源输入。                                                                                                                                                                                            |

| 15     | 15     | TXC<br>/REFCLK        | I/O,<br>PD          | MII 模式输出发送时钟，RMII 模式输出或输入参考时钟。<br>在 MII 模式下，该引脚为 TXD[3:0] 和 TXEN 信号提供参考时钟。TXC 在 100Mbps 和 10Mbps 模式下分别是 25MHz 和 2.5MHz。<br><br>在 RMII 模式下，该引脚用于输出或者输入 50MHz 参考时钟 REFCLK。方向由 RXDO/CLKCTL 引脚或页 7 寄存器 16 决定。 |

| 16     | 16     | TXD0                  | I, PD               | 发送数据位 TXD[3:0]。<br>由 MAC 驱动，向 PHY 提供并行的发送数据。<br>当 TXEN 使能时，TXD[0:3] 数据有效。                                                                                                                                 |

| 17     | 17     | TXD1                  | I, PD               |                                                                                                                                                                                                           |

| 18     | 18     | TXD2                  | I, PD               |                                                                                                                                                                                                           |

| 19     | 19     | TXD3                  | I, PD               |                                                                                                                                                                                                           |

| 20     | 20     | TXEN                  | I, PD               | 发送使能 (TXEN)。                                                                                                                                                                                              |

| 21     | 21     | RSTB                  | I, PU               | 复位输入，低电平有效。                                                                                                                                                                                               |

| 22     | 22     | MDC                   | I, PU               | SMI 管理接口的时钟输入 (MDC)。<br>该引脚输入与 MDIO 同步的串行时钟，<br>内置上拉电阻防止引脚浮空。                                                                                                                                             |

| 23     | 23     | MDIO                  | I/O,<br>PU          | SMI 管理接口的数据输入和输出 (MDIO)。<br>该引脚用于输入或输出管理信息的双向串行数据。                                                                                                                                                        |

| 24     | 24     | LEDO<br>/PA0<br>/PMEB | L1,<br>0/OD<br>, PU | PHY 的 SMI 管理接口的地址和自定义 LED 设置。<br>默认 LED 引脚为 LED 功能：<br>PHY 地址由 PA1 和 PA0 选择：00000~00011， 默认 01；                                                                                                           |

| 引脚号                                           |        | 引脚名称      | 类型           | 引脚说明                                                                   |                     |                                            |                                           |                                            |  |  |

|-----------------------------------------------|--------|-----------|--------------|------------------------------------------------------------------------|---------------------|--------------------------------------------|-------------------------------------------|--------------------------------------------|--|--|

| CH181H                                        | CH182H |           |              |                                                                        |                     |                                            |                                           |                                            |  |  |

| 25                                            | 25     | LED1 /PA1 | LI,<br>0, PD | 传统 LED 功能选择, 默认 LED_SEL 为 11:                                          |                     |                                            |                                           |                                            |  |  |

|                                               |        |           |              | LED_SEL                                                                | 00                  | 01                                         | 10                                        | 11                                         |  |  |

|                                               |        |           |              | LEDO                                                                   | ACT <sub>ALL</sub>  | LINK <sub>ALL</sub><br>/ACT <sub>ALL</sub> | LINK <sub>10</sub><br>/ACT <sub>ALL</sub> | LINK <sub>10</sub><br>/ACT <sub>10</sub>   |  |  |

|                                               |        |           |              | LED1                                                                   | LINK <sub>100</sub> | LINK <sub>100</sub>                        | LINK <sub>100</sub>                       | LINK <sub>100</sub><br>/ACT <sub>100</sub> |  |  |

|                                               |        |           |              | LED2                                                                   | 保留                  | 保留                                         | 保留                                        | 保留                                         |  |  |

| 注: CH181H LED 闪烁判断信号为以太网载波信号。                 |        |           |              |                                                                        |                     |                                            |                                           |                                            |  |  |

| 电源管理事件输出 (PMEB) :                             |        |           |              |                                                                        |                     |                                            |                                           |                                            |  |  |

| WOL 电源管理事件输出, 低电平有效。<br>如果接收到魔法包或唤醒帧, 则输出低电平。 |        |           |              |                                                                        |                     |                                            |                                           |                                            |  |  |

| 26                                            | 26     | CRS_DV    | 0, PD        | 载波检测/接收数据有效 (CRS_DV)。<br>如果接收媒介不处于空闲状态, 则输出高电平。                        |                     |                                            |                                           |                                            |  |  |

| 27                                            | 27     | COL       | 0, PD        | 碰撞监测 (COL) : 当检测到碰撞时, COL 输出高电平。                                       |                     |                                            |                                           |                                            |  |  |

| 28                                            | 28     | RXER      | 0, PD        | 接收错误指示 (RXER)。                                                         |                     |                                            |                                           |                                            |  |  |

| 29                                            | 29     | DVDDK     | P            | 外接 0.1uF (0.1uF~1uF) 对地电容贴近芯片放置。                                       |                     |                                            |                                           |                                            |  |  |

| 30                                            | 30     | VDDIO     | P            | I/O 接口的电源输入, 外接 0.1uF 对地电容。                                            |                     |                                            |                                           |                                            |  |  |

| 31                                            | 31     | XI        | I            | 晶振输入, 需外接 25MHz 晶体一端, 或外部 25MHz 时钟输入。                                  |                     |                                            |                                           |                                            |  |  |

| 32                                            | 32     | XO        | I/O          | 晶振反相输出, 需外接 25MHz 晶体另一端。<br>或在 XI 接 GND 时, XO 用于输入外部 25MHz 或 50MHz 时钟。 |                     |                                            |                                           |                                            |  |  |

注: I = 输入; O = 输出; I/O = 输入/输出; P = 电源;

OD = 开漏输出; PD = 上电复位内部拉低; PU = 上电复位内部拉高;

LI = 上电期间检测引脚状态并锁存输入用于功能配置。

## 5、寄存器描述

表 5-1 PHY 寄存器描述

| 寄存器名称(BASE)                             | 地址        | 默认值         |

|-----------------------------------------|-----------|-------------|

| Control Register                        | 0x00      | 3100h       |

| Status Register                         | 0x01      | 7849h       |

| PHY Identifier                          | 0x02/0x03 | 7371h/9XXXh |

| Auto-Negotiation Advertisement          | 0x04      | 01e1h       |

| Auto-Negotiation Link Partner Ability   | 0x05      | 0001h       |

| Auto-Negotiation Expansion              | 0x06      | 0044h       |

| PAGE_SEL                                | 0x1F      | 0000h       |

| 寄存器名称(PAGE 7) (适用于除 CH181H、CH182H 以外芯片) | 地址        | 默认值         |

| INTERRUPT_MASK                          | 0x13      | 0030h       |

| 寄存器名称(PAGE 18) (仅适用于 CH182D 芯片)         | 地址        | 默认值         |

| MAC_PHY_ADDR0                           | 0x1A      | X           |

| MAC_PHY_ADDR1                           | 0x1B      | X           |

| MAC_PHY_ADDR2                           | 0x1C      | X           |

注: 1. 上述寄存器描述中, 默认缩写形式如下:

复位值: 1 = 位设置为逻辑 1;

0 = 位设置为逻辑 0;

X = 没有默认值;

h = 十六进制;

访问类型: R0 = 只读;

RW = 读/写;

RC = 读取清除。

SC = 自清除。

2. 其它扩展寄存器包含接口时序、厂商自定义特性等, 通常不需要修改, 详细可参考《CH182DS2》手册。

## 5.1 寄存器 0 控制寄存器 Control Register

| 位       | 名称                       | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 访问     | 默认值 |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

|---------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|---------|------|---------|------|---------|-----------------------|---------|-----------------------|---------|-----------------------|---------|----------------------|----|---|

| 15      | Reset                    | 软件复位，复位完成后自动清0。                                                                                                                                                                                                                                                                                                                                                                                                                                              | RW, SC | 0   |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| 14      | Loopback                 | 设置发送到接收数据路径。<br>1 = 启用Loopback；0 = 正常工作。                                                                                                                                                                                                                                                                                                                                                                                                                     | RW     | 0   |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| 13      | Speed Selection          | 设置网络速度。<br>1 = 100Mbps；0 = 10Mbps。<br>完成自动协商后，该位反映速度状态。<br>1 = 100BASE-T；0 = 10BASE-T。<br>注：部分封装的默认值根据引脚锁存值确定。<br><table border="1"> <tr> <th>封装</th> <th>引脚</th> </tr> <tr> <td>CH182H8</td> <td>LED1</td> </tr> <tr> <td>CH182F8</td> <td>LEDO</td> </tr> <tr> <td>CH182H3</td> <td>LED1</td> </tr> <tr> <td>CH182H7</td> <td>{COL/CRS, RXD1, RXDO}</td> </tr> <tr> <td>CH182F7</td> <td>{CRS_DV, RXD1, RXDO}</td> </tr> </table>                          | 封装     | 引脚  | CH182H8 | LED1 | CH182F8 | LEDO | CH182H3 | LED1                  | CH182H7 | {COL/CRS, RXD1, RXDO} | CH182F7 | {CRS_DV, RXD1, RXDO}  | RW      | 1                    |    |   |

| 封装      | 引脚                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182H8 | LED1                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182F8 | LEDO                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182H3 | LED1                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182H7 | {COL/CRS, RXD1, RXDO}    |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182F7 | {CRS_DV, RXD1, RXDO}     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| 12      | Auto-Negotiation Enable  | 自动协商功能。<br>1 = 启用自动协商，位13和位8将被忽略；<br>0 = 禁用自动协商，位13和位8将确定链接速度和数据传输模式。<br>注：部分封装的默认值根据引脚锁存值确定。<br><table border="1"> <tr> <th>封装</th> <th>引脚</th> </tr> <tr> <td>CH182H8</td> <td>LEDO</td> </tr> <tr> <td>CH182F8</td> <td>LEDO</td> </tr> <tr> <td>CH182H3</td> <td>RXDO</td> </tr> <tr> <td>CH182H6</td> <td>RXDO</td> </tr> <tr> <td>CH182H7</td> <td>{COL/CRS, RXD1, RXDO}</td> </tr> <tr> <td>CH182F7</td> <td>{CRS_DV, RXD1, RXDO}</td> </tr> </table> | 封装     | 引脚  | CH182H8 | LEDO | CH182F8 | LEDO | CH182H3 | RXDO                  | CH182H6 | RXDO                  | CH182H7 | {COL/CRS, RXD1, RXDO} | CH182F7 | {CRS_DV, RXD1, RXDO} | RW | 1 |

| 封装      | 引脚                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182H8 | LEDO                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182F8 | LEDO                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182H3 | RXDO                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182H6 | RXDO                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182H7 | {COL/CRS, RXD1, RXDO}    |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182F7 | {CRS_DV, RXD1, RXDO}     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| 11      | Power Down               | 1 = 关闭电源；0 = 正常运行。                                                                                                                                                                                                                                                                                                                                                                                                                                           | RW     | 0   |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| 10      | Isolate                  | 1 = MII/RMII接口与PHY隔离，PHY依旧能够响应MDI/MDIO；<br>0 = 正常工作。<br>注：该位的上电初始值根据相应引脚锁存值确定，软复位会恢复到默认值。<br><table border="1"> <tr> <th>封装</th> <th>管脚</th> </tr> <tr> <td>CH182H8</td> <td>RXER</td> </tr> <tr> <td>CH182H3</td> <td>RXER</td> </tr> <tr> <td>CH182H7</td> <td>{COL/CRS, RXD1, RXDO}</td> </tr> <tr> <td>CH182F7</td> <td>{CRS_DV, RXD1, RXDO}</td> </tr> </table>                                                                                         | 封装     | 管脚  | CH182H8 | RXER | CH182H3 | RXER | CH182H7 | {COL/CRS, RXD1, RXDO} | CH182F7 | {CRS_DV, RXD1, RXDO}  | RW      | 0                     |         |                      |    |   |

| 封装      | 管脚                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182H8 | RXER                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |

| CH182H3 | RXER                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |     |         |      |         |      |         |                       |         |                       |         |                       |         |                      |    |   |