# 250-mA, 3.3-V OUTPUT, LOW-IQ, LOW-DROPOUT LINEAR REGULATOR

## **FEATURES**

- > Ultralow noise: 9 μVRMS, independent of VOUT

- Ultralow quiescent current

IGND = 15 μA with zero load

- Maximum output current: 250 mAInput voltage range: 3.7 V to 5.5 V

- Output voltage: 3.3 V

- Output voltage tolerance: ±1%

- $\triangleright$  Low shutdown current: < 1 $\mu$ A

- ➤ Low dropout: 140 mV

- ➤ PSRR performance of 62 dB at 1 kHz

- No additional noise bypass capacitor required

- Stable with 1 μF ceramic input and output capacitors

- Current limit and thermal overload protection

- Logic-controlled enable

- 5-Pin SOT-23 Package

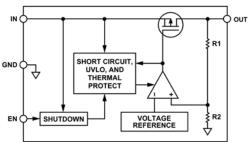

Figure 1. Functional Block Diagram

# **APPLICATIONS**

- Smartphones

- > Tablets

- Communications equipment

- Digital still cameras

- > Factory automation

# **SPECIFICATIONS**

at operating temperature range (TJ = -40°C to +125°C), VIN = 5.5V, VEN = VIN, IOUT = 1mA, CIN = 1 $\mu$ F, and COUT = 1 $\mu$ F, and TA = 25°C (unless otherwise noted).

|                      | PARAMETER                    | TEST CONDITIONS  TA = 25°C                     | MIN     | ТҮР | <b>MAX</b> 5.5 | UNIT<br>V |  |

|----------------------|------------------------------|------------------------------------------------|---------|-----|----------------|-----------|--|

| V <sub>IN</sub>      | Input voltage                |                                                | 3.7     |     |                |           |  |

| V <sub>OUT</sub>     | Output voltage               | TA = 25°C                                      |         | 3.3 |                | V         |  |

|                      | Output voltage accuracy      | IOUT = 10 mA, T <sub>J</sub> = -40°C to +125°C | -1      |     | +1             | %         |  |

| V <sub>EN</sub>      | Enable input voltage high    | 3.7 V ≤ VIN ≤ 5.5 V                            | 2.0 5.5 |     | V              |           |  |

|                      | Enable input voltage low     | 3.7 V ≤ VIN ≤ 5.5 V                            | 0       |     | 0.4            | V         |  |

| I <sub>OUT</sub>     | Output current               |                                                | 0       |     | 250            | mA        |  |

| I <sub>GND</sub>     | Operating supply current     | VEN = 5.5 V, IOUT = 0 mA                       |         | 15  | 28             |           |  |

|                      |                              | VEN = 5.5 V, IOUT = 10 mA                      |         | 45  | 60             | μA        |  |

|                      |                              | VEN = 5.5 V, IOUT = 250 mA                     |         | 270 | 320            |           |  |

| I <sub>G</sub>       | Shutdown current             | VEN = GND                                      |         | 0.2 | 0.7            |           |  |

|                      |                              | VEN = GND, T <sub>J</sub> = -40°C to +125°C    |         |     | 1              | μA        |  |

| $V_{DROP}$           | Dropout voltage              | IOUT = 10 mA                                   |         | 10  | 50             | m∨        |  |

|                      |                              | IOUT = 100 mA                                  |         | 80  | 100            |           |  |

|                      |                              | IOUT = 250 mA                                  |         | 140 | 260            |           |  |

| PSRR                 | Power-supply rejection ratio | 1 KHz, Iout = 10 mA                            |         | 62  | 65             | dB        |  |

|                      |                              | 10 KHz, Iоuт = 10 mA                           |         | 60  | 64             |           |  |

|                      |                              | 100 KHz, Iout = 10 mA                          |         | 55  | 58             |           |  |

| OUT <sub>Noise</sub> | Output noise voltage         | BW=10 Hz to 100 kHz                            |         | 9   | 50             |           |  |

|                      |                              | BW=10 Hz to 100 kHz, Iout = 1 mA               |         | 9   | 27             | μVrms     |  |

|                      |                              | BW=10 Hz to 100 kHz, Iout = 100 mA             |         | 10  | 35             |           |  |

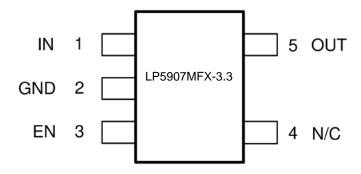

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

| TERMINAL |                                                                               | DESCRIPTION                                                                                   |  |

|----------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| NAME     | NO.                                                                           | DESCRIPTION                                                                                   |  |

| IN       | 1                                                                             | Regulator Input Supply. Bypass IN to GND with a 1 μF or greater capacitor                     |  |

| GND      | 2                                                                             | The ground return for the supply and signals.                                                 |  |

| EN       | 3                                                                             | Enable Input. Drive EN high to turn on the regulator; drive EN low to turn off the regulator. |  |

|          |                                                                               | For automatic startup, connect EN to IN.                                                      |  |

| N/C      | 4                                                                             | 4 No Connect. Not connected internally.                                                       |  |

| OUT      | Regulated Output Voltage. Bypass OUT to GND with a 1 μF or greater capacitor. |                                                                                               |  |

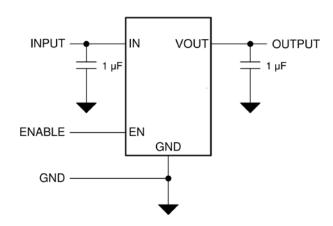

#### TYPICAL CONNECTION

Figure 3 shows a typical connection diagram for the LP5907MFX-3.3. The default minimum recommended value for input/output capacitance is 1  $\mu$ F. In certain applications, input and output capacitors with a capacitance greater than 1  $\mu$ F may be selected. To enable default automatic startup, connect the EN (enable) pin directly to IN.

Figure 3. Typical Circuit Configuration

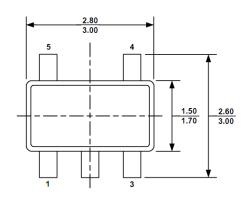

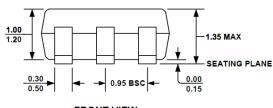

### **OUTLINE DIMENTIONS**

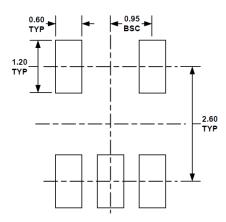

**TOP VIEW**

RECOMMENDED LAND PATTERN

**FRONT VIEW**

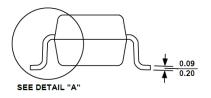

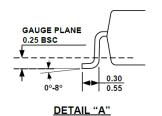

**SIDE VIEW**

NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING CONFORMS TO JEDEC MO-178, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

#### **NOTES**

- 1. Unpacked ICs, tube-mounted ICs, etc. must be stored in a drying cabinet, and the humidity in the drying cabinet < 20% R.H.

- 2. After access, the components are stored in an electrostatic packaging protective bag.

- 3. Anti-static damage: the device is an electrostatic sensitive device, and sufficient anti-static measures should be taken during transmission, assembly and testing.

- 4. The user should conduct a visual inspection before use, and the bottom, side and surrounding of the circuit can be welded only if it is bright. If oxidation occurs, the circuit can be processed by means of oxidation, and the circuit must be soldered within 12 hours after processing.