## 13.56MHz reader/writer for contactless communication

### **Feature and benefits**

- Highly integrated analog circuitry to demodulate and decode responses

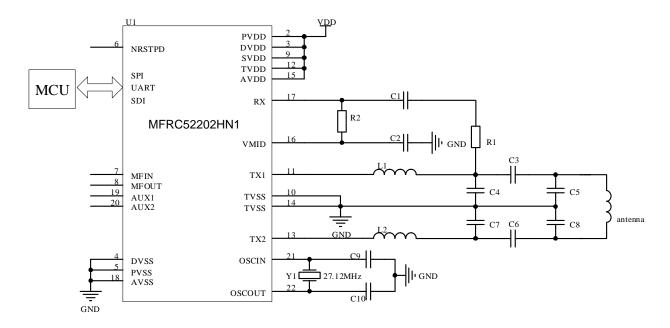

- Buffered output driver with minimal peripheral components connected to the antenna

- Supports ISO/IEC 14443 A

- Typical operating distance in Read/Write mode up to 50 mm depending on the antenna size and tuning

- Supports ISO/IEC 14443 A higher rate communication, up to 848 kBd

- Supported host interfaces

- -SPI up to 10 Mbit/s

- -I<sup>2</sup> C

- -RS232 Serial UART up to 1228.8 kBd, with voltage levels dependant on pin voltage supply

- buffer handles 64 byte send and receive

- Flexible interrupt modes

- Hard reset with low power function

- Power-down by software

- Programmable timer

- Internal oscillator for connection to 27.12 MHz quartz crystal

- 2.5 V to 3.6 V power supply

- CRC coprocessor

# Quick reference data

**Table 4-1 Limit parameter**

|                       |      | *   |      |  |  |  |

|-----------------------|------|-----|------|--|--|--|

| Condition             | Min  | Max | Unit |  |  |  |

| Supply voltage        |      |     |      |  |  |  |

| VDD                   | -0.5 | 4   | V    |  |  |  |

| Temperature           |      |     |      |  |  |  |

| Operating temperature | -40  | +85 | °C   |  |  |  |

#### **Table 4-2 Main parameter**

| Symbol    | Parameter      | Condition                   |     | Min | Тур | Max | Unit |

|-----------|----------------|-----------------------------|-----|-----|-----|-----|------|

| VDDA      | analog supply  | $VDD(PVDD) \le VDDA = VDDD$ | (1) | 2.5 | 3.3 | 4   | V    |

|           | voltage        | = VDD(TVDD);                |     |     |     |     |      |

| VDDD      | digital supply | VSSA = VSSD = VSS(PVSS) =   |     | 2.5 | 3.3 | 4   | V    |

|           | voltage        | VSS(TVSS) = 0 V             |     |     |     |     |      |

| VDD(TVDD) | TVDD supply    |                             |     | 2.5 | 3.3 | 4   | V    |

|           | voltage        |                             |     |     |     |     |      |

| VDD(PVDD) | PVDD supply    |                             | (1) | 2.5 | 3.3 | 4   | V    |

|           | voltage        |                             |     |     |     |     |      |

| VDD(SVDD) | SVDD supply    | VSSA = VSSD = VSS(PVSS) =   |     | 2.5 | 3.3 | 4   | V    |

|           | voltage        | VSS(TVSS) = 0 V             |     |     |     |     |      |

| Ipd       | power-down     | VDDA=VDDD = VDD(TVDD)       |     |     |     |     |      |

|           | current        | = VDD(PVDD) = 3.3 V         |     |     |     |     |      |

|           |                | hard power-down;            | (2) | -   | 1.2 | 1.5 | uA   |

|           |                | pin NRSTPD set LOW          |     |     |     |     |      |

|           |                | soft power-down;            | (2) | -   | 1.5 | 2.5 | uA   |

|           |                | RF level detector on        |     |     |     |     |      |

| IDDD      | digital supply | pin DVDD; VDDD = 3.3 V      |     | -   | 0.9 | 1.5 | uA   |

|           | voltage        |                             |     |     |     |     |      |

| IDDA      | analog supply  | pin AVDD; VDDA = 3.3 V,     |     | -   | 2.9 | 4   | mA   |

|           | voltage        | CommandReg register's       |     |     |     |     |      |

|           |                | RcvOff bit = 0              |     |     |     |     |      |

|           |                | pin AVDD; receiver          |     | -   | 0.8 | 1   | mA   |

|           |                | switched off; VDDA = 3.3    |     |     |     |     |      |

|           | V, CommandReg register's  RevOff bit = 1 |     |   |    |    |    |

|-----------|------------------------------------------|-----|---|----|----|----|

| IDD(TVDD) |                                          | (3) | - | 25 | 30 | mA |

<sup>(1)</sup> VDDA, VDDD and VDD(TVDD) must always be the same voltage.

- (2) Ipd is the total current for all supplies.

- (3)During typical circuit operation, the overall current is below 30 mA

**Table 4-3 Recommend value**

| Symbol    | Paran     | neter  | Condition               | Min | Тур | Max  | Unit |

|-----------|-----------|--------|-------------------------|-----|-----|------|------|

| VDDA      | Analog    | supply | VDD(PVDD) < VDDA =      | 2.5 | 3.3 | 4.0  | V    |

|           | voltage   |        | VDDD = VDD(TVDD);       |     |     |      |      |

| VDDD      | Digital   | supply | VSSA = VSSD = VSS(PVSS) | 2.5 | 3.3 | 4.0  | V    |

|           | voltage   |        | = VSS(TVSS) $=$ 0 V     |     |     |      |      |

| VDD(TVDD) | TVDD      | supply |                         | 2.5 | 3.3 | 4.0  | V    |

|           | voltage   |        |                         |     |     |      |      |

| VDD(PVDD) | PVDD      | supply |                         | 2.5 | 3.3 | 4.0  | V    |

|           | voltage   |        |                         |     |     |      |      |

| VDD(SVDD) | SVDD      | supply | VSSA = VSSD = VSS(PVSS) | 2.5 | 3.3 | 4.0  | V    |

|           | voltage   |        | = VSS(TVSS) $=$ 0V      |     |     |      |      |

|           | storage   |        | QFN32                   | -55 | -   | +125 | °C   |

|           | temperat  | ure    |                         |     |     |      |      |

|           | operating |        | QFN32                   | -40 | -   | +85  | °C   |

|           | temperat  | ure    |                         |     |     |      |      |

Note:Stresses beyond those Absolute Maximum Ratings may cause permanent damage to the device.

**Table 4-4 Version information**

| Chip code    | Description |

|--------------|-------------|

| MFRC52202HN1 | -           |

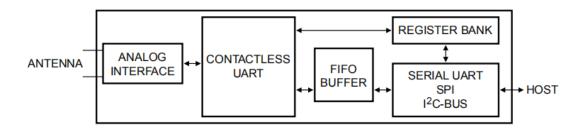

## **Block diagram**

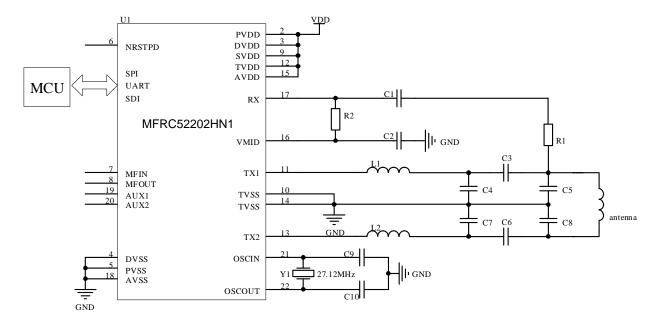

The analog interface handles the modulation and demodulation of the analog signals. The contactless UART manages the protocol requirements for the communication protocols in cooperation with the host. The FIFO buffer ensures fast and convenient data transfer to and from the host and the contactless UART.

Various host interfaces are implemented to meet different customer requirements.

Figure 5-1 Simplified block diagram

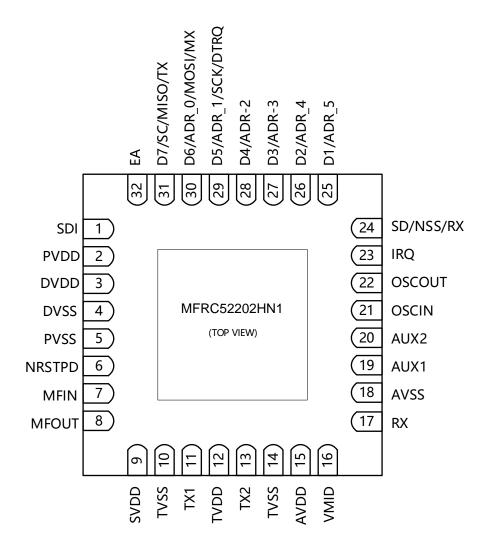

## **Pinning information**

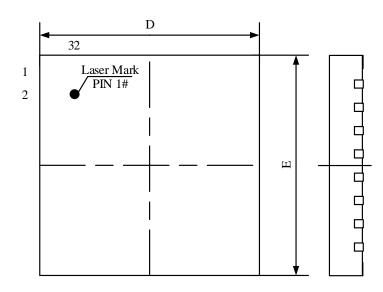

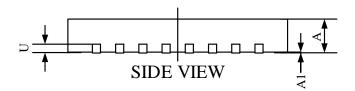

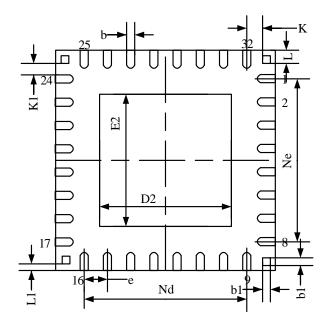

Figure 6-1 Pinning configuration (QFN32L)

**Table 6-1 Pinning description**

|     | Table 0-1 1 mining description |         |                                                                       |  |  |  |

|-----|--------------------------------|---------|-----------------------------------------------------------------------|--|--|--|

| Pin | Symbol                         | Type[1] | Description                                                           |  |  |  |

| 1   | SDI                            | I       | I <sup>2</sup> C bus input                                            |  |  |  |

| 2   | PVDD                           | P       | Pad power supply                                                      |  |  |  |

| 3   | DVDD                           | P       | Digital Power Supply                                                  |  |  |  |

| 4   | DVSS                           | P       | Digital Ground                                                        |  |  |  |

| 5   | PVSS                           | P       | Pad power supply ground                                               |  |  |  |

| 6   | NRSTPD                         | I       | Reset and Power Down input: When LOW, internal current sinks          |  |  |  |

|     |                                |         | are switched off, the oscillator is inhibited, and the input pads are |  |  |  |

|    |        | 1   |                                                                               |

|----|--------|-----|-------------------------------------------------------------------------------|

|    |        |     | disconnected from the outside world. With a positive edge on this             |

|    |        |     | pin the internal reset phase starts.                                          |

| 7  | MFIN   | I   | Test signal input                                                             |

| 8  | MFOUT  | О   | Test signal output                                                            |

| 9  | SVDD   | P   | Provides power to the MFIN/MFOUT                                              |

| 10 | TVSS   | P   | Transmitter Ground: supplies the output stage of TX1 and TX2                  |

| 11 | TX1    | О   | Transmitter 1: delivers the modulated 13.56 MHz energy carrier                |

| 12 | TVDD   | P   | Transmitter Power Supply: supplies the output stage of TX1 and TX2            |

| 13 | TX2    | 0   | Transmitter 2: delivers the modulated 13.56 MHz energy carrier                |

| 14 | TVSS   | P   | Transmitter Ground: supplies the output stage of TX1 and TX2                  |

| 15 | AVDD   | P   | Analog Power Supply                                                           |

| 16 | VMID   | P   | Internal Reference Voltage: This pin delivers the internal reference voltage. |

| 17 | RX     | I   | Receiver Input                                                                |

| 18 | AVSS   | P   | Analog Ground                                                                 |

| 19 | AUX1   | 0   | Auxiliary Outputs: These pins are used for testing.                           |

| 20 | AUX2   | 0   | Auxiliary Outputs: These pins are used for testing.                           |

| 21 | OSCIN  | I   | Crystal Oscillator Input: input to the inverting amplifier of the             |

|    |        |     | oscillator. This pin is also the input for an externally generated clock      |

|    |        |     | (fosc = 27.12 MHz).                                                           |

| 22 | OSCOUT | О   | Crystal Oscillator Output: Output of the inverting amplifier of the           |

|    |        |     | oscillator.                                                                   |

| 23 | IRQ    | О   | Interrupt Request: output to signal an interrupt event                        |

| 24 | SD     | I/O | I <sup>2</sup> C bus serial data input and output                             |

|    | NSS    | I   | SPI input                                                                     |

|    | RX     | I   | UART address input                                                            |

| 25 | D1     | I/O | Test port                                                                     |

|    | ADR_5  | I/O | I <sup>2</sup> C bus address5 input                                           |

| 26 | D2    | I/O | Test port                                                                  |

|----|-------|-----|----------------------------------------------------------------------------|

|    | ADR_4 | I   | I <sup>2</sup> C bus address4 input                                        |

| 27 | D3    | I/O | Test port                                                                  |

|    | ADR_3 | I   | I <sup>2</sup> C bus address3 input                                        |

| 28 | D4    | I/O | Test port                                                                  |

|    | ADR_2 | I   | I <sup>2</sup> C bus address2 input                                        |

| 29 | D5    | I/O | Test port                                                                  |

|    | ADR_1 | I   | I <sup>2</sup> C bus address1 input                                        |

|    | SCK   | I   | SPI seria clock input l                                                    |

|    | DTRQ  | О   | UART makes a request to controller                                         |

| 30 | D6    | I/O | Test port                                                                  |

|    | ADR_0 | I   | I <sup>2</sup> C bus address0 input                                        |

|    | MOSI  | I/O | SPI Master Out Slave In                                                    |

|    | MX    | О   | UART for the output of the controller                                      |

| 31 | D7    | I/O | Test port                                                                  |

|    | SCL   | I/O | I <sup>2</sup> C bus clock input/output                                    |

|    | MISO  | I/O | SPI Master In Slave Out                                                    |

|    | TX    | О   | UART Data output to controller                                             |

| 32 | EA    | I   | External address input: can be used to define the I <sup>2</sup> C address |

| L  | 1     |     |                                                                            |

<sup>1)</sup> Pin types: I = Input, O = Output, I/O = Input/Output, P = Power and G = Ground

<sup>2)</sup> DVSS is the connection of heatsink pad on package underside.

## **Functional description**

The 52202 transmission module supports the Read/Write mode for ISO/IEC 14443 A using various transfer speeds and modulation protocols.

Table 7-1 Communication overview for ISO/IEC 14443 A reader/writer

| Table/-1 Communication overview for ISO/IEC 14445 A reader/writer |              |                 |                 |                 |                 |  |  |  |

|-------------------------------------------------------------------|--------------|-----------------|-----------------|-----------------|-----------------|--|--|--|

| Communicati                                                       | Signal type  | Transfer speed  |                 |                 |                 |  |  |  |

| on direction                                                      |              | 106kBd          | 212kBd          | 424kBd          | 848kBd          |  |  |  |

| Reader to                                                         | reader side  | 100%ASK         | 100%ASK         | 100%ASK         | 100%ASK         |  |  |  |

| card (send                                                        | modulation   |                 |                 |                 |                 |  |  |  |

| data from the                                                     | bit encoding | modified Miller | modified Miller | modified Miller | modified Miller |  |  |  |

| 52202 to a                                                        |              | encoding        | encoding        | encoding        | encoding        |  |  |  |

| card)                                                             | bit length   | (128/13.56) µs  | (64/13.56) μs   | (32/13.56) μs   | (16/13.56) μs   |  |  |  |

| Card to                                                           | card side    | subcarrier load | subcarrier load | subcarrier load | subcarrier load |  |  |  |

| reader                                                            | modulation   | modulation      | modulation      | modulation      | modulation      |  |  |  |

| (52202                                                            | subcarrier   | 13.56MHz/16     | 13.56MHz/16     | 13.56MHz/16     | 13.56MHz/16     |  |  |  |

| receives data                                                     | frequency    |                 |                 |                 |                 |  |  |  |

| from a card)                                                      | bit encoding | Manchester      | BPSK            | BPSK            | BPSK            |  |  |  |

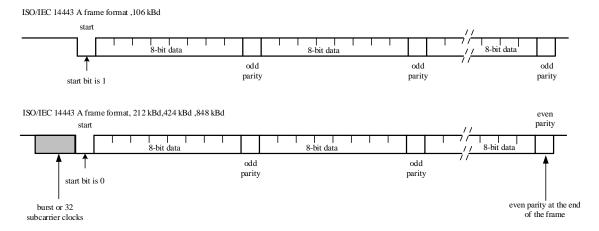

The 52202's contactless UART and dedicated external host must manage the complete ISO/IEC 14443 A protocol. Figure 7-1 shows the data coding and framing according to ISO/IEC 14443 A.

Figure 7-1 Data coding and framing according to ISO/IEC 14443 A

The internal CRC coprocessor calculates the CRC value based on ISO/IEC 14443 A part 3 and handles parity generation internally based on the transmission rates.

Automatic parity generation can be switched off using the ManualRCVReg register's ParityDisable bit.

## **Digital interfaces**

#### Automatic microcontroller interface detection

The 52202 supports direct interfacing of hosts using SPI, I<sup>2</sup> C or serial UART interfaces. The 52022 resets its interface and checks the current host interface type automatically after performing a power-on or hard reset. The 52202 identifies the host interface by sensing the logic levels on the control pins after the reset phase. This is done using a combination of fixed pin connections. Table 7-1 shows the different connection configurations.

Table 7-2 Connection protocol for detecting different interface types

| Pin | Interface types |              |                        |  |  |  |

|-----|-----------------|--------------|------------------------|--|--|--|

|     | UART (input)    | SPI (output) | I <sup>2</sup> C (I/O) |  |  |  |

| SD  | RX              | NSS          | SD                     |  |  |  |

| SDI | 0               | 0            | 1                      |  |  |  |

| EA  | 0               | 1            | EA                     |  |  |  |

| D7  | TX              | MISO         | SC                     |  |  |  |

| D6  | MX              | MOSI         | ADR_0                  |  |  |  |

| D5  | DTRQ            | SCK          | ADR_1                  |  |  |  |

| D4  | -               | -            | ADR_2                  |  |  |  |

| D3  | -               | -            | ADR_3                  |  |  |  |

| D2  | -               | -            | ADR_4                  |  |  |  |

| D1  | -               | -            | ADR_5                  |  |  |  |

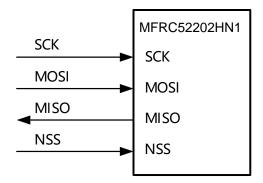

#### **SPI**

A serial peripheral interface (SPI compatible) is supported to enable high-speed communication to the host. The interface can handle data speeds up to 10 Mbit/s. When communicating with a host, the 52202 acts as a slave, receiving data from the external host for register settings, sending and receiving data relevant for RF interface

communication.

An interface compatible with SPI enables high-speed serial communication between the 52202 and a microcontroller. The implemented interface is in accordance with the SPI standard.

Figure 7-2 SPI connection to host

The 52022 acts as a slave during SPI communication. The SPI clock signal SCK must be generated by the master. Data communication from the master to the slave uses the MOSI line. The MISO line is used to send data from the 52202 to the master.

Data bytes on both MOSI and MISO lines are sent with the MSB first. Data on both MOSI and MISO lines must be stable on the rising edge of the clock and can be changed on the falling edge. Data is provided by the 52202 on the falling clock edge and is stable during the rising clock edge.

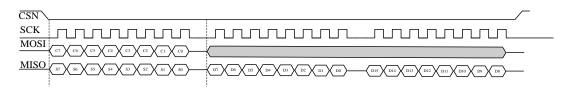

#### SPI read data

Reading data using SPI requires the byte order. It is possible to read out up to n-data bytes. The first byte sent defines both the mode and the address.

Table 7-3 MOSI and MISO byte order

| Line | Byte0     | Byte1     | Byte2     | То | Byte n    | Byte n+1 |

|------|-----------|-----------|-----------|----|-----------|----------|

| MOSI | address 0 | address 1 | address 2 |    | address n | 00       |

| MISO | X         | data 0    | data 1    |    | data n-1  | data n   |

NOTE: The MSB must be sent first.

Figure 7-3 SPI read timing

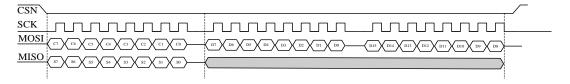

#### SPI write data

To write data to the 52202 using SPI requires the byte order shown in Table 7-4. It is possible to write up to n data bytes by only sending one address byte. The first send byte defines both the mode and the address byte.

**Table7-4** MOSI and MISO Byte order

| Line | Byte 0    | Byte 1 | Byte 2 | То  | Byte n   | Byte n+1 |

|------|-----------|--------|--------|-----|----------|----------|

| MOSI | address 0 | data 0 | data 1 |     | data n-1 | data n   |

| MISO | X         | X      | X      | ••• | X        | X        |

NOTE: The MSB must be sent first.

Figure 7-4 SPI write timing

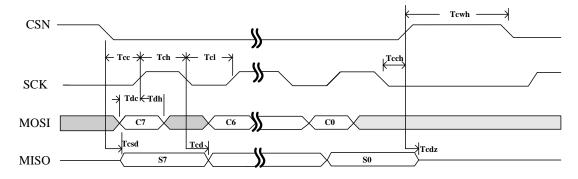

#### **SPI** timing

SPI typical timing is shown in Figure 7-5 and SPI typical timing parameter is shown in Table 7-5.

Figure 7-5 SPI typical timing

Table 7-5 SPI typical timing parameter

| Symbol | Parameters           | Min | Max | Units |

|--------|----------------------|-----|-----|-------|

| Tdc    | Data to SCK Setup    | 2   |     | ns    |

| Tdh    | SCK to Data Hold     | 2   |     | ns    |

| Tcsd   | CSN to Data Valid    |     | 42  | ns    |

| Tcd    | SCK to Data Valid    |     | 58  | ns    |

| Tcl    | SCK Low Time         | 40  |     | ns    |

| Tch    | SCK High Time        | 40  |     | ns    |

| Fsck   | SCK Frequency        | 0   | 10  | MHz   |

| Tr,Tf  | SCK Rise and Fall    |     | 100 | ns    |

| Тсс    | CSN to SCK Setup     | 2   |     | ns    |

| Tcch   | SCK to CSN Hold      | 2   |     | ns    |

| Tcwh   | CSN Inactive time    | 50  |     | ns    |

| Tcdz   | CSN to Output High Z |     | 42  | ns    |

### SPI address byte

The address byte has to meet the following format. The MSB of the first byte defines the mode used. To read data from the 52202 the MSB is set to logic 1. To write data to the 52202 the MSB must be set to logic 0. Bits 6 to 1 define the address and the LSB is set to logic 0.

Table 7-6 Address byte format

| 7 (MSB)        | 6: 1    | 0 (LSB) |

|----------------|---------|---------|

| 1=read/0=write | Address | 0       |

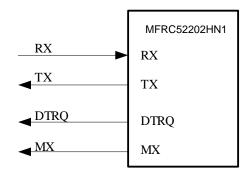

#### **UART** interface

#### Connection to a host

Figure 7-6 UART connection to microcontrollers

NOTE: Signals DTRQ and MX can be disabled by clearing TestPinEnReg register's RS232LineEn bit.

#### **Selectable UART transfer speeds**

The internal UART interface is compatible with an RS232 serial interface.

The default transfer speed is 9.6 kBd. To change the transfer speed, the host controller must write a value for the new transfer speed to the SerialSpeedReg register. Bits BR\_T0[2:0] and BR\_T1[4:0] define the factors for setting the transfer speed in the SerialSpeedReg register. Different transfer speeds and relevant registers setting are shown in Table 7-7.

**Table7-7** Selectable UART transfer speeds

| Transfer speed | SeriaSpeedReg value | Transfer speed accuracy |       |

|----------------|---------------------|-------------------------|-------|

| (kBd)          | Decimal             | Hexadecimal             | (%)   |

| 7.2            | 250                 | FAh                     | -0.25 |

| 8.6            | 235                 | EBh                     | 0.32  |

| 14.4           | 218                 | DAh                     | -0.25 |

| 19.2           | 203                 | CBh                     | 0.32  |

| 171 | ABh               | 0.32                                              |

|-----|-------------------|---------------------------------------------------|

| 154 | 9Ah               | -0.25                                             |

| 122 | 7Ah               | -0.25                                             |

| 116 | 74h               | -0.06                                             |

| 90  | 5Ah               | -0.25                                             |

| 58  |                   | -0.25                                             |

|     |                   | 1.45                                              |

|     |                   | 0.32                                              |

|     | 154<br>122<br>116 | 154 9Ah  122 7Ah  116 74h  90 5Ah  58 3Ah  28 1Ch |

The selectable transfer speeds shown in table above are calculated according to the following equations:

transfer speed =

$$(27.12 \times 10^6) / (BR_T0 + 1)$$

When BR\_T0[2:0] > 0:

transfer speed =

$$(27.12 \times 10^6 \times 2^{(BR\_T0-1)}) / (BR\_T1 + 33)$$

NOTE: Transfer speed more than 1228.8kBd is not supported.

## **UART** framing

Table 7-8 UART framing

|       |        | <u> </u> |

|-------|--------|----------|

| Bit   | Length | Value    |

| Start | 1bit   | 0        |

| Data  | 8bits  | Data     |

| Stop  | 1bit   | 1        |

NOTE: The LSB for data and address bytes must be sent first. No parity bit is used during transmission.

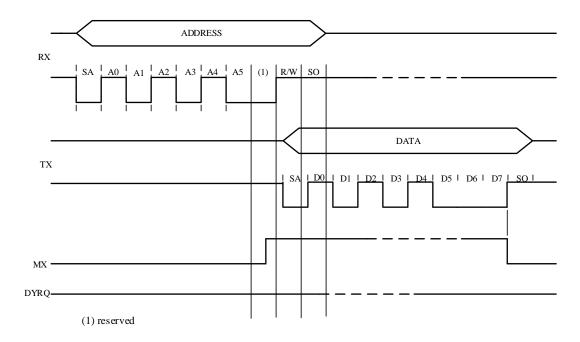

Figure 7-7 UART read timing

Read data: To read data to the 52202 using the UART interface, the structure shown in Table 7-9 must be used. The first byte sent defines both the mode and the address.

Table7-9 Read data byte order

| Pin | Byte0   | Byte1  |

|-----|---------|--------|

| RX  | address | -      |

| TX  | -       | data 0 |

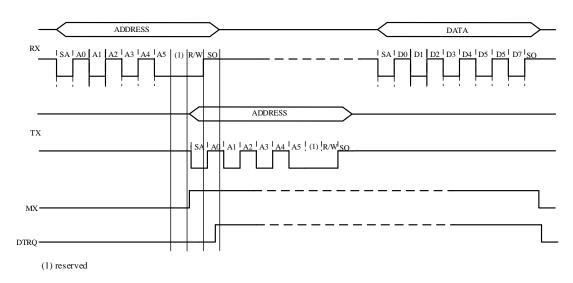

Write data: To write data to the 52202 using the UART interface, the structure shown in Table 7-10 must be used. The first byte sent defines both the mode and the address.

Table7-10 Write data byte order

| Tubie? To Write duta byte order |          |          |  |  |  |  |

|---------------------------------|----------|----------|--|--|--|--|

| Pin                             | Byte0    | Byte1    |  |  |  |  |

| RX                              | address0 | data 0   |  |  |  |  |

| TX                              | -        | address0 |  |  |  |  |

Figure 7-8 UART write timing

I<sup>2</sup>C

I<sup>2</sup> C is compatible

#### **FIFO**

An 64x8 bit FIFO buffer is used in the 52202 It buffers the input and output data stream between the host and the 52202's internal state machine. This makes it possible to manage data streams up to 64 bytes long without the need to take timing constraints into account.

The FIFO buffer input and output data bus is connected to the FIFODataReg register. Writing to this register stores one byte in the FIFO buffer and increments the internal FIFO buffer write pointer. Reading from this register shows the FIFO buffer contents stored in the FIFO buffer read pointer and decrements the FIFO buffer read pointer. The distance between the write and read pointer can be obtained by reading the FIFOLevelReg register.

The 52202 can generate two interrupts signal to know the condition of the FIFO buffer in time: HiAlertIRq 和 LoAlertIRq.

If the maximum number of WaterLevel[5:0] bits (as set in the WaterLevelReg register) or less are stored in the FIFO buffer, the HiAlert bit is set to logic 1. If it

enables interrupt, the HiAlertIRq will be generated.

$$HiAlert = (64 - FIFOLength) \leq WaterLevel$$

If the number of WaterLevel[5:0] bits (as set in the WaterLevelReg register) or less are stored in the FIFO buffer, the LoAlert bit is set to logic 1.If it enables interrupt, the LoAlertIRq will be generated.

$$LoAlert = FIFOLength \leq WaterLevel$$

#### **Interrupt request system**

The 52202 indicates certain events by setting the Status 1 Reg register's IRq bit and, if activated, by pin IRQ.

**Table7-11 Interrupt sources**

| Table 7-11 Interrupt sources |                  |                                                  |  |  |  |

|------------------------------|------------------|--------------------------------------------------|--|--|--|

| Interrupt flag               | Interrupt source | Trigger action                                   |  |  |  |

| IRq                          | timer unit       | the timer counts from 1 to 0                     |  |  |  |

| TxIRq                        | transmitter      | a transmitted data stream ends                   |  |  |  |

| CRCIRq                       | CRC coprocessor  | all data from the FIFO buffer has been processed |  |  |  |

| RxIRq                        | receiver         | a received data stream ends                      |  |  |  |

| IdleIRq                      | ComIRqReg        | command execution finishes                       |  |  |  |

| HiAlertIRq                   | FIFO             | the FIFO buffer is almost full                   |  |  |  |

| LoAlertIRq                   | FIFO             | the FIFO buffer is almost empty                  |  |  |  |

| ErrIRq                       | Contactless UART | an error is detected                             |  |  |  |

#### **Power reduction modes**

### Hard power-down

Hard power-down mode is enabled when pin NRSTPD is LOW. After exiting hard power-down mode, all registers will be reset.

#### Soft power-down mode

Soft Power-down mode is entered immediately after the CommandReg register's

PowerDown bit is set to logic 1. During soft power-down, all register values, the FIFO buffer content and the configuration keep their current contents.

## Transmitter power -down mode

The Transmitter Power-down mode switches off the internal antenna drivers thereby, turning off the RF field. Transmitter power-down mode is entered by setting either the TxControlReg register's Tx1RFEn bit or Tx2RFEn bit to logic 0.

## **Command set**

### **General description**

The 52202 operation is determined by a state machine capable of performing a set of commands. A command is executed by writing a command code to the CommandReg register.

#### General characteristics

- 1) Except for the Transmive command, commands that require a data bit stream (or data byte stream) as input immediately process any data in the FIFO buffer. When the Transmive command is executed, the sending of data is initiated by the StartSend bit of the BitFramingReg register.

- 2) Commands that require a certain number of parameters are only processed when the correct number of parameters are received from the FIFO buffer.

- 3) At the beginning of the command, the FIFO buffer will not be automatically cleared. It supports writing command parameters and data bytes to the FIFO buffer, and then starting the command.

- 4) The host writes a new command code to the CommandReg register to interrupt the currently executing command, such as the Idle command.

#### **Command overview**

Table8-1 command overview

| Command           | Command code | Description                                           |

|-------------------|--------------|-------------------------------------------------------|

| Idle              | 0000         | no action, cancels current command execution          |

| Mem               | 0001         | Store 25 bytes in FIFO buffer                         |

| Generate RandomID | 0010         | IDgenerates a 10-byte random ID number                |

| CalcCRC           | 0011         | activates the CRC coprocessor or performs a self test |

| Transmit          | 0100         | transmits data from the FIFO buffer                   |

| NoCmdChange | 0111 | no command change, can be used to modify the CommandReg register bits without affecting the command, for example, the PowerDown bit |

|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| Receive     | 1000 | activates the receiver circuits                                                                                                     |

| Transceive  | 1100 | transmits data from FIFO buffer to antenna and automatically activates the receiver after transmission                              |

| SoftReset   | 1111 | resets the MFRC52202HN1                                                                                                             |

# **Register mapping**

Table 9-1 52202 register mapping

| Address | Mnemonic E         | Bit Type Reset Description |                       |                                                         |                                                            |                          |

|---------|--------------------|----------------------------|-----------------------|---------------------------------------------------------|------------------------------------------------------------|--------------------------|

| (Hex)   | Wifemonie          | Dit                        | Турс                  | Value                                                   | Description                                                |                          |

| 00h     | reserved           |                            |                       | 00h                                                     | reserved for future use                                    |                          |

| 01h     | CommandReg         |                            |                       | 20h                                                     | starts and stops command execution                         |                          |

|         | reserved           | 7:6                        | -                     |                                                         | write 0 by default                                         |                          |

|         | RevOff             | 5                          | R/W                   |                                                         | 1: analog part of the receiver is switched off             |                          |

|         |                    |                            |                       |                                                         | 1: Soft Power-down mode entered                            |                          |

|         |                    |                            |                       |                                                         | 0: 52202 starts the wake up procedure during which this    |                          |

|         |                    |                            |                       |                                                         | bit is read as a logic 1; it is read as a logic 0 when the |                          |

|         | PowerDown          | 4                          | D                     |                                                         | 52202 is ready.                                            |                          |

|         |                    |                            |                       |                                                         | NOTE: The PowerDown bit cannot be set when the             |                          |

|         |                    |                            |                       |                                                         | SoftReset command is activated                             |                          |

|         |                    |                            |                       |                                                         | activates a command based on the Command value;            |                          |

|         | Command[3:0] 3:0 1 | D                          |                       | reading this register shows which command is executed   |                                                            |                          |

| 02h     | CommIEnReg         |                            |                       | 80h                                                     | enable and disable interrupt request control bits          |                          |

|         |                    |                            |                       |                                                         | 1: signal on pin IRQ is inverted with respect to the       |                          |

|         |                    |                            |                       |                                                         | Status1Reg register's IRq bit                              |                          |

|         |                    |                            |                       |                                                         | 0: signal on pin IRQ is equal to the IRq bit; in           |                          |

|         | IRqInv             | 7                          | R/W                   |                                                         | combination with the DivIEnReg register's                  |                          |

|         |                    |                            |                       |                                                         | IRqPushPull bit, the default value of logic 1 ensures      |                          |

|         |                    |                            |                       |                                                         | that the output level on pin IRQ is 3-state                |                          |

|         |                    |                            |                       |                                                         | 1: allows the transmitter interrupt request (TxIRq bit) to |                          |

|         | TxIEn              | 6                          | R/W                   |                                                         | be propagated to pin IRQ                                   |                          |

|         |                    |                            |                       | 1: allows the receiver interrupt request (RxIRq bit) to |                                                            |                          |

|         | RxIEn              | 5                          | 5 R/W                 | R/W                                                     |                                                            | be propagated to pin IRQ |

|         |                    |                            |                       |                                                         | 1: allows the idle interrupt request (IdleIRq bit) to be   |                          |

|         | IdleEn 4 R/W       | R/W                        | propagated to pin IRQ |                                                         |                                                            |                          |

|     |             |     |          | •   |                                                                                      |

|-----|-------------|-----|----------|-----|--------------------------------------------------------------------------------------|

|     | HiAlertIEn  | 3   | R/W      |     | allows the high alert interrupt request (HiAlertIRq bit) to be propagated to pin IRQ |

|     |             |     |          |     |                                                                                      |

|     | LoAlertIEn  | 2   | 2 R/W    |     | 1: allows the low alert interrupt request (LoAlertIRq                                |

|     | Eornomean   |     | 10 11    |     | bit) to be propagated to pin IRQ                                                     |

|     |             |     |          |     | 1: allows the error interrupt request (ErrIRq bit) to be                             |

|     | ErrIEn      | 1   | R/W      |     | propagated to pin IRQ                                                                |

|     |             |     |          |     | 1: allows the timer interrupt request (TimerIRq bit) to                              |

|     | TimerIEn    | 0   | R/W      |     | be propagated to pin IRQ                                                             |

| 03h | DivIEnReg   |     |          | 00h | enable and disable interrupt request control bits                                    |

|     |             |     |          |     | 1: pin IRQ is a standard CMOS output pin                                             |

|     | IRQPushPull | 7   | R/W      |     | 0: pin IRQ is an open-drain output pin                                               |

|     |             |     |          |     |                                                                                      |

|     | reserved    | 6:5 | -        |     | write 0 by default                                                                   |

|     | SiginActIEn | 4   | R/W      |     | 1: allows MFIN interrupt request to be propagated to                                 |

|     | 6           |     |          |     | pin IRQ                                                                              |

|     | reserved    | 3   | -        |     | reserved for future use                                                              |

|     |             |     |          |     | 1: allows the CRC interrupt request, indicated by the                                |

|     | CRCIEn      | 2   | R/W      |     | DivIrqReg register's CRCIRq bit, to be propagated to                                 |

|     |             |     |          |     | pin IRQ                                                                              |

|     | reserved    | 1:0 | -        |     | reserved for future use                                                              |

| 04h | CommIRqReg  |     |          | 14h | interrupt request bits                                                               |

|     |             |     |          |     | 1: indicates that the marked bits in the ComIrqReg                                   |

|     |             |     |          |     | register are set                                                                     |

|     | Set1        | 7   | W        |     | 0: indicates that the marked bits in the ComIrqReg                                   |

|     |             |     |          |     |                                                                                      |

|     |             |     |          |     | register are cleared                                                                 |

|     | TxIRq       | 6   | D        |     | 1: set immediately after the last bit of the transmitted                             |

|     | TAIKQ       |     | <i>υ</i> |     | data was sent out                                                                    |

|     |             |     |          |     | 1: receiver has detected the end of a valid data stream if                           |

|     | RxIRq       | 5   | D        |     | the RxModeReg register's RxNoErr bit is set to logic 1,                              |

|     |             |     |          |     | the RxIRq bit is only set to logic 1 when data bytes are                             |

|     | 1           | 1   |          | 1   | <u>i</u>                                                                             |

|     |             |     |   |     | available in the FIFO                                                                                                                                                                                                                                                                                                                 |

|-----|-------------|-----|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | IdleIRq     | 4   | D |     | 1: if a command terminates, for example, when the CommandReg changes its value from any command to the Idle command; if an unknown command is started, the CommandReg register Command[3:0] value changes to the idle state and the IdleIRq bit is set; if the microcontroller starting the Idle command does not set the IdleIRq bit |

|     | HiAlertIRq  | 3   | D |     | 1: the Status1Reg register's HiAlert bit is set the HiAlertIRq bit stores this event and can only be reset as indicated by the Set1 bit in this register                                                                                                                                                                              |

|     | LoAlertIRq  | 2   | D |     | 1: Status1Reg register's LoAlert bit is set the  LoAlertIRq bit stores this event and can only be reset as  indicated by the Set1 bit in this register                                                                                                                                                                                |

|     | ErrIRq      | 1   | D |     | 1: any error bit in the ErrorReg register is set                                                                                                                                                                                                                                                                                      |

|     | TimerIRq    | 0   | D |     | 1: the timer decrements the timer value in register  TCounterValReg to zero                                                                                                                                                                                                                                                           |

| 05h | DivIRqReg   |     |   | x0h | interrupt request bits                                                                                                                                                                                                                                                                                                                |

|     | Set2        | 7   | W |     | indicates that the marked bits in the DivIrqReg     register are set     indicates that the marked bits in the DivIrqReg     register are cleared                                                                                                                                                                                     |

|     | reserved    | 6:5 | - |     | reserved for future use                                                                                                                                                                                                                                                                                                               |

|     | SiginActIRq | 4   | D |     | 1: MFIN active this interrupt bit will be set to logic 1when detecting a rising edge or a falling edge                                                                                                                                                                                                                                |

|     | reserved    | 3   | - |     | reserved for future use                                                                                                                                                                                                                                                                                                               |

|     | CRCIRq      | 2   | D |     | 1: the CalcCRC command is active and all data is                                                                                                                                                                                                                                                                                      |

|       |               |     |                                                     |     | 1                                                        |

|-------|---------------|-----|-----------------------------------------------------|-----|----------------------------------------------------------|

|       |               |     |                                                     |     | processed                                                |

|       | reserved      | 1:0 | -                                                   |     | reserved for future use                                  |

| 0.61- | E             |     |                                                     | 00h | error bits showing the error status of the last command  |

| 06h   | ErrorReg      |     |                                                     | oon | executed                                                 |

|       |               |     |                                                     |     | 1: data is written into the FIFO buffer by the host if   |

|       |               |     |                                                     |     | data is written into the FIFO buffer by the host during  |

|       | WrErr         | 7   | R                                                   |     | the time between sending the last bit on the RF          |

|       |               |     |                                                     |     | interface and receiving the last bit on the RF interface |

|       |               |     |                                                     |     | 1: internal temperature sensor detects overheating, in   |

|       | TempErr       | 6   | R                                                   |     | which case the antenna drivers are automatically         |

|       |               |     |                                                     |     | switched off                                             |

|       | reserved      | 5   | -                                                   |     | reserved for future use                                  |

|       |               |     |                                                     |     | 1: the host or a 52202's internal state machine (e.g.    |

|       | BufferOvfl    | 4   | R                                                   |     | receiver) tries to write data to the FIFO buffer even    |

|       |               |     |                                                     |     | though it is already full                                |

|       |               |     |                                                     |     | 1: a bit-collision is detected                           |

|       |               |     |                                                     |     | cleared automatically at receiver start-up phase only    |

|       | CollErr       | 3   | R                                                   |     | valid during the bitwise anticollision at 106 kBd always |

|       |               |     |                                                     |     | set to logic 0 during communication protocols at 212     |

|       |               |     |                                                     |     | kBd, 424 kBd and 848 kBd                                 |

|       |               |     |                                                     |     | 1:the RxModeReg register's RxCRCEn bit is set and        |

|       | CRCErr        | 2   | R                                                   |     | the CRC calculation fails automatically cleared to logic |

|       |               |     |                                                     |     | 0 during receiver start-up phase                         |

|       |               |     |                                                     |     | 1: parity check failed                                   |

|       |               |     |                                                     |     | automatically cleared during receiver start-up phase     |

|       | ParityErr 1 R |     | only valid for ISO/IEC 14443 A communication at 106 |     |                                                          |

|       |               |     |                                                     |     | kBd                                                      |

|       |               |     |                                                     |     | 1: SOF is incorrect                                      |

|       | ProtocolErr   | 0   | R                                                   |     | automatically cleared during receiver start-up phase bit |

|       | i             | 1   | 1                                                   |     |                                                          |

|      |            |   |   |      | is only valid for 106 kBd                                    |

|------|------------|---|---|------|--------------------------------------------------------------|

| 07h  | Status1Reg |   |   | 21h  | communication status bits                                    |

| 0/11 | -          | 7 |   | 2111 | reserved for future use                                      |

|      | reserved   | 7 | - |      |                                                              |

|      |            |   |   |      | 1: the CRC result is zero                                    |

|      |            |   |   |      | the CRCOk bit is undefined for data transmission and         |

|      |            |   |   |      | reception: use the ErrorReg register's CRCErr bit            |

|      | CRCOk      | 6 | R |      | indicates the status of the CRC coprocessor, during          |

|      |            |   |   |      | calculation the value changes to logic 0, when the           |

|      |            |   |   |      | calculation is done correctly the value changes to logic     |

|      |            |   |   |      | 1                                                            |

|      |            |   |   |      | 1: the CRC calculation has finished; only valid for the      |

|      | CRCReady   | 5 | R |      | CRC coprocessor calculation using the CalcCRC                |

|      | ·          |   |   |      | command                                                      |

|      |            |   |   |      | indicates if any interrupt source requests attention with    |

|      | IRq        | 4 | R |      | respect to the setting of the interrupt enable bits: see the |

|      |            |   |   |      | ComIEnReg and DivIEnReg registers                            |

|      |            |   |   |      | 1: MFRC523's timer unit is running, i.e. the timer will      |

|      |            |   |   |      | decrement the TCounterValReg register with the next          |

|      |            |   |   |      | timer clock                                                  |

|      | TRunning   | 3 | R |      | NOTE: in gated mode, the TRunning bit is set to logic        |

|      |            |   |   |      | 1 when the timer is enabled by TModeReg register's           |

|      |            |   |   |      | TGated[1:0] bits; this bit is not influenced by the gated    |

|      |            |   |   |      | signal                                                       |

|      | reserved   | 2 | _ |      | reserved for future use                                      |

|      |            |   |   |      | 1: the alert level for the number of bytes in the FIFO       |

|      |            |   |   |      | buffer (FIFO Length[6:0]) is:                                |

|      | TT: A1- 4  | 1 | D |      | HiAlert = (64-FIFOLength) \( \subseteq \text{WaterLevel} \)  |

|      | HiAlert    | 1 | R |      |                                                              |

|      |            |   |   |      | Example:                                                     |

|      |            |   |   |      | FIFO Length = 60, WaterLevel = 4 -> HiAlert = 1              |

|     |                    | 1   |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|--------------------|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                    |     |     |     | FIFO Length = 59, WaterLevel = 4 -> HiAlert = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 08h | LoAlert Status2Reg | 0   | R   | 00h | 1: the alert level for number of bytes in the FIFO  buffer (FIFO Length[6:0]) is:  LoAlert = FIFOLength≤WaterLevel  Example:  FIFO Length = 4, WaterLevel = 4 -> LoAlert = 1  FIFO Length = 5, WaterLevel = 4 -> LoAlert = 0  receiver and transmitter status bits                                                                                                                                                                                                                                                                                  |

| Oon | Statusziceg        |     |     | OON |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | TempSensClear      | 7   | R/W |     | 1: clears the temperature error if the temperature is below the alarm limit of 125 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | reserved           | 6:3 | -   |     | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | ModemState[2:0]    | 2:0 | R   |     | shows the state of the transmitter and receiver state machines:  000: idle  001: wait for the BitFramingReg register's StartSend bit  010: TxWait: wait until RF field is present if the  TModeReg register's TxWaitRF bit is set to logic 1.  The minimum time for TxWait is defined by the  TxWaitReg register  011: transmitting  100: RxWait: wait until RF field is present if the  TModeReg register's TxWaitRF bit is set to logic 1.  The minimum time for RxWait is defined by the  RxWaitReg register  101: wait for data  110: receiving |

| 09h | FIFODataReg        |     |     | xxh | input and output of 64 byte FIFO buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | FIFOData[7:0]      | 7:0 | D   |     | data input and output port for the internal 64-byte FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                 |     |     |     | buffer. FIFO buffer acts as parallel in/parallel out       |

|-----|-----------------|-----|-----|-----|------------------------------------------------------------|

|     |                 |     |     |     |                                                            |

|     |                 |     |     |     | converter for all serial data stream inputs and outputs    |

| 0Ah | FIFOLevelReg    |     |     | 00h | number of bytes stored in the FIFO buffer                  |

|     |                 |     |     |     | 1: immediately clears the internal FIFO buffer's read      |

|     | FlushBuffer     | 7   | W   |     | and write pointer and ErrorReg register's BufferOvfl       |

|     |                 |     |     |     | bit. Reading this bit always returns 0                     |

|     |                 |     |     |     | indicates the number of bytes stored in the FIFO buffer.   |

|     | FIFOLevel[6:0]  | 6:0 | R   |     | Writing to the FIFODataReg register increments and         |

|     |                 |     |     |     | reading decrements the FIFOLevel value                     |

| 0Bh | WaterLevelReg   |     |     | 08h | level for FIFO underflow and overflow warning              |

|     | reserved        | 7:6 | -   |     | reserved for future use                                    |

|     |                 |     |     |     | defines a warning level to indicate a FIFO buffer          |

|     |                 |     |     |     | overflow or underflow:                                     |

|     |                 |     |     |     | Status1Reg register's HiAlert bit is set to logic 1 if the |

|     |                 |     |     |     | remaining number of bytes in the FIFO buffer space is      |

|     | WaterLevel[5:0] | 6:0 | R/W |     | equal to, or less than the defined number of               |

|     |                 |     |     |     | WaterLevel[5:0] bits                                       |

|     |                 |     |     |     | Status1Reg register's LoAlert bit is set to logic 1 if     |

|     |                 |     |     |     | equal to, or less than the WaterLevel[5:0] bits in the     |

|     |                 |     |     |     | FIFO buffer                                                |

| 0Ch | ControlReg      |     |     | 10h | miscellaneous control registers                            |

|     |                 |     |     |     | 1: timer stops immediately.                                |

|     | TStopNow        | 7   | W   |     | reading this bit always returns it to 0                    |

|     |                 |     |     |     | 1: timer starts immediately.                               |

|     | TStartNow       | 6   | W   |     | reading this bit always returns it to 0                    |

|     | reserved        | 5:3 | -   |     | reserved for future use                                    |

|     |                 |     |     |     | indicates the number of valid bits in the last received    |

|     | RxLastBits[2:0] | 2:0 | R   |     | byte. If this value is zero, the whole byte is valid       |

| 0Dh | BitFramingReg   |     |     | 00h | adjustments for bit-oriented frames                        |

|     |                 | 1   |     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|-----------------|-----|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | StartSend       | 7   | W   |     | starts the transmission of data only valid in     combination with the Transceive command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | RxAlign[2:0]    | 6:4 | R/W |     | used for reception of bit-oriented frames: defines the bit position for the first bit received to be stored in the FIFO buffer example:  0: LSB of the received bit is stored at bit position 0, the second received bit is stored at bit position 1  1: LSB of the received bit is stored at bit position 1, the second received bit is stored at bit position 2  7: LSB of the received bit is stored at bit position 7, the second received bit is stored at bit position 7, the second received bit is stored in the next byte that follows at bit position 0 these bits are only to be used for bitwise anticollision at |

|     |                 |     |     |     | 106 kBd, for all other modes they are set to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | reserved        | 3   | -   |     | reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | TxLastBits[2:0] | 2:0 | R/W |     | used for transmission of bit oriented frames: defines the number of bits of the last byte that will be transmitted.  000b indicates that all bits of the last byte will be transmitted                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0Eh | CollReg         |     |     | xxh | bit position of the first bit-collision detected on the RF interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | ValuesAfterColl | 7   | R/W |     | 0: all received bits will be cleared after a collision only used during bitwise anticollision at 106 kBd, otherwise it is set to logic 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | reserved        | 6   | _   |     | reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | CollPosNotValid | 5   | R   |     | 1: no collision detected or the position of the collision is out of the range of CollPos[4:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     | CollPos[4:0]    | 4:0 | R   |     | shows the bit position of the first detected collision in a received frame only data bits are interpreted example:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |           |     |           |           | 00h: indicates a bit-collision in the 32nd bit            |

|-----|-----------|-----|-----------|-----------|-----------------------------------------------------------|

|     |           |     |           |           | 01h: indicates a bit-collision in the 1st bit             |

|     |           |     |           |           | 08h: indicates a bit-collision in the 8th bit             |

|     |           |     |           |           | these bits will only be interpreted if the                |

|     |           |     |           |           | CollPosNotValid bit is set to logic 0                     |

| 0Fh | reserved  |     |           | 08h       | reserved for future use                                   |

| 10h | reserved  |     |           | 00h       | reserved for future use                                   |

| 11h | ModeReg   |     |           | 3Fh       | defines general modes for transmitting and receiving      |

|     |           |     |           |           | 1: CRC coprocessor calculates the CRC with MSB            |

|     |           |     |           |           | first. In the CRCResultReg register the values for the    |

|     | MSBFirst  | 7   | R/W       |           | CRCResultMSB[7:0] bits and the CRCResultLSB[7:0]          |

|     |           |     |           |           | bits are bit reversed                                     |

|     |           |     |           |           | NOTE: during RF communication this bit is ignored         |

|     | reserved  | 6   | -         |           | reserved for future use                                   |

|     |           |     |           |           | 1: transmitter can only be started if an RF field is      |

|     | TxWaitRF  | 5   | R/W       |           | generated                                                 |

|     | reserved  | 4   | -         |           | reserved for future use                                   |

|     | PolSigin  | 3   | R/W       |           | define the polarity of pin MFIN                           |

|     | reserved  | 2   | -         |           | reserved for future use                                   |

|     |           |     |           |           | defines the preset value for the CRC coprocessor for the  |

|     |           |     |           |           | CalcCRC command                                           |

|     |           |     |           |           | NOTE: during any communication, the preset values         |

|     |           |     |           |           | are selected automatically according to the definition of |

|     | CRCPreset | 1:0 | R/W       |           | bits in the RxModeReg and TxModeReg registers             |

|     |           |     |           |           | 00: 0000h                                                 |

|     |           |     |           | 01: 6363h |                                                           |

|     |           |     |           | 10: A671h |                                                           |

|     |           |     | 11: FFFFh |           |                                                           |

| 12h | TxModeReg |     |           | 00h       | defines transmission data rate and framing                |

|     |              |     |     | 1   |                                                      |

|-----|--------------|-----|-----|-----|------------------------------------------------------|

|     | T. CD.CE     |     | D/W |     | 1: enables CRC generation during data transmission   |

|     | TxCRCEn      | 7   | R/W |     | NOTE: it can only be set to logic 0 at 106 kBd       |

|     |              |     |     |     | defines the bit rate during data transmission. 52202 |

|     |              |     |     |     | handles transmission rates up to 848 kBd             |

|     |              |     |     |     | 000:106kBd                                           |

|     | TxSpeed[2:0] | 6:4 | D   |     | 001:212kBd                                           |

|     |              |     |     |     | 010:424kBd                                           |

|     |              |     |     |     | 011:848kBd                                           |

|     |              |     |     |     | 100-111: reserved                                    |

|     | InvMod       | 3   | R/W |     | 1: modulation of transmitted data is inverted        |

|     | reserved     | 2:0 | -   |     | reserved                                             |

| 13h | RxModeReg    |     |     | 00h | defines transmission data rate and framing           |

|     |              |     |     |     | 1: enables CRC generation during data transmission   |

|     | RxCRCEn      | 7   | R/W |     | NOTE: it can only be set to logic 0 at 106 kBd       |

|     |              |     |     |     | defines the bit rate during data transmission. 52202 |

|     |              |     |     |     | handles transmission rates up to 848 kBd             |

|     |              |     |     |     | 000:106kBd                                           |