# AAD08D2500

## 2.5GS/5GS 8Bits 模数转换器(ADC)

### 1 产品特点

- 高输入带宽: DC~3.5GHz

- 高采样率: 双通道模式 1~2.5Gsps

- 交织模式 2~5Gsps

- 输入时钟电平: LVDS

- 支持多芯片同步

- 功耗: ~4.2W

- 支持数字编程接口 (SPI)

### 2 产品描述

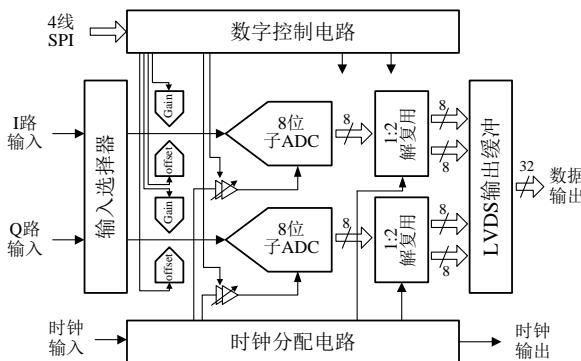

AAD08D2500 是采用 Si 基工艺制造的高速宽带模数转换器。该芯片可将差分 540mV 输入模拟信号转换成 8bit 数字信号，芯片内包含两个可最高工作在 2.5GS/s 的子 ADC，可工作在交织和非交织模式，在对数据进行 2 倍解复用 (Demux) 之后通过 LVDS 接口输出。输出信号包括 1 路时钟 (2 或 4 分频)、32 路数据输出以及 2 路超量程比特位输出，均为 LVDS 电平标准。芯片采用 +4.6V/+3.3V/+1.8V 电源供电，总功耗约为 4W。芯片支持 LQFP 和 FC-BGA 两种封装，增强型导热焊盘 LQFP 封装有 144 个引脚，可在工业级温度 (-40°C ≤ TA ≤ 85°C) 范围内正常工作。倒装 FC-BGA 有 380 个引脚。

### 3 应用范围

- 高速示波器

- 高速数据采集卡

- 宽带通信

### 4 主要性能指标

- 分辨率: 8Bits

- 最高转换速率: 5GSPS (min)

- ENOB: 6.4Bits (type)

- DNL : ±0.2LSB (type)

- 功耗: 3.8W (type)

- 通道数: 2

图 4-1 AAD08D2500 结构框图

## 目录

|      |                     |           |

|------|---------------------|-----------|

| 1    | 产品特点 .....          | 1         |

| 2    | 产品描述 .....          | 1         |

| 3    | 应用范围 .....          | 1         |

| 4    | 主要性能指标 .....        | 1         |

|      | 目录 .....            | 2         |

| 5    | 引脚配置 .....          | 3         |

| 6    | 性能参数 .....          | 7         |

| 6.1  | 绝对最大额定值 .....       | 7         |

| 6.2  | 封装热阻 .....          | 7         |

| 6.3  | ESD 信息 .....        | 7         |

| 6.4  | 建议工作条件 .....        | 7         |

| 6.5  | 电气性能 - 直流 .....     | 8         |

| 6.6  | 电气性能 - 交流 .....     | 错误!未定义书签。 |

| 6.7  | 典型测试结果 .....        | 10        |

| 6.8  | 典型测试结果 - 单音频谱 ..... | 错误!未定义书签。 |

| 7    | 产品详细描述 .....        | 16        |

| 7.1  | 概述 .....            | 16        |

| 7.2  | 电源电压 .....          | 16        |

| 7.3  | 模拟输入 .....          | 错误!未定义书签。 |

| 7.4  | 时钟输入 .....          | 错误!未定义书签。 |

| 7.5  | 控制接口 .....          | 错误!未定义书签。 |

| 7.6  | 寄存器表 .....          | 错误!未定义书签。 |

| 7.7  | 高速串行数据输出 .....      | 错误!未定义书签。 |

| 7.8  | 数据训练与接口同步 .....     | 错误!未定义书签。 |

| 7.9  | 校准功能说明 .....        | 错误!未定义书签。 |

| 7.10 | 多片间同步 .....         | 错误!未定义书签。 |

| 7.11 | 芯片布线规则及其他说明 .....   | 错误!未定义书签。 |

| 8    | 封装和订购信息： .....      | 25        |

| 9    | 修订版次 .....          | 26        |

| 10   | 声明 .....            | 27        |

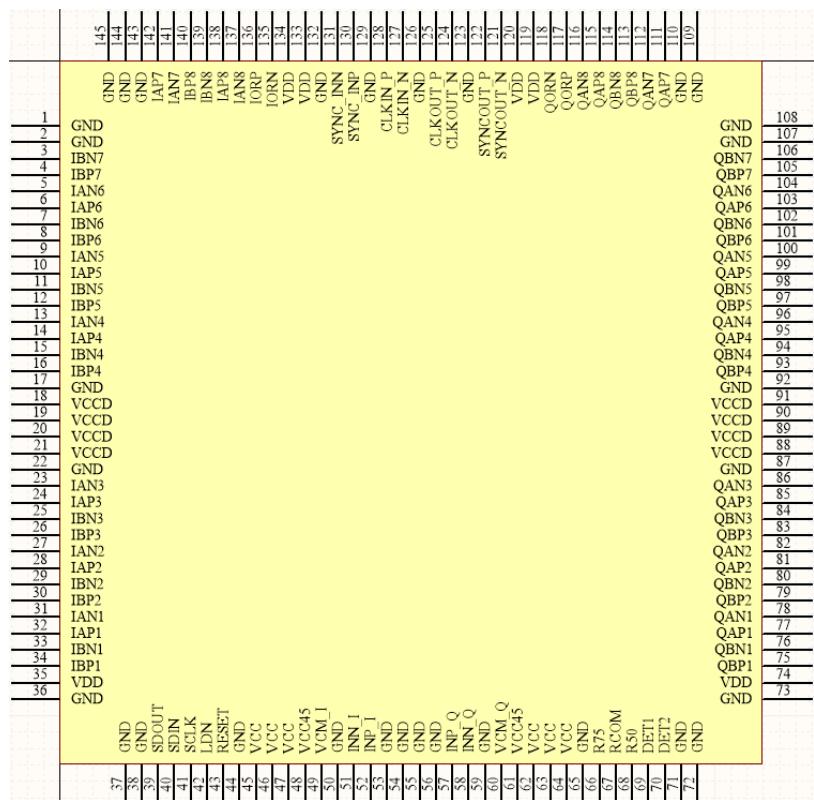

5 引脚配置

图 5-1 AAD08D2500\_LQFP144 封装引脚分布图

表 5-1 AAD08D2500\_LQFP144 引脚说明

| 引脚                                                                                                    |        | 类型 | 功能描述                   |

|-------------------------------------------------------------------------------------------------------|--------|----|------------------------|

| 引脚编号                                                                                                  | 引脚名称   |    |                        |

| 1,2,17,22,36,37,38,44,50,53,54,55,56,59,65,71,72,73,87,92,107,108,109,110,123,126,129,132,143,144,145 | GND    | 地  | 所有引脚统一接地               |

| 32/31                                                                                                 | I1AP/N | 输出 | LVDS 电平输出, 最高 1.25Gbps |

| 28/27                                                                                                 | I2AP/N | 输出 |                        |

| 24/23                                                                                                 | I3AP/N | 输出 |                        |

| 14/13                                                                                                 | I4AP/N | 输出 |                        |

| 10/9                                                                                                  | I5AP/N | 输出 |                        |

| 6/5                                                                                                   | I6AP/N | 输出 |                        |

| 142/141                                                                                               | I7AP/N | 输出 |                        |

| 138/137                                                                                               | I8AP/N | 输出 |                        |

| 34/33                                                                                                 | I1BP/N | 输出 | LVDS 电平输出, 最高 1.25Gbps |

| 30/29                                                                                                 | I2BP/N | 输出 |                        |

| 26/25                                                                                                 | I3BP/N | 输出 |                        |

| 16/15                                                                                                 | I4BP/N | 输出 |                        |

| 12/11                                                                                                 | I5BP/N | 输出 |                        |

| 8/7                                                                                                   | I6BP/N | 输出 |                        |

| 4/3                                                                                                   | I7BP/N | 输出 |                        |

| 140/139                                                                                               | I8BP/N | 输出 |                        |

| 77/78                                                                                                 | Q1AP/N | 输出 | LVDS 电平输出, 最高 1.25Gbps |

| 81/82                                                                                                 | Q2AP/N | 输出 |                        |

| 85/86                                                                                                 | Q3AP/N | 输出 |                        |

| 95/96                                                                                                 | Q4AP/N | 输出 |                        |

| 引脚                      |             | 类型    | 功能描述                                |

|-------------------------|-------------|-------|-------------------------------------|

| 引脚编号                    | 引脚名称        |       |                                     |

| 99/100                  | Q5AP/N      | 输出    | LVDS 电平输出, 最高 1.25Gbps              |

| 103/104                 | Q6AP/N      |       |                                     |

| 111/112                 | Q7AP/N      |       |                                     |

| 115/116                 | Q8AP/N      |       |                                     |

| 75/76                   | Q1BP/N      |       |                                     |

| 79/80                   | Q2BP/N      |       |                                     |

| 83/84                   | Q3BP/N      |       |                                     |

| 93/94                   | Q4BP/N      |       |                                     |

| 97/98                   | Q5BP/N      |       |                                     |

| 101/102                 | Q6BP/N      |       |                                     |

| 105/106                 | Q7BP/N      |       |                                     |

| 113/114                 | Q8BP/N      |       |                                     |

| 117/118                 | QORP/N      |       | 超量程时为 1, LVDS 电平, 不用时接 100 欧姆负载     |

| 136/135                 | IORP/N      |       |                                     |

| 18,19,20,21,88,89,90,91 | VCCD        | 电源    | 数字电源                                |

| 35,74,119,120,133,134   | VCCIO       | 电源    | 数字电源                                |

| 45,46,47,62,63,64       | VCCA        | 电源    | 模拟电源                                |

| 48,61                   | VCCT        | 电源    | 模拟电源                                |

| 39                      | SDOUT       | 输出    | 串行数据输出, 1.8V CMOS 电平                |

| 40                      | SDIN        | 输入    | 串行数据输入, 1.8V CMOS 电平                |

| 41                      | SCLK        | 输入    | 串行时钟输入, 1.8V CMOS 电平                |

| 42                      | LDN         | 输入    | 串行数据加载信号, 低有效, 1.8V CMOS 电平         |

| 43                      | RESET       | 输入    | 复位信号, 高有效, 1.8V CMOS 电平             |

| 49/60                   | VCM_I/VCM_Q | 输出    | 用于驱动带共模控制端的前置缓冲放大器。                 |

| 52/51                   | INI_P/INI_N | 输入    | I 路输入端, 内置偏置电路, 差分阻抗 100 欧姆         |

| 57/58                   | INQ_P/INQ_N | 输入    | Q 路输入端, 内置偏置电路, 差分阻抗 100 欧姆         |

| 66                      | R75         | 电阻监控端 | -                                   |

| 67                      | RCOM        |       |                                     |

| 68                      | R50         |       |                                     |

| 69                      | DET1        | 温度监控端 | 温度二极管, 可用来监控芯片的结温。接 1.5K 欧姆电阻至 VCCA |

| 70                      | DET2        |       |                                     |

| 122/121                 | SYNCOUT_P/N | 输出    | 同步信号, LVDS 电平, 不用时接 100 欧姆负载。       |

| 125/124                 | CLKOUT_P/N  | 输出    | 输出时钟, 采样时钟的 1/2 或 1/4 分频, LVDS 电平   |

| 128/127                 | CLKIN_P/N   | 输入    | 输入时钟, 内置偏置电路, 差分阻抗 100 欧姆。          |

| 130/131                 | SYNCIN_P/N  | 输入    | 同步信号, 需直流耦合, 差分阻抗 100 欧姆。           |

|   | 1     | 2     | 3         | 4         | 5    | 6     | 7          | 8          | 9     | 10    | 11    | 12    | 13      | 14      | 15   | 16    | 17       | 18       | 19    | 20    |   |

|---|-------|-------|-----------|-----------|------|-------|------------|------------|-------|-------|-------|-------|---------|---------|------|-------|----------|----------|-------|-------|---|

| A |       | GND   | SYNCOUT_N | SYNCOUT_P | GND  |       |            |            |       | GND   | GND   |       |         |         |      | GND   | SYNCIN_N | SYNCIN_P | GND   |       | A |

| B | QOR_N | QOR_P | GND       | GND       | GND  | GND   | CLKOUT_T_N | CLKOUT_T_P | GND   | GND   | GND   | GND   | CLKIN_N | CLKIN_P | GND  | GND   | GND      | GND      | IOR_P | IOR_N | B |

| C | QA8_N | QA8_P | GND       | GND       | GND  | GND   | GND        | GND        | VCCIO | VCCIO | VCCIO | VCCIO | GND     | GND     | GND  | GND   | GND      | IA8_P    | IA8_N |       | C |

| D | QB8_N | QB8_P | GND       | GND       | GND  | VCCIO | VCCIO      | VCCIO      | VCCIO | VCCIO | VCCIO | VCCIO | VCCIO   | VCCIO   | GND  | GND   | IB8_P    | IB8_N    |       | D     |   |

| E | QA7_N | QA7_P | GND       | GND       | GND  | GND   | GND        | GND        | GND   | GND   | GND   | GND   | GND     | GND     | GND  | GND   | GND      | IA7_P    | IA7_N |       | E |

| F | QB7_N | QB7_P | GND       | GND       | GND  | GND   | GND        | GND        | GND   | GND   | GND   | GND   | GND     | GND     | GND  | GND   | GND      | IB7_P    | IB7_N |       | F |

| G | QA6_N | QA6_P | GND       | GND       | GND  | GND   | GND        | GND        | GND   | GND   | GND   | GND   | GND     | GND     | GND  | GND   | GND      | IA6_P    | IA6_N |       | G |

| H | QB6_N | QB6_P | GND       | GND       | GND  | GND   | GND        | GND        | GND   | GND   | GND   | GND   | GND     | GND     | GND  | GND   | GND      | IB6_P    | IB6_N |       | H |

| J | QA5_N | QA5_P | GND       | VCCD      | VCCD | VCCD  | VCCD       | GND        | GND   | GND   | GND   | GND   | VCCD    | VCCD    | VCCD | VCCD  | GND      | IA5_P    | IA5_N |       | J |

| K | QB5_N | QB5_P | GND       | VCCD      | VCCD | VCCD  | VCCD       | GND        | GND   | GND   | GND   | GND   | VCCD    | VCCD    | VCCD | VCCD  | GND      | IB5_P    | IB5_N |       | K |

| L | QA4_N | QA4_P | GND       | VCCD      | VCCD | VCCD  | VCCD       | GND        | GND   | GND   | GND   | GND   | VCCD    | VCCD    | VCCD | VCCD  | GND      | IA4_P    | IA4_N |       | L |

| M | QB4_N | QB4_P | GND       | VCCD      | VCCD | VCCD  | VCCD       | GND        | GND   | GND   | GND   | GND   | VCCD    | VCCD    | VCCD | VCCD  | GND      | IB4_P    | IB4_N |       | M |

| N | QA3_N | QA3_P | GND       | GND       | GND  | GND   | GND        | GND        | GND   | GND   | GND   | GND   | GND     | GND     | GND  | GND   | GND      | IA3_P    | IA3_N |       | N |

| P | QB3_N | QB3_P | GND       | GND       | GND  | GND   | GND        | GND        | GND   | GND   | GND   | GND   | GND     | GND     | GND  | GND   | GND      | IB3_P    | IB3_N |       | P |

| R | QA2_N | QA2_P | GND       | GND       | GND  | GND   | GND        | GND        | GND   | GND   | GND   | GND   | GND     | GND     | GND  | GND   | GND      | IA2_P    | IA2_N |       | R |

| T | QB2_N | QB2_P | GND       | GND       | GND  | GND   | VCCA       | VCCA       | VCCA  | VCCA  | VCCA  | VCCA  | VCCA    | VCCA    | VCCA | GND   | GND      | IB2_P    | IB2_N |       | T |

| U | QA1_N | QA1_P | GND       | GND       | GND  | GND   | VCCA       | VCCA       | VCCT  | VCCT  | VCCT  | VCCT  | VCCA    | VCCA    | GND  | GND   | GND      | IA1_P    | IA1_N |       | U |

| V | QB1_N | QB1_P | GND       | GND       | GND  | GND   | GND        | GND        | VCCT  | VCCT  | VCCT  | VCCT  | GND     | GND     | GND  | GND   | GND      | IB1_P    | IB1_N |       | V |

| W | R50   | RCOM  | R75       | VCM_Q     | GND  | GND   | INQ_N      | INQ_P      | GND   | GND   | GND   | INI_P | INI_N   | GND     | GND  | VCM_I | SCLK     | SDIN     | SDOUT |       | W |

| Y |       | DET2  | DET1      | GND       | GND  |       |            |            | GND   | GND   |       |       |         | GND     | GND  | RESET | LDN      |          |       |       | Y |

|   | 1     | 2     | 3         | 4         | 5    | 6     | 7          | 8          | 9     | 10    | 11    | 12    | 13      | 14      | 15   | 16    | 17       | 18       | 19    | 20    |   |

图 5-2 AAD08D2500\_FCBGA380 封装引脚分布图 (顶视图)

表 5-2 AAD08D2500\_FCBGA380 引脚说明

| 引脚                                                                                                                                                                                                                                                                   |        | 类型 | 功能描述                   |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----|------------------------|--|

| 引脚编号                                                                                                                                                                                                                                                                 | 引脚名称   |    |                        |  |

| A2,A5,A10,A11,A16,A19,B3-B6,B9-B12,B15-B18,C3-C9,C12-C18,D3-D5,D16-D18,E3-E18,F3-F18,G3-G18,H3-H18,J3,J8-J13,J18,K3,K8-K13,K18,L3,L8-L13,L18,M3,M8-M13,M18,N3-N18,P3-P18,R3-R18,T3-T6,T15-T18,U3-U6,U15-U18,V3-V9,V12-V18,W5,W6,W9-W12,W15,W16,Y4,Y5,Y10,Y11,Y16,Y17 | GND    | 地  | 所有引脚统一接地               |  |

| U19/U20                                                                                                                                                                                                                                                              | I1AP/N | 输出 | LVDS 电平输出, 最高 1.25Gbps |  |

| R19/R20                                                                                                                                                                                                                                                              | I2AP/N | 输出 |                        |  |

| N19/N20                                                                                                                                                                                                                                                              | I3AP/N | 输出 |                        |  |

| L19/L20                                                                                                                                                                                                                                                              | I4AP/N | 输出 |                        |  |

| J19/J20                                                                                                                                                                                                                                                              | I5AP/N | 输出 |                        |  |

| G19/G20                                                                                                                                                                                                                                                              | I6AP/N | 输出 |                        |  |

| E19/E20                                                                                                                                                                                                                                                              | I7AP/N | 输出 |                        |  |

| C19/C20                                                                                                                                                                                                                                                              | I8AP/N | 输出 |                        |  |

| 引脚                                                      |             | 类型    | 功能描述                                |

|---------------------------------------------------------|-------------|-------|-------------------------------------|

| 引脚编号                                                    | 引脚名称        |       |                                     |

| V19/V20                                                 | I1BP/N      | 输出    | LVDS 电平输出, 最高 1.25Gbps              |

| T19/T20                                                 | I2BP/N      |       |                                     |

| P19/P20                                                 | I3BP/N      |       |                                     |

| M19/M20                                                 | I4BP/N      |       |                                     |

| K19/K20                                                 | I5BP/N      |       |                                     |

| H19/H20                                                 | I6BP/N      |       |                                     |

| F19/F20                                                 | I7BP/N      |       |                                     |

| D19/D20                                                 | I8BP/N      |       |                                     |

| U2/U1                                                   | Q1AP/N      |       |                                     |

| R2/R1                                                   | Q2AP/N      |       |                                     |

| N2/N1                                                   | Q3AP/N      | 输出    | LVDS 电平输出, 最高 1.25Gbps              |

| L2/L1                                                   | Q4AP/N      |       |                                     |

| J2/J1                                                   | Q5AP/N      |       |                                     |

| G2/G1                                                   | Q6AP/N      |       |                                     |

| E2/E1                                                   | Q7AP/N      |       |                                     |

| C2/C1                                                   | Q8AP/N      |       |                                     |

| V2/V1                                                   | Q1BP/N      |       |                                     |

| T2/T1                                                   | Q2BP/N      |       |                                     |

| P2/P1                                                   | Q3BP/N      |       |                                     |

| M2/M1                                                   | Q4BP/N      |       |                                     |

| K2/K1                                                   | Q5BP/N      | 输出    | LVDS 电平输出, 最高 1.25Gbps              |

| H2/H1                                                   | Q6BP/N      |       |                                     |

| F2/F1                                                   | Q7BP/N      |       |                                     |

| D2/D1                                                   | Q8BP/N      |       |                                     |

| B2/B1                                                   | QORP/N      |       |                                     |

| B19/B20                                                 | IORP/N      |       |                                     |

| J4-J7,J14-J17,K4-K7,K14-K17,L4-L7,L14-L17,M4-M7,M14-M17 | VCCD        |       |                                     |

| C10,C11,D6-D15                                          | VCCIO       |       |                                     |

| T7-T14,U7,U8,U13, U14                                   | VCCA        |       |                                     |

| U9-U12,V10,V11                                          | VCCT        |       |                                     |

| W20                                                     | SDOUT       | 输出    | 串行数据输出, 1.8V CMOS 电平                |

| W19                                                     | SDIN        |       |                                     |

| W18                                                     | SCLK        |       |                                     |

| Y19                                                     | LDN         |       |                                     |

| Y18                                                     | RESET       |       |                                     |

| W17                                                     | VCM_I       |       |                                     |

| W4                                                      | VCM_Q       |       |                                     |

| W13/W14                                                 | INI_P/INI_N |       |                                     |

| W8/W7                                                   | INQ_P/INQ_N |       |                                     |

| W3                                                      | R75         | 电阻监控端 | 温度二极管, 可用来监控芯片的结温。接 1.5K 欧姆电阻至 VCCA |

| W2                                                      | RCOM        |       |                                     |

| W1                                                      | R50         |       |                                     |

| Y3                                                      | DET1        |       |                                     |

| Y2                                                      | DET2        | 温度监控端 | 同步信号, LVDS 电平, 不用时接 100 欧姆负载。       |

| A4/A3                                                   | SYNCOUT_P/N |       |                                     |

| B8/B7                                                   | CLKOUT_P/N  |       |                                     |

| B14/B13                                                 | CLKIN_P/N   |       |                                     |

| A18/A17                                                 | SYNCIN_P/N  | 输入    | 输出时钟, 采样时钟的 1/2 或 1/4 分频, LVDS 电平   |

|                                                         |             | 输入    | 输入时钟, 内置偏置电路, 差分阻抗 100 欧姆。          |

|                                                         |             | 输入    | 同步信号, 需直流耦合, 差分阻抗 100 欧姆。           |

## 6 性能参数

### 6.1 绝对最大额定值

注意，超出绝对最大额定值可能会导致器件永久性损坏。绝对最大额定值仅代表产品的压力等级，不作为实现产品功能的工作条件的限值，超过本手册中推荐工作条件章节的限值均是不推荐的行为。

| 参数                           | 最小值   | 最大值   |

|------------------------------|-------|-------|

| 模拟电源 (VCCT)                  | -0.5  | +5.5V |

| 模拟电源 (VCCA)                  | -0.5  | +4V   |

| 数字电源 (VCCD)                  | -0.5  | +4V   |

| 数字电源电压 (VCCIO)               | -0.5  | +2.2V |

| 模拟输入端电压 (VINX_P, VINX_N)     | 0     | +3.3V |

| 时钟输入端电压 (VCLKIN_P, VCLKIN_N) | 0     | +3.3V |

| 工作温度                         | -40°C | +85°C |

| 储藏温度                         | -65°C | 150°C |

### 6.2 封装热阻

以下数据为封装热阻仿真结果，仿真条件为自然空气对流环境，JEDEC 2s2p PCB。为了使芯片发挥更佳性能，推荐用户在芯片顶部增加辅助散热装置。

| 封装类型           | $\theta_{JA}$ | $\theta_{JC-TOP}$ | $\theta_{JC-Bot}$ |

|----------------|---------------|-------------------|-------------------|

| 144-Lead, LQFP | 6.2°C/W       | -                 | 5.5°C/W           |

| FCBGA-380      | 11.4°C/W      | 1.4°C/W           | 6.3°C/W           |

### 6.3 ESD 信息

注意：本产品内置防静电保护装置有限，为了防止静电损坏门电路，在储存或处理过程中应使引脚短接在一起或将产品放置在导电泡沫材料中。

#### ➤ LQFP-144

**HBM (ANSI/ESDA/JEDEC JS 001 2017) : HBM 耐压值 1000V; HBM 等级: 1C**

注意：HBM 的耐压值由 SPI 串行数据输出引脚决定 (SDOUT)，通过 1000V；其他所有引脚均通过 2000V。

#### ➤ FCBGA-380

**HBM (ANSI/ESDA/JEDEC JS 001 2017) : HBM 耐压值 1000V; HBM 等级: 1C**

注意：HBM 的耐压值由电阻监控端口引脚决定 (R50)，通过 1000V；其他所有引脚均通过 1100V。

### 6.4 建议工作条件

| 参数                                      | 最小值  | 典型值 | 最大值  | 单位  |

|-----------------------------------------|------|-----|------|-----|

| 模拟电源 (VCCT)                             | 4.55 | 4.6 | 4.65 | V   |

| 模拟电源 (VCCA)                             | 3.25 | 3.3 | 3.35 | V   |

| 数字电源 (VCCD)                             | 3.25 | 3.3 | 3.35 | V   |

| 数字电源 (VCCIO)                            | 1.7  | 1.8 | 1.9  | V   |

| 输入电流 ( $I_{IN}$ )                       | 1.27 | -   | 1.50 | A   |

| 模拟输入端电压 ( $V_{INX\_P}/V_{INX\_N}$ )     | +1.5 |     | +2.1 | V   |

| 时钟输入端电压 ( $V_{CLKIN\_P}/V_{CLKIN\_N}$ ) | +1.4 |     | +2.2 | V   |

| 输入时钟频率 ( $f_{CLK}$ )                    | 500  |     | 2500 | MHz |

| 功耗 ( $P_D$ )                            | -    | 3.9 | -    | W   |

| 工作温度 ( $T_A$ )                          | -40  | -   | +85  | °C  |

## 6.5 电气性能 - 直流

以下规格适用于 TA=+25°C。

| 参数                  | 测试条件           | 最小值               | 典型值                    | 最大值   | 单位                     |                  |

|---------------------|----------------|-------------------|------------------------|-------|------------------------|------------------|

| I <sub>CCT</sub>    | 模拟电源电流         | -                 | 0.065                  | 0.078 | A                      |                  |

| I <sub>CCA</sub>    | 模拟电源电流         | -                 | 0.30                   | 0.40  | A                      |                  |

| I <sub>CCD</sub>    | 数字电源电流         | -                 | 0.45                   | 0.54  | A                      |                  |

| I <sub>CCIO</sub>   | 数字 IO 电流       | -                 | 0.15                   | 0.21  | A                      |                  |

| P                   | 功耗             | -                 | 3.0                    | 3.8   | W                      |                  |

| V <sub>COM</sub>    | 共模电压           | -                 | 1.70                   | 1.80  | 1.90                   | V                |

| V <sub>IN_FSR</sub> | 全摆幅模拟差分信号输入范围  | -                 | 450                    | 520   | 650                    | mV <sub>PP</sub> |

| R <sub>IN</sub>     | 差分输入阻抗         | -                 | 90                     | 100   | 110                    | Ω                |

| Offset              | 失调误差           | -                 | -0.7                   | -     | 0.6                    | LSB              |

| LSB                 | 最低有效位          | -                 | 1.7                    | 2.0   | 2.4                    | mV               |

| V <sub>ID</sub>     | 差分时钟输入电平       | -                 | 0.6                    | 0.9   | 1.2                    | V <sub>PP</sub>  |

| V <sub>OD</sub>     | LVDS 差分输出      | -                 | 470                    | 700   | 920                    | mV <sub>PP</sub> |

| V <sub>OS</sub>     | LVDS 输出共模电压    | -                 | 950                    | 1250  | 1550                   | mV <sub>PP</sub> |

| V <sub>IH</sub>     | LVCMOS 输入逻辑高电平 | -                 | 0.85*V <sub>CCIO</sub> | -     | -                      | V                |

| V <sub>IL</sub>     | LVCMOS 输入逻辑低电平 | -                 | -                      | -     | 0.15*V <sub>CCIO</sub> | V                |

| V <sub>OH</sub>     | LVCMOS 输出逻辑高电平 | -                 | 1.5                    | -     | -                      | V                |

| V <sub>OL</sub>     | LVCMOS 输出逻辑低电平 | -                 | -                      | -     | 0.3                    | V                |

| INL                 | 积分非线性          | 满量程 10MHz 低失真正弦信号 | -                      | ±1.5  | ±2.7                   | LSB              |

| DNL                 | 差分非线性          |                   | -                      | ±0.7  | ±1.0                   | LSB              |

## 6.6 电气性能 - 交流

以下规格适用于  $T_A = +25^\circ\text{C}$ 。除非另行说明，所有其他的界限均适用于温度  $T_A = 25^\circ\text{C}$ 。

| 参数             |          | 测试条件                               | 最小值   | 典型值        | 最大值    | 单位     |

|----------------|----------|------------------------------------|-------|------------|--------|--------|

| FPBW           | 模拟输入带宽   | -1dB                               | -     | 2          | -      | GHz    |

|                |          | -3dB                               | -     | 3          | -      | GHz    |

| -              | 超出范围输出码  | $V_{IN+} - V_{IN-} > \text{正向满摆幅}$ | -     | -          | 255    | -      |

|                |          | $V_{IN+} - V_{IN-} < \text{正向满摆幅}$ | 0     | -          | -      | -      |

| <b>非交织模式</b>   |          |                                    |       |            |        |        |

| -C.E.R.        | 误码率      | $f_{IN} = 510.99\text{MHz}$        | -     | $10^{-15}$ | -      | Errors |

| ENOB           | 有效比特位    |                                    | -     | 6.12       | -      | Bits   |

| SINAD          | 信号和噪声失真比 |                                    | -     | 40.57      | -      | dB     |

| SNR            | 信噪比      |                                    | -     | 41.62      | -      | dB     |

| THD            | 总谐波失真    |                                    | -     | -47.05     | -      | dB     |

| SFDR           | 无杂散动态范围  |                                    | -     | 50.80      | -      | dB     |

| ENOB           | 有效比特位    |                                    | 6.00  | 6.03       | -      | Bits   |

| SINAD          | 信号和噪声失真比 |                                    | 38.00 | 38.05      | -      | dB     |

| SNR            | 信噪比      |                                    | 38.00 | 38.72      | -      | dB     |

| THD            | 总谐波失真    |                                    | -     | -46.58     | -46.00 | dB     |

| SFDR           | 无杂散动态范围  |                                    | 48.00 | 48.67      | -      | dB     |

| <b>交织模式校准前</b> |          |                                    |       |            |        |        |

| ENOB           | 有效比特位    | $f_{IN} = 510.99\text{MHz}$        |       | 5.87       |        | Bits   |

| SINAD          | 信号和噪声失真比 |                                    |       | 37.10      |        | dB     |

| SNR            | 信噪比      |                                    |       | 37.47      |        | dB     |

| THD            | 总谐波失真    |                                    |       | -47.98     |        | dB     |

| SFDR           | 无杂散动态范围  |                                    |       | 51.03      |        | dB     |

| ENOB           | 有效比特位    |                                    | 5.20  | 5.25       |        | Bits   |

| SINAD          | 信号和噪声失真比 |                                    | 33.00 | 33.35      |        | dB     |

| SNR            | 信噪比      |                                    | 33.00 | 33.57      |        | dB     |

| THD            | 总谐波失真    |                                    | -     | -46.44     | -46.00 | dB     |

| SFDR           | 无杂散动态范围  |                                    | 48.00 | 48.01      |        | dB     |

| <b>交织模式校准后</b> |          |                                    |       |            |        |        |

| ENOB           | 有效比特位    | $f_{IN} = 1095.95\text{MHz}$       |       | 6.5        |        | Bits   |

| SINAD          | 信号和噪声失真比 |                                    |       | 41.27      |        | dB     |

| SNR            | 信噪比      |                                    |       | 42.25      |        | dB     |

| THD            | 总谐波失真    |                                    |       | -48.22     |        | dB     |

| SFDR           | 无杂散动态范围  |                                    |       | 50.5       |        | dB     |

| ENOB           | 有效比特位    |                                    | 6.10  | 6.16       |        | Bits   |

| SINAD          | 信号和噪声失真比 |                                    | 38.00 | 38.87      |        | dB     |

| SNR            | 信噪比      |                                    | 36.00 | 36.73      |        | dB     |

| THD            | 总谐波失真    |                                    | -     | -46.33     | -46.00 | dB     |

| SFDR           | 无杂散动态范围  |                                    | 47.00 | 47.7       |        | dB     |

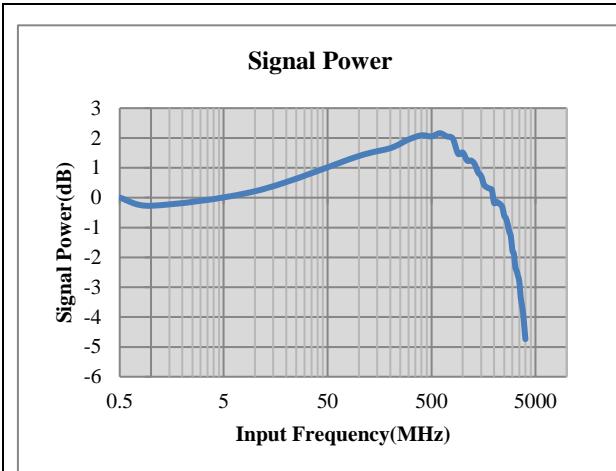

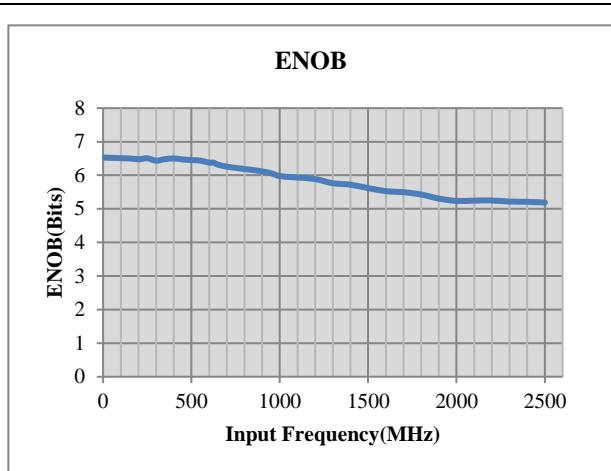

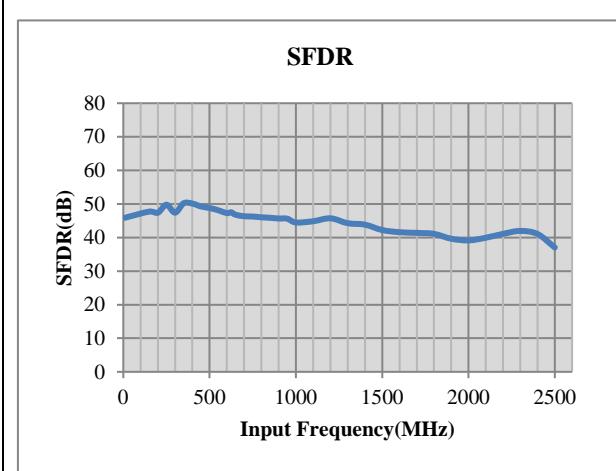

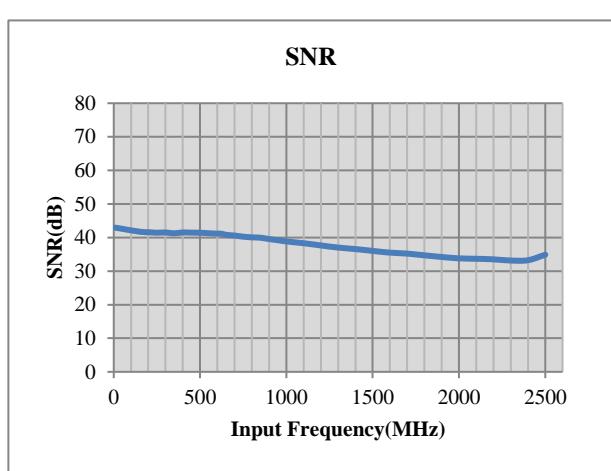

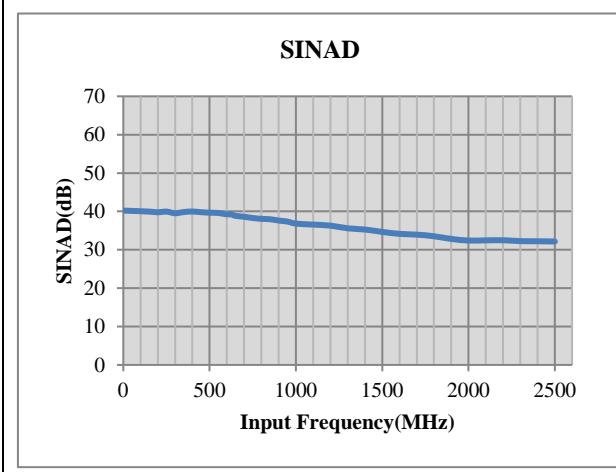

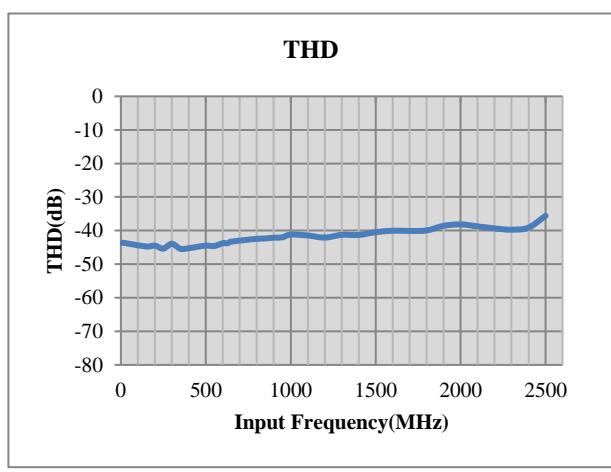

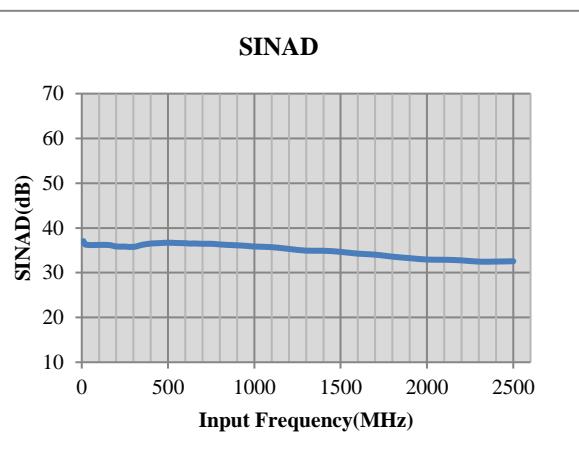

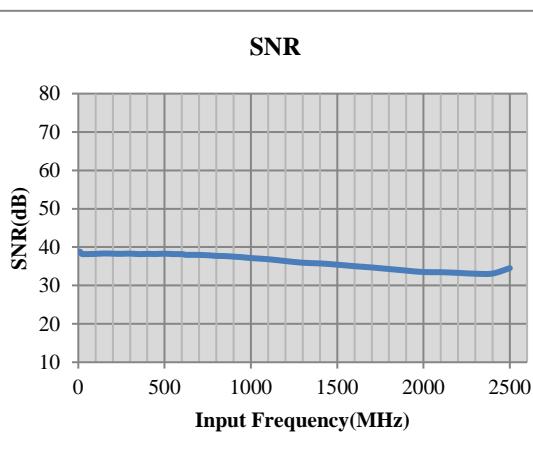

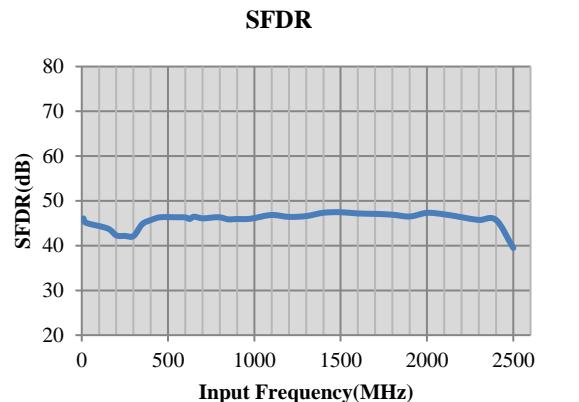

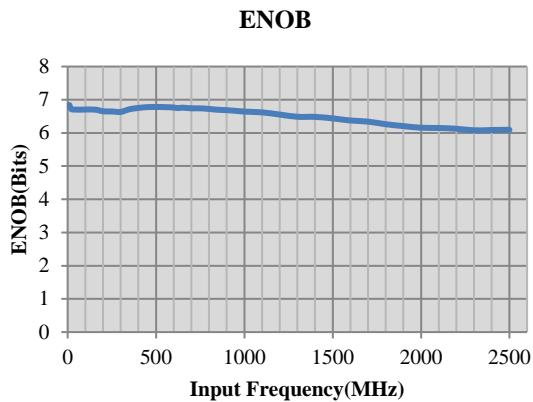

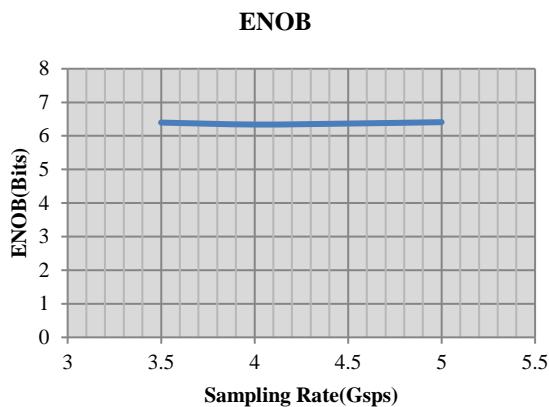

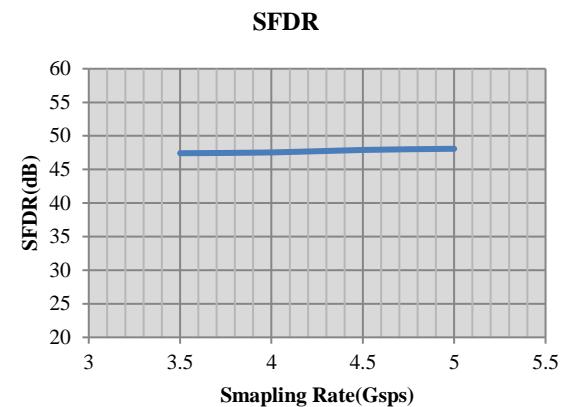

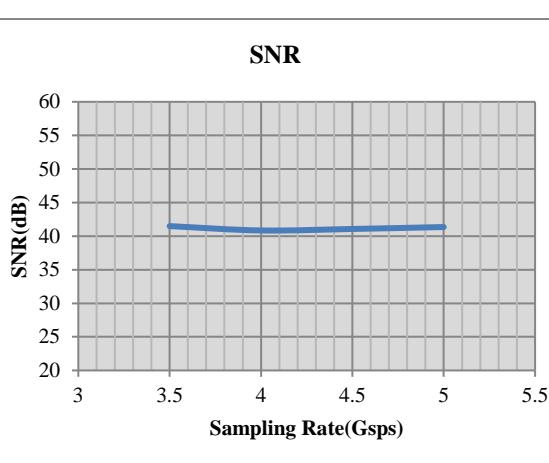

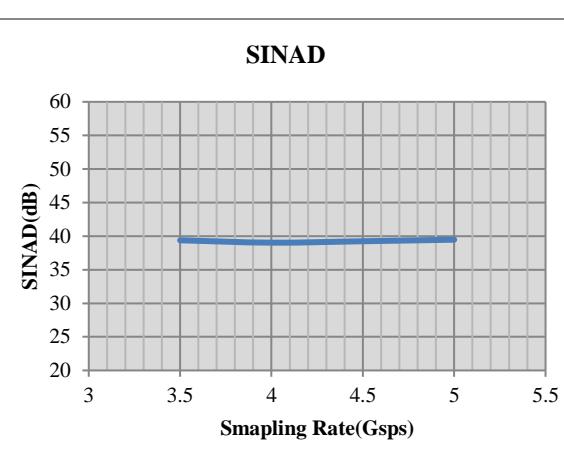

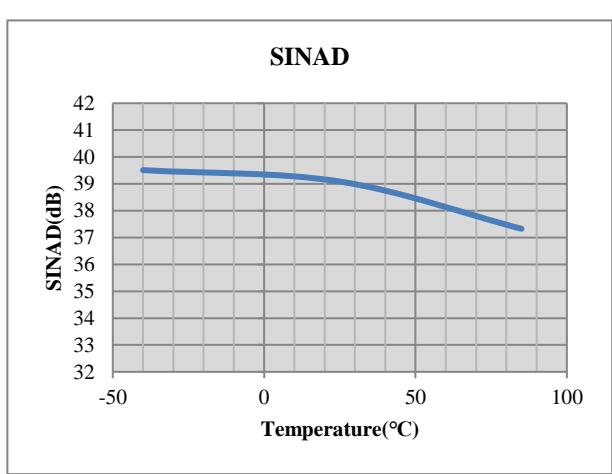

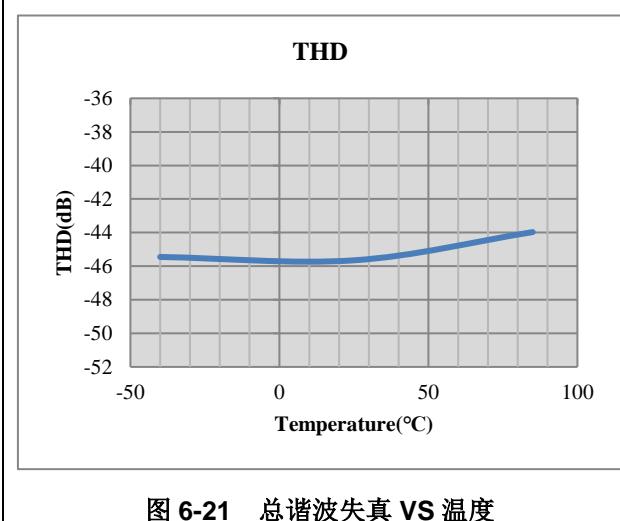

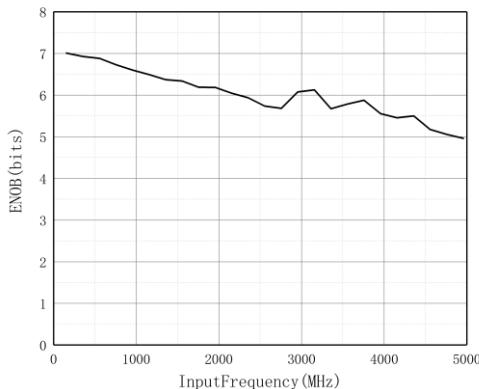

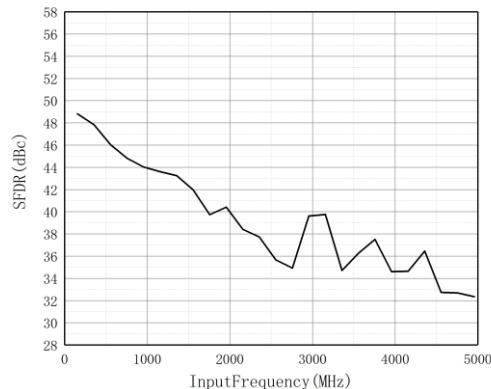

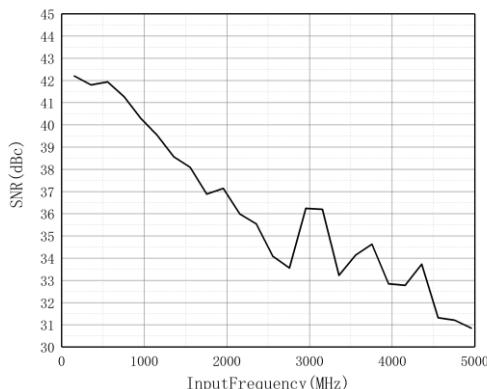

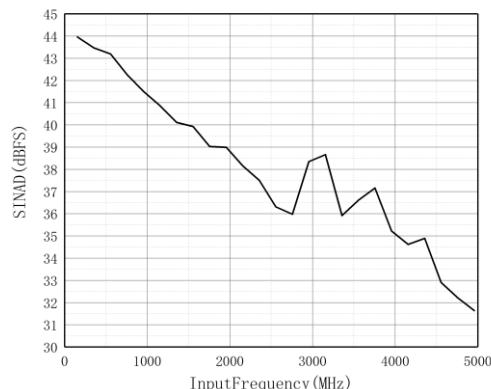

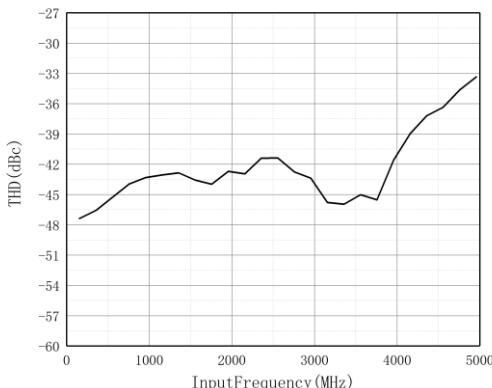

## 6.7 典型测试结果

非特别注明，以下所有测量均在  $V_{CCT}=+4.5V$ ,  $V_{CCA}=+3.3V$ ,  $V_{CCD}=+3.3V$ ,  $V_{CCIO}=+1.8V$ ,  $f_{CLK}=2.5GHz$ ,  $T_A=25^\circ C$  交织模式下进行，输出幅值为-1dBFS (Package: LQFP144) :

图 6-1 转换器输出幅频特性曲线

图 6-2 有效位 VS 输入频率

图 6-3 无杂散动态范围 VS 输入频率

图 6-4 信噪比 VS 输入频率

图 6-5 信纳比 VS 输入频率

图 6-6 总谐波失真 VS 输入频率

## 6.8 典型测试结果（续）

非特别注明，以下所有测量均在  $V_{CC1}=+4.5V$ ,  $V_{CCA}=+3.3V$ ,  $V_{CCD}=+3.3V$ ,  $V_{CCIO}=+1.8V$ ,  $f_{CLK}=2.5GHz$ ,  $T_A=25^\circ C$  交织模式下进行，输出幅值为-6dBFS (Package: LQFP144) :

## 6.9 典型测试结果（续）

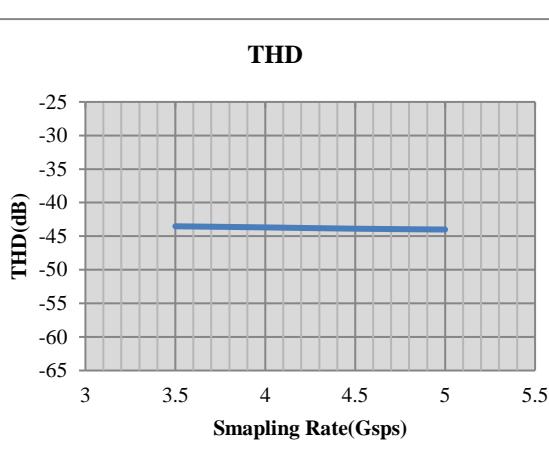

非特别注明，以下所有测量均在  $V_{CC1}=+4.5V$ ,  $V_{CCA}=+3.3V$ ,  $V_{CCD}=+3.3V$ ,  $V_{CCIO}=+1.8V$ ,  $f_{IN}=625.13MHz$ ,  $T_A=25^\circ C$  交织模式下进行，输出幅值为-1dBFS (Package: LQFP144) :

图 6-12 有效位 VS 采样率

图 6-13 无杂散动态范围 VS 采样率

图 6-14 信噪比 VS 采样率

图 6-15 信纳比 VS 采样率

图 6-16 总谐波失真 VS 采样率

## 6.10 典型测试结果（续）

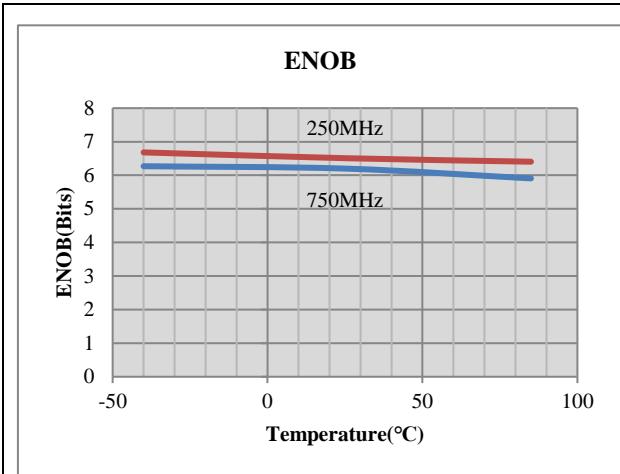

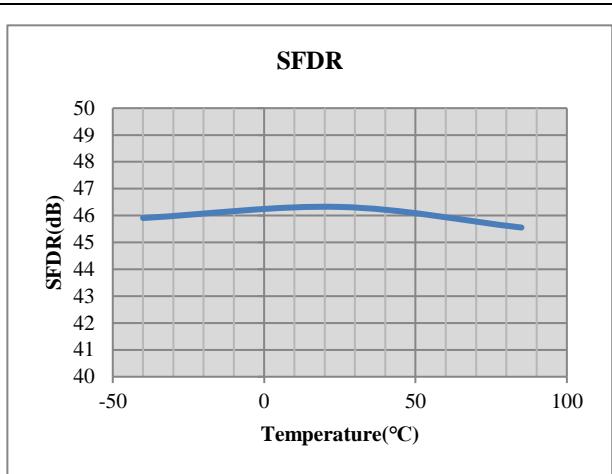

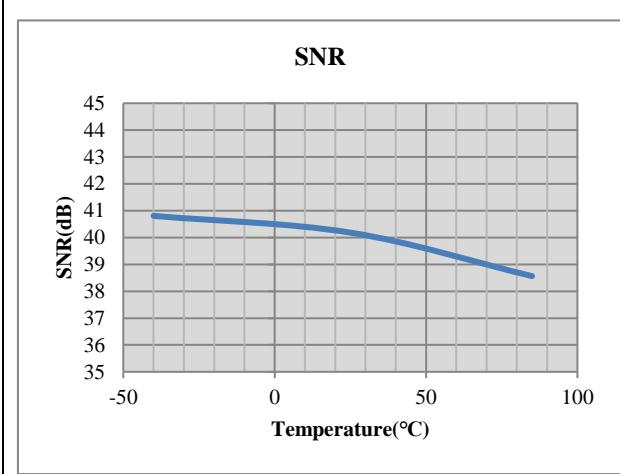

非特别注明，以下所有测量均在  $V_{CC1}=+4.5V$ ,  $V_{CCA}=+3.3V$ ,  $V_{CCD}=+3.3V$ ,  $V_{CCIO}=+1.8V$ ,  $f_{CLK}=2.5GHz$ ,  $f_{IN}=750.13MHz$ , 交织模式下进行，输出幅值为-1dBFS (Package: LQFP144) :

图 6-17 有效位 VS 温度

图 6-18 无杂散动态范围 VS 温度

图 6-19 信噪比 VS 温度

图 6-20 信纳比 VS 温度

图 6-21 总谐波失真 VS 温度

## 6.11 典型测试结果（续）

非特别注明，以下所有测量均在  $V_{CC1}=+4.5V$ ,  $V_{CCA}=+3.3V$ ,  $V_{CCD}=+3.3V$ ,  $V_{CCIO}=+1.8V$ ,  $f_{CLK}=2.5GHz$ ,  $f_{IN}=750.13MHz$ ,  $T_A=25^\circ C$  交织模式下进行，输出幅值为-3dBFS (Package: FCBGA380) :

图 6-22 有效位 VS 输入频率

图 6-23 无杂散动态范围 VS 输入频率

图 6-24 信噪比 VS 输入频率

图 6-25 信纳比 VS 输入频率

图 6-26 总谐波失真 VS 输入频率

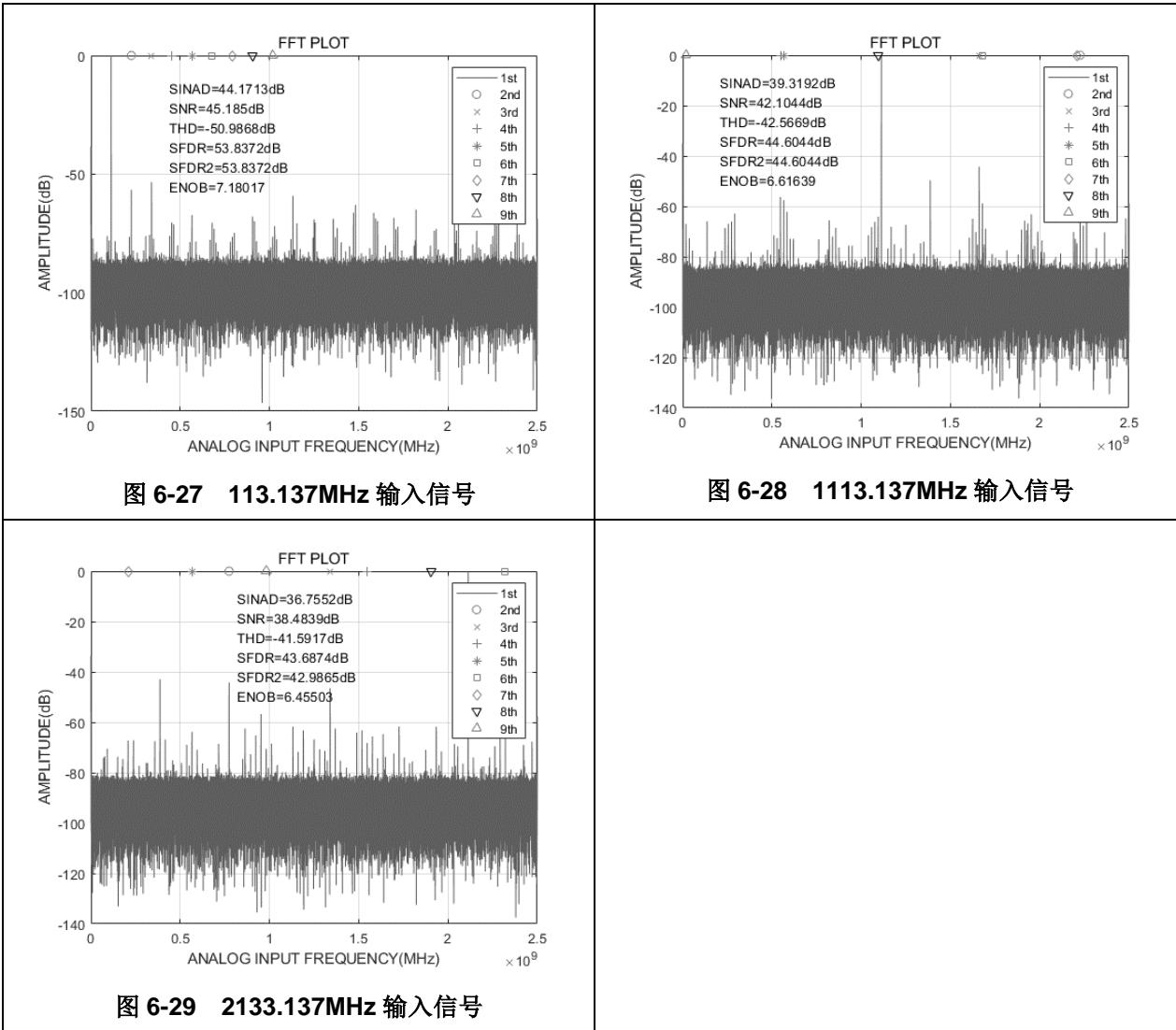

## 6.12 典型测试结果（续）

非特别注明，以下所有测量均在  $V_{CCT}=+4.5V$ ,  $V_{CCA}=+3.3V$ ,  $V_{CCD}=+3.3V$ ,  $V_{CCIO}=+1.8V$ ,  $f_{CLK}=2.5GHz$ ,  $T_A=25^\circ C$  交织模式下进行（Package: FCBGA380）：

## 7 产品详细描述

### 7.1 概述

AAD08D2500 芯片采用折叠内插结构设计，最高可达到 6.5 个有效比特位，折叠放大器的使用大大降低了比较器的数目和功率消耗。另外，片上校验也大大降低了折叠结构常见的积分非线性误差的曲线效应。这些共同造就了一个非常快速且高性能的转换器。

理想情况下，在转换器输入电压范围之内的模拟输入信号将在 1GSPS 到 5GSPS 的采样速率下被量化为 8 位数字信号。不管差分输入电压的哪端低于负的满量程电压还是高过正的满量程电压均会触发溢出位生效。

每个转换器都有一个可提供两路 LVDS 总线的 1: 2 多路输出选择器。每路总线的数据输出速率是 ADC 采样速率的一半，用户可以将其交织使用使数据输出速率达到转换器的全速。

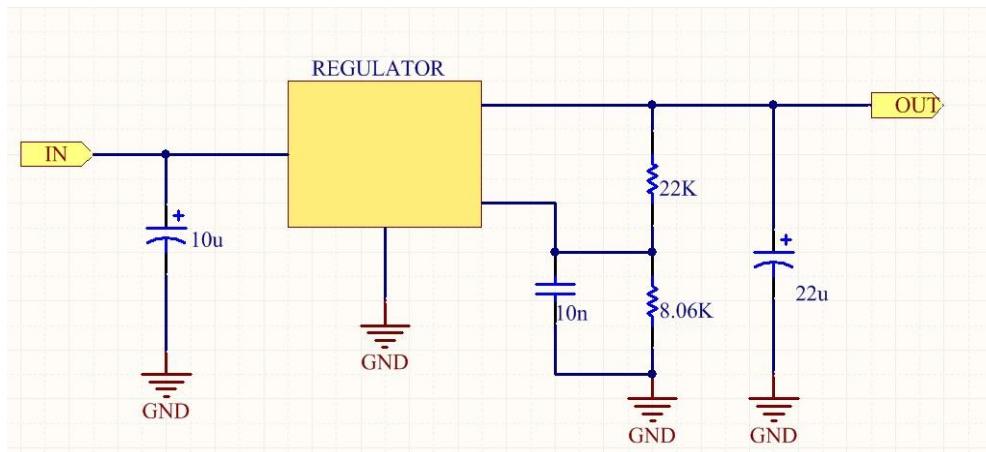

### 7.2 电源电压

如果没有合适的旁路，AD 转换器会招致足够污染自身电源的瞬时电流。在距离 AD 转换器电源引脚 1 英寸即 2.5 厘米之内需要放置一个  $22\mu F$  的电容。一个  $10nF$  和一个  $100pF$  的电容要尽可能的接近所有驱动引脚，最好在 0.5 厘米以内。无引脚贴片电容是首选，因为他们有较低的导线电感。

模拟驱动和数字驱动引脚应相互隔离以防止任何数字噪声和 ADC 的模拟部分耦合。

AAD08D2500 芯片规定的多个工作电压分别是  $+4.6V \pm 0.1V$  /  $+3.3V \pm 0.1V$  /  $+1.8V \pm 0.1V$ 。需要非常注意的是，如果芯片长期工作在稍高的电源驱动电压下，容易造成产品的寿命降低。

即使在上电和断电时，也要严格遵守最大有效值范围的要求。在电源打开和关闭时产生的电源脉冲会破坏 AAD08D2500 芯片。**错误！未找到引用源。** 提供了一种电源的过点保护方式。

除非提供一个很小的负载，很多线性稳压器都会在上电时产生一个输出脉冲。除非电源电压达到几百个毫伏，否则有源器件产生的电流会很小。因此除非给电源一个很小的负载，否则这将会导致产生一个可以破坏 AAD08D2500 芯片的上电脉冲。推荐的做法是选择一个低噪声的 LDO 电压稳压器来降低上电时的脉冲。

ADC 的多个电源域建议一起上电，考虑到综合供电效率和性能，通常我们推荐采用 DCDC 和 LDO 混合的方式为 ADC 芯片供电。

图 7-1 无脉冲电源方案应用

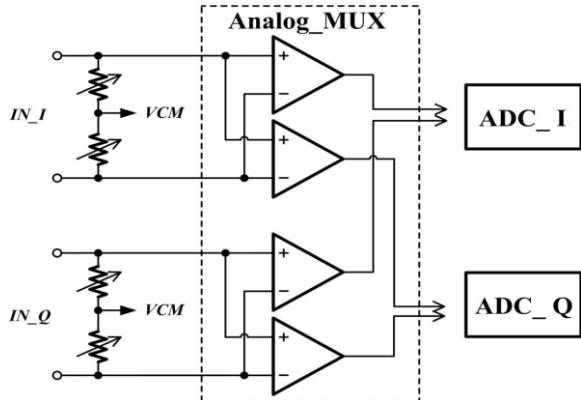

### 7.3 模拟输入

模拟输入的原理图如图所示，主要特性如下：

- 输入共模电平：1.8V

- 共模电平输出端口：1.8V

- 输入信号满幅差分摆幅：520mVpp

- 输入阻抗可调：40~60.5Ω

- 集成校准信号发生模块

- 可选择交织模式、双通道模式自动校准模式

图 7-2 模拟输入结构示意图

### 7.4 时钟输入

时钟为差分输入模式，内置 100 欧姆差分阻抗，需用 AC 耦合。

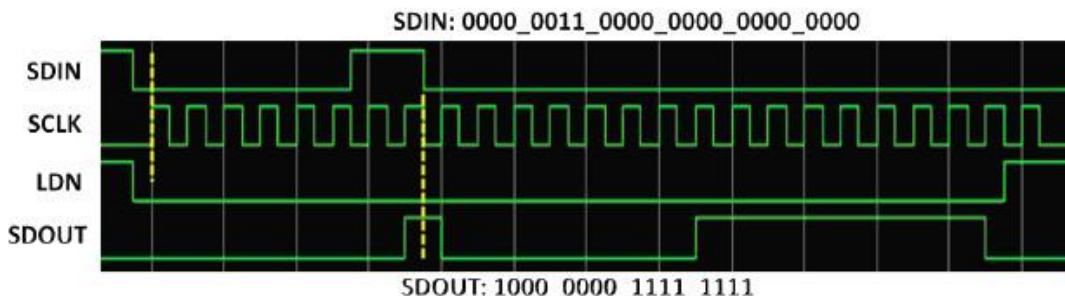

### 7.5 控制接口

- 标准 SPI 四线接口，外加 RESET 端口，接口电平 1.8V；

- RESET 端口为高电平时，ADC 内部寄存器重置为默认值（在复位状态时，ADC 仍可正常工作）；

- SDIN、SDOUT、SCLK、LDN 分别为串行输入、串行输出、串行时钟、加载信号，时序波形如下所示；

图 7-3 SPI 接口时序图

SPI 每次传输 24bits 数据，其中 1bit 为读/写标识位，7bits 为地址，16bits 为数据。如上图所示第一根黄虚线处，SDIN 在 SCLK 的上升沿采集第一个 bit 数据 0，第二根黄虚线处，SDOUT 在 SCLK 的下降沿发送第一个 bit 数据 1，SDOUT 在第 8 个 SCLK 上升沿后开始出现，输出 16bits 数据后结束，采集与发送均为 MSB 在前。LDN 为低时开启传输过程，SCLK 输出 24 个上升沿后 LDN 置高，SCLK 需再输出一个上升沿，此时写入的数据将加载到内部寄存器；LDN 为高时，任何输入都不会改变 ADC 内部寄存器；

控制命令格式：

- 总共 24bits 控制字 ({ A[7:0], D[15:0] } )，高位先发送低位后发送；

- 最高位为 R/W 指示位 (A[7])，1 表示写，0 表示读；

- 地址为 A[6:0]，最多支持 128 中命令。

## 7.6 寄存器表

### 7.6.1 寄存器表

| 地址[6:0] | 描述        |                                                                                | 读写  | 默认值    |

|---------|-----------|--------------------------------------------------------------------------------|-----|--------|

| 0x00    | ChipID    | 芯片 ID 及版本, D[15:8]为芯片类型, D[7:4]为子类, D[3:0]为版本                                  | R   | 0x0112 |

| 0x01    | Control   | 控制芯片采样模式及低功耗模式等                                                                | R/W | 0x0004 |

| 0x02    | Status    | 校准状态读取                                                                         | R   | -      |

| 0x03    | Delay     | D[7:0]:0x00~0xff, 输入时钟延时, 调节范围为 xx ps ~ xx ps, D[15]控制时钟延迟使能, 1 为使能, 0 为关闭 该功能 | R/W | 0x0000 |

| 0x04    | FineDelay | I/QADC 的采样时钟微调                                                                 | R/W | 0x8080 |

| 0x05    | Gain      | I/QADC 的增益微调                                                                   | R/W | 0x8080 |

| 0x06    | Offset    | I/QADC 的失调微调                                                                   | R/W | 0x8080 |

| 0x07    | ResAmp    | 输入阻抗调整 (D[3:0]), 输出 LVDS 幅度调整 (D[6:4])                                         | R/W | 0x0048 |

| 0x08    | CalCtrl   | 校准控制寄存器                                                                        | R/W | 0x0010 |

| 0x09    | IAutoCal  | 自动校准 I 路增益、失调                                                                  | W   | -      |

| 0x0a    | QAutoCal  | 自动校准 Q 路增益、失调                                                                  | W   | -      |

| 0x0b    | SkewCal   | 自动校准 I、Q 路时钟                                                                   | W   | -      |

| 0x0c    | AutoCal   | 开始一次全自动校准                                                                      | W   | -      |

| 0x0d    | CompDly   | 比较器时钟延迟, I 路 D[3:0], Q 路 D[7:4]                                                | W   | 0x0077 |

| 0x11    | InICal1I  | I_INL[15:0]                                                                    | W   | -      |

| 0x12    | InICal2I  | I_INL[31:16]                                                                   | W   | -      |

| 0x13    | InICal3I  | I_INL[47:32]                                                                   | W   | -      |

| 0x14    | InICal4I  | I_INL[63:48]                                                                   | W   | -      |

| 0x15    | InICal5I  | I_INL[74:64]                                                                   | W   | -      |

| 0x16    | InICa1Q   | Q_INL[15:0]                                                                    | W   | -      |

| 0x17    | InICa2Q   | Q_INL[31:16]                                                                   | W   | -      |

| 0x18    | InICa3Q   | Q_INL[47:32]                                                                   | W   | -      |

| 0x19    | InICa4Q   | Q_INL[63:48]                                                                   | W   | -      |

| 0x1a    | InICa5Q   | Q_INL[74:64]                                                                   | W   | -      |

| 0x1b    | Limit     | D[15:8]:high, D[7:0]:low                                                       | W   | -      |

| 0x1c    | GainTh    | D[7:0]:gain                                                                    | W   | 0xE3   |

| 0x20    | IntDly    | 读取内部时钟校准寄存器                                                                    | R   | -      |

| 0x21    | IntGain   | 读取内部增益校准寄存器                                                                    | R   | -      |

| 0x22    | IntOffset | 读取内部失调校准寄存器                                                                    | R   | -      |

| 0x23    | I_A, Q_A  | 读取 ADC 转换数值                                                                    | R   | -      |

| 0x24    | I_B, Q_B  | 读取 ADC 转换数值                                                                    | R   | -      |

说明：

IAutoCal 寄存器为 I 路的增益和失调自动校准，发任意值即可进行 I 路的增益和失调校准；

QAutoCal 寄存器为 Q 路的增益和失调自动校准，发任意值即可进行 Q 路的增益和失调校准；

SkewCal 寄存器为 I、Q 两路的时钟自动校准，发任意值即可进行 I、Q 两路的时钟校准；

AutoCal 寄存器为 IAutoCal 寄存器、QAutoCal 寄存器和 SkewCal 寄存器的组合，发任意值即可进行增益、

失调和时钟的校准。

Limit 寄存器为 Skew 校准的参考电平，其中低八位为参考低电平，高八位为参考高电平；

GainTh 寄存器位 Gain 阈值，默认值为 0xE3。

## 7.6.2 主要寄存器说明

### ➤ Control 控制寄存器

| 数据位    | 功能          | 数值  | 详细说明                    | 默认值   |

|--------|-------------|-----|-------------------------|-------|

| D[1:0] | InputMux 控制 | 00  | 输入 I 路至 IADC, I 路至 QADC | 2'b00 |

|        |             | 01  | 输入 Q 路至 IADC, I 路至 QADC |       |

|        |             | 10  | 输入 I 路至 IADC, Q 路至 QADC |       |

|        |             | 11  | 输入 Q 路至 IADC, Q 路至 QADC |       |

| D[2]   | 交织控制        | 0   | 两路 ADC 同时采样模式           | 1'b0  |

|        |             | 1   | 两路 ADC 交织模式             |       |

| D[5:4] | 休眠控制        | 00  | 全速模式                    | 2'b00 |

|        |             | 01  | I 路关闭, Q 路工作            |       |

|        |             | 10  | Q 路关闭, I 路工作            |       |

|        |             | 11  | 完全低功耗模式                 |       |

| D[6]   | 多芯片同步控制     | 0   | 关闭同步功能                  | 1'b0  |

|        |             | 1   | 打开同步功能                  |       |

| D[7]   | 同步控制        | 0   | 同步输入上升沿接收               | 1'b0  |

|        |             | 1   | 同步输入下降沿接收               |       |

| D[9:8] | 同步控制        | 0~3 | 内部同步时钟延迟, 1~4 个时钟周期     | 1'b0  |

| D[10]  | 输出时钟选择      | 0   | 输出时钟为 DDR 模式, 1/4 时钟    | 1'b0  |

|        |             | 1   | 输出时钟为 SDR 模式, 1/2 时钟    |       |

| D[11]  | 内部电路时钟选择    | 0   | 内部时钟选择 1/32 时钟          | 1'b0  |

|        |             | 1   | 内部时钟选择 1/16 时钟          |       |

| D[12]  | 内部时钟开关      | 0   | 内部时钟关闭                  | 1'b0  |

|        |             | 1   | 内部时钟打开                  |       |

| D[15]  | 测试码流开关      | 0   | 正常输出模式                  | 1'b0  |

|        |             | 1   | 输出特定的数据码流               |       |

➤ CalCtrl 寄存器

| 数据位    | 功能       | 数值  | 详细说明                                 | 默认值   |

|--------|----------|-----|--------------------------------------|-------|

| D[1:0] | 校准模式     | 00  | 手动失调校准模式                             | 2'b00 |

|        |          | 01  | 手动增益校准模式                             |       |

|        |          | 10  | 手动时序校准模式                             |       |

| D[2]   | 手动校准开关   | 0   | 手动校准关闭                               | 1'b0  |

|        |          | 1   | 手动校准打开（内部产生校准信号）                     |       |

| D[3]   | 选通内部校准开关 | 0~1 | 1 表示选通内部校准寄存器                        | 1'b0  |

| D[5:4] |          | 0~3 | 内部校准电路频率控制                           | 2'b01 |

| D[7:6] | 欠采样模式开关  | 0~3 | 0 表示普通模式，1 表示始终开启欠采样模式，2 表示始终关闭欠采样模式 | 2'b00 |

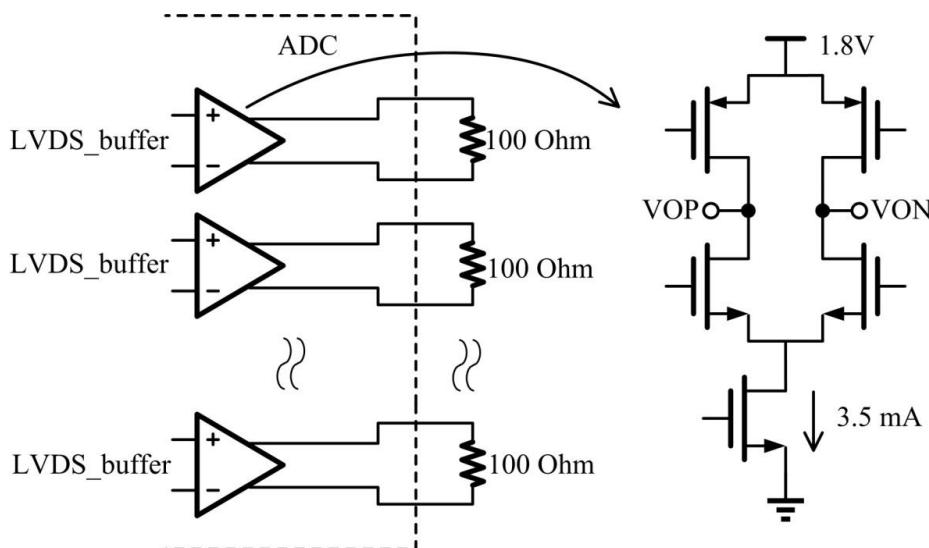

## 7.7 数字输出

LVDS 数字输出原理图如图所示，主要特性如下：

- 输出信号共模电平典型值：1.25V

- 输出信号摆幅典型值：350mVpp

- 输出摆幅可调：270mV~400mV

图 7-4 LVDS 输出电路原理图

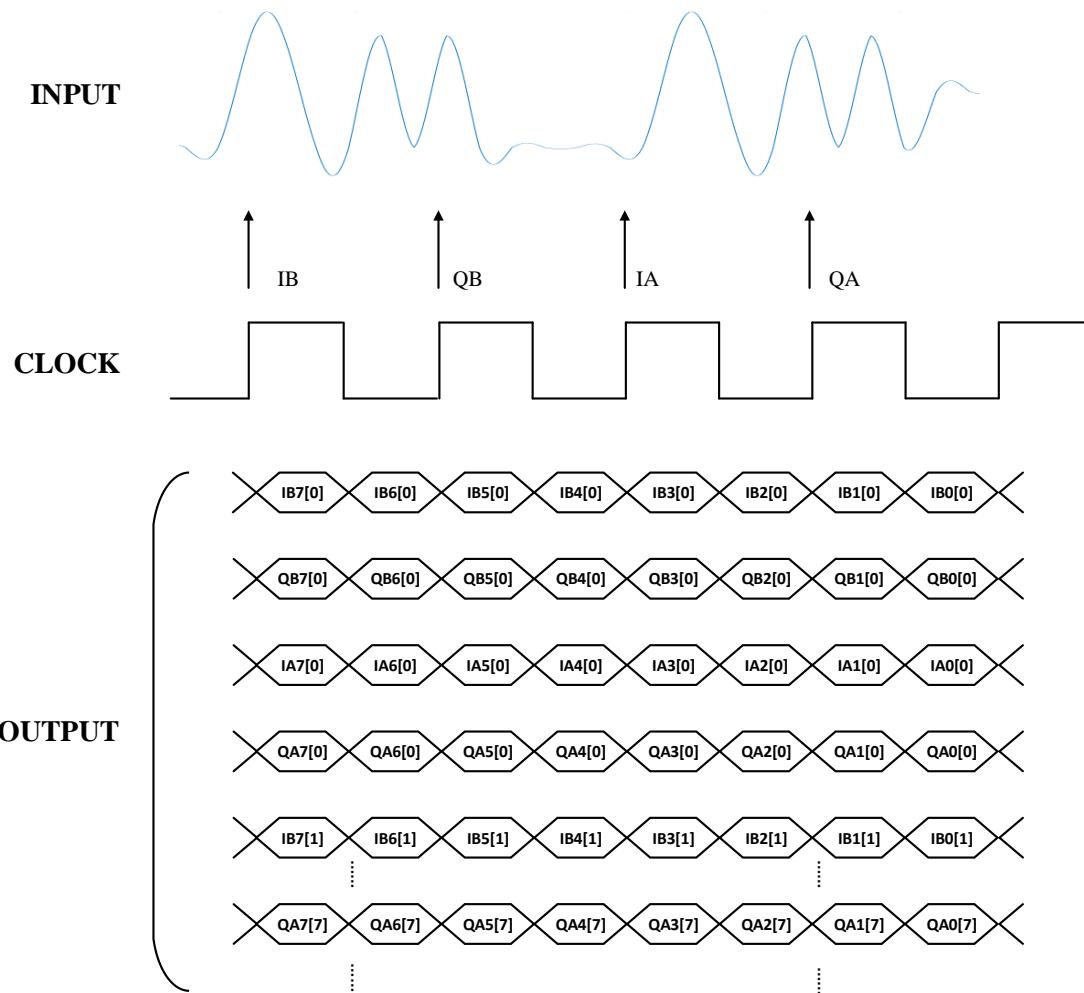

ADC 交织输入信号和输出信号时序如下图所示：

图 7-5 ADC 输入输出时序图

## 7.8 校准

AAD08D2500 可提供手动校准和自动校准两种模式，在交织和非交织模式下均可以校准两路通道之间的增益、失调和时钟误差。

FineDelay、Gain、Offset 寄存器说明：高 8 位控制 Q 路，低 8 位控制 I 路，FineDelay 寄存器越大延迟越大，调节范围约为 $\pm 20\text{ps}$ ，Gain 约为 $\pm 10\%$ ，Offset 约为 $\pm 10\text{LSB}$ 。

### 7.8.1 芯片内置的自动校准模式

启用自动校准模式需要将 CalCtrl 寄存器的 D[3]置 1，来选通内部校准寄存器；将 Control 寄存器的 D[12]置 1，来使能内部校准电路的时钟，同时将 Control 寄存器的 D[1:0]、和 D[2]按正确的需求进行配置，其他均保持默认值即可。

然后，可以通过配置 0x09、0x0a、和 0x0b 寄存器来进行自动校准。

实际测试表明，发送 0x09、0x0a 自动校准命令后，增益误差、失调误差仍然存在，校准效果不理想；发送 0x0b 自动校准命令后，时钟误差几乎被消除，校准效果较好。

0x0c 命令相当于 0x09、0x0a、0x0b 三个命令的组合，实测效果与单独校准的三个命令相差无几。

理论上，对于本芯片，最好的方式是采用手动方式校准增益误差、失调误差，自动方式校准时钟误差。然而，自动校准模式下，Gain、Offset、FineDelay 寄存器均采用 ADC 内部产生的数值，所以无法在自动校准模式下人工改变 Gain、Offset 寄存器。

解决方式是先发送 0x09 命令，校准时钟误差后，再发送 0x20 命令回读内部 FineDelay 的数值，再切换到手动校准模式下（CalCtrl 寄存器的 D[3]置 0），发送 0x04 命令将读回的数值写入 FineDelay 寄存器，此时再手动修改 Gain、Offset 寄存器。

### 7.8.2 芯片内置的手动校准模式

Control 寄存器的 D[12]置 1 或置 0 均可，CalCtrl 寄存器的 D[3]置 0（选择外部输入的校准寄存器）。

ADC 各个子通道之间存在很多差异，如：失调误差、增益误差，采样时间间隔误差等，这些差异严重制约交织 ADC 的转换精度，因此要对这些通道间的失配进行校准。该模块主要是对三种失配误差校准算法的实现，三种算法各自独立，互不影响。三种失配误差的详细介绍及校准算法请查看文章《基于 FPGA 的超高速时间交织 ADC 后台校准技术》。

FPGA 逻辑根据 ADC 采集转换后的数字信号，分别依据不同失配误差的校准算法实时计算出误差值，以 CMD 形式传给 SPI\_CTRL，而后实时发送给 ADC 芯片，直至收敛校准完成。三种校准方法对应的 SPI 命令地址为 0X06、0X05、0X04，其中在对增益失配误差和时间间隔失配误差进行校准时，需要固定一路，I 路或者 Q 路作为基准，去校准另外一路，所以在 5G/8bit ADC 测试逻辑中会看见在发送校准命令时，固定了 I 路，发送默认值 0X80，然后去校准 Q 路。

通常可外部输入数个固定电压来校准增益、失调，输入正弦波来校准时钟误差，也可以直接输入正弦波来校准增益、失调、时钟误差三项误差。

### 7.8.3 外部辅助的手动校准模式

Control 寄存器的 D[12]置 1 或置 0 均可，CalCtrl 寄存器的 D[3]置 0（选择外部输入的校准寄存器），CalCtrl 寄存器的 D[7: 6]置为 2，CalCtrl 寄存器的 D[2]置 1。

CalCtrl 寄存器的 D[1: 0]用于控制该模式下的子模式：

2'b00：用于失调校准，此时 ADC 将采集芯片内部产生的零点电压，正常输出应当为 0x80，如果不是则通过 0x06 命令修改 Offset 寄存器来校准。（补充说明：实测表明，该模式下内部产生的零点电压不是很准，实际应用时，建议保持 I 或 Q 路 Offset 寄存器不变，改变 Q 或 I 路的 Offset 寄存器，使得 I、Q 采集到的数值相等。）

2'b01：用于增益校准，此时 ADC 将采集芯片内部产生的固定电压，正常输出应当为 0xE3，如果不是则通过 0x05 命令修改 Gain 寄存器来校准。（补充说明：实测表明，该模式下内部产生的固定电压不是很准，实际应用时，建议保持 I 或 Q 路 Gain 寄存器不变，改变 Q 或 I 路的 Gain 寄存器，使得 I、Q 采集到的数值相等。）

2'b10：用于时钟误差校准，此时 ADC 将采集芯片内部产生的三角波，CalCtrl 寄存器 D[5: 4]用于控制三

角波的频率，通常采用默认值即可，FPGA 获取到 ADC 抓取的数据再经过自定义的算法来校准 ADC 的时钟误差。（补充说明：实际应用时，也可以在该模式下校准失调和增益误差，通过判断三角波的平均值校准失调，判断三角波的幅度来校准增益。）

补充说明：采用此种方式校准失调、增益、时钟误差后，可能最终仍存在少许误差，原因是 ADC 芯片内部产生校准用波形的电路和 ADC 物理上的输入引脚之间仍有一部分有源电路，该部分电路所产生少许误差在该种模式下无法消除。

## 7.9 数据同步

经 ADC 转换后输入 FPGA 的 34 路数据需要进行数据同步，在同步之前首先要将芯片的输出模式配置为 pattern 模式，此时，ADC 芯片输出特定的数据码流。

为了对应 ADC 芯片 I/Q 两路输出的 A 路、B 路以及溢出位 OR 的 pattern 码流，在编码过程中分别定义了三种 pattern 码流。

```

patternA = 16'b0101_0101_1010_1010;

```

```

patternB = 16'b1010_1011_0101_0100;

```

```

patternOR = 16'b1111_1111_1111_1110.

```

## 7.10 片间同步

AAD08D2500 支持片间同步，此时，SYNCIN\_P/N 需要一个持续的低频时钟信号输入。由于，该信号可能会对主时钟信号造成干扰，从而引入新的杂散。因此，如果对 ADC 的性能需求较高，建议不要开启片间同步功能。不启用同步功能时，建议将 SYNCIN\_P 端接一个  $1\text{K}\Omega$  电阻到地，SYNCIN\_N 端接  $2\text{K}\Omega$  电阻到 $+3.3\text{V}$  电源。

一个变通的方案是：先开启片间同步功能，并给 SYNCIN 输入所需的信号，在完成片间同步后，将同步功能关闭，最后将 SYNCIN 端输入的信号也关闭。即可避免 SYNCIN 信号对主时钟产生干扰。这可以通过在主从芯片 SYNC 信号链路中添加一个 LVDS 电平与门或 MUX 来实现。

## 7.11 热能管理

AAD08D2500 芯片相对于它的高速度来说，本身的性能表现令人印象深刻。但是不管怎么说它的功耗仍然足够高，因此不得不额外关注它的热能管理。为了可靠性的原因，芯片必须保证最高不超过  $120^\circ\text{C}$ 。这就是说，环境温度 (TA) 加上功耗乘以 ADC 的热阻系数之和必须低于  $120^\circ\text{C}$ 。这就意味着如果保证环境温度按照额定工作范围的要求最高不超过  $85^\circ\text{C}$ ，那么这将没有任何问题。

为了便于用户使用，AAD08D2500 芯片内部包含一个热量二极管来帮助测量温度。但是该二极管没有任何特性描述，而且迅芯微电子也无法提供任何有关于其特性的信息。因此当使用该二极管时，无法获得任何有关温度精度的有效信息。

以下是将裸焊盘安装于 PCB 上时的基本建议。这应当被视作是印刷电路板和装配工艺开发的起点，建议可根据以往的装配经验来开发该流程。

AAD08D2500 芯片的封装底部有一个裸焊盘，提供了主要的散热途径以及跟印刷电路板之间的良好的电气接地。连接到印刷电路板上的焊盘焊接区与常规的 LQFP 封装一样，但是该裸焊盘必须连接到电路板上以尽可能的散去封装内的热量，来确保产品最佳性能参数。

为了尽最大的可能散去封装内的热量，导热焊盘焊接区必须将电路板和封装引脚糅合在一起。芯片的裸焊盘必须被焊接上以确保可以从封装内传导出足够的热量。该裸焊盘的焊接区应该至少有 10X10mm 的大小，且被焊接住的该芯片的裸焊盘应该是全部的热传导焊接区。该热传导焊接区应从电气上接地，该焊接区和封装的装配引脚之间至少要有 2mm 的明显的间隙。

由于单个的一个大开孔可能会导致较差的热能释放，因此可将其细分为直径较小的孔的阵列，形状则类似于焊接区的形状。

为了使结温降到最低，建议在电路板上安装一个散热片，这包括在电路板的反面做一个大约 2 平方英寸（6.5 平方厘米）的铜金属区。该区域可以采用镀覆或者焊覆来防止腐蚀，但是不能采用保行涂层，因为这将会造成散热不良。应使用导热通孔将电路板的正反面铜金属区连接起来，这些通孔可以作为导热管将热量从芯片所在面传递到电路板的另一面来更加有效地散热。导热通孔的数量推荐 100 到 169 个为佳。

导热通孔的放置应该是 1.2mm 网格间距，孔径在 0.3mm 到 0.33mm 之间。这些通孔均需要滚镀以防止在焊接过程中焊锡材料进入其中，因为这可能会导致芯片裸焊盘和电路板热焊接区之间产生焊锡空洞。这些空洞会提高芯片和电路板热焊接区的热阻系数，使芯片工作时热量更大。

如果希望监控芯片的结温，可以将温度传感器安装在电路板的散热片上尽可能靠近导热通孔的区域。温度传感器和 AAD08D2500 芯片之间存在一个热阻系数  $\theta_{J-PAD}$  乘以标准功耗的温度差，值为  $5.5^{\circ}\text{C}/\text{W} \times 4.2\text{W} = 23.1^{\circ}\text{C}$ 。加上焊盘和温度传感器之间的温差。这就意味着将焊盘温度维持在 95°C 时将确保芯片温度不超过 120°C，该假定是建立在确保芯片完美焊接且导热通孔足够胜任的基础上的。（上述计算中温度传感器的不精确性须另计。）

## 8 封装和订购信息：

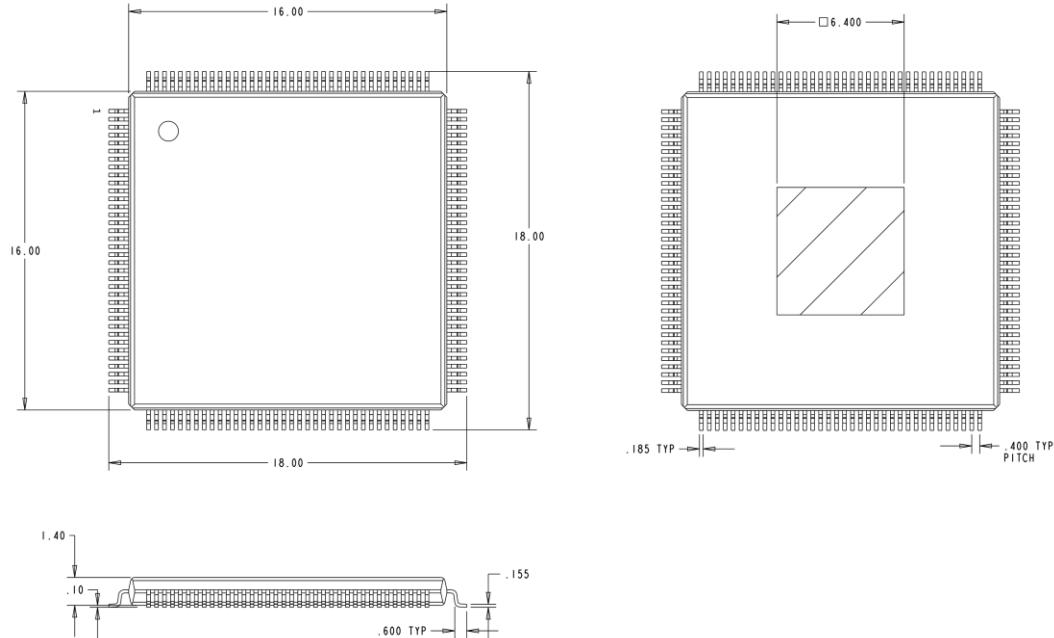

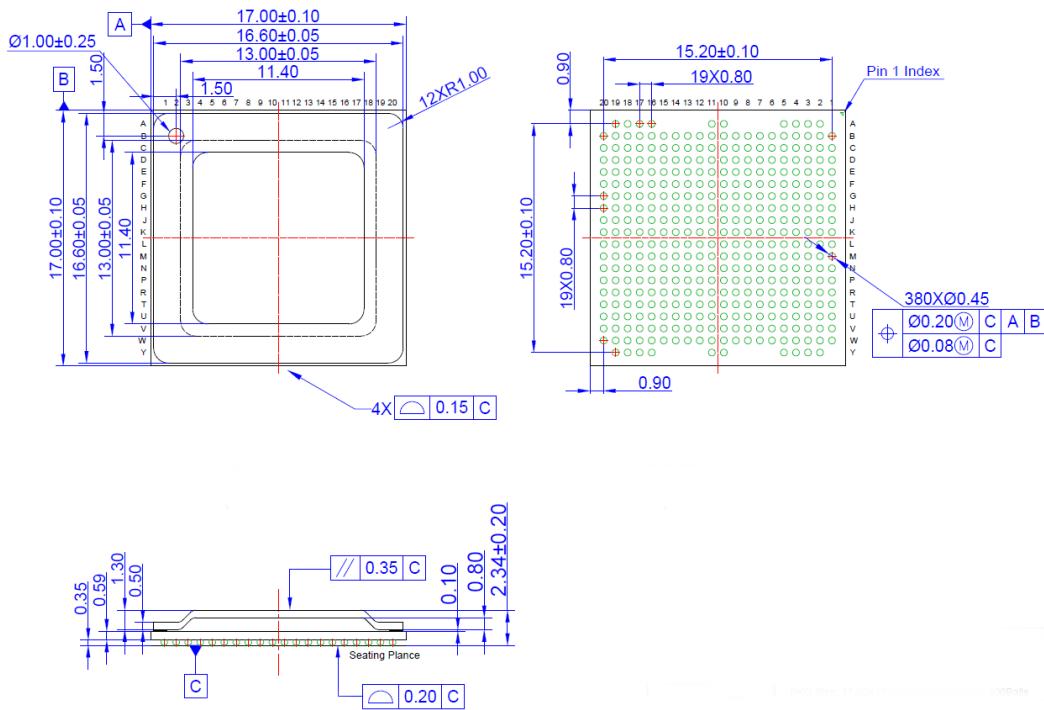

| 封装                  | 温度范围(芯片壳温)  | 输出接口 | 封装描述                     |

|---------------------|-------------|------|--------------------------|

| AAD08D2500_LQFP144  | -40°C~+85°C | LVDS | 144 引脚薄型四方扁平封装<br>(LQFP) |

| AAD08D2500_FCBGA380 | -40°C~+85°C | LVDS | BGA380_17x17             |

图 8-1 AAD08D2500\_LQFP144 封装示意图

注：1、所有单位均为 mm。

2、芯片底部的裸焊盘必须在焊接时接地以保证芯片的性能可靠。

图 8-2 AAD08D2500\_FCBGA380 封装示意图

## 9 修订版次

| 版本信息                                | 日期 | 版本号    |

|-------------------------------------|----|--------|

| 初始版本                                |    | Rev1.0 |

| 明确时钟分频信息                            |    | Rev1.1 |

| 更正热能管理章节的热阻值                        |    | Rev1.2 |

| 增加 ADC 输入输出时序图                      |    | Rev1.3 |

| 更新 ADC 芯片输入满摆幅                      |    | Rev1.4 |

| 增加 ADC 芯片电性特征                       |    | Rev1.5 |

| 更新自动校准部分内容                          |    | Rev1.6 |

| 增加上电顺序说明                            |    | Rev1.7 |

| 更新管脚 SYNCIN_P/N 的顺序                 |    | Rev1.8 |

| 增加片间同步的说明                           |    | Rev1.9 |

| 更正芯片工作电流及功耗                         |    | Rev2.0 |

| 增加 FCBGA380 封装相关尺寸信息、管脚定义信息以及典型测试数据 |    |        |

| 增加封装热阻和 ESD 信息                      |    |        |

|                                     |    |        |

|                                     |    |        |

|                                     |    |        |

## 10 声明

迅芯微电子（苏州）股份有限公司及其分公司和经销商有权对其公司提供的半导体产品进行修正、增强、提高及做出其他的改变。同时也拥有在最新版产品已经发布的基础上，中止任何一款产品和服务的权利。购买者应在下单前获取相关的最新信息，并确认这些信息的有效性和完整性。所有售出的半导体产品都必须遵循迅芯微电子（苏州）股份有限公司在接到订单确认时的销售条款和条件。

根据迅芯微电子（苏州）股份有限公司销售的半导体产品的保修条款，迅芯微电子（苏州）股份有限公司担保器件的性能规范适用于销售之时。本公司采取了必要的测试和质量控制手段来支持产品达到这样的品质。除非有法律的具体规定，否则并不是每个器件的所有参数都是必须要执行测试的。

迅芯微电子（苏州）股份有限公司对购买者使用产品做出的设计和应用不承担任何的连带责任，购买者应对使用了迅芯微电子（苏州）股份有限公司器件的产品和应用自负其责。并应采取适当的设计或操作时的具体保护措施来使您所设计的产品风险降至最低。

对于任何使用迅芯微电子（苏州）股份有限公司的器件和服务的所有相关的组合、设备或过程，迅芯微电子（苏州）股份有限公司不保证或代表许可——无论是明示或暗示——授予其使用任何相关的专利权、版权或其他任何知识产权。迅芯微电子（苏州）股份有限公司对第三方产品或服务不构成许可使用这些产品或服务的保修或背书。使用这样的信息可能需要从第三方的专利或第三方的其他知识产权获得许可或授权，或从迅芯微电子（苏州）股份有限公司获得专利和其他知识产权的授权。

从迅芯微电子（苏州）股份有限公司的数据手册中复制重要的章节是被允许的，只要复制时没有更改，同时附上所有相关的担保、条件、限制和告示信息。迅芯微电子（苏州）股份有限公司不对这些修改后的文件承担责任，第三方的信息可能会受到附加条件的约束。

超出迅芯微电子（苏州）股份有限公司所标明的器件或服务的参数范围或在与之不同参数下转售苏州迅芯微电子的器件或服务，或对迅芯微电子（苏州）股份有限公司的器件或服务无法提供有效服务并且暗含担保无效的行为，都是一种不公平且带有欺骗性质的商业行为。迅芯微电子（苏州）股份有限公司不为这样的声明承担责任。

购买者应确认并同意，尽管迅芯微电子（苏州）股份有限公司可能提供了与应用相关的信息或支持，但您将自行负责遵守与您的产品以及在应用中使用任何迅芯微电子（苏州）股份有限公司的器件有关的所有法律、法规和安全方面的要求。购买者应表示并同意您具备所有必要的专业知识，能够创建和实施安全措施以预测故障的危险后果、监控故障及其后果、降低可能导致伤害的故障的可能性并采取适当的补救措施。购买者将全额赔偿因在重大的安全应用中使用任何迅芯微电子（苏州）股份有限公司器件而对迅芯微电子（苏州）股份有限公司及其所代表方造成的所有损失。

在某些情况下，为了推广安全相关应用，有可能对迅芯微电子（苏州）股份有限公司的器件进行专门提升。借助于这样的器件，迅芯微电子（苏州）股份有限公司的目标旨在帮助客户设计和创立其特有的可满足功能性安全标准和要求的终端产品解决方案。尽管如此，此类器件仍然遵守本条款。