## 产品特点

- 输入带宽: 450MHz

- 采样率: 1GSps/500MSps/250MSps

- 输入满量程: 差分峰峰值 1.6V

- 输出接口: LVDS

- 输入接口内置 4X4 MUX, 支持各种选通模式

## 产品描述

AAD12Q0250 是采用 CMOS 工艺制造的高速模数转换芯片。该芯片可将宽带输入模拟信号转换为数字，并通过标准的 LVDS 接口输出。输入信号差模满量程峰峰值为 1.6V，输出 12 路 1Gbps 的 LVDS 信号。芯片通道数可配置，支持 1/2/4 通道模式；模拟输入选通方案可配置，任意一路模拟输入可以加载到任意一路子 ADC。电源电压采用 1.8V/1.9V 供电，总功耗约为 900mW，采用 pitch 为 0.4mm 的 QFN-

128 封装。

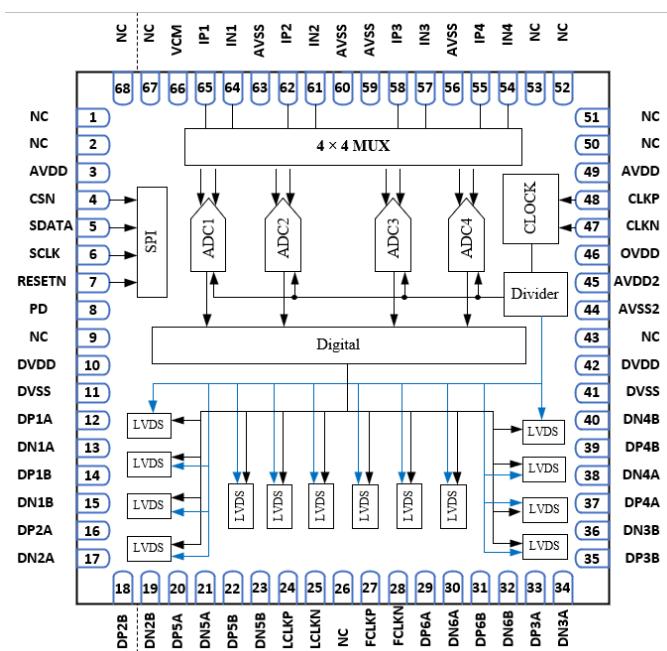

## 产品功能结构框图

68 封装。可以在[-40°C, +85°C]工业级温度环境中正常工作。

应用范围

- 激光雷达

- 示波器

- 高速数据采集

主要性能指标

- 分辨率: 12Bits

- 最高转换速率: 1GSps

- ENOB: 9.5@250MHz (子 ADC 性能)

9.5@500MHz (子 ADC 性能)

9.0@1GHz (子 ADC 性能)

- SFDR: 70@250MHz (子 ADC 性能)

70@500MHz (子 ADC 性能)

63@1GHz (子 ADC 性能)

- 功耗: 0.9W

图 1：产品功能结构框图

## 目录

|                  |    |

|------------------|----|

| 产品特点.....        | 1  |

| 产品描述.....        | 1  |

| 应用范围.....        | 1  |

| 主要性能指标.....      | 1  |

| 产品功能结构框图.....    | 1  |

| 目录 .....         | 2  |

| 封装尺寸信息: .....    | 3  |

| 引脚分布及功能描述: ..... | 4  |

| 推荐工作条件: .....    | 7  |

| 转换器电气性能指标: ..... | 7  |

| 典型测试结果: .....    | 9  |

| 绝对最大额定值: .....   | 10 |

| 封装热阻: .....      | 10 |

| 产品详细描述: .....    | 11 |

| 1 控制接口.....      | 11 |

| 2 寄存器描述.....     | 16 |

| 3 初始化流程.....     | 24 |

| 4 数字输出.....      | 25 |

| 5 接口同步.....      | 26 |

| 6 片间同步.....      | 26 |

| 7 模拟输入.....      | 27 |

| 8 时钟输入.....      | 27 |

| 订购信息: .....      | 28 |

| 版本记录: .....      | 29 |

| 声明 .....         | 30 |

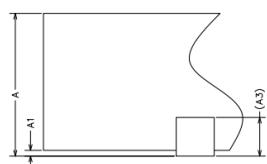

**封装尺寸信息：**

**AAD12Q0250**

图 2: AAD12Q0250 芯片封装图

注：（1）、本图中所有尺寸请参照下表，单位均为mm。

（2）、芯片底部的裸焊盘必须在焊接时接地以保证芯片的性能可靠。

表 1: AAD08Q0250芯片封装尺寸信息

| SYMBOL | MIN     | NOM  | MAX  |

|--------|---------|------|------|

| A      | 0.70    | 0.75 | 0.80 |

| A1     | 0       | 0.02 | 0.05 |

| A3     | 0.20REF |      |      |

| b      | 0.15    | 0.20 | 0.25 |

| D      | 7.90    | 8.00 | 8.10 |

| E      | 7.90    | 8.00 | 8.10 |

| D2     | 6.10    | 6.20 | 6.30 |

| E2     | 6.10    | 6.20 | 6.30 |

| e      | 0.30    | 0.40 | 0.50 |

| K      | 0.20    | -    | -    |

| L      | 0.35    | 0.40 | 0.45 |

| R      | 0.09    | -    | -    |

**AAD12Q0250**

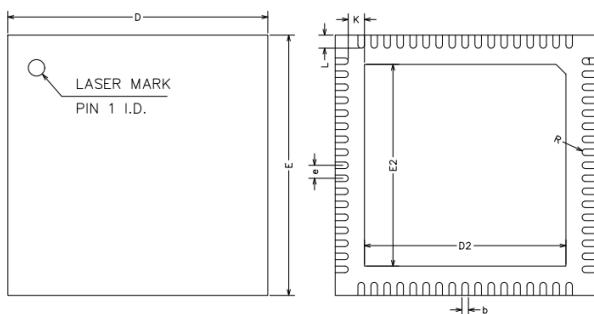

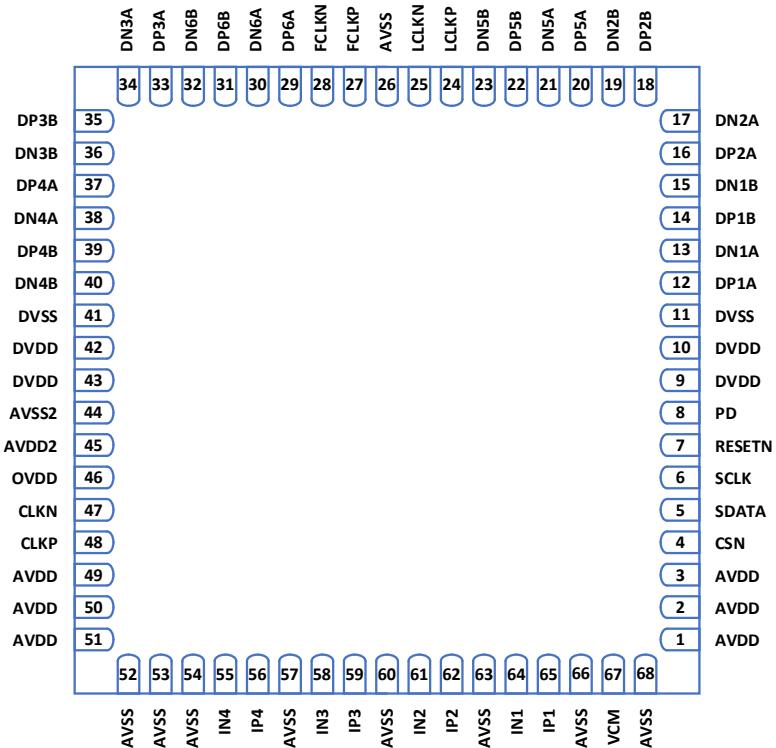

### 引脚分布及功能描述：

图 3：芯片引脚排列图（顶视图）

| 编号                         | 引脚名称  | 功能    | 备注   |

|----------------------------|-------|-------|------|

| 26,52,53,54,57,60,63,66,68 | AVSS  | 模拟地   | 0V   |

| 11,41                      | DVSS  | 数字地   | 0V   |

| 1,2,3,49,50,51             | AVDD  | 模拟电源  | 1.9V |

| 9,10,42,43                 | DVDD  | 数字电源  | 1.8V |

| 45                         | AVDD2 | 模拟电源  | 1.8V |

| 44                         | AVSS2 | 模拟地   | 0V   |

| 46                         | OVDD  | IO 电源 | 1.8V |

AAD12Q0250

| 编号    | 引脚名称      | 功能           | 备注                 |

|-------|-----------|--------------|--------------------|

| 24    | LCLKP     | LVDS 数据时钟正端  | 数据随路时钟             |

| 25    | LCLKN     | LVDS 数据时钟负端  |                    |

| 27    | FCLKP     | LVDS 数据帧时钟正端 | 数据帧时钟              |

| 28    | FCLKN     | LVDS 数据帧时钟负端 |                    |

| 47    | CLKN      | 时钟输入负端       | 集成 100ohm<br>差分电阻， |

| 48    | CLKP      | 时钟输入正端       |                    |

| 4     | CSN       | 片选信号，低有效     | SPI 接口控制<br>信号     |

| 5     | SDATA     | SPI 数据       |                    |

| 6     | SCLK      | SPI 时钟       |                    |

| 7     | RESETN    | SPI 复位，低有效   |                    |

| 8     | PD        | 掉电控制信号，高有效   |                    |

| 67    | VCM       | 共模电压信号，输出    | 0.9V               |

| 12/13 | DP1A/DN1A | 通道 1 差分输出端口  | LVDS 差分输出<br>数据端口  |

| 14/15 | DP1B/DN1B | 通道 1 差分输出端口  |                    |

| 16/17 | DP2A/DN2A | 通道 2 差分输出端口  |                    |

| 18/19 | DP2B/DN2B | 通道 2 差分输出端口  |                    |

| 20/21 | DP5A/DN5A | 通道 5 差分输出端口  |                    |

| 22/23 | DP5B/DN5B | 通道 5 差分输出端口  |                    |

AAD12Q0250

| 编号    | 引脚名称      | 功能          | 备注      |

|-------|-----------|-------------|---------|

| 29/30 | DP6A/DN6A | 通道 6 差分输出端口 | 差分输入信号端 |

| 31/32 | DP6B/DN6B | 通道 6 差分输出端口 |         |

| 33/34 | DP3A/DN3A | 通道 3 差分输出端口 |         |

| 35/36 | DP3B/DN3B | 通道 3 差分输出端口 |         |

| 37/38 | DP4A/DN4A | 通道 4 差分输出端口 |         |

| 39/40 | DP4B/DN4B | 通道 4 差分输出端口 |         |

| 64/65 | IN1/IP1   | 通道 1 差分输入端口 |         |

| 61/62 | IN2/IP2   | 通道 2 差分输入端口 |         |

| 58/59 | IN3/IP3   | 通道 3 差分输入端口 |         |

| 55/56 | IN4/IP4   | 通道 4 差分输入端口 |         |

| 0     | EPAD      | 中心焊盘        | 必须可靠接地  |

本产品内置防静电保护装置有限，为了防止静电损坏门电路，在储存或处理过程中应使引脚短接在一起或将产品放置在导电泡沫材料中。

AAD12Q0250

### 推荐工作条件：

| 参数      | 最小值  | 标准值 | 最大值 | 单位  |

|---------|------|-----|-----|-----|

| 时钟频率    | 0.5  | 1   | 1.1 | GHz |

| AVDD    | 1.85 | 1.9 | 2.0 | V   |

| AVDD2   | 1.7  | 1.8 | 2.0 | V   |

| DVDD    | 1.75 | 1.8 | 2.0 | V   |

| OVDD    | 1.75 | 1.8 | 2.0 | V   |

| I-AVDD  | -    | 305 | -   | mA  |

| I-AVDD2 | -    | 15  | -   | mA  |

| I-DVDD  | -    | 180 | -   | mA  |

| I-OVDD  | -    | 5   | -   | mA  |

### 转换器电气性能指标：

以下规格适用于  $T_A=+25^\circ\text{C}$ , AVDD= +1.9V , AVDD2 = +1.8V, DVDD&OVDD = +1.8V。除非另行说明所有其他的界限均适用于温度  $T_A = 25^\circ\text{C}$ 。

| 参数       | 最小值       | 典型值 | 最大值       | 单位   |

|----------|-----------|-----|-----------|------|

| 最高采样率    | 1         | 1.1 | -         | GS/s |

| 功耗       |           | 0.9 |           | W    |

| 有效位数     |           | 12  | -         | Bit  |

| 模拟输入带宽   |           | 450 |           | MHz  |

| 失调误差     | $\pm 0.5$ |     | $\pm 1.0$ | LSB  |

| 积分非线性误差  | $\pm 3$   |     | $\pm 4$   | LSB  |

| 微分非线性误差  | $\pm 0.5$ |     | $\pm 1.5$ | LSB  |

| 模拟输入共模电压 |           | 0.9 |           | V    |

| 带隙基准输出电压 | 0.85      | 0.9 | 0.95      | V    |

| 逻辑输入高电平  | 1.8       |     |           | V    |

| 逻辑输入低电平  |           |     | 0         | V    |

| 数字输出高电平  | 1.25      |     |           | V    |

| 数字输出低电平  |           |     | 0.82      | V    |

迅芯微电子（苏州）股份有限公司保密信息，未经允许禁止传播！

AAD12Q0250

|                     |    |     |    |   |

|---------------------|----|-----|----|---|

| 模拟差分输入电阻            | 48 |     | 50 | Ω |

| 差分输入满量程<br>(差分峰峰值)  | -  | 1.6 | -  | V |

| 输入端共模电压             | -  | 0.9 |    | V |

| 输入时钟信号幅度<br>(差分峰峰值) |    | 1.2 |    | V |

### 典型测试结果：

除非另有说明, AVDD = 1.9V, AVDD2 = 1.8V, DVDD = 1.8V, OVDD = 1.8V, 50%时钟占空比, -1dB 70MHz 输入信号, 增益 = 1X。

| 性能参数                  | 描述                 | 最小值 | 典型值  | 最大值 | 单位   |

|-----------------------|--------------------|-----|------|-----|------|

| SNR                   | 信噪比, 不包括交错杂散       |     |      |     |      |

|                       | 单通道模式, Fs=1000MSPS | -   | 58.8 | -   | dBFS |

|                       | 双通道模式, Fs=500MSPS  | -   | 59.8 | -   | dBFS |

|                       | 四通道模式, Fs=250MSPS  | -   | 59.3 | -   | dBFS |

| SINAD <sub>incl</sub> | 信纳比, 包括交错杂散        |     |      |     |      |

|                       | 单通道模式, Fs=1000MSPS | -   | 43.5 | -   | dBFS |

|                       | 双通道模式, Fs=500MSPS  | -   | 56.6 | -   | dBFS |

|                       | 四通道模式, Fs=250MSPS  | -   | 59.3 | -   | dBFS |

| SFDR <sub>incl</sub>  | 无杂散动态范围, 包括交错杂散    | -   |      | -   |      |

|                       | 单通道模式, Fs=1000MSPS | -   | 44.6 | -   | dBc  |

|                       | 双通道模式, Fs=500MSPS  | -   | 61.2 | -   | dBc  |

|                       | 四通道模式, Fs=250MSPS  | -   | 61.3 | -   | dBc  |

| SFDR <sub>excl</sub>  | 无杂散动态范围, 不包括交错杂散   |     |      |     |      |

|                       | 单通道模式, Fs=1000MSPS | -   | 63   | -   | dBc  |

|                       | 双通道模式, Fs=500MSPS  | -   | 70.4 | -   | dBc  |

|                       | 四通道模式, Fs=250MSPS  | -   | 68.8 | -   | dBc  |

| ENOB <sub>excl</sub>  | 有效位数, 不包括交织杂散      |     |      |     |      |

|                       | 单通道模式, Fs=1000MSPS | -   | 9.0  | -   | Bits |

|                       | 双通道模式, Fs=500MSPS  | -   | 9.5  | -   | Bits |

|                       | 四通道模式, Fs=250MSPS  | -   | 9.3  | -   | Bits |

Acela

Micro

迅芯微电子（苏州）股份有限公司保密信息，未经允许禁止传播！

AAD12Q0250

### 绝对最大额定值：

注意，超出绝对最大额定值可能会导致器件永久性损坏。绝对最大额定值仅代表产品的压力等级，不作为实现产品功能的工作条件的限值，超过本规范中推荐工作条件章节的限值均是不推荐的行为。长期在绝对最大额定值条件下工作会影响器件的可靠性。

|                    |                |

|--------------------|----------------|

| 模拟电源电压 AVDD/ AVDD2 | 2.2V           |

| 数字电源电压 DVDD        | 2.2V           |

| IO 电源电压 OVDD       | 2.2V           |

| 工作温度               | -40°C~+85°C    |

| 储藏温度               | -65°C ~ +150°C |

### 封装热阻：

非特别注明，以下数据均在自然空气对流环境，环境温度 20°C下所得。

| 封装类型   | $\theta_{JA}$ Ambient | $\theta_{JC}$ Top of Package | $\theta_{JC}$ Thermal Pad |

|--------|-----------------------|------------------------------|---------------------------|

| QFN-68 | 33.4°C/W              | 20.1°C/W                     | 13.3°C/W                  |

## 产品详细描述：

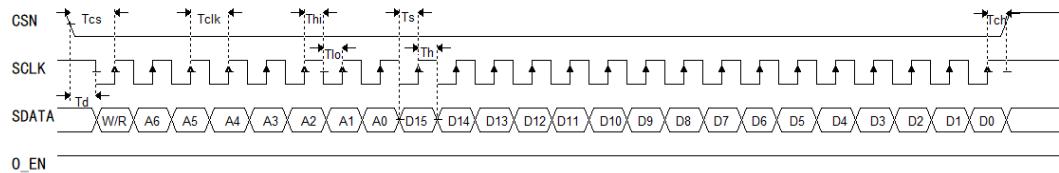

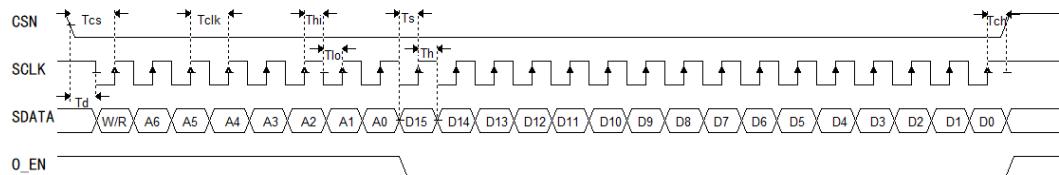

### 1 控制接口

#### 1.1 控制接口时序说明

➤ 写时序

图 4: SPI 写时序

➤ 读时序

图 5: SPI 读时序

#### 1.2 接口时序定义

表 2: 接口时序定义表

| 参数   | 描述                               | 最小值 | 单位 |

|------|----------------------------------|-----|----|

| Td   | Setup time between CSN and ~SCLK | 8   | ns |

| Tcs  | Setup time between CSN and SCLK  | 16  | ns |

| Tch  | Hold time between CSN and SCLK   | 8   | ns |

| Thi  | SCLK high time                   | 40  | ns |

| Tlo  | SCLK low time                    | 40  | ns |

| Tclk | SCLK period time                 | 100 | ns |

| Ts   | Data setup time                  | 5   | ns |

| Th   | Data hold time                   | 5   | ns |

补充说明：

- (1) W/R 读写位，0 是写，1 是读。

- (2) 读模式下，芯片内部三态门，在第 8 个 SCLK 的下降沿，从输入切换成输出；

- (3) 读模式下，确保接入 ADC 采样时钟（比如 1GHz），同时确保芯片不处于 PD 模式。

## 1.3 寄存器表

| 属性  | 地址<br>[6:0] | 描述                                                                                                                                                                                                                    | 默认值                  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| R/W | 0x00        | [0]: rst *, 自清零软件复位                                                                                                                                                                                                   | 1'b0                 |

| R/W | 0x0F        | [3:0]: sleep4_ch <4:1>, 设置特定通道休眠<br>[9]: pd, 进入掉电模式                                                                                                                                                                   | 4'b0<br>1'b0         |

| R/W | 0x11        | [2:0]: ilvds_lclk <2:0>, LCLKP 和 LCLKN 引脚的 LVDS 电流驱动编程<br>[6:4]: ilvds_frame <2:0>, FCLKP 和 FCLKN 引脚的 LVDS 电流驱动编程<br>[10:8]: ilvds_dat <2:0>, 输出数据引脚的 LVDS 电流驱动编程                                                     | 3'b0<br>3'b0<br>3'b0 |

| R/W | 0x24        | [3:0]: invert4_ch <4:1>, 四通道模拟下, 输出相位取反, 写入前要重新写入 channel_num <2:0>寄存器。<br>[5:4]: invert2_ch <2:1>, 二通道模拟下, 输出相位取反, 写入前要重新写入 channel_num <2:0>寄存器。<br>[6]: invert1_ch, 单通道模拟下, 输出相位取反, 写入前要重新写入 channel_num <2:0>寄存器。 | 4'b0<br>2'b0<br>1'b0 |

| R/W | 0x25        | [6]: en_ramp, 使能输出斜坡信号<br>[5]: dual_custom_pat, 使能输出在两个码之间切换<br>[4]: single_custom_pat, 使能输出固定码                                                                                                                       | 1'b0<br>1'b0<br>1'b0 |

| R/W | 0x26        | [15:8]: bits_custom1 <7:0>, 单个自定义模式码和双自定义模式码的第一个码                                                                                                                                                                     | 8'b0                 |

| R/W | 0x27        | [15:8]: bits_custom2 <7:0>, 双自定义模式码的第二个码                                                                                                                                                                              | 8'b0                 |

| 属性  | 地址<br>[6:0] | 描述                                                                                                                                                                                                                                                                                                                                          | 默认值                          |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| R/W | 0x2A        | [3:0]: cgain4_ch1 <3:0>, 四通道设置中通道 1 的可编程粗调增益, 写入前要重新写入 channel_num <2:0>寄存器。<br><br>[7:4]: cgain4_ch2 <3:0>, 四通道设置中通道 2 的可编程粗调增益, 写入前要重新写入 channel_num <2:0>寄存器。<br><br>[11:8]: cgain4_ch3 <3:0>, 四通道设置中通道 3 的可编程粗调增益, 写入前要重新写入 channel_num <2:0>寄存器。<br><br>[15:12]: cgain4_ch4 <3:0>, 四通道设置中通道 4 的可编程粗调增益, 写入前要重新写入 channel_num <2:0>寄存器。 | 4'b0<br>4'b0<br>4'b0<br>4'b0 |

| R/W | 0x2B        | [3:0]: cgain2_ch1 <3:0>, 双通道设置中通道 1 的可编程粗调增益, 写入前要重新写入 channel_num <2:0>寄存器。<br><br>[7:4]: cgain2_ch2 <3:0>, 双通道设置中通道 2 的可编程粗调增益, 写入前要重新写入 channel_num <2:0>寄存器。                                                                                                                                                                            | 4'b0<br>4'b0                 |

| R/W | 0x2B        | [11:8]: cgain1_ch1 <3:0>, 单通道设置中通道 1 的可编程粗调增益, 写入前要重新写入 channel_num <2:0>寄存器。                                                                                                                                                                                                                                                               | 4'b0                         |

| R/W | 0x31        | [2:0]: channel_num <2:0> *, 设置通道数: 1、2 或 4 通道                                                                                                                                                                                                                                                                                               | 3'b100                       |

| R/W | 0x33        | [0]: coarse_gain_cfg, 配置粗调增益设置<br><br>[1]: fine_gain_en, 启用精调增益设置                                                                                                                                                                                                                                                                           | 1'b1<br>1'b0                 |

| R/W | 0x34        | [7:0]: fgain_branch1 <7:0>, 第一通道分支 1 可编程精调增益<br><br>[15:8]: fgain_branch2 <7:0>, 第一通道分支 2 可编程精调增益                                                                                                                                                                                                                                           | 8'b0<br>8'b0                 |

| R/W | 0x35        | [7:0]: fgain_branch3 <7:0>, 第二通道分支 1 可编程精调增益<br><br>[15:8]: fgain_branch4 <7:0>, 第二通道分支 2 可编程精调增益                                                                                                                                                                                                                                           | 8'b0<br>8'b0                 |

| R/W | 0x36        | [7:0]: fgain_branch5 <7:0>, 第三通道分支 1 可编程精调增益<br><br>[15:8]: fgain_branch6 <7:0>, 第三通道分支 2 可编程精调增益                                                                                                                                                                                                                                           | 8'b0<br>8'b0                 |

| R/W | 0x37        | [7:0]: fgain_branch7 <7:0>, 第四通道分支 1 可编程精调增益<br><br>[15:8]: fgain_branch8 <7:0>, 第四通道分支 2 可编程精调增益                                                                                                                                                                                                                                           | 8'b0<br>8'b0                 |

| 属性  | 地址<br>[6:0] | 描述                                                                                | 默认值                  |

|-----|-------------|-----------------------------------------------------------------------------------|----------------------|

| R/W | 0x3A        | [4:0]; inp_sel_adc1 <4:0>, adc 1 的输入选择<br>[12:8]; inp_sel_adc2 <4:0>, adc 2 的输入选择 | 5'b00010<br>5'b00100 |

| R/W | 0x3B        | [4:0]; inp_sel_adc3 <4:0>, adc 3 的输入选择<br>[12:8]; inp_sel_adc4 <4:0>, adc 4 的输入选择 | 5'b01000<br>5'b10000 |

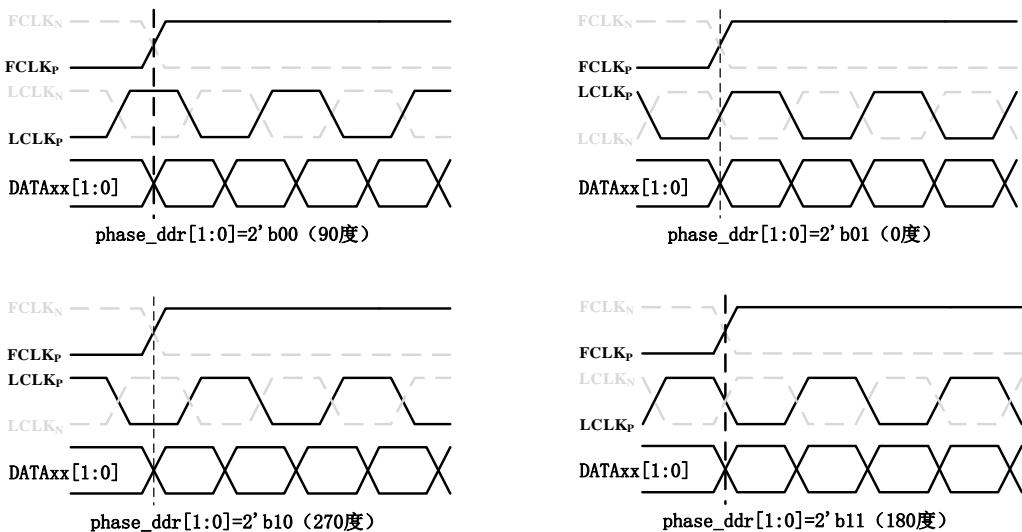

| R/W | 0x42        | [6:5]: phase_ddr <1:0>, 控制 LCLK 输出相对于数据的相位                                        | 2'b10                |

| R/W | 0x45        | [0]: pat_deskew, 置 1 后输出, '01010101'<br>[1]: pat_sync, , 置 1 后输出, '11110000'      | 1'b0<br>1'b0         |

| R/W | 0x46        | [2]: btc_mode, ADC 输出数据的二进制补码格式                                                   | 1'b0                 |

| R/W | 0x50        | [2:0]: adc_curr <2:0>, ADC 电流调整<br>[5:4]: ext_vcm_bc <1:0>, VCM 缓冲器驱动强度控制         | 3'b0<br>2'b01        |

| R/W | 0x55        | [5:0]: fs_cntrl <5:0>, 精调 ADC 满量程范围                                               | 6'b100000            |

| R/W | 0x57        | [0]: sync, 同步控制, 写一次相位挪动一拍                                                        | 1'b0                 |

| R/W | 0x58        | [0]: offset_wen, 手动输入 offset 的使能                                                  | 1'b0                 |

| R/W | 0x59        | [5:0]: 内部参数控制寄存器                                                                  | 6'b001000            |

| R/W | 0x5A        | [0]: trim_RST<0>触发一次 offset 校准<br>[1] : trim_RST<1>短接 ADC 的输入                     | 2'b0                 |

| R/W | 0x60        | [13:0]: offset_write0, 手动输入第 1 个 adc 的 offset 值                                   | 14'b0                |

| R/W | 0x61        | [13:0]: offset_write1, 手动输入第 2 个 adc 的 offset 值                                   | 14'b0                |

| R/W | 0x62        | [13:0]: offset_write2, 手动输入第 3 个 adc 的 offset 值                                   | 14'b0                |

| R/W | 0x63        | [13:0]: offset_write3, 手动输入第 4 个 adc 的 offset 值                                   | 14'b0                |

| 属性  | 地址<br>[6:0] | 描述                                              | 默认值      |

|-----|-------------|-------------------------------------------------|----------|

| R/W | 0x64        | [13:0]: offset_write4, 手动输入第 5 个 adc 的 offset 值 | 14'b0    |

| R/W | 0x65        | [13:0]: offset_write5, 手动输入第 6 个 adc 的 offset 值 | 14'b0    |

| R/W | 0x66        | [13:0]: offset_write6, 手动输入第 7 个 adc 的 offset 值 | 14'b0    |

| R/W | 0x67        | [13:0]: offset_write7, 手动输入第 8 个 adc 的 offset 值 | 14'b0    |

| R   | 0x68        | [13:0]: offset_cal0, 自动校准的第 1 个 adc 的 offset 值  | NA       |

| R   | 0x69        | [13:0]: offset_cal1, 自动校准的第 2 个 adc 的 offset 值  | NA       |

| R   | 0x6A        | [13:0]: offset_cal2, 自动校准的第 3 个 adc 的 offset 值  | NA       |

| R   | 0x6B        | [13:0]: offset_cal3, 自动校准的第 4 个 adc 的 offset 值  | NA       |

| R   | 0x6C        | [13:0]: offset_cal4, 自动校准的第 5 个 adc 的 offset 值  | NA       |

| R   | 0x6D        | [13:0]: offset_cal5, 自动校准的第 6 个 adc 的 offset 值  | NA       |

| R   | 0x6E        | [13:0]: offset_cal6, 自动校准的第 7 个 adc 的 offset 值  | NA       |

| R   | 0x6F        | [13:0]: offset_cal7, 自动校准的第 8 个 adc 的 offset 值  | NA       |

| R   | 0x7D        | [15:0]: Chip_ID,                                | 16'b01C0 |

| R/W | 0x7E        | [15:0]: test_reg0, 测试寄存器                        | 16'b0    |

| 属性  | 地址<br>[6:0] | 描述                       | 默认值   |

|-----|-------------|--------------------------|-------|

| R/W | 0x7F        | [15:0]: test_reg1, 测试寄存器 | 16'b0 |

## 2 寄存器描述

### 2.1 软件复位

rst[0]寄存器位设为1时将恢复芯片内部所有寄存器的默认值。

### 2.2 休眠模式

AAD12Q0250 支持指定任意子 ADC 进入休眠状态。sleep4\_ch[0]为1时，四通道中第一个通道休眠，对应 LVDS 接口 D1A 和 D1B 无输出；sleep4\_ch[1]为1时，四通道中第二个通道休眠，对应 LVDS 接口 D2A 和 D2B 无输出；sleep4\_ch[2]为1时，四通道中第三个通道休眠，对应 LVDS 接口 D3A 和 D3B 无输出；sleep4\_ch[3]为1时，四通道中第四个通道休眠，对应 LVDS 接口 D4A 和 D4B 无输出。

表 3: Sleep Mode VS. Channel & LVDS 接口

| Sleep4_ch[4:1] | Sleep Channel | LVDS 接口  |

|----------------|---------------|----------|

| 0001           | CH1           | D1A, D1B |

| 0010           | CH2           | D2A, D2B |

| 0100           | CH3           | D3A, D3B |

| 1000           | CH4           | D4A, D4B |

### 2.3 LVDS 接口驱动能力

AAD12Q0250 支持 LVDS 接口驱动能力可调，用户可以按表 2 进行配置，默认电流为 3.5mA，这是 LVDS 标准规定的值。

其中，ilvds\_lclk[2:0]控制 LCLKP 和 LCLKN 引脚上的 LCLK 时钟输出的电流驱动能力；ilvds\_frame[2:0]控制 FCLKP 和 FCLKN 引脚上的 FCLK 帧时钟输出的电流驱动能力；ilvds\_dat[2:0]控制 DP[4:1]A, DP[4:1]B, DN[4:1]A, DN[4:1]B 引脚上数据输出的电流驱动能力。

表 4: LVDS 驱动能力

| ilvds_*<2:0> | 驱动能力       |

|--------------|------------|

| 000          | 3.5mA (默认) |

| 001          | 2.5mA      |

| 101          | 1.5mA      |

|     |       |

|-----|-------|

| 011 | 0.5mA |

| 100 | 7.5mA |

| 010 | 6.5mA |

| 110 | 5.5mA |

| 111 | 4.5mA |

## 2.4 模拟输入取反

设置 invertx\_ch[n:0]会交换模拟正负输入，各通道独立控制。

## 2.5 LVDS 测试码

设置 en\_ramp[0]=1 时，所有数据输出均为重复的满量程斜坡图形。斜坡从码值 0 开始，每个时钟周期增加 1 LSB，直到满量程后回到码值 0，再次开始斜升。

设置 single\_custom\_pat[0] = 1 时，器件输出为恒定值，该值可利用 bits\_custom1[7:0]设置为所需码值。该模式下，bits\_custom1[7:0]替换输出端的 ADC 数据。

设置 dual\_custom\_pat[0]=1 时，器件交替输出两个码值。两个码值分别是 bits\_custom1 [7:0] 和 bits\_custom2[7:0]的内容。

还可以选择两个预设模式码：

1. 去偏斜模式码：设置 pat\_deskew[0] = 1，器件恒定输出码值 01010101；

2. 同步模式码：设置 pat\_sync[0] = 1，器件恒定输出码值 11110000。

注意：同一时间只能使用上述其中一种 LVDS 测试码。

## 2.6 增益调节

### 2.6.1 粗调增益

AAD12Q0250 支持增益可调功能，各通道的增益可以通过 cgain\_[3:0] 寄存器进行设置。增益寄存器由 coarse\_gain\_cfg 寄存器配置，当 coarse\_gain\_cfg = 0 时，使能 dB Step 模式，如表 1 所示；当 coarse\_gain\_cfg = 1 时，使能 X Step 模式，如表 2 所示。

- dB step 模式

表 5：dB Step 模式

| cgain_cfg | cgain | gain (dB) |

|-----------|-------|-----------|

| 0         | 0000  | 0         |

| 0         | 0001  | 1         |

| 0         | 0010  | 2         |

| 0         | 0011  | 3         |

| 0         | 0100  | 4         |

| 0         | 0101  | 5         |

| 0         | 0110  | 6         |

| 0         | 0111  | 7         |

| 0         | 1000  | 8         |

| 0         | 1001  | 9         |

| 0         | 1010  | 10        |

| 0         | 1011  | 11        |

| 0         | 1100  | 12        |

Acela

Micro

迅芯微电子（苏州）股份有限公司保密信息，未经允许禁止传播！

➤ X step 模式

AAD12Q0250

表 6: X Step 模式

| cgain_cfg | cgain | gain (x) |

|-----------|-------|----------|

| 1         | 0000  | 1        |

| 1         | 0001  | 1.25     |

| 1         | 0010  | 2        |

| 1         | 0011  | 2.5      |

| 1         | 0100  | 4        |

| 1         | 0101  | 5        |

| 1         | 0110  | 8        |

| 1         | 0111  | 10       |

| 1         | 1000  | 12.5     |

| 1         | 1001  | 16       |

| 1         | 1010  | 20       |

| 1         | 1011  | 25       |

| 1         | 1100  | 32       |

## 2.6.2 精调增益

AAD12Q0250 由 ADC1、ADC2、ADC3 和 ADC4 四个子通道组成，每个子通道由两个分支 (branch) 交织而成。比如 ADC1 对应 branch1 和 branch2，ADC2 对应 branch3 和 branch4，以此类推。每个 branch 的增益可支持精调。

要使能精调增益，fine\_gain\_en 寄存器需设置为 1。

表 7：增益精调

| fgain_X<7:0> | 增益公式                                                            | Gain(dB) |

|--------------|-----------------------------------------------------------------|----------|

| 01111111     | $OUT=IN*(1+2^{-5}+2^{-6}+2^{-7}+2^{-8}+2^{-9}+2^{-10}+2^{-11})$ | 0.500    |

| 01111110     | $OUT=IN*(1+2^{-5}+2^{-6}+2^{-7}+2^{-8}+2^{-9}+2^{-10})$         | 0.496    |

| 01111101     | $OUT=IN*(1+2^{-5}+2^{-6}+2^{-7}+2^{-8}+2^{-9}+2^{-11})$         | 0.492    |

| 01111100     | $OUT=IN*(1+2^{-5}+2^{-6}+2^{-7}+2^{-8}+2^{-9})$                 | 0.488    |

| ...          |                                                                 |          |

| 00000011     | $OUT=IN*(1+2^{-10}+2^{-11})$                                    | 0.012    |

| 00000010     | $OUT=IN*(1+2^{-10})$                                            | 0.008    |

| 00000001     | $OUT=IN*(1+2^{-11})$                                            | 0.004    |

| 00000000     | $OUT=IN$                                                        | 0.0000   |

| 11111111     | $OUT=IN$                                                        | 0.0000   |

| 11111110     | $OUT=IN*(1-2^{-11})$                                            | -0.004   |

| 11111101     | $OUT=IN*(1-2^{-10})$                                            | -0.008   |

| 11111100     | $OUT=IN*(1-2^{-10}-2^{-11})$                                    | -0.012   |

| ...          |                                                                 |          |

| 10000011     | $OUT=IN*(1-2^{-5}-2^{-6}-2^{-7}-2^{-8}-2^{-9})$                 | -0.488   |

| 10000010     | $OUT=IN*(1-2^{-5}-2^{-6}-2^{-7}-2^{-8}-2^{-9}-2^{-11})$         | -0.492   |

| 10000001     | $OUT=IN*(1-2^{-5}-2^{-6}-2^{-7}-2^{-8}-2^{-9}-2^{-10})$         | -0.496   |

| 10000000     | $OUT=IN*(1-2^{-5}-2^{-6}-2^{-7}-2^{-8}-2^{-9}-2^{-10}-2^{-11})$ | -0.500   |

## 2.7 工作模式

AAD12Q0250 有三种工作模式，由表 3 所示额寄存器 channel\_num[2:0]进行控制。单通道时内部四个子通道交织；两通道时内部四个子通道两两交织；四通道时内部四个子通道不交织同步输出。

表 8：工作模式

| channel_num<2:0> | 通道数目 | 描述                                                      |

|------------------|------|---------------------------------------------------------|

| 001              | 1    | 单通道， ADC1~ADC4 四路交织                                     |

| 010              | 2    | 双通道，通道 1：ADC1 和 ADC2 交织；<br>通道 2：ADC3 和 ADC4 交织         |

| 100              | 4    | 四通道，通道 1：ADC1；<br>通道 2：ADC2；<br>通道 3：ADC3；<br>通道 4：ADC4 |

## 2.8 输入选择

AAD12Q0250 支持模拟信号选择，用户可以通过 inp\_sel\_adcX [4:0]寄存器配置将任意一路模拟输入加载到任意一路 ADC (ADC1~ADC4)。在单通道模式下，可以选择四个输入中任何一个作为单个 ADC 通道的有效输入；在双通道模式下，可以为每一个 ADC 通道选择四个输入中的任意两个；在四通道模式下，任意输入都可以分配至任意 ADC 通道。输入切换可以在正常工作期间进行，无需额外的操作。切换会在每个 SPI 命令结束时立即生效。

表 9：输入选择

| inp_sel_adcX<4:0> | 选择的模拟输入 |

|-------------------|---------|

| 00010             | IP1/IN1 |

| 00100             | IP2/IN2 |

| 01000             | IP3/IN3 |

| 10000             | IP4/IN4 |

## 2.9 LCLK 相位控制

LCLK 位时钟相对于输出帧时钟 FCLK 和输出数据的相位可利用 phase\_addr[1:0]进行调节。LCLK 相位模式如图 6 所示，其中默认时序与设置 phase\_addr[1:0]=2'b10 相同。

图 6: LCLK 相位模式

## 2.10 输出格式

器件默认数据输出为偏移二进制。设置 b7c\_mode[0] = 1 时，MSB 发生反转使得器件以二进制补码的模式进行输出。

## 2.11 电流控制

通过 ADC 内核电流寄存器和输出 VCM 驱动能力寄存器可以用来调整 AAD12Q0250 芯片的性能和功耗。

adc\_curr[2:0]寄存器可调整 ADC 内核的电流消耗。标称设置时可以保证 ADC 的性能，降低 adc\_curr 的值可以实现更低的功耗。对于低至最小值的设置，性能影响较低，但这取决于 ADC 的采样率。

ext\_vcm\_bc[1:0]寄存器控制输出共模电压的驱动能力，用其提供 VCM 引脚电压。如果不使用此引脚，可以断开。如果从 VCM 引脚汲取电流，则可提高驱动强度以使得此引脚电压保持正确电平。

表 10: ADC 内核电流控制设置

| adc_curr<2:0> | 内核电流 |

|---------------|------|

| 100           | -40% |

| 101           | -30% |

| 110           | -20% |

| 111           | -10% |

| 000           | 默认值  |

| 001           | 10%  |

| 010           | 20%  |

| 011           | 30%  |

表 11: 输出共模电压驱动能力控制

| ext_vcm_bc<1:0> | 驱动能力等级 |

|-----------------|--------|

| 01              | 低（默认）  |

| 10              | 中      |

| 11              | 高      |

## 2.12 满量程控制

AAD12Q0250 满量程电压范围可以通过 fs\_cntrl[5:0]寄存器进行调整。该寄存器值所对应的小调节范围大约是满量程的 0.3%，因此，最大调节范围大约是±10%。表 12 显示了寄存器值与满量程范围的对应关系。注意：这里的满量程范围调整的只是近似值。

表 12: 寄存器值 VS. 满量程范围变化

| fs_cntrl<5:0> | 满量程调整  |

|---------------|--------|

| 111111        | 9.70%  |

| 111110        | 9.40%  |

| ...           |        |

| 100001        | 0.30%  |

| 100000        | 0%     |

| 011111        | -0.30% |

| ...           |        |

|        |        |

|--------|--------|

| 000001 | -9.70% |

| 000000 | -10%   |

### 2.13 同步控制

AAD12Q0250 芯片支持多片同步功能，芯片的多片同步功能需要通过 sync[0]寄存器进行配置。该寄存器每操作一次，数字电路就会发出一个脉冲，使得整个 ADC 芯片的时钟相位均后移一拍。通过连续、多次的操作该寄存器，实现 ADC 芯片内部时钟相位的循环移动，能够完成多片 ADC 芯片之间的同步。

### 2.14 自动校准触发

AAD12Q0250 芯片内置失调校准功能，在 ADC 每次复位之后自动完成。为了使失调校准更加灵活，内置失调校准控制寄存器。trim\_rst[0]可以再触发一次失调的自动校准。trim\_rst[0]可以将模拟输入端口短接，所有子通道输出为 0，用于外部失调校准。

### 2.15 offset 失调值

设置 offset\_wen[0] = 1 时，AAD12Q0250 芯片可以通过 offset\_writex[13:0]寄存器手动输入单个子 ADC 的失调值，代替自动校准的效果。同时也能通过寄存器进行修调自动校准的结果。由于内部校准算法是将 8bit 进行补零扩展成 14bit，使得寄存器位宽为 14bit，所以理论上可以实现 1/64 LSB 的修调。

## 3 初始化流程

- (1) 启动电源；

- (2) 芯片复位；在 RESETN 管脚上提供一个脉冲宽度大于 1us 的低脉冲信号。同时支持软件复位，首先对 0x00 寄存器进行操作，依次配置为 0x0001 和 0x0000；然后对 0x5A 寄存器写入 0x0002；最后将 0x5A 寄存器配置为 0x0001。

- (3) 将 0x50 寄存器中的 adc\_curr [2:0]配置为 3'b110；

- (4) 设置工作模式：

- 单通道 0x31: 0x0001;

- 双通道 0x31: 0x0002;

- 四通道 0x31: 0x0004;

- (5) 推荐的模拟输入选择：

- 单通道 0x3A: 0x1010; 0x3B: 0x1010;

- 双通道 0x3A: 0x0404; 0x3B: 0x0808;

- 四通道 0x3A: 0x1008; 0x3B: 0x0402。

## 4 数字输出

### 4.1 数字输出接口规范

采用标准 LVDS 输出，输出电流可调整。

### 4.2 数字输出时序关系

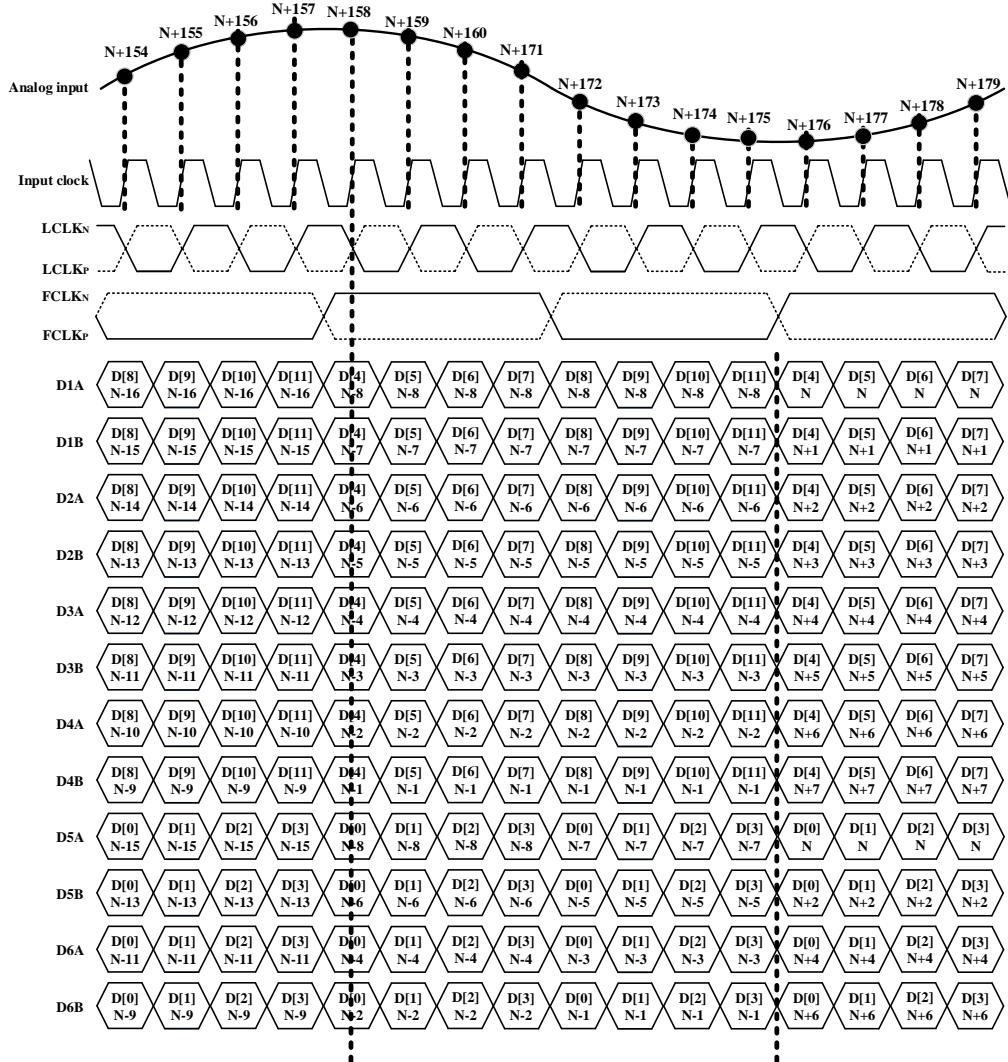

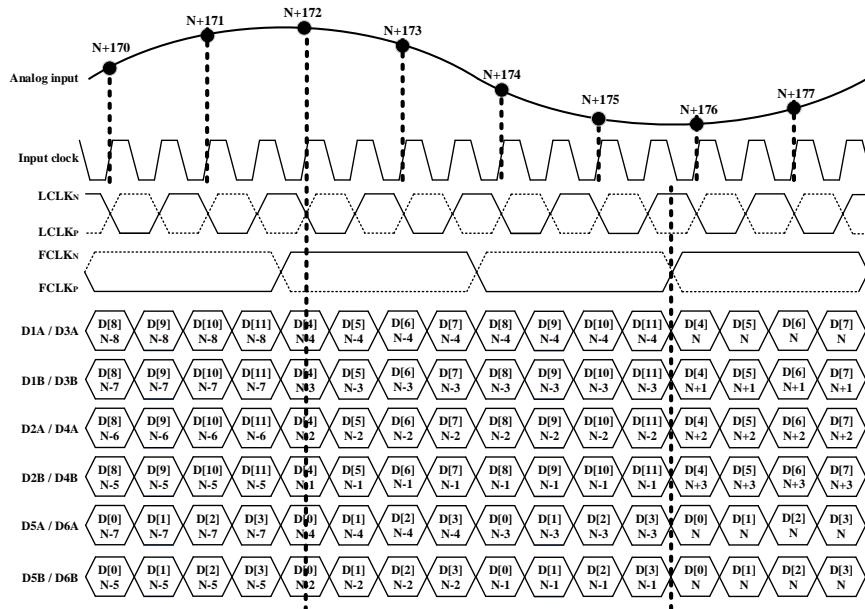

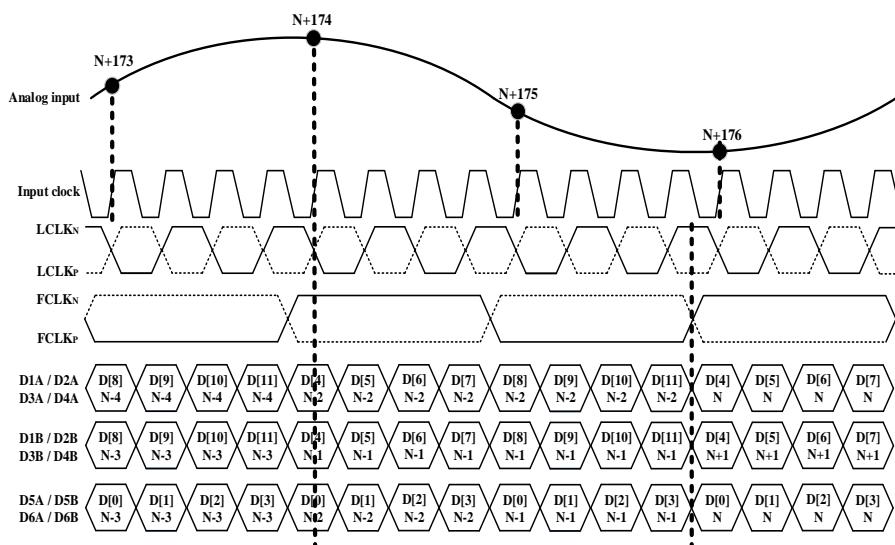

AAD12Q0250 芯片的输出数据和 Frame Clock/LVDS Clock 的时序关系如下：比如第一通道第一个分支和第二分支的高八位分别从 D1A 路和 D1B 路 LVDS 输出，第一分支的低四位和第二分支的低四位从 D5A 路 LVDS 输出，其他通道的数据输出依此类推。

图 7：单通道-LVDS 时序 12 位输出

**AAD12Q0250**

图 8：双通道-LVDS 时序 12 位输出

图 9：四通道-LVDS 时序 12 位输出

## 5 接口同步

输出 LVDS 之间的同步，芯片内置丰富的同步方案。包括输出斜坡信号、固定码、跳变码等，便于数字接口同步。

## 6 片间同步

支持多片同步，通过 sync 寄存器可以控制内部时序的相位，多次调整实现多片同步。

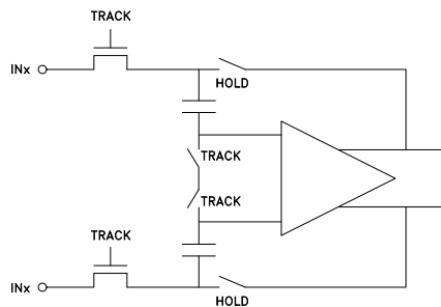

## 7 模拟输入

模拟输入等效电路如下所示，使用时需要外加 0.9V 共模电平。

图 10：模拟输入等效电路

## 8 时钟输入

差分时钟输入，差分幅度需要大于 600mV.内置共模电平，无需外加共模电平。

迅芯微电子（苏州）股份有限公司保密信息，未经允许禁止传播！

AAD12Q0250

订购信息：

| 型号             | 温度范围 | 输出接口 | 封装描述                |

|----------------|------|------|---------------------|

| AAD12Q0250     | TBD  | LVDS | 68 脚方形扁平无引脚封装 (QFN) |

| AAD12Q0250_EVM | TBD  |      | 评估板                 |

## 版本记录:

AAD12Q0250

## 声明

迅芯微电子（苏州）股份有限公司及其分公司和经销商有权对其公司提供的半导体产品进行修正、增强、提高及做出其他的改变。同时也拥有在最新版产品已经发布的基础上，中止任何一款产品和服务的权利。购买者应在下单前获取相关的最新信息，并确认这些信息的有效性和完整性。所有售出的半导体产品都必须遵循迅芯微电子（苏州）股份有限公司在接到订单确认时的销售条款和条件。

根据迅芯微电子（苏州）股份有限公司销售的半导体产品的保修条款，迅芯微电子（苏州）股份有限公司担保器件的性能规范适用于销售之时。本公司采取了必要的测试和质量控制手段来支持产品达到这样的品质。除非有法律的具体规定，否则并不是每个器件的所有参数都是必须要执行测试的。

迅芯微电子（苏州）股份有限公司对购买者使用产品做出的设计和应用不承担任何的连带责任，购买者应对使用了迅芯微电子（苏州）股份有限公司器件的产品和应用自负其责。并应采取适当的设计或操作时的具体保护措施来使您所设计的产品风险降至最低。

对于任何使用迅芯微电子（苏州）股份有限公司的器件和服务的所有相关的组合、设备或过程，迅芯微电子（苏州）股份有限公司不保证或代表许可——无论是明示或暗示——授予其使用任何相关的专利权、版权或其他任何知识产权。迅芯微电子（苏州）股份有限公司对第三方产品或服务不构成许可使用这些产品或服务的保修或背书。使用这样的信息可能需要从第三方的专利或第三方的其他知识产权获得许可或授权，或从迅芯微电子（苏州）股份有限公司获得专利和其他知识产权的授权。

从迅芯微电子（苏州）股份有限公司的数据手册中复制重要的章节是被允许的，只要复制时没有更改，同时附上所有相关的担保、条件、限制和告示信息。迅芯微电子（苏州）股份有限公司不对这些修改后的文件承担任何责任，第三方的信息可能会受到附加条件的约束。

超出迅芯微电子（苏州）股份有限公司所标明的器件或服务的参数范围或在与之不同参数下转售苏州迅芯微电子的器件或服务，或对迅芯微电子（苏州）股份有限公司的器件或服务无法提供有效服务并且暗含担保无效的行为，都是一种不公平且带有欺骗性质的商业行为。迅芯微电子（苏州）股份有限公司不为这样的声明承担任何责任。

购买者应确认并同意，尽管迅芯微电子（苏州）股份有限公司可能提供了与应用相关的信息或支持，但您将自行负责遵守与您的产品以及在应用中使用任何迅芯微电子（苏州）股份有限公司的器件有关的所有法律、法规和安全方面的要求。购买者应表示并同意您具备所有必要的专业知识，能够创建和实施安全措施以预测故障的危险后果、监控故障及其后果、降低可能导致伤害的故障的可能性并采取适当的补救措施。购买者将全额赔偿因在重大的安全应用中使用任何迅芯微电子（苏州）股份有限公司器件而对迅芯微电子（苏州）股份有限公司及其所代表方造成的所有损失。

在某些情况下，为了推广安全相关应用，有可能对迅芯微电子（苏州）股份有限公司的器件进行专门提升。借助于这样的器件，迅芯微电子（苏州）股份有限公司的目标旨在帮助客户设计和创立其特有的可满足功能性安全标准和要求的终端产品解决方案。尽管如此，此类器件仍然遵守本条款。