# CAN Transceiver, ISO 11992 NCV7390

## **Description**

The NCV7390 transceiver provides a point-to-point connection for serial data interchange between towing and towed vehicle or other similar automotive applications.

The transceiver is the interface between a controller area network (CAN) protocol controller and the physical bus.

The device provides differential transmit capability but allow switching in error conditions to a single-wire transmitter and/or receiver.

#### **Features**

- Designed for Systems According to the International Standard ISO 11992-1

- Suited Both for 12 V and 24 V Battery Systems Applications

- Error Detection Circuit and Capability of Single Wire Operation

- Sleep Mode with Low Current Consumption and Bus wake-up Function

- V<sub>CC</sub> Pin Allowing Interfacing with 3 V to 5 V Microcontrollers

- Low Electromagnetic Emission (EME) and High Electromagnetic Susceptibility

- Ground Shift Robustness

- Under all Supply Conditions the Chip Behaves Predictably

- Thermal Protection

- AEC-Q100 Qualified and PPAP Capable

- These are Pb-Free Devices

# **Typical Applications**

• Automotive, Interface Between Truck and Trailer

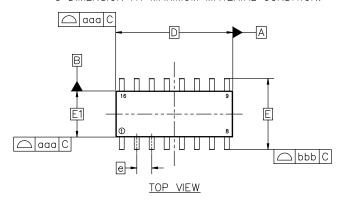

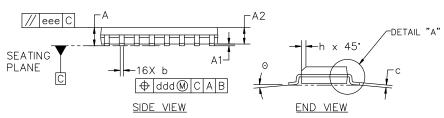

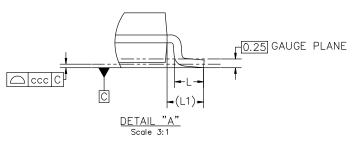

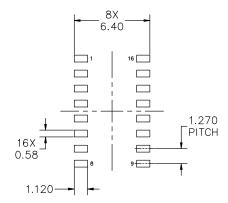

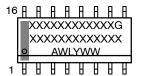

SOIC-16 CASE 751B-05

#### **MARKING DIAGRAM**

A = Assembly Site

WL = Wafer Lot Number

YY = Year of Production

WW = Work Week Number

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 16 of this data sheet.

# **TYPICAL APPLICATIONS**

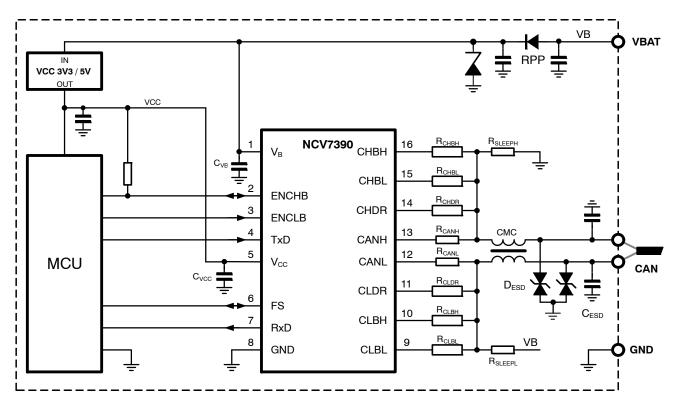

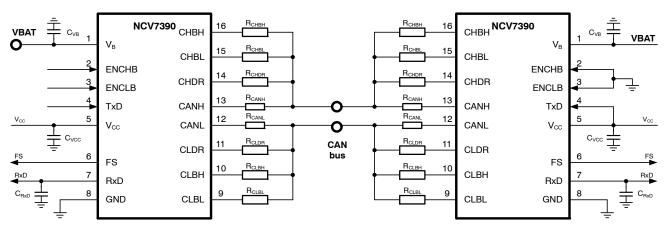

Figure 1. Typical Application Diagram

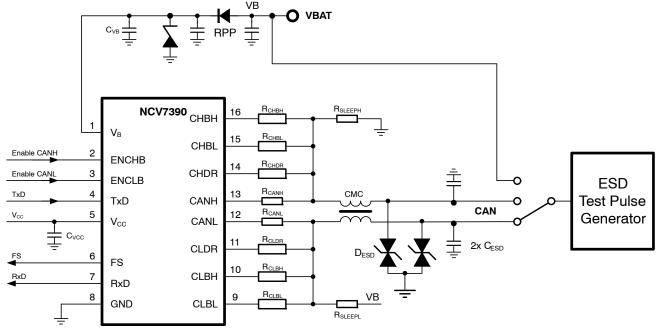

Figure 2. Typical Application Diagram with Sleep / Wake-up Mode

# RECOMMENDED EXTERNAL COMPONENTS FOR THE APPLICATION DIAGRAM

| Component           | Function                                                    | Value | Unit | Note                                                    |

|---------------------|-------------------------------------------------------------|-------|------|---------------------------------------------------------|

| RPP                 | Diode, Reverse polarity protection                          |       |      | e.g. Vishay RS2JHE3_A/I                                 |

| C <sub>VB</sub>     | Decoupling capacitor on V <sub>B</sub> supply pin, ceramic  | 100   | nF   |                                                         |

| C <sub>VCC</sub>    | Decoupling capacitor on V <sub>CC</sub> supply pin, ceramic | 100   | nF   | Type 0603 or less                                       |

| D <sub>ESD</sub>    | CAN bus protection element                                  |       |      | e.g.: - SZMMBZ33VALT1G - varistor, TDK, B72500E5250L060 |

| C <sub>ESD</sub>    | ESD protection capacitor                                    | 220   | pF   | 100 V                                                   |

| CMC                 | Common mode choke                                           | 51    | μН   | e.g. TDK ACT45B-510-2P-TL003                            |

| R <sub>CANH</sub>   | CANH protection resistor                                    | 1     | kΩ   | ≤ 1%, ≥ 0.25 W                                          |

| R <sub>CANL</sub>   | CANL protection resistor                                    | 1     | kΩ   | ≤ 1%, ≥ 0.25 W                                          |

| R <sub>SLEEPH</sub> | Sleep mode resistor (optional)                              | 22    | kΩ   | ≤ 1%, ≥ 0.25 W                                          |

| R <sub>SLEEPL</sub> | Sleep mode resistor (optional)                              | 22    | kΩ   | ≤ 1%, ≥ 0.25 W                                          |

| 24 V SYSTEM         |                                                             |       |      |                                                         |

| R <sub>CHBH</sub>   | Resistor, recessive level bias high, CANH                   | 1.62  | kΩ   | ≤ 1%, ≥ 1 W                                             |

| R <sub>CHBL</sub>   | Resistor, recessive level bias low, CANH                    | 887   | Ω    | ≤ 1%, ≥ 1 W                                             |

| R <sub>CHDR</sub>   | Resistor, dominant level, CANH                              | 274   | Ω    | ≤ 1%, ≥ 1 W                                             |

| R <sub>CLBH</sub>   | Resistor, recessive level bias high, CANL                   | 887   | Ω    | ≤ 1%, ≥ 1 W                                             |

| R <sub>CLBL</sub>   | Resistor, recessive level bias low, CANL                    | 1.91  | kΩ   | ≤ 1%, ≥ 1 W                                             |

| R <sub>CLDR</sub>   | Resistor, dominant level, CANL                              | 280   | Ω    | ≤ 1%, ≥ 1 W                                             |

| 12 V SYSTEM         |                                                             |       |      |                                                         |

| R <sub>CHBH</sub>   | Resistor, recessive level bias high, CANH                   | 1.62  | kΩ   | ≤ 1%, ≥ 1 W                                             |

| R <sub>CHBL</sub>   | Resistor, recessive level bias low, CANH                    | 887   | Ω    | ≤ 1%, ≥ 1 W                                             |

| R <sub>CHDR</sub>   | Resistor, dominant level, CANH                              | 221   | Ω    | ≤ 1%, ≥ 1 W                                             |

| R <sub>CLBH</sub>   | Resistor, recessive level bias high, CANL                   | 887   | Ω    | ≤ 1%, ≥ 1 W                                             |

| R <sub>CLBL</sub>   | Resistor, recessive level bias low, CANL                    | 2.21  | kΩ   | ≤ 1%, ≥ 1 W                                             |

| R <sub>CLDR</sub>   | Resistor, dominant level, CANL                              | 274   | Ω    | ≤ 1%, ≥ 1 W                                             |

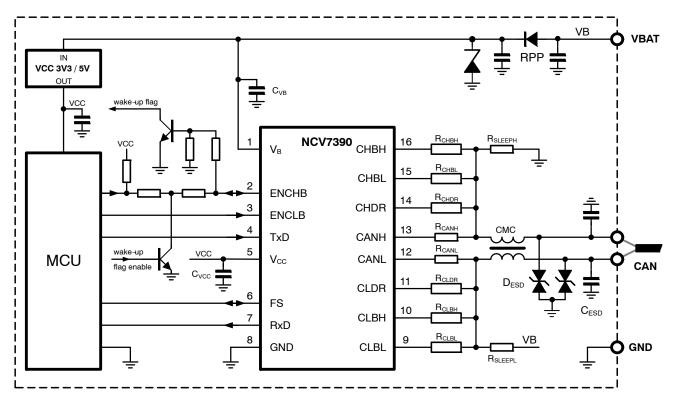

# **BLOCK DIAGRAM**

Figure 3. NCV7390 Block Diagram

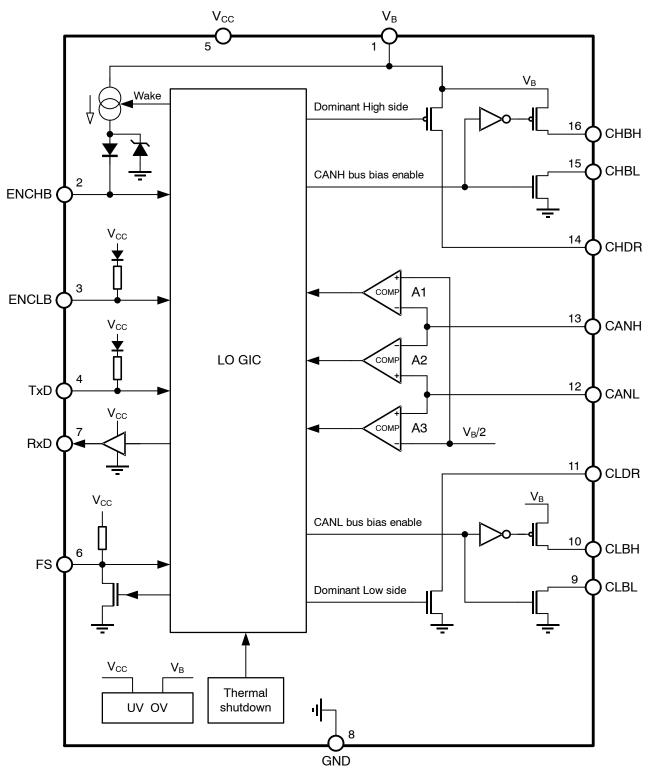

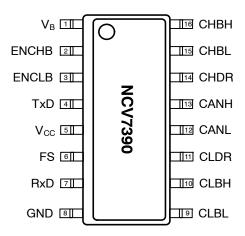

# **PIN CONNECTIONS**

Figure 4. Pin Connections – SOIC–16 (Top View)

# PIN FUNCTION DESCRIPTION

| Pin | Name            | Description                                     |

|-----|-----------------|-------------------------------------------------|

| 1   | V <sub>B</sub>  | Battery supply connection                       |

| 2   | ENCHB           | CANH Enable input (active low) / wake-up output |

| 3   | ENCLB           | CANL Enable input (active low)                  |

| 4   | TxD             | Transmit data input                             |

| 5   | V <sub>CC</sub> | Logic supply voltage                            |

| 6   | FS              | Fault state input/output                        |

| 7   | RxD             | Receive data output                             |

| 8   | GND             | Ground                                          |

| 9   | CLBL            | CANL Bias voltage Low                           |

| 10  | CLBH            | CANL Bias voltage High                          |

| 11  | CLDR            | CANL Driver                                     |

| 12  | CANL            | CANL receiver input                             |

| 13  | CANH            | CANH receiver input                             |

| 14  | CHDR            | CANH Driver                                     |

| 15  | CHBL            | CANH Bias voltage Low                           |

| 16  | CHBH            | CANH Bias voltage High                          |

## **MAXIMUM RATINGS**

| Symbol               | Parameter                                                         | Conditions                  | Min  | Max                   | Unit |

|----------------------|-------------------------------------------------------------------|-----------------------------|------|-----------------------|------|

| V <sub>B</sub>       | Supply Voltage, pin V <sub>B</sub>                                | (Note 1)                    | -0.3 | +65                   | V    |

| V <sub>CC</sub>      | Supply Voltage, pin V <sub>CC</sub>                               | (Note 1)                    | -0.3 | +6.0                  | V    |

| V <sub>CAN</sub>     | DC Voltage at Pins CANH, CANL, CLBL, CLBH, CLDR, CHDR, CHBL, CHBH | 0 < V <sub>CC</sub> < 5.5 V | -0.3 | V <sub>B</sub> + 0.3  | ٧    |

| V <sub>DIG_IN</sub>  | DC Voltage at Pin ENCHB                                           |                             | -0.3 | +65                   | V    |

| V <sub>DIG_IN</sub>  | DC Voltage at Pin TxD, ENCLB                                      |                             | -0.3 | +6.0                  | V    |

| V <sub>DIG_OUT</sub> | DC Voltage at Pin RxD                                             |                             | -0.3 | V <sub>CC</sub> + 0.3 | V    |

#### **MAXIMUM RATINGS**

| Symbol               | Parameter                                                                                                                                                                                         | Conditions                | Min  | Max  | Unit |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------|------|

| V <sub>DIG_OUT</sub> | DC Voltage at Pin FS                                                                                                                                                                              |                           | -0.3 | +6   | V    |

| I <sub>OP1A</sub>    | Peak Output Current CHBH, CLBL (Bus Short)                                                                                                                                                        | Duration of 2 ms          | -    | 41   | mA   |

| I <sub>OP2A</sub>    | Peak Output Current CHBL, CLBH (Bus Short)                                                                                                                                                        | Duration of 2 ms          | -    | 77   | mA   |

| I <sub>OP3A</sub>    | Peak Output Current CHDR, CLDR (Bus Short)                                                                                                                                                        | Duration of 2 ms          | -    | 228  | mA   |

| I <sub>OP1</sub>     | Peak Output Current CHBH, CLBL                                                                                                                                                                    | Duration of 1 sec         | -    | 28   | mA   |

| I <sub>OP2</sub>     | Peak Output Current CHBL, CLBH                                                                                                                                                                    | Duration of 1 sec         | -    | 54   | mA   |

| I <sub>OP3</sub>     | Peak Output Current CHDR, CLDR                                                                                                                                                                    | Duration of 1 sec         | -    | 82   | mA   |

| V <sub>ESD_IEC</sub> | Electrostatic Discharge Voltage at CAN Bus Pins and V <sub>B</sub> Pin, Test Circuit as shown in Figure 10 System HBM, Direct Contact                                                             | (Note 2)                  | -16  | +16  | kV   |

| V <sub>ESD_HBM</sub> | Electrostatic Discharge Voltage at all Pins;<br>Component HBM                                                                                                                                     | (Note 3)                  | -2   | +2   | kV   |

| V <sub>ESD_CDM</sub> | Electrostatic Discharge Voltage at all Pins;<br>Component CDM                                                                                                                                     | (Note 4)                  | -250 | +250 | V    |

| $V_{TRAN}$           | Voltage Transients, CAN Bus Pins                                                                                                                                                                  | test pulses 1             | -200 | -    | V    |

|                      | Test Pulses According to ISO7637-2, Class C<br>Test Circuit as shown in Figure 10                                                                                                                 | test pulses 2a            | -    | +300 | 1    |

|                      | _                                                                                                                                                                                                 | test pulses 3a            | -200 | -    |      |

|                      |                                                                                                                                                                                                   | test pulses 3b            | -    | +200 |      |

|                      | Voltage Transients, pin V <sub>B</sub> , According to ISO7637–2,<br>Class C<br>Maximum voltage seen on IC V <sub>B</sub> Pin clamped by exter-<br>nal element. Test Circuit as shown in Figure 10 | Test pulse 5<br>Load dump | -    | 65   |      |

| Latch-up             | Static Latch-up at all Pins                                                                                                                                                                       | (Note 5)                  | -    | 150  | mA   |

| TJ                   | Maximum Junction temperature                                                                                                                                                                      |                           | -40  | +150 | °C   |

| T <sub>A</sub>       | Maximum Ambient temperature                                                                                                                                                                       |                           | -40  | +125 | °C   |

| T <sub>STG</sub>     | Storage Temperature                                                                                                                                                                               |                           | -55  | +150 | °C   |

| MSL                  | Moisture Sensitivity Level                                                                                                                                                                        |                           |      | 2    | -    |

| T <sub>SLD</sub>     | Peak Soldering Temperature (Note 6)                                                                                                                                                               |                           | _    | 260  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHĂRACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

- 2. System human body model electrostatic discharge (ESD) pulses in accordance with IEC 61000–4–2. Equivalent to discharging a 150 pF capacitor through a 330  $\Omega$  resistor referenced to GND. External components according to the table: Recommended External Components for the Application Diagram.

- Standardized human body model electrostatic discharge (ESD) pulses in accordance with EIA–JESD22. Equivalent to discharging a 100 pF capacitor through a 1.5 kΩ resistor.

- 4. Standardized charged device model ESD pulses when tested according to AEC-Q100-011.

- 5. Static latch-up immunity: Static latch-up protection level when tested according to EIA/JESD78.

- 6. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### THERMAL CHARACTERISTICS

| Rating                                                                                                                                            | Symbol                              | Value     | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------|------|

| Thermal Characteristics, SOIC 16 small – 150 mil (Note 7) Thermal Resistance Junction-to-Air (Note 8) Thermal Resistance Junction-to-Air (Note 9) | $R_{	heta JA\_1} \ R_{	heta JA\_2}$ | 170<br>96 | K/W  |

- Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

- 8. Test board according to EIA/JEDEC Standard JESD51-3 (1S0P PCB), signal layer with 10% trace coverage.

- 9. Test board according to EIA/JEDEC Standard JESD51-7 (2S2P PCB), signal layers with 10% trace coverage.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 3.0 \text{ V}$  to 5.5 V;  $V_B = 7.0 \text{ V}$  to 32 V; for typical values  $T_A = 25^{\circ}\text{C}$ , for min/max values  $T_J = -40^{\circ}\text{C}$  to +150°C,  $C_{RXD} = 15 \text{ pF}$ ; unless otherwise noted. All voltages are referenced to GND (pin 8). Positive currents flow into the respective pin)

| Symbol                      | Parameter                                               | Conditions                                                                                                                                  | Min      | Тур      | Max         | Unit    |

|-----------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------------|---------|

| V <sub>CC</sub> SUPPLY INPU | JT (Pin V <sub>CC</sub> )                               |                                                                                                                                             |          |          |             |         |

| V <sub>CC</sub>             | Supply Voltage (input condition)                        |                                                                                                                                             | 3.0      | _        | 5.5         | V       |

| I <sub>CC</sub>             | Supply Current, all modes                               | $V_{TxD} = V_{ENCLB} = V_{ENCHB} = V_{CC}$<br>FS High                                                                                       | -        | -        | 10          | μΑ      |

|                             |                                                         | V <sub>TxD</sub> = V <sub>ENCLB</sub> = V <sub>ENCHB</sub> = 0 V<br>FS Low                                                                  | -        | -        | 2           | mA      |

| I <sub>CC_peak</sub>        | AC Peak Current during start-up                         | 0 V < V <sub>CC</sub> < 3.0 V<br>Not tested in production                                                                                   | -        | -        | 20          | mA      |

| V <sub>CC_slope</sub>       | Slew rate for V <sub>CC</sub> power off                 | Prepare for Sleep mode                                                                                                                      | _        | -        | 2.0         | V/ms    |

| V <sub>CC_UVR</sub>         | Undervoltage Recovery Threshold                         | V <sub>CC</sub> rising                                                                                                                      | 2.0      | -        | 2.9         | V       |

| V <sub>CC_UVD</sub>         | Undervoltage Detection Threshold                        | V <sub>CC</sub> falling                                                                                                                     | 1.9      | -        | 2.6         | V       |

| V <sub>CC_UVH</sub>         | Undervoltage Threshold<br>Hysteresis                    |                                                                                                                                             | 250      | _        | 400         | mV      |

| ΔV <sub>CCUV_ENCLB</sub>    | Difference: V <sub>CC_UVD</sub> _ V <sub>IH_ENCLB</sub> |                                                                                                                                             | 100      | -        | _           | mV      |

| V <sub>B</sub> SUPPLY INPUT | -                                                       | •                                                                                                                                           | <u>-</u> | <u>-</u> | <u>-</u>    |         |

| V <sub>B</sub>              | Supply Voltage on Pin V <sub>B</sub> (input condition)  |                                                                                                                                             | 7.0      | _        | 32          | V       |

| V <sub>B_PORH</sub>         | V <sub>B</sub> Power-on Threshold                       | V <sub>B</sub> rising                                                                                                                       | -        | 4.5      | 4.9         | V       |

| V <sub>B_PORL</sub>         | V <sub>B</sub> Power-off Threshold                      | V <sub>B</sub> falling                                                                                                                      | 4.0      | 4.4      | -           | V       |

| V <sub>th_OFF_CLDR</sub>    | CLDR pin switch off V <sub>B</sub> Threshold            |                                                                                                                                             | _        | 38       | 41          | V       |

| Ι <sub>Β</sub>              | Active Mode Supply Current                              | Without bias network current and dominant driver current (CxDR, CxBH, CxBL open)  VENCHB = VENCLB = 0 V, VTXD = VCC IOH_ENCHB not activated | -        | 1.5      | 6.4         | mA      |

| I <sub>B_LP</sub>           | Low-power Mode Supply Current                           | Standby Mode<br>V <sub>B</sub> = 7 V to 24 V                                                                                                | -        | 15       | 50          | μΑ      |

|                             |                                                         | Sleep Mode<br>V <sub>B</sub> = 7 V to 24 V<br>I <sub>OH_ENCHB</sub> not activated                                                           | -        | 30       | 80          | μΑ      |

| TRANSMITTER DA              | ATA INPUT (Pin TxD)                                     |                                                                                                                                             |          | 1        | 1           |         |

| V <sub>IH_TxD</sub>         | High-level input voltage                                | Output recessive                                                                                                                            | 2.0      | _        | _           | V       |

| V <sub>IL TxD</sub>         | Low-level input voltage                                 | Output dominant                                                                                                                             | _        | _        | 0.8         | V       |

| I <sub>PU TxD</sub>         | Pull-up current                                         | V <sub>TxD</sub> = GND                                                                                                                      | -550     | _        | -100        | μΑ      |

| I <sub>LEAK TxD</sub>       | Leakage current                                         | $V_{TxD} = V_{CC}$                                                                                                                          | -1.0     | 0        | +1.0        | μΑ      |

| <br>C <sub>i</sub>          | Input capacitance                                       | (Note 10)                                                                                                                                   | -        | 5        | 10          | pF      |

| RECEIVER DATA               | OUTPUT (Pin RxD)                                        |                                                                                                                                             |          | 1        | 1           |         |

| I <sub>OH_RxD</sub>         | High-level output current                               | $V_{RxD} = V_{CC} - 0.4 V$                                                                                                                  | _        | _        | -2.0        | mA      |

| I <sub>OL_RxD</sub>         | Low-level output current                                | V <sub>RxD</sub> = 0.4 V                                                                                                                    | 4.0      | -        | _           | mA      |

| TRANSMITTER M               | ODE SELECT (Pin ENCLB)                                  | •                                                                                                                                           |          |          |             |         |

|                             |                                                         |                                                                                                                                             | 2.0      | _        | _           | V       |

| V <sub>IH ENCLB</sub>       | High-level input voltage                                |                                                                                                                                             | 2.0      | _        |             |         |

| V <sub>IH_ENCLB</sub>       | High-level input voltage  Low-level input voltage       |                                                                                                                                             | -        | _        | 0.8         | V       |

| <u>_</u>                    |                                                         | V <sub>ENCLB</sub> = GND                                                                                                                    |          |          | 0.8<br>-100 | V<br>μA |

| V <sub>IL_ENCLB</sub>       | Low-level input voltage                                 | V <sub>ENCLB</sub> = GND V <sub>ENCLB</sub> = V <sub>CC</sub>                                                                               | -        | _        |             |         |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 3.0 \text{ V}$  to 5.5 V;  $V_B = 7.0 \text{ V}$  to 32 V; for typical values  $T_A = 25^{\circ}\text{C}$ , for min/max values  $T_J = -40^{\circ}\text{C}$  to +150°C,  $C_{RXD} = 15 \text{ pF}$ ; unless otherwise noted. All voltages are referenced to GND (pin 8). Positive currents flow into the respective pin)

| Symbol                  | Parameter                                                 | Conditions                                                                                               | Min                  | Тур      | Max      | Unit     |

|-------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------|----------|----------|----------|

| TRANSMITTER MO          | ODE SELECT, bus wake-up signalin                          | ng (Pin ENCHB)                                                                                           | •                    |          |          | •        |

| V <sub>IH_ENCHB</sub>   | High-level input voltage                                  |                                                                                                          | 2.0                  | _        | _        | V        |

| V <sub>IL_ENCHB</sub>   | Low-level input voltage                                   |                                                                                                          | -                    | _        | 0.8      | V        |

| I <sub>OH_ENCHB</sub>   | Pull-up current, bus wake-up signaling                    | 0 V < V <sub>ENCHB</sub> < 3.0 V;<br>wake-up detected                                                    | -5.0                 | -        | -0.5     | mA       |

| V <sub>ENCHB</sub> _OUT | Maximum voltage output if bus wake-up signaling activated | wake-up detected, no load current                                                                        | 3.675                | _        | 5.25     | V        |

| I <sub>LEAK_ENCHB</sub> | Leakage current                                           | V <sub>ENCHB</sub> = V <sub>CC</sub>                                                                     | -1.0                 | 0        | +1.0     | μΑ       |

| ILEAK_ENCHB_GND         | Weak pull-up current to internal IO cell supply           | V <sub>ENCHB</sub> = GND                                                                                 | -10.0                | -1.5     | -0.4     | μΑ       |

| C <sub>i</sub>          | Input capacitance                                         | (Note 10)                                                                                                | -                    | 5        | 10       | pF       |

| FS INPUT / OUTPU        | T                                                         |                                                                                                          | •                    |          | -        |          |

| V <sub>IH_FS</sub>      | High-level input voltage                                  |                                                                                                          | 2.0                  | _        | _        | V        |

| V <sub>IL_FS</sub>      | Low-level input voltage                                   |                                                                                                          | -                    | _        | 0.8      | V        |

| I <sub>LEAK_FS</sub>    | Leakage current                                           | V <sub>FS</sub> = V <sub>CC</sub>                                                                        | -1.0                 | 0        | +1.0     | μΑ       |

| I <sub>RPU_FS</sub>     | Pull-up current                                           | V <sub>FS</sub> = GND, V <sub>CC</sub> = 5.0 V                                                           | -400                 | -250     | -85      | μΑ       |

| V <sub>OL_FS</sub>      | Low-level output voltage                                  | I <sub>FS</sub> = 5.0 mA                                                                                 | -                    | _        | 0.5      | V        |

| C <sub>i</sub>          | Input capacitance                                         | (Note 10)                                                                                                | -                    | 5        | 10       | pF       |

| BUS BIAS PIN (Pi        | n CHBH)                                                   |                                                                                                          | •                    |          | -        |          |

| V <sub>OH_СНВН</sub>    | High-level output voltage                                 | $I_{CHBH}$ = -20 mA, $V_{B}$ = 32 V, or $I_{CHBH}$ = -4.5 mA, $V_{B}$ = 7.0 V                            | V <sub>B</sub> – 0.9 | -        | -        | V        |

| I <sub>LEAK_CHBH</sub>  | Leakage current                                           | ENCHB = High, V <sub>CHBH</sub> = 0 V                                                                    | -2.0                 | 0        | +2.0     | μΑ       |

| BUS BIAS PIN (Pi        | n CLBH)                                                   |                                                                                                          |                      |          | <u>.</u> |          |

| V <sub>OH_CLBH</sub>    | High-level output voltage                                 | $I_{CLBH}$ = -40 mA, $V_B$ = 32 V, or $I_{CLBH}$ = -9 mA, $V_B$ = 7.0 V                                  | V <sub>B</sub> – 1.0 | -        | -        | V        |

| I <sub>LEAK_CLBH</sub>  | Leakage current                                           | ENCLB = High, V <sub>CLBH</sub> = 0 V                                                                    | -2.0                 | 0        | +2.0     | μΑ       |

| BUS BIAS PIN (Pi        | n CHBL)                                                   |                                                                                                          | •                    |          | -        |          |

| V <sub>OL_CHBL</sub>    | Low-level output voltage                                  | I <sub>CHBL</sub> = 40 mA, V <sub>B</sub> = 32 V, or<br>I <sub>CHBL</sub> = 9 mA, V <sub>B</sub> = 7.0 V | _                    | -        | 400      | mV       |

| I <sub>LEAK_CHBL</sub>  | Leakage current                                           | ENCHB = High, V <sub>CHBL</sub> = V <sub>B</sub>                                                         | -2.0                 | 0        | +2.0     | μΑ       |

| BUS BIAS PIN (Pi        | n CLBL)                                                   |                                                                                                          | •                    |          |          | •        |

| V <sub>OL_CLBL</sub>    | Low-level output voltage                                  | $I_{CLBL}$ = 20 mA, $V_{B}$ = 32 V, or $I_{CLBL}$ = 4.5 mA, $V_{B}$ = 7.0 V                              | _                    | _        | 400      | mV       |

| I <sub>LEAK_CLBL</sub>  | Leakage current                                           | ENCLB = High, V <sub>CLBL</sub> = V <sub>B</sub>                                                         | -2.0                 | 0        | +2.0     | μА       |

| CAN HIGH SIDE D         | RIVE (Pin CHDR)                                           |                                                                                                          | •                    |          | •        | •        |

| R <sub>ON_CHDR</sub>    | Driver output resistance                                  | I <sub>CHDR</sub> = -40 mA                                                                               | 2.0                  | _        | 25       | Ω        |

| V <sub>OH_CHDR</sub>    | High level output voltage                                 | $V_B=32$ V, $I_{CHDR}=-115$ mA, or $V_B=7.0$ V, $I_{CHDR}=-26$ mA, ENCHB = Low, TxD = Low                | V <sub>B</sub> – 2.0 | -        | -        | V        |

| I <sub>LEAK_CHDR</sub>  | Leakage current                                           | ENCHB = High, V <sub>CHDR</sub> = 0 V                                                                    | -2.0                 | 0        | +2.0     | μΑ       |

| CAN LOW SIDE D          | RIVE (Pin CLDR)                                           |                                                                                                          | -                    | <u>-</u> | <u>-</u> | <u>-</u> |

| R <sub>ON CLDR</sub>    | Driver output resistance                                  | I <sub>CLDR</sub> = 40 mA                                                                                | 2.0                  | _        | 25       | Ω        |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 3.0 \text{ V}$  to 5.5 V;  $V_B = 7.0 \text{ V}$  to 32 V; for typical values  $T_A = 25^{\circ}\text{C}$ , for min/max values  $T_J = -40^{\circ}\text{C}$  to +150°C,  $C_{RXD} = 15 \text{ pF}$ ; unless otherwise noted. All voltages are referenced to GND (pin 8). Positive currents flow into the respective pin)

| Symbol                          | Parameter                                                                                                        | Conditions                                                                                                                                        | Min    | Тур | Max    | Unit           |

|---------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|--------|----------------|

| CAN LOW SIDE D                  | RIVE (Pin CLDR)                                                                                                  |                                                                                                                                                   |        |     |        |                |

| V <sub>OL_CLDR</sub>            | High level output voltage                                                                                        | $V_B$ = 32 V, $I_{CLDR}$ = 115 mA, or $V_B$ = 7.0 V, $I_{CHDR}$ = 26 mA, ENCLB = Low, TxD = Low                                                   | -      | -   | 2.0    | V              |

| I <sub>LEAK_CLDR</sub>          | Leakage current                                                                                                  | ENCLB = High, V <sub>CLDR</sub> = V <sub>B</sub>                                                                                                  | -2.0   | 0   | +2.0   | μΑ             |

| CAN RECEIVER (I                 | Pins CANH and CANL)                                                                                              |                                                                                                                                                   |        |     |        |                |

| I <sub>LEAK(off)</sub>          | Input leakage current                                                                                            | 0 < (V <sub>CANH</sub> = V <sub>CANL</sub> ) < 32 V                                                                                               | -5.0   | 0   | +5.0   | μΑ             |

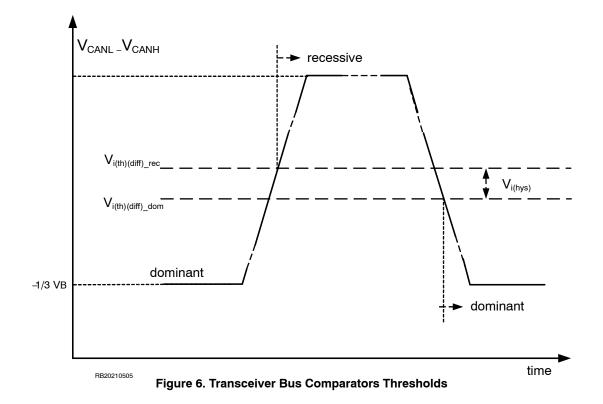

| V <sub>i(th)(diff)_dom_A2</sub> | Differential receiver threshold<br>voltage<br>Voltage (V <sub>CANL</sub> – V <sub>CANH</sub> ),<br>Comparator A2 | Dominant state 2.25 V $\leq$ V <sub>CANH</sub> , V <sub>CANL</sub> $\leq$ V <sub>B</sub> $-$ 2.9 V                                                | -0.65  | -   | 0      | V              |

| Vi(th)(diff)_rec_A2             | Differential receiver threshold<br>voltage<br>Voltage (V <sub>CANL</sub> – V <sub>CANH</sub> ),<br>Comparator A2 | Recessive state 2.25 V $\leq$ V <sub>CANH</sub> , V <sub>CANL</sub> $\leq$ V <sub>B</sub> $-$ 2.9 V ENCHB, ENCLB = Low                            | 0      | -   | 0.65   | V              |

| V <sub>i(th)(se)_</sub> A1      | Receiver threshold voltage<br>Voltage V <sub>CANH</sub> , Comparator A1                                          | ENCHB = Low, ENCLB = High                                                                                                                         | 0.48   | -   | 0.52   | V <sub>B</sub> |

| V <sub>i(th)(se)_</sub> A3      | Receiver threshold voltage<br>Voltage V <sub>CANL</sub> , Comparator A3                                          | ENCHB = High, ENCLB = Low                                                                                                                         | 0.48   | -   | 0.52   | V <sub>B</sub> |

| V <sub>i(th)_</sub> A1_sleep    | Receiver threshold voltage<br>Comparator A1 in Prepare for<br>sleep and Sleep mode                               | ENCHB = High,<br>ENCLB = High, TxD = Low                                                                                                          | 0.43   | -   | 0.47   | V <sub>B</sub> |

| V <sub>i(th)_</sub> A3_sleep    | Receiver threshold voltage<br>Comparator A3 in Prepare for<br>sleep and Sleep mode                               | ENCHB = High,<br>ENCLB = High, TxD = Low                                                                                                          | 0.49   | -   | 0.53   | V <sub>B</sub> |

| THERMAL SHUTE                   | OOWN                                                                                                             |                                                                                                                                                   |        |     |        |                |

| T <sub>JSD</sub>                | Shutdown junction temperature                                                                                    | Junction temperature rising                                                                                                                       | 160    | 180 | 200    | °C             |

| T <sub>JSD_HYST</sub>           | Shutdown junction temperature hysteresis                                                                         |                                                                                                                                                   | -      | 10  | -      | °C             |

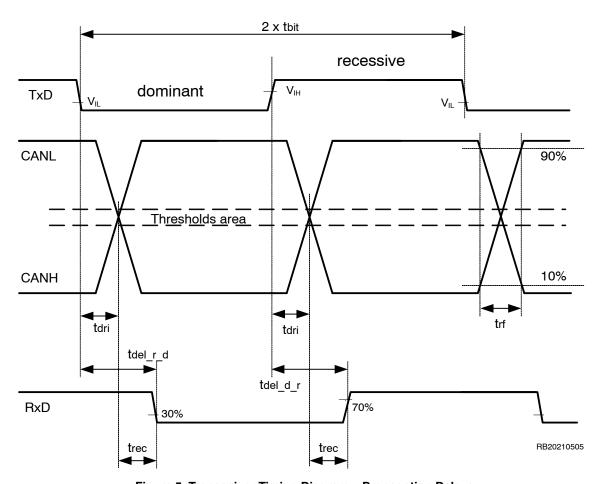

| TIMING CHARACT                  | TERISTICS (see and Figure 6)                                                                                     |                                                                                                                                                   |        |     |        |                |

| t <sub>bit125</sub>             | Bit time (input condition)                                                                                       | 125 kbps                                                                                                                                          | 7.9992 | 8.0 | 8.0008 | μs             |

| t <sub>bit250</sub>             | Bit time (input condition)                                                                                       | 250 kbps                                                                                                                                          | 3.9996 | 4.0 | 4.0004 | μs             |

| t <sub>dri</sub>                | Driving delay time                                                                                               | Active mode                                                                                                                                       | -      | 100 | -      | ns             |

| t <sub>rec</sub>                | Receiving delay time                                                                                             | Active mode                                                                                                                                       | -      | 100 | -      | ns             |

| <sup>t</sup> del_r_d            | Propagation delay TxD to RxD recessive to dominant transition                                                    | Active mode ENCHB = Low, ENCLB = Low  t <sub>del</sub> = t <sub>dri</sub> + t <sub>rec</sub> For setup see Figure 9                               | -      | -   | 350    | ns             |

| t <sub>del_d_r_</sub> amb       | Propagation delay TxD to RxD dominant to recessive transition                                                    | Active mode, $8.0 < V_B < 32 V$ , $T_{AMB} = 25^{\circ}C$ ENCHB = Low, ENCLB = Low $t_{del} = t_{dri} + t_{rec}$ For setup see Figure 9 (Note 10) | -      | -   | 400    | ns             |

| t <sub>del_d_</sub> r           | Propagation delay TxD to RxD dominant to recessive transition                                                    | Active mode, $8.0 < V_B < 32 V$ ,<br>ENCHB = Low, ENCLB = Low<br>$t_{del} = t_{dri} + t_{rec}$<br>For setup see Figure 9                          | -      | -   | 420    | ns             |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 3.0 \text{ V}$  to 5.5 V;  $V_B = 7.0 \text{ V}$  to 32 V; for typical values  $T_A = 25^{\circ}\text{C}$ , for min/max values  $T_J = -40^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ ,  $C_{RXD} = 15 \text{ pF}$ ; unless otherwise noted. All voltages are referenced to GND (pin 8). Positive currents flow into the respective pin)

| Symbol                    | Parameter                                                          | Conditions                                                                                                                                                    | Min  | Тур | Max  | Unit           |

|---------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|----------------|

| TIMING CHARAC             | TERISTICS (see and Figure 6)                                       |                                                                                                                                                               | •    |     | •    |                |

| t <sub>del_r_d_sw</sub>   | Propagation delay TxD to RxD recessive to dominant transition      | Active mode, 8.0 < $V_B$ < 32 V,<br>Either ENCLB or ENCHB are High<br>(single wire communication),<br>$t_{del} = t_{dri} + t_{rec}$<br>For setup see Figure 9 | -    | -   | 350  | ns             |

| <sup>t</sup> del_d_r_sw   | Propagation delay TxD to RxD dominant to recessive transition      | Active mode, 8.0 < $V_B$ < 32 V, Either ENCLB or ENCHB are High (single wire communication), $t_{del} = t_{dri} + t_{rec}$ For setup see Figure 9             | -    | -   | 500  | ns             |

| t <sub>EN</sub>           | Enable / Disable time, ENCLB and ENCHB pins                        |                                                                                                                                                               | -    | _   | 4.5  | μs             |

| t <sub>rf</sub>           | Rise / Fall time, CAN bus                                          | For setup see Figure 9                                                                                                                                        | -    | -   | 250  | ns             |

| t <sub>err_det</sub>      | Bus error detection filter time                                    |                                                                                                                                                               | -    | -   | 3.5  | μs             |

| t <sub>FS_res</sub>       | Delay time for FS reset                                            | (Note 10)                                                                                                                                                     | -    | -   | 1.0  | μs             |

| t <sub>Wake_width_L</sub> | CANL wake-up filter time                                           | Sleep mode, V <sub>CANL</sub> < 1/3 V <sub>B</sub>                                                                                                            | 1.5  | -   | 7.5  | μs             |

| t <sub>Wake_width_H</sub> | CANH wake-up filter time                                           | Sleep mode, V <sub>CANH</sub> > 2/3 V <sub>B</sub>                                                                                                            | 1.5  | _   | 7.5  | μs             |

| SYSTEM CHARA              | CTERISTICS                                                         |                                                                                                                                                               |      |     |      | _              |

| $V_{ m off\_GND}$         | Ground offset between the two interfaces during two wire operation |                                                                                                                                                               | -1/8 | -   | +1/8 | V <sub>B</sub> |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>10.</sup> Values based on design and characterization, not tested in production.

Figure 5. Transceiver Timing Diagram – Propagation Delays

## **FUNCTIONAL DESCRIPTION**

## **GENERAL FUNCTION**

There are two logical states for bus line, dominant or recessive. The bus is in the recessive state, when the driving sections of both transceivers connected to the bus are passive. (TxD is high)

The recessive state is specified by a voltage levels of typ.  $1/3 V_B$  at CANH and typ.  $2/3 V_B$  at CANL.

If at least one driver became active the bus changes into the dominant state. The dominant state is specified by a voltage levels of typ. 2/3  $V_B$  at CANH and typ. 1/3  $V_B$  at CANL. So, the differential voltage (Voltage at pin CANL minus voltage at pin CANH) change from typ. +1/3  $V_B$  in the recessive state to typ. -1/3  $V_B$  in the dominant state (See Figure 6).

The transceiver includes a bus driving section with biasing (CHBH, CLBH, CHBL, CLBL) and driver outputs (CHDR, CLDR) for CANH and CANL. The biasing outputs for the recessive state will be active if the corresponding enable (ENCHB, ENCLB) input is set to a low state.

To change to the dominant state, it is only necessary to activate the driver output by a low level at the input TxD.

The biasing and driver outputs are implemented as open drain push (CHDR, CHBH, CLBH) and pull (CLDR CHBL, CLBL) driver, with a matched (but opposite) slew rate at CHDR and CLDR.

The bus receiving section consists of an integrated RF-Filter followed by three comparators (A1..3). The comparators sense the state of the bus lines CANH and CANL. The reception of a dominant state causes a low level at RxD.

## **POWER SUPPLY**

NCV7390 implements two power supply inputs – battery supply input  $V_{B}$  and logic supply input  $V_{CC}$ .

## V<sub>B</sub> Supply pin

$V_{\rm B}$  is the main supply pin of the NCV7390. This supply input is used to provide the minimum power required for the operation in case of absence of the  $V_{\rm CC}$  supply. Typically, this is the only active supply in a low-power Sleep mode providing power supply to the low-power wake-up detector.

The digital part is supplied by an internal voltage supply derived from V<sub>B</sub>.

## V<sub>CC</sub> Supply pin

$V_{CC}$  pin provides supply for the logical interface of NCV7390. In case of missing  $V_{CC}$  the bus drivers of the NCV7390 are disabled until  $V_{CC} > V_{CC\_UVR}$ . After  $V_{CC} > V_{CC\_UVR}$  the CANH and CANL driver blocks can be activated by a low level with their corresponding ENCHB and ENCLB pins.

#### **OPERATION MODES**

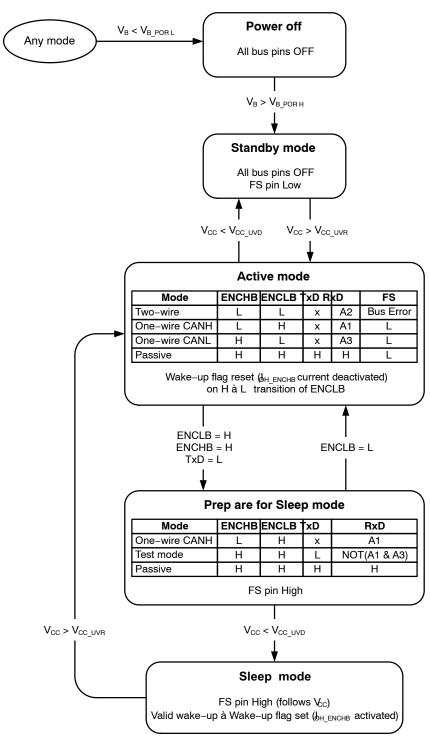

NCV7390 provides different operation modes. These modes are entered according to Figure 7.

#### Power-off

This virtual mode is entered when the  $V_B$  supply voltage falls below  $V_{B\_PORL}$  level. The internal logic is reset. CAN bus pins are left floating. As soon as  $V_B$  voltage rises above  $V_{B\_PORH}$  level, a power–on event is detected and the device proceeds to Standby mode. Bus receiver is in power down state.

## **Standby Mode**

The NCV7390 proceeds from Power-off mode to Standby mode as soon as the  $V_B$  supply is available ( $V_B > V_B$  PORH)

If  $V_{CC}$  <  $V_{CC\_UVD}$  and Prepare–for–sleep–mode is not active the circuit is in Standby mode with minimized current consumption.

Bus error detection counter is reset. Bus pins drivers and biases are off. Bus receiver is in power down state. FS pin is always Low in Standby mode.

## **Active Mode**

In the Active mode (see truth Table in Figure 7), the transceiver is able to communicate via the bus lines. The signals are transmitted and received to the CAN controller via the pins TxD and RxD.

The FS output is permanently reset (FS pin is set Low) if ENCHB or ENCLB pin is set High.

Wake-up flag is reset and the I<sub>OH\_ENCHB</sub> current is deactivated upon detecting High to Low level transition on ENCLB pin.

Based on status of pins ENCHB, ENCLB and TxD the active mode has four possible sub modes:

- Two-wire mode

- One-wire mode CANH

- One-wire mode CANL

- Passive sub mode

Two-wire Mode

All bus bias and driver pins are activated.

The differential signal from bus is detected by comparator A2 (see Figure 3) and signaled on RxD pin.

The Bus failure detection is active in this sub mode only.

One-wire Modes

The One-wire modes are failure modes to avoid total breakdown of the data transmission in case of a single bus failure.

To switch over from Two-wire mode to One-wire mode, it is necessary to disable the CANH or CANL line by a high state at the corresponding enable input. By this the corresponding biasing and driver outputs are disabled. In case of One-wire operation on CANH or CANL comparators, A1/A3 compares the voltage level on CANH/CANL pin with an internal reference voltage. Dominant state is signaled if there is voltage below

$V_{i(th)(se)\_A3}$  on CANL pin or voltage level above  $V_{i(th)(se)\_A1}$  on CANH pin.

#### Passive Mode

All bus bias and driver pins are deactivated (High impedance state).

The output RxD is forced to High level by the internal logic.

## **Prepare for Sleep Mode**

Prepare–for–sleep mode is an intermediate state used to put the transceiver into Sleep mode in a controlled way.

Prepare-for-sleep mode is entered from Active mode when ENCHB and ENCHL are set to High and TxD pin is set to Low. This condition will be latched and acknowledged by a high level at FS pin.

Based on status of pins ENCHB, ENCLB and TxD the active mode has three possible sub modes: One-wire mode CANH, Test mode and Passive sub mode.

## One-wire Mode CANH:

This mode is identical to one wire mode CANH in Active mode.

#### Test Mode:

In this mode the RxD pin is signaling result of this logical function of A1 and A3 comparators: NOT (A1 & A3).

#### Passive Mode:

The output RxD is forced to a high level by the internal logic.

If  $V_{CC}$  falls below  $V_{CC\_UVD}$  level and Prepare for Sleep mode is active, the device proceeds to Sleep mode. For this function, a slew rate of max.  $V_{CC}$  slope at  $V_{CC}$  is allowed.

## Sleep Mode

Sleep mode is a low-power mode in which the consumption is kept minimal.

The bias and driver outputs are in an off state. The voltage level at FS follows  $V_{\rm CC}$  because of the internal pull-up resistor.

Bus wake-up detection is enabled in Sleep mode. A wake-up flag is set when 16 dominant symbols longer that twake\_width\_H/L are detected by A1 comparator (CANH), or A3 comparator (CANL), or their combination. Short dominant glitches, caused by potential noise, are discarded.

Similarly, permanent bus dominant state caused by potential but short to GND or battery voltage does not lead to bus wake-up event detection.

No wake-up detection timeout is implemented.

ENCHB is pulled up to  $V_B$  level by a current source  $I_{OH\ ENCHB}$  when the wake-up flag is set.

While in Sleep mode and if  $V_{CC}$  supply rises above  $V_{CC\_UVR}$  level the device will transition directly to Active mode (see Figure 7).

Figure 7. Operation Modes

#### **FAILURE DETECTION**

#### Bus Failures

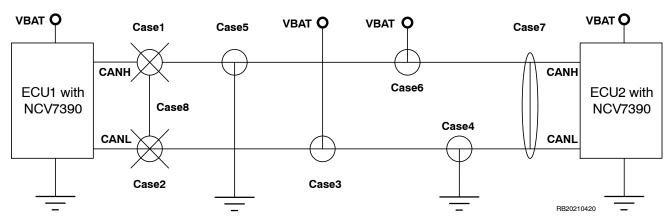

Several open and short failures can occur that may influence operation. They are shown in Figure 8. Those failures are described in accordance to ISO 11992.

NCV7390 allows to maintain data transmission by control via ENCLB and ENCHB in case of an interruption of CANH or CANL (cases 1 and 2) or a short of one cable to ground (cases 4 and 5) or to supply voltage (cases 3 and 6) or a short circuit between CANH and CANL (case 7). Data transmission is no longer possible if both cables are affected by a short circuit (except case 7) or interruption (case 8).

## **Bus Failure Detection**

The bus failure detection is active in Active Two-wire mode only.

The implemented fault status flags an incorrect 2-wire receiving condition in case of wire break or short condition at one bus line.

An internal error counter is incremented upon following events:

- A2 detects recessive to dominant edge while A1 or A3 is recessive,

- A1 or A3 detects dominant to recessive edge while A2 is dominant.

The first detection condition covers one bus line interruption scenario (case 1 and 2). The bus differential comparator A2 may still receive valid signal, but the single-ended comparators A1 or A3 receives permanent recessive.

The second detection condition covers CANH short to battery supply scenario (case 6) and CANL short to GND scenario (case 4) where the single-ended comparator A1 or A3 still receives correct data while the differential comparator A2 permanently receives dominant state.

The NCV7390 is typically not able to detect following cases, where the differential A2 receiver stays recessive:

- short circuit between CANH and CANL (case 7)

- both CANH and CANL interruption (case 8)

- CANH shorted to GND (case 5)

- CANL shorted to supply voltage (case 3)

These failure modes can be still detected by the microcontroller as a communication timeout since there are no data on RxD output.

A bus failure is detected when the internal error counter reaches value 7. Once the bus failure is detected, the fault status output FS is set High. The FS pin combines an open drain output with an internal pull-up resistor and a digital input that allows to receive an external request to reset the error logic.

The bus error logic can be reset by following events:

- Power on reset

- Low level on TxD pin if the failure was not yet set active (FS still low level)

- High level on ENCHB or ENCLB pins

- Forcing the FS pin Low externally if the pin is in high state

## Overtemperature Detection

The thermal protection circuit protects the IC from damage by switching off all CAN bias and driving pins if the junction temperature exceeds the thermal shutdown temperature (See parameter  $T_{\rm JSD}$ ). The overtemperature is not flagged on FS pin.

All other IC functions continue to operate.

Because these CAN bias and driver pins dissipates most of the power, the power dissipation and temperature of the IC is expected to be reduced once the transmitter is disabled. The CAN bias and driving pins are re-enabled when the junction temperature falls below the thermal shutdown temperature T<sub>JSD</sub> minus hysteresis. (See T<sub>JSD</sub> HYST).

The thermal protection circuit is particularly needed in case of a bus line short condition.

Figure 8. Bus Failures

## **FAIL SAFE FEATURES**

A current-limiting circuit protects the bus bias and driving pins from damage caused by accidental short circuit to either positive or negative supply voltage, although power dissipation increases during this fault condition.

The bus is protected from automotive electrical transients (according to ISO 7637; see Figure 10).

Pin TxD and pin ENCLB are pulled high internally should the input become disconnected.

## **MEASUREMENT SETUPS AND DEFINITIONS**

Figure 9. Test Circuit for Timing Characteristics

Figure 10. Test Circuit for ESD and Automotive Transients

## **ORDERING INFORMATION**

| Part Number   | Description                | Package | Shipping <sup>†</sup> |

|---------------|----------------------------|---------|-----------------------|

| NCV7390DB0R2G | CAN Transceiver, ISO 11992 | SOIC-16 | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

## SOIC-16 9.90x3.90x1.37 1.27P CASE 751B ISSUE M

**DATE 18 OCT 2024**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2018.

- 2. DIMENSION IN MILLIMETERS. ANGLE IN DEGREES.

- 3. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD PROTRUSION.

- 4. MAXIMUM MOLD PROTRUSION 0.15mm PER SIDE.

- 5. DIMENSION 6 DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127mm TOTAL IN EXCESS OF THE 6 DIMENSION AT MAXIMUM MATERIAL CONDITION.

| MILLIMETERS |          |          |          |  |  |

|-------------|----------|----------|----------|--|--|

| DIM         | MIN      | NOM      | MAX      |  |  |

| А           | 1.35     | 1.55     | 1.75     |  |  |

| A1          | 0.10     | 0.18     | 0.25     |  |  |

| A2          | 1.25     | 1.37     | 1.50     |  |  |

| b           | 0.35     | 0.42     | 0.49     |  |  |

| С           | 0.19     | 0.22     | 0.25     |  |  |

| D           |          | 9.90 BSC |          |  |  |

| E           |          | 6.00 BSC |          |  |  |

| E1          |          | 3.90 BSC |          |  |  |

| е           |          | 1.27 BSC |          |  |  |

| h           | 0.25     |          | 0.50     |  |  |

| L           | 0.40     | 0.83     | 1.25     |  |  |

| L1          |          | 1.05 REF |          |  |  |

| Θ           | 0.       |          | 7*       |  |  |

| TOLERAN     | CE OF FC | RM AND   | POSITION |  |  |

| aaa         | 0.10     |          |          |  |  |

| bbb         | 0.20     |          |          |  |  |

| ccc         |          | 0.10     |          |  |  |

| ddd         |          | 0.25     | ·        |  |  |

| eee         |          | 0.10     |          |  |  |

#### RECOMMENDED MOUNTING FOOTPRINT

\*FOR ADDITIONAL INFORMATION ON OUR

PB-FREE STRATEGY AND SOLDERING DETAILS,

PLEASE DOWNLOAD THE onsemi SOLDERING

AND MOUNTING TECHNIQUES REFERENCE

MANUAL, SOLDERRM/D

| DOCUMENT NUMBER: | 98ASB42566B                  | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | SOIC-16 9.90X3.90X1.37 1.27P |                                                                                                                                                                                   | PAGE 1 OF 2 |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

## **SOIC-16 9.90x3.90x1.37 1.27P** CASE 751B

ISSUE M

**DATE 18 OCT 2024**

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code

A = Assembly Location

WL = Wafer Lot

Y = Year

WW = Work Week

G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| STYLE 1:          |                                    | STYLE 2:          |                | STYLE 3:   | S                                              | TYLE 4: |                   |

|-------------------|------------------------------------|-------------------|----------------|------------|------------------------------------------------|---------|-------------------|

|                   | COLLECTOR                          | PIN 1.            | CATHODE        | PIN 1.     | COLLECTOR, DYE #1                              | PIN 1.  | COLLECTOR, DYE #1 |

|                   | BASE                               | 2.                | ANODE          | 2.         | BASE. #1                                       | 2.      |                   |

| 3.                | EMITTER                            | 3.                | NO CONNECTION  | 3.         | EMITTER. #1                                    | 3.      |                   |

| 4.                | NO CONNECTION                      | 4.                | CATHODE        | 4.         | COLLECTOR, #1                                  | 4.      | COLLECTOR, #2     |

| 5.                | EMITTER                            | 5.                | CATHODE        | 5.         | COLLECTOR, #2                                  | 5.      | COLLECTOR, #3     |

| 6.                | BASE                               | 6.                | NO CONNECTION  | 6.         | BASE, #2                                       | 6.      | COLLECTOR, #3     |

| 7.                | COLLECTOR                          | 7.                | ANODE          | 7.         | EMITTER, #2                                    | 7.      | COLLECTOR, #4     |

| 8.                | COLLECTOR                          | 8.                | CATHODE        | 8.         | COLLECTOR, #2                                  | 8.      | COLLECTOR, #4     |

| 9.                | BASE                               | 9.                | CATHODE        | 9.         | COLLECTOR, #3                                  | 9.      | BASE, #4          |

| 10.               | EMITTER                            | 10.               | ANODE          | 10.        | BASE, #3                                       | 10.     | EMITTER, #4       |

| 11.               | NO CONNECTION                      | 11.               | NO CONNECTION  | 11.        | EMITTER, #3                                    | 11.     |                   |

|                   | EMITTER                            | 12.               | CATHODE        | 12.        | COLLECTOR, #3                                  | 12.     |                   |

| 13.               | BASE                               | 13.               |                | 13.        | COLLECTOR, #4                                  | 13.     | BASE, #2          |

| 14.               | COLLECTOR                          | 14.               | NO CONNECTION  | 14.        | BASE, #4                                       | 14.     |                   |

| 15.               | EMITTER                            | 15.               | ANODE          | 15.        | EMITTER, #4                                    | 15.     |                   |

| 16.               | COLLECTOR                          | 16.               | CATHODE        | 16.        | COLLECTOR, #4                                  | 16.     | EMITTER, #1       |

|                   |                                    |                   |                |            |                                                |         |                   |

| STYLE 5:          |                                    | STYLE 6:          |                | STYLE 7:   |                                                |         |                   |

| PIN 1.            | DRAIN, DYE #1                      | PIN 1.            | CATHODE        | PIN 1.     | SOURCE N-CH                                    |         |                   |

| 2.                | DRAIN, #1                          | 2.                | CATHODE        | 2.         | COMMON DRAIN (OUTPUT)                          |         |                   |

| 3.                | ,                                  | 3.                | CATHODE        | 3.         | COMMON DRAIN (OUTPUT)                          |         |                   |

| 4.                | ,                                  | 4.                | CATHODE        | 4.         |                                                |         |                   |

| 5.                | DRAIN, #3                          | 5.                |                | 5.         | COMMON DRAIN (OUTPUT)                          |         |                   |

| 6.                | DRAIN, #3                          | 6.                |                | 6.         | COMMON DRAIN (OUTPUT)                          |         |                   |

| 7.                | DRAIN, #4                          |                   | CATHODE        | 7.         | COMMON DRAIN (OUTPUT)                          |         |                   |

| 8.                | DRAIN, #4                          |                   | CATHODE        | 8.         | SOURCE P-CH                                    |         |                   |

|                   | GATE, #4                           |                   | ANODE          | 9.         | SOURCE P-CH                                    |         |                   |

| 10.               | SOURCE, #4                         |                   | ANODE          | 10.        |                                                |         |                   |

| 11.               | GATE, #3                           |                   | ANODE          | 11.        |                                                |         |                   |

| 12                | SOURCE, #3                         | 12                | ANODE          | 12.        |                                                |         |                   |

|                   |                                    |                   | -              |            |                                                |         |                   |

| 13.               | GATE, #2                           | 13.               | ANODE          | 13.        |                                                |         |                   |

| 13.<br>14.        | GATE, #2<br>SOURCE, #2             | 13.<br>14.        | ANODE          | 14.        | COMMON DRAIN (OUTPUT)                          |         |                   |

| 13.<br>14.<br>15. | GATE, #2<br>SOURCE, #2<br>GATE, #1 | 13.<br>14.<br>15. | ANODE<br>ANODE | 14.<br>15. | COMMON DRAIN (OUTPUT)<br>COMMON DRAIN (OUTPUT) |         |                   |

| 13.<br>14.        | GATE, #2<br>SOURCE, #2             | 13.<br>14.        | ANODE          | 14.        | COMMON DRAIN (OUTPUT)                          |         |                   |

| DOCUMENT NUMBER: | 98ASB42566B              | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |

|------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DESCRIPTION:     | SOIC-16 9.90X3.90X1.37 1 | PAGE 2 OF 2                                                                                                                                                                         |  |  |  |  |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales