High Fidelity Stereo SPDT Switch with Pop and Click Elimination

#### WWW.TECHPUBLIC.COM

#### **Features**

- Single supply range operating from 3.0V to 4.5V

- -118dB THD+N into 100kΩ load at 2Vrms

- -114dB THD+N into 32Ω load at 2Vrms

- Signal-to-Noise (SNR) Ratio 132dBA

- 100dB PSRR at 10kHz

- 145dB crosstalk & separation

- Pop/Click shunt circuit

- Audio Path Soft Turn-On/Off for Pop & Click Elimination

- operates over an ambient temperature range of -40 °C to +85 °C

- Packaging: WLCSP 1.2 x 1.2 -9 Ball

### **Applications**

- Mobile Phones/Tablet PCs

- Notebook/Ultrabook Computers

### **General Description**

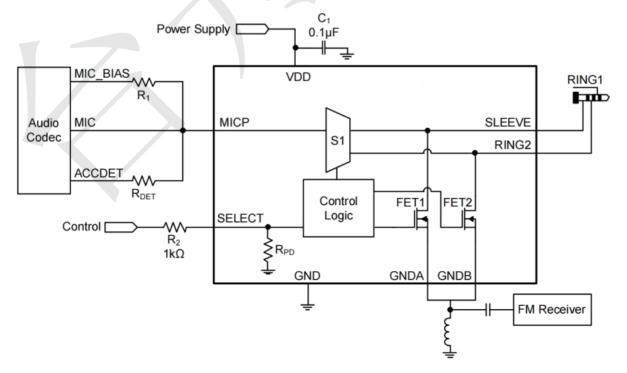

The is an audio headset analog switch that is used to detect 3.5mm accessories and switch sleeve and ring by external controller. The ground signal is routed through a pair of low-impedance ground FETs ( $75m\Omega$  typical), resulting minimal impact on audio cross-talk performance. The ground FETs of the device are designed to allow FM signal pass-through, making it possible to use the ground line of the headset as an FM antenna in mobile audio application.

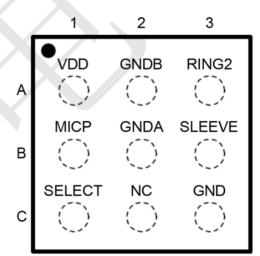

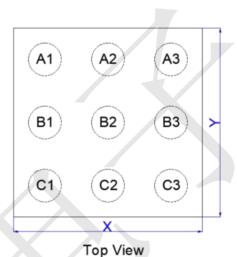

### PIN CONFIGURATIONS (TOP VIEW)

### **PIN DESCRIPTION**

| PIN | NAME   | FUNCTION                                                                                                                         |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------|

| A1  | VDD    | Power Supply for the Chip.                                                                                                       |

| A2  | GNDB   | FET2 Ground Reference.                                                                                                           |

| A3  | RING2  | Connected to the RING2 Segment of the Jack. This pin will be routed to MICP or GNDB depending on the logic level of SELECT pin.  |

| B1  | MICP   | Microphone Signal Connection to Codec. Microphone bias should be fed into this pin.                                              |

| B2  | GNDA   | FET1 Ground Reference.                                                                                                           |

| ВЗ  | SLEEVE | Connected to the SLEEVE Segment of the Jack. This pin will be routed to MICP or GNDA depending on the logic level of SELECT pin. |

| C1  | SELECT | The Logic Signal Used to Control S1 Switch, FET1 and FET2.                                                                       |

| C2  | NC     | No Connection.                                                                                                                   |

| C3  | GND    | Chip Ground Reference.                                                                                                           |

High Fidelity Stereo SPDT Switch with Pop and Click Elimination

WWW.TECHPUBLIC.COM

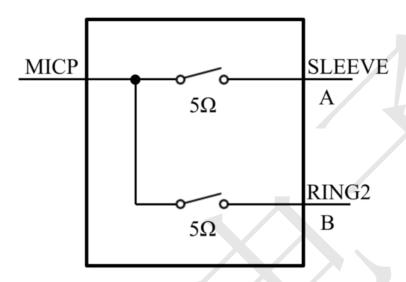

## **Functional Diagram**

### **Truth Table**

|                                                  | SELECT | FUNCTION                                        |  |  |

|--------------------------------------------------|--------|-------------------------------------------------|--|--|

|                                                  | 0      | MICP = A = SLEEVE, FET2 Turn On, FET1 Turn Off. |  |  |

| 1 MICP = B = RING2, FET2 Turn Off, FET1 Turn On. |        | MICP = B = RING2, FET2 Turn Off, FET1 Turn On.  |  |  |

# **Typical Application**

High Fidelity Stereo SPDT Switch with Pop and Click Elimination

WWW.TECHPUBLIC.COM

## **Absolute Maximum Ratings**

| Parameter                                | Symbol           | Value     | Unit |  |

|------------------------------------------|------------------|-----------|------|--|

| Supply Voltage                           | Vcc              | -0.3 ~6   | V    |  |

| Voltage Range on SELECT, MICP, RING2,    | V <sub>IS</sub>  | -0.3 ~    | V    |  |

| SLEEVE                                   | Vis              | VDD+0.3V  | V    |  |

| Storage Temperature Range                | T <sub>STG</sub> | -55 ~ 150 | °C   |  |

| Junction Temperature                     | T <sub>J</sub>   | 150       | °C   |  |

| Lead Temperature (Soldering, 10 seconds) | Tι               | 260       | °C   |  |

| Thermal Resistance                       | R <sub>0JA</sub> | 80        | °C/W |  |

#### Note:

Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied

# **Recommend operating ratings**

| Parameter                                  | Symbol          | Value        | Unit       |

|--------------------------------------------|-----------------|--------------|------------|

| Supply Voltage                             | Vcc             | 2.6 ~ 5.0    | V          |

| Input/Output Voltage Range                 | V <sub>IN</sub> | 0.0 ~ 3.3    | V          |

| operates over an ambient temperature range | TA              | -40°C to +85 | $^{\circ}$ |

#### Note:

The input and output negative voltage ratings may be exceeded if the input and output diode current ratings are observed.

High Fidelity Stereo SPDT Switch with Pop and Click Elimination

**WWW.TECHPUBLIC.COM**

#### **DC Electrical Characteristics**

(V<sub>DD</sub> = 2.6V to 5.0V, typical values are at V<sub>DD</sub> = 3.3V, T<sub>A</sub> = +25 °C, unless otherwise noted.)

| PARAMETER                        | SYMBOL | CONDITIONS                                                                       | MIN | TYP | MAX | UNITS |  |

|----------------------------------|--------|----------------------------------------------------------------------------------|-----|-----|-----|-------|--|

| Input Voltage Range              | VDD    |                                                                                  | 2.6 |     | 5.0 | V     |  |

| Quiescent Current                | IQ     | VDD = 4.5V, VMICP = 1.8V to VDD, SELECT = Low or SELECT = High (after detection) |     | 4   |     | μА    |  |

| Input/Output Voltage Range       | VIO    |                                                                                  | 0   |     | 3.3 | V     |  |

|                                  |        | VDD = 2.6V                                                                       | 1.1 |     | VDD |       |  |

| Input Logic High for SELECT      | N/m s  | V <sub>DD</sub> = 3.3V                                                           | 1.1 |     | VDD | V     |  |

|                                  | VIH    | V <sub>DD</sub> = 4.5V                                                           | 1.3 |     | VDD |       |  |

|                                  |        | VDD = 2.6V                                                                       | 0   |     | 0.7 |       |  |

| Input Logic Low for SELECT       | VIL    | V <sub>DD</sub> = 3.3V                                                           | 0   |     | 0.8 | V     |  |

|                                  |        | VDD = 4.5V                                                                       | 0   |     | 0.8 |       |  |

| Pull Down Resistor of Select Pin | RPD    |                                                                                  |     | 560 |     | kΩ    |  |

| FET1 On Resistance               | RF1    | V <sub>DD</sub> = 2.6V, V <sub>GND</sub> = 0V,                                   |     | 75  |     | mΩ    |  |

| FET2 On Resistance               | RF2    | IGND = 10mA                                                                      |     | 75  |     | 11177 |  |

| S1 On Resistance (Closed to A)   | RS1A   | VDD = 2.6V,                                                                      |     | 5   |     |       |  |

| S1 On Resistance (Closed to B)   | RS1B   | VSLEEVE/RING2 = 0V to<br>2.6V,IMIC = ±10mA                                       |     | 5   | -   | Ω     |  |

#### Note:

- (1) Flatness is defined as the difference between maximum and minimum value of ON-resistance at the specified analog signal voltage points.

- (2)  $R_{\text{ON}}$  matching between channels is calculated by subtracting the channel with the lowest max Ron value from the channel with the highest max Ron value.

High Fidelity Stereo SPDT Switch with Pop and Click Elimination

**WWW.TECHPUBLIC.COM**

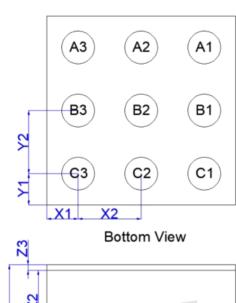

# **Package informantion**

WLCSP-9B(1.2X1.2) (Unit: mm)

.X3

Side View

| Symbol     | Dimensions In Millimeter |       |       |  |  |

|------------|--------------------------|-------|-------|--|--|

| Symbol     | Min.                     | Тур.  | Max.  |  |  |

| X          | 1.145                    | 1.17  | 1.195 |  |  |

| Y          | 1.145                    | 1.17  | 1.195 |  |  |

| X1         |                          | 0.185 |       |  |  |

| X2         |                          | 0.400 |       |  |  |

| Х3         | 0.245                    | 0.270 | 0.295 |  |  |

| Y1         |                          | 0.185 |       |  |  |

| Y2         |                          | 0.400 |       |  |  |

| Z          | 0.535                    | 0.575 | 0.615 |  |  |

| <b>Z</b> 1 | 0.170                    | 0.195 | 0.22  |  |  |

| Z2         | 0.345                    | 0.355 | 0.365 |  |  |

| Z3         | 0.02                     | 0.025 | 0.03  |  |  |