# 4.1-A Brushed DC Motor Driver with **Integrated Current Sense and Regulation**

# (compatible to DRV8251A (TI USA)

#### **Feature** 1.

- N-channel H-bridge brushed DC motor driver

- 4.5V to 48V Operating Supply Voltage Range

- High Output Current Capability: 4.1-A Peak

- Low MOSFET R<sub>DS</sub>(on) Typical 0.50Ω(HS+LS)

- Low Power Sleep Mode

- <2uA at VM=24V, TJ = 25°C

- **PWM Control Interface**

- **Protection Features:**

- Overcurrent Protection (OCP)

- Thermal Shutdown (TSD)

- VM Undervoltage Lockout (UVLO)

# **Applications**

- **POS Printers**

- **Printers**

- Washer and Dryer

- Coffee machine

- Surgical Equipment

- Fitness Machine

# **General Description**

The HT8251A device is an integrated motor driver with N-channel H-bridge, charge pump, current regulation, and protection circuitry. The charge pump improves efficiency by supporting N-channel MOSFET half bridges and 100% duty cycle driving.

An internal current mirror architecture on the IPROPI pin implements current sensing and regulation. This eliminates the need for a large power shunt resistor, saving board area and reducing system cost. The IPROPI current-sense output allows a microcontroller to detect motor stall or changes in load conditions. The external voltage reference pin,

determines the threshold of current regulation during start-up and stall events without interaction from a microcontroller.

A low-power sleep mode achieves ultra-low quiescent current draw by shutting down most of the internal circuitry. Internal protection features include supply undervoltage lockout, output overcurrent, and device overtemperature.

The HT8251A is available in a 8-pin eSOP8

### **Package**

| Part Number | Package | Body Size     |

|-------------|---------|---------------|

| HT8251AREZ  | eSOP8   | 4.9mm x 6.0mm |

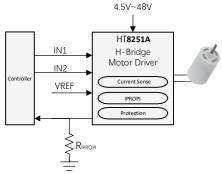

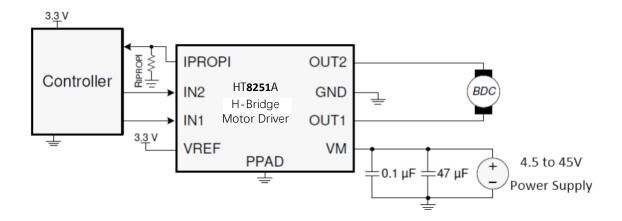

Fig.1 Block diagram of HT8251A

# 5. PIN Definition

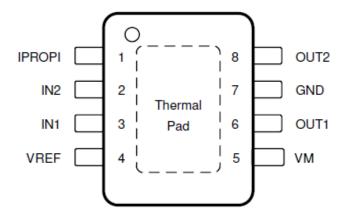

8-Pin HSOP Top View Fig.2 Pad definition of HT8251A

Table 1 Pad Functions

| Pin | Name   | I/O | Description                                                                           |

|-----|--------|-----|---------------------------------------------------------------------------------------|

| 1   | IPROPI | PWR | Analog current output proportional to load current                                    |

| 2   | IN2    | I   | Logic inputs. Controls the H-bridge output. Has internal pulldowns                    |

| 3   | IN1    | I   | Logic inputs. Controls the H-bridge output. Has internal pulldowns                    |

| 4   | VREF   | I   | Analog input. Apply a voltage between 0 to 5 V. For information on current regulation |

| 5   | VM     | PWR | 4.5-V to 48-V power supply. Connect a 0.1-μF bypass capacitor to ground               |

| 6   | OUT1   | I   | H-bridge output. Connect directly to the motor or other inductive load                |

| 7   | GND    | PWR | Device power ground. Connect to system ground.                                        |

| 8   | OUT2   | I   | H-bridge output. Connect directly to the motor or other inductive load                |

# **Absolute Maximum Ratings**

(If out of these ratings, the filter may be fail or damaged)

Table 2

|                                       |                                       |     | MIN                   | MAX                   | UNIT |

|---------------------------------------|---------------------------------------|-----|-----------------------|-----------------------|------|

| Power supply pin voltage              | VM                                    |     | -0.3                  | 50                    | V    |

| Power supply transient voltage ramp   | VM                                    |     | 0                     | 2                     | V/µs |

| Logic pin voltage                     | INx                                   |     | -0.3                  | 7                     | V    |

| Reference input pin voltage           | VR                                    | EF  | -0.3                  | 6                     | V    |

| Output pin voltage                    | OU                                    | Tx  | -0.7                  | VM + 0.7              | V    |

| Current sense input pin voltage       | ISE                                   | EN  | -0.5                  | 1                     | V    |

| Output current                        | OU                                    | Tx  | Internally<br>Limited | Internally<br>Limited | А    |

| Ambient temperature, T <sub>A</sub>   |                                       |     | -40                   | 125                   | °C   |

| Junction temperature, T <sub>J</sub>  |                                       | -40 | 150                   | °C                    |      |

| Storage temperature, T <sub>stg</sub> | Storage temperature, T <sub>stg</sub> |     |                       | 150                   | °C   |

# 6. Recommended Operating Conditions

Table 3

|                   |                                     |      | MIN | TYP | MAX | UNIT |

|-------------------|-------------------------------------|------|-----|-----|-----|------|

| V <sub>VM</sub>   | Power supply voltage                | VM   | 4.5 |     | 48  | ٧    |

| V <sub>VREF</sub> | Reference voltage                   | VREF | 0   |     | 5   | V    |

| V <sub>IN</sub>   | Logic input voltage                 | INx  | 0   |     | 5.5 | V    |

| f <sub>PWM</sub>  | PWM frequency                       | INx  |     | 0   |     | 200  |

| kHz               | Peak output current 4.5V ≤ Vvм<5.5V |      |     |     | 3.7 |      |

| Іоит              | OUTx Peak output current 5.5V ≤ V∨м | OUIX |     |     | 4.1 | Α    |

| T <sub>A</sub>    | Operating ambient temperature       |      | -40 |     | 125 | °C   |

| TJ                | Operating junction temperature      |      | -40 |     | 150 | °C   |

# 7. Electrical Characteristics

Table 4

| PARAMETI                               | ≣R                                   | TEST CONDITIONS                                                                               | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| POWER S                                | JPPLY (VM)                           |                                                                                               |      |      |      |      |

| I <sub>VMQ</sub>                       | VM sleep mode current                | V <sub>VM</sub> = 24 V, IN1 = IN2 = 0, T <sub>J</sub> = 25°C                                  |      |      | 2    | μΑ   |

| I <sub>VM</sub>                        | VM active mode current               | V <sub>VM</sub> = 24 V, IN1 = IN2 = 1                                                         |      | 3    | 4    | mA   |

| t <sub>WAKE</sub>                      | Turn on time                         | Control signal to active mode                                                                 |      |      | 250  | μs   |

| t <sub>SLEEP</sub>                     | Turn off time                        | Control signal to sleep mode                                                                  | 0.8  |      | 1.5  | ms   |

| LOGIC-LE                               | VEL INPUTS (INx)                     |                                                                                               |      |      |      |      |

| V <sub>IL</sub>                        | Input logic low voltage              |                                                                                               |      |      | 0.7  | V    |

| V <sub>IH</sub>                        | Input logic high voltage             |                                                                                               | 1.5  |      |      | V    |

| V <sub>HYS</sub>                       | Input hysteresis                     |                                                                                               |      | 200  |      | mV   |

| I <sub>IL</sub>                        | Input logic low current              | V <sub>IN</sub> = 0 V                                                                         | -1   |      | 1    | μA   |

| I <sub>IH</sub>                        | Input logic high current             | V <sub>IN</sub> = 3.3 V                                                                       |      | 33   | 100  | μA   |

| R <sub>PD</sub>                        | Input pulldown resistance            | To GND                                                                                        |      | 100  |      | kΩ   |

| DRIVER O                               | UTPUTS (OUTx)                        |                                                                                               |      |      | •    |      |

| R <sub>DS(on)_HS</sub>                 | High-side MOSFET on resistance       | V <sub>VM</sub> = 24 V, I = 1 A, f <sub>PWM</sub> = 25 kHz                                    |      | 250  |      | mΩ   |

| R <sub>DS(on)_LS</sub>                 | Low-side MOSFET on resistance        | V <sub>VM</sub> = 24 V, I = 1 A, f <sub>PWM</sub> = 25 kHz                                    |      | 250  |      | mΩ   |

| V <sub>SD</sub>                        | Body diode forward voltage           | I <sub>OUT</sub> = 1 A                                                                        |      | 0.8  |      | V    |

| t <sub>RISE</sub>                      | Output rise time                     | V <sub>VM</sub> = 24 V, OUTx rising from 10% to 90%                                           |      | 220  |      | ns   |

| t <sub>FALL</sub>                      | Output fall time                     | V <sub>VM</sub> = 24 V, OUTx falling from 90% to 10%                                          |      | 220  |      | ns   |

| t <sub>PD</sub>                        | Input to output propagation delay    | INx to OUTx                                                                                   |      | 0.7  | 1    | μs   |

| t <sub>DEAD</sub>                      | Output dead time                     |                                                                                               |      | 200  |      | ns   |

| INTEGRAT                               | ED CURRENT SENSE AND REGULA          | ATION (IPROPI, VREF)                                                                          |      |      |      |      |

| A <sub>IPROPI</sub>                    | Current mirror scaling factor        |                                                                                               |      | 1500 |      | uA/A |

| AERR                                   | Current mirror total error           | $I_{OUT} = 1.5 \text{ A}, V_{VM} \geqslant 6.5 \text{ V}, V_{IPROPI} \leqslant 3.0 \text{ V}$ | -5   |      | 5    | %    |

| t <sub>OFF</sub>                       | Current regulation off time          |                                                                                               |      | 25   |      | μs   |

| t <sub>BLANK</sub>                     | Current regulation blanking time     |                                                                                               |      | 2    |      | μs   |

| t <sub>DEG</sub>                       | Current regulation deglitch time     |                                                                                               |      | 0.7  |      | μs   |

| PROTECT                                | ON CIRCUITS                          |                                                                                               |      |      |      |      |

| V <sub>UVLO</sub>                      |                                      | Supply rising                                                                                 | 4.15 | 4.3  | 4.45 | V    |

| VUVLO                                  | Supply undervoltage lockout (UVLO)   | Supply falling                                                                                | 4.05 | 4.2  | 4.35 | V    |

| V <sub>UVLO_HYS</sub>                  | Supply UVLO hysteresis               | Rising to falling threshold                                                                   |      | 100  |      | mV   |

| t <sub>UVLO</sub>                      | Supply undervoltage deglitch time    |                                                                                               |      | 10   |      | us   |

|                                        |                                      | 4.5V≤Vvм<5.5V                                                                                 | 3.7  |      |      |      |

| loce Overcurrent protection trip point |                                      | 5.5V≤VvM                                                                                      | 4.1  |      |      | Α    |

| tocp                                   | Overcurrent protection deglitch time |                                                                                               |      | 2    |      | μs   |

| t <sub>RETRY</sub>                     | Overcurrent protection retry time    |                                                                                               |      | 3    |      | ms   |

| Ttsd                                   | Thermal shutdown temperature         |                                                                                               |      | 165  |      | °C   |

### 8. Detailed Description

#### 8.1 Overview

The HT8251A is an 8-pin device for driving brushed DC motors from a 4.5-V to 48-V supply rail. Two logic inputs control the H-bridge driver, which consists of four N-channel MOSFETs that have a typical RDS(on) of 500 m $\Omega$  (including one high-side and one low-side FET). A single power input, VM, serves as both device power and

the motor winding bias voltage. The integrated charge pump of the device boosts VM internally and fully enhances the high-side FETs. Motor speed can be controlled with pulse-width modulation at frequencies between 0 to 200 kHz. The device enters a low-power sleep mode by bringing both inputs low.

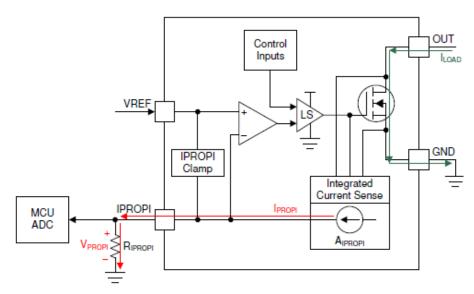

The HT8251A also integrates current sense feedback to a microcontroller using current mirrors on the low-side power MOSFETs. The IPROPI pin sources a small current that is proportional to the current in the MOSFETs. This current can be converted to a proportional voltage using an external resistor (RIPROPI). This integrated current sensing scheme out-performs traditional external shunt resistor sensing by providing current information even during the off-time slow decay recirculating period and removing the need for an external power shunt resistor. The integrated current regulation feature allows the device to limit the output current with a fixed off-time PWM chopping scheme. The VREF pin configures the current regulation level during motor operation to limit the load current.

A variety of integrated protection features protect the device in the case of a system fault. These include undervoltage lockout (UVLO), overcurrent protection (OCP), and overtemperature shutdown (TSD).

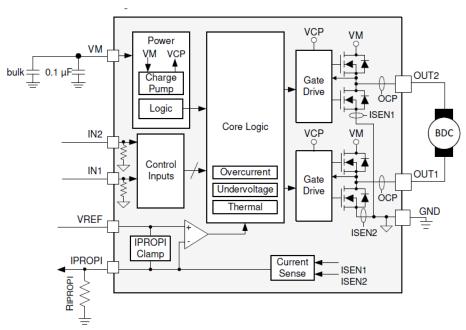

# 8.2 Functional Block Diagram

Figure 3. Function Block Diagram

### 8.3 Bridge Control

The HT8251A output consists of four N-channel MOSFETs that are designed to drive high current. These outputs are controlled by the two logic inputs IN1 and IN2 as listed in table 5.

| Table 6 11 Enage Logic |                        |        |             |                                                               |  |  |  |

|------------------------|------------------------|--------|-------------|---------------------------------------------------------------|--|--|--|

| IN1                    | IN2 OUT1 OUT2 DESCRIPT |        | DESCRIPTION |                                                               |  |  |  |

| 0                      | 0                      | High-Z | High-Z      | Coast; H-bridge disabled to High-Z (sleep entered after 1 ms) |  |  |  |

| 0                      | 1                      | L      | Н           | Reverse (Current OUT2 → OUT1)                                 |  |  |  |

| 1                      | 0                      | Н      | L           | Forward (Current OUT1 → OUT2)                                 |  |  |  |

| 1                      | 1                      | L      | L           | Brake; low-side slow decay                                    |  |  |  |

Table 5 H-Bridge Logic

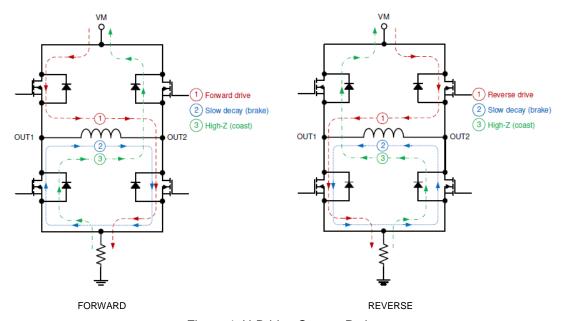

The inputs can be set to static voltages for 100% duty cycle drive, or they can be pulse-width modulated (PWM) for variable motor speed. When using PWM, switching between driving and braking typically works best. For example, to drive a motor forward with 50% of the maximum RPM, IN1 = 1 and IN2 = 0 during the driving period, and IN1 = 1 and IN2 = 1 during the other period. Alternatively, the coast mode (IN1 = 0, IN2 = 0) for fast current decay is also available. Figure 4 shows how the motor current flows through the H-bridge. The input pins can be powered before VM is applied.

Figure 4. H-Bridge Current Paths

### 8.4 Current Sense and Regulation (IPROPI)

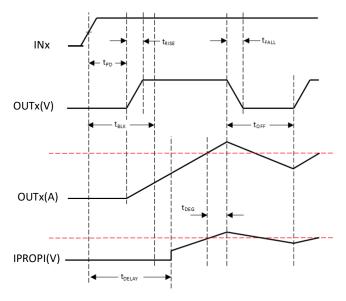

The HT8251A device integrates current sensing, regulation, and feedback as part of the IPROPI feature. These features allow the device to sense the output current without an external sense resistor or sense circuitry reducing system size, cost, and complexity. This also allows for the device to limit the output current in the case of motor stall or high torque events and give detailed feedback to the controller about the load current through a current proportional output. The figure5 shows the IPROPI timings specified in the Electrical Characteristics table.

Figure 5. Detailed IPROPI Timing Diagram

## 8.5 Current Sensing

The IPROPI pin outputs an analog current proportional to the current flowing through the low-side power MOSFETs in the H-bridge scaled by AIPROPI. The IPROPI output current can be calculated by equation1. The ILSX in equation1 is only valid when the current flows from drain to source in the low-side MOSFET. If current flows from source to drain or through the body diode, the value of ILSX for that channel is zero. For instance, if the bridge is in the brake, slow-decay state, then the current out of IPROPI is only proportional to the current in one of the low-side MOSFETs.

IPROPI

$$(\mu A) = (ILS1 + ILS2) (A) \times AIPROPI (\mu A/A)$$

(1)

The Aerr parameter in the Electrical Characteristics table is the error associated with the Aipropi gain. It indicates the combined effect of offset error added to the IOUT current and gain error. The motor current is measured by an internal current mirror architecture on the low-side FETs which removes the need for an external power sense resistor as shown in Figure 6. The current mirror architecture allows for the motor winding current to be sensed in both the drive and brake low-side slow-decay periods allowing for continuous current monitoring in typical bidirectional brushed DC motor applications. In coast mode, the current is freewheeling and cannot be sensed because it flows from source to drain. However, the current can be sampled by briefly re-enabling the driver in either drive or slow-decay modes and measuring the current before switching back to coast mode again.

After toff elapses, the output is re-enabled according to the two inputs, Inx. The drive time (tdrive) until reaching another ITRIP event heavily depends on the VM voltage, the back-EMF of the motor, and the inductance of the motor.

Figure 6. Integrated Current Sensing

The IPROPI pin should be connected to an external resistor (RIPROPI) to ground in order to generate a proportional voltage (VIPROPI) on the IPROPI pin with the IIPROPI analog current output. This allows for the load current to be measured as the voltage drop across the RIPROPI resistor with a standard analog to digital converter (ADC). The RIPROPI resistor can be sized based on the expected load current in the application so that the full range of the controller ADC is utilized. Additionally, the HT8251A device implements an internal IPROPI voltage clamp circuit to limit VIPROPI with respect to VVREF on the VREF pin and protect the external ADC in case of output overcurrent or unexpected high current events.

VIPROPI (V) = IPROPI (A)

$$\times$$

RIPROPI ( $\Omega$ ) (2)

The corresponding IPROPI voltage to the output current can be calculated by equation 2.

The IPROPI output bandwidth is limited by the sense delay time (tdelay) of the internal current sensing circuit. This time is the delay from the low-side MOSFET enable command (from the INx pins) to the IPROPI output being ready. If the device is alternating between drive and slow-decay (brake) in an H-bridge PWM pattern, then the low-side MOSFET sensing the current is continuously on and the sense delay time has no impact to the IPROPI output. If a command on the INx pins disables the low-side MOSFETs, the IPROPI output will disable with the input logic signal. Although the low-side MOSFETs may still conduct current as they disable according to the device slew rate (noted in the Electrical Characteristics table by trise time), IPROPI will not represent the current in the low-side MOSFETs during this turnoff time.

### 8.6 Current Regulation

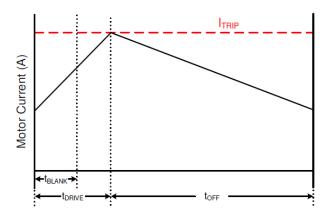

The HT8251A device integrates current regulation using a fixed off-time current chopping scheme. This allows the devices to limit the output current in case of motor stall, high torque, or other high current load events without involvement from the external controller as shown in Figure 7.

Figure 7. Current-Regulation Time Periods

The current chopping threshold (ITRIP) is set through a combination of the VREF voltage (VVREF) and IPROPI output resistor (RIPROPI). This is done by comparing the voltage drop across the external RIPROPI resistor to VVREF with an internal comparator.

ITRIP (A) x AIPROPI (

$$\mu$$

A/A) = VVREF (V) / RIPROPI ( $\Omega$ ) (3)

For example, if  $V_{VREF} = 3.3V$ ,  $R_{IPROPI} = 1310\Omega$ , and  $A_{IPROPI} = 1575 \,\mu\text{A/A}$ , then  $I_{TRIP}$  will be approximately 1.6 A.

The fixed off-time current chopping scheme supports up to 100% duty cycle current regulation since the H-bridge automatically enables after the toff period and does not require a new control input edge on the INx pins to reset the outputs. When the motor current exceeds the ITRIP threshold, the outputs will enter a current chopping mode with a fixed off time (toff). During toff, the H-bridge enters a brake/low-side slow decay state (both low-side MOSFETs ON) for toff duration after lout exceeds Itrip. After toff, the outputs re-enable according to the control inputs if lout is less than Itrip. If lout is still greater than Itrip, the H-bridge enters another period of brake/low-side slow decay for toff. If the state of the INx control pins changes during the toff time, the remainder of the toff time is ignored, and the outputs will again follow the inputs.

The ITRIP comparator has both a blanking time (tblk) and a deglitch time (tdle). The internal blanking time helps to prevent voltage and current transients during output switching from effecting the current regulation. These transients may be caused by a capacitor inside the motor or on the connections to the motor terminals. The internal deglitch time ensures that transient conditions do not prematurely trigger the current regulation. In certain cases, where the transient conditions are longer than the deglitch time, placing a 10-nF capacitor on the IPROPI pin, close to the device, will help filter the transients on IPROPI output so current regulation does not prematurely trigger. The capacitor value can be adjusted as needed, however large capacitor values may slow down the response time of the current regulation circuitry.

# 8.7 Protection Circuits

The HT8251 device is fully protected against VM undervoltage, overcurrent, and overtemperature events.

### 8.7.1 Overcurrent Protection (OCP)

An analog current limit circuit on each FET limits the current through the FET by limiting the gate drive internally. If this analog current limit persists for longer than the OCP deglitch time (tocp), all FETs in the H-bridge will disable. The driver re-enables after the OCP retry period (tretry) has passed. If the fault condition is still present, the cycle repeats.

#### 8.7.2 Thermal Shutdown (TSD)

If the die temperature exceeds safe limits, all FETs in the H-bridge are disabled. After the die temperature has fallen to a safe level, operation automatically resumes.

#### 8.7.3 Thermal Shutdown (TSD)

If the die temperature exceeds safe limits, all FETs in the H-bridge are disabled. After the die temperature has fallen to a safe level, operation automatically resumes.

#### 8.7.4 VM Undervoltage Lockout (UVLO)

Whenever the voltage on the VM pin falls below the UVLO falling threshold voltage, VUVLO, all circuitry in the device is disabled, the output FETS are disabled, and all internal logic is reset.

#### 8.8 Device Functional Modes

Table 6 summarizes the HT8251A functional modes described in this section.

| MODE                 | CONDITION               | H-BRIDGE  | INTERNAL CIRCUITS |

|----------------------|-------------------------|-----------|-------------------|

| Active Mode          | IN1 or IN2 = logic high | Operating | Operating         |

| Low-Power Sleep Mode | IN1 = IN2 = logic low   | Disabled  | Disabled          |

| Fault Mode           | Any fault condition met | Disabled  | See Table 7       |

Table 6 Modes of Operation

#### 8.8.1 Active Mode

After the supply voltage on the VM pin has crossed the undervoltage threshold VuvLo, the INx pins are in a state other than IN1 = 0 & IN2 = 0, and twake has elapsed, the device enters active mode. In this mode, the H-bridge, charge pump, and internal logic are active and the device is ready to receive inputs.

### 8.8.2 Low-Power Sleep Mode

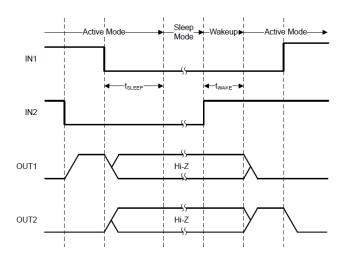

When the IN1 and IN2 pins are both low for time tsleep, the HT8251A device enters a low-power sleep mode. In sleep mode, the outputs remain High-Z and the device draws minimal current from the supply pin (IVMQ). If the device is powered up while all inputs are low, it immediately enters sleep mode. After any of the input pins are set high for longer than the duration of twake, the device becomes fully operational. Figure 8 shows an example timing diagram for entering and leaving sleep mode.

Figure 8. Sleep Mode Entry and Wakeup Timing Diagram

#### 8.8.3 Fault Mode

The HT8251A device enters a fault mode when a fault is encountered. This is utilized to protect the device and the output load. The device behavior in the fault mode is described in and depends on the fault condition. The device will leave the fault mode and re-enter the active mode when the recovery condition is met.

| rabio i i dan conditione cammary |                                     |          |                   |                                                      |  |

|----------------------------------|-------------------------------------|----------|-------------------|------------------------------------------------------|--|

| FAULT                            | CONDITION                           | H-BRIDGE | INTERNAL CIRCUITS | RECOVERY                                             |  |

| VM undervoltage (UVLO)           | $V_{M} < V_{UVLO,falling}$          | Disabled | Disabled          | $V_M > V_{UVLO,rising}$                              |  |

| Overcurrent (OCP)                | I <sub>OUT</sub> > I <sub>OCP</sub> | Disabled | Operating         | I <sub>OUT</sub> < I <sub>OCP</sub>                  |  |

| Thermal Shutdown (TSD)           | $T_J > T_{TSD}$                     | Disabled | Operating         | T <sub>J</sub> < T <sub>TSD</sub> - T <sub>HYS</sub> |  |

Table 7 Fault Conditions Summary

# 8.9 Typical Application

Figure 9. Typical Application Schematic

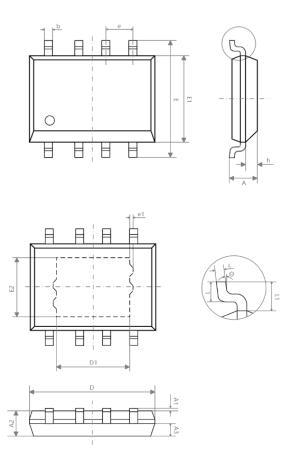

# 9. Package (eSOP 4.9\*6.0-8)

| <i>*</i> *□ | 毫米(mm)    |           |      |  |  |

|-------------|-----------|-----------|------|--|--|

| 符号          | 最小        | 典型        | 最大   |  |  |

| Α           |           |           | 1.65 |  |  |

| <b>A</b> 1  | 0.05      |           | 0.15 |  |  |

| A2          | 1.30      | 1.40      | 1.50 |  |  |

| <b>A</b> 3  | 0.60      | 0.65      | 0.70 |  |  |

| b           | 0.39      |           | 0.47 |  |  |

| D           | 4.80      | 4.90      | 5.00 |  |  |

| E           | 5.80      | 6.00      | 6.20 |  |  |

| E1          | 3.80      | 3.90      | 4.00 |  |  |

| e           | 1.27(BSC) |           |      |  |  |

| h           | 0.25      |           | 0.50 |  |  |

| L           | 0.50      | 0.60      | 0.80 |  |  |

| L1          |           | 1.05(REF) |      |  |  |

| θ           | 0         |           | 8°   |  |  |

| e1          | 0.10(REF) |           |      |  |  |

| D1          | 3.10(REF) |           |      |  |  |

| E2          |           | 2.21(REF) |      |  |  |

# 免责声明核心条款

本规格书所载信息由[深圳市海天芯微电子有限公司](以下简称"海天芯")提供,仅作为技术参考文档使用。本公司不对规格书中任何数据的准确性、完整性或适用性作出明示或暗示的保证,包括但不限于:

- 1.更新与终止:本公司保留随时修改、补充或终止本规格书的权利,恕不另行通知。

- 2.设计参数、性能指标及测试结果可能因实际应用环境、制造工艺或第三方组件 差异而发生变化。

- 3.文档中引用的第三方技术或专利信息可能存在更新滞后,建议用户自行核实最 新状态。

- 4.规格书不构成对产品功能、可靠性或安全性的承诺,实际表现需经用户独立验证。

- 5.因使用本规格书信息导致的直接、间接、特殊或衍生性损失(包括但不限于利润损失、生产中断或数据损坏)。

- 6.用户基于未经验证的设计参数实施工程决策所产生的后果。

- 7.第三方知识产权侵权索赔,除非该侵权由本公司故意行为直接导致。

- 8.在应用本规格书前,自行评估设计可行性并承担全部技术风险。

- 9.不将文档内容用于未经授权的商业目的或侵犯第三方权益。

- 10.发现信息矛盾或缺陷时,立即停止使用并通知本公司。