**LKAD7606LQ 型**

**16 位 ADC**

**产品说明书**

瓴科微

# LKAD7606LQ 型 8 通道，16 位 ADC

## 1 特点

- 8 通道同步采样输入

- 真双极性模拟输入范围:  $\pm 10V$ 、 $\pm 5V$

- 5V 单模拟电源, VDRIVE: 2.5V~5V

- 模拟输入钳位保护 $\pm 22V$

- 具有  $1M\Omega$  模拟输入阻抗

- 片内精密基准电压

- 16 位、200kSPS ADC(所有通道)

- 最大支持 64 倍过采样

- 支持并行和串行接口

- 工作温度:  $-40^{\circ}C \sim +85^{\circ}C$

- 封装: LQFP 塑封

## 2 应用

- 电力线监控和继电保护

- 工业自动化和控制

- 数据采集系统 (DAS)

- 自动化测试设备

- 多相电机控制

## 3 概述

LKAD7606LQ 是一款 8 通道 16 位精度的同步采样模数转换器。LKAD7606LQ 采用 5V 单电源供电, 可以处理 $\pm 10V$  和 $\pm 5V$  的真双极性输入信号, 所有通道均能以 200kSPS 的吞吐速率采样。

LKAD7606LQ 提供  $1M\Omega$  的输入阻抗以及二阶低通滤波器, 因此无需片外驱动运算放大器。芯片内置模拟输入钳位保护, 二阶低通滤波器, 2.5V 低温漂基准电压源以及高速串行和并行接口。同时, LKAD7606LQ 支持最高 64 倍过采样及数字滤波, 提升 SNR 性能, 并降低 3dB 带宽。

### 器件信息

| 型号         | 封装     | 封装尺寸                 |

|------------|--------|----------------------|

| LKAD7606LQ | LQFP64 | 10.0mm×10.0mm×1.60mm |

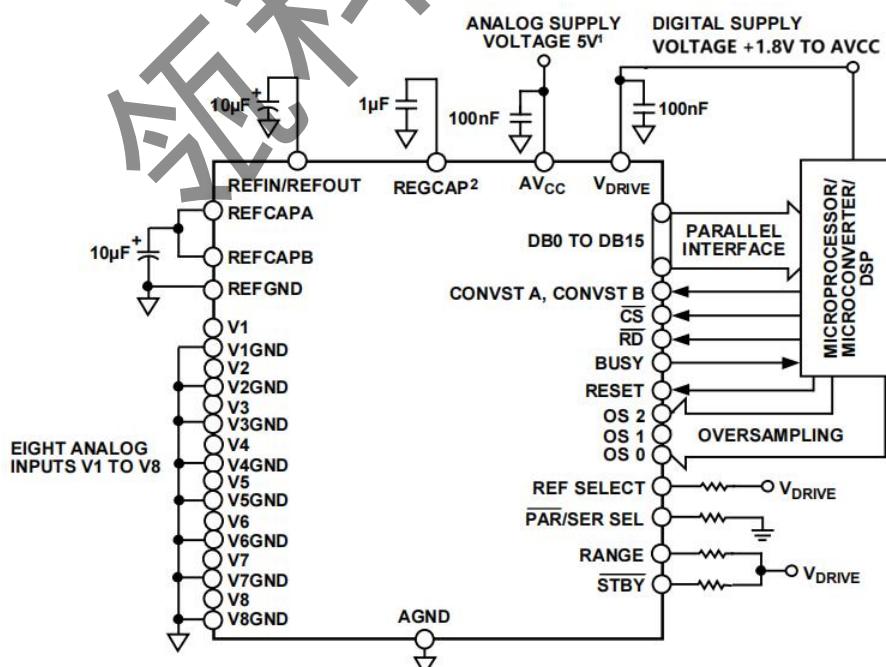

图 1 典型应用图

## 目 录

|                       |    |

|-----------------------|----|

| 1 特点 .....            | 1  |

| 2 应用 .....            | 1  |

| 3 概述 .....            | 1  |

| 4 管脚排布与功能描述 .....     | 4  |

| 4.1 引脚排列 .....        | 4  |

| 5 电特性 .....           | 6  |

| 5.1 绝对最大额定值 .....     | 6  |

| 5.2 推荐工作条件 .....      | 6  |

| 5.3 热性能信息 .....       | 6  |

| 5.4 电特性 .....         | 6  |

| 5.5 时序特性 .....        | 8  |

| 6 特性曲线 .....          | 11 |

| 7 工作原理 .....          | 13 |

| 7.1 转换器描述 .....       | 13 |

| 7.2 模拟输入及钳位保护 .....   | 13 |

| 7.3 模拟输入低通滤波器 .....   | 14 |

| 7.4 内部/外部基准电压 .....   | 14 |

| 7.5 复位功能 .....        | 14 |

| 7.6 转换控制 .....        | 15 |

| 7.7 省电模式 .....        | 15 |

| 7.8 数字接口 .....        | 16 |

| 7.9 串行接口模式 .....      | 16 |

| 7.10 并行接口模式 .....     | 16 |

| 7.11 并行字节接口模式 .....   | 16 |

| 7.12 转换期间读取 .....     | 17 |

| 7.13 数字滤波器（过采样） ..... | 17 |

| 8 应用信息 .....          | 18 |

| 8.1 典型应用 .....        | 18 |

| 9 封装形式 .....          | 19 |

| 10 机械、包装和可订购的信息 ..... | 20 |

| 10.1 托盘信息 .....       | 20 |

| 10.2 载带和卷盘信息 .....    | 21 |

| 10.3 订货信息 .....       | 22 |

| 11 版本信息 .....         | 23 |

## 4 管脚排布与功能描述

### 4.1 引脚排列

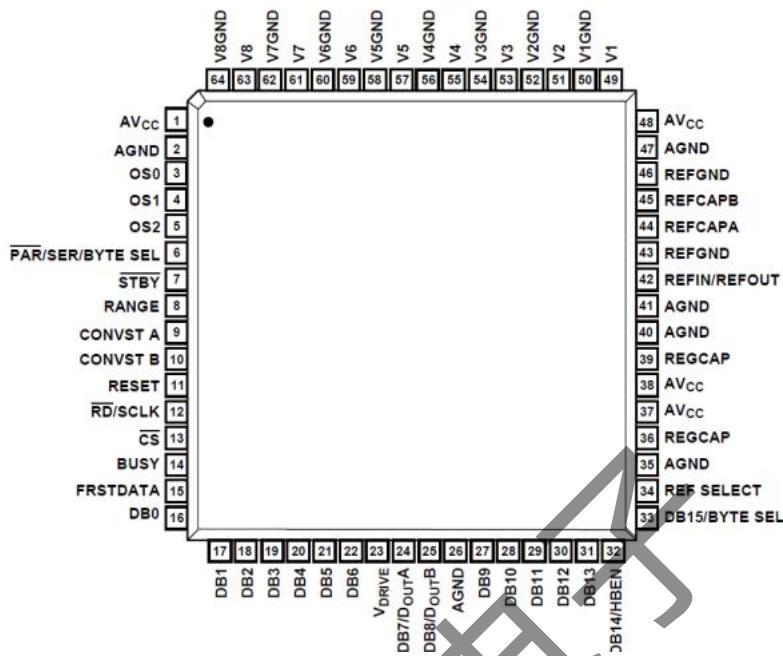

图2 引脚排列图（顶视图）

表1 引脚说明

| 引脚编号 | 引脚名字     | IO 类型 | 描述                                                                  |

|------|----------|-------|---------------------------------------------------------------------|

| 1    | AVCC     | P     | 模拟电源电压 5.0V                                                         |

| 2    | AGND     | G     | 模拟地                                                                 |

| 3    | OS0      | IP    | 过采样控制引脚，可配置 2 至 64 倍过采样                                             |

| 4    | OS1      | IP    | 过采样控制引脚，可配置 2 至 64 倍过采样                                             |

| 5    | OS2      | IP    | 过采样控制引脚，可配置 2 至 64 倍过采样                                             |

| 6    | PAR_N    | IP    | 输出模式选择，可配置并行，串行及字节模式                                                |

| 7    | STBY_N   | IP    | 待机模式控制引脚                                                            |

| 8    | RANGE    | IP    | 模拟输入范围选择引脚，可配置±10V 和±5V 输入范围<br>RANGE=1, ±10V 范围<br>RANGE=0, ±5V 范围 |

| 9    | CONVST_A | IP    | 转换开启引脚，通道 1 至通道 4                                                   |

| 10   | CONVST_B | IP    | 转换开启引脚，通道 5 至通道 8                                                   |

| 11   | RESET    | IP    | 复位引脚，典型脉宽 50ns                                                      |

| 12   | RD_N     | IP    | 串行或并行接口时钟输入                                                         |

| 13   | CS_N     | IP    | 串行或并行接口片选                                                           |

| 14   | BUSY     | OP    | 转换指示信号，BUSY 下降沿锁存转换数据                                               |

| 15   | FRSTDATA | OP    | 串行或并行接口第一通道 V1 指示信号                                                 |

| 16   | DB0      | OP    | 并行数据输出 DB0                                                          |

| 17   | DB1      | OP    | 并行数据输出 DB1                                                          |

| 18   | DB2      | OP    | 并行数据输出 DB2                                                          |

| 19   | DB3      | OP    | 并行数据输出 DB3                                                          |

|    |               |    |                                                                                         |

|----|---------------|----|-----------------------------------------------------------------------------------------|

| 20 | DB4           | OP | 并行数据输出 DB4                                                                              |

| 21 | DB5           | OP | 并行数据输出 DB5                                                                              |

| 22 | DB6           | OP | 并行数据输出 DB6                                                                              |

| 23 | VDRIVE        | P  | 接口 IO 电源输入                                                                              |

| 24 | DB7           | OP | 并行数据输出 DB7,或串行数据 DoutA                                                                  |

| 25 | DB8           | OP | 并行数据输出 DB7,或串行数据 DoutB                                                                  |

| 26 | AGND          | G  | 接口 IO 地                                                                                 |

| 27 | DB9           | OP | 并行数据输出 DB9                                                                              |

| 28 | DB10          | OP | 并行数据输出 DB10                                                                             |

| 29 | DB11          | OP | 并行数据输出 DB11                                                                             |

| 30 | DB12          | OP | 并行数据输出 DB12                                                                             |

| 31 | DB13          | OP | 并行数据输出 DB13                                                                             |

| 32 | DB14/HBEN     | OP | 并行数据输出 DB14, HBEN 并行字节模式时有效<br>HBEN=0, 首先输出 LSB, 然后输出 MSB<br>HBEN=1, 首先输出 MSB, 然后输出 LSB |

| 33 | DB15/BYTE_SEL | OP | 并行数据输出 DB15, 并行字节模式选择                                                                   |

| 34 | REF_SELECT    | IP | 内部、外部基准电压选择输入<br>REF_SELECT=0, 内部基准<br>REF_SELECT=1, 外部基准                               |

| 35 | AGND          | G  | 模拟地                                                                                     |

| 36 | REGCAP        | P  | 内部稳压器去耦电容引脚, 1uF 陶瓷电容, 1.83V                                                            |

| 37 | AVCC          | P  | 模拟电源电压 5.0V                                                                             |

| 38 | AVCC          | P  | 模拟电源电压 5.0V                                                                             |

| 39 | REGCAP        | P  | 内部稳压器去耦电容引脚, 1uF 陶瓷电容, 1.90V                                                            |

| 40 | AGND          | G  | 模拟地                                                                                     |

| 41 | AGND          | G  | 模拟地                                                                                     |

| 42 | REFIN/REFOUT  | IP | 基准电压输入/基准电压输出, 2.5V, 外接 10uF 去耦电容                                                       |

| 43 | REFGND        | G  | 基准电压地                                                                                   |

| 44 | REFCAPA       | OP | 基准电压去耦引脚, 4.5V, 10uF 低 ESR 陶瓷去耦电容                                                       |

| 45 | REFCAPB       | OP | 基准电压去耦引脚, 4.5V, 10uF 低 ESR 陶瓷去耦电容                                                       |

| 46 | REFGND        | G  | 基准电压地                                                                                   |

| 47 | AGND          | G  | 模拟地                                                                                     |

| 48 | AVCC          | P  | 模拟电源电压 5.0V                                                                             |

| 49 | V1            | IP | 模拟输入引脚                                                                                  |

| 50 | V1GND         | IP | 模拟输入引脚接地                                                                                |

| 51 | V2            | IP | 模拟输入引脚                                                                                  |

| 52 | V2GND         | IP | 模拟输入引脚接地                                                                                |

| 53 | V3            | IP | 模拟输入引脚                                                                                  |

| 54 | V3GND         | IP | 模拟输入引脚接地                                                                                |

| 55 | V4            | IP | 模拟输入引脚                                                                                  |

| 56 | V4GND         | IP | 模拟输入引脚接地                                                                                |

| 57 | V5            | IP | 模拟输入引脚                                                                                  |

| 58 | V5GND         | IP | 模拟输入引脚接地                                                                                |

|    |       |    |          |

|----|-------|----|----------|

| 59 | V6    | IP | 模拟输入引脚   |

| 60 | V6GND | IP | 模拟输入引脚接地 |

| 61 | V7    | IP | 模拟输入引脚   |

| 62 | V7GND | IP | 模拟输入引脚接地 |

| 63 | V8    | IP | 模拟输入引脚   |

| 64 | V8GND | IP | 模拟输入引脚接地 |

## 5 电特性

### 5.1 绝对最大额定值

| 参数                   | 最小值  | 最大值                     | 单位 |

|----------------------|------|-------------------------|----|

| AVCC 至 AGND          | -0.3 | +7                      | V  |

| VDRIVE 至 AGND        | -0.3 | AVCC+0.3                | V  |

| REFIN 至 ANGD         | -0.3 | AVCC+0.3                | V  |

| 模拟输入电压至 AGND         | -22  | +22                     | V  |

| 数字输入电压至 AGND         | -0.3 | V <sub>DRIVE</sub> +0.3 | V  |

| 数字输出电压至 AGND         | -0.3 | V <sub>DRIVE</sub> +0.3 | V  |

| 输入电流至除电源外的任何引脚       | -10  | +10                     | mA |

| 工作温度范围(TA)           | -40  | +85                     | °C |

| 存储温度范围(TSTG)         | -65  | +150                    | °C |

| 铅锡焊接温度(TL, 回流焊 10 秒) | -    | 260                     | °C |

### 5.2 推荐工作条件

| 参数     | 描述     | 最小值 | 标准值 | 最大值  | 单位 |

|--------|--------|-----|-----|------|----|

| AVCC   | 模拟电源   | 4.5 | 5   | 5.5  | V  |

| VDRIVE | 数字接口电源 | 1.8 | 3.3 | AVCC | V  |

### 5.3 热性能信息

| 热指标                     | LKAD7606LQ<br>64 个引脚 | 单位   |

|-------------------------|----------------------|------|

|                         |                      |      |

| R <sub>θJA</sub> 结至环境热阻 | 50                   | °C/W |

### 5.4 电特性

若无特殊说明，测试条件为 TA = -40°C~+85°C, VREF=2.5V 内部基准电压, AVCC=5V, VDRIVE=3.3V, fSAMPLE=200kSPS。

| 参数       | 描述                         | 最小值 | 标准值  | 最大值 | 单位   |

|----------|----------------------------|-----|------|-----|------|

| 转换速率     |                            |     |      |     |      |

| 转换时间     | 所有八个通道                     | -   | 4    | -   | us   |

| 采样保持时间   | -                          | -   | 1    | -   | us   |

| 吞吐速率     | -                          | -   | -    | 200 | kSPS |

| 动态特性     |                            |     |      |     |      |

| 信噪比(SNR) | 无过采样,±10V 范围, fin=1kHz 正弦波 | 80  | 89.5 | -   | dB   |

|          | 无过采样,±5V 范围, fin=1kHz 正弦波  | 80  | 89   | -   | dB   |

|                |                                              |     |           |          |                  |

|----------------|----------------------------------------------|-----|-----------|----------|------------------|

|                | 16 倍过采样, $\pm 10V$ 范围,<br>$f_{in}=130Hz$ 正弦波 | -   | 96        | -        | dB               |

|                | 16 倍过采样, $\pm 5V$ 范围, $f_{in}=130Hz$<br>正弦波  | -   | 95        | -        | dB               |

| 信纳比(SINAD)     | 无过采样, $\pm 10V$ 范围, $f_{in}=1kHz$ 正弦波        | -   | 88.9      | -        | dB               |

|                | 无过采样, $\pm 5V$ 范围, $f_{in}=1kHz$ 正弦波         | -   | 88.2      | -        | dB               |

| 总谐波失真(THD)     | -                                            | -80 | -102      | -        | dB               |

| 峰值谐波(SFDR)     | -                                            | -80 | -106      | -        | dB               |

| 通道间隔离度         | -                                            | -   | -90       | -        | dB               |

| 模拟输入带宽         |                                              |     |           |          |                  |

| 全功率带宽          | -3dB, $\pm 10V$ 范围                           | -   | 18        | -        | kHz              |

|                | -3dB, $\pm 5$ 范围                             | -   | 11        | -        | kHz              |

|                | -0.1dB, $\pm 10V$ 范围                         | -   | 9         | -        | kHz              |

|                | -0.1dB, $\pm 5V$ 范围                          | -   | 5         | -        | kHz              |

| $t_{GROUP}$ 延迟 | $\pm 10V$ 范围                                 | -   | 12        | -        | us               |

|                | $\pm 5V$ 范围                                  | -   | 16        | -        | us               |

| 静态特性           |                                              |     |           |          |                  |

| 分辨率            | 无失码                                          | 16  | -         | -        | Bits             |

| 微分非线性(DNL)     | -                                            | -   | $\pm 0.5$ | -        | LSB              |

| 积分非线性(INL)     | -                                            | -   | $\pm 1$   | -        | LSB              |

| 正满量程误差匹配       | 内部基准                                         | -   | $\pm 6$   | -        | LSB              |

|                | 外部基准                                         | -   | $\pm 6$   | $\pm 30$ | LSB              |

| 正满量程误差漂移       | 内部基准                                         | -   | $\pm 5$   | -        | ppm/ $^{\circ}C$ |

|                | 外部基准                                         | -   | $\pm 2$   | -        | ppm/ $^{\circ}C$ |

| 正满量程误差匹配       | $\pm 10V$ 范围                                 | -   | 5         | -        | LSB              |

|                | $\pm 5V$ 范围                                  | -   | 10        | 20       | LSB              |

| 双极性零代码误差       | $\pm 10V$ 范围                                 | -   | $\pm 1$   | -        | LSB              |

|                | $\pm 5V$ 范围                                  | -   | $\pm 2$   | $\pm 10$ | LSB              |

| 双极性零代码漂移       | $\pm 10V$ 范围                                 | -   | 10        | -        | LSB              |

|                | $\pm 5V$ 范围                                  | -   | 5         | -        | LSB              |

| 双极性零代码匹配       | $\pm 10V$ 范围                                 | -   | 1         | 5        | LSB              |

|                | $\pm 5V$ 范围                                  | -   | 2         | 20       | LSB              |

| 负满量程误差匹配       | 内部基准                                         | -   | $\pm 6$   | -        | LSB              |

|                | 外部基准                                         | -   | $\pm 6$   | $\pm 30$ | LSB              |

| 负满量程误差漂移       | 内部基准                                         | -   | $\pm 5$   | -        | ppm/ $^{\circ}C$ |

|                | 外部基准                                         | -   | $\pm 2$   | -        | ppm/ $^{\circ}C$ |

| 负满量程误差匹配       | $\pm 10V$ 范围                                 | -   | 5         | -        | LSB              |

|                | $\pm 5V$ 范围                                  | -   | 10        | 20       | LSB              |

| 模拟输入           |                                              |     |           |          |                  |

| 输入电压范围         | RANG=1                                       | -   | -         | $\pm 10$ | V                |

|                | RANG=0                                       | -   | -         | $\pm 5$  | V                |

|                    |            |                        |         |                        |                   |

|--------------------|------------|------------------------|---------|------------------------|-------------------|

| 模拟输入电流             | 10V 输入     | -                      | 8       | -                      | uA                |

|                    | 5V 输入      | -                      | 3       | -                      | uA                |

| 模拟输入电容             | 8 通路模拟输入   | -                      | 5       | -                      | pF                |

| 输入阻抗               | 8 通路模拟输入   | -                      | 1       | -                      | Mohm              |

| 基准输入输出             |            |                        |         |                        |                   |

| 基准输入电压范围           | -          | 2.475                  | 2.5     | 2.525                  | V                 |

| 基准输出电压             | -          | 2.49                   | -       | 2.505                  | V                 |

| 基准源温度系数            | -          | -                      | $\pm 5$ | -                      | ppm/ $^{\circ}$ C |

| 逻辑输入输出             |            |                        |         |                        |                   |

| 输入高电压              | -          | $0.9 \times V_{DRIVE}$ | -       | -                      | V                 |

| 输入低电压              | -          | -                      | -       | $0.1 \times V_{DRIVE}$ | V                 |

| 输入电流               | -          | -                      | -       | $\pm 2$                | uA                |

| 输入电容               | -          | -                      | 5       | -                      | pF                |

| 输出高电压              | -          | $V_{DRIVE} - 0.2$      | -       | -                      | V                 |

| 输出低电压              | -          | -                      | -       | 0.2                    | V                 |

| 浮空态漏电流             | -          | -                      | $\pm 2$ | -                      | uA                |

| 浮空态输出电容            | -          | -                      | 5       | -                      | pF                |

| 输出编码格式             | 二进制补码      | -                      | -       | -                      | -                 |

| 电源要求及功耗            |            |                        |         |                        |                   |

| AVCC               | -          | 4.75                   | 5       | 5.25                   | V                 |

| V <sub>DRIVE</sub> | -          | 1.8                    | -       | 5.25                   | V                 |

| 正常不转换模式            | ADC 静态不转换  | -                      | 20      | -                      | mA                |

| 正常转换模式             | 200kSPS 转换 | -                      | 23      | -                      | mA                |

| 待机模式               | -          | -                      | 5.5     | -                      | mA                |

| 关断模式               | -          | -                      | 10      | -                      | uA                |

## 5.5 时序特性

| 参数                            | 最小值  | 标准值  | 最大值 | 单位 | 描述                   |

|-------------------------------|------|------|-----|----|----------------------|

| 并行/串行/字节模式                    |      |      |     |    |                      |

| t <sub>CYCLE</sub>            | 5    | -    | -   | us | 吞吐速率周期               |

| t <sub>CONV</sub>             | 3.45 | 4.25 | 4.5 | us | 无过采样                 |

|                               | -    | -    | 11  | us | 2 倍过采样               |

|                               | -    | -    | 25  | us | 4 倍过采样               |

|                               | -    | -    | 55  | us | 8 倍过采样               |

|                               | -    | -    | 100 | us | 16 倍过采样              |

|                               | -    | -    | 202 | us | 32 倍过采样              |

|                               | -    | -    | 400 | us | 64 倍过采样              |

| t <sub>Wake-up Standby</sub>  | -    | -    | 100 | us | 从待机模式上电              |

| t <sub>Wake-up Shutdown</sub> | -    | -    | 30  | ms | 内部基准, 从关断模式上电        |

|                               | -    | -    | 13  | ms | 外部基准, 从关断模式上电        |

| t <sub>RESET</sub>            | 20   | -    | -   | ns | RESET 高电平脉冲宽度        |

| t <sub>OS_SETUP</sub>         | 20   | -    | -   | ns | BUSY 到 OS[2:0]引脚设置时间 |

| t <sub>OS_HOLD</sub>          | 20   | -    | -   | ns | BUSY 到 OS[2:0]引脚设置时间 |

|                 |          |   |     |     |                                                                  |

|-----------------|----------|---|-----|-----|------------------------------------------------------------------|

| t1              | -        | - | 40  | ns  | CONVST_A/B 高电平到 BUSY 高电平                                         |

| t2              | 20       | - | -   | ns  | 最短 CONVST_A/B 低电平脉冲                                              |

| t3              | 20       | - | -   | ns  | 最短 CONVST_A/B 高电平脉冲                                              |

| t4              | 0        | - | -   | ns  | BUSY 下降沿到 CS_N 下降沿设置时间                                           |

| t5              | -        | - | 0.5 | ms  | COVNST_A/B 上升沿之间最大容许延迟                                           |

| t6              | -        | - | 25  | ns  | 最后 CS_N 上升沿与 BUSY 下降沿之间最长时间                                      |

| t7 <sup>1</sup> | 80       | - | -   | ms  | RESET 低电平到 CONVST_A/B 高电平最短延迟时间<br>RESET 下降沿用于 Efuse 导入数据，占用时间较长 |

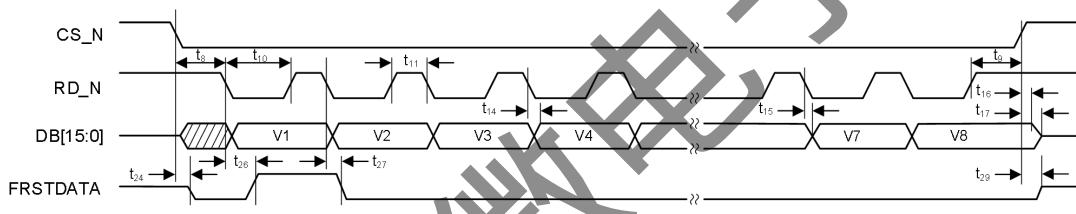

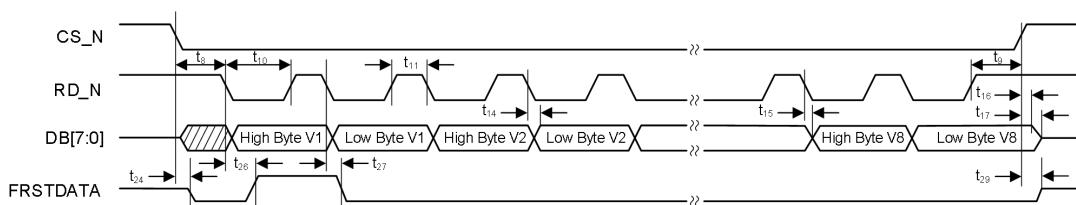

| 并行/字节读取操作       |          |   |     |     |                                                                  |

| t8              | 0        | - | -   | ns  | CS_N 到 RD_N 设置时间                                                 |

| t9              | 0        | - | -   | ns  | CS_N 到 RD_N 保持时间                                                 |

| t10             | 21       | - | -   | ns  | RD_N 低电平脉冲宽度                                                     |

| t11             | 15       | - | -   | ns  | RD_N 高电平脉冲宽度                                                     |

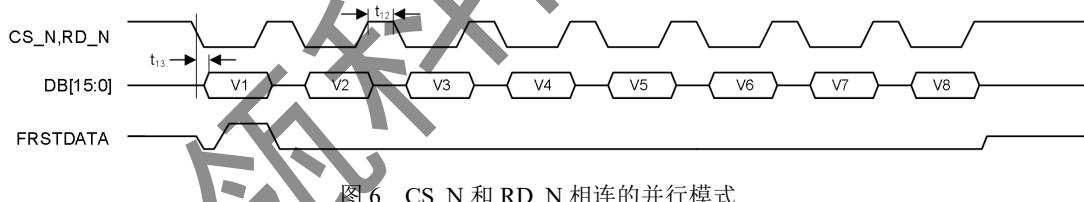

| t12             | 22       | - | -   | ns  | CS_N 高电平脉冲宽度                                                     |

| t13             | -        | - | 20  | ns  | 从 CS_N 到 DB[15:0] 三态禁用的延迟时间                                      |

| t14             | -        | - | 21  | ns  | RD_N 下降沿后的数据访问时间                                                 |

| t15             | 6        | - | -   | ns  | RD_N 下降沿后的数据保持时间                                                 |

| t16             | 6        | - | -   | ns  | CS_N 到 DB[15:0] 保持时间                                             |

| t17             | -        | - | 35  | ns  | 从 CS_N 到 DB[15:0] 三态使能的延迟时间                                      |

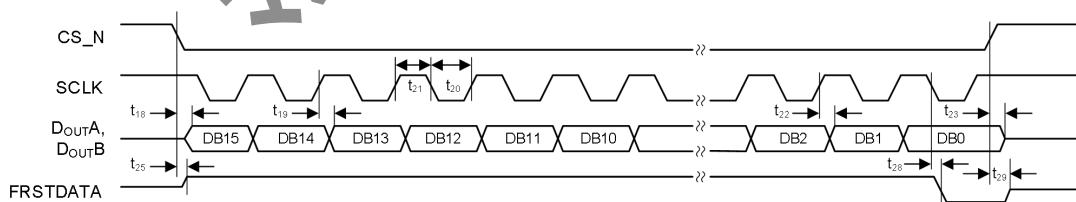

| 串行读取操作          |          |   |     |     |                                                                  |

| fsCLK           | -        | - | 25  | MHz | 串行读取时钟频率                                                         |

| t18             | -        | - | 20  | ns  | 从 CS_N 直到 DoutA/DoutB 三态禁用的延迟时间<br>从 CS_N 直到 MSB 有效的延迟时间         |

| t19             | -        | - | 23  | ns  | SCLK 上升沿后的数据访问时间                                                 |

| t20             | 0.4tSCLK | - | -   | -   | SCLK 低电平脉冲宽度                                                     |

| t21             | 0.4tSCLK | - | -   | -   | SCLK 高电平脉冲宽度                                                     |

| t22             | 7        | - | -   | -   | SCLK 上升沿到 DoutA/DoutB 有效的保持时间                                    |

| t23             | -        | - | 22  | -   | CS_N 上升沿到 DoutA/DoutB 三态使能                                       |

| FRSTDAT A 读取操作  |          |   |     |     |                                                                  |

| t24             | -        | - | 20  | -   | 从 CS_N 下降沿直到 FRSTDAT A 三态禁用的延迟时间                                 |

| t25             | -        | - | 20  | -   | 从 CS_N 下降沿直到 FRSTDAT A 高电平的延迟时间，串行模式                             |

| t26             | -        | - | 20  | -   | 从 RD_N 下降沿到 FRSTDAT A 高电平的延迟时间                                   |

| t27             | -        | - | 20  | -   | 从 RD_N 下降沿到 FRSTDAT A 低电平的延迟时间                                   |

| t28             | -        | - | 25  | -   | 从第 16 个 SCLK 下降沿到 FRSTDAT A 低电平的延迟时间                             |

| t29             | -        | - | 24  | -   | 从 CS_N 上升沿到 FRSTDAT A 三态使能的延迟时间                                  |

注：

1、上电必须 RESET 器件，RESET 完需等待 80ms，确保后续转换数据正常工作。

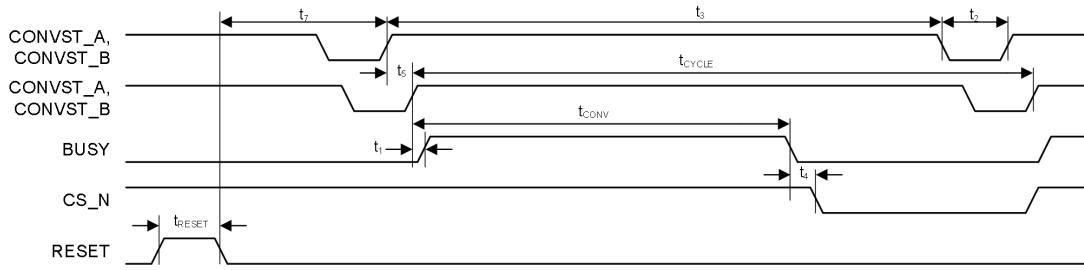

图3 CONVST 时序-转换之后读取

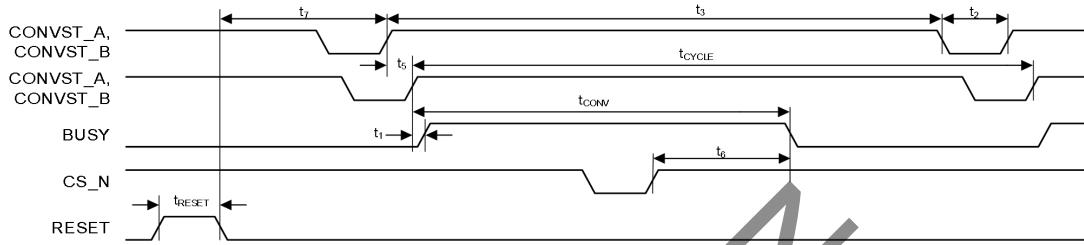

图4 CONVST 时序-转换期间读取

图5 并行模式，独立 CS\_N 和 RD\_N 读数

图6 CS\_N 和 RD\_N 相连的并行模式

图7 串行读取操作（通道 V1）

图8 字节读取操作

## 6 特性曲线

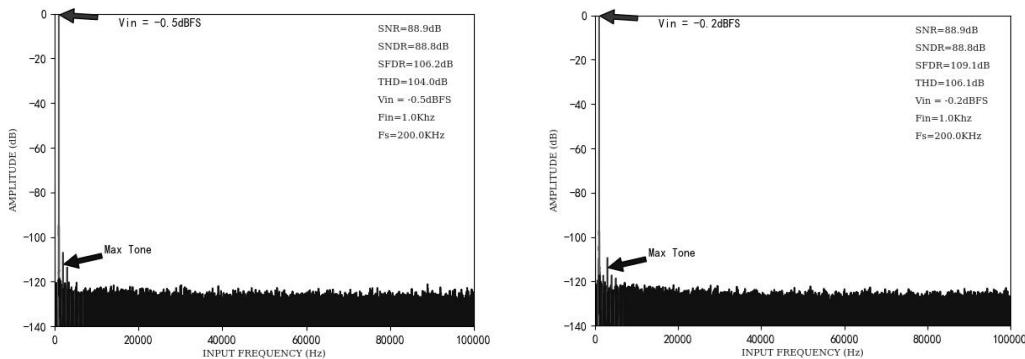

### ◆ 动态特性 $\pm 10V$ 范围和 $\pm 5V$ 范围（外部基准）

### ◆ 动态特性 $\pm 10V$ 范围和 $\pm 5V$ 范围（内部基准）

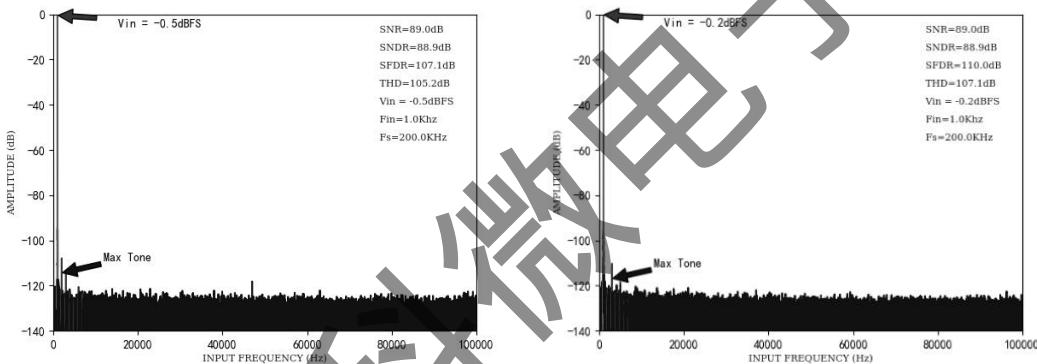

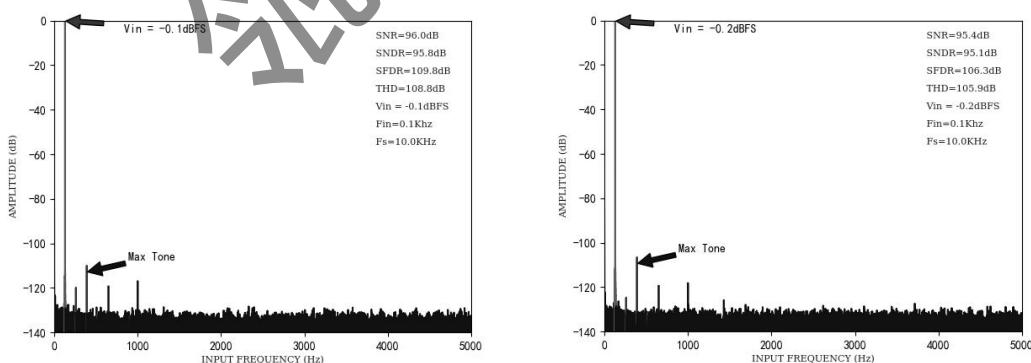

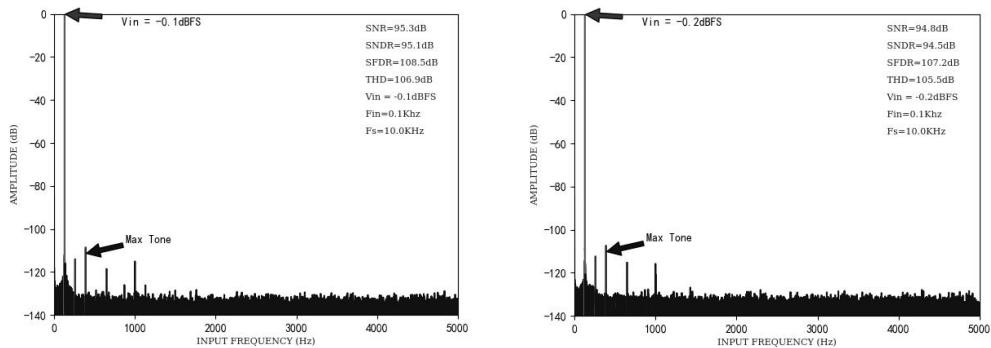

### ◆ 动态特性 16 倍过采样， $\pm 10V$ 范围和 $\pm 5V$ 范围（外部基准）

◆ 动态特性 16 倍过采样， $\pm 10V$  范围和 $\pm 5V$  范围（内部基准）

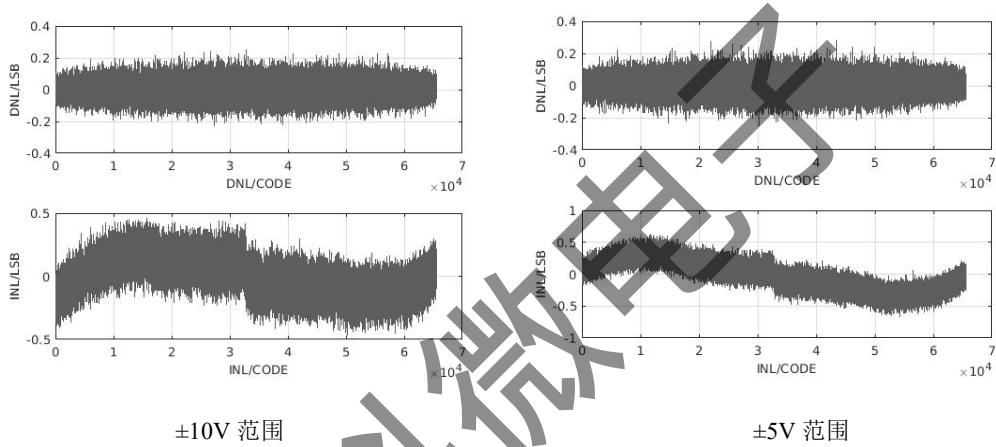

◆ 静态特性 DNL 和 INL， $\pm 10V$  范围和 $\pm 5V$  范围（内部基准）

◆ 静态特性 DNL 和 INL， $\pm 10V$  范围和 $\pm 5V$  范围（外部基准）

## 7 工作原理

### 7.1 转换器描述

LKAD7606LQ 采用高速，低功耗，电荷再分配逐次逼近型模数转换器（ADC）的数据采集系统。模拟输入支持单端输入或者真双极性输入信号。使用 RANGE 引脚选择±10V 或者±5V 的输入范围。使用 REFSEL 引脚选择片内基准或者片外基准。

LKAD7606LQ 采用 5V 单电源供电，内置输入钳位保护，可变增益放大器，二阶低通滤波器，采样保持电路，片内基准电压源，基准电压缓冲器，高精度 ADC，数字滤波器以及并行和串行接口。

### 7.2 模拟输入及钳位保护

LKAD7606LQ 的模拟前端输入阻抗为 1M 欧姆。高模拟输入阻抗可以不需要前端的驱动放大器，允许器件与信号源或传感器直接相连，简化系统方案。

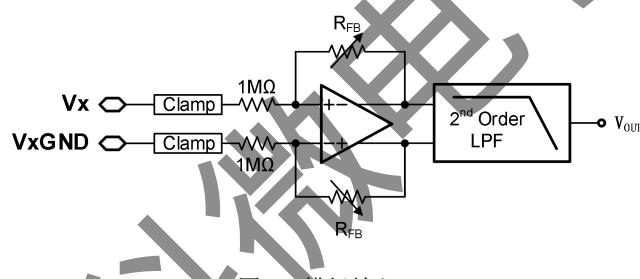

在产品应用中，可能会存在过压，过流或者短路等情况，导致输入高压波动，钳位电路可以有效抵抗这类场景。

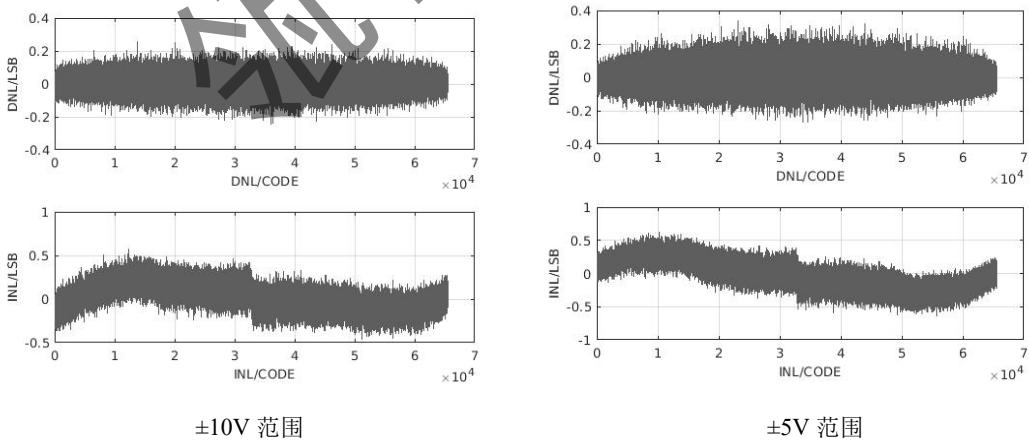

下图显示了 LKAD7606LQ 的模拟输入结构，8 个通道均包含钳位保护电路，允许输入过压达到±22V。

图 9 模拟输入

下图显示了钳位电路电压和电流的关系。当输入电压不超过±22V 时，钳位电路中几乎无电流。当输入电压超过±22V 时，钳位保护电路开启。在实际应用中，推荐模拟输入通道上串联一个低阻电阻，可以有效防止电压超过±22V 时，使得输入电流限制在±10mA 以下。

图 10 输入钳位保护特性

### 7.3 模拟输入低通滤波器

LKAD7606LQ 模拟前端内置一个低通滤波器（二阶巴特沃兹），用于滤除高频噪声。在 $\pm 5V$  范围，-3dB 带宽典型值为 12kHz；在 $\pm 10V$  范围内，-3dB 带宽典型值为 18kHz。

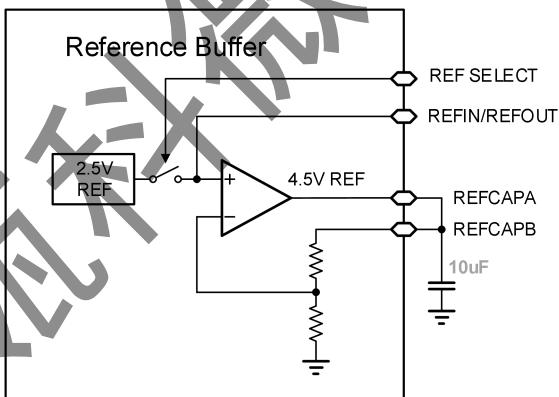

### 7.4 内部/外部基准电压

LKAD7606LQ 内置一个 2.5V 片内基准电压源，也可以使用片外 2.5V 基准，它们都可以通过片内的基准源放大缓冲器产生 4.5V 基准电压。REFIN/REFOUT 引脚既可以使用片内的基准电压源，也可以外接片外的 2.5V 基准电压源，提供给客户选择使用。

片内基准或者片外基准的选取可以通过 REF SELECT 引脚来控制，如果该引脚为高电平，则选择内部基准电压，如果该引脚为低电平，则选择外部基准电压，内部基准无效。无论使用内部还是外部基准电压，都需要对 REFIN/REFOUT 引脚去耦，外接 10uF 陶瓷去耦电容。

LKAD7606LQ 内置一个片内基准源放大缓冲器，把 2.5V 基准电压放大至 4.5V，作为 ADC 转换的参考电压。REFCAPA 和 REFCAPB 引脚必须在外部短接在一起，并且通过一个 10uF 的陶瓷去耦电容连接至 REFGND，以确保参考电压缓冲器工作在闭环中。

LKAD7606LQ 有四个 AVCC 电源引脚，需要各使用一个 100nF 的去耦电容放置在引脚处，在电源端使用一个 10uF 的电容去耦，提升电源的噪声和抗干扰能力。VDRIVE 作为数字接口的供电电源，应当连接到处理器同一电源。

图 11 基准电压及缓冲放大器

### 7.5 复位功能

可通过 RESET 引脚对 LKAD7606LQ 进行复位操作，涉及到以下过程：

- 复位 ADC 转换过程

- 复位数字电路模块

- 启动校准数据 Efuse 加载模块

使用 RESET 时需注意：在 RESET 的下降沿将装载 Efuse 数据，该过程约需 50μs。

在使用过程中进行复位时，若 RESET 高电平维持时间较短(<500ns)，基准缓冲器输出电压不会产生明显变化，等

待至少 50 $\mu$ s 以后，即可进行数据采集。

若 RESET 高电平维持时间较长(>1ms)，那么新装载的 Efuse 数据将调整基准缓冲器输出，基准缓冲器需要更长的稳定时间(数 ms)。需注意：装载 Efuse 数据不会影响 ADC 其他模块正常工作，但在基准缓冲器未稳定期间，ADC 采集精度可能受到轻微影响，满量程误差最大可能增大 100LSB。

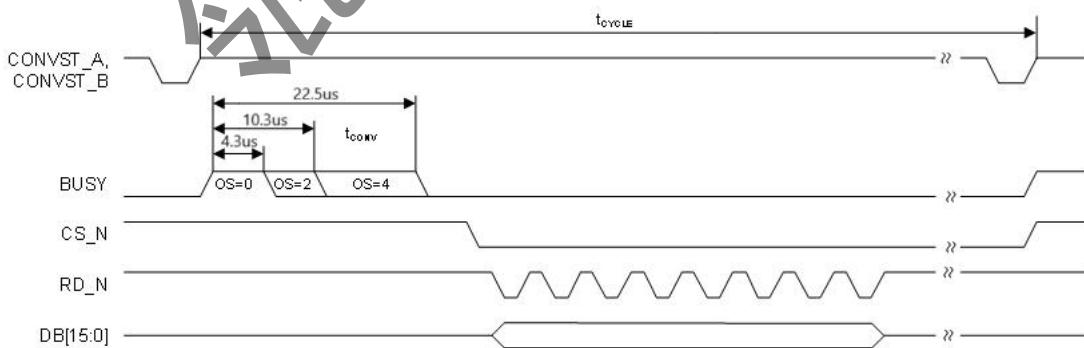

## 7.6 转换控制

LKAD7606LQ 内置八个通道采样保持放大器，通过引脚 CONVST\_A 和 CONVST\_B 分别控制 4 个通道转换和采样。CONVST\_A 和 CONVST\_B 上升沿触发 ADC 转换，而转换采用内部时钟，所有通道的转换时间约为 4us。在 ADC 转换期间，BUSY 引脚为高电平，转换完成后，BUSY 引脚恢复低电平，表示转换结束。在 BUSY 信号的下降沿，各个通道的采样保持放大器切回跟踪输入信号模式。BUSY 引脚变为低电平后，可以通过并行，并行字节或者串行接口读取转换数据。

当两个引脚 CONVST\_A 和 CONVST\_B 连在一起时，所有通道同步采样；当引脚 CONVST\_A 和 CONVST\_B 分别控制时，允许模拟输入通道以两组的形式进行同步采样（V1~V4 和 V5~V8 两组）。这个功能可以用在电力线保护和测量系统中，以补偿 PT 和 CT 变压器所引入的相位误差。在 50Hz 系统中，两组同步采样的功能可以提供最多 9° 的相位补偿。

## 7.7 省电模式

LKAD7606LQ 提供两种省电模式：待机模式和关断模式，由引脚 STBY\_N 和 RANGE 控制。处于待机模式时，模拟 LDO 处于关闭状态，片内基准和参考基准缓冲电路仍正常工作，芯片最大功耗 6mA，上电时间约 100us。当处于关断模式时，所有电路均关断，最大功耗 10uA，上电时间约 10ms。

注意，从关断模式退出，需要完成一次 RESET 操作，复位完成后仍需等待 80ms，才能进入正常转换。

省电模式选择：

| 省电模式 | STBY_N | RANGE |

|------|--------|-------|

| 待机   | 0      | 1     |

| 关断   | 0      | 0     |

## 7.8 数字接口

LKAD7606LQ 提供三种接口模式：串行接口，平行接口和并行字节接口。所需接口模式可以通过对应引脚来控制。

表 2 接口模式选择

| PAR_N/SER/BYTE_SEL | DB15 | 接口模式     |

|--------------------|------|----------|

| 0                  | 0    | 并行接口模式   |

| 1                  | 0    | 串行接口模式   |

| 1                  | 1    | 并行字节接口模式 |

## 7.9 串行接口模式

引脚配置：PAR\_N=1

LKAD7606LQ 有两个串行数据输出引脚：DOUTA 和 DOUTB，可通过单路或者双路读回数据。通道 V1 至 V8 的数据依次出现在 DOUTA 引脚；通道 V5 至 V8，然后 V1 至 V4 的数据依次出现在 DOUTB 引脚。如果通过一个输出引脚读取八个通道的转换数据，总共需要 128 个 SCLK 周期，如果通过两个输出引脚读取数据，只需要 64 个 SCLK 周期。

CS\_N 下降沿使能 DOUTA 和 DOUTB 引脚输出，脱离三态，并且输出转换结果的 MSB。SCLK 上升沿依次把所有数据位串行输出，数据再 SCLK 的下降沿有效。

FRSTDATA 输出信号指示何时读取第一个通道 V1，当数据是 V1 通道时，FRSTDATA 输出高电平，当数据是其他通道时，FRSTDATA 输出低电位。当 CS\_N 下降沿使能 FRSTDATA 引脚输出，脱离三态。

## 7.10 并行接口模式

引脚配置：PAR\_N=0

可以通过标准的 CS\_N 和 RD\_N 信号通过并行接口 DB[15:0]读取数据。CS\_N 下降沿使能总线脱离三态，利用该功能可以同时控制多个 LKAD7606LQ 器件共享同一并行数据总线。在 BUSY 信号变为低电平后，读取新的转换数据；或者，在 BUSY 信号高电平时，读取前一次转换的数据。BUSY 信号变为低电平的第一个 RD\_N 下降沿输出通道 V1 的转换数据，下一个 RD\_N 下降沿输出通道 V2 的转换数据，依次类推。

如果不共享总线时，可以使用一个控制信号来读取数据，只需要把 CS\_N 和 RD\_N 连在一起，如图 6 所示。并行模式下，读取 8 个通道的数据只需要 8 个 RD\_N 时钟。

## 7.11 并行字节接口模式

引脚配置：PAR\_N=1,DB15=1

并行字节接口模式跟并行接口模式非常相似，只是数据总线通道只有 DB[7:0]，不同通道的数据需要通过两次 8 位传输读出。因此，读取 8 个通道的转换数据，总共需要 16 个 RD\_N 时钟。

并行自己接口模式下，DB14 复用 HBEN 引脚。当 DB14/HBEN 为高电平时，DB[7:0]引脚首先输出转换结果的高字节（MSB，即 DOUT[15:8]），然后输出低字节（LSB，即 DOUT[7:0]）。当 DB14/HBEN 为低电平时，DB[7:0]引脚

首先输出转换结果的低字节（LSB，即 DOUT[7:0]），然后输出高字节（MSB，即 DOUT[15:8]）。

FRSTDATA 引脚输出高电平，只至通道 V1 的数据传输完成。

## 7.12 转换期间读取

当 BUSY 信号为高电平，说明 ADC 转换正在进行中。BUSY 的下降沿完成更新转换数据。因此，也可在 BUSY 高位平时，读取转换数据，这样不会影响转换器的性能，而且可以实现更快的吞吐速率。转换器件读取的时序操作满足 t6 要求即可。

## 7.13 数字滤波器（过采样）

在需要更高信噪比或者更大动态范围的应用中，可以通过降低吞吐率实现过采样功能。LKAD7606LQ 内置一个可选带宽的数字滤波器，通过引脚 OS[2:0]控制。

开启过采样功能时，CONVST\_A 和 CONVST\_B 引脚必须连在一起控制，转换过程指示信号 BUSY 周期会延长，取决于过采样倍率。图 12 显示了 BUSY 信号宽度随过采样倍率提高而延长。

测试条件：±10V 输入范围，外部基准，电源电压 AVCC=5V，VDRIVE=3.3V，TA =25°C

| 引脚 OS[2:0] | 过采样倍数  | SNR(dB) | 3dB 带宽(kHz) | 采样频率(kHz) |

|------------|--------|---------|-------------|-----------|

| 0          | No OSR | 89.5    | 18.5        | 200       |

| 1          | 2      | 91.3    | 18.5        | 80        |

| 10         | 4      | 93.1    | 15          | 40        |

| 11         | 8      | 94.1    | 10          | 20        |

| 100        | 16     | 96.1    | 5           | 10        |

| 101        | 32     | 96.2    | 2.5         | 5         |

| 110        | 64     | 97.1    | 1.25        | 2.5       |

| 111        | -      |         |             |           |

注意: OS[2:0]不建议配置成全部高电平

图 12 无过采样，2 倍过采样和 4 倍过采样，转换和数据读取

## 8 应用信息

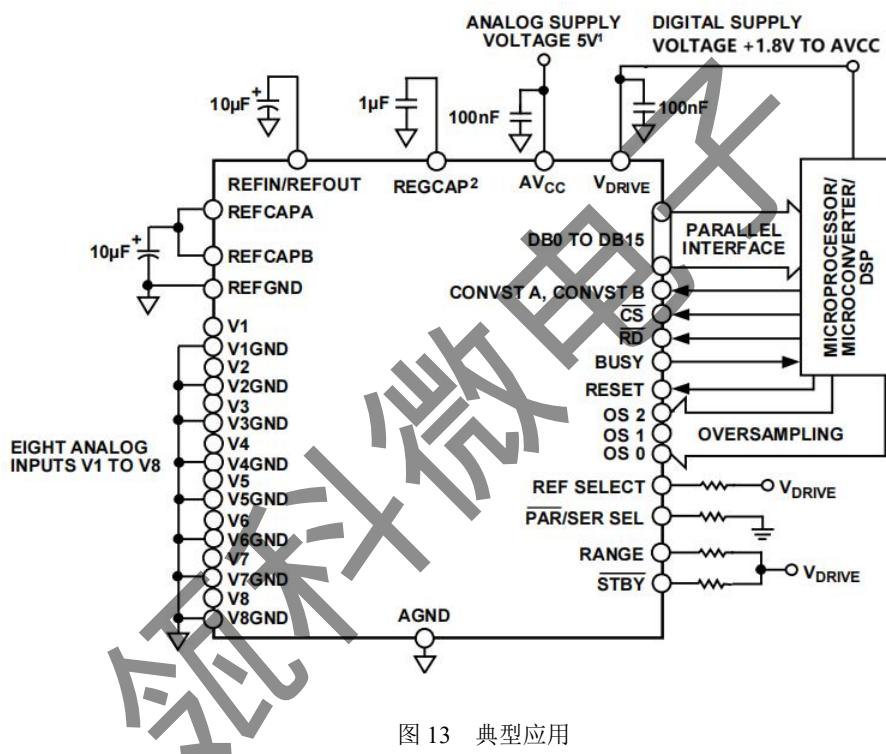

### 8.1 典型应用

LKAD7606LQ 的典型连接图如图 13 所示。它有四个 AVCC 电源引脚，这四个电源引脚应各用一个 100nF 去耦电容，并在电源侧使用一个 10μF 去耦电容。LKAD7606LQ 被配置为在内部基准电压模式下工作，当 PCB 板上只有一个 LKAD7606LQ 时，应使用一个 10μF 电容对 REFIN/REFOUT 引脚去耦。REFCAPA 和 REFCAPB 引脚短路在一起，并通过一个 10μF 陶瓷电容去耦。VDRIVE 电源与处理器连接到相同的电源，VDRIVE 电压控制输出逻辑信号的电压值。

LKAD7606LQ 上电后，应对其进行复位，以确保将其配置为正确的工作模式。

图 13 典型应用

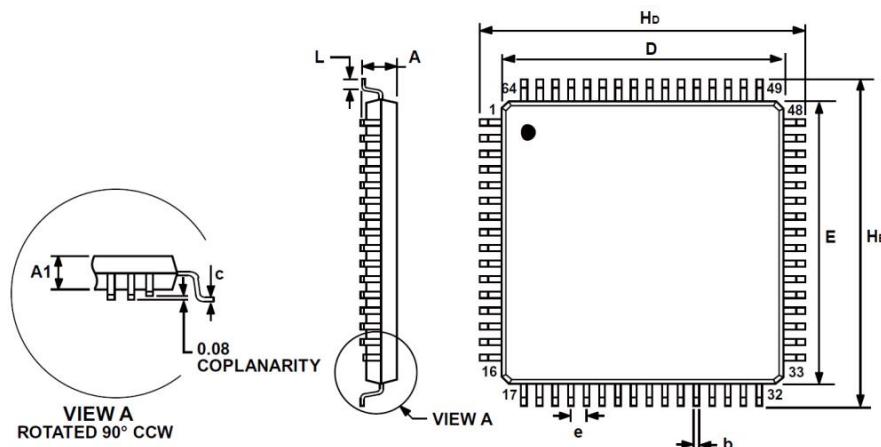

## 9 封装形式

| 尺寸符号           | 单 位: mm |       |       |

|----------------|---------|-------|-------|

|                | 最 小     | 公 称   | 最 大   |

| A              | -       | -     | 1.60  |

| A1             | 1.25    | 1.35  | 1.60  |

| b              | 0.18    | -     | 0.27  |

| c              | 0.13    | -     | 0.18  |

| D              | 9.90    | 10.00 | 10.10 |

| E              | 9.90    | 10.00 | 10.10 |

| e              | 0.65BSC |       |       |

| H <sub>E</sub> | 11.80   | 12.00 | 12.20 |

| L              | 0.45    | 0.60  | 0.75  |

## 10 机械、包装和可订购的信息

以下页面包括机械、包装和可订购的信息。

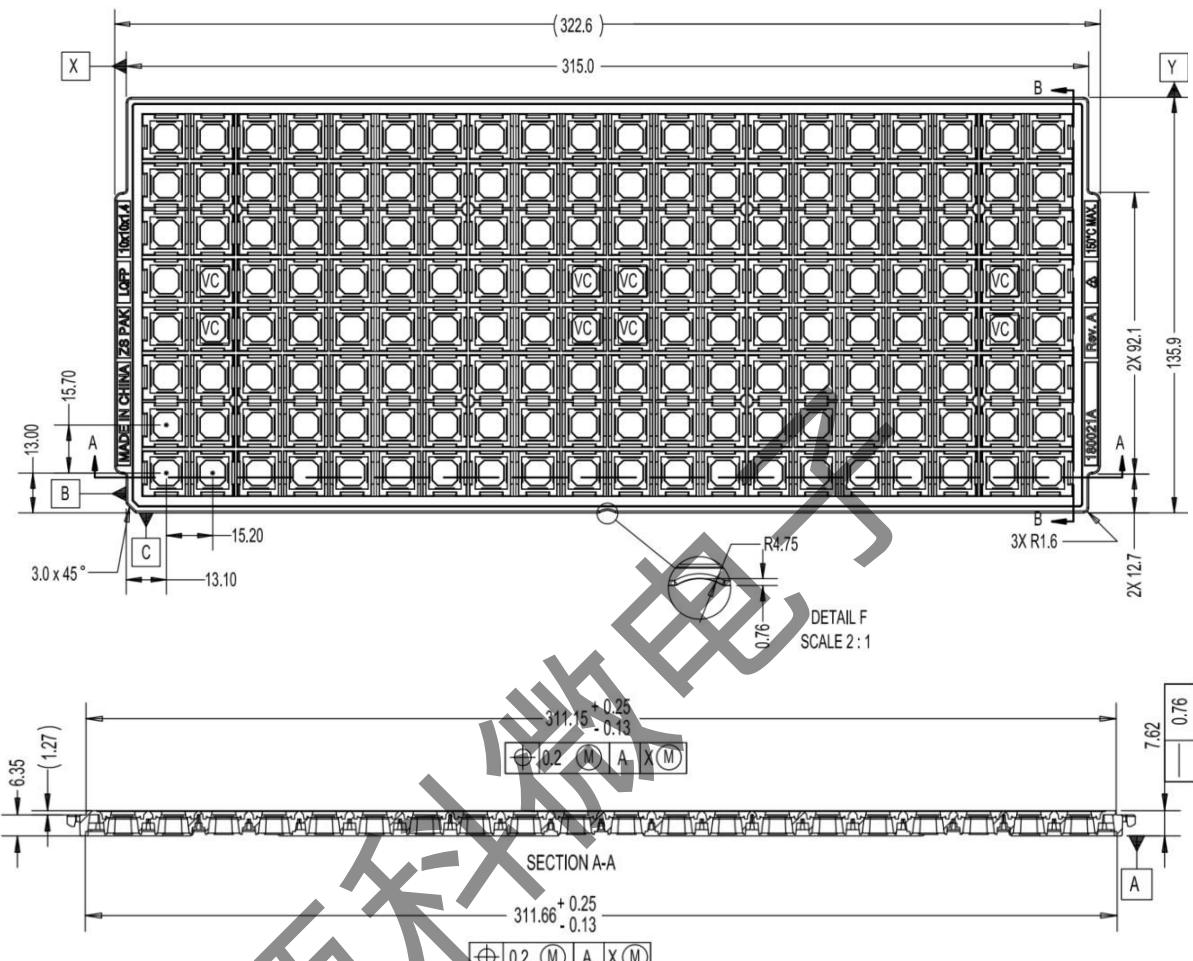

### 10.1 托盘信息

注：

1. 托盘的 45°倒角表明芯片 1 脚的位置。

2. 单位：mm。

| 封装形式                 | 托盘        | 内盒       | 包装箱 | 只/盘 | 盘/盒 | 只/盒  | 盒/箱 | 只/箱  |

|----------------------|-----------|----------|-----|-----|-----|------|-----|------|

| LQFP<br>10X10X1.6 64 | IC-TP-240 | IC-15-0N | *1  | 160 | 10  | 1600 | 4   | 6400 |

\*1. 该箱内盒尺寸 360×158×92，编号为：IC-15-0N；外箱尺寸 375×335×220，编号为：IC-16-0W。

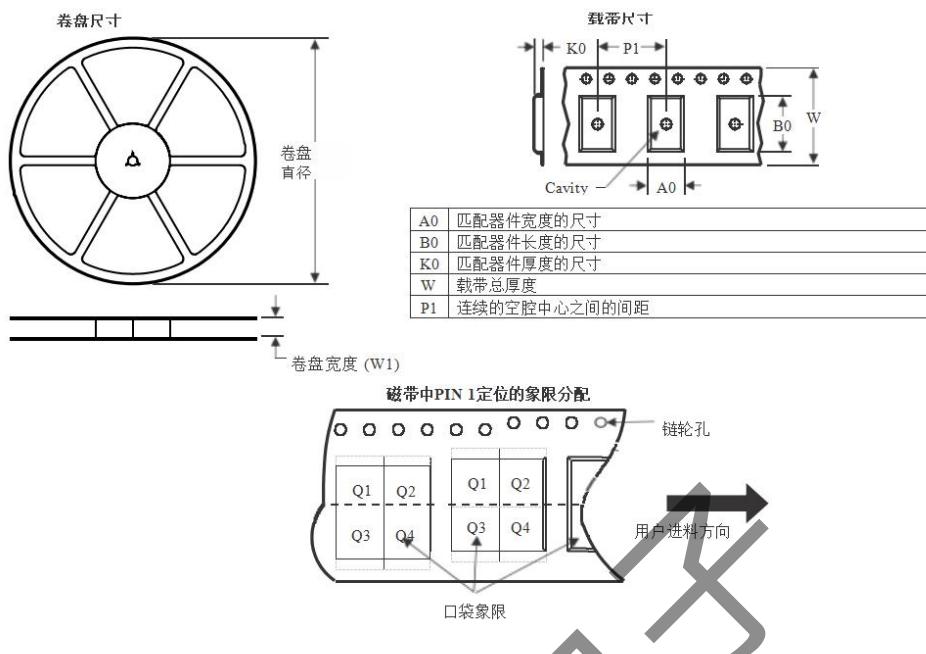

## 10.2 载带和卷盘信息

\*所有尺寸均为标称尺寸

| 器件         | 封装   | 引脚数 | 卷盘直径(mm) | 卷盘宽度 W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W(mm) | 引脚 1 象限 |

|------------|------|-----|----------|--------------|---------|---------|---------|---------|-------|---------|

| LKAD7606LQ | LQFP | 64  | 330.0    | 16.4         | 6.9     | 10.2    | 1.8     | 12.0    | 16.0  | Q1      |

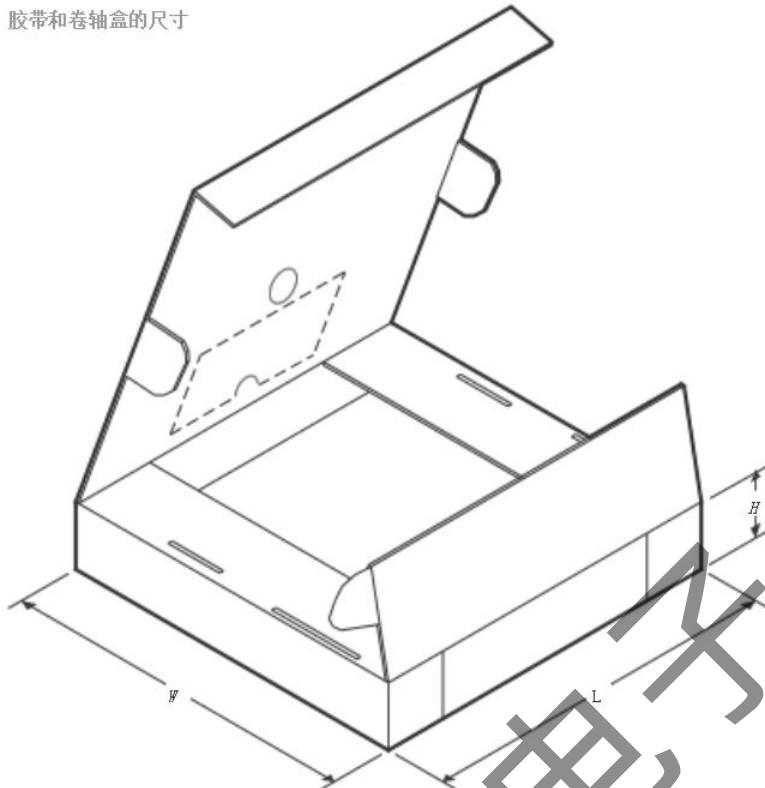

胶带和卷轴盒的尺寸

\*所有尺寸均为标称尺寸

| 器件         | 封装   | 引脚数 | 长度 (mm) | 宽度 (mm) | 高度 (mm) |

|------------|------|-----|---------|---------|---------|

| LKAD7606LQ | LQFP | 64  | 350.0   | 350.0   | 43.0    |

### 10.3 订货信息

**LK**

①

**AD**

②

**7606**

③

**LQ**

④

- ① 产品系列代号

- ② 分类标识

- ③ 产品代号

- ④ 封装形式

表 3 订货信息表

| 型号         | 封装           | 质量等级 | 工作温度          |

|------------|--------------|------|---------------|

| LKAD7606LQ | LQFP64, 塑料封装 | 工业级  | -40°C ~ +85°C |

## 11 版本信息

| 版本号      | 日期         | 版本说明 | 更改说明       |

|----------|------------|------|------------|

| REV 1.00 | 2024-07-04 | 更新版本 | —          |

| REV 1.01 | 2024-12-24 | 更新版本 | 更正时序特性表中参数 |

| REV 1.02 | 2025-11-28 | 更新版本 | 内容优化       |

| REV 1.03 | 2025-12-17 | 更新版本 | 增加托盘包装信息   |

领科微电子