## 1. Description

The UMW UCC27524ADR device is a dual-channel, high-speed, low-side, gate-driver device capable of effectively driving MOSFET and IGBT power switches. It has a matching rise and fall time when charging and discharging the gate of the power switch. In addition, UMW UCC27524ADR has a high degree of latch resistance under all conditions in its rated power and voltage range. UMW UCC27524ADR is not damaged when noise spikes (any polarity) of up to 5V appear on the ground pin. UMW UCC27524ADR can accept up to 500mA of reverse current without causing damage or logic confusion. All terminals are fully protected by ESD up to 2.0 kV.

## 3. Features

- Latch Protection: withstand 0.5 A reverse current

- Ability to Handle Negative Voltages (-10 V) at Inputs

- Low Output Impedance

- Two Independent Gate-Drive Channel

- Independent-Enable Function for Each Output

- 4-A Peak Source and Sink-Drive Current

- 4.5 to 20-V Single-Supply Range

## 2. Applications

- line drivers

- Pulse transformer driver

- Driving MOSFETs and IGBTs

- Motor drives

- Pulse generator

- Switch-Mode Power Supplies

- DC-to-DC Converters

- Class D switching amplifier

- High Ability of driving capacitive load:

- Switch time at 1nF load < 25ns

- Rise/Fall time matching

- Fast Propagation Delays (40-ns Typical)

- Operating Temperature Range of -40 to 125°C

- Turn on/Turn off Delays:

- Ton/Toff =70ns/70ns

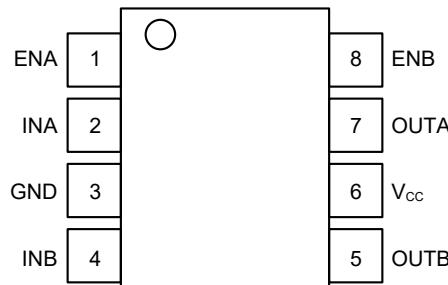

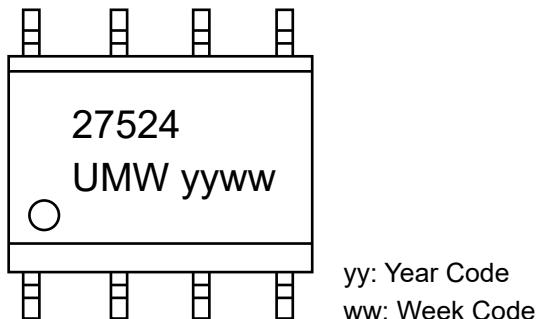

#### 4. Pin Configuration

## 5. Pinning Information

**SOT23-5**

### Pin Functions

| Number | Symbol          | Description                                                                                                                                                                                                                                                       |

|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | ENA             | Enable input for Channel A: ENA is biased LOW to disable the Channel A output regardless of the INA state. ENA is biased HIGH or left floating to enable the Channel A output. ENA is allowed to float; hence the pin-to-pin compatibility with the 27524 N/C pin |

| 2      | INA             | Input to Channel A: INA is the non-inverting input in the 27524 device. OUTA is held LOW if INA is unbiased or floating                                                                                                                                           |

| 3      | GND             | Ground: All signals are referenced to this pin                                                                                                                                                                                                                    |

| 4      | INB             | Input to Channel B: INB is the non-inverting input in the 27524 device. OUTB is held LOW if INB is unbiased or floating                                                                                                                                           |

| 5      | OUTB            | Output of Channel B                                                                                                                                                                                                                                               |

| 6      | V <sub>cc</sub> | Bias supply input                                                                                                                                                                                                                                                 |

| 7      | OUTA            | Output of Channel A                                                                                                                                                                                                                                               |

| 8      | ENB             | Enable input for Channel B: ENB is biased LOW to disable the Channel B output regardless of the INB state. ENB is biased HIGH or left floating to enable the Channel B output. ENB is allowed to float; hence the pin-to-pin compatibility with the 27524 N/C pin |

## 6. Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. All voltages are with respect to GND unless otherwise noted. Currents are positive into, negative out of the specified terminal, environment temperature is 25°C.

| Parameter                                         | Symbol          | Min | Max                  | Units |

|---------------------------------------------------|-----------------|-----|----------------------|-------|

| Supply voltage range                              | V <sub>CC</sub> |     | 25                   | V     |

| INA, INB voltage                                  | V <sub>IN</sub> | -5  | V <sub>CC</sub> +0.3 | V     |

| Human body model (HBM)                            | ESD             |     | 2000                 | V     |

| Charged device model (CDM)                        |                 |     | 500                  | V     |

| SOIC package power( $T_A \leq 70^\circ\text{C}$ ) | P <sub>D</sub>  |     | 470                  | mW    |

| Operating junction temperature                    | T <sub>J</sub>  |     | 150                  | °C    |

| Storage temperature                               | T <sub>S</sub>  | -45 | 150                  | °C    |

## 7. Electrical Characteristics

$T_A=25^\circ\text{C}$ ,  $4.5\text{V} \leq V_{CC} \leq 18\text{V}$  (unless otherwise noted)

| Parameter                                                                       | Symbol        | Condition                                     | Min            | Typ  | Max   | Units         |

|---------------------------------------------------------------------------------|---------------|-----------------------------------------------|----------------|------|-------|---------------|

| Input signal high threshold                                                     | $V_{IH}$      |                                               | 2.4            |      |       | V             |

| Input signal low threshold                                                      | $V_{IL}$      |                                               |                |      | 0.8   | V             |

| Input current                                                                   | $I_{IN}$      | $0\text{V} \leq V_{IN} \leq V_{CC}$           |                |      | 300   | $\mu\text{A}$ |

| High output voltage                                                             | $V_{OH}$      |                                               | $V_{CC}-0.025$ |      |       | V             |

| Low output voltage                                                              | $V_{OL}$      |                                               |                |      | 0.025 | V             |

| Output pullup resistance                                                        | $R_{OH}$      | $V_{CC}=18\text{V}$ , $I_o=100\text{mA}$      |                | 0.7  |       | $\Omega$      |

| Output pulldown resistance                                                      | $R_{OL}$      | $V_{CC}=18\text{V}$ , $I_o=100\text{mA}$      |                | 0.4  |       | $\Omega$      |

| Peak output source current                                                      | $I_{PK}$      |                                               |                | 4    |       | A             |

| Reverse current that latch protection can withstand (Working cycle $\leq 2\%$ ) | $I_{REV}$     | $t \leq 300\text{us}$ , $V_{CC}=18\text{V}$   |                | >0.5 |       | A             |

| Rise time                                                                       | $t_R$         | $V_{CC}=18\text{V}$ , $C_{LOAD}=100\text{pF}$ |                |      | 15    | ns            |

| Fall time                                                                       | $t_F$         | $V_{CC}=18\text{V}$ , $C_{LOAD}=100\text{pF}$ |                |      | 15    | ns            |

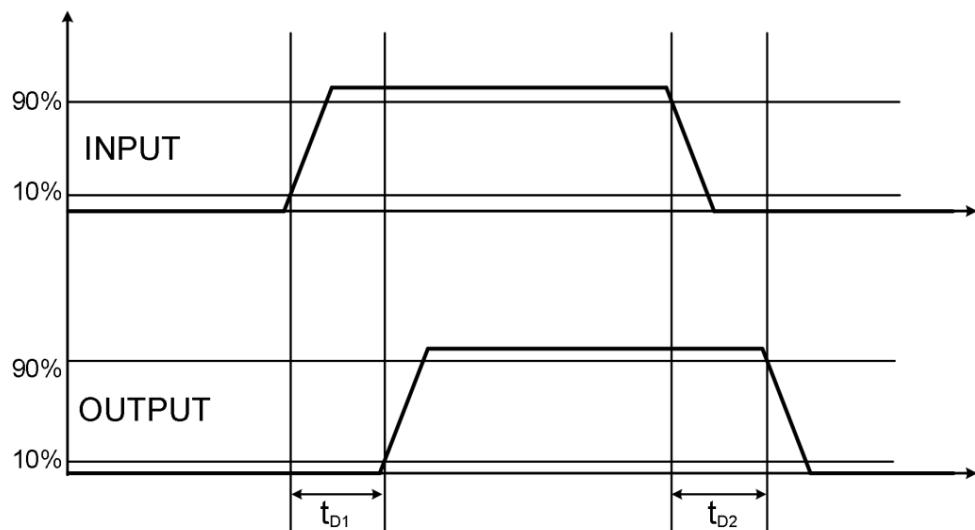

| Turn-on propagation delay                                                       | $t_{ON}$      | $V_{CC}=18\text{V}$ , $C_{LOAD}=100\text{pF}$ |                | 25   | 40    | ns            |

| Turn-off propagation delay                                                      | $t_{OFF}$     | $V_{CC}=18\text{V}$ , $C_{LOAD}=100\text{pF}$ |                | 25   | 40    | ns            |

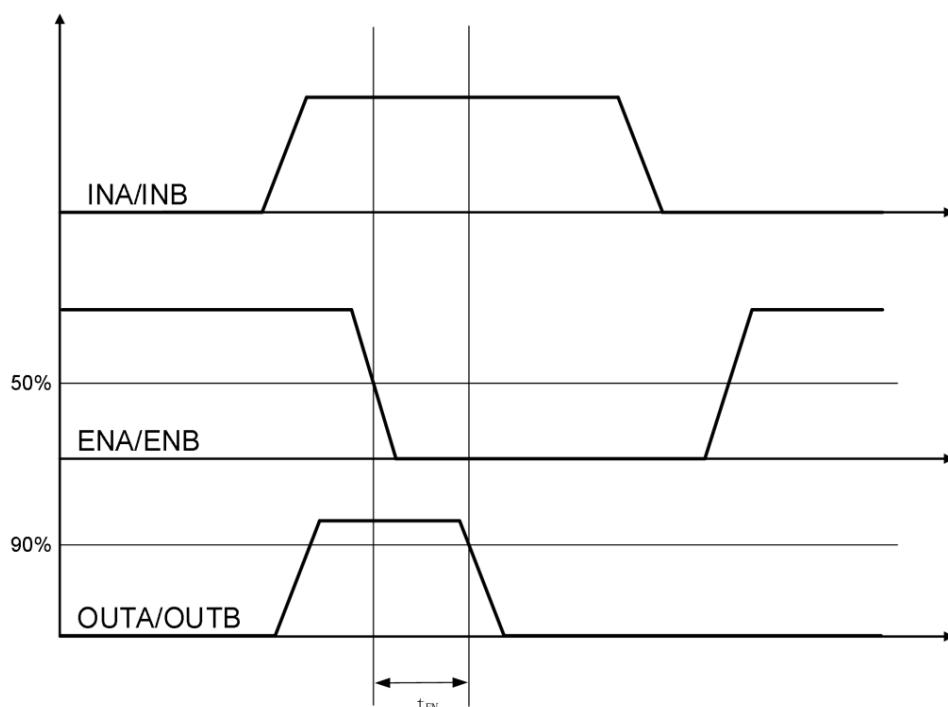

| Enable propagation delay                                                        | $t_{EN}$      | $V_{CC}=18\text{V}$ , $C_{LOAD}=100\text{pF}$ |                | 25   | 40    | ns            |

| $V_{CC}$ quiescent supply current                                               | $I_{Q1}$      | $V_{INA}=V_{INB}=\text{HIGH}$                 |                |      | 1.5   | mA            |

| $V_{CC}$ quiescent supply current                                               | $I_{Q0}$      | $V_{INA}=V_{INB}=\text{LOW}$                  |                |      | 1.5   | mA            |

| High level threshold of enable signal                                           | $V_{EN\_H}$   | Output is enabled                             | 1.9            | 2.1  | 2.3   | V             |

| Low level threshold of enable signal                                            | $V_{EN\_L}$   | Output is disabled                            | 0.95           | 1.15 | 1.35  | V             |

| Enable delay                                                                    | $V_{EN\_HYS}$ |                                               | 0.7            | 0.95 | 1.1   | V             |

Figure 1. Input-Output waveform(non-inverting)

Figure 2. Enable Function waveform

## 8.1 Typical Characteristic

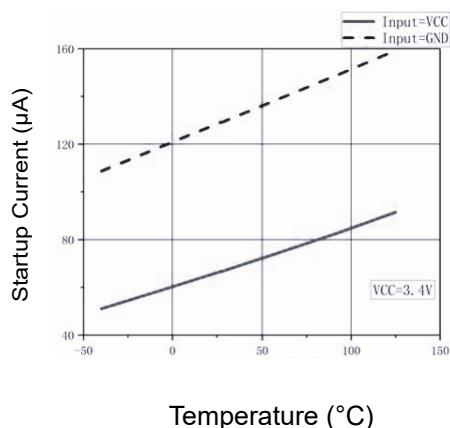

Figure 3: Start-Up Current vs Temperature

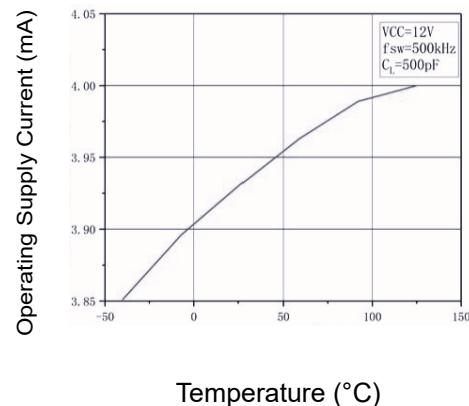

Figure 4: Operating Supply Current vs Temperature (Outputs Switching)

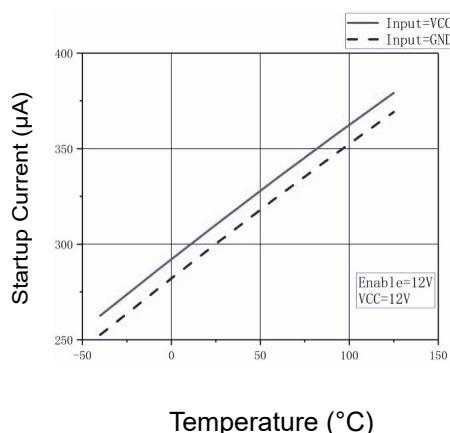

Figure 5: Supply Current vs Temperature (Outputs In DC On/Off Condition)

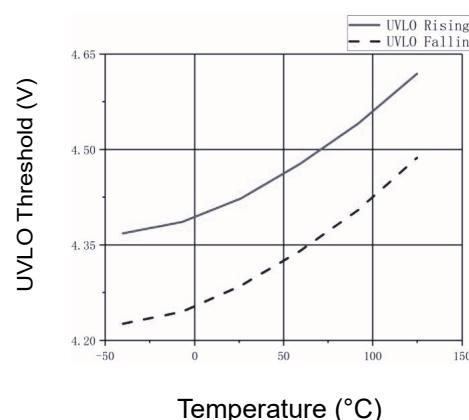

Figure 6: UVLO Threshold vs Temperature

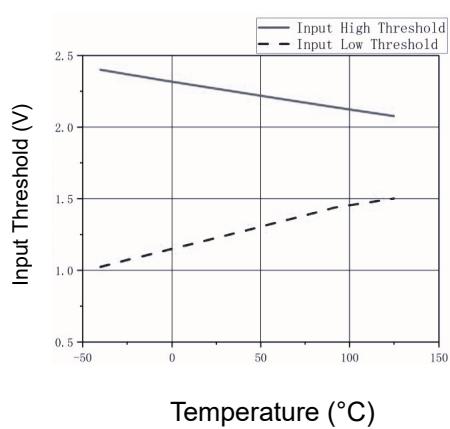

Figure 7: Input Threshold vs Temperature

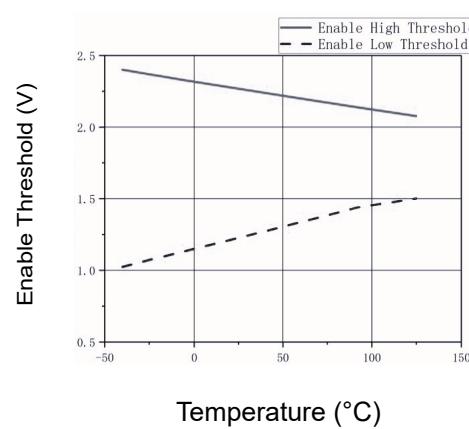

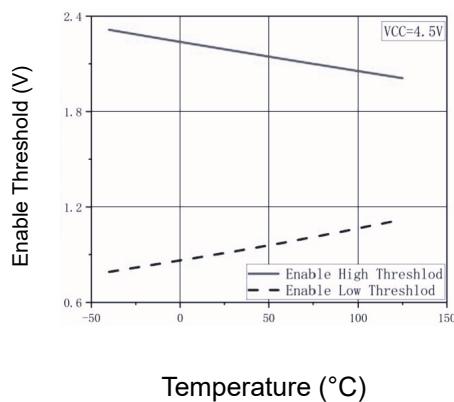

Figure 8: Enable Threshold vs Temperature

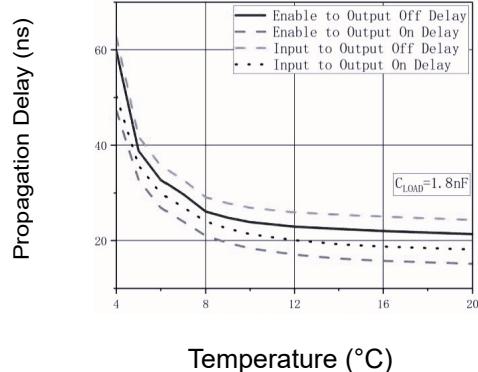

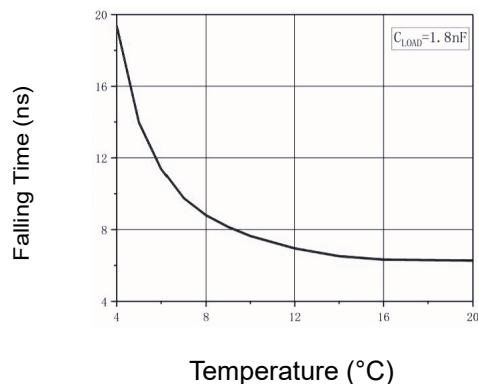

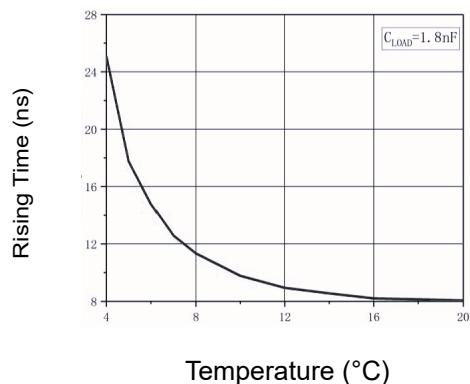

## 8.2 Typical Characteristic

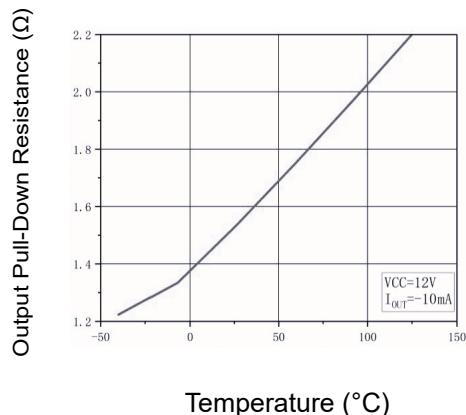

Figure 9: Output Pull-up Resistance vs Temperature

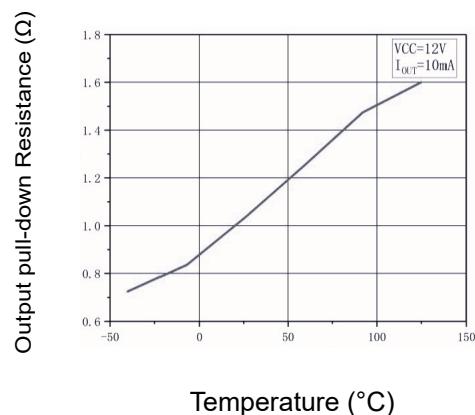

Figure 10: Output Pull-down Resistance vs Temperature

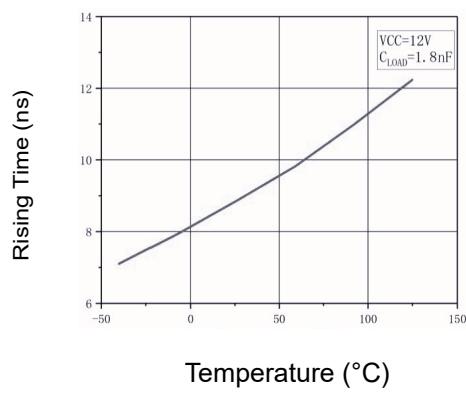

Figure 11: Rise Time vs Temperature

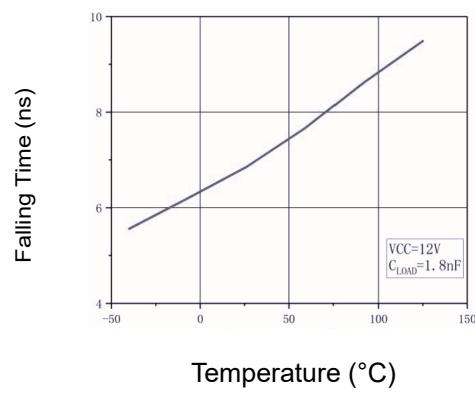

Figure 12: Fall Time vs Temperature

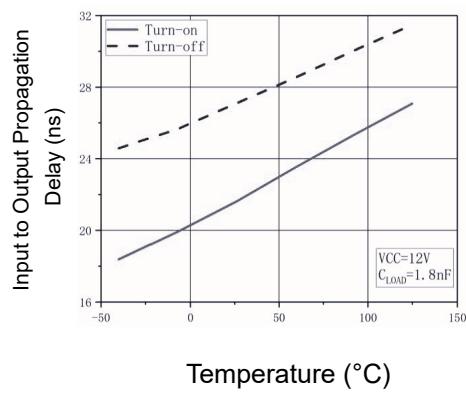

Figure 13: Input to Output Propagation Delay vs Temperature

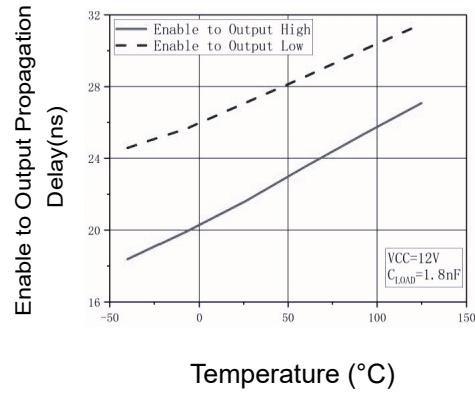

Figure 14: En to Output Propagation Delay vs Temperature

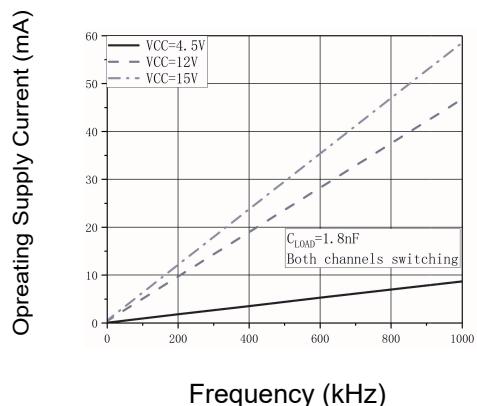

### 8.3 Typical Characteristic

Figure 15: Operating Supply Current vs Frequency

Figure 16: Propagation Delays vs Supply Voltage

Figure 17: Rise Time vs Supply Voltage

Figure 18: Fall Time vs Supply Voltage

Figure 19: Enable Threshold vs Temperature

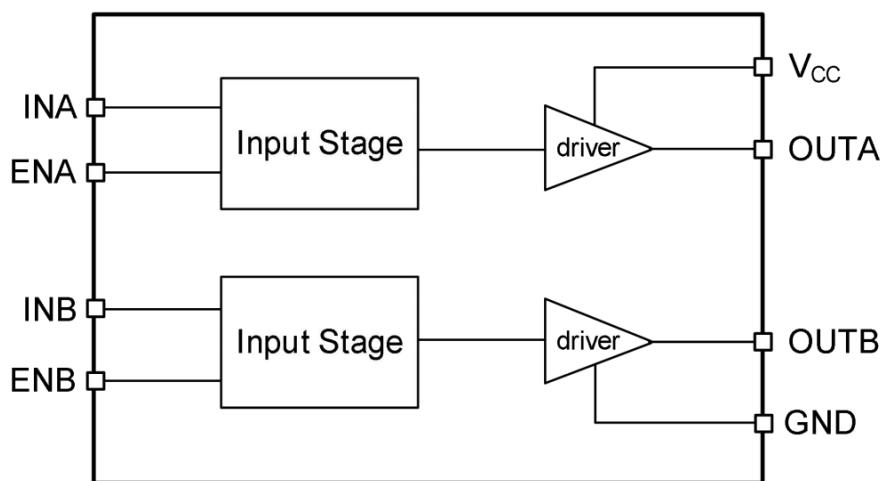

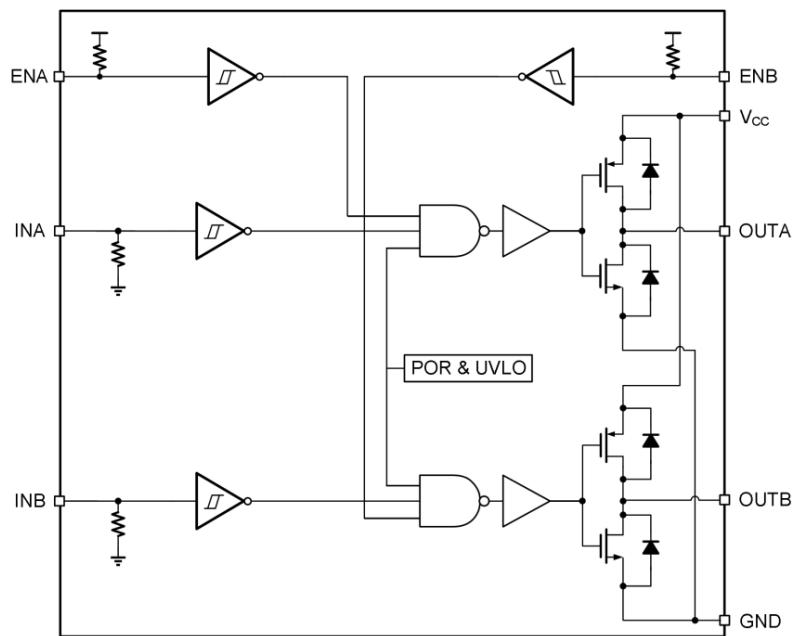

## 9. Functional Block Diagram

## 10. Device Functional Modes

Table 1 Device Logic Table

| ENA              | ENB              | INA              | INB              | OUTA | OUTB |

|------------------|------------------|------------------|------------------|------|------|

| H                | H                | L                | L                | L    | L    |

| H                | H                | L                | H                | L    | H    |

| H                | H                | H                | L                | H    | L    |

| H                | H                | H                | H                | H    | H    |

| L                | L                | Any              | Any              | L    | L    |

| Any              | Any              | x <sup>(1)</sup> | x <sup>(1)</sup> | L    | L    |

| x <sup>(1)</sup> | x <sup>(1)</sup> | L                | L                | L    | L    |

| x <sup>(1)</sup> | x <sup>(1)</sup> | L                | H                | L    | H    |

| x <sup>(1)</sup> | x <sup>(1)</sup> | H                | L                | H    | L    |

| x <sup>(1)</sup> | x <sup>(1)</sup> | H                | H                | H    | H    |

Notes: (1) Floating condition.

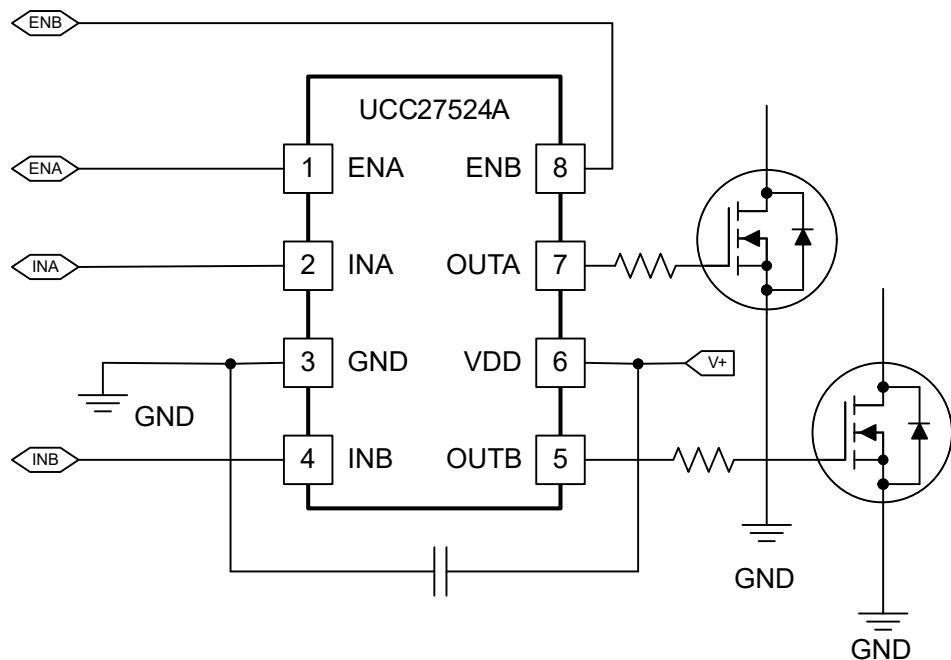

## 11. Typical Application

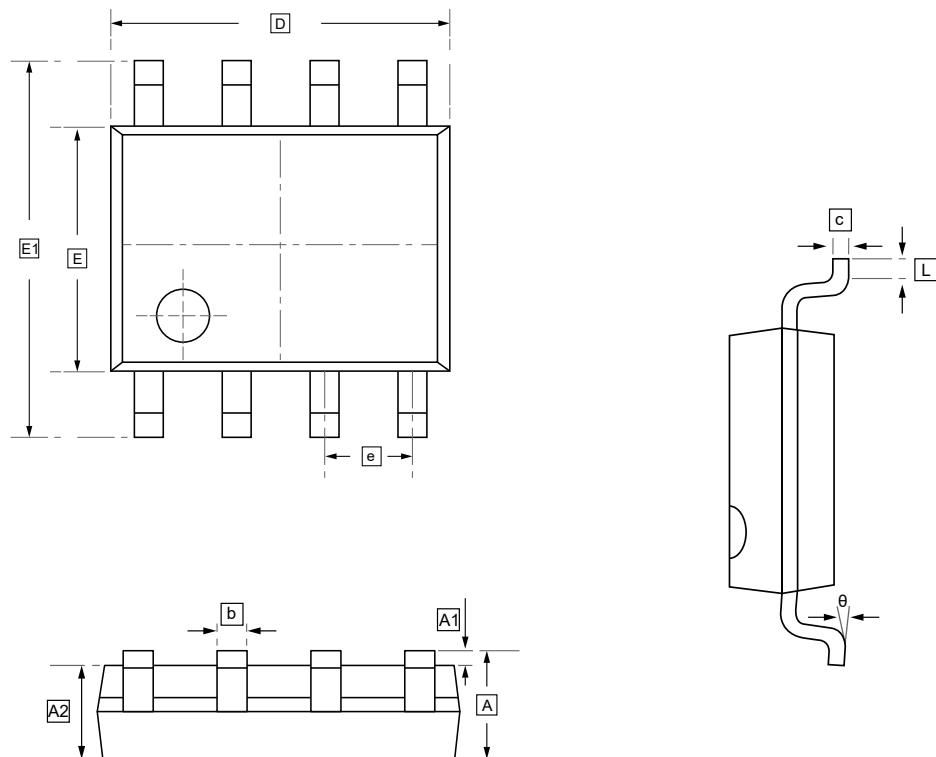

## 12.SOP-8 Package Outline Dimensions

### DIMENSIONS (mm are the original dimensions)

| Symbol     | A     | A1    | A2    | b     | c     | D     | E     | E1    | e     | L     | $\theta$ |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------|

| <b>Min</b> | 1.350 | 0.000 | 1.350 | 0.330 | 0.170 | 4.700 | 3.800 | 5.800 | 1.270 | 0.400 | 0°       |

| <b>Max</b> | 1.750 | 0.100 | 1.550 | 0.510 | 0.250 | 5.100 | 4.000 | 6.200 | BSC   | 1.270 | 8°       |

### 13.Ordering information

| Order Code      | Package | Base QTY | Delivery Mode |

|-----------------|---------|----------|---------------|

| UMW UCC27524ADR | SOP-8   | 2500     | Tape and reel |

## 14.Disclaimer

UMW reserves the right to make changes to all products, specifications. Customers should obtain the latest version of product documentation and verify the completeness and currency of the information before placing an order.

When applying our products, please do not exceed the maximum rated values, as this may affect the reliability of the entire system. Under certain conditions, any semiconductor product may experience faults or failures. Buyers are responsible for adhering to safety standards and implementing safety measures during system design, prototyping, and manufacturing when using our products to prevent potential failure risks that could lead to personal injury or property damage.

Unless explicitly stated in writing, UMW products are not intended for use in medical, life-saving, or life-sustaining applications, nor for any other applications where product failure could result in personal injury or death. If customers use or sell the product for such applications without explicit authorization, they assume all associated risks.

When reselling, applying, or exporting, please comply with export control laws and regulations of China, the United States, the United Kingdom, the European Union, and other relevant countries, regions, and international organizations.

This document and any actions by UMW do not grant any intellectual property rights, whether express or implied, by estoppel or otherwise. The product names and marks mentioned herein may be trademarks of their respective owners.