### 1.Description

The ESD7504 surge protection is designed to protect high speed data lines from ESD. Ultralow capacitance and low ESD clamping voltage make this device an ideal solution for protecting voltage sensitive high speed data lines.

# 2.Applications

- USB 3.0

- eSATA 1.0/2.0/3.0

- HDMI 1.3/1.4

- Display Port

#### 3.Features

- Low Capacitance (0.55 pF Max, I/O to GND)

- Protection for the Following IEC Standards:

- IEC 61000-4-2 (Level 4)

- Low ESD Clamping Voltage

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

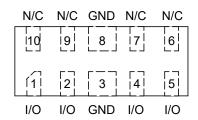

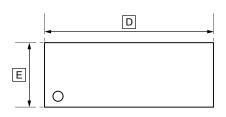

### 4. Pinning information

**DFN2510**

### **5.Absolute Maximum Ratings**

| Parameter                                     | Symbol           | Value      | Units |

|-----------------------------------------------|------------------|------------|-------|

| Junction Temperature Range                    | TJ               | -55 to 125 | °C    |

| Storage Temperature Range                     | T <sub>STG</sub> | -55 to 150 | °C    |

| Lead Solder Temperature -Maximum (10 Seconds) | TL               | 260        | °C    |

| IEC 61000-4-2 Contact (ESD)                   | V                | ±15        | kV    |

| IEC 61000-4-2 Air (ESD)                       | V <sub>ESD</sub> | ±15        | kV    |

Notes: Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## **6.Electrical Characteristics (T<sub>A</sub>=25°C unless otherwise specified)**

| Parameter                 | Symbol         | Conditions                                           |                                  | Min                 | Тур  | Max  | Units |

|---------------------------|----------------|------------------------------------------------------|----------------------------------|---------------------|------|------|-------|

| Reverse Working Voltage   | $V_{RWM}$      | I/O Pin to GND                                       |                                  |                     |      | 3.3  | V     |

| Breakdown Voltage         | $V_{BR}$       | $I_{\tau}$ =1mA, I/O Pin to GND                      |                                  | 4                   | 5    |      | V     |

| Reverse Leakage Current   | I <sub>R</sub> | V <sub>RWM</sub> =3.3V, I/O Pin to GND               |                                  |                     |      | 1    | μA    |

| Clamping Voltage (Note 1) | Vc             | IEC61000-4-2, ±8 kV Contact                          |                                  | See Figures 1 and 2 |      | V    |       |

| Clamping Voltage          |                | I <sub>PP</sub> =8A                                  | IEC 61000-4-2 Level 2 equivalent |                     | 10.2 |      | V     |

| TLP (Note 2)              | V <sub>C</sub> | I <sub>PP</sub> =-8A                                 | (±4 kV Contact, ±4 kV Air)       |                     | -4.5 |      | V     |

| See Figures 5 through 6   | V <sub>C</sub> | I <sub>PP</sub> =16A                                 | IEC 61000-4-2 Level 4 equivalent |                     | 13.7 |      | V     |

|                           |                | I <sub>PP</sub> =-16A                                | (±8 kV Contact, ±15 kV Air)      |                     | -8.1 |      | V     |

| Junction Capacitance      | C <sub>J</sub> | V <sub>R</sub> =0 V, f=1MHz between I/O Pins and GND |                                  |                     |      | 0.55 | pF    |

#### Notes:

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

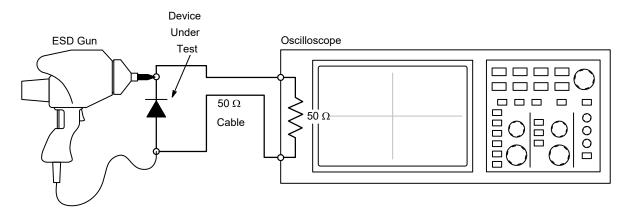

- 1. For test procedure see Figures 3 and 4

- 2. ANSI/ESD STM5.5.1 Electrostatic Discharge Sensitivity Testing using Transmission Line Pulse (TLP) Model.

TLP conditions:  $Z_0$  = 50  $\Omega$ ,  $t_p$  = 100 ns,  $t_r$  = 4 ns, averaging window;  $t_1$  = 30 ns to  $t_2$  = 60 ns.

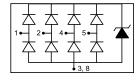

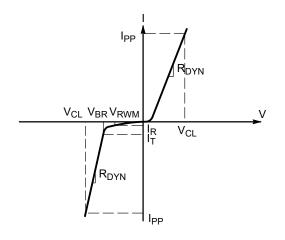

# 7.Electrical Parameters ( $T_A$ =25°C unless otherwise noted)

Uni-Directional

| Symbol          | Parameter                                          |  |  |  |  |  |

|-----------------|----------------------------------------------------|--|--|--|--|--|

| I <sub>PP</sub> | Maximum Reverse Peak Pulse Current                 |  |  |  |  |  |

| V <sub>C</sub>  | Clamping Voltage @ I <sub>PP</sub>                 |  |  |  |  |  |

| $V_{RWM}$       | Working Peak Reverse Voltage                       |  |  |  |  |  |

| I <sub>R</sub>  | Maximum Reverse Leakage Current @ V <sub>RWM</sub> |  |  |  |  |  |

| $V_{BR}$        | Breakdown Voltage @ I <sub>⊤</sub>                 |  |  |  |  |  |

| I <sub>T</sub>  | Test Current                                       |  |  |  |  |  |

| $R_{DYN}$       | Dynamic Resistance                                 |  |  |  |  |  |

# 8.1Typical characteristic

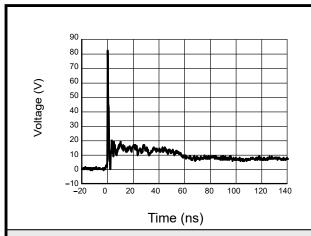

Figure 1: IEC61000-4-2 +8 kV Contact Clamping Voltage

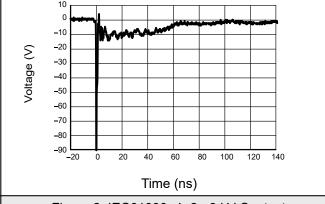

Figure 2: IEC61000-4-2 -8 kV Contact Clamping Voltage

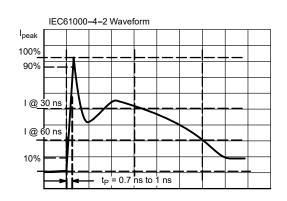

| Level | Test<br>Voltage<br>(kV) | First Peak Current (A) Current at 30 ns(A |    | Current<br>at<br>60 ns(A) |

|-------|-------------------------|-------------------------------------------|----|---------------------------|

| 1     | 2                       | 7.5                                       | 4  | 2                         |

| 2     | 4                       | 15                                        | 8  | 4                         |

| 3     | 6                       | 22.5                                      | 12 | 6                         |

| 4     | 8                       | 30                                        | 16 | 8                         |

Figure 3: IEC61000-4-2 Spec

## 8.2Typical characteristic

Figure 4. Diagram of ESD Clamping Voltage Test Setup

#### **ESD Voltage Clamping**

For sensitive circuit elements it is important to limit the voltage that an IC will be exposed to during an ESD event to as low a voltage as possible. The ESD clamping voltage is the voltage drop across the ESD protection diode during an ESD event per the IEC61000-4-2 waveform. Since the IEC61000-4-2 was written as a pass/fail spec for largersystems such as cell phones or laptop computers it is not clearly defined in the spec how to specify a clamping voltage at the device level. That has developed a way to examine the entire voltage waveform across the ESD protection diode over the time domain of an ESD pulse in the form of an oscilloscope screenshot, which can be found on the datasheets for all ESD protection diodes.

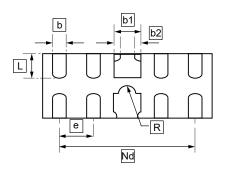

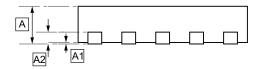

# 9.DFN2510 Package Outline Dimensions

### **DIMENSIONS** (mm are the original dimensions)

| Symbol | D    | E    | b1   | b2   | b    | L    | Nd   | е    | R     | Α    | <b>A1</b> | A2   |

|--------|------|------|------|------|------|------|------|------|-------|------|-----------|------|

| Min    | 2.45 | 0.95 | 0.35 | 0.15 | 0.10 | 0.33 | 2.00 | 0.50 | 0.125 | 0.45 | 0.152     | 1    |

| Max    | 2.55 | 1.05 | 0.45 | 0.25 | 0.20 | 0.43 | BSC  | BSC  | BSC   | 0.55 | REF       | 0.05 |

# 10.Ordering information

| Order Code       | Package | Base QTY | Delivery Mode |

|------------------|---------|----------|---------------|

| UMW ESD7504MUTAG | DFN2510 | 3000     | Tape and reel |

#### 11.Disclaimer

UMW reserves the right to make changes to all products, specifications. Customers should obtain the latest version of product documentation and verify the completeness and currency of the information before placing an order.

When applying our products, please do not exceed the maximum rated values, as this may affect the reliability of the entire system. Under certain conditions, any semiconductor product may experience faults or failures. Buyers are responsible for adhering to safety standards and implementing safety measures during system design, prototyping, and manufacturing when using our products to prevent potential failure risks that could lead to personal injury or property damage.

Unless explicitly stated in writing, UMW products are not intended for use in medical, life-saving, or life-sustaining applications, nor for any other applications where product failure could result in personal injury or death. If customers use or sell the product for such applications without explicit authorization, they assume all associated risks.

When reselling, applying, or exporting, please comply with export control laws and regulations of China, the United States, the United Kingdom, the European Union, and other relevant countries, regions, and international organizations.

This document and any actions by UMW do not grant any intellectual property rights, whether express or implied, by estoppel or otherwise. The product names and marks mentioned herein may be trademarks of their respective owners.