## 1. Description

The UMW IRS2181STR is a high voltage, high speed power MOSFET drivers with dependent high and low-side referenced output channels. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The logic input is compatible with standard CMOS or LSTTL output, down to 3.3V logic. The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive an N-channel power MOSFET in the high-side configuration which operates up to 700V.

## 3. Features

- Floating channel designed for bootstrap operation

- Fully operational to +700 V

- 3.3V, 5V and 15V input logic compatible

- dV/dt noise Immunity  $\pm 50$  V/nsec

- Allowable negative Vs capability: -9V

- Gate drive supply range from 10V to 20V

- Typically output Source/Sink current capability: 4A/4A

## 2. Applications

- Motor Control

- Air Conditioners/ Washing Machines

- General Purpose Inverters

- Micro/Mini Inverter Drives

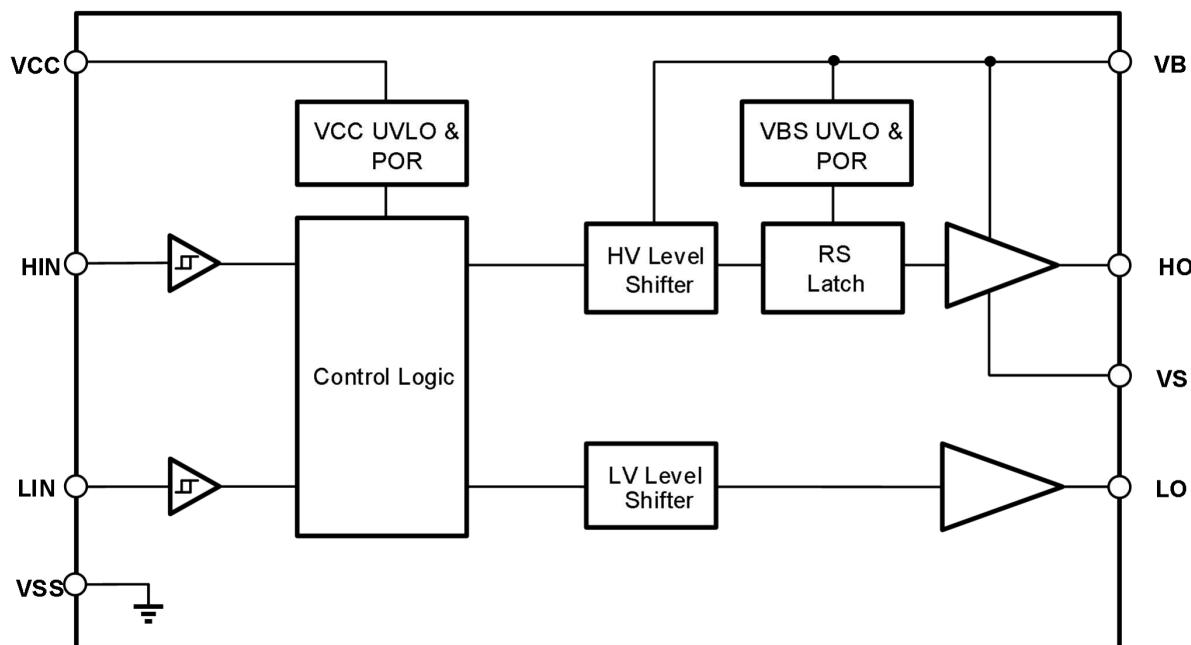

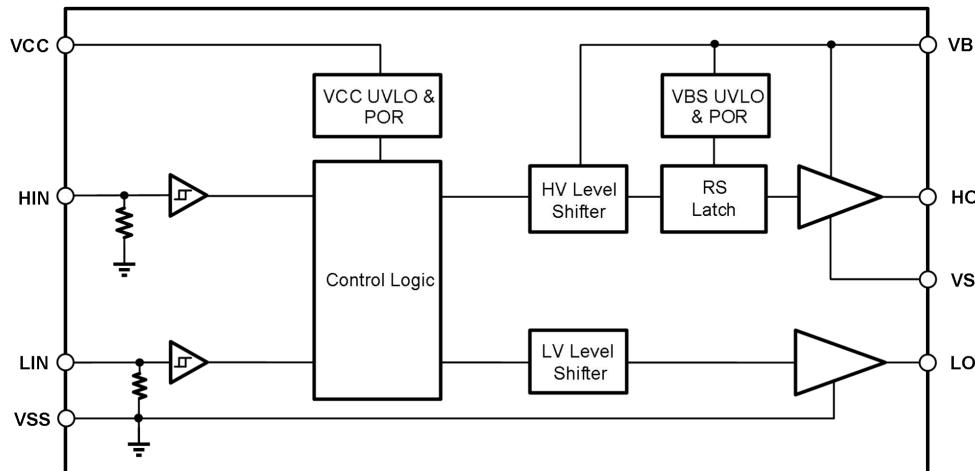

#### 4. Functional Block Diagram

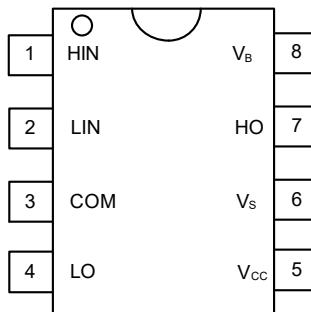

## 5. Pinning Information

SOP-8

### Lead Definitions

| Number | Symbol          | Description                                                 |

|--------|-----------------|-------------------------------------------------------------|

| 1      | HIN             | Logic input for high side gate driver output (HO), in phase |

| 2      | LIN             | Logic input for low side gate driver output (LO), in phase  |

| 3      | COM             | Low side return                                             |

| 4      | LO              | Low side gate drive output                                  |

| 5      | V <sub>cc</sub> | Low side and logic fixed supply                             |

| 6      | V <sub>s</sub>  | High side floating supply return                            |

| 7      | HO              | High side gate drive output                                 |

| 8      | V <sub>b</sub>  | High side floating supply                                   |

## 6. Absolute Maximum Ratings

Exceeding the limit maximum rating may cause permanent damage to the device. All voltage parameters are rated with reference to  $V_{SS}$  and an ambient temperature of 25°C.

| Parameter                                          | Symbol     | Min       | Max          | Units |

|----------------------------------------------------|------------|-----------|--------------|-------|

| High side floating supply                          | $V_B$      | -0.3      | 725          | V     |

| High side floating supply return                   | $V_S$      | $V_B-25$  | $V_B+0.3$    | V     |

| High side gate drive output                        | $V_{HO}$   | $V_S-0.3$ | $V_B+0.3$    | V     |

| Low side and main power supply                     | $V_{CC}$   | -0.3      | 25           | V     |

| Low side gate drive output                         | $V_{LO}$   | -0.3      | $V_{CC}+0.3$ | V     |

| Logic input of HIN & LIN                           | $V_{IN}$   | -0.3      | $V_{CC}+0.3$ | V     |

| HBM Model                                          | ESD        | 1.5       |              | kV    |

| Machine Mode                                       |            | 500       |              | V     |

| IPackage Power Dissipation @ $T_A \leq 25^\circ C$ | $P_D$      |           | 0.625        | W     |

| Thermal Resistance, Junction to Ambient            | $R_{thJA}$ |           | 200          | °C/W  |

| Junction Temperature                               | $T_J$      |           | 150          | °C    |

| Storage Temperature                                | $T_S$      | -55       | 150          | °C    |

| Lead Temperature (Soldering, 10 seconds)           | $T_L$      |           | 300          | °C    |

## 7. Recommended Operating Conditions

For proper operation, the device should be used under the following recommended conditions. The bias ratings of VS and VSS are measured at a supply voltage of 15V, and unless otherwise specified, the ratings of all voltage parameters are referenced to VSS and the ambient temperature is 25°C.

| Parameter                        | Symbol          | Min                 | Max                 | Units |

|----------------------------------|-----------------|---------------------|---------------------|-------|

| High side floating supply        | V <sub>B</sub>  | V <sub>S</sub> + 10 | V <sub>S</sub> + 20 | V     |

| High side floating supply return | V <sub>S</sub>  | -9                  | 700                 | V     |

| High side gate drive output      | V <sub>HO</sub> | V <sub>S</sub>      | V <sub>B</sub>      | V     |

| Low side and main power supply   | V <sub>CC</sub> | 10                  | 20                  | V     |

| Low side gate drive output       | V <sub>LO</sub> | 0                   | V <sub>CC</sub>     | V     |

| Logic input of HIN & LIN         | V <sub>IN</sub> | 0                   | V <sub>CC</sub>     | V     |

| Ambient temperature              | T <sub>A</sub>  | -40                 | 125                 | °C    |

## 8. Electrical Characteristics

Valid for temperature range at  $T_A=25^\circ\text{C}$ ,  $V_{CC}=V_B=15\text{V}$ ,  $C_L=1\text{nF}$ , unless otherwise specified.

| Parameter                                   | Symbol        | Conditions                               | Min | Typ | Max | Units         |

|---------------------------------------------|---------------|------------------------------------------|-----|-----|-----|---------------|

| Turn-on propagation delay                   | $t_{ON}$      | $V_S=0\text{V}$                          |     | 130 | 250 | ns            |

| Turn-off propagation delay                  | $t_{OFF}$     | $V_S=0\text{V}$ or $700\text{V}$         |     | 130 | 250 | ns            |

| Turn-on rise time                           | $t_R$         | $V_S=0\text{V}$                          |     | 15  | 20  | ns            |

| Turn-off fall time                          | $t_F$         | $V_S=0\text{V}$                          |     | 10  | 15  | ns            |

| Matched propagation time delay              | MT            |                                          |     |     | 50  | ns            |

| $V_{CC}$ supply UVLO threshold              | $V_{CCUV+}$   |                                          | 8   | 8.9 | 9.8 | V             |

|                                             | $V_{CCUV-}$   |                                          | 7.4 | 8.2 | 9   | V             |

| Hysteresis of $V_{CC}$ UVLO                 | $V_{CCUVHYS}$ |                                          |     | 0.7 |     | V             |

| $V_{BS}$ supply UVLO threshold              | $V_{BSUV+}$   |                                          | 8   | 8.9 | 9.8 | V             |

|                                             | $V_{BSUV-}$   |                                          | 7.4 | 8.2 | 9   | V             |

| hysteresis of $V_{BS}$ UVLO                 | $V_{BSUVHYS}$ |                                          |     | 0.7 |     | V             |

| High-side floating supply leakage current   | $I_{LK}$      | $V_B=V_S=700\text{V}$                    |     |     | 50  | $\mu\text{A}$ |

| Quiescent $V_B$ supply current              | $I_{QBS}$     | $V_{IN}=0\text{V}$ or $5\text{V}$        |     | 50  | 100 | $\mu\text{A}$ |

| Quiescent $V_{CC}$ supply current           | $I_{QCC}$     | $V_{IN}=0\text{V}$ or $5\text{V}$        |     | 150 | 240 | $\mu\text{A}$ |

| Logic "1" input voltage                     | $V_{IH}$      | $V_{CC}=10\text{V}$ to $20\text{V}$      | 2.5 |     |     | V             |

| Logic "0" input voltage                     | $V_{IL}$      | $V_{CC}=10\text{V}$ to $20\text{V}$      |     |     | 0.8 | V             |

| High level output voltage, $V_{BIAS} - V_O$ | $V_{OH}$      | $I_O=0\text{A}$                          |     |     | 1.4 | V             |

| Low level output voltage, $V_O$             | $V_{OL}$      | $I_O=20\text{mA}$                        |     |     | 0.1 | V             |

| Logic "1" input bias current                | $I_{IN+}$     | $LIN=5\text{V}$                          |     | 25  | 60  | $\mu\text{A}$ |

| Logic "0" input bias current                | $I_{IN-}$     | $LIN=0\text{V}$                          |     |     | 2   | $\mu\text{A}$ |

| Output high short circuit pulsed current    | $I_{O+}$      | $V_O=0\text{V}$ , $PW \leq 10\text{us}$  | 3   | 4   |     | A             |

| Output low short circuit pulsed current     | $I_{O-}$      | $V_O=15\text{V}$ , $PW \leq 10\text{us}$ | 3   | 4   |     | A             |

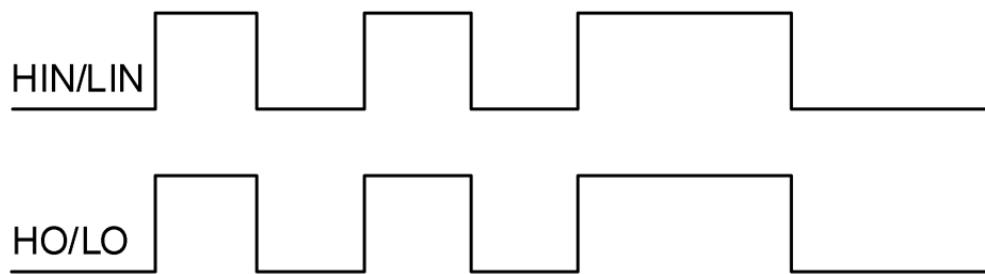

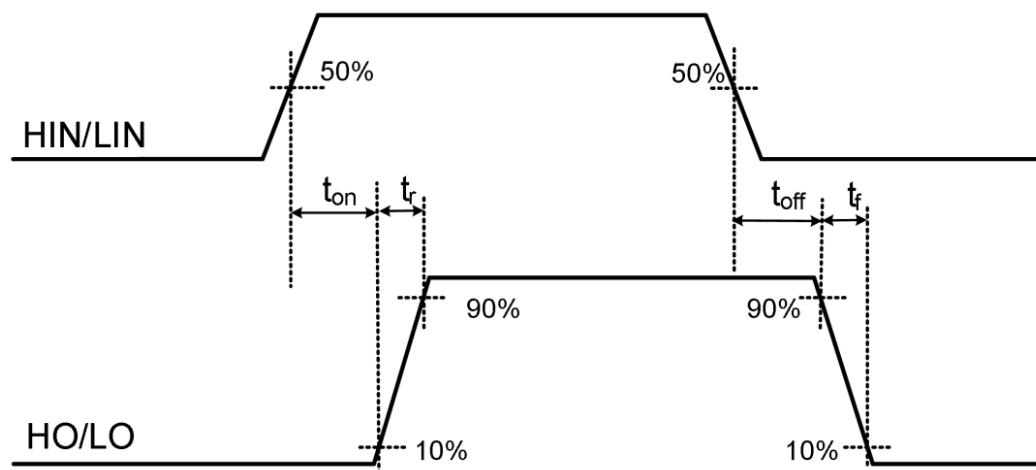

## 9. Function Description

Figure 1. UMW IRS2181STR Input and output timing waveform

Figure 2. Propagation Time Waveform Definition

## 10. Function Block Diagram

Figure 3. Function Block Diagram of UMW IRS2181STR

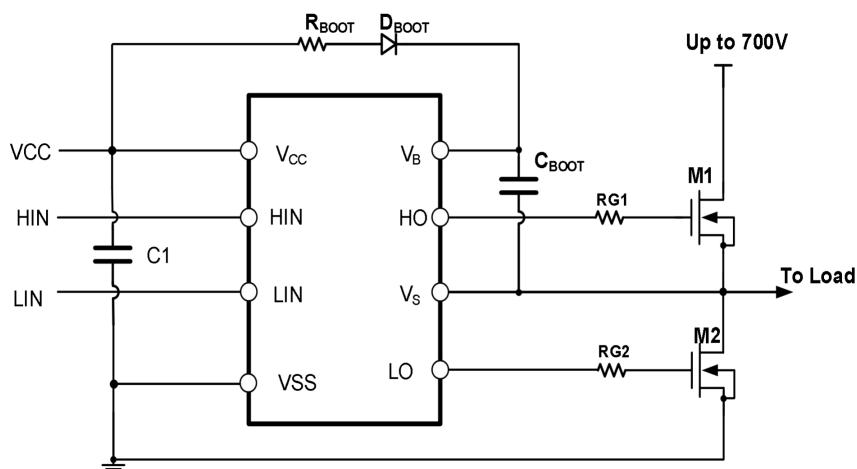

## 11. Application Message

Figure 4. Typical application circuit of UMW IRS2181STR

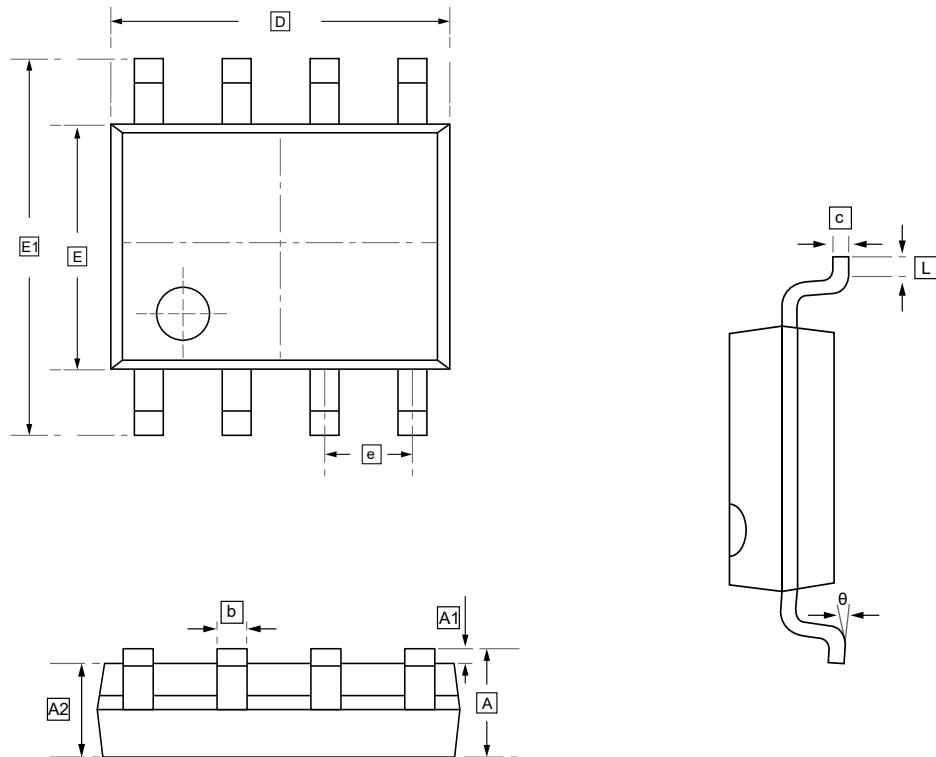

## 12. SOP-8 Package Outline Dimensions

### DIMENSIONS (mm are the original dimensions)

| Symbol     | A     | A1    | A2    | b     | c     | D     | E     | E1    | e     | L     | θ  |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----|

| <b>Min</b> | 1.350 | 0.000 | 1.350 | 0.330 | 0.170 | 4.700 | 3.800 | 5.800 | 1.270 | 0.400 | 0° |

| <b>Max</b> | 1.750 | 0.100 | 1.550 | 0.510 | 0.250 | 5.100 | 4.000 | 6.200 | BSC   | 1.270 | 8° |

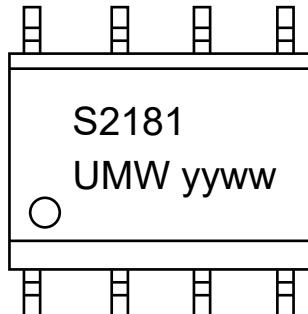

### **13.Ordering information**

yy: Year Code

ww: Week Code

| Order Code     | Package | Base QTY | Delivery Mode |

|----------------|---------|----------|---------------|

| UMW IRS2181STR | SOP-8   | 2500     | Tape and reel |

## 14.Disclaimer

UMW reserves the right to make changes to all products, specifications. Customers should obtain the latest version of product documentation and verify the completeness and currency of the information before placing an order.

When applying our products, please do not exceed the maximum rated values, as this may affect the reliability of the entire system. Under certain conditions, any semiconductor product may experience faults or failures. Buyers are responsible for adhering to safety standards and implementing safety measures during system design, prototyping, and manufacturing when using our products to prevent potential failure risks that could lead to personal injury or property damage.

Unless explicitly stated in writing, UMW products are not intended for use in medical, life-saving, or life-sustaining applications, nor for any other applications where product failure could result in personal injury or death. If customers use or sell the product for such applications without explicit authorization, they assume all associated risks.

When reselling, applying, or exporting, please comply with export control laws and regulations of China, the United States, the United Kingdom, the European Union, and other relevant countries, regions, and international organizations.

This document and any actions by UMW do not grant any intellectual property rights, whether express or implied, by estoppel or otherwise. The product names and marks mentioned herein may be trademarks of their respective owners.