## AT32F415使用限制

## 前言

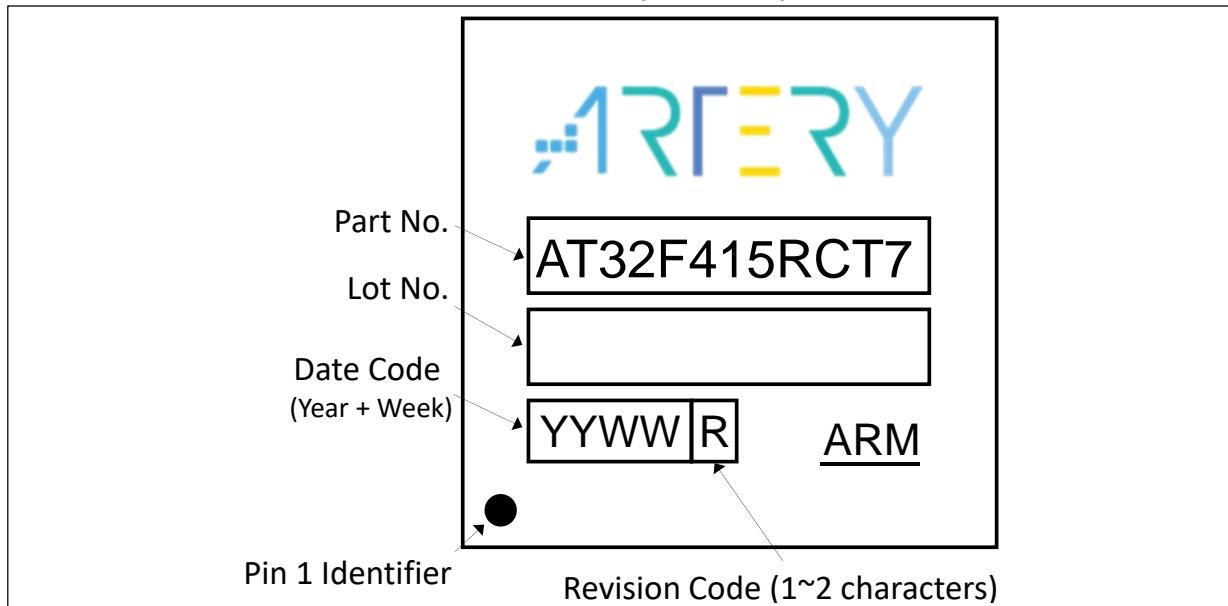

该勘误表适用于雅特力科技的AT32F415系列芯片。该芯片系列集成了ARM® 32位Cortex®-M4内核。表2列出了涉及的产品型号。表1列出了本文涉及产品的识别：

- 通过芯片封装上产品标识下的版本号

表 1. 芯片的识别

| 销售型号     | 标注在芯片上的版本代码 |

|----------|-------------|

| AT32F415 | “B”         |

|          | “C”         |

|          | “D”         |

|          |             |

1. 产品容量信息和器件唯一ID寄(UID地址：0x1FFF F7E8)中的Bit[78:76] Mask\_Version指明芯片的版本号，即通过地址0x1FFF7F1的Bit[6:4]获知版本号，比如

B版：0b001

C版：0b010

D版：0b011

2. 关于在不同芯片封装上识别版本号，请参 [2 产品上硅版本号标示](#)。

表 2. 芯片概览

|    |             |

|----|-------------|

| 型号 | AT32F415 系列 |

|----|-------------|

# 目录

|          |                                                      |          |

|----------|------------------------------------------------------|----------|

| <b>1</b> | <b>AT32F415 芯片的使用限制.....</b>                         | <b>7</b> |

| 1.1      | ADC.....                                             | 8        |

| 1.1.1    | ADC 普通通道组序列转换期间更改抢占通道配置将会导致普通通道组转换数据错序 .             | 8        |

| 1.1.2    | ADC 抢占通道组转换结束标志无法清除及置位问题 .....                       | 8        |

| 1.2      | CAN.....                                             | 9        |

| 1.2.1    | CAN 通讯数据域期间出现位填充错误会导致下一帧数据错位问题 .....                 | 9        |

| 1.2.2    | 32 位宽标识符掩码模式下无法有效过滤标准帧的 RTR 位 .....                  | 12       |

| 1.2.3    | CAN 在有窄脉冲干扰 BS2 段的条件下有概率会发送非预期的报文.....               | 13       |

| 1.2.4    | CAN 总线在人为或异常断开后执行邮箱的取消发送命令无效.....                    | 13       |

| 1.3      | ERTC .....                                           | 14       |

| 1.3.1    | TAMPER PIN 产生唤醒事件输出的条件.....                          | 14       |

| 1.3.2    | TIME 和 DATE 寄存器的值更新条件 .....                          | 14       |

| 1.3.3    | 使用 LEXT 做 ERTC 时钟源时，每次系统复位后时间慢 3~6 个 LEXT 时钟周期 ..... | 14       |

| 1.4      | GPIO .....                                           | 15       |

| 1.4.1    | 复位期间 PC0~5 下拉电阻异常开启 .....                            | 15       |

| 1.4.2    | FT (5 V 容忍) 引脚浮空输入时维持在中间电平 .....                     | 15       |

| 1.5      | I2S .....                                            | 15       |

| 1.5.1    | I2S 的 CK 线在受到干扰后，通信就无法再自动恢复正常 .....                  | 15       |

| 1.5.2    | I2S 飞利浦协议在特定条件下通讯起始帧数据异常 .....                       | 15       |

| 1.5.3    | I2S PCM 长帧只收模式下接收第一笔数据错位问题.....                      | 16       |

| 1.5.4    | I2S 从发模式非连续通讯状态下误置位 UDR 标志问题 .....                   | 16       |

| 1.5.5    | I2S 24 位数据封装成 32 位帧格式接收异常问题 .....                    | 16       |

| 1.6      | OTG .....                                            | 16       |

| 1.6.1    | OTG_FS Device 模式下 VBUS (PA9) 无法释放给其它外设使用 .....       | 16       |

| 1.7      | PWC .....                                            | 16       |

| 1.7.1    | VDD 大于 PVM 阈值时使能 PVM 会误触发一次 PVM 事件 .....             | 16       |

| 1.7.2    | AHB 分频后 DEEPSLEEP 模式无法被唤醒 .....                      | 17       |

| 1.7.3    | Systick 中断误唤醒 DEEPSLEEP .....                        | 17       |

| 1.7.4    | 进 DEEPSLEEP 过程瞬间被立即唤醒时异常 .....                       | 17       |

|        |                                                                          |    |

|--------|--------------------------------------------------------------------------|----|

| 1.7.5  | 待机唤醒引脚使能时误置位 SWEF 标志问题 .....                                             | 17 |

| 1.7.6  | DEEPSLEEP 过渡状态唤醒后无法立即配置系统时钟 .....                                        | 18 |

| 1.7.7  | 使运行和睡眠模式达到更省电的设置方法 .....                                                 | 18 |

| 1.7.8  | V <sub>BAT</sub> 供电域寄存器在特定条件时上电复位失败 .....                                | 19 |

| 1.7.9  | V <sub>BAT</sub> 和 V <sub>DD</sub> 同时上电且上电速度慢于 3ms/V 可能引起 LEXT 不起振 ..... | 19 |

| 1.8    | SPI .....                                                                | 20 |

| 1.8.1  | SPI 已置位的接收数据传输 DMA 请求无法通过读 DT 寄存器清除 .....                                | 20 |

| 1.8.2  | SPI 从机硬件 CS 模式下 CS 下降沿不会做重同步 .....                                       | 20 |

| 1.9    | TMR .....                                                                | 20 |

| 1.9.1  | 外部时钟模式 B 加挂起模式条件下挂起模式失效 .....                                            | 20 |

| 1.9.2  | TMR 产生的 DMA 请求的清除方式 .....                                                | 20 |

| 1.9.3  | TMR 在编码器模式下的溢出事件 .....                                                   | 21 |

| 1.9.4  | TMR 用 DMA 访问 0x4C 偏移地址可能导致 DMA 请求异常 .....                                | 21 |

| 1.9.5  | 次 TMR 无法接收由外部触发的主 TMR 复位的输出信号 .....                                      | 21 |

| 1.9.6  | 未使能定时器时 (TMREN = 0), 刹车输入无效 .....                                        | 22 |

| 1.9.7  | CxORAW 信号清除功能在启用死区时, 输出异常 .....                                          | 22 |

| 1.10   | USART .....                                                              | 22 |

| 1.10.1 | USART3 和 TMR1/TMR3 同时使用至 PA7 异常 .....                                    | 22 |

| 1.10.2 | USART 在 IrDA 模式下无法正常接收 .....                                             | 22 |

| 1.10.3 | USART 配置完后立即清除 TDC 位, 无法正常发送数据 .....                                     | 23 |

| 1.10.4 | USART 仅能透过读取数据寄存器清除 RDBF 标志位 .....                                       | 23 |

| 1.10.5 | USART 在静默状态下用 DMA 接收仍能收到数据 .....                                         | 23 |

| 1.11   | WWDT .....                                                               | 23 |

| 1.11.1 | 使用 WWDT 中断时, 无法清除 RLDF 标志 .....                                          | 23 |

| 1.12   | WDT .....                                                                | 24 |

| 1.12.1 | 使能 WDT 后立即进入 Standby 模式, 会发生复位 .....                                     | 24 |

| 1.12.2 | 使能 WDT 后立即进入 deepsleep 模式, WDT 未被成功使能 .....                              | 24 |

| 1.13   | CRM .....                                                                | 24 |

| 1.13.1 | 进入 DEEPSLEEP 模式后 CLKOUT 可能有时钟输出问题 .....                                  | 24 |

| 1.13.2 | PLL 的倍频系数 2 倍 3 倍可能错误 .....                                              | 25 |

| 1.14   | I2C .....                                                                | 25 |

|                                                           |           |

|-----------------------------------------------------------|-----------|

| 1.14.1 在 APB 时钟小于等于 4MHz 时, I2C 做从机无法在 400kHz 的速度下通讯..... | 25        |

| 1.14.2 I2C 在通信开始前, 当总线上出现 BUSERR 时序, 会误检测到 BUSERR .....   | 25        |

| 1.15 FLASH.....                                           | 25        |

| 1.15.1 SLib 以及 boot memory AP mode 配置要求.....              | 25        |

| <b>2 产品上硅版本号标示 .....</b>                                  | <b>27</b> |

| <b>3 版本历史 .....</b>                                       | <b>28</b> |

## 表目录

|                    |    |

|--------------------|----|

| 表 1. 芯片的识别.....    | 1  |

| 表 2. 芯片概览.....     | 1  |

| 表 3. 芯片局限性列表 ..... | 7  |

| 表 4. 文档版本历史 .....  | 28 |

## 图目录

|                       |    |

|-----------------------|----|

| 图 1. 丝印标记(封装俯视图)..... | 27 |

|-----------------------|----|

# 1 AT32F415 芯片的使用限制

下表是所有已经发现的局限性概览：

表 3. 芯片局限性列表

| 章节       | 内容                                                                       | B版   | C版    | D版    |

|----------|--------------------------------------------------------------------------|------|-------|-------|

| 1.1 ADC  | 1.1.1 ADC 普通通道组序列转换期间更改抢占通道配置将会导致普通通道组转换数据错序                             | Fail | Fixed | Fixed |

|          | 1.1.2 ADC 抢占通道组转换结束标志无法清除及置位问题                                           | Fail | Fail  | Fail  |

| 1.2 CAN  | 1.2.1 CAN 通讯数据域期间出现位填充错误会导致下一帧数据错位问题                                     | Fail | Fail  | Fixed |

|          | 1.2.2 32 位宽标识符掩码模式下无法有效过滤标准帧的 RTR 位                                      | Fail | Fail  | Fail  |

|          | 1.2.3 CAN 在有窄脉冲干扰 BS2 段的条件下有概率会发送非预期的报文                                  | Fail | Fail  | Fixed |

|          | 1.2.4 CAN 总线在人为或异常断开后执行邮箱的取消发送命令无效                                       | Fail | Fail  | Fail  |

| 1.3 ERTC | 1.3.1 TAMPER PIN 产生唤醒事件输出的条件                                             | Fail | Fixed | Fixed |

|          | 1.3.2 TIME 和 DATE 寄存器的值更新条件                                              | Fail | Fail  | Fail  |

|          | 1.3.3 使用 LEXT 做 ERTC 时钟源时，每次系统复位后时间慢 3~6 个 LEXT 时钟周期                     | Fail | Fixed | Fixed |

| 1.4 GPIO | 1.4.1 复位期间 PC0~5 下拉电阻异常开启                                                | Fail | Fixed | Fixed |

|          | 1.4.2 FT (5 V 容忍) 引脚浮空输入时维持在中间电平                                         | Fail | Fail  | Fail  |

| 1.5 I2S  | 1.5.1 I2S 的 SCK 线在受到干扰后，通信就无法再自动恢复正常                                     | Fail | Fixed | Fixed |

|          | 1.5.2 I2S 飞利浦协议在特定条件下通讯起始帧数据异常                                           | Fail | Fixed | Fixed |

|          | 1.5.3 I2S PCM 长帧只收模式下接收第一笔数据错位问题                                         | Fail | Fail  | Fail  |

|          | 1.5.4 I2S 从发模式非连续通讯状态下误置位 UDR 标志问题                                       | Fail | Fail  | Fail  |

|          | 1.5.5 I2S 24 位数据封装成 32 位帧格式接收异常问题                                        | Fail | Fail  | Fail  |

| 1.6 OTG  | 1.6.1 OTG_FS Device 模式下 VBUS (PA9) 无法释放给其它外设使用                           | Fail | Fixed | Fixed |

| 1.7 PWC  | 1.7.1 VDD 大于 PVM 阈值时使能 PVM 会误触发一次 PVM 事件                                 | Fail | Fail  | Fail  |

|          | 1.7.2 AHB 分频后 DEEPSLEEP 模式无法被唤醒                                          | Fail | Fail  | Fail  |

|          | 1.7.3 Systick 中断误唤醒 DEEPSLEEP                                            | Fail | Fail  | Fail  |

|          | 1.7.4 进 DEEPSLEEP 过程瞬间被立即唤醒时异常                                           | Fail | Fixed | Fixed |

|          | 1.7.5 待机唤醒引脚使能时误置位 SWEF 标志问题                                             | Fail | Fail  | Fail  |

|          | 1.7.6 DEEPSLEEP 过渡状态唤醒后无法立即配置系统时钟                                        | Fail | Fail  | Fail  |

|          | 1.7.7 使运行和睡眠模式达到更省电的设置方法                                                 | Fail | Fixed | Fixed |

|          | 1.7.8 VBAT 供电域寄存器在特定条件时上电复位失败                                            | Fail | Fail  | Fail  |

|          | 1.7.9 V <sub>BAT</sub> 和 V <sub>DD</sub> 同时上电且上电速度慢于 3ms/V 可能引起 LEXT 不起振 | Fail | Fail  | Fail  |

| 1.8 SPI  | 1.8.1 SPI 已置位的接收数据传输 DMA 请求无法通过读 DT 寄存器清除                                | Fail | Fail  | Fail  |

|          | 1.8.2 SPI 从机硬件 CS 模式下 CS 下降沿不会做重同步                                       | Fail | Fail  | Fail  |

| 1.9 TMR  | 1.9.1 外部时钟模式 B 加挂起模式条件下挂起模式失效                                            | Fail | Fixed | Fixed |

|          | 1.9.2 TMR 产生的 DMA 请求的清除方式                                                | Fail | Fixed | Fixed |

|          | 1.9.3 TMR 在编码器模式下的溢出事件                                                   | Fail | Fixed | Fixed |

|          | 1.9.4 TMR 用 DMA 访问 0x4C 偏移地址可能导致 DMA 请求异常                                | Fail | Fixed | Fixed |

|          | 1.9.5 次 TMR 无法接收由外部触发的主 TMR 复位的输出信号                                      | Fail | Fail  | Fail  |

|          | 1.9.6 未使能定时器时 (TMREN = 0)，刹车输入无效                                         | Fail | Fail  | Fail  |

|          | 1.9.7 CxORAW 信号清除功能在启用死区时，输出异常                                           | Fail | Fail  | Fail  |

| 章节         | 内容                                                  | B版   | C版    | D版    |

|------------|-----------------------------------------------------|------|-------|-------|

| 1.10 USART | 1.10.1 USART3 和 TMR1/TMR3 同时使用至 PA7 异常              | Fail | Fixed | Fixed |

|            | 1.10.2 USART 在 IrDA 模式下无法正常接收                       | Fail | Fixed | Fixed |

|            | 1.10.3 USART 配置完后立即清除 TDC 位，无法正常发送数据                | Fail | Fixed | Fixed |

|            | 1.10.4 USART 仅能透过读取数据寄存器清除 RDBF 标志位                 | Fail | Fixed | Fixed |

|            | 1.10.5 USART 在静默状态下用 DMA 接收仍能收到数据                   | Fail | Fail  | Fail  |

| 1.11 WWDT  | 1.11.1 使用 WWDT 中断时，无法清除 RLDF 标志                     | Fail | Fixed | Fixed |

| 1.12 WDT   | 1.12.1 使能 WDT 后立即进入 Standby 模式，会发生复位                | Fail | Fixed | Fixed |

|            | 1.12.2 使能 WDT 后立即进入 deepsleep 模式，WDT 未被成功使能         | Fail | Fixed | Fixed |

| 1.13 CRM   | 1.13.1 进入 DEEPSLEEP 模式后 CLKOUT 可能有时钟输出问题            | Fail | Fail  | Fail  |

|            | 1.13.2 PLL 的倍频系数 2 倍和 3 倍可能出错                       | Fail | Fail  | Fail  |

| 1.14 I2C   | 1.14.1 在 APB 时钟小于等于 4MHz 时，I2C 做从机无法在 400kHz 的速度下通讯 | Fail | Fail  | Fail  |

|            | 1.14.2 I2C 在通信开始前，当总线上出现 BUSERR 时序，会误检测到 BUSERR     | Fail | Fail  | Fail  |

| 1.15 FLASH | 1.15.1 SLib 以及 boot memory AP mode 配置要求             | Fail | Fail  | Fail  |

## 1.1 ADC

### 1.1.1 ADC 普通通道组序列转换期间更改抢占通道配置将会导致普通通道组转换数据错序

- 问题描述：

ADC普通通道组序列及反复转换模式下，在普通通道组转换过程中更改抢占通道组通道配置将导致普通通道组转换数据错序。

例如：普通通道组序列转换1、2、3、4 通道，在通道2转换期间更改抢占通道组通道配置，将会导致普通通道组通道2重复转换两次，最终普通通道转换数据为 1、2、2、3、4。

- 解决方法：

同时使用多通道普通及抢占转换时，配置完抢占通道组后，不能再去切换其配置。

- 改版记录：

已于硅版本C修正。

### 1.1.2 ADC 抢占通道组转换结束标志无法清除及置位问题

- 问题描述：

当ADC“清除抢占通道组转换结束标志PCCE”与“普通通道组转换结束CCE事件”同时发生时，会出现PCCE标志无法被及时清除，且下一次PCCE标志无法及时置位问题。

- 解决方法：

在原清除PCCE标志命令处再执行一次该标志的清除命令。参考如下

```

/* 修改前 */

adc_flag_clear(ADC1, ADC_PCCE_FLAG);

/* 修改后 */

adc_flag_clear(ADC1, ADC_PCCE_FLAG);

adc_flag_clear(ADC1, ADC_PCCE_FLAG);

```

- 改版记录：

无。

## 1.2 CAN

### 1.2.1 CAN 通讯数据域期间出现位填充错误会导致下一帧数据错位问题

- 问题描述：

如果CAN因为外部干扰导致通讯的数据域期间出现位填充错误，此时会按照期望停止接收当前帧数据并回馈错误到总线上，但是下一帧通讯报文会出现数据错序，且随后的报文又自动恢复正常的现象。

- 解决方法：

方法1：开启CAN的错误类型记录中断号对应的错误中断（中断优先级需设定为最高），在CAN错误类型记录中断的中断函数内检测到出现位填充错误时，复位CAN（可只复位CAN寄存器，其相关的GPIO等、NVIC不需复位），并在CAN错误中断函数内完成CAN的重新初始化。

此方法适用于期望快速完成CAN的初始化，以保障CAN及时参与通讯，避免过多CAN数据丢失的场景。

以CAN1为例，其典型示例代码如下：

```

/* 开启 CAN 的上次错误中断号对应的错误中断并设定中断最高优先级 */

nvic_irq_enable(CAN1_SE_IRQn, 0x00, 0x00);

can_interrupt_enable(CAN1, CAN_ETRIEN_INT, TRUE);

can_interrupt_enable(CAN1, CAN_EOIEN_INT, TRUE);

/* 中断服务函数 */

void CAN1_SE_IRQHandler(void)

{

__IO uint32_t err_index = 0;

if(can_flag_get(CAN1,CAN_ETR_FLAG) != RESET)

{

err_index = CAN1->est & 0x70;

can_flag_clear(CAN1, CAN_ETR_FLAG);

if(err_index == 0x00000010)

{

can_reset(CAN1);

/* 调用CAN初始化函数 */

}

}

}

```

#### 注意事项

- a) CAN错误类型记录中断的优先级需设定为最高；

- b) 由于CAN初始化存在耗时，出现问题后CAN不能及时恢复参与通讯，因此存在丢数据的现

象。

方法2：开启CAN的错误类型记录中断号对应的错误中断（中断优先级需设定为最高），在CAN错误类型记录中断的中断函数内检测到出现位填充错误时，复位CAN（可只复位CAN寄存器，其相关的GPIO等、NVIC不需复位），及记录复位事件，并通过在其他低优先级中断或main函数内重新进行CAN初始化。

此方法适用于可接受CAN不能及时参与通讯，需严格保障CAN的重新初始化不影响其他应用逻辑的实现场景。

以CAN1为例，其典型示例代码如下：

```

/* 开启 CAN 的上次错误中断号对应的错误中断并设定中断最高优先级 */

nvic_irq_enable(CAN1_SE_IRQn, 0x00, 0x00);

can_interrupt_enable(CAN1, CAN_ETRIEN_INT, TRUE);

can_interrupt_enable(CAN1, CAN_EOIEN_INT, TRUE);

/* 中断服务函数 */

__IO uint32_t can_reset_index = 0;

void CAN1_SE_IRQHandler(void)

{

__IO uint32_t err_index = 0;

if(can_flag_get(CAN1,CAN_ETR_FLAG) != RESET)

{

err_index = CAN1->estst & 0x70;

can_flag_clear(CAN1, CAN_ETR_FLAG);

if(err_index == 0x00000010)

{

can_reset(CAN1);

can_reset_index = 1;

}

}

}

```

应用再在期望的地方（例如main函数内）查询can\_reset\_index是否置位，置位后调用CAN初始化函数。

### 注意事项

- a) CAN错误类型记录中断的优先级需设定为最高；

- b) 由于CAN初始化及其他应用中断存在耗时，出现问题后CAN不能及时恢复参与通讯，因此存在丢数据的现象。

方法3：开启CAN的错误类型记录中断号对应的错误中断（中断优先级需设定为最高），在CAN错误类型记录中断的中断函数内检测到出现位填充错误时，强制发送一帧标识符优先级最高的无效报文。

此方法适用于不期望消耗时间去复位CAN，CAN总线上的所有报文标识符均为已知，且CAN各个节点有严格按照标识符过滤条件来接收报文的实现场景。

以CAN1为例，其典型示例代码如下：

```

/* 强制发送一帧标识符优先级最高的无效报文 */

static void can_transmit_data(void)

{

uint8_t transmit_mailbox;

can_tx_message_type tx_message_struct;

tx_message_struct.standard_id = 0x0;

tx_message_struct.extended_id = 0x0;

tx_message_struct.id_type = CAN_ID_STANDARD;

tx_message_struct.frame_type = CAN_TFT_DATA;

tx_message_struct.dlc = 8;

tx_message_struct.data[0] = 0x00;

tx_message_struct.data[1] = 0x00;

tx_message_struct.data[2] = 0x00;

tx_message_struct.data[3] = 0x00;

tx_message_struct.data[4] = 0x00;

tx_message_struct.data[5] = 0x00;

tx_message_struct.data[6] = 0x00;

tx_message_struct.data[7] = 0x00;

can_message_transmit(CAN1, &tx_message_struct);

}

/* 开启 CAN 的上次错误中断号对应的错误中断并设定最高优先级 */

nvic_irq_enable(CAN1_SE_IRQn, 0x00, 0x00);

can_interrupt_enable(CAN1, CAN_ETRIEN_INT, TRUE);

can_interrupt_enable(CAN1, CAN_EOINEN_INT, TRUE);

/* 中断服务函数 */

void CAN1_SE_IRQHandler(void)

{

__IO uint32_t err_index = 0;

if(can_flag_get(CAN1,CAN_ETR_FLAG) != RESET)

{

err_index = CAN1->ests & 0x70;

can_flag_clear(CAN1, CAN_ETR_FLAG);

if(err_index == 0x00000010)

{

can_transmit_data();

}

}

}

```

### 注意事项

- a) CAN错误类型记录中断的优先级需设定为最高;

- b) 此方法仅适用于发送FIFO优先级由报文标识符决定的场景;

- c) 此方法无效报文的标识符可修改，但一定要确保其标识符的优先级是CAN总线上最高的，且不会被其他节点当做正常报文接收;

- d) 用于解法的无效报文可以是不带数据的远程帧;

- e) 若节点本身需要使用发送功能，则在解法内容执行时，需要先取消邮箱内已有的报文发送，随后才可发送无效报文;

- f) 若总线环境比较恶劣，致使节点可能会处于错误被动状态时，不适用本解法。

- 改版记录：

已于硅版本D修正。

## 1.2.2 32位宽标识符掩码模式下无法有效过滤标准帧的RTR位

- 问题描述：

当CAN的过滤器模式设置为32位宽标识符掩码模式时，在标准帧的过滤过程中，RTR位（即远程帧标识符）无法被有效过滤。

即同时满足如下使用条件时，需要采用解决方法描述进行处理：

1. 过滤器模式选用32位宽标识符掩码模式

2. 进行标准帧过滤且不期望接收符合过滤条件的远程帧

- 解决方法：

方法1：使用软件补充RTR位的过滤。即32位宽标识符掩码模式下过滤标准帧时，使用软件判断RTR位（远程帧标识符）的状态，来决定该帧报文是否被应用需要。参考示例：

```

void CAN1_RX0_IRQHandler(void)

{

can_rx_message_type rx_message_struct;

if(can_flag_get(CAN1,CAN_RF0MN_FLAG) != RESET)

{

can_message_receive(CAN1, CAN_RX_FIFO0, &rx_message_struct);

/* only store the data frame,discard the remote frame */

if((rx_message_struct.id_type == CAN_ID_STANDARD) && (rx_message_struct.frame_type ==

CAN_TFT_DATA))

{

/* user store the receive data */

}

}

}

```

方法2：更换使用其他过滤模式。结合实际应用需求，使用其他过滤模式来替代，比如32位宽标识符列表模式、16位宽标识符掩码模式或16位宽标识符列表模式。

- 改版记录：

无。

### 1.2.3 CAN 在有窄脉冲干扰 BS2 段的条件下有概率会发送非预期的报文

- 问题描述:

当CAN总线上有大量的窄脉冲干扰（脉冲宽度小于 $1tq$ ），CAN节点发送时有一定概率发出非预期报文的情况，例如将数据帧发送成远程帧，将标准帧发送成扩展帧，或数据段出现错误。

- 解决方法:

设置同步跳跃宽度RSAW = BTS2段宽度，以避免出现发出非预期错误的现象。

需要注意的是，在设置RSAW = BTS2后，在CAN总线有大量干扰的情况下，CAN总线的通信效率会降低。

```

static void can_configuration(void)

{

...

/* can baudrate, set baudrate = pclk/(baudrate_div * (3 + bts1_size + bts2_size)) */

can_baudrate_struct.baudrate_div = 10;

can_baudrate_struct.rsa_size = CAN_RSAW_3TQ;

can_baudrate_struct.bts1_size = CAN_BTS1_8TQ;

can_baudrate_struct.bts2_size = CAN_BTS2_3TQ;

...

}

```

- 改版记录:

已于硅版本D修正。

### 1.2.4 CAN 总线在人为或异常断开后执行邮箱的取消发送命令无效

- 问题描述:

CAN作为报文发送节点，若同时满足如下条件，则在CAN错误被动中断内执行邮箱的取消发送命令将会无效，使得断开CAN总线时刻邮箱内的待发报文的发送并未被实际取消，其会在等待后续CAN总线恢复后重新发送出来。

1. 人为或异常断开CAN总线（CANH/L）

2. 自动重传功能有开启

- 解决方法:

使能CAN的错误被动中断，在其中断函数内关闭自动重传，并在报文发送函数内重新开启自动重传。代码实现如下

- 1) 在CAN的初始化时使能错误被动中断

```

nvic_irq_enable(CAN1_SE_IRQn, 0x00, 0x00);

can_interrupt_enable(CAN1, CAN_EPIEN_INT, TRUE);

can_interrupt_enable(CAN1, CAN_EOIEN_INT, TRUE);

```

- 2) 在CAN的错误被动中断内关闭自动重传功能

```

void CAN1_SE_IRQHandler(void)

{

if(can_flag_get(CAN1,CAN_EPF_FLAG) != RESET)

{

CAN1->mctrl |= (uint32_t)(1<<4);

can_flag_clear(CAN1, CAN_EPF_FLAG);

}

}

```

- 3) 在CAN的报文发送函数内重新开启自动重传功能

```

CAN1->mctrl &= (uint32_t)~(1<<4);

```

- 改版记录:

无。

## 1.3 ERTC

### 1.3.1 TAMPER PIN 产生唤醒事件输出的条件

- 问题描述:

在唤醒事件产生后，TAMPER PIN未产生唤醒事件输出。

- 解决方法:

使能唤醒定时器中断（WATIEN = 1），产生唤醒事件后硬件会立即进入中断，在中断处理函数里读取唤醒定时器标志（WATF）并清除该标志，即可产生唤醒事件输出。

- 改版记录:

已于硅版本C修正。

### 1.3.2 TIME 和 DATE 寄存器的值更新条件

- 问题描述:

如果没有操作ERTC寄存器，TIME、DATE寄存器的值不会更新，而是上一次操作寄存器时更新的值。

- 解决方法:

在读取TIME、DATE寄存器时，先读取状态寄存器。

- 改版记录:

无。

### 1.3.3 使用 LEXT 做 ERTC 时钟源时，每次系统复位后时间慢 3~6 个 LEXT 时钟周期

- 问题描述:

使用LEXT做ERTC时钟源时，每次系统复位（如从Standby唤醒、掉电复位、看门狗复位）后，时间慢3~6个LEXT 时钟周期。

- 解决方法:

无。

- 改版记录：

已于硅版本C修正。

## 1.4 GPIO

### 1.4.1 复位期间 PC0~5 下拉电阻异常开启

- 问题描述：

复位期间GPIO应都维持浮空状态，但PC0~5下拉电阻此时异常开启了。

- 解决方法：

无。建议点亮LED灯或驱动外设以高电平使能来设计电路。

- 改版记录：

已于硅版本C修正。

### 1.4.2 FT (5 V 容忍) 引脚浮空输入时维持在中间电平

- 问题描述：

5 V容忍管脚在浮空输入模式时，仍有约小于10  $\mu\text{A}$ 的上拉电流能力，以致管脚可能维持约2.0 V。

- 解决方法：

引脚外部加下拉电阻（150  $\text{k}\Omega$ 或以下）解决。

- 改版记录：

无。

## 1.5 I2S

### 1.5.1 I2S 的 CK 线在受到干扰后，通信就无法再自动恢复正常

- 问题描述：

I2S的CK与WS信号在芯片内部未做同步约束，导致最终实际通讯时clock线上出现干扰时，该干扰将被I2S当做CK信号进行处理，且后续不会自动恢复正常。

- 解决方法：

根据期望的音频协议及I2SCLKPOL配置，对WS及CK脚进行内部或者外部上下拉处理。且如果检测到通信出错时，可通过关闭并重新使能I2S来实现恢复。

- 改版记录：

已于硅版本C修正。

### 1.5.2 I2S 飞利浦协议在特定条件下通讯起始帧数据异常

- 问题描述：

I2S飞利浦协议、主收从发、I2SCLKPOL为High配置条件下，通讯的第一帧数据左声道对应的WS信号下降沿不会被真正输出出来，可能导致有些设备无法接收到该左声道数据。

- 解决方法：

根据期望的音频协议及 I2SCLKPOL 配置，对 WS 及 SCK 脚进行内部或者外部上下拉处理。

- 改版记录：

已于硅版本C修正。

### 1.5.3 I2S PCM 长帧只收模式下接收第一笔数据错位问题

- 问题描述:

当PCLK分频系数大于1, I2S配置PCM长帧标准只收模式, 若配置I2SCPOL = 0, 且在使能I2S前SCK线上异常保持为高电平时, 此时接收到的第一笔数据会出现错位。

- 解决方法:

根据 I2SCLKPOL 配置, 对 SCK 脚进行对应的内部或者外部上下拉处理。

- 改版记录:

无。

### 1.5.4 I2S 从发模式非连续通讯状态下误置位 UDR 标志问题

- 问题描述:

I2S从发模式, 不连续通讯时, 虽在通讯起始前有写入待发数据, 但还是会异常置位UDR标志。

- 解决方法:

结合协议特点, I2S 从发模式建议使用 DMA 或中断等高效的数据传输方式, 保障通讯连续。

- 改版记录:

无。

### 1.5.5 I2S 24 位数据封装成 32 位帧格式接收异常问题

- 问题描述:

I2S在24位数据封装成32位帧格式时, 8个无效CLK对应的数据会被接收方当做正常数据接收。

- 解决方法:

解法一: 收发双方采用相同的 24 位数据封装成 32 位帧格式的方式;

解法二: 采用软件处理, 在此帧格式条件下, 丢弃 8 个无效 CLK 对应的数据。

- 改版记录:

无。

## 1.6 OTG

### 1.6.1 OTG\_FS Device 模式下 VBUS (PA9) 无法释放给其它外设使用

- 问题描述:

当OTG作为Device功能时, PA9必须作为OTG VBUS 输入引脚, 不能再分配给GPIO或其它外设使用, 建议PA9接上拉电阻至VBUS或V<sub>DD</sub>。

- 解决方法:

无

- 改版记录:

已于硅版本C修正。C版可通过配置寄存器OTGFS\_GCCFG的位21 VBUSIG, 以释放给其他外设使用。。

## 1.7 PWC

### 1.7.1 VDD 大于 PVM 阈值时使能 PVM 会误触发一次 PVM 事件

- 问题描述:

当VDD大于PVM阈值时，使能PWC的电压监测功能，会立即产生一次非期望的PVM事件。

- 解决方法：

在PVM初始化期间清除掉该非预期的PVM事件。

- 改版记录：

无。

## 1.7.2 AHB 分频后 DEEPSLEEP 模式无法被唤醒

- 问题描述：

如果将AHB做分频配置后，任何唤醒源唤醒DEEPSLEEP模式都会存在无法唤醒的情况。

- 解决方法：

使用DEEPSLEEP模式时，不能对AHB进行分频。

即进DEEPSLEEP模式前，将AHB分频修改为不分频，唤醒后再按照期望设定AHB的分频。

- 改版记录：

无。

## 1.7.3 Systick 中断误唤醒 DEEPSLEEP

- 问题描述：

若进 DEEPSLEEP 前未关闭 Systick 或 Systick 中断时，进 DEEPSLEEP 后 Systick 将保持运行，且随后产生的 Systick 中断会唤醒 DEEPSLEEP。

- 解决方法：

进DEEPSLEEP前关闭Systick或Systick中断。

- 改版记录：

无。

## 1.7.4 进 DEEPSLEEP 过程瞬间被立即唤醒时异常

- 问题描述：

当唤醒源在进DEEPSLEEP模式的过渡状态（约3个LICK时钟周期）出现时，DEEPSLEEP唤醒后有可能会出现漏执行指令问题。

- 解决方法：

DEEPSLEEP 唤醒后，延时 3 个 LICK 时钟周期再执行应用程序（详情请参考文档 FAQ0114）。

- 改版记录：

已于硅版本 C 修正。

## 1.7.5 待机唤醒引脚使能时误置位 SWEF 标志问题

- 问题描述：

当待机唤醒引脚使能前，该引脚被用作GPIO通用推挽输出并输出高或通用上拉输入时，此时在待机唤醒引脚使能会立即误置位SWEF标志。

- 解决方法：

如果之前有使用待机唤醒引脚作为普通 IO，则在使能待机唤醒引脚前将其 IO 重新初始化为下拉输入或模拟输入。参考示例：

```

gpio_init_type gpio_init_struct;

/* enable the button clock */

crm_periph_clock_enable(CRM_GPIOA_PERIPH_CLOCK, TRUE);

/* set default parameter */

gpio_default_para_init(&gpio_init_struct);

/* configure wakeup pin as input with pull-down */

gpio_init_struct.gpio_drive_strength = GPIO_DRIVE_STRENGTH_STRONGER;

gpio_init_struct.gpio_out_type = GPIO_OUTPUT_PUSH_PULL;

gpio_init_struct.gpio_mode = GPIO_MODE_INPUT;

gpio_init_struct.gpio_pins = USER_BUTTON_PIN;

gpio_init_struct.gpio_pull = GPIO_PULL_DOWN;

gpio_init(GPIOA, &gpio_init_struct);

/* enable wakeup pin - pa0 */

pwc_wakeup_pin_enable(PWC_WAKEUP_PIN_1, TRUE);

```

- 改版记录:

无。

## 1.7.6 DEEPSLEEP 过渡状态唤醒后无法立即配置系统时钟

- 问题描述:

若同时满足如下所有条件时，会出现DEEPSLEEP唤醒后的系统时钟配置失败现象（表现为HEXT或PLL的使能命令无法生效）。

条件1：在进DEEPSLEEP的过渡状态唤醒（执行进DEEPSLEEP命令后的3个LICK周期内）

条件2：唤醒后立即配置系统时钟（比如使能HEXT、使能PLL）

- 解决方法:

在DEEPSLEEP唤醒后，先延时等待约3个LICK时钟周期，随后再进行系统时钟的配置。

- 改版记录:

无。

## 1.7.7 使运行和睡眠模式达到更省电的设置方法

- 问题描述:

0x4000\_7050[2]保持默认值0时，电池供电域时钟会保持存在，而该时钟域内外设大部分在V<sub>DD</sub>电源域会造成运行和睡眠模式时较大的耗电。即使电池供电域寄存器没有读、写使用时，这个耗电仍然一直存在。

- 解决方法:

建议软件手动设置寄存器地址0x4000\_7050[2]为1，让硬件自动管理电池供电域时钟，以达到运行和睡眠模式时省电效果。

- 改版记录:

已于硅版本C修正。

## 1.7.8 V<sub>BAT</sub> 供电域寄存器在特定条件时上电复位失败

- 问题描述:

在同时满足如下条件时，V<sub>BAT</sub>供电域寄存器上电复位可能失败，从而导致V<sub>BAT</sub>供电域寄存器内容不确定。

条件1 V<sub>DD</sub>与V<sub>BAT</sub>接在一起

条件2 V<sub>DD</sub>未掉电至0.1V以下，又再次上电

- 解决方法:

判断上电复位标志位（CRM\_CTRLSTS寄存器PORRSTF位），如果PORRSTF位有置起，则先复位VBAT域(CRM\_BPDC寄存器BPDRST位先写1，再写0)，然后重新初始化VBAT域寄存器，最后清零PORRSTF位。

- 改版记录:

无。

## 1.7.9 V<sub>BAT</sub> 和 V<sub>DD</sub> 同时上电且上电速度慢于 3ms/V 可能引起 LEXT 不起振

- 问题描述:

在同时满足如下条件时，LEXT使能后可能不会起振。

条件1 V<sub>DD</sub>与V<sub>BAT</sub>接在一起或两者上电速度同步

条件2 上电速度慢于3ms/V

- 解决方法:

打开PVM功能，通过PVM判断电源电压是否高于2.6V；等电源电压高于2.6V后，判断上电复位标志位（CRM\_CTRLSTS寄存器PORRSTF位），如果PORRSTF位有置起，则执行一次系统复位，最后清零PORRSTF位。可在时钟初始化之前执行以下参考代码：

```

int main(void)

{

crm_periph_clock_enable(CRM_PWC_PERIPH_CLOCK, TRUE);

pwc_pvm_level_select(PWC_PVM_VOLTAGE_2V6);

pwc_power_voltage_monitor_enable(TRUE);

while(pwc_flag_get(PWC_PVM_OUTPUT_FLAG)==SET);

if((CRM->ctrlsts_bit.porrstf == SET) && (CRM->ctrlsts_bit.swrstf == RESET))

{

NVIC_SystemReset();

}

crm_flag_clear(CRM_ALL_RESET_FLAG);

.....

system_clock_config();

.....

.....

}

```

- 改版记录:

无。

## 1.8 SPI

### 1.8.1 SPI 已置位的接收数据传输 DMA 请求无法通过读 DT 寄存器清除

- 问题描述:

示例，在使用 SPI 全双工实现分时收发应用中，SPI 发送期间置位的无效数据接收传输的 DMA 请求，将无法通过读 DT 寄存器进行清除。

- 解决方法:

在SPI接收对应的DMA通道处于关闭状态下，使用关闭SPI使能命令替代原读DT寄存器命令，随后再在期望的通讯起始处开启SPI使能。

- 改版记录:

无。

### 1.8.2 SPI 从机硬件 CS 模式下 CS 下降沿不会做重同步

- 问题描述:

SPI 从机硬件 CS 模式下，不会在每个 CS 下降沿进行数据传输的起始 CLK 同步。

- 解决方法:

解法一：严格约束从机CS线，在通讯完毕后及时拉高CS；

解法二：开启CRC校验，当检测到CRC校验错误时，复位SPI并重新进行握手通讯。

- 改版记录:

无。

## 1.9 TMR

### 1.9.1 外部时钟模式 B 加挂起模式条件下挂起模式失效

- 问题描述：外部时钟模式B下，配置了挂起模式，挂起模式不起作用（无论挂起电平是高电平，还是低电平，Timer都在计数）

- 解决方法：

无。

- 改版记录：

已于硅版本C修正。

### 1.9.2 TMR 产生的 DMA 请求的清除方式

- 问题描述：

TMR无法通过Reset/Set DMA/中断使能寄存器（TMRx\_IDEN）中相应的DMA请求使能位的方式来清除。

- 解决方法：

在开启DMA通道传送前，需复位TMR（即复位TMR的CRM时钟），再初始化配置TMR，确保能清除之前已挂起的DMA请求。

- 改版记录：

已于硅版本C修正。

### 1.9.3 TMR 在编码器模式下的溢出事件

- 问题描述：

在编码器模式计数时，如Counter是在0和PR之间来回计数，此上溢或下溢时TMR的OVFIF事件不会置位。

- 解决方法：

方法1：需占用当前使用编码器TMR的C3IF、C4IF通道为输出模式，设C3DT = AR、C4DT = 0，并使能C3IF、C4IF中断。

在中断中判断“C3IF事件 & 向下计数”，则此时发生了“下溢”；

在中断中判断“C4IF事件 & 向上计数”，则此时发生了“上溢”；

注此解法有限制：如编码器计数的输入信号频率太快，需反复进中断并由软件处理，可能会来不及处理。可应用于编码器的外部输入信号频率不太快的情况。

方法2：换用有增强模式的定时器(Counter能由16bit扩展为32bit的位宽来计数)，以增加编码器检测正反转的计数范围，将Counter的初值设为PR/2，不让定时器产生溢出。

注此解法有限制：编码器计数的正反转，只能在一定范围内去转动，如总往一个方向转也会产生溢出。可应用于编码器检测的正反转是在一定范围内去转动的情况。

- 改版记录：

已于硅版本C修正。

### 1.9.4 TMR用DMA访问0x4C偏移地址可能导致DMA请求异常

- 问题描述：

TMR用DMA访问0x4C偏移地址时，可能导致DMA请求异常。

当使用以下情形之一时，可能出现异常，需采用对应解决方法描述进行处理：

情形1：TMR1发出DMA请求时（未使用TMR DMA BURST功能），当前所属地址总线的低8位地址是0x4C；

情形2：使用TMR自带DMA BURST功能。

- 解决方法：

情形1解法：使用TMR1以外的定时器实现上述功能；

情形2解法：不使用TMR自带DMA BURST功能。

- 改版记录：

已于硅版本C修正。

### 1.9.5 次TMR无法接收由外部触发的主TMR复位的输出信号

- 问题描述：

在同时满足如下配置条件时，次TMR无法接收到复位信号，导致次TMR无法被触发复位。

- 1 主TMR的次模式配置成复位模式，且次模式的触发源为外部信号输入

- 2 当主TMR的输出信号为复位信号同时送给次TMR，次TMR的次模式也配置成复位模式

- 解决方法：

将主TMR的输出信号由复位信号换成溢出信号，即可在主TMR复位时，次定时器也能被触发复位。

- 改版记录：

已于硅版本B修正。

### 1.9.6 未使能定时器时 (**TMREN = 0**), 刹车输入无效

- 问题描述:

未使能定时器时 (**TMREN = 0**), 刹车输入无效, 从而导致刹车输入无法触发刹车事件或中断。

例如: 当使用单周期模式时, 一个周期的计数完成后硬件会自动将**TMREN**清0, 此时刹车输入由于上述原因将被屏蔽, 从而导致输出使能位 (**OEN**) 无法被清零、刹车标志无法置位。

- 解决方法:

无。

- 改版记录:

无。

### 1.9.7 CxORAW 信号清除功能在启用死区时, 输出异常

- 问题描述:

TMR在同时满足如下配置条件时, 互补通道输出会出现周期性死区宽度的脉冲抖动。且满足条件的CxORAW信号清除事件也会滞后到溢出事件时发生。

条件1: 配置为PWM互补输出模式

条件2: 配置为可用外部事件清除CxORAW信号

条件3: 设置有死区时间

条件4: 外部输入为有效电平

- 解决方法:

无。

- 改版记录:

无。

## 1.10 USART

### 1.10.1 USART3 和 TMR1/TMR3 同时使用至 PA7 异常

- 问题描述:

USART3开启了时钟且不remap时, 此时TMR1/3无法使用PA7这个通道.

- 解决方法:

无。

- 改版记录:

已于硅版本C修正。

### 1.10.2 USART 在 IrDA 模式下无法正常接收

- 问题描述:

USART的IrDA模式下, 当USART波特率配置为小于等于38400时, USART无法正常接收到数据。

- 解决方法:

USART 波特率避免配置小于等于 38400。

- 改版记录:

已于硅版本C修正。

### 1.10.3 USART 配置完后立即清除 TDC 位，无法正常发送数据

- 问题描述：

在初始化USART后，立即清TDC flag，然后判断TDC置起，再发送数据，此时数据无法正常发出。

- 解决方法：

按照正常的逻辑来说，不应该软件去清除TDC标志。TDC标志置起，表明数据发送完毕。若将TDC清除的话，只有再发数据后，TDC才能置起，不然TDC标志会一直处于0状态。

- 改版记录：

已于硅版本C修正。

### 1.10.4 USART 仅能透过读取数据寄存器清除 RDBF 标志位

- 问题描述：

普通异步通讯模式下，读数据寄存器非空标志RDBF的清除方式有二，其一为通过对USART\_DT寄存器的读操作清除，另一个为直接对状态寄存器的RDBF Bit写0来清除，B版仅能透过对USART\_DT进行读操作清除。

- 解决方法：

无。

- 改版记录：

已于硅版本C修正。

### 1.10.5 USART 在静默状态下用 DMA 接收仍能收到数据

- 问题描述：

USART在静默状态（地址匹配唤醒模式）下，向RX端发送数据，此时RDBF并未置位，但仍能产生DMA的接收请求且DT数据寄存器也会接收数据，此时静默模式会失效。

- 解决方法：

无。

- 改版记录：

无。

## 1.11 WWDT

### 1.11.1 使用 WWDT 中断时，无法清除 RLDF 标志

- 描述：

在使用WWDT的中断时，在进入中断程序中 $CNT = 0x40$ 时无法清除RLDF标志，所以进入中断后需要先进行喂狗操作，再清除RLDF标志。

- 解决方法：

在WWDT中断处理函数中，先进行喂狗操作，再清除RLDF标志。

```

Void WWDT_IRQHandler(void)

{

wwdt_counter_set(127);

wwdt_flag_clear();

}

```

- 改版记录：

已于硅版本C修正。

## 1.12 WDT

### 1.12.1 使能 WDT 后立即进入 Standby 模式，会发生复位

- 描述：

使能WDT（WDT\_CMD = 0xFFFF）后立即进入standby模式，会立即发生复位。

- 解决方法：

使能WDT后加入一段延时约几个us，再进入Standby模式。

- 改版记录：

已于硅版本C修正。

### 1.12.2 使能 WDT 后立即进入 deepsleep 模式，WDT 未被成功使能

- 描述：

使能WDT（WDT\_CMD = 0xFFFF）后立即进入deepsleep模式，WDT未被成功使能。

- 解决方法：

使能WDT后加入一段延时约30us，再进入deepsleep模式。

- 改版记录：

已于硅版本C修正。

## 1.13 CRM

### 1.13.1 进入 DEEPSLEEP 模式后 CLKOUT 可能有时钟输出问题

- 描述：

当DEEPSLEEP\_DEBUG位设置为0,CLKOUT配置输出系统时钟，在进入DEEPSLEEP模式后,CLKOUT脚上还会有时钟输出,频率为LICK时钟的频率。

- 解决方法：

在进入DEEPSLEEP模式前，将CLKOUT的时钟输出配置为NOCLK，等退出DEEPSLEEP模式后再配置为输出系统时钟。

- 改版记录：

无。

### 1.13.2 PLL 的倍频系数 2 倍 3 倍可能错误

- 描述:

由于PLL的输出范围的限制，PLL输出时钟应大于等于16 MHz，所以在输入PLL的时钟频率较低时，采用倍频系数2倍或3倍可能出错。

- 解决方法:

尽量避免使用PLL的2倍和3倍倍频系数。

- 改版记录:

无。

## 1.14 I2C

### 1.14.1 在 APB 时钟小于等于 4MHz 时，I2C 做从机无法在 400kHz 的速度下通讯

- 描述:

在APB时钟小于等于4MHz时，I2C做从机无法在400kHz的速度下通讯。

- 解决方法:

APB时钟增加到8MHz或者I2C速度降到100kHz运行。

- 改版记录:

无。

### 1.14.2 I2C 在通信开始前，当总线上出现 BUSERR 时序，会误检测到 BUSERR

- 描述:

I2C同时满足下列条件时，会检测到BUSERR条件，导致不能正常通信

条件1 I2C使能

条件2 通信开始前

条件3 总线上出现BUSERR时序

- 解决方法:

通讯开始前检查BUSERR标志是否置起，如果置起，清除标志后便可正常通讯。

也可以开启错误中断，当BUSERR标志置起后在中断里清除。

- 改版记录:

无。

## 1.15 FLASH

### 1.15.1 SLib 以及 boot memory AP mode 配置要求

- 描述:

为确保配置过程的稳定性和安全性，SLib和boot memory AP mode的配置，不建议使用代码配置。

- 解决方法:

通过烧录工具ICP或ISP进行配置。

- 改版记录：

无。

## 2 产品上硅版本号标示

下图显示了 AT32F415 芯片上硅版本号标示的位置，标出的部分是 R (Revision Code) 的第 1 码。例如，'B' 表示该芯片硬件版本为硅版本 B。

图 1. 丝印标记(封装俯视图)

### 3 版本历史

表 4. 文档版本历史

| 日期         | 版本     | 变更                                                                                                                                                       |

|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2021.11.22 | 2.0.0  | 最初版本                                                                                                                                                     |

| 2022.01.20 | 2.0.1  | 增加进入DEEPSLEEP模式后CLKOUT可能有时钟输出问题章节<br>“BPR”部分内容名称统一为“电池供电域”                                                                                               |

| 2022.03.01 | 2.0.2  | 增加CAN的“32位宽标识符掩码模式下无法有效过滤标准帧的RTR位”<br>增加CRM的“PLL的倍频系数2倍3倍可能错误”                                                                                           |

| 2022.04.07 | 2.0.3  | 增加CAN的“在有窄脉冲干扰BS2段的条件下有概率会发送非预期的报文”<br>增加ERTC的“使用LEXT做ERTC时钟源时，每次系统复位后时间慢3~6个LEXT 时钟周期”                                                                  |

| 2022.04.15 | 2.0.4  | 增加“I2S PCM长帧只收模式下接收第一笔数据错位问题”<br>增加“I2S从发模式非连续通讯状态下误置位UDR标志问题”<br>增加“I2S 24位数据封装成32位帧格式接收异常问题”<br>增加“SPI从机硬件CS模式下CS下降沿不会做重同步”                            |

| 2022.04.27 | 2.0.5  | 增加“32位宽标识符掩码模式下无法有效过滤标准帧的RTR位”的解法示例<br>增加“待机唤醒引脚使能时误置位SWEF标志问题”的解法示例<br>增加“1.4.2 FT (5 V容忍) 引脚浮空输入时维持在中间电平”<br>增加“在APB时钟小于等于4MHz时，I2C做从机无法在400kHz的速度下通讯” |

| 2022.06.02 | 2.0.6  | 完善前言中获知版本号的描述                                                                                                                                            |

| 2022.09.06 | 2.0.7  | 增加“I2C在通信开始前，当总线上出现BUSERR时序，会误检测到BUSERR”                                                                                                                 |

| 2022.09.27 | 2.0.8  | 增加“ADC抢占通道组转换结束标志无法清除及置位问题”                                                                                                                              |

| 2023.03.08 | 2.0.9  | 增加“次TMR无法接收由外部触发的主TMR复位的输出信号”                                                                                                                            |

| 2023.08.03 | 2.0.10 | 增加“未使能定时器时 (TMREN = 0)，刹车输入无效”<br>修改“CAN通讯数据域期间出现位填充错误会导致下一帧数据错位问题”描述<br>增加“CAN总线在人为或异常断开后执行邮箱的取消发送命令无效”                                                 |

| 2024.01.31 | 2.0.11 | 增加“CxORAW信号清除功能在启用死区时，输出异常”<br>增加“SLib以及boot memory AP mode配置要求”                                                                                         |

| 2024.05.15 | 2.0.12 | 修改“TMR用DMA访问0x4C偏移地址可能导致DMA请求异常”描述                                                                                                                       |

| 2025.01.09 | 2.0.13 | 修改“DEEPSLEEP过渡状态唤醒后无法立即配置系统时钟”描述<br>修改“CAN通讯数据域期间出现位填充错误会导致下一帧数据错位问题”解法3描述<br>增加“VBAT供电域寄存器在特定条件时上电复位失败”                                                 |

| 2025.04.23 | 2.0.14 | 增加“VBAT和VDD同时上电且上电速度慢于3ms/V可能引起LEXT不起振”                                                                                                                  |

| 2025.04.30 | 2.0.15 | 更新如下芯片局限性的改版记录为：已于硅版本D修正。<br>1.2.1 CAN通讯数据域期间出现位填充错误会导致下一帧数据错位问题<br>1.2.3 CAN在有窄脉冲干扰BS2段的条件下有概率会发送非预期的报文                                                 |

**重要通知 – 请仔细阅读**

买方自行负责对本文所述雅特力产品和服务的选择和使用，雅特力概不承担与选择或使用本文所述雅特力产品和服务相关的任何责任。

无论之前是否有过任何形式的表示，本文档不以任何方式对任何知识产权进行任何明示或默示的授权或许可。如果本文档任何部分涉及任何第三方产品或服务，不应被视为雅特力授权使用此类第三方产品或服务，或许可其中的任何知识产权，或者被视为涉及以任何方式使用任何此类第三方产品或服务或其中任何知识产权的保证。

除非在雅特力的销售条款中另有说明，否则，雅特力对雅特力产品的使用和/或销售不做任何明示或默示的保证，包括但不限于有关适销性、适合特定用途（及其依据任何司法管辖区的法律的对应情况），或侵犯任何专利、版权或其他知识产权的默示保证。

雅特力产品并非设计或专门用于下列用途的产品：(A) 对安全性有特别要求的应用，例如：生命支持、主动植入设备或对产品功能安全有要求的系统；(B) 航空应用；(C) 航天应用或航天环境；(D) 武器，且/或(E) 其他可能导致人身伤害、死亡及财产损害的应用。如果采购商擅自将其用于前述应用，即使采购商向雅特力发出了书面通知，风险及法律责任仍将由采购商单独承担，且采购商应独自负责在前述应用中满足所有法律和法规要求。

经销的雅特力产品如有不同于本文档中提出的声明和/或技术特点的规定，将立即导致雅特力针对本文所述雅特力产品或服务授予的任何保证失效，并且不应以任何形式造成或扩大雅特力的任何责任。

© 2025 雅特力科技 保留所有权利