# nPM2100 Power Management IC

The nPM2100 Power Management IC (PMIC) is designed for primary (non-rechargeable) batteries in an extremely compact form factor. It features an ultra-efficient boost regulator and a wide range of energy-saving features, all of which extend the operating time for non-rechargeable battery applications. nPM2100 provides power regulation for low power microcontroller units (MCU) and System-on-Chip (SoC) devices, like the nRF52, nRF53, and nRF54L Series advanced wireless multiprotocol SoCs from Nordic Semiconductor.

It features one boost regulator that supplies 1.8 V to 3.3 V output, from input voltages of 0.7 V to 3.4 V. Supported batteries include any battery that operates within the input voltage range of nPM2100.

The 150 nA IQ internal boost regulator is among the most efficient boost regulators on the market. A 35 nA Ship mode allows the device to be shipped with batteries inserted without draining the battery. Timed wakeup is available in Hibernate mode for applications that spend most of their time in deep sleep, lowering sleep current to 175 nA and extending battery lifetime by almost triple.

Designed to provide highly efficient power regulation for any primary-cell application, the nPM2100 comes with exceptional software support found in the nRF Connect SDK. The nPM2100 is also suitable for use with other host devices.

The nPM2100 supports precise algorithm-based fuel gauging. Standard voltage-based estimations are often inaccurate, leading to replacing batteries that are still charged, or unexpected shutdown. Instead, nPM2100 uses a voltage and temperature-based fuel gauge running on the host microprocessor for more accurate readings, ensuring full battery utilization with minimal additional load.

## Key features

- Ultra-efficient boost regulator

- Up to 95%

- 1.8 V to 3.3 V output

- 150 mA max

- LDO/Load switch supplied by the boost regulator

- 0.8 V to 3.0 V in LDO mode

- 50 mA max

- 35 nA Ship Mode

- 175 nA Hibernate mode with wakeup timer

- Fuel gauge for primary cell batteries

- 0.7 V to 3.4 V supply voltage

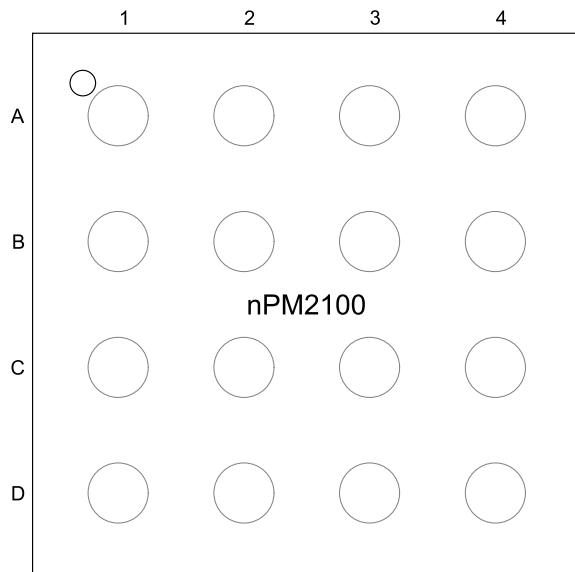

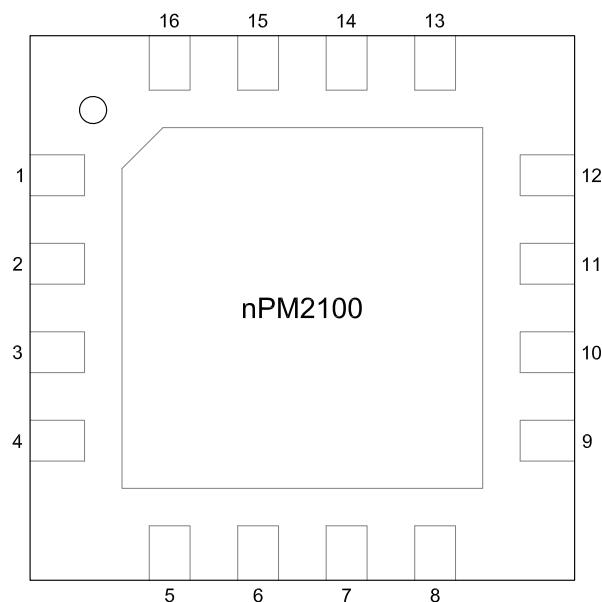

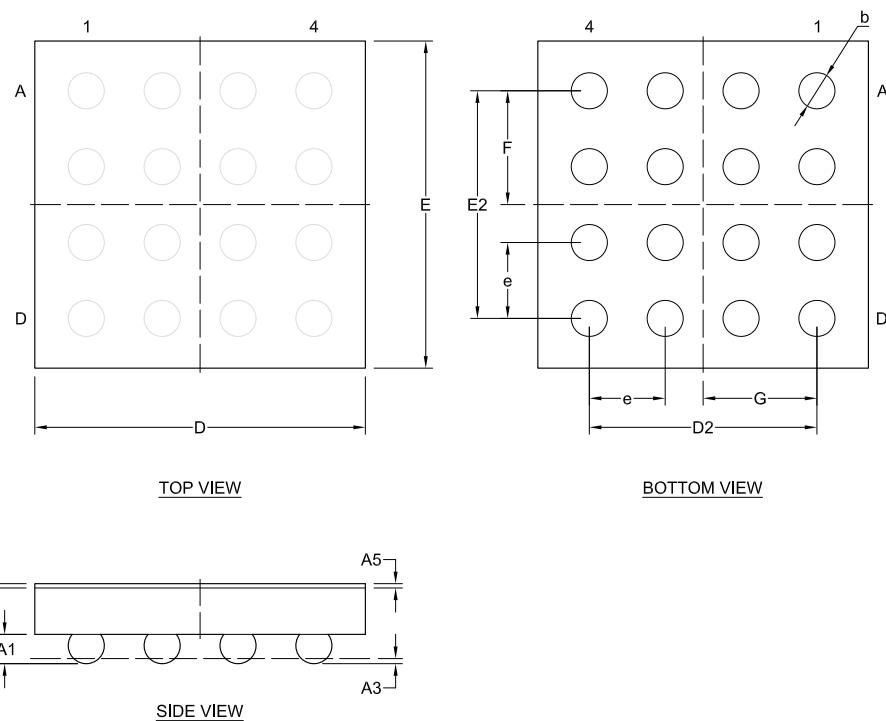

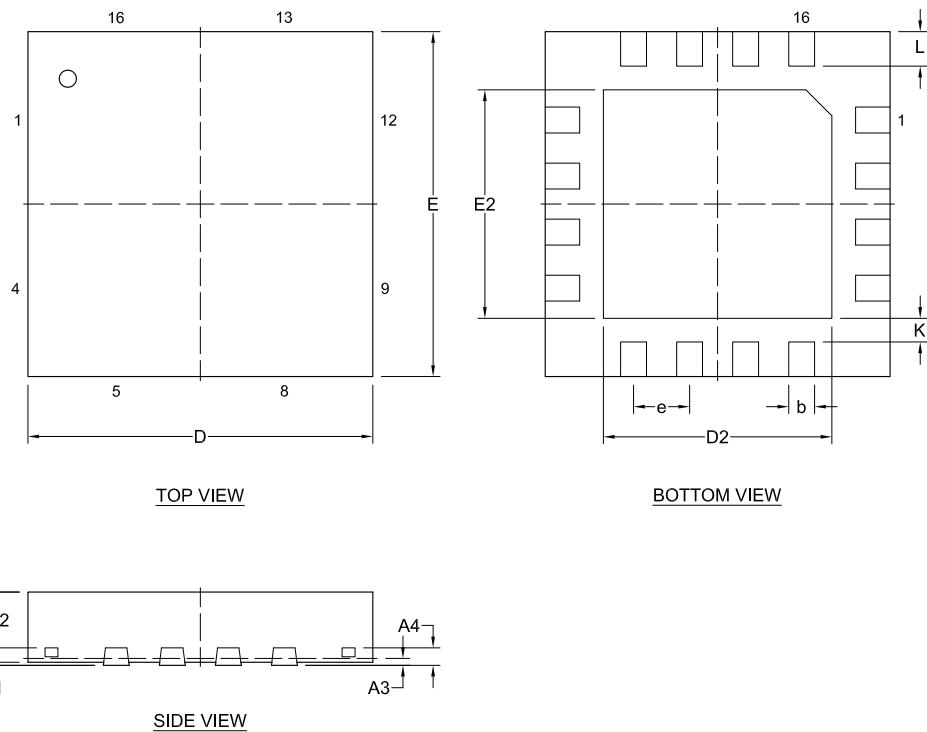

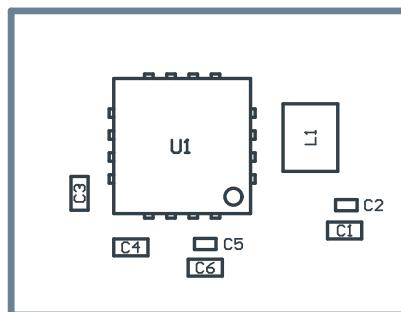

- Multiple package options

- 1.9x1.9 mm WLCSP

- 4.0x4.0 mm QFN16

## Applications

- Computer peripherals/HID

- Remote controls

- Smart home sensors

- Bluetooth® asset tracking

- Fitness accessories

- Personal medical devices

# Key features

## Features:

- Ultra-high efficiency boost regulator

- 0.7 V to 3.4 V input voltage range

- 1.8 V to 3.3 V output voltage range

- Up to 150 mA output current

- Up to 95% efficiency

- Linear voltage regulator/load switch (LDOSW)

- Input connected to boost output

- 0.8 V to 3 V output voltage range

- Up to 50 mA output current

- Ultra-low power Ship mode

- Down to 35 nA current consumption

- Wakeup or enter from a button press

- Wakeup from breaking a connection (break-to-wake)

- Enables the product to be shipped with batteries

- Eliminates pull-tabs and enhances out-of-the-box experience

- Low power fuel gauge and System Monitor

- Battery state-of-charge information when paired with Nordic fuel gauge algorithm running on host MCU

- Multifunction single-button support

- Long-press hard reset

- Ship mode enter/exit

- Power ON/OFF

- User interface

- Two general purpose input/output (GPIO) pins

- Boost and LDO/load switch control

- Interrupt output

- System management features

- Down to 175 nA Hibernate mode with wakeup timer

- Watchdog timer

- Boot monitor

- Power good output

- GPIO pins

- I<sup>2</sup>C compatible two-wire interface (TWI) for control and monitoring

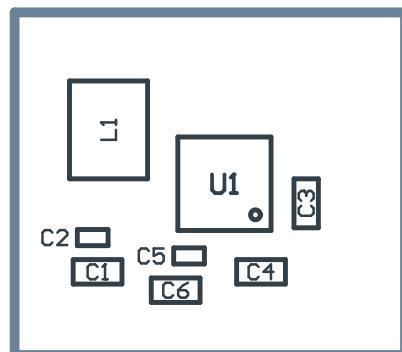

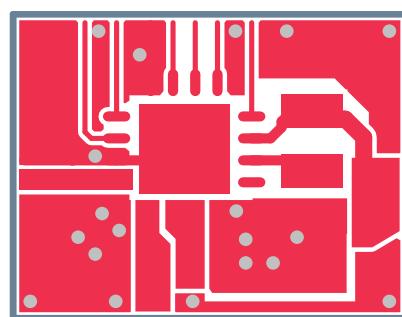

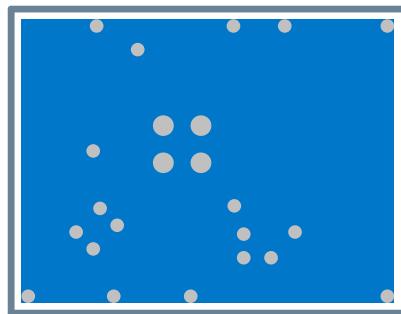

- Low cost BOM and small solution size

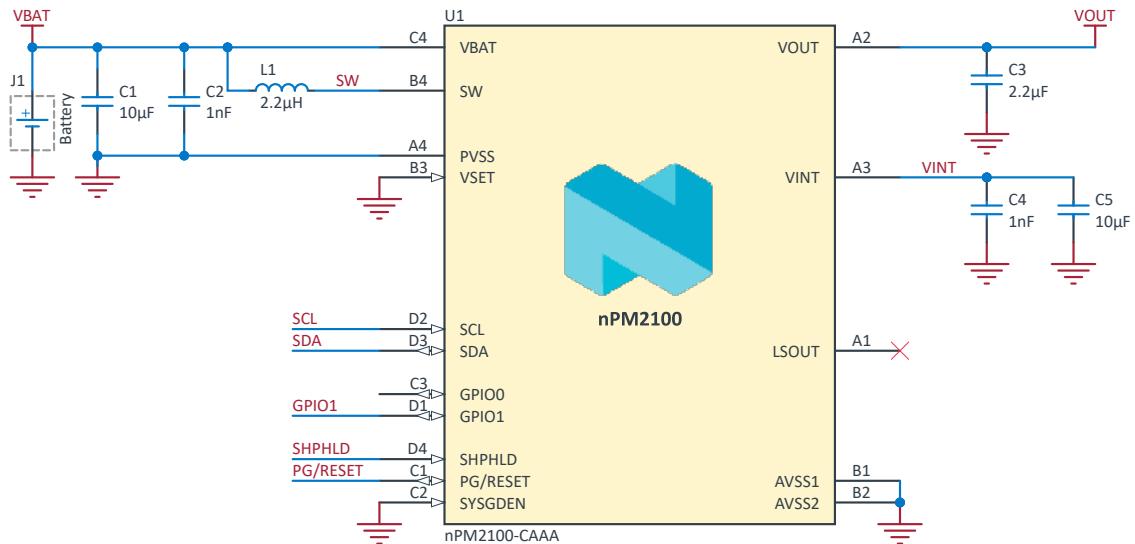

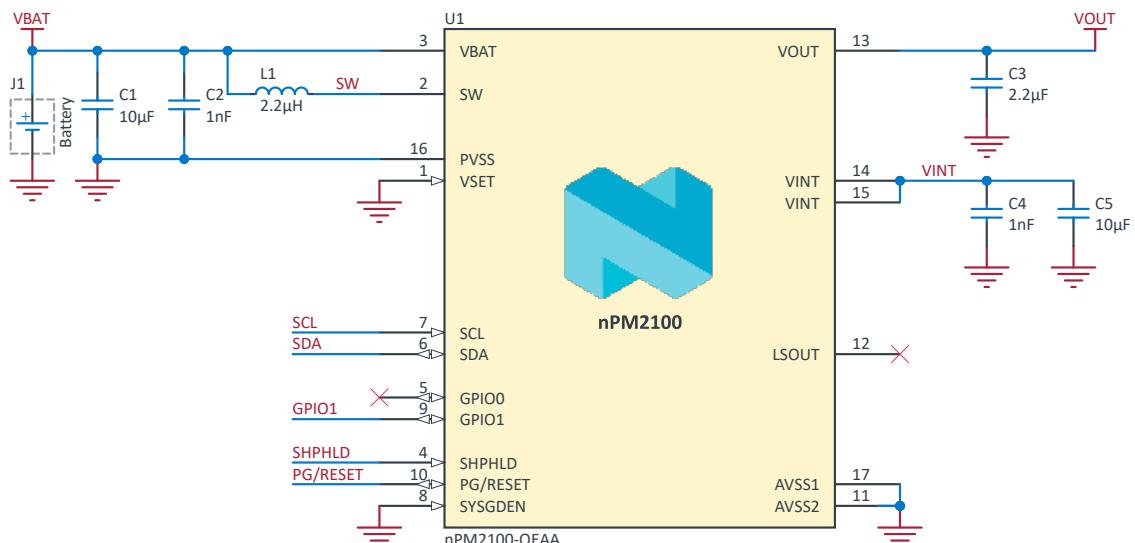

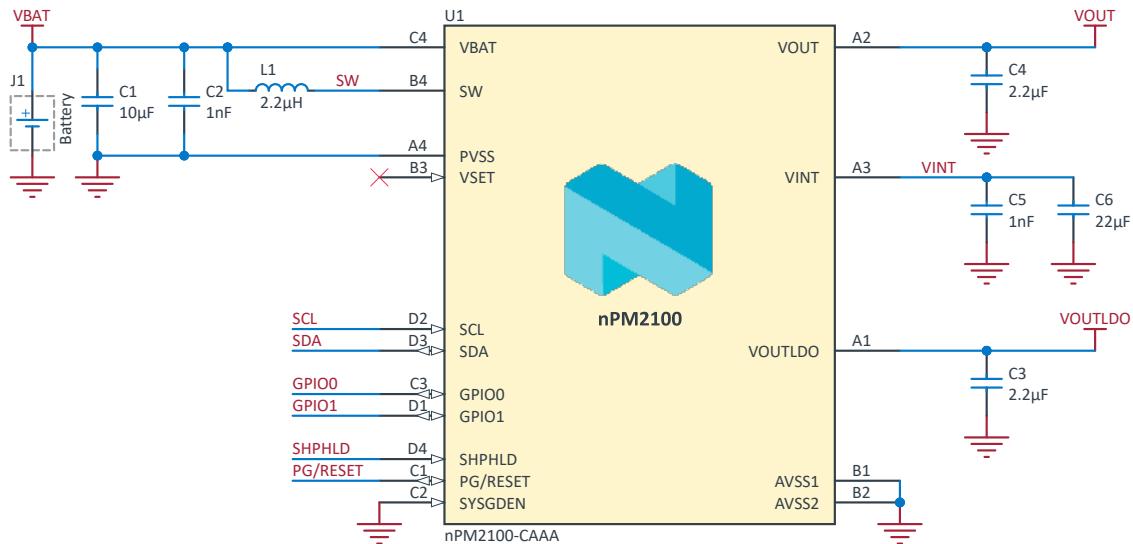

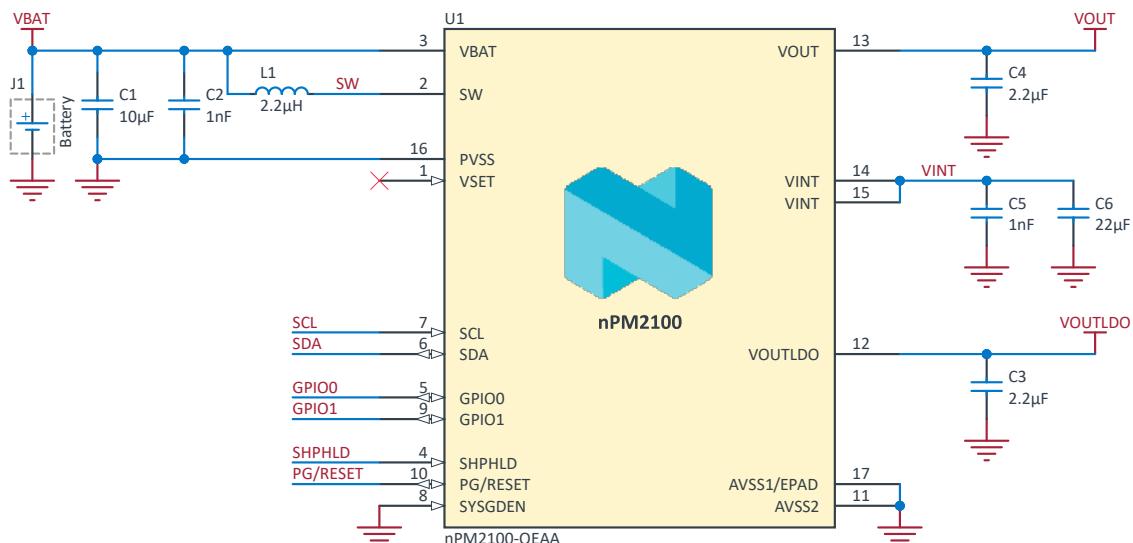

- Small form factor inductor and 5 capacitors

- PCB area from 3.9x3.6 mm

- Package options

- WLCSP 1.9x1.9 mm

- QFN 4.0x4.0 mm

## Applications:

- Computer peripherals/HID

- Remote controls

- Smart home sensors

- *Bluetooth*<sup>®</sup> Low Energy asset tracking

- Fitness accessories

- Personal medical devices

# 1 Revision history

| Date      | Version | Description   |

|-----------|---------|---------------|

| June 2025 | 1.0     | First release |

# 2 About this document

This document is organized into chapters that are based on the modules available in the IC.

## 2.1 Document status

The document status reflects the level of maturity of the document.

| Document name         | Description                                                                                                                                                                                                                                                  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preliminary Datasheet | Applies to document versions up to 1.0.<br>This document contains target specifications for product development.                                                                                                                                             |

| Datasheet             | Applies to document versions 1.0 and higher.<br>This document contains final product specifications. Nordic Semiconductor ASA reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

*Table 1: Defined document names*

## 2.2 Core component chapters

Every core component has a unique capitalized name or an abbreviation of its name, such as BOOST, used for identification and reference. This name is used in chapter headings and references, and it will appear in the C-code header file to identify the component.

The core component instance name, which is different from the core component name, is constructed using the core component name followed by a numbered postfix, starting with 0. For example, BOOST0. A postfix is normally only used if a core component can be instantiated more than once. The core component instance name is also used in the C-code header file to identify the core component instance.

The chapters describing core components may include the following information:

- A detailed functional description of the core component

- Register configuration for the core component

- Electrical specification tables, containing performance data which apply for the operating conditions described in [Recommended operating conditions](#) on page 13

# 3 Product overview

nPM2100 is an integrated Power Management IC (PMIC) designed for primary (non-rechargeable) batteries in an extremely compact form factor. It features an ultra-efficient boost regulator and a wide range of energy-saving features, extending the operating time for non-rechargeable battery applications.

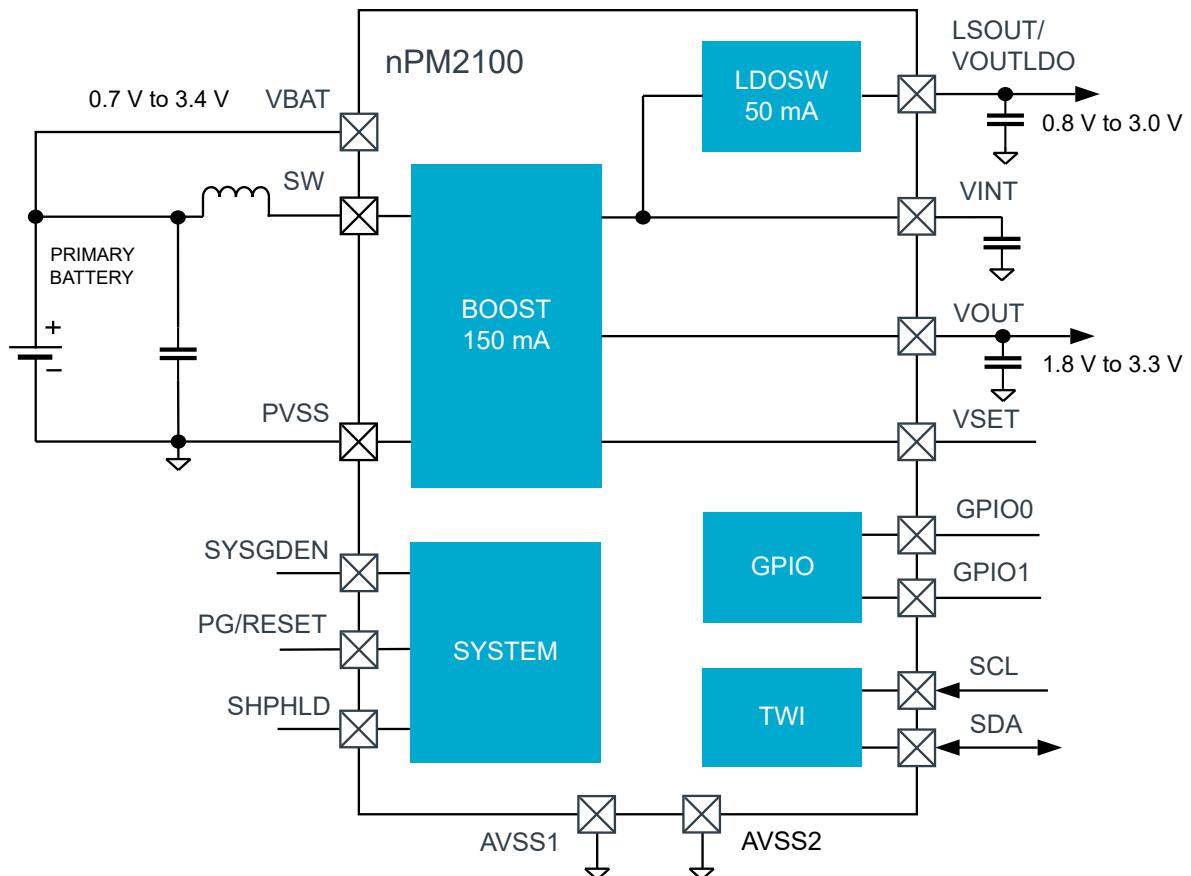

nPM2100 provides power regulation for low-power microcontroller units (MCU) and System-on-Chip (SoC) devices, like the nRF52, nRF53, and nRF54 Series advanced wireless multiprotocol SoCs from Nordic Semiconductor. The device is optimized for maximum efficiency and uses an I<sup>2</sup>C compatible two-wire interface (TWI) for configuration. This interface enables easy access to a range of advanced functions, including Ship mode.

The boost regulator provides output voltages in the range of 1.8 V to 3.3 V and supports automatic Pass-through mode when the battery voltage exceeds the target output voltage. nPM2100 also includes a load switch/LDO that supports up to 50 mA output current and output voltages in the range of 0.8 V to 3.0 V.

nPM2100 supports battery voltages up to 3.4 V and can run from batteries such as one or two alkaline AA/AAA in series or one CR2032. It is able to start-up from 0.8 V battery voltage and run down to 0.7 V.

nPM2100 measures temperature and battery voltage, supporting algorithm-based fuel gauging. This is a unique feature in primary batteries for monitoring the state-of-charge in a non-rechargeable battery more accurately and eliminates unnecessary battery replacements.

Products can be shipped with the battery installed when using Ship mode. Ship mode supports sleep current down to 35 nA with multiple wakeup options, including a break-to-wake function that wakes a product from Ship mode when an electrical connection is broken. Hibernation mode uses an ultra-low power wakeup timer that enables timed wakeups. It provides lower power consumption than an SoC or MCU power-down.

The PMIC also features two GPIO pins that can control time-critical functions as an alternative to serial communication.

Application examples for nPM2100 include computer peripherals/HID, remote controls, smart home sensors, Bluetooth Low Energy asset tracking, fitness accessories and personal medical devices.

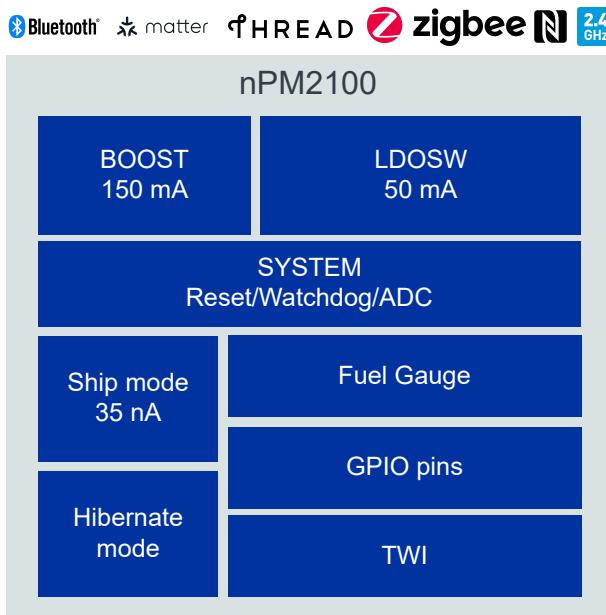

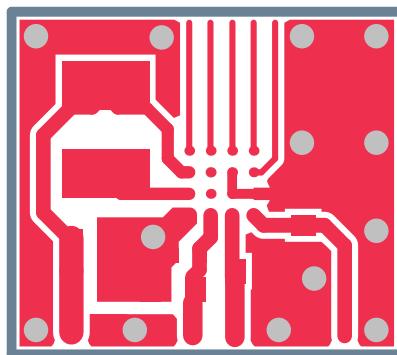

## 3.1 Block diagram

The block diagram illustrates the overall system.

Figure 1: Block diagram

### 3.1.1 In-circuit configurations

The device is configurable for different applications and battery characteristics through input pins. The following pins must be configured before a power-on reset.

| Pin            | Function                                                                                                                             | Reference           |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| <b>VSET</b>    | BOOST output voltage selection<br>VOUT=3.0 V when the pin is not connected<br>VOUT=1.8 V when the pin is grounded                    | <b>BOOST</b>        |

| <b>SYSGDEN</b> | Boot monitor (timer) control<br>Boot monitor enabled when the pin is not connected<br>Boot monitor disabled when the pin is grounded | <b>Boot monitor</b> |

Table 2: In-circuit configurations

## 3.2 System description

The device has the following core components that are described in detail in their respective chapters.

- **BOOST** — Boost regulator on page 14

- [LDOSW – Linear voltage regulator/load switch](#) on page 39

- [GPIO – General purpose input/output](#) on page 51

- [System Monitor](#) on page 57

- [TIMER — Timer/monitor](#) on page 64

- [TWI — I<sup>2</sup>C compatible two-wire interface](#) on page 80

## 3.3 Power-on reset and brownout reset

VBAT and VINT are the two power domains on the device.

When the following condition is met, a power-on reset (POR) occurs:

- VBAT domain –  $\text{VBAT} > \text{VBAT}_{\text{POR\_RISING}}$

- VINT domain –  $\text{VINT} > \text{VINT}_{\text{POR}}$

When the following condition is met, a brownout reset (BOR) occurs in the VINT domain and the device enters the COLD START state:

- $\text{VINT} < \text{VINT}_{\text{BOR}}$

When the following condition is met, a reset occurs in the VBAT domain and the device enters the NO SUPPLY state:

- $\text{VBAT} < \text{VBAT}_{\text{POR\_FALLING}}$

## 3.4 Device protection

The device includes the following protection:

- Thermal protection

- Overcurrent protection for BOOST

- Short circuit protection for LDOSW

**Note:** External load on the **VINT** pin is not allowed.

### 3.4.1 Thermal protection

If the die temperature exceeds the operating temperature range ( $\text{TSD}_{\text{SD}}$ ), the device enters the COLD START state. When the device cools down, it returns to Active mode.

The die temperature is monitored when the BOOST is in High Power mode.

There is a warning threshold,  $\text{TSD}_{\text{WARN}}$ , that can be set to give an interrupt to the host.

#### 3.4.1.1 Thermal specification

| Symbol                             | Description                              | Min. | Typ. | Max. | Units |

|------------------------------------|------------------------------------------|------|------|------|-------|

| $\text{TSD}_{\text{WARN\_RISING}}$ | Thermal warning limit, rising threshold  | 85   |      | 105  | °C    |

| $\text{TSD}_{\text{SD\_RISING}}$   | Thermal shutdown limit, rising threshold | 110  |      | 125  | °C    |

| $\text{TSD}_{\text{WARN\_HYS}}$    | Thermal warning limit, hysteresis        |      | 10   |      | °C    |

Table 3: Thermal protection electrical specification

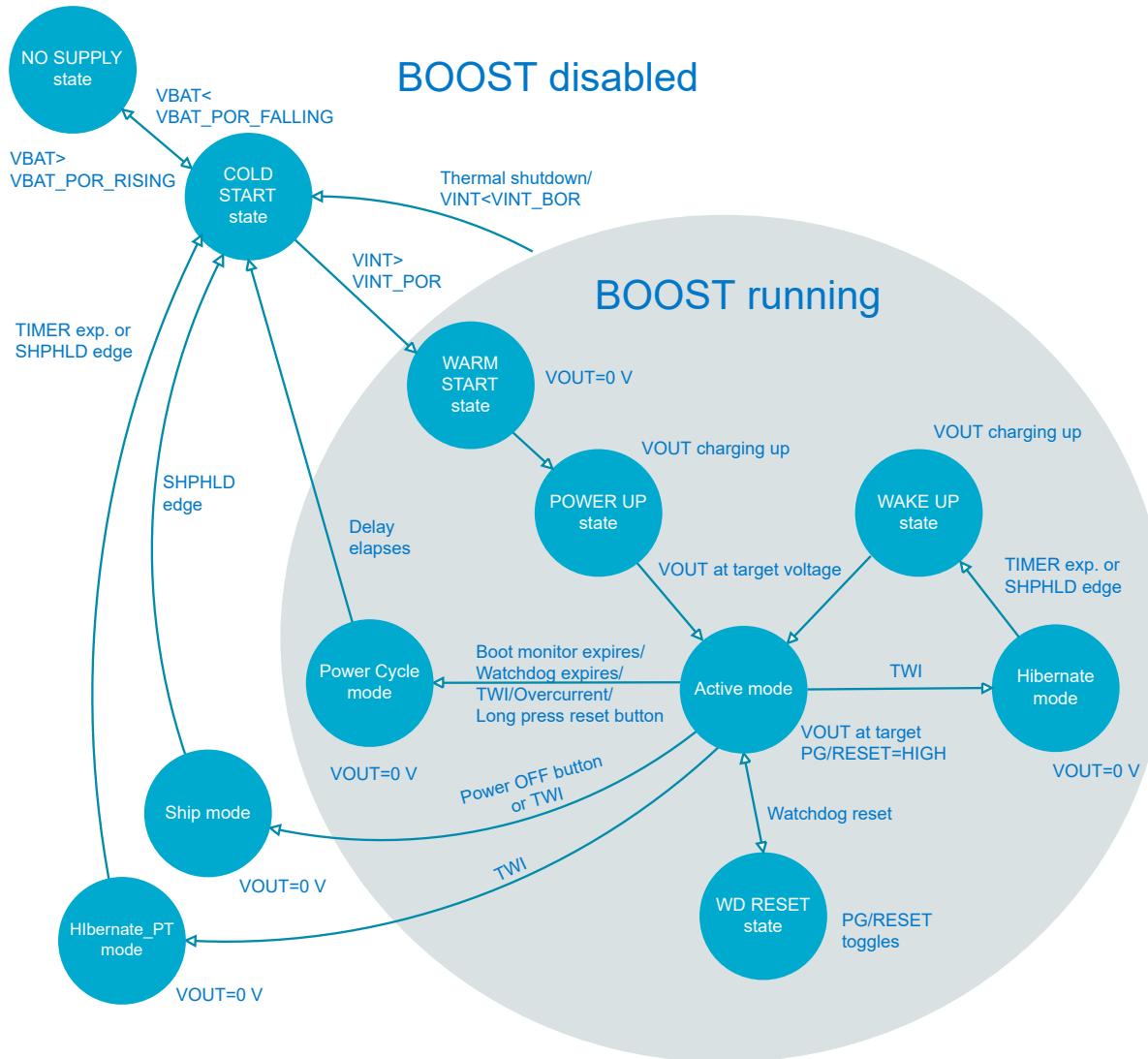

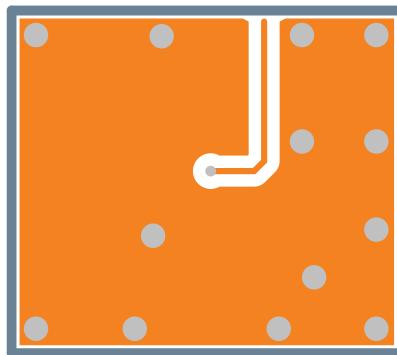

### 3.5 Operational modes and states

The device behavior when in specific operation modes and states is shown in the following diagram.

Figure 2: Operational modes and states diagram

## Active mode

**PG/RESET** is set HIGH unless the Reset button is pulling it LOW.

Ship, Hibernate, and Hibernate\_PT modes can be entered through TWI and register bits.

The chip enters the Ship mode when pressing and holding the **Ship** button for 2 seconds.

A reset is initiated by pressing and holding the **Reset** button for  $t_{RST\_DEB\_L}$  seconds (default 10 s). This forces the device to enter the Power cycle mode. A watchdog reset takes the chip to WD RESET state.

A BOOST overcurrent event sets the chip to the Power cycle mode.

Die temperature rising over  $T_{SD}$  sets the chip to the COLD START state.

## Hibernate mode

**V<sub>OUT</sub>** is discharged to ground. **V<sub>INT</sub>** remains supplied as BOOST is running in Ultra-Low Power mode. LDOSW can be configured to be ON in Ultra-Low Power mode. If enabled, the wakeup timer is running. **PG/RESET** is set **LOW**.

The **SHPHLD** pin and **TIMER** can set the chip to the WAKE UP state.

Please refer to [Hibernate mode](#) for more details.

## Hibernate\_PT mode

**V<sub>OUT</sub>** is discharged to ground. BOOST is in Pass-through mode so that **V<sub>INT</sub>** remains at **V<sub>BAT</sub>** level. LDOSW is OFF. If enabled, the wakeup timer is running. **PG/RESET** is set **LOW**.

A wakeup from the **SHPHLD** pin or **TIMER** causes the chip to enter the COLD START state and resets the registers.

Please refer to [Hibernate mode](#) for more details.

## Ship mode

Everything is disabled and only the **SHPHLD** pin can wake up the chip.

Please refer to [Ship mode](#) for more details.

## Power Cycle mode

BOOST and LDOSW are disabled in Power cycle mode. **V<sub>OUT</sub>** and **LSOUT/V<sub>OUTLDO</sub>** are discharged to ground and **PG/RESET** is set **LOW**. The registers will be reset.

When a delay of **t<sub>PWRDN</sub>** occurs, the chip returns to Active mode.

### 3.5.1 Electrical specification

T<sub>J</sub>=-40°C to 105°C, V<sub>BAT</sub>=0.8 V to 3.4 V and T<sub>J</sub>=25°C, V<sub>BAT</sub>=1.25 V for typical values (unless otherwise noted).

| Symbol                | Description                                                                                                                               | Min. | Typ. | Max. | Units         |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---------------|

| $IQ_{SHIP}$           | Current consumption from battery in Ship mode                                                                                             |      | 35   |      | nA            |

| $IQ_{BREAKTOWAKE}$    | Current consumption from battery in Break-to-wake mode                                                                                    |      | 65   |      | nA            |

| $IQ_{HIB}$            | Current consumption from battery in Hibernate mode with TIMER running (VINT=1.8 V, LDOSW disabled)                                        |      | 320  |      | nA            |

| $IQ_{HIB\_PT}$        | Current consumption from battery in Hibernate Pass-through mode with TIMER running (VBAT=3 V, $T_J=25^\circ\text{C}$ , LDOSW disabled)    |      | 175  |      | nA            |

| $IQ_{ULP}$            | Current consumption from battery when BOOST is running in Ultra-Low Power mode, no load (VOUT=3 V, LDOSW disabled)                        |      | 300  |      | nA            |

| $IQ_{LP}$             | Current consumption from battery when BOOST is running in forced Low Power mode, no load (VOUT=3 V, LDOSW disabled)                       |      | 2.7  |      | $\mu\text{A}$ |

| $IQ_{HP}$             | Current consumption from battery when BOOST is running in forced High Power mode, no load (VOUT=3 V, LDOSW disabled)                      |      | 7.2  |      | mA            |

| $IQ_{PT}$             | Quiescent current, Pass-through mode (no load, OCP disabled)                                                                              |      | 170  |      | nA            |

| $VBAT_{COLD\_START}$  | Battery voltage range, cold start (loaded voltage). The battery needs to be able to provide at least 10 mA (typ.) current during startup. | 0.8  |      | 3.4  | V             |

| $VBAT_{OVR}$          | Battery voltage range, operating (loaded voltage)                                                                                         | 0.7  |      | 3.4  | V             |

| $VBAT_{POR\_RISING}$  | Power-on reset rising threshold                                                                                                           |      | 0.6  |      | V             |

| $VBAT_{POR\_FALLING}$ | Power-down reset falling threshold, VBAT domain                                                                                           |      | 0.5  |      | V             |

| $VINT_{POR}$          | Power-on reset rising, VINT domain                                                                                                        |      | 2.2  |      | V             |

| $VINT_{BOR}$          | Brown-out reset, VINT domain                                                                                                              |      | 1.6  |      | V             |

Table 4: System electrical specification

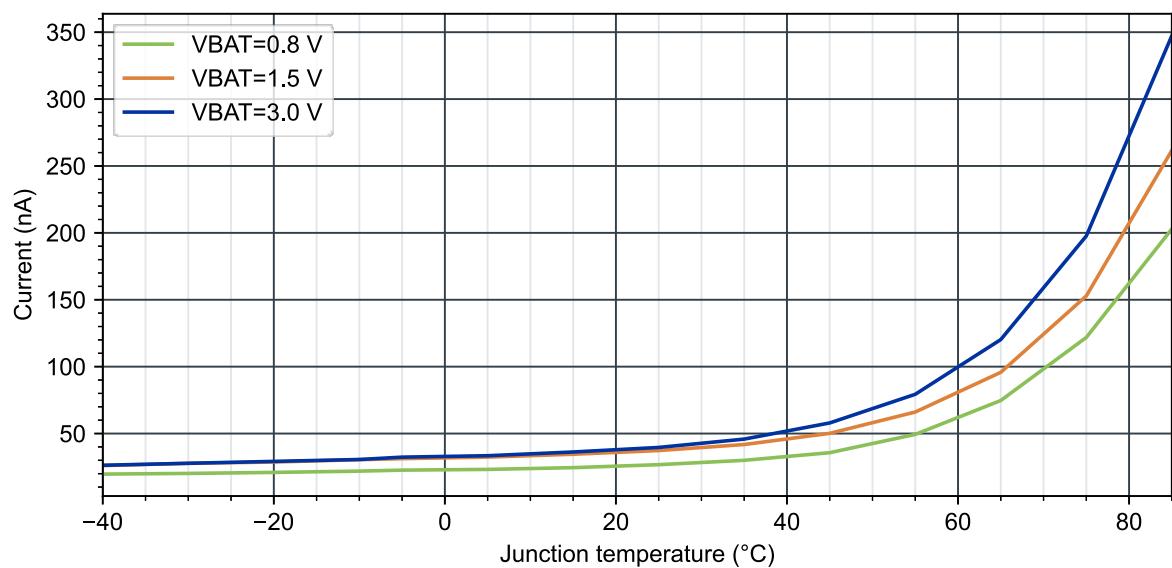

### 3.5.2 Electrical characteristics

The following graph shows typical Ship mode current consumption.

Figure 3: Ship mode current from the battery vs. junction temperature  $T_J$

# 4 Absolute maximum ratings

Maximum ratings are the extreme limits to which the device can be exposed for a limited amount of time without permanently damaging it. Exposure to absolute maximum ratings for prolonged periods of time may affect the reliability of the device.

| Pin                                                    | Notes                            | Min. | Max. | Units |

|--------------------------------------------------------|----------------------------------|------|------|-------|

| <b>VBAT, SW, VOUT, LSOUT/VOUTLDO, VINT</b>             | Power (wrt <b>AVSS1</b> )        | -0.3 | 5.5  | V     |

| <b>SDA, SCL, VSET, PG/RESET, GPIO0, GPIO1, SYSGDEN</b> | Digital pins (wrt <b>AVSS1</b> ) | -0.3 | 5.5  | V     |

| <b>SHPHLD</b>                                          | Analog pins (wrt <b>AVSS1</b> )  | -0.3 | 1.9  | V     |

Table 5: Absolute maximum ratings

|                     | Notes                      | Min. | Max. | Units |

|---------------------|----------------------------|------|------|-------|

| Storage temperature |                            | -40  | +125 | °C    |

| MSL WLCSP           | Moisture sensitivity level |      | 1    |       |

| MSL QFN             | Moisture sensitivity level |      | 2    |       |

| ESD HBM             | Human body model class 2   |      | 2    | kV    |

| ESD CDM             | Charged device model       |      | 500  | V     |

Table 6: Environmental

# 5

# Recommended operating conditions

The operating conditions are the physical parameters that the chip can operate within.

| Parameter                           | Min. | Max. | Units |

|-------------------------------------|------|------|-------|

| Supply voltage V <sub>BAT</sub>     | 0.7  | 3.4  | V     |

| Junction temperature T <sub>J</sub> | -40  | 105  | °C    |

| Ambient temperature T <sub>A</sub>  | -40  | 85   | °C    |

Table 7: Recommended operating conditions

## 5.1 Dissipation ratings

Thermal resistances and thermal characterization parameters as defined by JESD51-7 are shown in the following tables.

| Symbol                | Parameter                                    | Value | Units |

|-----------------------|----------------------------------------------|-------|-------|

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 58    | °C/W  |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 11    | °C/W  |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 26    | °C/W  |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 1.1   | °C/W  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 26.6  | °C/W  |

Table 8: Thermal resistances and characterization parameters, WLCSP

| Symbol                | Parameter                                    | Value | Units |

|-----------------------|----------------------------------------------|-------|-------|

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 40    | °C/W  |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 22    | °C/W  |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 20    | °C/W  |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.75  | °C/W  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 19.9  | °C/W  |

Table 9: Thermal resistances and characterization parameters, QFN

## 5.2 WLCSP light sensitivity

WLCSP package is sensitive to visible and near infrared light, which means that a final product design must shield the chip properly.

# 6 Core components

## 6.1 BOOST — Boost regulator

BOOST consists of a step-up boost regulator with the following features.

- Low voltage startup, even from a battery with high internal resistance

- Flexible and power efficient operating modes

- High Power (HP)

- Low Power (LP)

- Ultra-Low Power (ULP)

- Pass-through (PT)

- Pin selectable initial output voltage 1.8 V and 3.0 V

- Configurable output voltage in 50 mV steps from 1.8 V to 3.3 V

- Overcurrent protection (OCP) for pass-through operation

### 6.1.1 Output voltage selection

The output voltage range for BOOST is programmable with TWI. The default output voltage selection is defined by the **VSET** pin and is effective only at startup. A pin that is not connected configures VOUT to 3 V, and a grounded pin configures VOUT to 1.8 V.

Output voltage can be set in 50 mV steps in register **BOOST.VOUT**. Once the voltage is selected, register **BOOST.VOUTSEL** must be written to for the values to take effect.

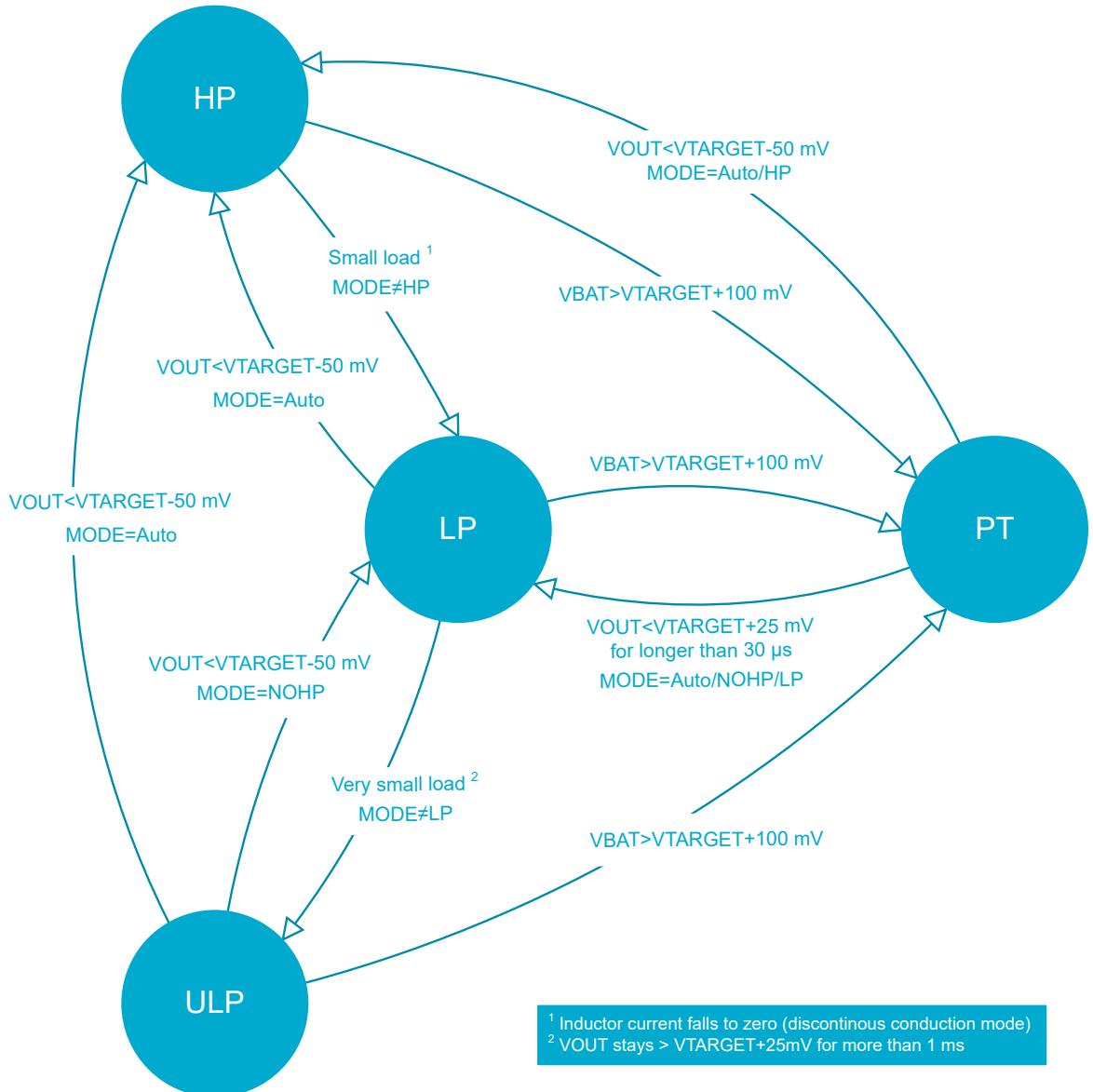

### 6.1.2 Mode selection

BOOST efficiency and quiescent current consumption depend on the operating mode.

In Auto mode, BOOST switches automatically between High Power, Low Power, Ultra-Low Power, and Pass-through modes. In Low Power and Ultra-Low Power modes, the average output voltage of BOOST is 50 mV above the target level.

BOOST can be blocked from entering High Power mode (NOHP). In this case, it will automatically choose between Low Power, Ultra-Low Power, or Pass-through mode.

BOOST enters Pass-through mode when battery voltage is at least 100 mV above the target VOUT.

Exit criteria from Pass-through mode depends on the following settings:

- Auto or High Power – BOOST exits to High Power mode when VOUT drops 50 mV below the target VOUT

- Auto, No High Power or Low Power – BOOST exits to Low Power mode when VOUT falls below target VOUT +25 mV for longer than 30  $\mu$ s

BOOST can be forced to High Power, Low Power, or Pass-through modes through registers **BOOST.GPIO**, **BOOST.PIN**, or **BOOST.OPER**. When forced to High Power or Low Power mode, it can still enter Pass-through mode. When in forced Low Power mode, Ultra-Low Power mode is not available.

**Note:** A GPIO pulled HIGH should request for a lower power mode. For example, GPIO HIGH=Low Power (host sleeping) and GPIO LOW=High Power (host active). This ensures that the host is supplied when a host reset occurs.

Figure 4: BOOST operating modes

### High Power mode

High Power mode has the highest output current capability  $I_{VOUT\_MAX}$  and highest quiescent current  $IQ_{HP}$ .

### Low Power mode

Low Power mode provides less output current but also consumes much less quiescent current  $IQ_{LP}$  compared to High Power mode. See Figure [Load current triggering mode change vs.  \$V\_{OUT}\$](#)  on page 20 for details.

### Ultra-Low Power mode

Ultra-Low Power mode has very low quiescent current consumption  $IQ_{ULP}$ .

## Pass-through mode

Pass-through mode has very low quiescent current consumption  $IQ_{PT}$  and can provide output current up to  $I_{VOUT\_MAX\_PT}$ .

In case Pass-through is a valid operating mode for the application (e.g. a fresh battery has higher voltage than target VOUT), it is strongly recommended to set BOOST in Auto mode. The only additional configuration needed is the setting of the output voltage either by using pin VSET or register BOOST.VOUT. Once battery has been discharged and its voltage falls, BOOST automatically exits the Pass-through mode to regulate the output voltage.

In order to use forced Pass-through mode, BOOST output voltage VOUT has to be first configured to the minimum setting (1.8 V) and only then forced Pass-through mode is to be set in register BOOST.OPER. Forced Pass-through operation continues until the mode is changed by the host, even if battery voltage falls below 1.8 V.

### 6.1.3 Active output capacitor discharge

The **VOUT** pin is discharged to **AVSS1** when the chip enters Ship, Hibernate, Hibernate\_PT, or Power Cycle mode.

### 6.1.4 Electrical specification

Electrical parameters have been measured using a 2.2  $\mu$ H Taiyo Yuden inductor (LSCNB1608HKT2R2MD),  $C_{VBAT}=10 \mu F$ ,  $C_{VINT}=22 \mu F$ ,  $C_{VOUT}=2.2 \mu F$ ,  $T_J=-40^{\circ}C$  to  $105^{\circ}C$ ,  $VBAT=0.8$  V to 3.4 V and  $T_J=25^{\circ}C$ ,  $VBAT=1.25$  V for typical values (unless otherwise noted).

| Symbol                 | Description                                                                                                              | Min. | Typ.                 | Max. | Units   |

|------------------------|--------------------------------------------------------------------------------------------------------------------------|------|----------------------|------|---------|

| $V_{BAT_{START}}$      | Regulator power stage input voltage range, cold start                                                                    | 0.8  |                      | 3.4  | V       |

| $V_{BAT_{OPER}}$       | Regulator core part input voltage range, operating                                                                       | 0.7  |                      | 3.4  | V       |

| $V_{BAT_{PT}}$         | Regulator core part input voltage range, Pass-through mode                                                               | 1.8  |                      | 3.4  | V       |

| $V_{OUT_{PROG}}$       | Programmable output voltage range (except Pass-through mode)                                                             |      | 1.8 to 3.3           |      | V       |

| $V_{OUT_{STEP}}$       | Output voltage step                                                                                                      |      | 50                   |      | mV      |

| $V_{OUT_{LP}}$         | Average $V_{OUT}$ level in Low Power and Ultra-Low Power modes                                                           |      | $V_{OUT.LVL} + 0.05$ |      | V       |

| $V_{OUT_{LP\_RIPPLE}}$ | $V_{OUT}$ ripple in Low Power and Ultra-Low Power modes                                                                  |      | 70                   |      | mVp-p   |

| $I_{VOUT\_MAX\_PT}$    | Maximum output current, Pass-through mode                                                                                |      |                      | 150  | mA      |

| $P_{OUT_{MAX}}$        | Maximum output power, High Power mode ( $3.0 < V_{OUT} \leq 3.3$ V, loaded $V_{BAT} \geq 1.25$ V)                        |      |                      | 450  | mW      |

| $I_{VOUT\_MAX}$        | Maximum output current, High Power mode ( $V_{OUT} \leq 3.0$ V, loaded $V_{BAT} \geq 1.25$ V)                            |      |                      | 150  | mA      |

| $C_{V_{BAT}}$          | Effective input capacitance on $V_{BAT}$ pin                                                                             | 3.5  |                      |      | $\mu F$ |

| $C_{V_{INT}}$          | Effective capacitance on $V_{INT}$ pin                                                                                   | 3.5  |                      |      | $\mu F$ |

| $C_{V_{OUT}}$          | Effective capacitance on $V_{OUT}$ pin                                                                                   | 0.7  |                      | 15   | $\mu F$ |

| $V_{OUT_{ACCURWC}}$    | $V_{OUT}$ accuracy, High Power mode, includes line and load regulation (loaded $V_{BAT} \geq 1.25$ V)                    | -5   |                      | 5    | %       |

| $V_{OUT_{ACCUR}}$      | $V_{OUT}$ accuracy, High Power mode, excluding load and line regulation (loaded $V_{BAT} = 1.25$ V, $T_J = 25^\circ C$ ) | -2   |                      | 2    | %       |

| $F_{BOOST}$            | Switching frequency in High Power mode                                                                                   |      | 2                    |      | MHz     |

| $EFF_{ULP1V5}$         | Efficiency ( $V_{BAT} = 1.5$ V, $V_{OUT} = 1.8$ V, $I_{VOUT} = 0.1$ mA, Ultra-Low Power mode)                            |      | 87                   |      | %       |

| $EFF_{ULP2V9}$         | Efficiency ( $V_{BAT} = 2.9$ V, $V_{OUT} = 3$ V, $I_{VOUT} = 0.1$ mA, Ultra-Low Power mode)                              |      | 91                   |      | %       |

| $EFF_{LP1V5}$          | Efficiency ( $V_{BAT} = 1.5$ V, $V_{OUT} = 1.8$ V, $I_{VOUT} = 10$ mA, Low Power mode)                                   |      | 88                   |      | %       |

| $EFF_{LP2V9}$          | Efficiency ( $V_{BAT} = 2.9$ V, $V_{OUT} = 3$ V, $I_{VOUT} = 10$ mA, Low Power mode)                                     |      | 92                   |      | %       |

| $EFF_{HP1V5}$          | Efficiency ( $V_{BAT} = 1.5$ V, $V_{OUT} = 1.8$ V, $I_{VOUT} = 110$ mA, High Power mode)                                 |      | 88                   |      | %       |

| Symbol                    | Description                                                                   | Min. | Typ.         | Max. | Units |

|---------------------------|-------------------------------------------------------------------------------|------|--------------|------|-------|

| EFF <sub>HP2V9</sub>      | Efficiency (VBAT=2.9 V, VOUT=3 V, I <sub>VOUT</sub> =110 mA, High Power mode) |      | 93           |      | %     |

| ILIM <sub>BOOST</sub>     | Input (valley) current limiter ILIM range, High Power mode                    |      | 100 to 800   |      | mA    |

| ILIM <sub>STEP</sub>      | ILIM step (register setting)                                                  |      | 100          |      | mA    |

| VBAT <sub>MON</sub>       | Input voltage monitoring: VBATMINL and VBATMINH range                         |      | 0.65 to 3.15 |      | V     |

| VBATMIN <sub>STEP</sub>   | Step for VBATMINL and VBATMINH                                                |      | 50           |      | mV    |

| VOUT <sub>MON</sub>       | Threshold range for output voltage monitoring, VOUTMIN and VOUTWRN            |      | 1.7 to 3.25  |      | V     |

| VOUT <sub>STEP SIZE</sub> | Step size for VOUTMIN and VOUTWRN                                             |      | 50           |      | mV    |

| OCP <sub>BOOST_PT</sub>   | Overcurrent protection limit for the PMOS transistor in Pass-through mode     |      | 325          |      | mA    |

Table 10: BOOST electrical specification

### 6.1.5 Electrical characteristics

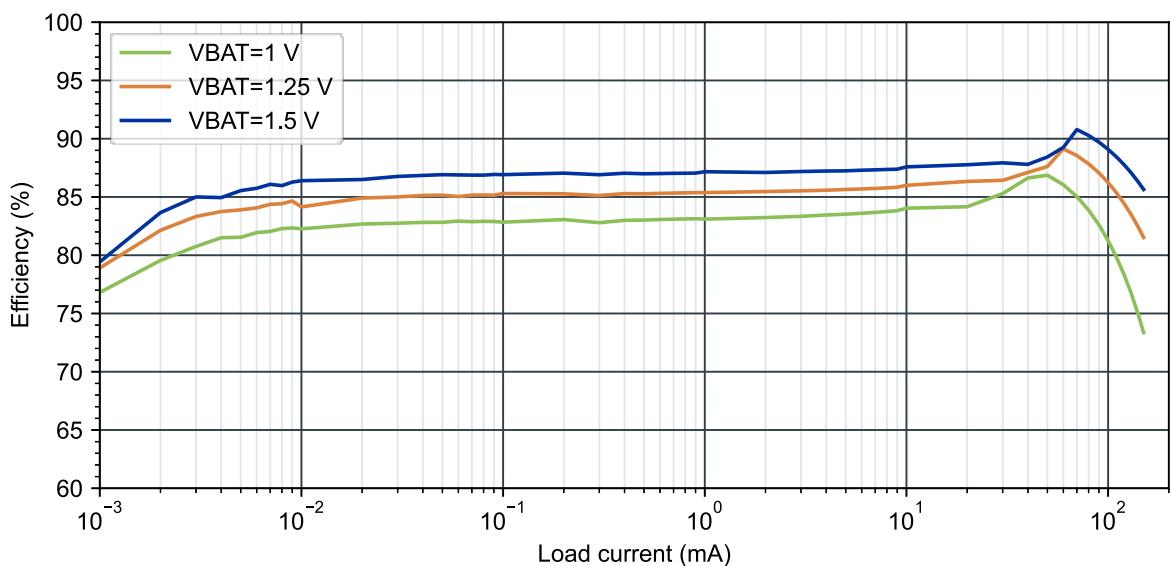

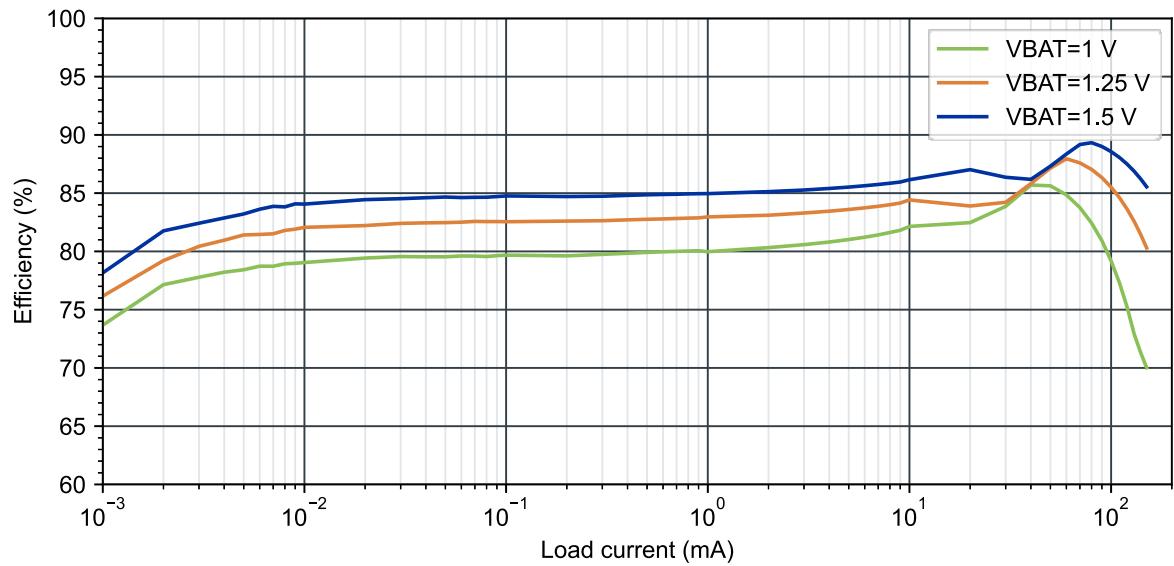

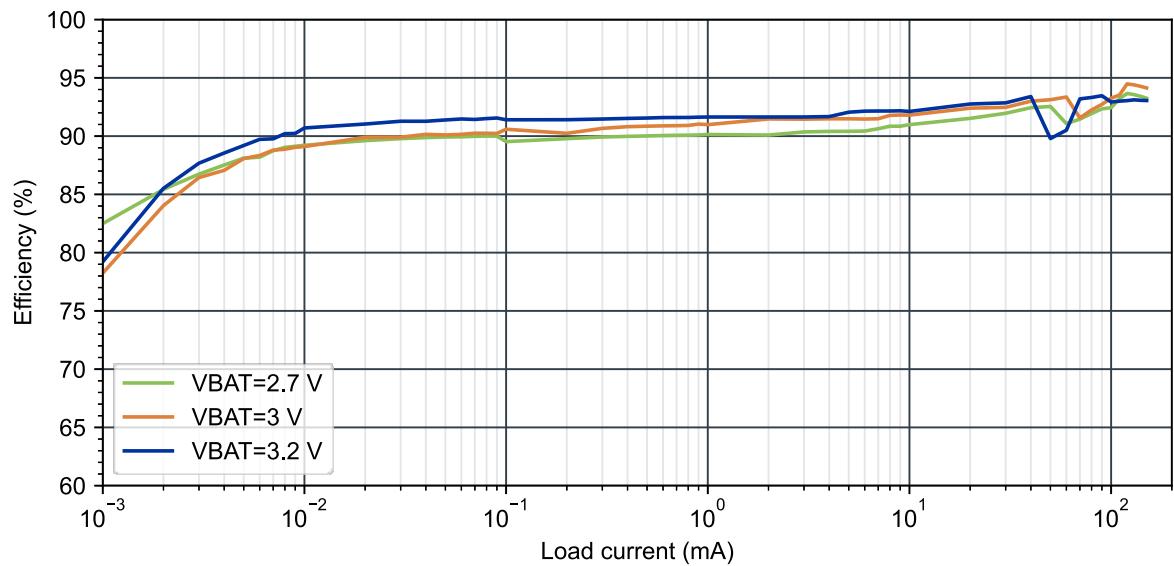

The graphs show typical electrical characteristics for BOOST when supplied by an alkaline AA battery. They have been measured using a 2.2  $\mu$ H Taiyo Yuden inductor (LSCNB1608HKT2R2MD), C<sub>VBAT</sub>=10  $\mu$ F, C<sub>VINT</sub>=22  $\mu$ F, and C<sub>VOUT</sub>=2.2  $\mu$ F, unless mentioned otherwise.

The following three figures show efficiency in Auto mode for various output voltages.

Figure 5: Efficiency, VOUT=1.8 V

Figure 6: Efficiency,  $V_{OUT}=3.3\text{ V}$ Figure 7: Efficiency,  $V_{OUT}=3.3\text{ V}$

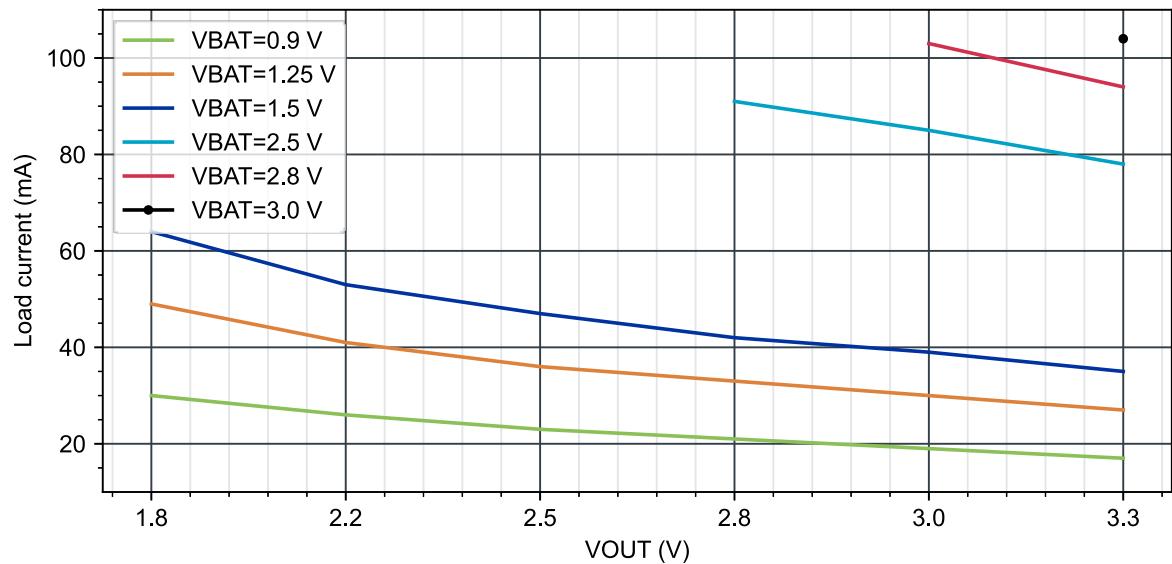

The following figure shows the typical load current threshold in Auto mode where BOOST changes from Low Power to High Power mode.

Figure 8: Load current triggering mode change vs.  $V_{OUT}$

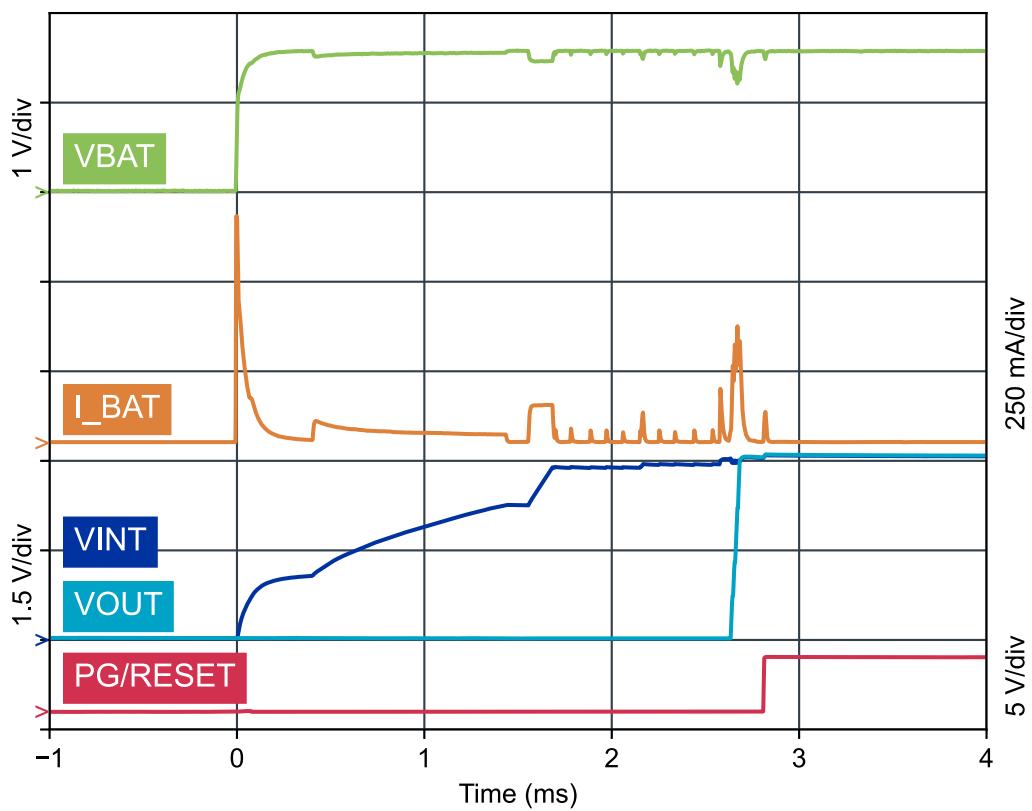

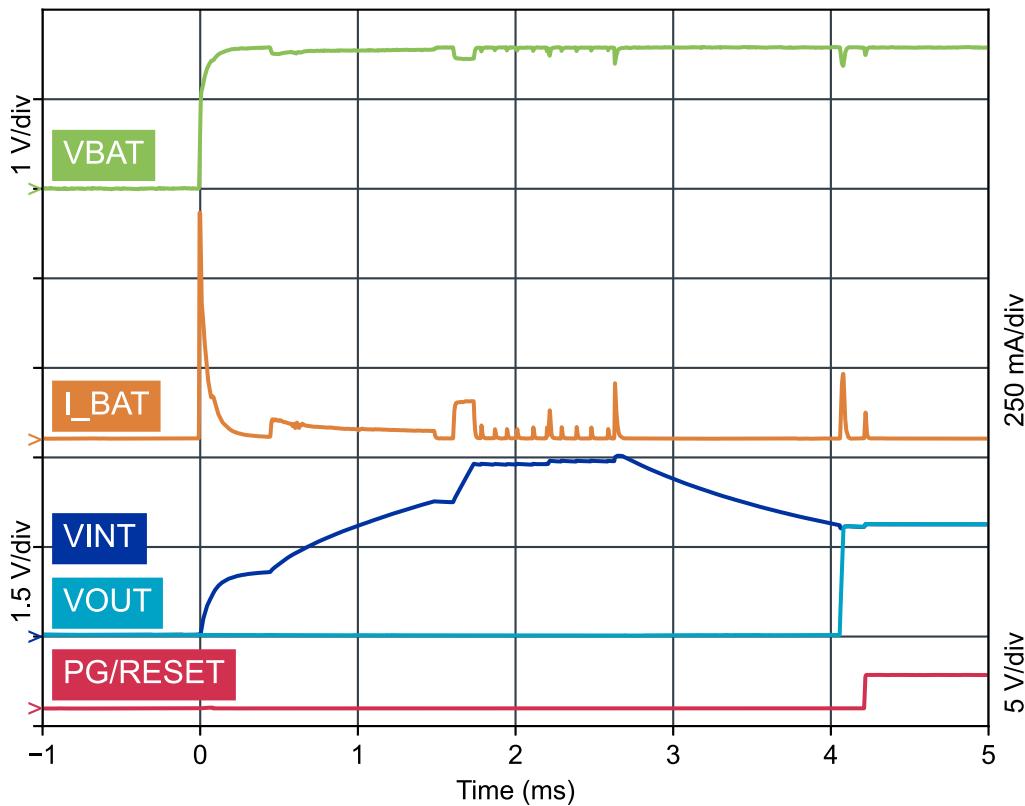

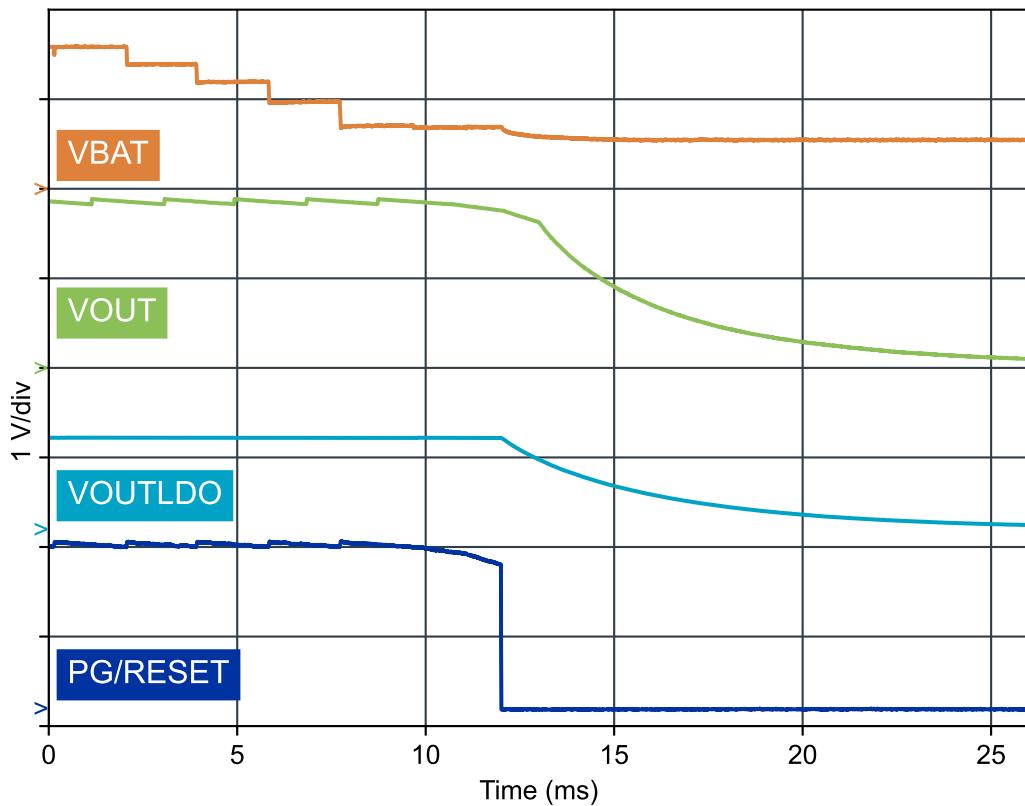

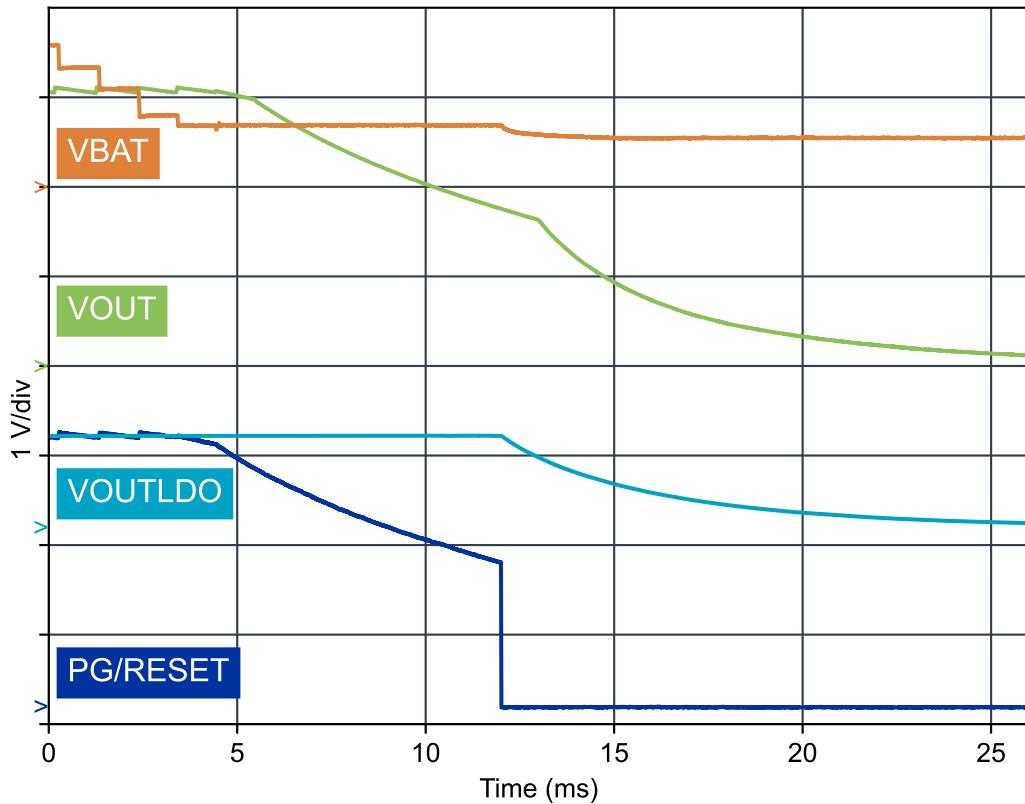

The following two figures show device startup at various  $V_{SET}$  configurations when an alkaline AA battery is inserted.

Figure 9: Battery insertion,  $V_{SET}$  not connected

Figure 10: Battery insertion,  $V_{SET}$  connected to ground

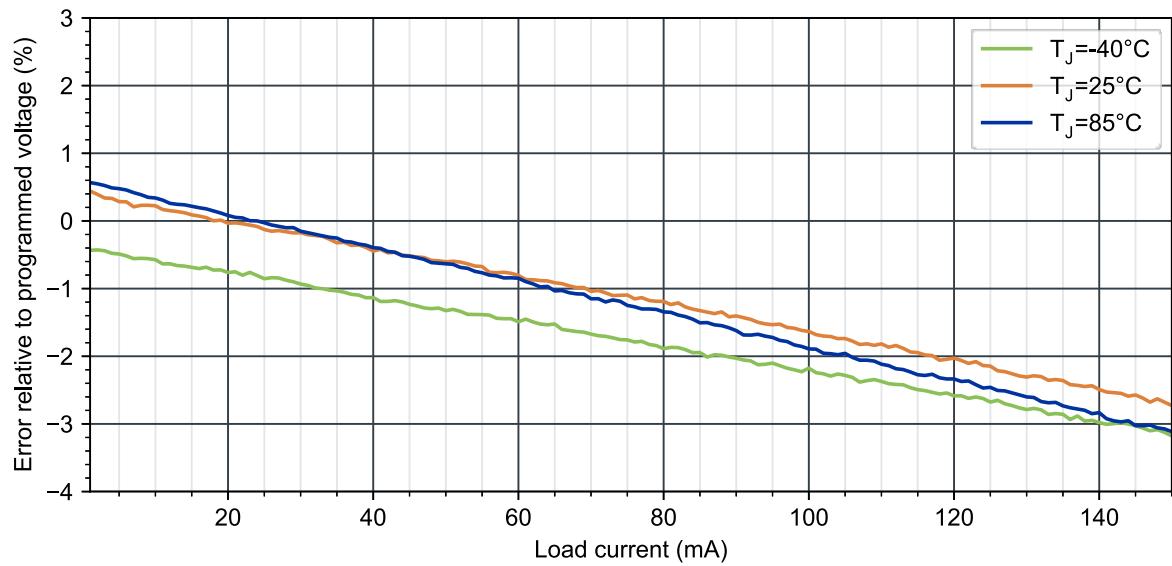

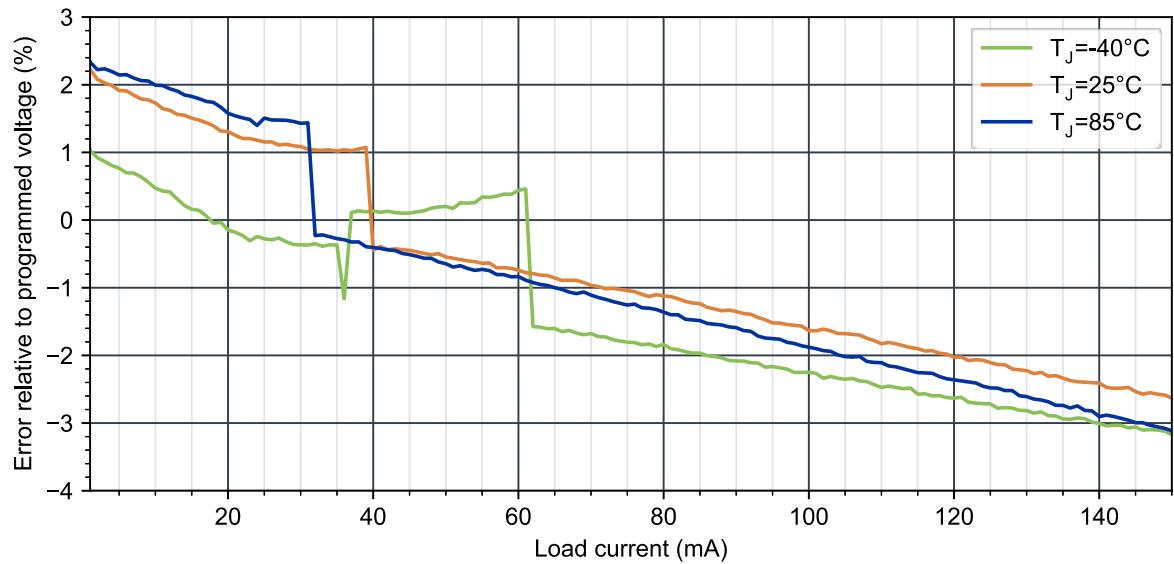

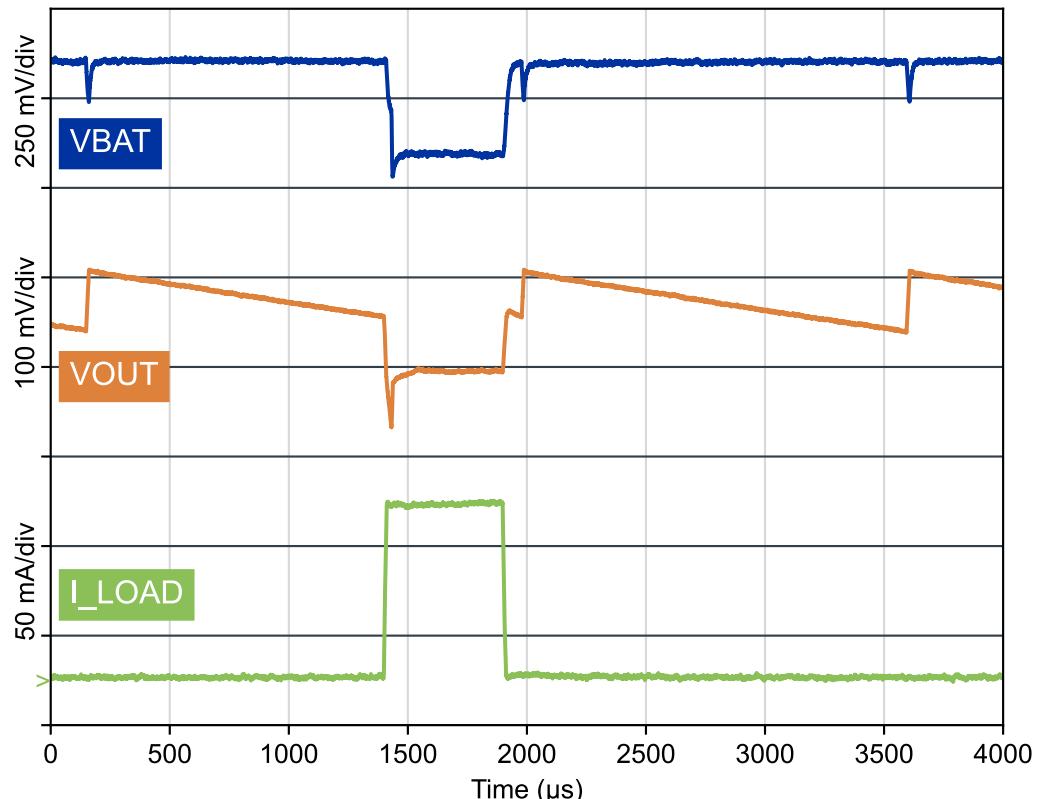

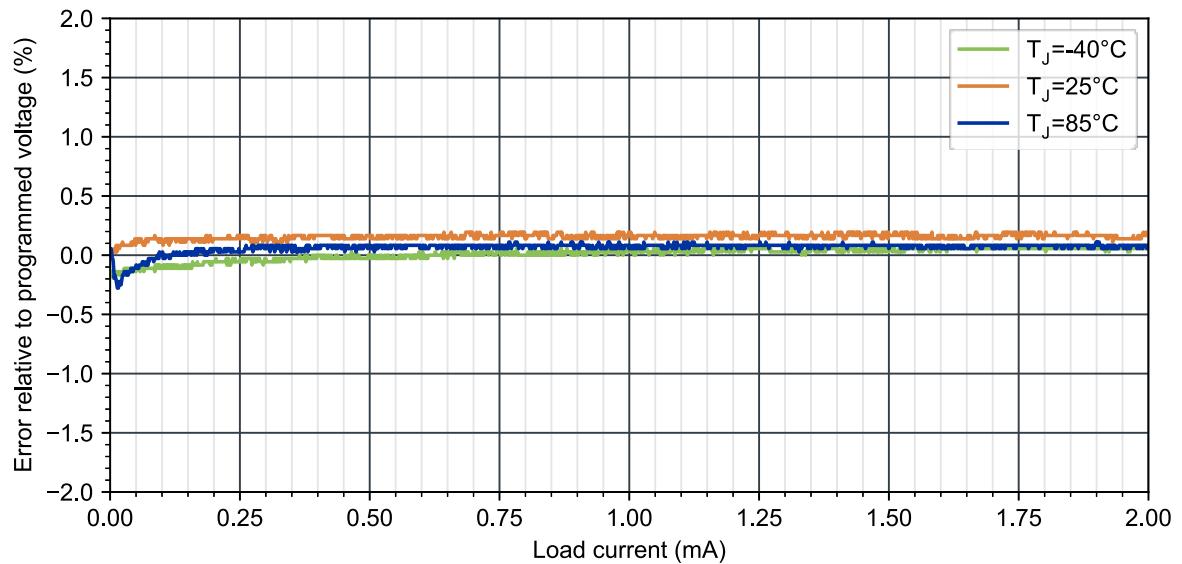

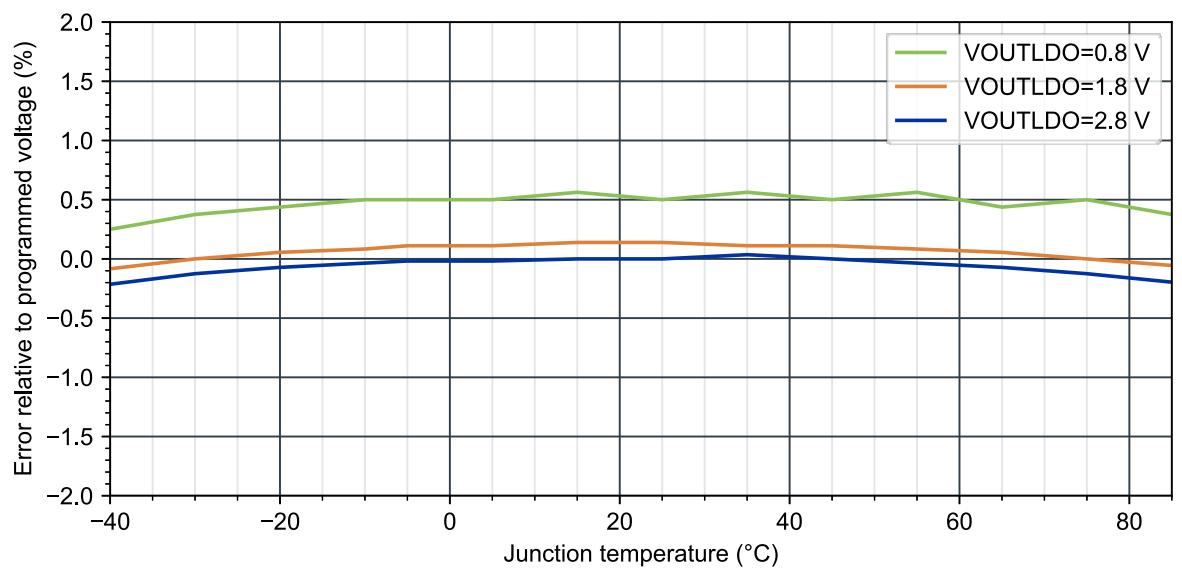

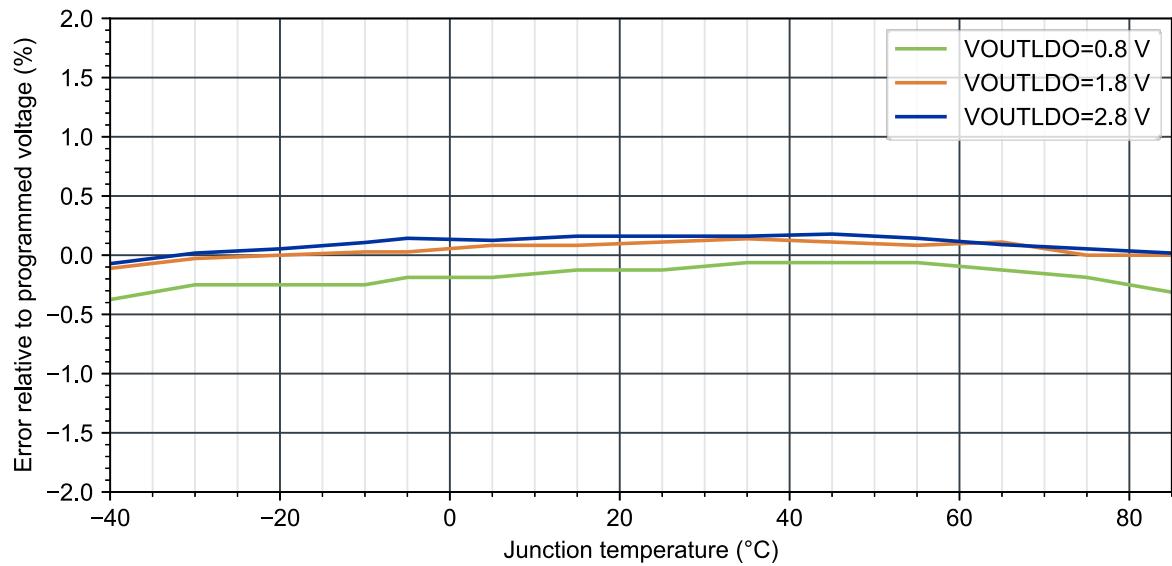

The following two figures show load regulation in High Power mode for various output voltages.

Figure 11: Load regulation,  $V_{OUT}=1.8\text{ V}$  ( $V_{BAT}=1.5\text{ V}$ )

Figure 12: Load regulation,  $V_{OUT}=3.0\text{ V}$  ( $V_{BAT}=2.5\text{ V}$ )

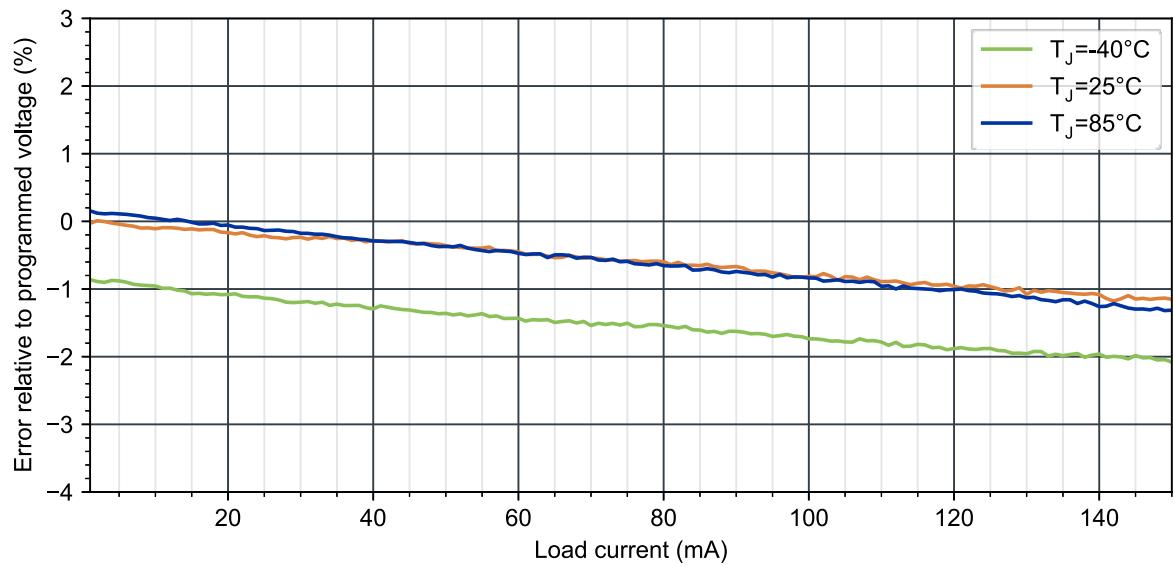

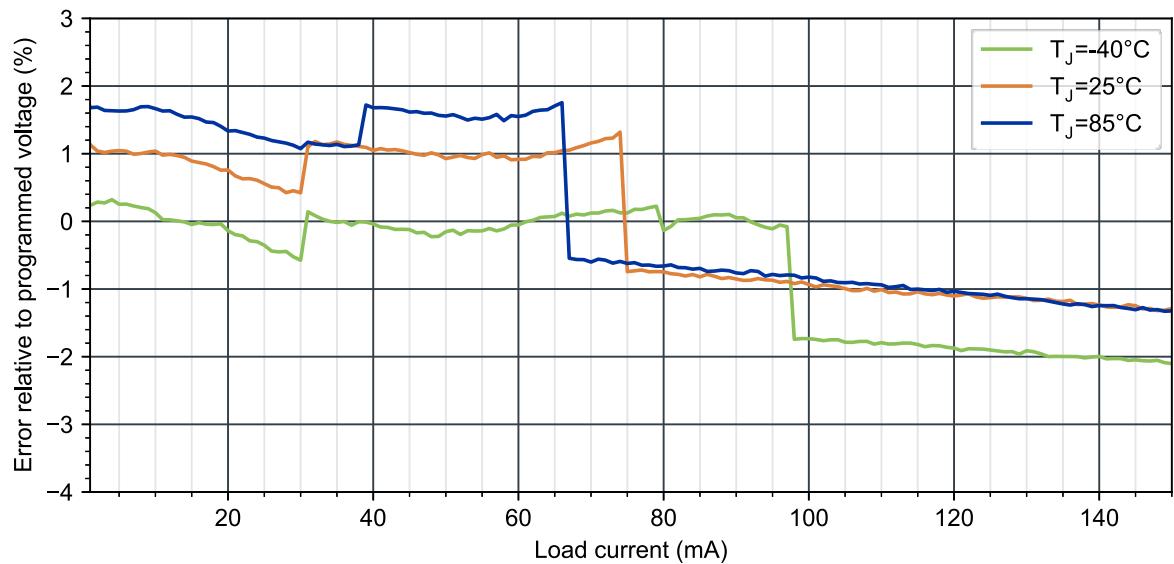

The following two figures show load regulation in Auto mode for various output voltages.

Figure 13: Load regulation,  $V_{OUT}=1.8\text{ V}$  ( $V_{BAT}=1.5\text{ V}$ )

Figure 14: Load regulation,  $V_{OUT}=3.0\text{ V}$  ( $V_{BAT}=2.5\text{ V}$ )

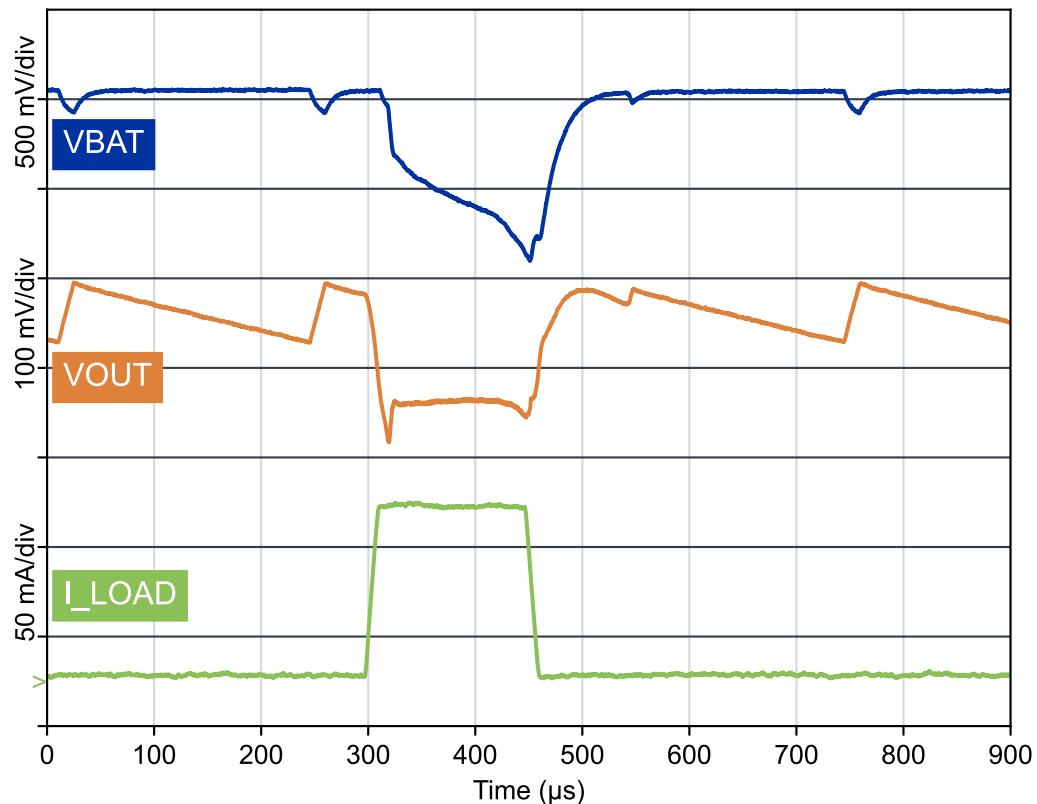

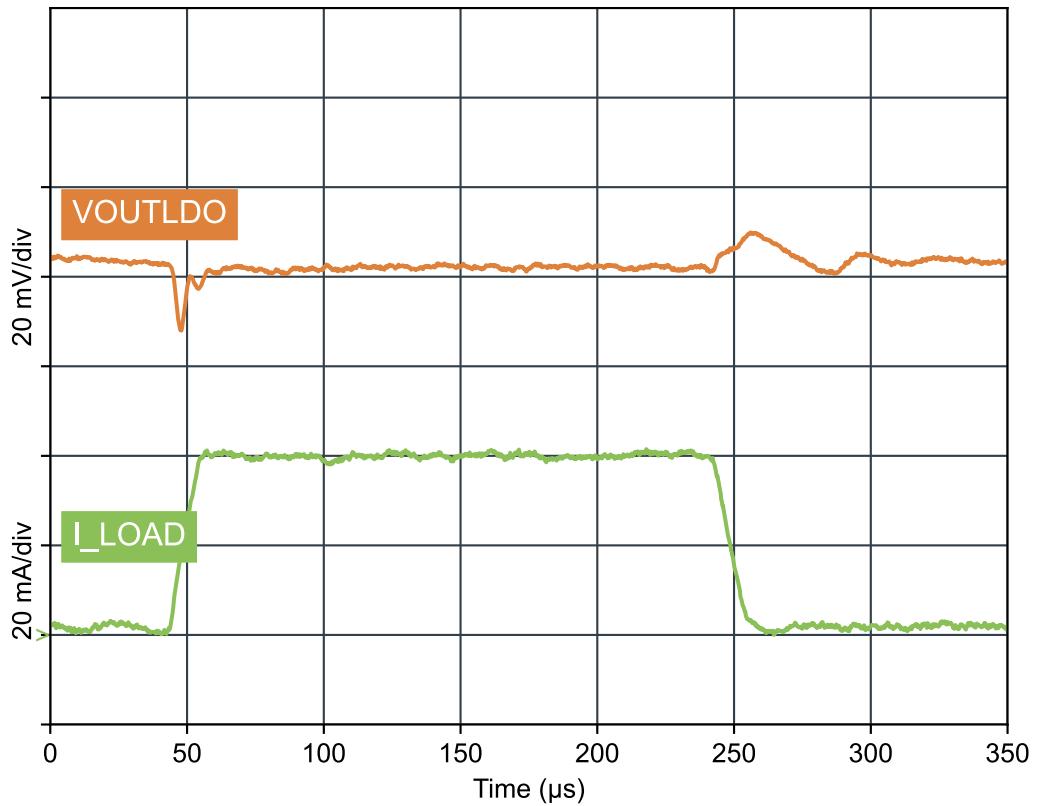

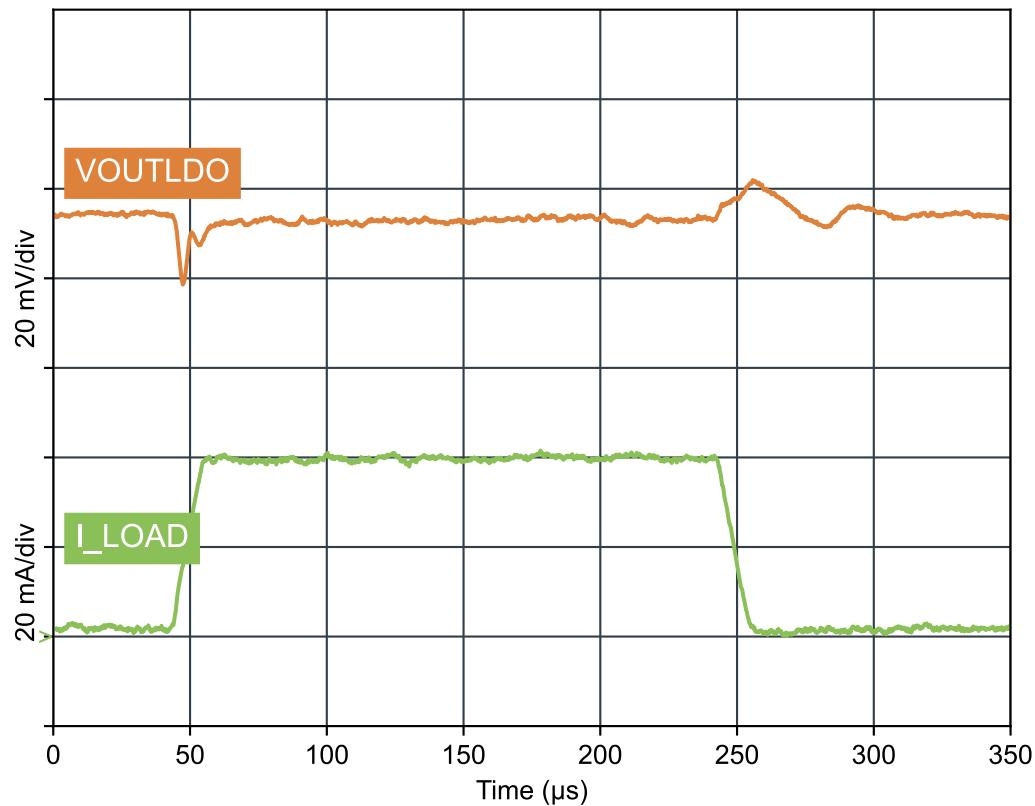

The following two figures show load transient in Auto mode (automatic mode change from Low Power mode to High Power mode, and back) when supplied by an alkaline AA battery. Load changes from 1 mA to 100 mA in 10  $\mu\text{s}$ .

Figure 15: Load transient,  $V_{OUT}=1.8\text{ V}$

Figure 16: Load transient,  $VOUT=3.0\text{ V}$

The following two figures show load transient in Low Power mode when supplied by an alkaline AA battery. Load changes from 1 mA to 100 mA in 10  $\mu\text{s}$ .

Figure 17: Load transient,  $V_{OUT}=1.8\text{ V}$

Figure 18: Load transient,  $V_{OUT}=3.0\text{ V}$

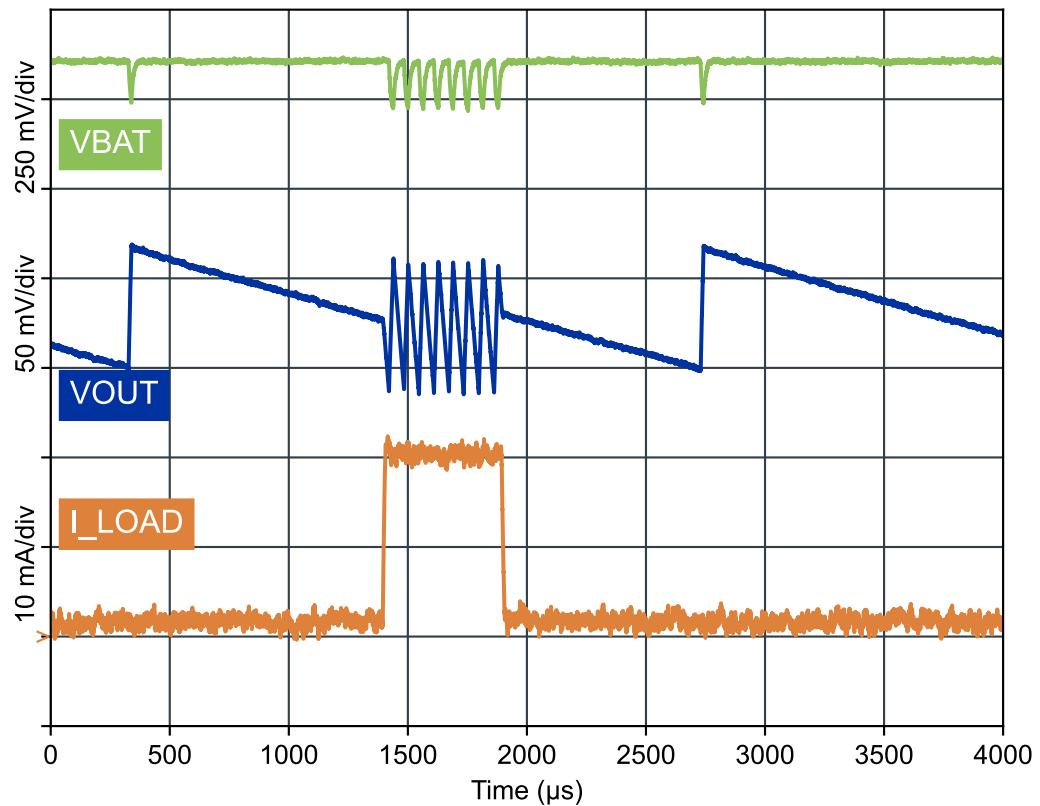

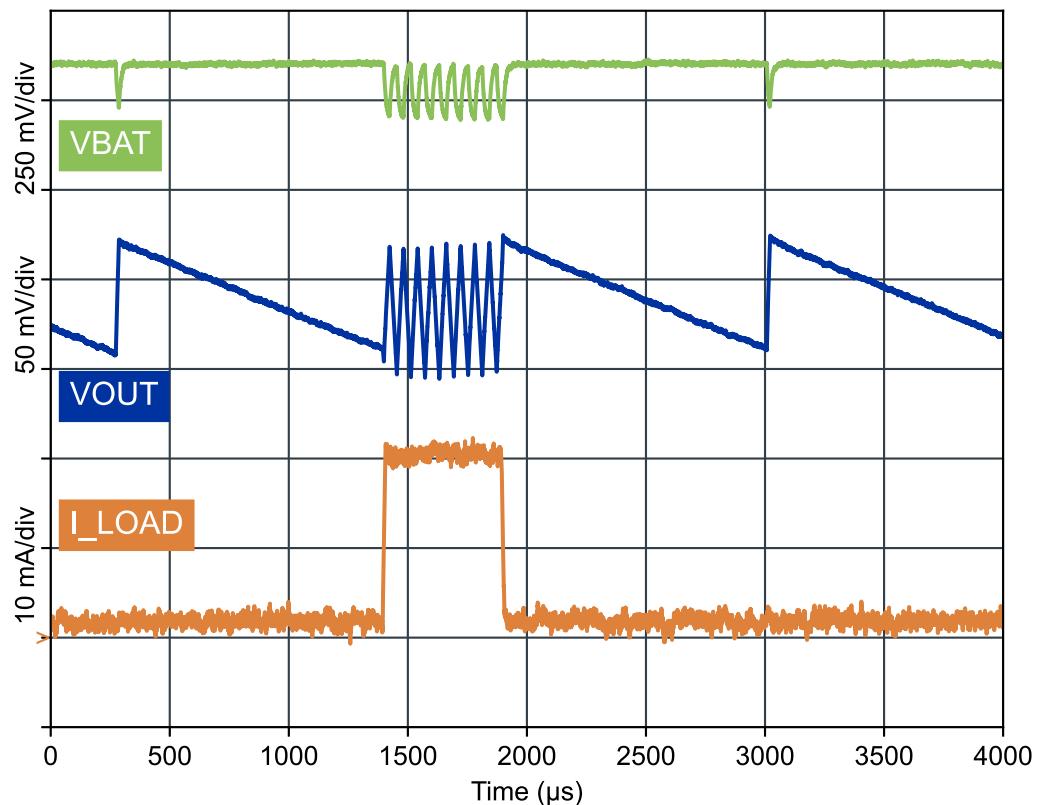

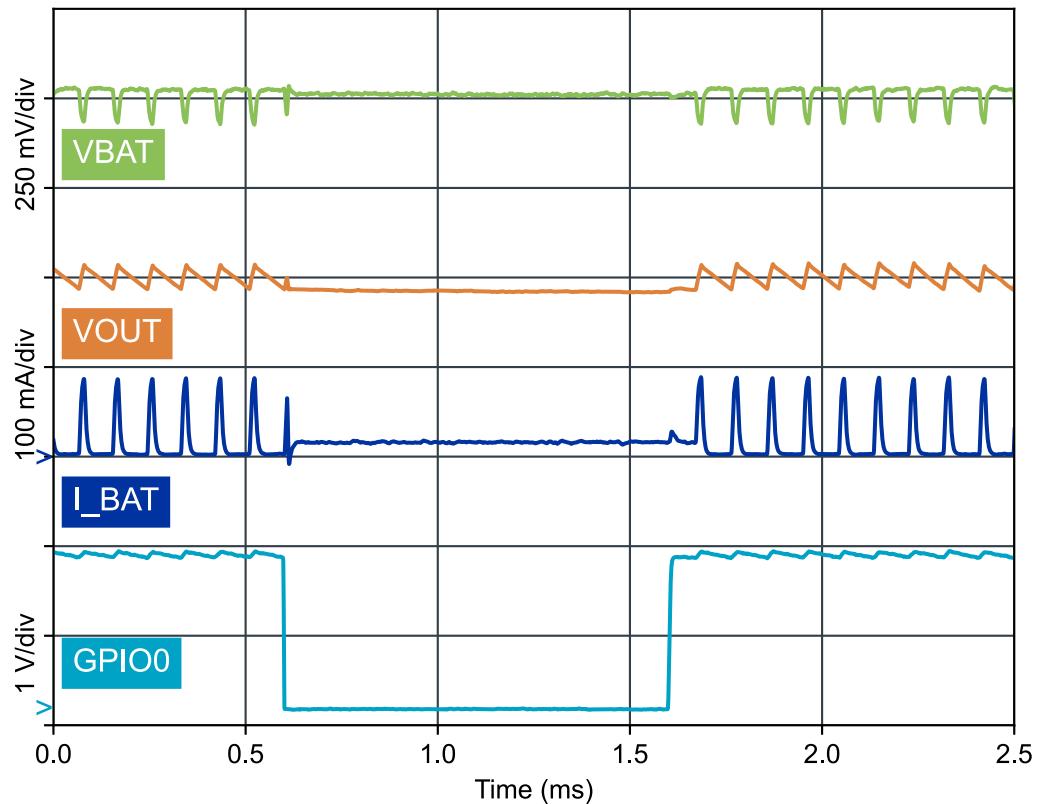

The following figure shows mode change from Low Power to High Power mode using GPIO control when supplied by an alkaline AA battery. Load is 10 mA.

Figure 19: Mode change,  $V_{OUT}=1.8$  V

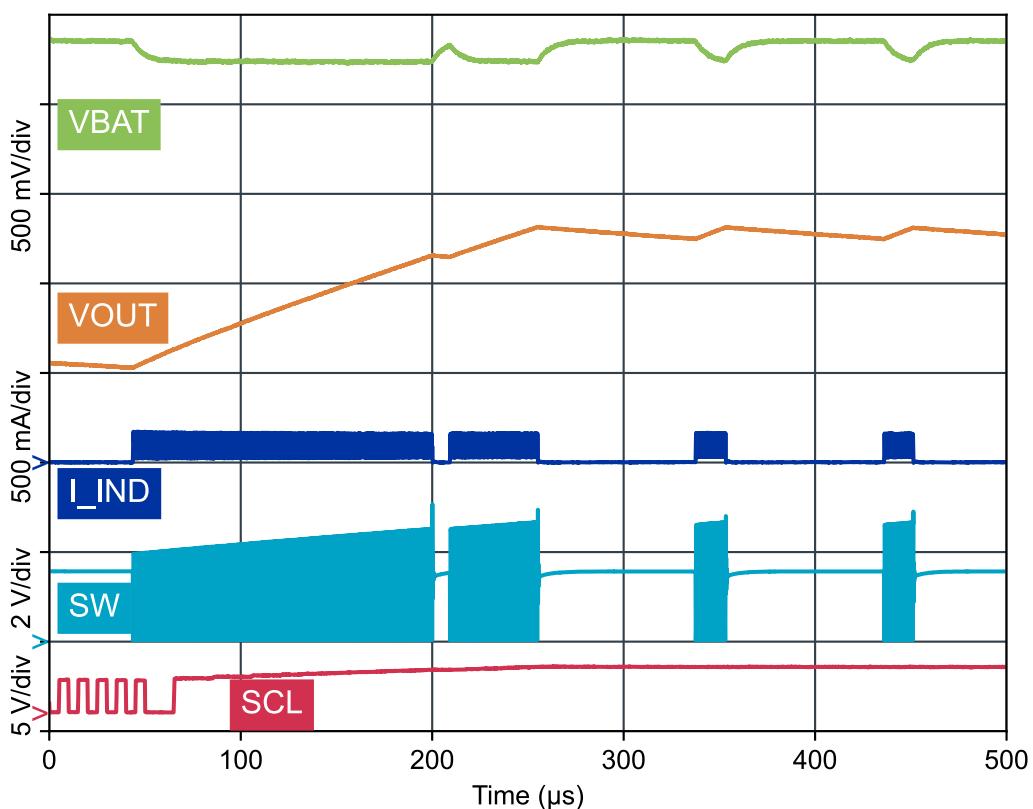

The following two figures show output voltage programming via TWI from 1.8 V to 2.5 V in various modes without load when supplied by an alkaline AA battery (LDOSW is in High Power mode, no load).

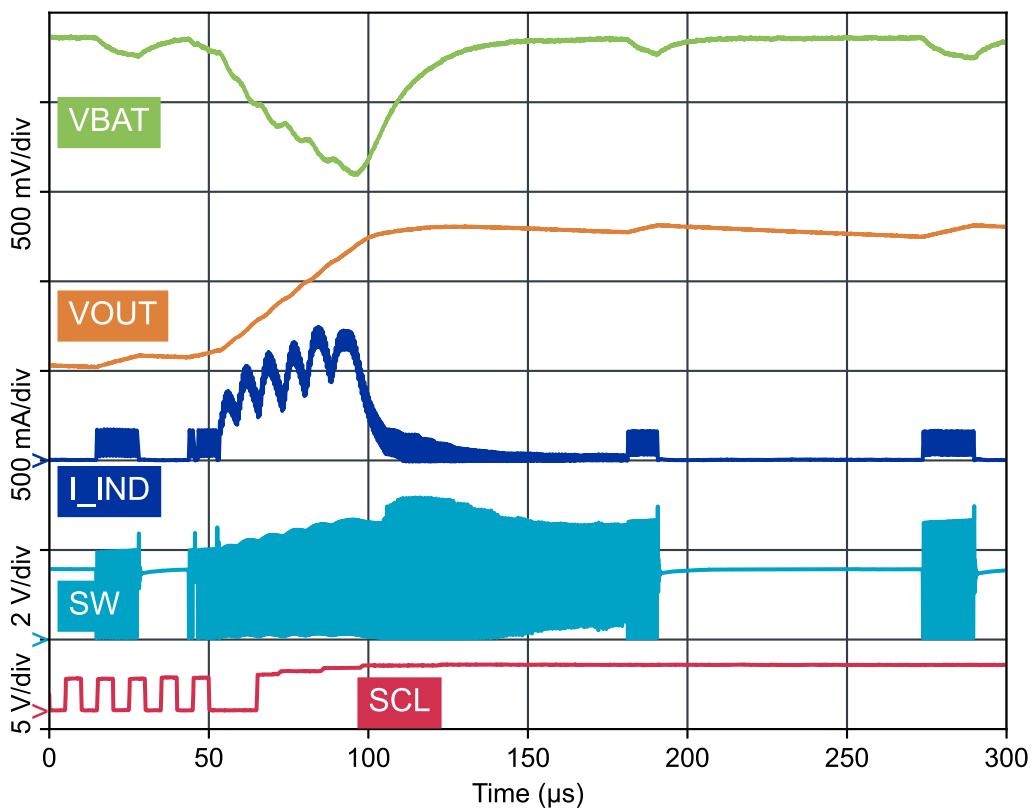

The following figure shows output voltage programming via TWI from 2.5 V to 1.8 V in Low Power mode without load when supplied by an alkaline AA battery (LDOSW is in High Power mode, no load).

Figure 22: Output voltage programming downwards

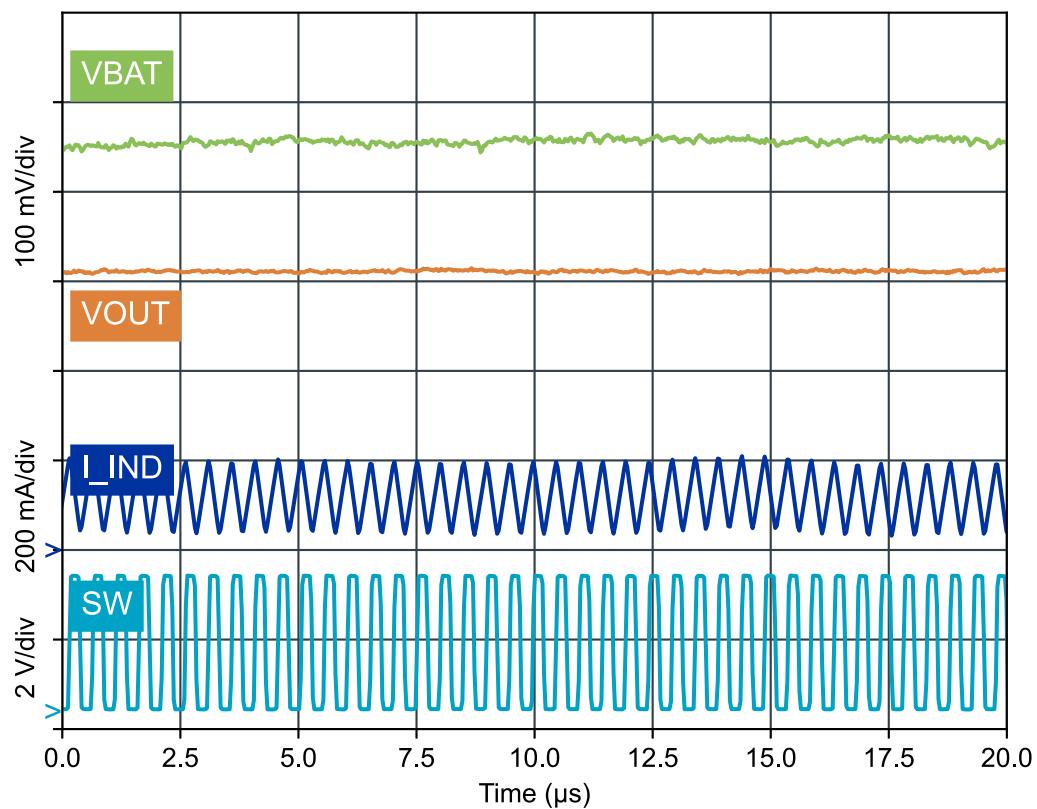

The following two figures show switching waveforms in various modes when VOUT=3.0 V when supplied by an alkaline AA battery.

Figure 23: Switching waveforms in High Power mode, load=50 mA

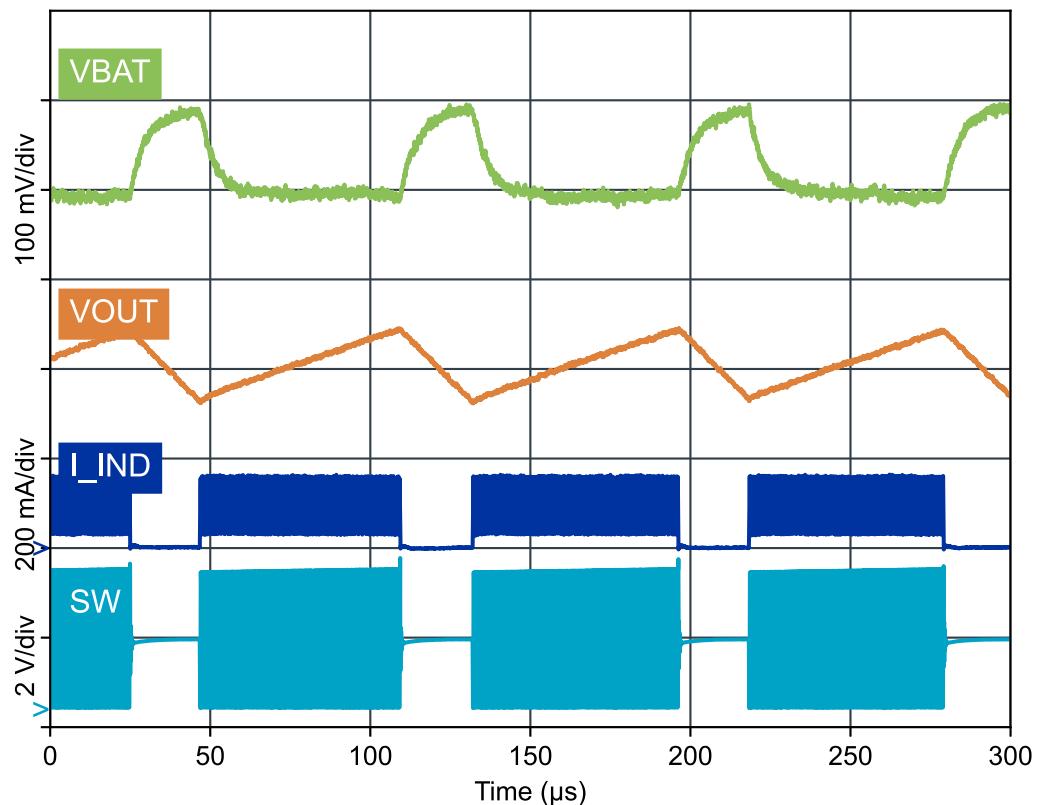

Figure 24: Switching waveforms in Low Power mode (load=30 mA)

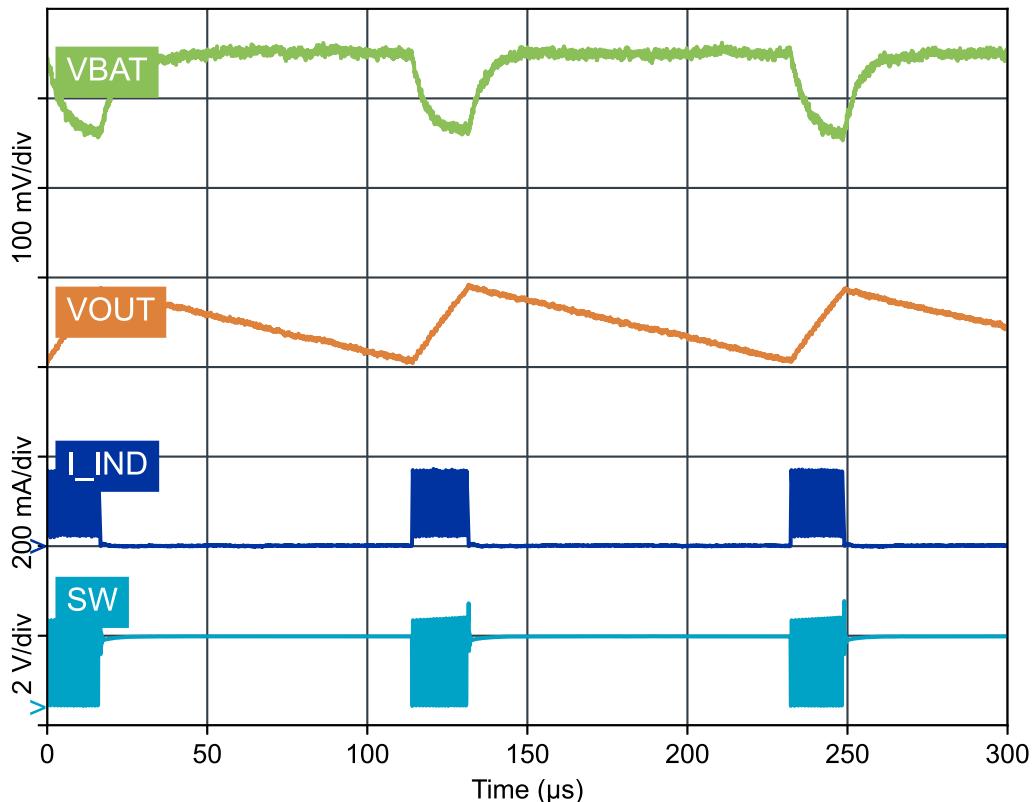

The following figure shows switching waveforms when  $V_{OUT}=1.8$  V and load=10 mA when supplied by an alkaline AA battery.

Figure 25: Switching waveforms in Ultra-Low Power mode

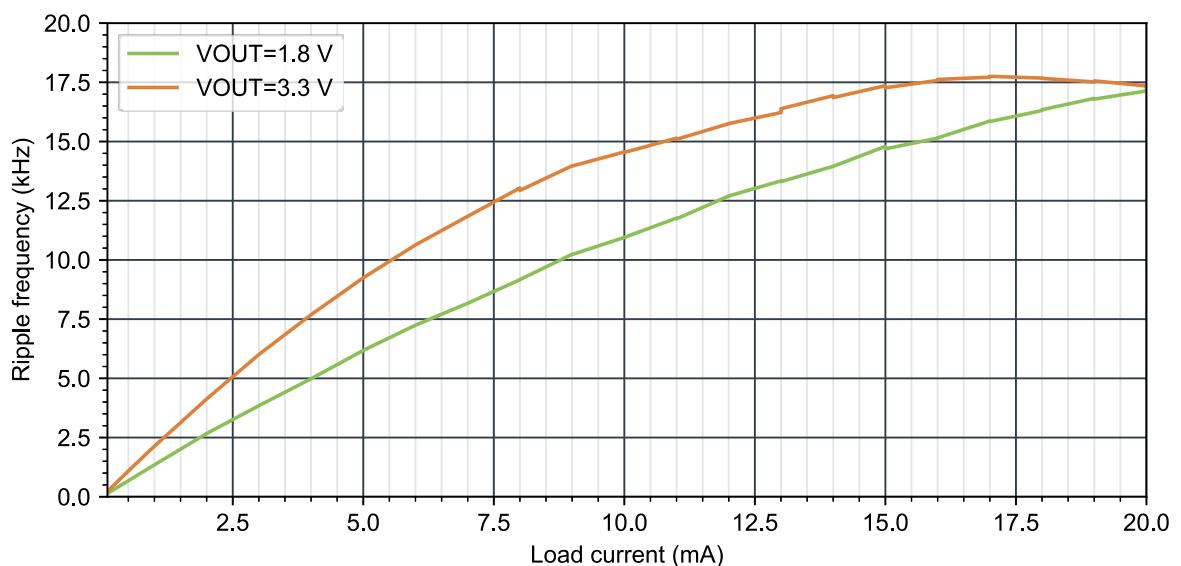

The following figure shows  $V_{OUT}$  ripple frequency vs. load in Low Power mode.

Figure 26: Ripple frequency vs. load current ( $V_{BAT}=1.5$  V)

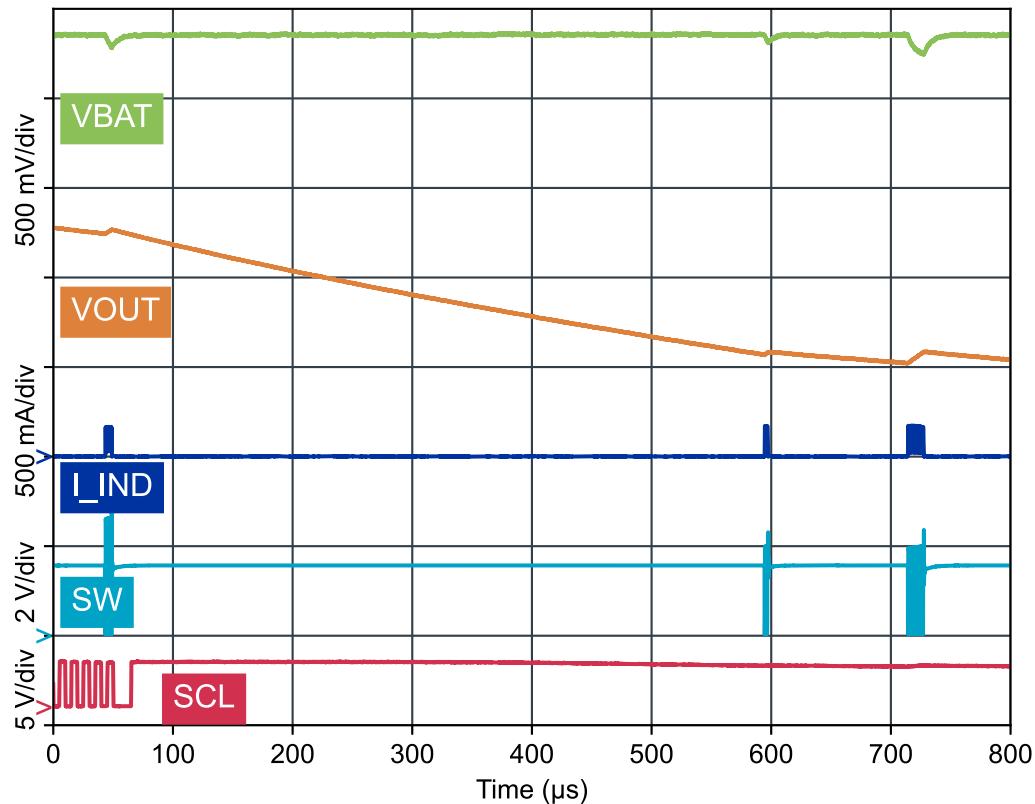

The following two figures show alkaline AA battery removal for various output voltages (LDOSW in High Power mode, no load).

Figure 27: Battery removal,  $VOUT=1.8\text{ V}$ Figure 28: Battery removal,  $VOUT=3.0\text{ V}$

## 6.1.6 Registers

### Instances

| Instance | Base address | Description     |

|----------|--------------|-----------------|

| BOOST    | 0x00000000   | BOOST Registers |

### Register overview

| Register     | Offset | Description                                                             |

|--------------|--------|-------------------------------------------------------------------------|

| TASKS_START  | 0x20   | Start tasks                                                             |

| VOUT         | 0x22   | Output voltage setting                                                  |

| VOUTSEL      | 0x23   | Output voltage set by pin or register                                   |

| OPER         | 0x24   | Operating mode selection                                                |

| COUNT        | 0x25   | Coil current pulse counter result in DPS mode                           |

| LIMIT        | 0x26   | Coil current pulse limiter setting in DPS mode                          |

| DPS          | 0x27   | Duration of DPS mode                                                    |

| GPIO         | 0x28   | GPIO and polarity selection for BOOST control                           |

| PIN          | 0x29   | GPIO usage for BOOST control                                            |

| CTRLSET      | 0x2A   | Enable VOUTMIN, VOUTWRN, VOUTDPS, OCP and VBATMINSEL                    |

| CTRLCLR      | 0x2B   | Disable VOUTMIN, VOUTWRN, VOUTDPS, OCP and VBATMINSEL                   |

| IBATLIM      | 0x2D   | Battery current limit setting                                           |

| VBATMINLHSEL | 0x2E   | Enable register control for VBATMINL and VBATMINH comparator thresholds |

| VBATMINL     | 0x2F   | Battery voltage threshold setting for VBATMINL                          |

| VBATMINH     | 0x30   | Battery voltage threshold setting for VBATMINH                          |

| VOUTMIN      | 0x31   | Output voltage threshold setting for VOUTMIN                            |

| VOUTWRN      | 0x32   | Output voltage threshold setting for VOUTWRN                            |

| VOUTDPS      | 0x33   | Output voltage threshold setting for VOUTDPS                            |

| STATUS0      | 0x34   | Read operating mode                                                     |

| STATUS1      | 0x35   | Status of output voltage                                                |

### 6.1.6.1 TASKS\_START

Address offset: 0x20

Start tasks

| Bit number        | 7   | 6        | 5        | 4     | 3                                             | 2 | 1 | 0                 |  |

|-------------------|-----|----------|----------|-------|-----------------------------------------------|---|---|-------------------|--|

| ID                |     |          |          |       |                                               |   |   | B A               |  |

| <b>Reset 0x00</b> |     |          |          |       |                                               |   |   | 0 0 0 0 0 0 0 0 0 |  |

| ID                | R/W | Field    | Value ID | Value | Description                                   |   |   |                   |  |

| A                 | W   | PULSECNT |          |       | Start coil current pulse counter for DPS mode |   |   |                   |  |

|                   |     |          | NoEffect | 0     | No effect                                     |   |   |                   |  |

|                   |     |          | Trigger  | 1     | Start counter                                 |   |   |                   |  |

| B                 | W   | DPSDUR   |          |       | Start DPS mode duration measurement           |   |   |                   |  |

|                   |     |          | NoEffect | 0     | No effect                                     |   |   |                   |  |

|                   |     |          | Trigger  | 1     | Start measurement                             |   |   |                   |  |

### 6.1.6.2 VOUT

Address offset: 0x22

Output voltage setting

| Bit number | 7   | 6     | 5        | 4     | 3                                                               | 2 | 1 | 0 |  |

|------------|-----|-------|----------|-------|-----------------------------------------------------------------|---|---|---|--|

| ID         | A   | A     | A        | A     | A                                                               | A | A | A |  |

| Reset 0x00 | 0   | 0     | 0        | 0     | 0                                                               | 0 | 0 | 0 |  |

| ID         | R/W | Field | Value ID | Value | Description                                                     |   |   |   |  |

| A          | RW  | LVL   |          |       | Output voltage setting (VOUT=1.8V+LVL*0.05V, legal range: 0-30) |   |   |   |  |

|            |     |       | 1V8      | 0     | 1.8 V (default)                                                 |   |   |   |  |

|            |     |       | 3V3      | 30    | 3.3 V                                                           |   |   |   |  |

## 6.1.6.3 VOUTSEL

Address offset: 0x23

Output voltage set by pin or register

| Bit number | 7   | 6      | 5        | 4     | 3                                                     | 2 | 1 | 0 |  |

|------------|-----|--------|----------|-------|-------------------------------------------------------|---|---|---|--|

| ID         |     |        |          |       |                                                       |   |   | A |  |

| Reset 0x00 | 0   | 0      | 0        | 0     | 0                                                     | 0 | 0 | 0 |  |

| ID         | R/W | Field  | Value ID | Value | Description                                           |   |   |   |  |

| A          | RW  | PINREG |          |       | Output voltage set by pin VSET or register BOOST.VOUT |   |   |   |  |

|            |     |        | Pin      | 0     | VOUT level is set by VSET pin                         |   |   |   |  |

|            |     |        | Register | 1     | VOUT is set by register BOOST.VOUT                    |   |   |   |  |

## 6.1.6.4 OPER

Address offset: 0x24

Operating mode selection

| Bit number | 7   | 6        | 5         | 4     | 3                                                               | 2 | 1 | 0 |  |

|------------|-----|----------|-----------|-------|-----------------------------------------------------------------|---|---|---|--|

| ID         | C   | C        | B         | B     | A                                                               | A | A | A |  |

| Reset 0x00 | 0   | 0        | 0         | 0     | 0                                                               | 0 | 0 | 0 |  |

| ID         | R/W | Field    | Value ID  | Value | Description                                                     |   |   |   |  |

| A          | RW  | MODE     |           |       | Set BOOST operating mode                                        |   |   |   |  |

|            |     |          | Auto      | 0     | Auto (HP/LP/ULP/PT) mode                                        |   |   |   |  |

|            |     |          | HP        | 1     | Forced High Power (HP) mode                                     |   |   |   |  |

|            |     |          | LP        | 2     | Forced Low Power (LP) mode                                      |   |   |   |  |

|            |     |          | PT        | 3     | Forced Pass-through (PT) mode                                   |   |   |   |  |

|            |     |          | NOHP      | 4     | Forced Prevent High Power mode                                  |   |   |   |  |

| B          | RW  | DPS      |           |       | DPS mode control                                                |   |   |   |  |

|            |     |          | Disable   | 0     | DPS operation not allowed                                       |   |   |   |  |

|            |     |          | ALLOW     | 1     | Allow DPS mode (MODE must be set to '4' or '2')                 |   |   |   |  |

|            |     |          | ALLOWLPLP | 2     | Allow DPS mode only in LP mode (MODE must be set to '4' or '2') |   |   |   |  |

| C          | RW  | DPSTIMER |           |       | Periodic timer setting for DPS mode                             |   |   |   |  |

|            |     |          | 100us     | 0     | 100 us (default)                                                |   |   |   |  |

|            |     |          | 200us     | 1     | 200 us                                                          |   |   |   |  |

|            |     |          | 400us     | 2     | 400 us                                                          |   |   |   |  |

|            |     |          | 800us     | 3     | 800 us                                                          |   |   |   |  |

## 6.1.6.5 COUNT

Address offset: 0x25

Coil current pulse counter result in DPS mode

| Bit number | 7   | 6      | 5        | 4     | 3                                                                           | 2 | 1 | 0 |  |

|------------|-----|--------|----------|-------|-----------------------------------------------------------------------------|---|---|---|--|

| ID         | A   | A      | A        | A     | A                                                                           | A | A | A |  |

| Reset 0x00 | 0   | 0      | 0        | 0     | 0                                                                           | 0 | 0 | 0 |  |

| ID         | R/W | Field  | Value ID | Value | Description                                                                 |   |   |   |  |

| A          | R   | PULSES |          |       | Number of counted coil current pulses per re-fresh period in DPS mode (pcs) |   |   |   |  |

### 6.1.6.6 LIMIT

Address offset: 0x26

Coil current pulse limiter setting in DPS mode

| Bit number | 7   | 6       | 5        | 4     | 3                                                                      | 2 | 1 | 0 |  |

|------------|-----|---------|----------|-------|------------------------------------------------------------------------|---|---|---|--|

| ID         | A   | A       | A        | A     | A                                                                      | A | A | A |  |

| Reset 0x00 | 0   | 0       | 0        | 0     | 0                                                                      | 0 | 0 | 0 |  |

| ID         | R/W | Field   | Value ID | Value | Description                                                            |   |   |   |  |

| A          | RW  | PULSES  |          |       | Limit setting for coil current pulses per re-fresh period in DPS mode. |   |   |   |  |

|            |     | NoLimit | 0        |       | Coil current pulse count not limited                                   |   |   |   |  |

|            |     | Sel3    | 3        |       | 3 pulses (min. value)                                                  |   |   |   |  |

|            |     | Sel4    | 4        |       | 4 pulses                                                               |   |   |   |  |

|            |     | Sel255  | 255      |       | 255 pulses                                                             |   |   |   |  |

### 6.1.6.7 DPS

Address offset: 0x27

Duration of DPS mode

| Bit number | 7   | 6        | 5        | 4     | 3                         | 2 | 1 | 0 |  |

|------------|-----|----------|----------|-------|---------------------------|---|---|---|--|

| ID         | A   | A        | A        | A     | A                         | A | A | A |  |

| Reset 0x00 | 0   | 0        | 0        | 0     | 0                         | 0 | 0 | 0 |  |

| ID         | R/W | Field    | Value ID | Value | Description               |   |   |   |  |

| A          | R   | DURATION |          |       | Duration of DPS mode (ms) |   |   |   |  |

### 6.1.6.8 GPIO

Address offset: 0x28

GPIO and polarity selection for BOOST control

| Bit number | 7   | 6       | 5        | 4     | 3                                                                              | 2 | 1 | 0 |  |

|------------|-----|---------|----------|-------|--------------------------------------------------------------------------------|---|---|---|--|

| ID         |     |         |          |       |                                                                                |   |   |   |  |

| Reset 0x00 | 0   | 0       | 0        | 0     | 0                                                                              | 0 | 0 | 0 |  |

| ID         | R/W | Field   | Value ID | Value | Description                                                                    |   |   |   |  |

| A          | RW  | POL     |          |       | One GPIO can be selected to control BOOST. Polarity can be active low or high. |   |   |   |  |

|            |     | None    | 0        |       | No GPIO controls BOOST                                                         |   |   |   |  |

|            |     | GPIO0LO | 1        |       | GPIO0 in use, active low                                                       |   |   |   |  |

|            |     | GPIO0HI | 2        |       | GPIO0 in use, active high                                                      |   |   |   |  |

|            |     | GPIO1LO | 3        |       | GPIO1 in use, active low                                                       |   |   |   |  |

|            |     | GPIO1HI | 4        |       | GPIO1 in use, active high                                                      |   |   |   |  |

|            |     | GPIO2LO | 5        |       | Reserved (GPIO2 in use, active low)                                            |   |   |   |  |

|            |     | GPIO2HI | 6        |       | Reserved (GPIO2 in use, active high)                                           |   |   |   |  |

### 6.1.6.9 PIN

Address offset: 0x29

GPIO usage for BOOST control

| Bit number |     |       |          | 7                                                                                                                                                                                    | 6                                         | 5 | 4 | 3 | 2 | 1 | 0 |             |

|------------|-----|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---|---|---|---|---|---|-------------|

| ID         |     |       |          | A A                                                                                                                                                                                  |                                           |   |   |   |   |   |   |             |

| Reset 0x00 |     |       |          | 0 0 0 0 0 0 0 0                                                                                                                                                                      |                                           |   |   |   |   |   |   |             |

| ID         | R/W | Field | Value ID | Value                                                                                                                                                                                |                                           |   |   |   |   |   |   | Description |

| A          | RW  | FORCE |          | Operating mode setting when GPIO is used to control BOOST. Active GPIO selects the mode from this register. When GPIO is inactive, operating mode is defined by register BOOST.OPER. |                                           |   |   |   |   |   |   |             |

|            |     |       | HP       | 0                                                                                                                                                                                    | Active GPIO forces High Power (HP) mode   |   |   |   |   |   |   |             |

|            |     |       | LP       | 1                                                                                                                                                                                    | Active GPIO forces Low Power (LP) mode    |   |   |   |   |   |   |             |

|            |     |       | PT       | 2                                                                                                                                                                                    | Active GPIO forces Pass-through (PT) mode |   |   |   |   |   |   |             |

|            |     |       | NOHP     | 3                                                                                                                                                                                    | Active GPIO forces Prevent HP mode        |   |   |   |   |   |   |             |

### 6.1.6.10 CTRLSET

Address offset: 0x2A

Enable VOUTMIN, VOUTWRN, VOUTDPS, OCP and VBATMINSEL

| Bit number |     |            |          | 7                                                         | 6      | 5         | 4 | 3 | 2 | 1 | 0 |             |

|------------|-----|------------|----------|-----------------------------------------------------------|--------|-----------|---|---|---|---|---|-------------|

| ID         |     |            |          | E D C B A                                                 |        |           |   |   |   |   |   |             |

| Reset 0x08 |     |            |          | 0 0 0 0 1 0 0 0                                           |        |           |   |   |   |   |   |             |

| ID         | R/W | Field      | Value ID | Value                                                     |        |           |   |   |   |   |   | Description |

| A          | RW  | VOUTMIN    |          | Enable output voltage comparator VOUTMIN                  |        |           |   |   |   |   |   |             |

|            |     | W1S        |          | NoEffect                                                  | 0      | No effect |   |   |   |   |   |             |

|            |     |            | Enable   | 1                                                         | Enable |           |   |   |   |   |   |             |

| B          | RW  | VOUTWRN    |          | Enable output voltage comparator VOUTWRN                  |        |           |   |   |   |   |   |             |

|            |     | W1S        |          | NoEffect                                                  | 0      | No effect |   |   |   |   |   |             |

|            |     |            | Enable   | 1                                                         | Enable |           |   |   |   |   |   |             |

| C          | RW  | VOUTDPS    |          | Enable output voltage comparator VOUTDPS                  |        |           |   |   |   |   |   |             |

|            |     | W1S        |          | NoEffect                                                  | 0      | No effect |   |   |   |   |   |             |

|            |     |            | Enable   | 1                                                         | Enable |           |   |   |   |   |   |             |

| D          | RW  | OCP        |          | Enable overcurrent protection (OCP) for Pass-through mode |        |           |   |   |   |   |   |             |

|            |     | W1S        |          | NoEffect                                                  | 0      | No effect |   |   |   |   |   |             |

|            |     |            | Enable   | 1                                                         | Enable |           |   |   |   |   |   |             |

| E          | RW  | VBATMINSEL |          | Allow VOUTMIN comparator to control VBATMIN L/H selection |        |           |   |   |   |   |   |             |

|            |     | W1S        |          | NoEffect                                                  | 0      | No effect |   |   |   |   |   |             |

|            |     |            | Enable   | 1                                                         | Enable |           |   |   |   |   |   |             |

### 6.1.6.11 CTRLCLR

Address offset: 0x2B

Disable VOUTMIN, VOUTWRN, VOUTDPS, OCP and VBATMINSEL

| Bit number |     |            |          |       | 7                                                                | 6 | 5         | 4 | 3 | 2 | 1 | 0 |

|------------|-----|------------|----------|-------|------------------------------------------------------------------|---|-----------|---|---|---|---|---|

| ID         |     |            |          |       | E D C B A                                                        |   |           |   |   |   |   |   |

| Reset 0x08 |     |            |          |       |                                                                  |   |           |   |   |   |   |   |

| ID         | R/W | Field      | Value ID | Value | Description                                                      |   |           |   |   |   |   |   |

| A          | RW  | VOUTMIN    |          |       | Disable output voltage comparator VOUTMIN                        |   |           |   |   |   |   |   |

|            |     | W1C        |          |       | NoEffect                                                         | 0 | No effect |   |   |   |   |   |

|            |     |            |          |       | Disable                                                          | 1 | Disable   |   |   |   |   |   |

| B          | RW  | VOUTWRN    |          |       | Disable output voltage comparator VOUTWRN                        |   |           |   |   |   |   |   |

|            |     | W1C        |          |       | NoEffect                                                         | 0 | No effect |   |   |   |   |   |

|            |     |            |          |       | Disable                                                          | 1 | Disable   |   |   |   |   |   |

| C          | RW  | VOUTDPS    |          |       | Disable output voltage comparator VOUTDPS                        |   |           |   |   |   |   |   |

|            |     | W1C        |          |       | NoEffect                                                         | 0 | No effect |   |   |   |   |   |

|            |     |            |          |       | Disable                                                          | 1 | Disable   |   |   |   |   |   |

| D          | RW  | OCP        |          |       | Disable overcurrent protection (OCP) for Pass-through mode       |   |           |   |   |   |   |   |

|            |     | W1C        |          |       | NoEffect                                                         | 0 | No effect |   |   |   |   |   |

|            |     |            |          |       | Disable                                                          | 1 | Disable   |   |   |   |   |   |

| E          | RW  | VBATMINSEL |          |       | Do not allow VOUTMIN comparator to control VBATMIN L/H selection |   |           |   |   |   |   |   |

|            |     | W1C        |          |       | NoEffect                                                         | 0 | No effect |   |   |   |   |   |

|            |     |            |          |       | Disable                                                          | 1 | Disable   |   |   |   |   |   |

### 6.1.6.12 IBATLIM

Address offset: 0x2D

Battery current limit setting

| Bit number |     |       |          |       | 7                                      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|-----|-------|----------|-------|----------------------------------------|---|---|---|---|---|---|---|

| ID         |     |       |          |       | A A A                                  |   |   |   |   |   |   |   |

| Reset 0x00 |     |       |          |       |                                        |   |   |   |   |   |   |   |

| ID         | R/W | Field | Value ID | Value | Description                            |   |   |   |   |   |   |   |

| A          | RW  | LVL   |          |       | Battery (valley) current limit setting |   |   |   |   |   |   |   |

|            |     |       | 600MA    | 0     | 600 mA (default)                       |   |   |   |   |   |   |   |

|            |     |       | 100MA    | 1     | 100 mA                                 |   |   |   |   |   |   |   |

|            |     |       | 200MA    | 2     | 200 mA                                 |   |   |   |   |   |   |   |

|            |     |       | 300MA    | 3     | 300 mA                                 |   |   |   |   |   |   |   |

|            |     |       | 400MA    | 4     | 400 mA                                 |   |   |   |   |   |   |   |

|            |     |       | 500MA    | 5     | 500 mA                                 |   |   |   |   |   |   |   |

|            |     |       | 700MA    | 6     | 700 mA                                 |   |   |   |   |   |   |   |

|            |     |       | 800MA    | 7     | 800 mA                                 |   |   |   |   |   |   |   |

### 6.1.6.13 VBATMINLHSEL

Address offset: 0x2E

Enable register control for VBATMINL and VBATMINH comparator thresholds

| Bit number                                     | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

| ID                                             |          |          |          |          |          |          |          | B A      |

| <b>Reset 0x00</b>                              | <b>0</b> |

| <b>ID R/W Field Value ID Value Description</b> |          |          |          |          |          |          |          |          |

| A RW VBATMINLSEL                               |          |          |          |          |          |          |          |          |

|                                                |          | Disable  | 0        |          |          |          |          |          |

|                                                |          | Enable   | 1        |          |          |          |          |          |

| B RW VBATMINHSEL                               |          |          |          |          |          |          |          |          |

|                                                |          | Disable  | 0        |          |          |          |          |          |

|                                                |          | Enable   | 1        |          |          |          |          |          |

### 6.1.6.14 VBATMINL

Address offset: 0x2F

Battery voltage threshold setting for VBATMINL

| Bit number                                     | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0           |

|------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|-------------|

| ID                                             |          |          |          |          |          |          |          | A A A A A A |

| <b>Reset 0x00</b>                              | <b>0</b>    |

| <b>ID R/W Field Value ID Value Description</b> |          |          |          |          |          |          |          |             |

| A RW LVL                                       |          |          |          |          |          |          |          |             |

|                                                |          |          |          |          |          |          |          |             |

|                                                |          | 0V65     | 0        |          |          |          |          |             |

|                                                |          | 3V15     | 50       |          |          |          |          |             |

### 6.1.6.15 VBATMINH

Address offset: 0x30

Battery voltage threshold setting for VBATMINH

| Bit number                                     | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0           |

|------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|-------------|

| ID                                             |          |          |          |          |          |          |          | A A A A A A |

| <b>Reset 0x00</b>                              | <b>0</b>    |

| <b>ID R/W Field Value ID Value Description</b> |          |          |          |          |          |          |          |             |

| A RW LVL                                       |          |          |          |          |          |          |          |             |

|                                                |          |          |          |          |          |          |          |             |

|                                                |          | 0V65     | 0        |          |          |          |          |             |

|                                                |          | 3V15     | 50       |          |          |          |          |             |

### 6.1.6.16 VOUTMIN

Address offset: 0x31

Output voltage threshold setting for VOUTMIN

| Bit number | 7   | 6     | 5        | 4     | 3                                                                                | 2 | 1 | 0 |

|------------|-----|-------|----------|-------|----------------------------------------------------------------------------------|---|---|---|

| ID         | A   | A     | A        | A     | A                                                                                | A | A | A |

| Reset 0x0A | 0   | 0     | 0        | 0     | 1                                                                                | 0 | 1 | 0 |

| ID         | R/W | Field | Value ID | Value | Description                                                                      |   |   |   |

| A          | RW  | LVL   |          |       | VOUTMIN comparator threshold setting (VOUTMIN=1.7V+LVL*0.05V, legal range: 0-31) |   |   |   |

|            |     | 1V70  | 0        | 0     | 1.70 V                                                                           |   |   |   |

|            |     | 2V20  | 10       | 10    | 2.20 V (default)                                                                 |   |   |   |

|            |     | 3V25  | 31       | 31    | 3.25 V                                                                           |   |   |   |

## 6.1.6.17 VOUTWRN

Address offset: 0x32

Output voltage threshold setting for VOUTWRN

| Bit number | 7   | 6     | 5        | 4     | 3                                                                                | 2 | 1 | 0 |

|------------|-----|-------|----------|-------|----------------------------------------------------------------------------------|---|---|---|

| ID         | A   | A     | A        | A     | A                                                                                | A | A | A |

| Reset 0x0C | 0   | 0     | 0        | 0     | 1                                                                                | 1 | 0 | 0 |

| ID         | R/W | Field | Value ID | Value | Description                                                                      |   |   |   |

| A          | RW  | LVL   |          |       | VOUTWRN comparator threshold setting (VOUTWRN=1.7V+LVL*0.05V, legal range: 0-31) |   |   |   |

|            |     | 1V70  | 0        | 0     | 1.70 V                                                                           |   |   |   |

|            |     | 2V30  | 12       | 12    | 2.30 V (default)                                                                 |   |   |   |

|            |     | 3V25  | 31       | 31    | 3.25 V                                                                           |   |   |   |

## 6.1.6.18 VOUTDPS

Address offset: 0x33

Output voltage threshold setting for VOUTDPS

| Bit number | 7   | 6     | 5        | 4     | 3                                                                                | 2 | 1 | 0 |

|------------|-----|-------|----------|-------|----------------------------------------------------------------------------------|---|---|---|

| ID         | A   | A     | A        | A     | A                                                                                | A | A | A |

| Reset 0x00 | 0   | 0     | 0        | 0     | 0                                                                                | 0 | 0 | 0 |

| ID         | R/W | Field | Value ID | Value | Description                                                                      |   |   |   |

| A          | RW  | LVL   |          |       | VOUTDPS comparator threshold setting (VOUTDPS=1.9V+LVL*0.05V, legal range: 0-31) |   |   |   |

|            |     | 1V9   | 0        | 0     | 1.9 V (default)                                                                  |   |   |   |

|            |     | 3V45  | 31       | 31    | 3.45 V                                                                           |   |   |   |

## 6.1.6.19 STATUS0

Address offset: 0x34

Read operating mode

| Bit number |     |       |  |  | 7               | 6 | 5 | 4     | 3                                  | 2 | 1 | 0 |

|------------|-----|-------|--|--|-----------------|---|---|-------|------------------------------------|---|---|---|

| ID         |     |       |  |  | A               |   | A |       |                                    |   |   |   |

| Reset 0x00 |     |       |  |  | 0 0 0 0 0 0 0 0 |   |   |       |                                    |   |   |   |

| ID         | R/W | Field |  |  | Value ID        |   |   | Value |                                    |   |   |   |

| A          | R   | MODE  |  |  |                 |   |   |       | Description                        |   |   |   |

|            |     |       |  |  |                 |   |   |       | Read BOOST operating mode          |   |   |   |

|            |     |       |  |  | HP              |   |   | 0     | High Power (HP) mode               |   |   |   |

|            |     |       |  |  | LP              |   |   | 1     | Low Power (LP) mode                |   |   |   |

|            |     |       |  |  | ULP             |   |   | 2     | Ultra-Low Power (ULP) mode         |   |   |   |

|            |     |       |  |  | PT              |   |   | 3     | Pass-through (PT) mode             |   |   |   |

|            |     |       |  |  | DPS             |   |   | 4     | Dynamic Power Smoothing (DPS) mode |   |   |   |

## 6.1.6.20 STATUS1

Address offset: 0x35

Status of output voltage

| Bit number |     |              |  |  | 7               | 6 | 5 | 4     | 3                                             | 2 | 1 | 0 |       |  |

|------------|-----|--------------|--|--|-----------------|---|---|-------|-----------------------------------------------|---|---|---|-------|--|

| ID         |     |              |  |  | G               |   | F |       | E                                             |   | D |   | C B A |  |

| Reset 0x00 |     |              |  |  | 0 0 0 0 0 0 0 0 |   |   |       |                                               |   |   |   |       |  |

| ID         | R/W | Field        |  |  | Value ID        |   |   | Value | Description                                   |   |   |   |       |  |

| A          | R   | VOUTMIN      |  |  |                 |   |   |       | Output voltage vs. VOUTMIN                    |   |   |   |       |  |

|            |     |              |  |  | NotActive       |   |   | 0     | VOUT above VOUTMIN threshold                  |   |   |   |       |  |

|            |     |              |  |  | Active          |   |   | 1     | VOUT below VOUTMIN threshold                  |   |   |   |       |  |

| B          | R   | VOUTWRN      |  |  |                 |   |   |       | Output voltage vs. VOUTWRN                    |   |   |   |       |  |

|            |     |              |  |  | NotActive       |   |   | 0     | VOUT above VOUTWRN threshold                  |   |   |   |       |  |

|            |     |              |  |  | Active          |   |   | 1     | VOUT below VOUTWRN threshold                  |   |   |   |       |  |

| C          | R   | VOUTDPS      |  |  |                 |   |   |       | Output voltage vs. VOUTDPS                    |   |   |   |       |  |

|            |     |              |  |  | NotActive       |   |   | 0     | VOUT above VOUTDPS threshold                  |   |   |   |       |  |

|            |     |              |  |  | Active          |   |   | 1     | VOUT below VOUTDPS threshold                  |   |   |   |       |  |

| D          | R   | VOUTLVL      |  |  |                 |   |   |       | Output voltage vs. target                     |   |   |   |       |  |

|            |     |              |  |  | UnderVolt       |   |   | 0     | VOUT is below target level                    |   |   |   |       |  |

|            |     |              |  |  | AtTarget        |   |   | 1     | VOUT at target level                          |   |   |   |       |  |

| E          | R   | CNTRDY       |  |  |                 |   |   |       | Coil current pulse count valid (for DPS mode) |   |   |   |       |  |

|            |     |              |  |  | NotReady        |   |   | 0     | Coil current pulse count not available        |   |   |   |       |  |

|            |     |              |  |  | Ready           |   |   | 1     | Coil current pulse counter result ready       |   |   |   |       |  |

| F          | R   | DURRDY       |  |  |                 |   |   |       | DPS mode duration result valid                |   |   |   |       |  |

|            |     |              |  |  | NotReady        |   |   | 0     | DPS mode duration result not available        |   |   |   |       |  |

|            |     |              |  |  | Ready           |   |   | 1     | DPS mode duration result ready                |   |   |   |       |  |

| G          | R   | VSETCAPTURED |  |  |                 |   |   |       | Captured value of VSET pin                    |   |   |   |       |  |

|            |     |              |  |  | GND             |   |   | 0     | Grounded (low)                                |   |   |   |       |  |

|            |     |              |  |  | NC              |   |   | 1     | Not connected (high)                          |   |   |   |       |  |

## 6.2 LDOSW – Linear voltage regulator/load switch

The linear voltage regulator/load switch (LDOSW) can be used as a switch or LDO regulator both in Active and Hibernate modes.

LDOSW is supplied from BOOST output (VINT). LDO or load switch must be selected prior to enabling LDOSW in register [LDOSW.SEL](#). The mode can also be controlled through a GPIO by selecting [PINCTRL](#) in register [LDOSW.SEL](#) and configuring register [LDOSW.GPIO](#).

The power modes for LDOSW are configured in register [LDOSW.SEL](#) and consist of the following:

- Auto – This is the default mode where the device operating mode determines the LDOSW mode. When the device is in Active mode, LDOSW is in High Power mode. When the device is in Hibernate mode, LDOSW is in Ultra-Low Power mode.

- High Power – Output current up to 50 mA.

- Ultra-Low Power – Output current up to 2 mA.

Overcurrent protection is enabled by default. It can be disabled in register [CONF](#). The current limits for soft start and overcurrent protection can be configured in register [PRGOCP](#). The **LSOUT/VOUTLDO** pin is actively discharged when LDOSW is disabled.

**Note:** GPIO controls must be disabled before entering Hibernate or Hibernate\_PT mode.

## LDO mode

The LDO is OFF by default. LDO mode is set by selecting **LDO** in register [LDOSW.SEL](#). The output voltage is configurable in 50 mV steps in register [LDOSW.VOUT](#) and enabled in register [LDOSW.LDOSW](#).

## Load switch

The load switch is OFF by default. Load switch mode is set by selecting **LoadSW** in register [LDOSW.SEL](#) and enabled in register [LDOSW.LDOSW](#).

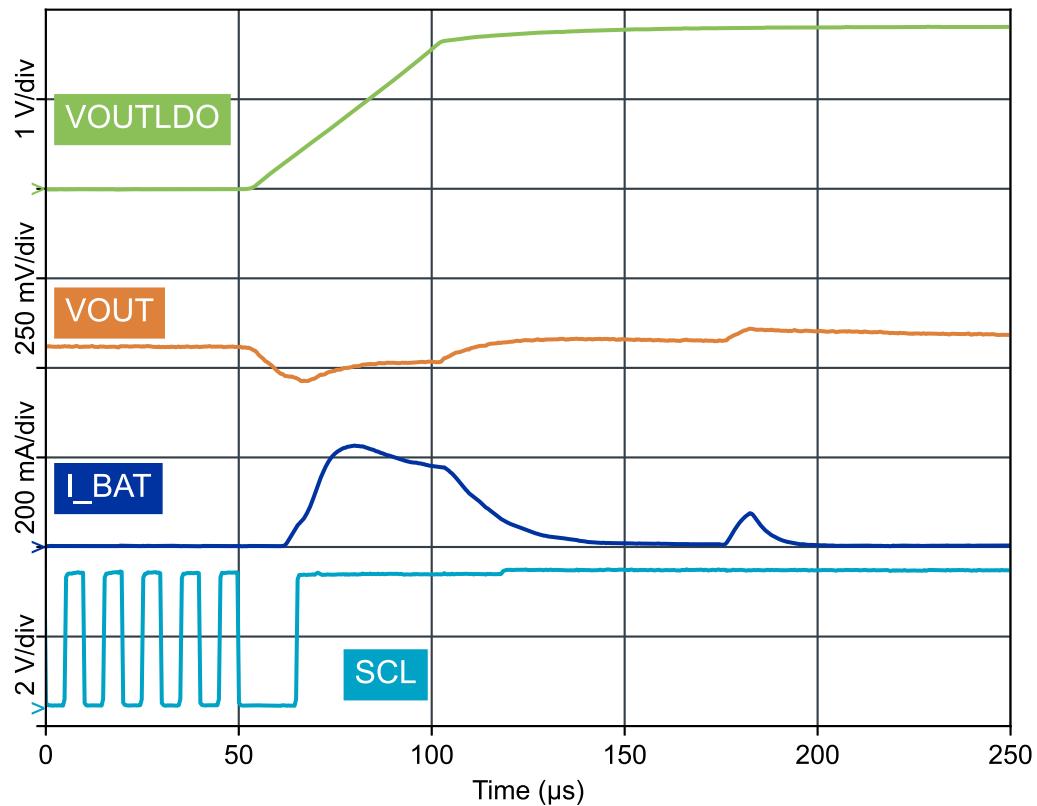

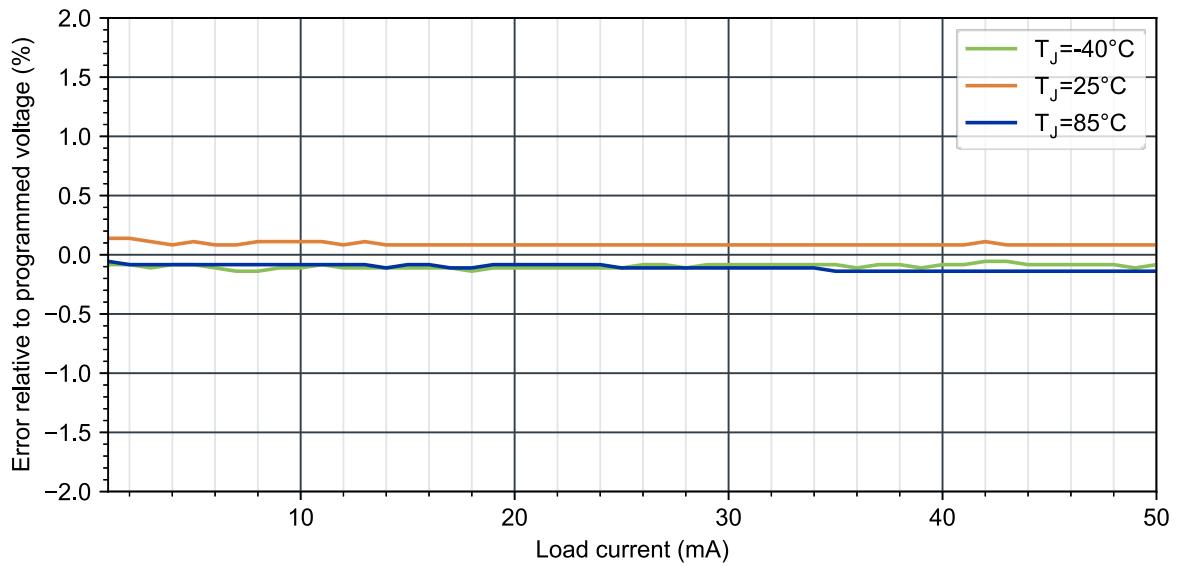

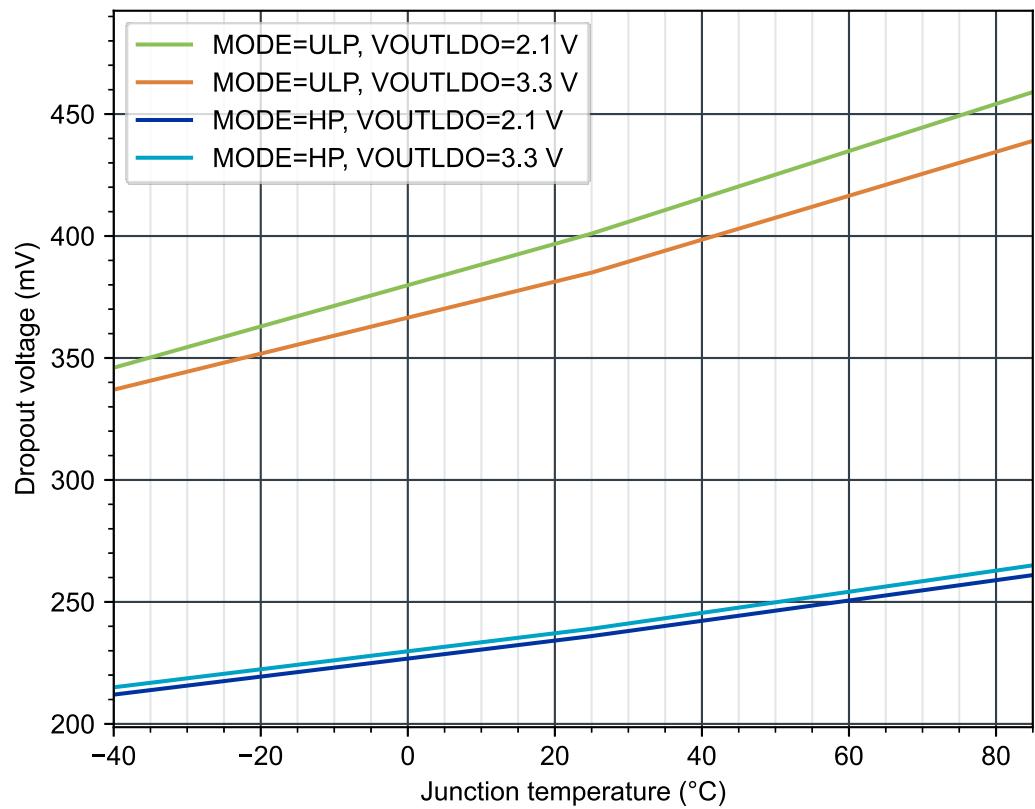

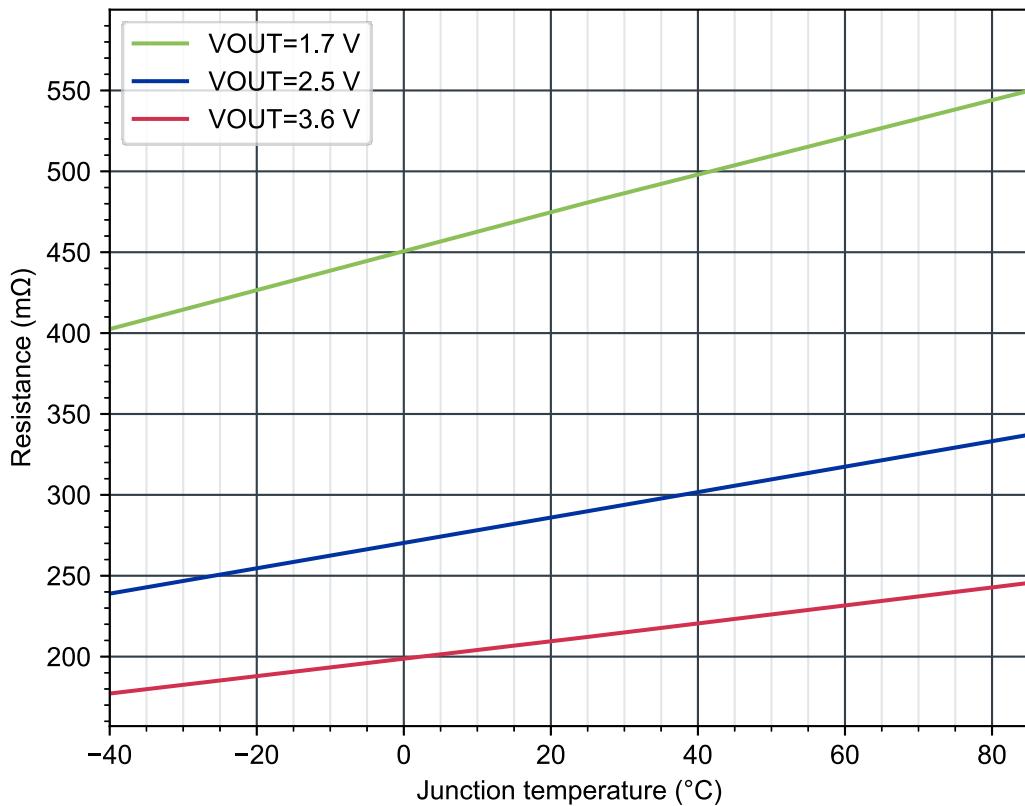

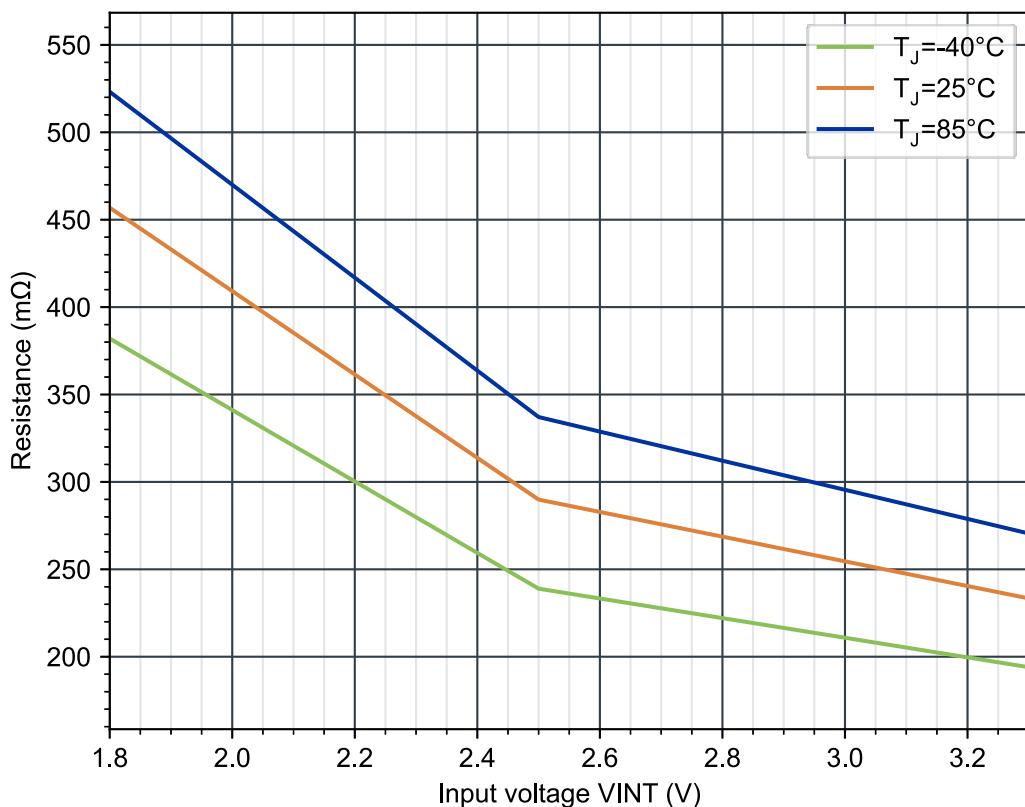

### 6.2.1 LDO electrical specification

Electrical parameters have been measured using a 2.2  $\mu$ F output capacitor.  $T_J$ =-40°C to 105°C,  $V_{BAT}$ =0.8 V to 3.4 V and  $T_J$ =25°C,  $V_{BAT}$ =1.25 V for typical values (unless otherwise noted).

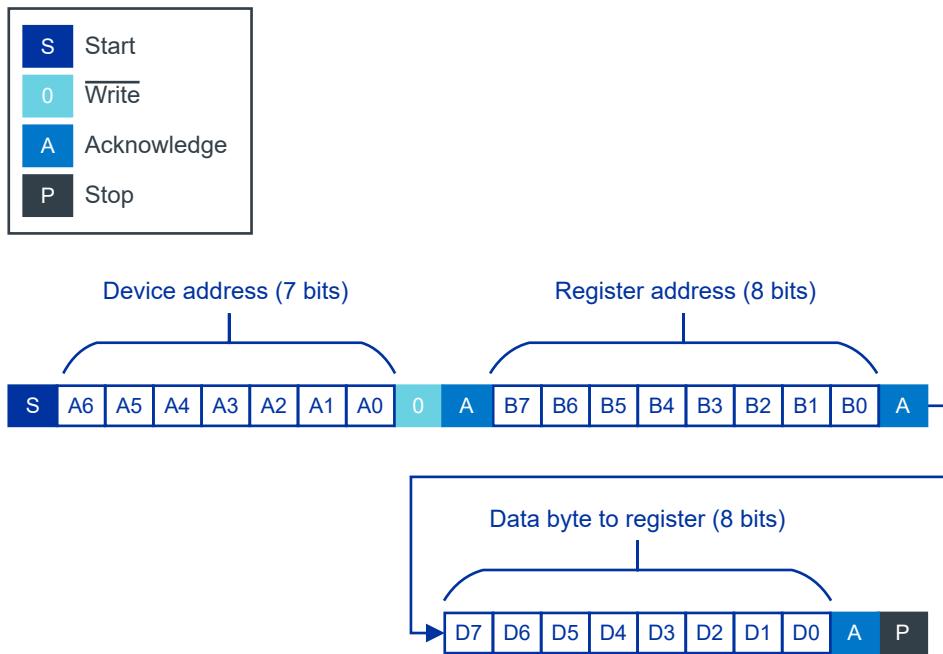

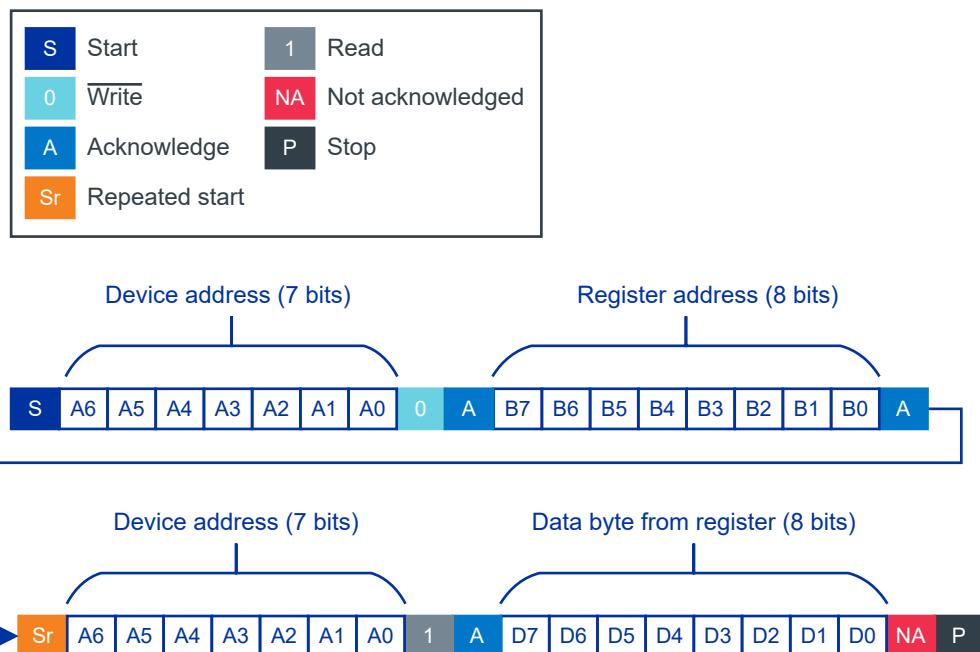

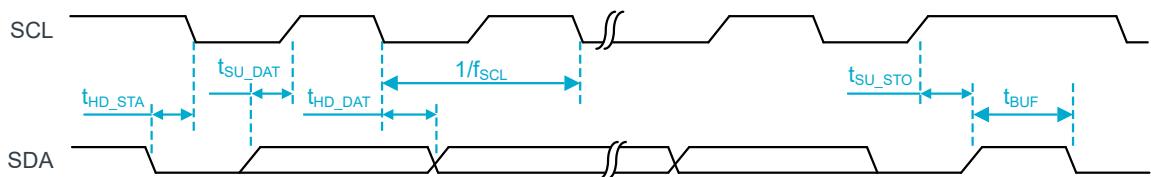

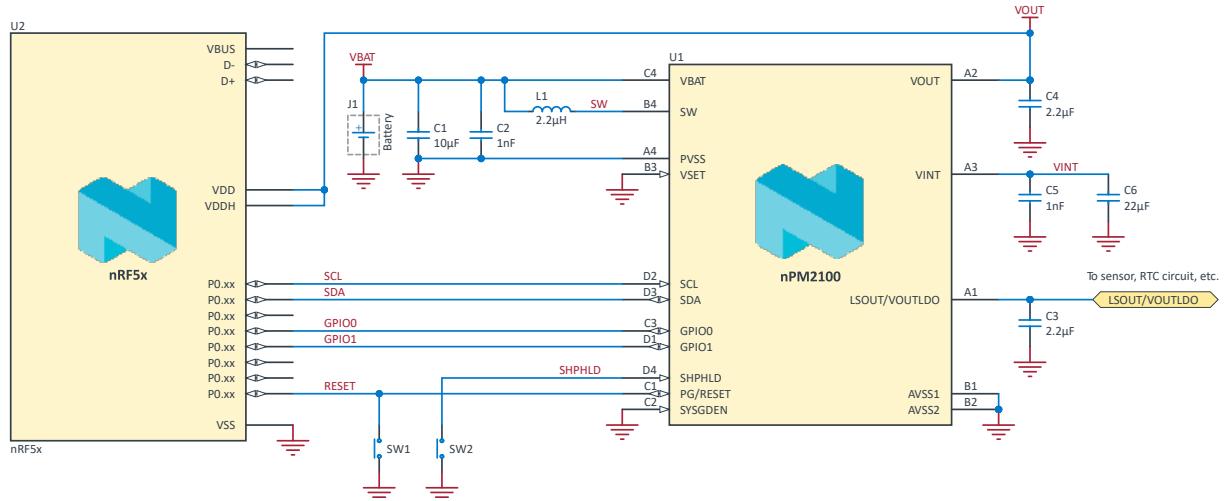

| Symbol                       | Description                                                                                                                          | Min. | Typ.     | Max. | Units |