## MCP1085S

# 十通道多模式宽频数字电容处理器芯片

## 1. 概述

MCP1085S (Mysentech Capacitive Processor) 是敏源传感推出的新一代电容传感微处理器 SOC 芯片，集成了十通道、多模式、宽频电容模拟前端传感电路、微处理器、存储及丰富的 I/O 接口。电容测量频率在 0.1~30MHz 范围内可配置，输出为 16bit 数字信号，最高分辨率为 1fF。芯片支持多种工作模式，可以测量包括单端电容、双端浮空电容和互电容多种模式。芯片内部集成了 16bit 高精度的数字温度传感器，可用于需要温度补偿及其它温度复合传感的场景。

为了解决各行业电容感知的嵌入式处理，SOC 芯片集成了 Arm® Cortex®-M0+ 内核的微处理器，可实现各种感知算法的边缘计算，将原始测量的振荡频率数值，转换成电容值及液位、含水率、位移、接近距离、等具体物理量。芯片内置了 64KB Flash、1KB Data Flash 及 4KB SRAM，可让开发者编写应用软件，并存储传感校准及应用数据。芯片同时集成了 ADC、高级定时器、通用定时器、16 位基本定时器等硬件资源以及 USART 和 I2C 等接口。

## 2. 特性

- 电容检测前端

- 10 路单端电容/5 路双端电容测量

- 电容测量范围：1pF~10nF

- 电容检测频率：100KHz~30MHz

- 电容/频率分辨率：16bit

- 支持有源屏蔽

- 集成了数字测温功能，16bit，0.5°C 典型精度

- 内核与系统

- 32-bit Arm® Cortex®-M0+

- 工作频率可达 48MHz

- 存储器

- 64KB Flash

- 1KB Data Flash

- 4KB SRAM

- 时钟、复位和电源管理

- 2.3V~5.5V 供电

- 上电/断电复位 (POR/PDR)、可编程电压

### 监测器 (PVD)

- 内嵌 48MHz HSI 高速振荡器

- 内嵌 40KHz LSI 低速振荡器

- 低功耗

- 支持低功耗模式，包括：睡眠 (Sleep) 和深度睡眠 (Deep Sleep)

- 平均功耗：6.4uA@1Hz

- 5 个定时器

- 1 个 16 位 4 通道高级控制定时器 (TIM1)

- 1 个 16 位 4 通道通用定时器 (TIM3)

- 1 个 16 位基本定时器 (TIM14)

- 1 个独立时钟的硬件看门狗定时器 (IWDG)

- 1 个 SysTick 定时器：24 位自减型计数器

- 10 个快速 I/O 端口

- 所有 I/O 口可以映像到外部中断

- 所有端口均可输入输出电压不高于 VDD 的信号

- 3 个通信接口

- 2 个 USART 接口

- 1 个 I2C 接口

- 1 个 12 位模数转换器 (ADC)，支持最快 1μs 转换时间(1MSPS 采样率)，配置 5 个外部通道和 1 个可采集内置参考电压的内部通道

- CRC 计算单元

- 96 位芯片唯一 ID (UID)

- 调试模式-串行调试接口 (SWD) 接口

- 工作温度范围-40°C~+85°C

- 单通道转换时间：0.1ms~23.5ms 可配置

- 内置 16bit 高精度数字测温

## 3. 应用

- 液位测量

- 含水率测量

- 干湿度分析

- 水浸传感

- 介电检测

- 接近感知

- 触控按键

### 产品信息

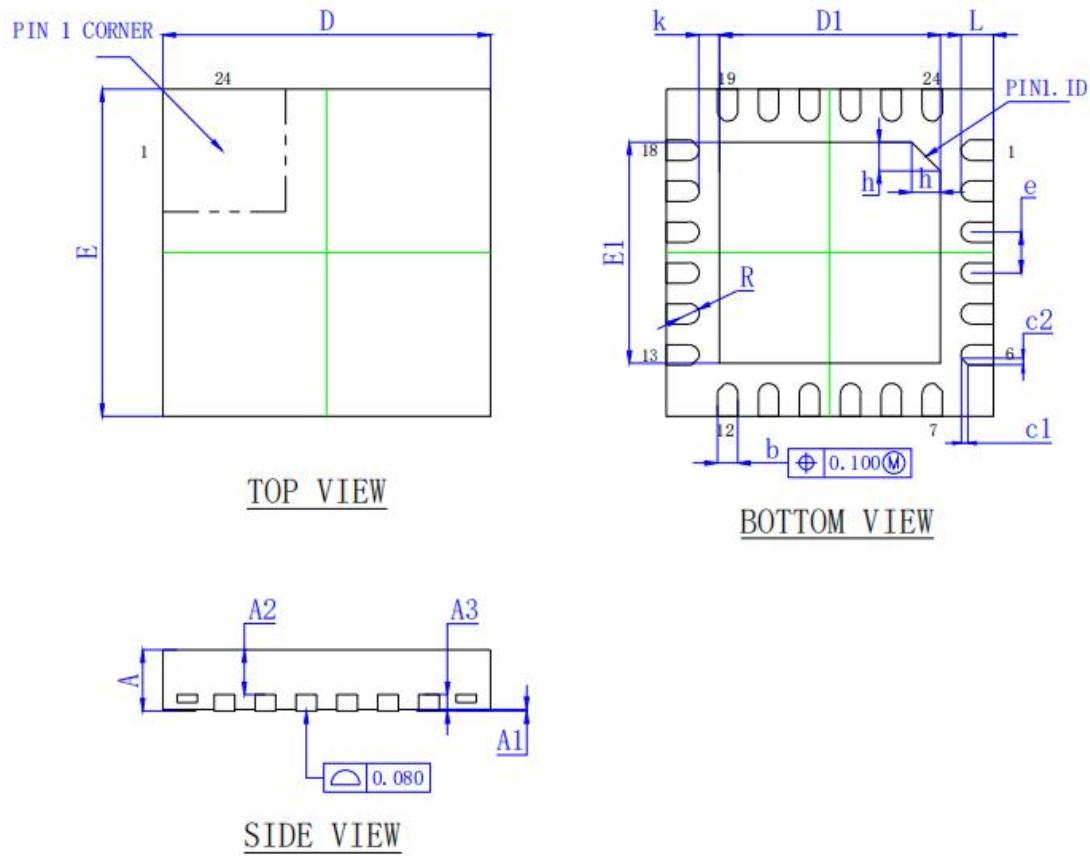

| 型号       | 封装    | 尺寸             |

|----------|-------|----------------|

| MCP1085S | QFN24 | 4.0*4.0*0.75mm |

## 目录

|                             |    |

|-----------------------------|----|

| 1. 概述                       | 1  |

| 2. 特性                       | 1  |

| 3. 应用                       | 1  |

| 4. 封装管脚描述及复用功能              | 4  |

| 4.1 MCP1085S 封装管脚描述 (QFN24) | 4  |

| 4.2 引脚复用                    | 5  |

| 5. 典型应用电路                   | 6  |

| 6. 功能描述                     | 8  |

| 6.1 系统框图                    | 8  |

| 6.2 CAP-AFE                 | 9  |

| 6.3 存储器映像                   | 9  |

| 6.4 NVIC                    | 9  |

| 6.5 EXTI                    | 10 |

| 6.6 MCU 系统时钟                | 10 |

| 6.7 定时器和看门狗                 | 10 |

| 6.8 GPIO                    | 11 |

| 6.9 USART                   | 11 |

| 6.10 I2C                    | 11 |

| 6.11 ADC                    | 12 |

| 6.12 CRC                    | 12 |

| 6.13 SWD                    | 12 |

| 7. 电气特性                     | 12 |

| 7.1 电容测量                    | 12 |

| 7.2 绝对最大额定值                 | 13 |

| 7.3 工作条件                    | 14 |

| 7.3.1 通用工作条件                | 14 |

| 7.3.2 上电和掉电时的工作条件           | 14 |

| 7.3.3 内嵌复位和电源控制模块特性         | 15 |

| 7.3.4 内置的参照电压               | 16 |

| 7.3.5 供电电流特性                | 16 |

| 7.3.6 外部时钟源特性               | 20 |

| 7.3.7 内部时钟源特性               | 20 |

| 7.3.8 存储器特性                 | 21 |

| 7.3.9 EMC 特性                | 22 |

|                              |    |

|------------------------------|----|

| 7.3.10 I/O 端口特性 .....        | 23 |

| 7.3.11 Timer 定时器特性 .....     | 26 |

| 7.3.12 I2C 接口特性 .....        | 27 |

| 7.3.13 USART 接口特性 .....      | 28 |

| 7.3.14 ADC 特性 .....          | 29 |

| 8. CAP_AFE 特征描述 .....        | 30 |

| 8.1 CAP-AFE 时钟系统 .....       | 30 |

| 8.2 电容测量 .....               | 31 |

| 8.3 电容测量模式 .....             | 31 |

| 8.3.1 单端对地电容 .....           | 31 |

| 8.3.2 双端浮空电容 .....           | 32 |

| 8.3.3 互电容 .....              | 32 |

| 8.3.4 电容测量流程 .....           | 33 |

| 8.3.5 单端模式通道选择及端口配置 .....    | 33 |

| 8.3.6 单端模式驱动强度及幅度配置 .....    | 35 |

| 8.3.7 双端模式通道选择及端口配置 .....    | 35 |

| 8.3.8 双端模式驱动强度及幅度配置 .....    | 36 |

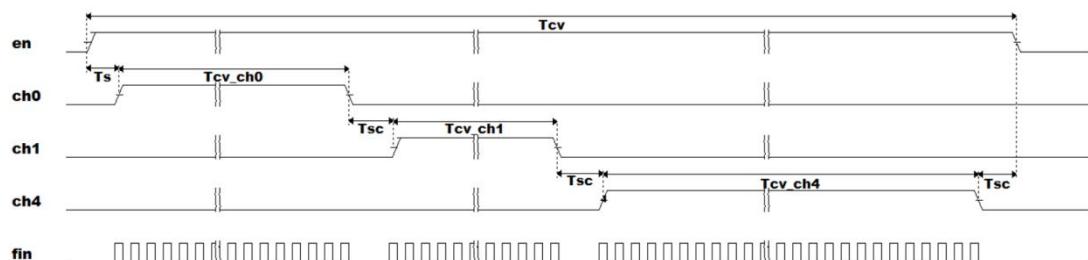

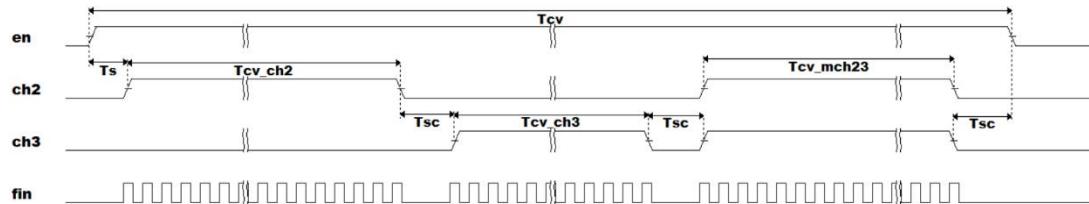

| 8.4 测量及转换时间 .....            | 37 |

| 8.5 状态及溢出 .....              | 40 |

| 8.6 CAP-AFE 时钟配置 .....       | 40 |

| 8.7 数据读取及电容计算 .....          | 42 |

| 8.8 参比电容的选取 .....            | 45 |

| 8.9 有源屏蔽 .....               | 45 |

| 8.10 温度测量 .....              | 46 |

| 8.10.1 测温测量参数配置 .....        | 46 |

| 8.10.2 温度数据格式与计算公式 .....     | 47 |

| 8.11 CAP-AFE 功耗模式与工作模式 ..... | 47 |

| 8.12 CAP-AFE 独立软件复位 .....    | 48 |

| 9. CAP-AFE 工作流程 .....        | 49 |

| 9.1 上电启动 .....               | 49 |

| 9.2 转换模式 .....               | 49 |

| 9.3 休眠与唤醒机制 .....            | 49 |

| 10. 封装 .....                 | 50 |

| 11. 订购须知 .....               | 51 |

## 4. 封装管脚描述及复用功能

### 4.1 MCP1085S 封装管脚描述 (QFN24)

表 4.1 MCP1085S 管脚定义

| QFN24 | Name     | Type <sup>(1)</sup> | I/O level <sup>(2)</sup> | Main function             | Multiplex function                  | Additional function |

|-------|----------|---------------------|--------------------------|---------------------------|-------------------------------------|---------------------|

| 1     | PA1/U2TX | I/O                 | TC                       | PA1                       | USART1_SCK<br>USART2_TX<br>I2C1_SDA | -                   |

| 2     | VDD      | P                   | -                        | Power                     | -                                   | -                   |

| 3     | GNDA     | G                   | -                        | Analog Ground             | -                                   | -                   |

| 4     | C9       | A                   | -                        | Channel 9 capacitor input | -                                   | -                   |

| 5     | C8       | A                   | -                        | Channel 8 capacitor input | -                                   | -                   |

| 6     | C7       | A                   | -                        | Channel 7 capacitor input | -                                   | -                   |

| 7     | C6       | A                   | -                        | Channel 6 capacitor input | -                                   | -                   |

| 8     | C5       | A                   | -                        | Channel 5 capacitor input | -                                   | -                   |

| 9     | C4       | A                   | -                        | Channel 4 capacitor input | -                                   | -                   |

| 10    | C3       | A                   | -                        | Channel 3 capacitor input | -                                   | -                   |

| 11    | C2       | A                   | -                        | Channel 2 capacitor input | -                                   | -                   |

| 12    | C1       | A                   | -                        | Channel 1 capacitor input | -                                   | -                   |

| 13    | C0       | A                   | -                        | Channel 0 capacitor input | -                                   | -                   |

| 14    | SHLD     | O                   | -                        | Conditional output        | -                                   | -                   |

|    |                           |     |       | shielding |                                                                    |             |

|----|---------------------------|-----|-------|-----------|--------------------------------------------------------------------|-------------|

| 15 | PA5                       | I/O | TC+HS | PA5       | TIM1_CH1N<br>I2C1_SCL                                              | -           |

| 16 | PA7                       | I/O | TC+HS | PA7       | TIM1_CH1N<br>TIM1_CH2N<br>MCO<br>TIM1_CH4                          | ADC1_VIN[7] |

| 17 | PA8                       | I/O | TC+CC | PA8       | TIM1_CH2<br>I2C1_SDA<br>TIM3_CH1                                   | -           |

| 18 | PA13                      | I/O | TC    | PA13      | SWDIO<br>USART1_RX<br>USART2_RX<br>I2C1_SCL                        | -           |

| 19 | GND                       | G   | -     | Ground    | -                                                                  | -           |

| 20 | PA11                      | I/O | TC+CC | PA11      | USART2_NR<br>TS<br>USART1_SCK<br>TIM1_CH2<br>TIM14_CH1<br>TIM3_CH1 | ADC1_VIN[4] |

| 21 | PA12                      | I/O | TC+CC | PA12      | USART1_TX                                                          | ADC1_VIN[3] |

| 22 | PA3                       | I/O | TC+CC | PA3       | USART1_RX<br>USART2_SCK                                            | ADC1_VIN[2] |

| 23 | PA14(NRST) <sup>(3)</sup> | I/O | TC    | PA14      | SWCLK<br>USART1_TX<br>USART2_TX                                    | -           |

| 24 | PB1                       | I/O | TC    | PB1       | USART2_RX<br>USART1_NR<br>TS                                       | ADC1_VIN[0] |

备注 1: I=输入, O=输出, P=电源, G=地, A=模拟

备注 2: TC: 标准 IO, 输入信号不超过 VDD 电压; CC: 可配置为恒流源模式的 IO; HS: 可配置为灌电流模式的 IO

备注 3: 当 RCC\_SYSCFG 的 SFT\_NRST\_RMP 位被设置为 1 时, PA14 被映射为 NRST 外部复位, 且复位时低电平至少保持 4us。

## 4.2 引脚复用

表 4.2-1 PA 端口功能复用 AF0-AF4

| Pin | AF0 | AF1        | AF2        | AF3      | AF4 |

|-----|-----|------------|------------|----------|-----|

| PA1 | -   | USART1_SCK | USART2_TX  | I2C1_SDA | -   |

| PA3 | -   | USART1_RX  | USART2_SCK | -        | -   |

| PA5 | -   | TIM1_CH1N  | -          | I2C1_SCL | -   |

|      |             |            |           |           |          |

|------|-------------|------------|-----------|-----------|----------|

| PA7  | -           | TIM1_CH1N  | TIM1_CH2N | MCO       | TIM1_CH4 |

| PA8  | -           | TIM1_CH2   | -         | I2C1_SDA  | TIM3_CH1 |

| PA11 | USART2_NRTS | USART1_SCK | TIM1_CH2  | TIM14_CH1 | TIM3_CH1 |

| PA12 | -           | USART1_TX  | -         | -         | -        |

| PA13 | SWDIO       | USART1_RX  | USART2_RX | I2C1_SCL  | -        |

| PA14 | SWCLK       | USART1_TX  | USART2_TX | -         | -        |

表 4.2-2 PB 端口功能复用 AF0-AF4

| Pin | AF0 | AF1 | AF2       | AF3         | AF4 |

|-----|-----|-----|-----------|-------------|-----|

| PB1 | -   | -   | USART2_RX | USART1_NRTS | -   |

## 5. 典型应用电路

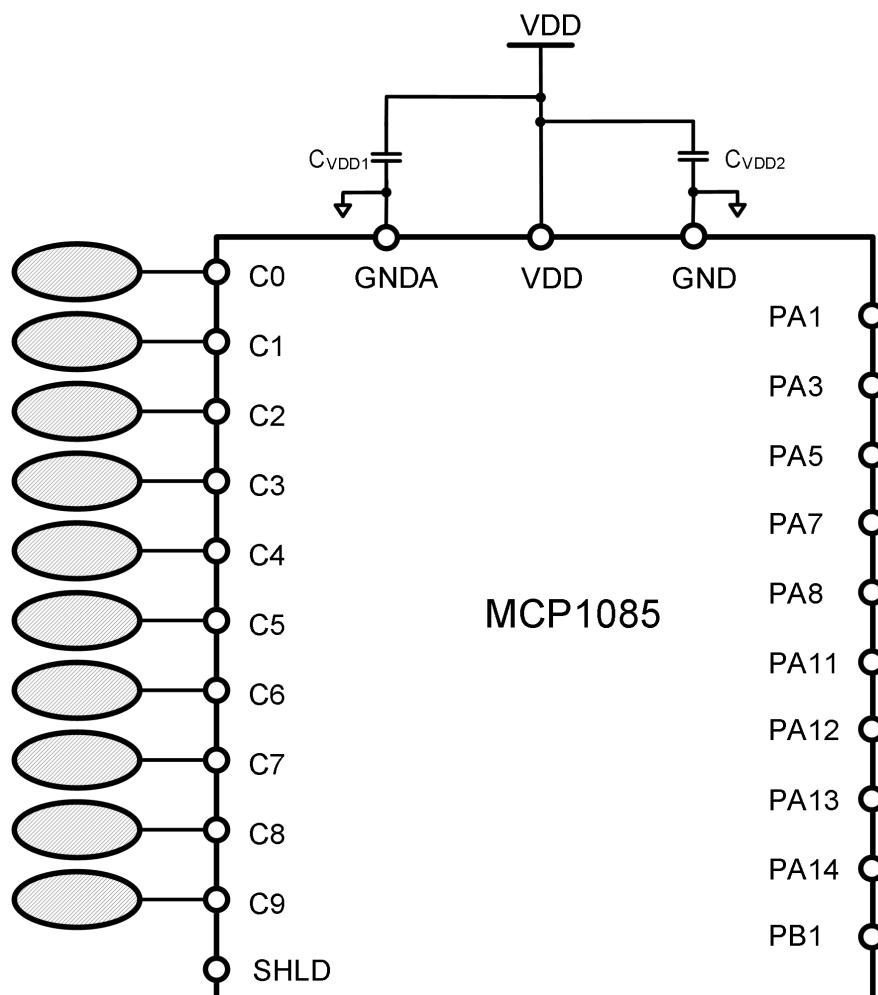

MCP1085 的单端模式典型应用电路如下：

图 5.1 单端模式典型应用电路

其中管脚 C0 至 C9 连接单端电极，选取内部 20pF 作为参比电容。图中管脚分配仅为一种示例。在实际应用中，可以根据需要，分配管脚连接单端电极、互电容电极或者外接电容。具体说明参见章节 8.3。图中 VDD 滤波电容 CVDD1 和 CVDD2 的取值范围为 100nF 至 10uF，两个 GND 管脚都需要接地。

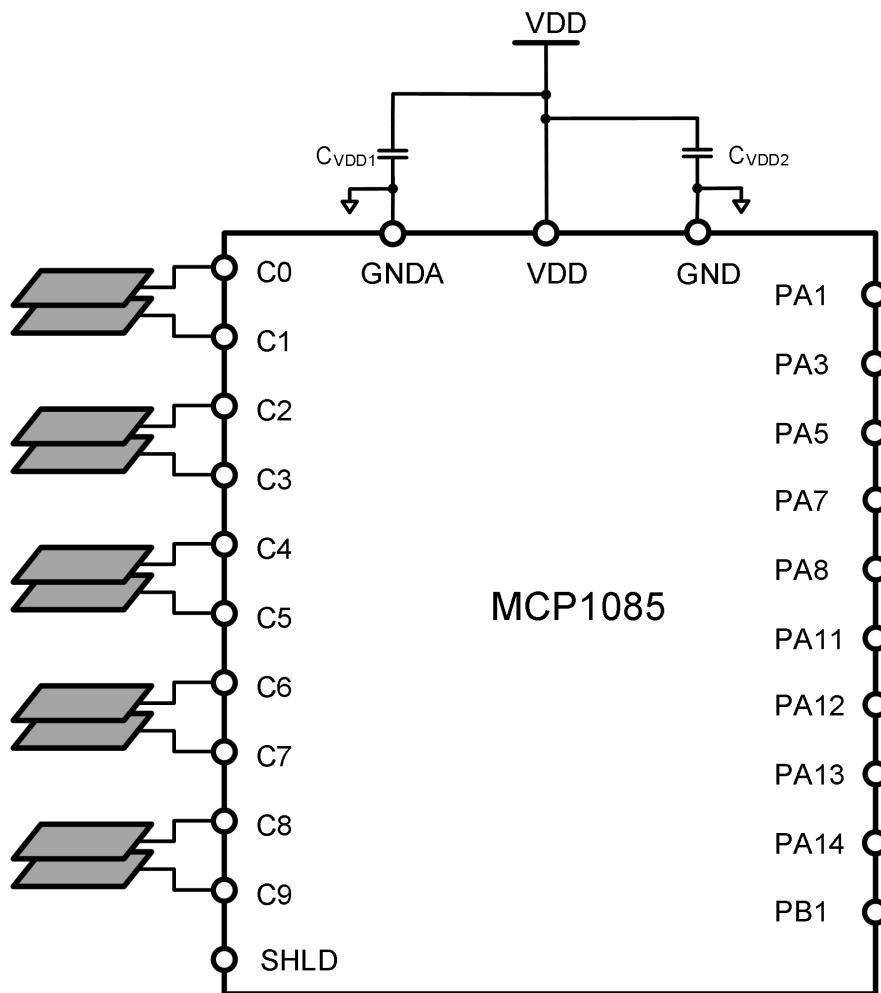

MCP1085 的双端模式典型应用电路如下：

图 5.2 双端模式典型应用电路

其中管脚 C0 和 C1、C2 和 C3、C4 和 C5、C6 和 C7、C8 和 C9 接双端电极，选取内部 20pF 作为参比电容。在实际应用中，可以根据需要，分配管脚连接双端电极或者外接电容。具体说明参见章节 8.3。图中 VDD 滤波电容 CVDD1 和 CVDD2 的取值范围为 100nF 至 10uF，两个 GND 管脚都需要接地。

## 6. 功能描述

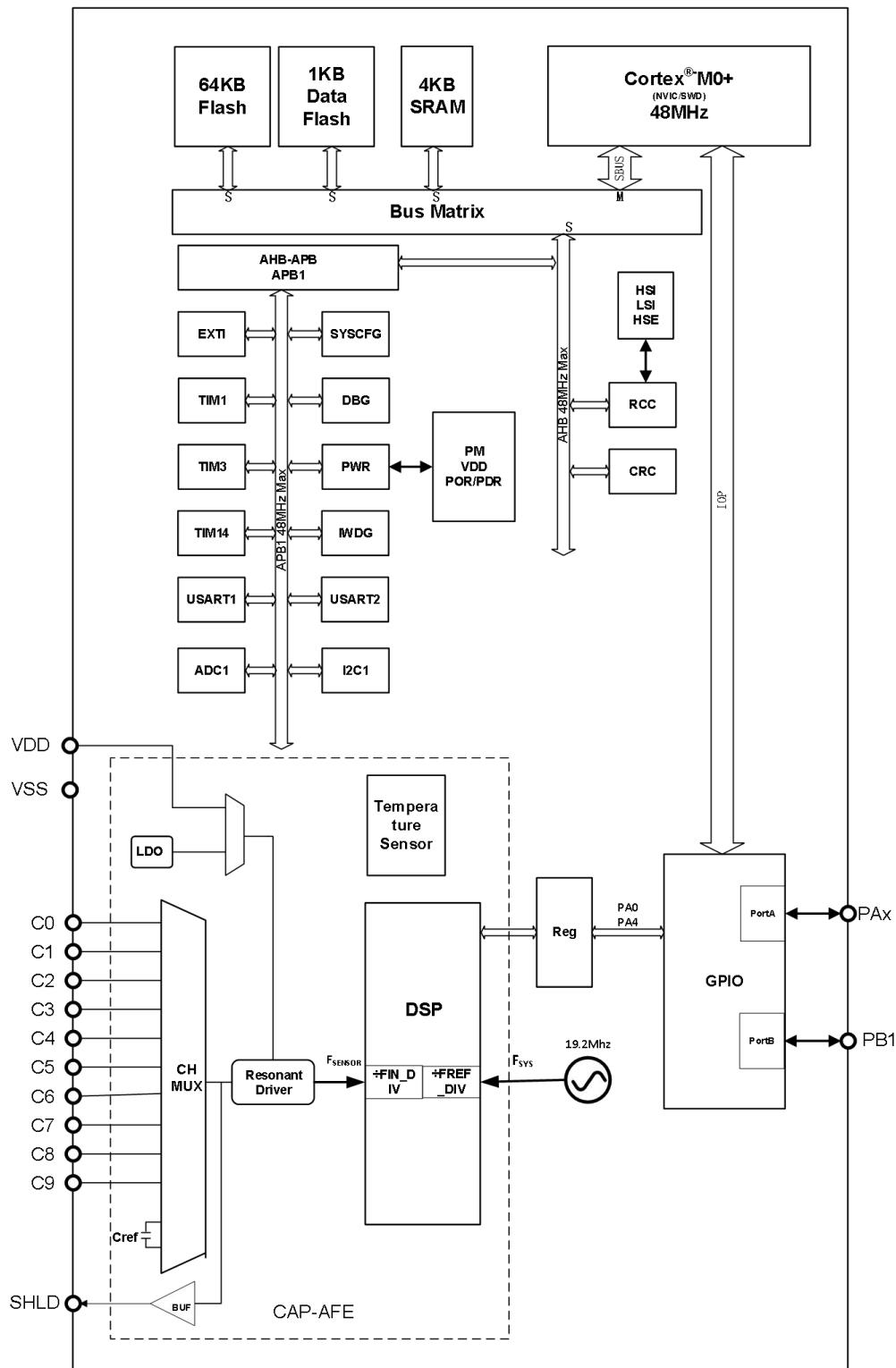

### 6.1 系统框图

图 6.1 系统框图

## 6.2 CAP-AFE

参见图 6.1，芯片内置了高集成度、多通道、宽量程的电容传感电路，最多可同时测量 10 路单端电容，或者 5 路双端电容。可根据应用需求直接与被测物附近的电容极板相连，通过测量振荡频率，解算被测目标的电容。AFE 通过内部模拟时钟配置不同分频比来提供基准。内部集成了 16bit 高精度数字温度传感器，处理器端口 PA0、PA4 用于在芯片内部与电容传感 AFE 之间进行 I2C 通讯。

## 6.3 存储器映像

表 6.3 存储器映像

| BUS   | Address range           | Size  | Peripheral        |

|-------|-------------------------|-------|-------------------|

| Flash | 0x08000000 - 0x0800FFFF | 64 KB | Main Flash memory |

|       | 0x1FFE0000 - 0x1FFE03FF | 1 KB  | 数据存储区             |

| SRAM  | 0x20000000 - 0x20000FFF | 4 KB  | SRAM              |

| APB1  | 0x40000400 - 0x400007FF | 1 KB  | TIM3              |

|       | 0x40003000 - 0x400033FF | 1 KB  | IWDG              |

|       | 0x40004400 - 0x400047FF | 1 KB  | USART2            |

|       | 0x40005400 - 0x400057FF | 1 KB  | I2C1              |

|       | 0x40007000 - 0x400073FF | 1 KB  | PWR               |

|       | 0x40010000 - 0x400103FF | 1 KB  | SYSCFG            |

|       | 0x40010400 - 0x400107FF | 1 KB  | EXTI              |

|       | 0x40012400 - 0x400127FF | 1 KB  | ADC1              |

|       | 0x40012C00 - 0x40012FFF | 1 KB  | TIM1              |

|       | 0x40013000 - 0x400133FF | 1 KB  | 保留                |

|       | 0x40013400 - 0x400137FF | 1 KB  | DBG               |

|       | 0x40013800 - 0x40013BFF | 1 KB  | USART1            |

|       | 0x40014000 - 0x400143FF | 1 KB  | TIM14             |

|       | 0x40014400 - 0x400147FF | 1 KB  | COMP              |

| AHB   | 0x40021000 - 0x400213FF | 1 KB  | RCC               |

|       | 0x40022000 - 0x400223FF | 1 KB  | Flash Interface   |

|       | 0x40023000 - 0x400233FF | 1 KB  | CRC               |

| IOP   | 0x50000000 - 0x500003FF | 1 KB  | GPIOA             |

|       | 0x50000400 - 0x500007FF | 1 KB  | GPIOB             |

## 6.4 NVIC

芯片内置嵌套的向量式中断控制器能够处理多个可屏蔽中断通道和 4 个可编程优先级。

## 6.5 EXTI

外部中断/事件控制器 (EXTI) 包含多个边沿检测器，用于捕获来自 IO 引脚的电平变化，进而产生中断/事件请求。所有 IO 引脚可以连接到外部中断线。每个中断线均可独立开关，或启用各自的触发模式（上升沿、下降沿或双边沿）。一个挂起状态寄存器将会维持所有中断请求的状态。EXTI 可以检测到脉冲宽度小于内部 APB 总线时钟周期的电平变化。

## 6.6 MCU 系统时钟

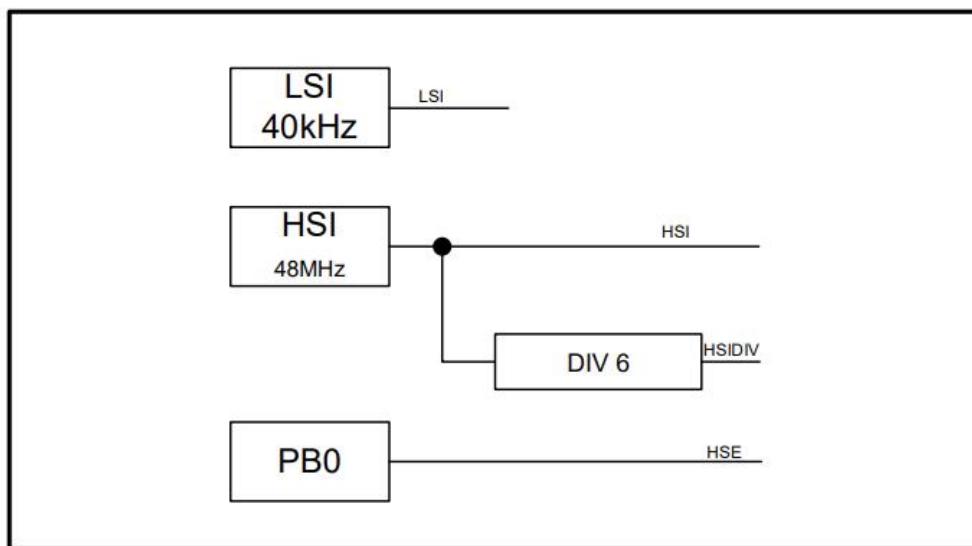

如图 6.6 所示，芯片包含以下内部或外部时钟源：

- HSI 48MHz

- LSI 40KHz

- HSE

图 6.6 系统时钟源

系统时钟可从以下内部或外部时钟选择：

- HSI – HSI 48MHz 输出

- HSIDIV – HSI 48MHz 的 6 分频输出，即 8MHz 输出

- LSI – LSI 40KHz 输出

- HSE – 从 OSC\_IN (PB0) 引脚的外部时钟输入

系统时钟分频后可作为 CPU 和 AHB 总线时钟，CPU 和 AHB 总线的最高工作频率为 48MHz。APB 总线的最高工作频率和 AHB 总线相同。在复位后，首先使用 HSIDIV (8MHz) 作为默认的系统时钟，随后可选择使用 HSI、LSI 或 HSE 作为时钟源。

## 6.7 定时器和看门狗

芯片包含 1 个高级定时器、1 个通用定时器、1 个基本定时器、1 个看门狗定时器和 1 个系

---

统时基定时器。

高级控制定时器 (TIM1) 是由 16 位计数器、4 个比较通道以及三相互补 PWM 发生器组成，它具有带死区插入的互补 PWM 输出，还可以被当成完整的通用定时器。

通用定时器 (TIM3) 产品中内置了 1 个 16 位通用定时器 (TIM3)。定时器有一个 16 位的自动加载递加/递减计数器、一个 16 位的预分频器和 4 个独立的通道，每个通道都可用于输入捕获、输出比较、PWM 和单脉冲模式输出。

基本定时器 (TIM14) 产品中内置 1 个基本定时器 (TIM14)，每个定时器有一个 16 位计数器，支持自动重载，仅支持递增计数。定时器有一个 16 位预分频器和 1 个独立通道，每个通道可用于输入捕捉、输出比较、PWM 输出或单脉冲输出。

独立看门狗 (IWDG) 独立的看门狗是基于一个 12 位的递减计数器和一个 8 位的预分频器，它由一个内部独立的 40KHz 的振荡器提供时钟。因为这个振荡器独立于主时钟，所以它可运行于停机和待机模式。它可以在系统发生问题时复位整个系统或作为一个自由定时器为应用程序提供超时管理。

系统时基定时器 (Systick) 这个定时器是专用于实时操作系统，也可当成一个标准的递减计数器。它具有下述特性：

- 24 位的递减计数器

- 自动重加载功能

- 当计数器为 0 时能产生一个可屏蔽系统中断

- 可编程时钟源

## 6.8 GPIO

每个 GPIO 引脚都可以由软件配置成输出（推挽或开漏）、输入（带或不带上拉或下拉）或复用的外设功能端口。多数 GPIO 引脚都与数字或模拟的复用外设共用。在需要的情况下，I/O 引脚的外设功能可以通过一个特定的操作锁定，以避免意外的写入 I/O 寄存器。

该芯片最多可为 2 个 8 段式共阴极 LED 数码管提供驱动，以节省外部硬件开销。GPIOA 中最多可配置 2 个特定 IO 为灌电流模式（最大 80mA），用于控制数码管阴极；最多可配置 4 个特定 IO 为恒流源模式（可配置为 2.5/5/7.5/10mA 四档），用于控制数码管段选。

## 6.9 USART

芯片内置 2 个通用同步/异步接收器/发送器 (USART) 接口。USART 为使用行业标准 NRZ 异步串行数据格式的外设提供全双工数据交换的灵活性。该模块可通过集成的波特率发生器支持广泛的波特率（包括整数和小数设置）。支持 LSB、MSB 收发模式，支持 8 位或 9 位可编程数据长度，支持 0.5/1/1.5/2 位停止位配置。支持同步或异步单向通信和半双工单线通信。支持最高 6Mbps 波特率。

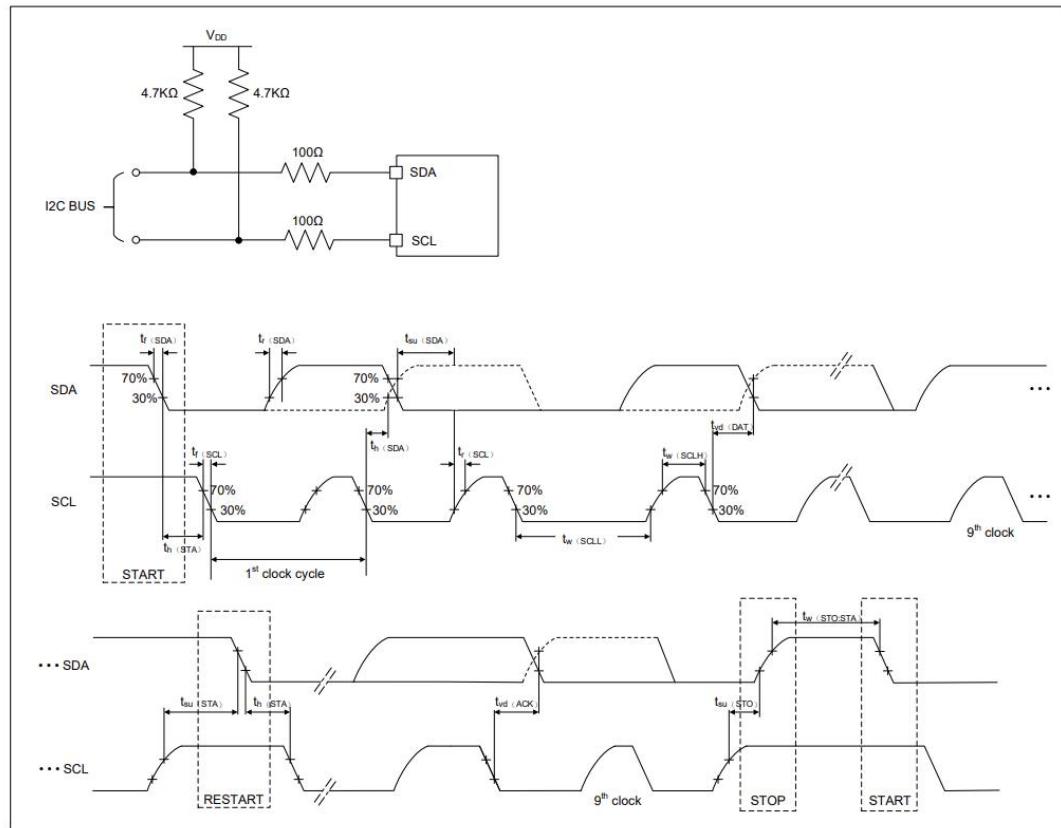

## 6.10 I2C

芯片中内嵌 1 个 I2C 接口，能够工作于多主模式或从模式，支持标准模式 (100Kbps) 和

快速模式 (400Kbps)。支持 7 位或 10 位寻址。

## 6.11 ADC

芯片内嵌 1 个 12 位的模拟/数字转换器 (ADC)，支持高达 1Msps 转换速率，芯片可至多配置 5 个外部通道和 1 个内部通道。

## 6.12 CRC

CRC (循环冗余校验) 计算单元使用一个固定的多项式发生器，从一个 32 位的数据字产生一个 CRC 码。在众多的应用中，基于 CRC 的技术被用于验证数据传输或存储的一致性。在 EN/IEC60335-1 标准的范围内，它提供了一种检测闪存存储器错误的手段，CRC 计算单元可以用于实时地计算软件的签名，并与在链接和生成该软件时产生的签名对比。

## 6.13 SWD

内嵌 Arm 标准的两线串行调试接口 (SW-DP)。

# 7. 电气特性

## 7.1 电容测量

芯片电容测量的电气特性如下表，除非特殊说明，表中数据条件为 T=25°C。

表 7.1-1 电源供电

| Symbol             | Parameter                                 | Conditions            | Min  | Typ. | Max  | Unit |

|--------------------|-------------------------------------------|-----------------------|------|------|------|------|

| Power              |                                           |                       |      |      |      |      |

| V <sub>DD</sub>    | Supply voltage                            | T = -40°C to +85°C    | 2.3  |      | 5.5  | V    |

| I <sub>VDD</sub>   | Measuring peak current <sup>(1)</sup>     | Single-Terminal Mode  | 0.63 |      | 3.35 | mA   |

|                    |                                           | Double-Terminals Mode | 0.93 |      | 2.75 | mA   |

| I <sub>DDAVG</sub> | Average conversion current <sup>(2)</sup> | V <sub>DD</sub> =5V   |      | 6.4  |      | uA   |

| I <sub>DDSL</sub>  | Sleep mode current                        | V <sub>DD</sub> =5V   |      | 2    |      | uA   |

备注 1：测量峰值电流，表示 CAP AFE 测量时的工作电流。

备注 2：平均转换电流的测试条件是 1s 转换一次，驱动电流为 4uA，转换时长为 1ms，LDO 配置为低功耗模式；转换完成后，芯片进入睡眠模式。

表 7.1-2 CAP AFE

| Symbol              | Parameter                 | Conditions | Min   | Typ. | Max | Unit |

|---------------------|---------------------------|------------|-------|------|-----|------|

| Capacitive sensing  |                           |            |       |      |     |      |

| C <sub>SENSOR</sub> | Measured capacitance      |            | 0.001 |      | 10  | nF   |

| C <sub>IN</sub>     | Pin parasitic capacitance |            |       | 5    |     | pF   |

| N <sub>BITS</sub>   | Data bits                 |            |       |      | 16  | Bit  |

|                       |                                  |                                                    |      |      |      |        |

|-----------------------|----------------------------------|----------------------------------------------------|------|------|------|--------|

| $f_{cs}$              | Channel sampling rate            |                                                    | 0.01 |      | 2    | kSPS   |

| <b>Oscillator</b>     |                                  |                                                    |      |      |      |        |

| $f_{SENSOR}$          | Oscillator frequency range       | $T = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | 0.1  |      | 30   | MHz    |

| $I_{DRIVE}$           | Oscillator driving current       | single channel                                     | 4    |      | 2000 | uA     |

| <b>Internal clock</b> |                                  |                                                    |      |      |      |        |

| $f_{INTCLK}$          | Internal clock frequency         | $T = 25^{\circ}\text{C}$                           |      | 19.2 |      | MHz    |

| $TC_{INTCLK}$         | Internal clock temperature drift | $T = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ |      | 25   | 100  | ppm/°C |

## 7.2 绝对最大额定值

加在器件上的载荷如果超过“绝对组最大额定值”列表（表 7.2-1、表 7.2-2、表 7.2-3）中给出的值，可能会导致器件永久性地损坏。这里只是给出能承受的最大载荷，并不意味在此条件下器件的功能性操作无误。器件长期工作在最大值条件下会影响器件的可靠性。

表 7.2-1 电压特性

| Symbol             | Description                  | Minimum | Maximum | Unit |

|--------------------|------------------------------|---------|---------|------|

| VDD – GND          | External main supply voltage | -0.3    | 5.8     | V    |

| VDD – GNDA         |                              |         |         |      |

| VIN <sup>(1)</sup> | Input voltage on other pins  | GND-0.3 | VDD+0.3 |      |

备注 1：必须始终遵循 VIN 的最大值。有关允许的最大注入电流值的信息，请参见下表。

表 7.2-2 电流特性

| Symbol                    | Description                                                                 | Maximum | Unit |

|---------------------------|-----------------------------------------------------------------------------|---------|------|

| $I_{VDD}^{(1)}$           | Total current through VDD power pins (supply current) <sup>(1)</sup>        | +100    | mA   |

| $I_{GND}/V_{GNDA}^{(1)}$  | Total current through GND/GNDA ground pins (outflow current) <sup>(1)</sup> | -100    |      |

| $I_{IO}$                  | Output sink current on general mode I/O and control pins                    | +20     | mA   |

|                           | Output source current on general mode I/O and control pins                  | -20     |      |

|                           | Output sink current on high sink mode I/O                                   | +80     |      |

| $I_{INJ(PIN)}^{(2)(3)}$   | NRST pin injection current                                                  | ±5      |      |

|                           | HSE OSC_IN pin injection current                                            | ±5      |      |

| $\sum I_{INJ(PIN)}^{(5)}$ | Other pins injection current <sup>(4)</sup>                                 | ±25     |      |

备注 1：在允许的范围内，所有主电源 ( $V_{DD}$ ) 和接地 (GND、GNDA) 引脚必须始终连接到外部电源。

备注 2：此电流消耗必须正确分布至所有 I/O 和控制引脚。总输出电流一定不能在参考高引脚数 LQFP 封装的两个连续电源引脚间灌/拉。

备注 3：反向注入电流会干扰器件的模拟性能。

备注 4：当  $V_{IN} > V_{DD}$  时，会产生正向注入电流；当  $V_{IN} < GND/GNDA$  时，会产生反向注入电流。不得超出  $I_{INJ(PIN)}$ 。

备注 5：当多个输入同时存在注入电流时， $\Sigma I_{INJ(PIN)}$  的最大值等于正向注入电流和反向注入电流（瞬时值）的绝对值之和。

表 7.2-3 温度特性

| Symbol    | Description          | Minimum | Maximum | Unit |

|-----------|----------------------|---------|---------|------|

| $T_J$     | Junction temperature | -40     | 105     | °C   |

| $T_{stg}$ | Storage temperature  | -40     | 105     | °C   |

备注：以上为极限参数，对于器件在超出此极限条件的环境中的功能运行，本规格书并不适用。长期暴露于此极限环境会影响器件的可靠性。

## 7.3 工作条件

### 7.3.1 通用工作条件

表 7.3.1 通用工作条件

| Symbol      | Parameter                                                                           | Conditions | Min. | Typ. | Max. | Unit |

|-------------|-------------------------------------------------------------------------------------|------------|------|------|------|------|

| $f_{HCLK}$  | Internal AHB clock frequency                                                        | -          | -    | -    | 48   | MHz  |

| $f_{PCLK1}$ | Internal APB1 clock frequency                                                       | -          | -    | -    | 48   |      |

| $V_{DD}$    | Digital and Analog circuit operating voltage (Analog performance is not guaranteed) | -          | 2.0  | -    | 2.5  | V    |

|             | Analog circuit operating voltage (Performance is guaranteed)                        | -          | 2.5  | 3.3  | 5.5  |      |

| $T_A$       | Ambient temperature (Industrial level)                                              | -          | -40  | -    | 85   | °C   |

|             | Ambient temperature (Extended industrial level)                                     | -          | -40  | -    | 85   |      |

### 7.3.2 上电和掉电时的工作条件

下表中给出的参数是在表 7.3.1 通用的工作条件下测试得出。

表 7.3.2 上电和掉电时的工作条件

| Symbol         | Conditions                   | Min. | Typ. | Max.   | Unit |

|----------------|------------------------------|------|------|--------|------|

| $t_{VDD}$      | $V_{DD}$ rise time $t_r$     | 2    | -    | 500000 | us   |

|                | $V_{DD}$ fall time $t_f$     | 300  | -    | -      |      |

| $V_{ft}^{(3)}$ | Power-down threshold voltage | -    | 200  | -      | mV   |

备注 1：由综合评估得出，不在生产中测试。

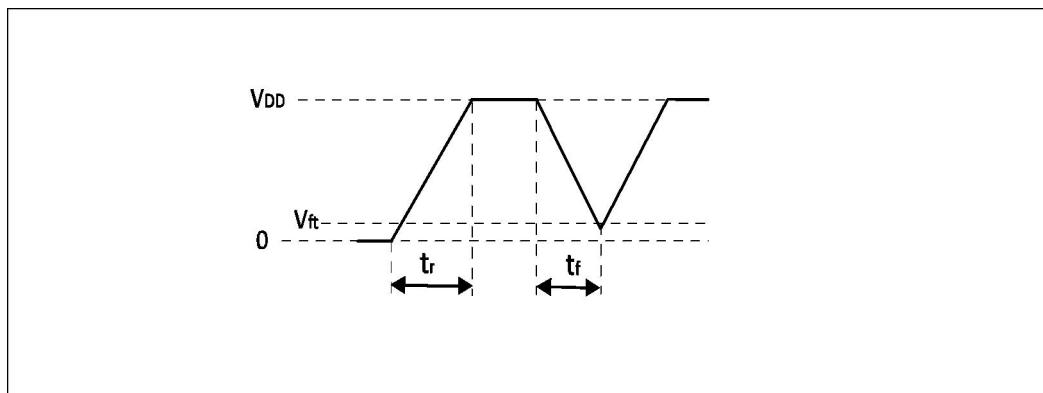

备注 2：芯片上与掉电  $V_{DD}$  波形需严格遵循以下波形图中  $t_r$  和  $t_f$  阶段，上电过程不得出现掉电现象

备注 3：为确保芯片可以可靠上电，所有上电需要从 200mV 开始。

图 7.3.2 上电与掉电波形

### 7.3.3 内嵌复位和电源控制模块特性

下表中给出的参数是依据表 7.3.1 列出的环境温度下和  $V_{DD}$  供电电压下测试得出。

表 7.3.3 内嵌复位和电源控制模块特性

| Symbol    | Parameter                                         | Condition                    | Min. <sup>(3)</sup> | Typ. | Max. <sup>(3)</sup> | Unit |

|-----------|---------------------------------------------------|------------------------------|---------------------|------|---------------------|------|

| $V_{PVD}$ | Level selection of programmable voltage detectors | PLS[3:0]=0000 (Rising edge)  | -                   | -    | -                   | V    |

|           |                                                   | PLS[3:0]=0000 (Falling edge) | -                   | -    | -                   |      |

|           |                                                   | PLS[3:0]=0001 (Rising edge)  | -                   | 2.1  | -                   |      |

|           |                                                   | PLS[3:0]=0001 (Falling edge) | -                   | 2.0  | -                   |      |

|           |                                                   | PLS[3:0]=0010 (Rising edge)  | -                   | 2.4  | -                   |      |

|           |                                                   | PLS[3:0]=0010 (Falling edge) | -                   | 2.3  | -                   |      |

|           |                                                   | PLS[3:0]=0011 (Rising edge)  | -                   | 2.7  | -                   |      |

|           |                                                   | PLS[3:0]=0011 (Falling edge) | -                   | 2.6  | -                   |      |

|           |                                                   | PLS[3:0]=0100 (Rising edge)  | -                   | 3.0  | -                   |      |

|           |                                                   | PLS[3:0]=0100 (Falling edge) | -                   | 2.9  | -                   |      |

|           |                                                   | PLS[3:0]=0101 (Rising edge)  | -                   | 3.3  | -                   |      |

|           |                                                   | PLS[3:0]=0101 (Falling edge) | -                   | 3.2  | -                   |      |

|           |                                                   | PLS[3:0]=0110 (Rising edge)  | -                   | 3.6  | -                   |      |

|           |                                                   | PLS[3:0]=0110 (Falling edge) | -                   | 3.5  | -                   |      |

|           |                                                   | PLS[3:0]=0111 (Rising edge)  | -                   | 3.9  | -                   |      |

|           |                                                   | PLS[3:0]=0111 (Falling edge) | -                   | 3.8  | -                   |      |

|           |                                                   | PLS[3:0]=1000 (Rising edge)  | -                   | 4.2  | -                   |      |

|                      |                  |                              |   |       |   |    |

|----------------------|------------------|------------------------------|---|-------|---|----|

|                      |                  | PLS[3:0]=1000 (Falling edge) | - | 4.1   | - |    |

|                      |                  | PLS[3:0]=1001 (Rising edge)  | - | 4.5   | - |    |

|                      |                  | PLS[3:0]=1001 (Falling edge) | - | 4.4   | - |    |

|                      |                  | PLS[3:0]=1010 (Rising edge)  | - | 4.8   | - |    |

|                      |                  | PLS[3:0]=1010 (Falling edge) | - | 4.7   | - |    |

| $V_{POR}^{(1)}$      | Power-on reset   | -                            | - | 1.805 | - | V  |

| $V_{PDR}^{(1)}$      | Power-down reset | -                            | - | 1.763 | - | V  |

| $V_{hyst\_PDR}$      | PDR hysteresis   | -                            | - | 42    | - | mV |

| $T_{RSTTEMPO}^{(2)}$ | Reset duration   | -                            | - | 3.6   | - | ms |

备注 1：产品的特性由设计保证至最小的数值  $V_{POR/PDR}$ 。

备注 2：由设计保证，不在生产中测试。

备注 3：由综合评估得出。复位持续时间的测量方法为从上电 (POR 复位) 到用户应用代码第一个 IO 翻转的时刻。

### 7.3.4 内置的参照电压

下表中给出的参数是依据表 7.3.1 列出的环境温度下和  $V_{DD}$  供电电压下测试得出。

表 7.3.4 内置的参照电压

| Symbol                 | Parameter                                       | Conditions                                             | Min. | Typ. | Max. | Unit |

|------------------------|-------------------------------------------------|--------------------------------------------------------|------|------|------|------|

| $V_{REFINT}$           | Built-in voltage reference                      | $-40^{\circ}\text{C} < \text{TA} < 85^{\circ}\text{C}$ | -    | 1.2  | -    | V    |

| $T_{s\_vrefint}^{(1)}$ | ADC sampling time when readout build-in voltage | -                                                      | -    | 2    | -    | us   |

备注 1. 最短的采样时间是通过应用中的多次循环得到。

### 7.3.5 供电电流特性

电流消耗是多种参数和因素的综合指标，这些参数和因素包括工作电压、环境温度、I/O 引脚的负载、产品的软件配置、工作频率、I/O 脚的翻转速率、程序在存储器中的位置以及执行的代码等。

本节中给出的所有运行模式下的电流消耗测量值，都是在执行一套精简的代码（停止电容测量部分）。

#### 电流消耗

微控制器处于下列条件：

所有的 I/O 引脚都处于输入模式，并连接到一个静态电平上— $V_{DD}$  或 GND（无负载）。

所有的外设都处于关闭状态，除非特别说明。

Flash 存储器的访问时间调整到  $f_{HCLK}$  的频率 (0~24 MHz 时为 0 个等待周期, 24~48MHz 时为 1 个等待周期)。

指令预取功能开启。当开启外设时:  $f_{HCLK}=f_{PCLK}$ 。

注: 指令预取功能必须在设置时钟和总线分频之前设置。

下表中给出的参数, 是依据表 7.3.1 列出的环境温度下和  $V_{DD}$  供电电压下测试得出。

表 7.3.5-1 运行模式下的典型电流消耗

| Symbol   | Parameters                 | Condition              | $f_{HCLK}$<br>(Hz) | Typical                 |      |      |      |      | Typical                  |      |      |      |      | Unit |

|----------|----------------------------|------------------------|--------------------|-------------------------|------|------|------|------|--------------------------|------|------|------|------|------|

|          |                            |                        |                    | All peripherals enabled |      |      |      |      | All peripherals disabled |      |      |      |      |      |

|          |                            |                        |                    | -40°C                   | 0°C  | 25°C | 55°C | 85°C | -40°C                    | 0°C  | 25°C | 55°C | 85°C |      |

| $I_{DD}$ | Supply current in Run mode | HSI is clock source    | 48M                | 4.46                    | 4.53 | 4.60 | 4.70 | 4.83 | 3.16                     | 3.22 | 3.29 | 3.39 | 3.53 | mA   |

|          |                            |                        | 24M                | 2.99                    | 3.06 | 3.13 | 3.23 | 3.37 | 2.16                     | 2.23 | 2.30 | 2.40 | 2.54 |      |

|          |                            |                        | 12M                | 2.05                    | 2.12 | 2.19 | 2.30 | 2.43 | 1.64                     | 1.70 | 1.78 | 1.88 | 2.02 |      |

|          |                            |                        | 6M                 | 1.58                    | 1.64 | 1.72 | 1.82 | 1.96 | 1.37                     | 1.44 | 1.51 | 1.62 | 1.75 |      |

|          |                            |                        | 3M                 | 1.34                    | 1.41 | 1.48 | 1.59 | 1.72 | 1.24                     | 1.30 | 1.38 | 1.49 | 1.62 |      |

|          |                            |                        | 750K               | 1.16                    | 1.23 | 1.30 | 1.41 | 1.59 | 1.14                     | 1.20 | 1.28 | 1.38 | 1.57 |      |

|          |                            |                        | 375K               | 1.13                    | 1.20 | 1.27 | 1.38 | 1.57 | 1.12                     | 1.19 | 1.26 | 1.37 | 1.55 |      |

|          |                            |                        | 187.5K             | 1.12                    | 1.18 | 1.26 | 1.36 | 1.55 | 1.11                     | 1.18 | 1.25 | 1.36 | 1.54 |      |

|          |                            |                        | 93.75K             | 1.11                    | 1.18 | 1.25 | 1.36 | 1.49 | 1.11                     | 1.17 | 1.25 | 1.35 | 1.49 |      |

|          |                            | HSIDIV is clock source | 8M                 | 1.63                    | 1.70 | 1.77 | 1.88 | 2.02 | 1.42                     | 1.48 | 1.56 | 1.66 | 1.80 |      |

|          |                            |                        | 4M                 | 1.38                    | 1.45 | 1.52 | 1.63 | 1.76 | 1.24                     | 1.31 | 1.38 | 1.49 | 1.63 |      |

|          |                            |                        | 2M                 | 1.23                    | 1.29 | 1.37 | 1.47 | 1.61 | 1.15                     | 1.22 | 1.30 | 1.40 | 1.54 |      |

|          |                            |                        | 1M                 | 1.15                    | 1.21 | 1.29 | 1.39 | 1.53 | 1.11                     | 1.18 | 1.25 | 1.36 | 1.50 |      |

|          |                            |                        | 500K               | 1.11                    | 1.17 | 1.25 | 1.35 | 1.49 | 1.09                     | 1.16 | 1.23 | 1.34 | 1.47 |      |

|          |                            |                        | 31.25K             | 1.07                    | 1.14 | 1.21 | 1.32 | 1.45 | 1.07                     | 1.14 | 1.21 | 1.32 | 1.45 |      |

|          |                            | LSI is clock           | 40K                | 0.57                    | 0.64 | 0.72 | 0.83 | 0.97 | 3.16                     | 3.22 | 3.29 | 3.39 | 3.53 |      |

**表 7.3.5-2 睡眠模式下的典型电流消耗**

| Symbol          | Parameters                   | Condition              | f <sub>HCLK</sub><br>(Hz) | Typical<br>All peripherals enabled |      |      |      |      | Typical<br>All peripherals disabled |      |      |      |      | Unit |

|-----------------|------------------------------|------------------------|---------------------------|------------------------------------|------|------|------|------|-------------------------------------|------|------|------|------|------|

|                 |                              |                        |                           | -<br>40°C                          | 0°C  | 25°C | 55°C | 85°C | -<br>40°C                           | 0°C  | 25°C | 55°C | 85°C |      |

| I <sub>DD</sub> | Supply current in Sleep mode | HSI is clock source    | 48M                       | 3.13                               | 3.20 | 3.28 | 3.38 | 3.52 | 1.82                                | 1.89 | 1.97 | 2.07 | 2.21 | mA   |

|                 |                              |                        | 24M                       | 2.30                               | 2.37 | 2.44 | 2.55 | 2.69 | 1.47                                | 1.54 | 1.61 | 1.72 | 1.86 |      |

|                 |                              |                        | 12M                       | 1.71                               | 1.78 | 1.85 | 1.96 | 2.09 | 1.29                                | 1.36 | 1.43 | 1.54 | 1.68 |      |

|                 |                              |                        | 6M                        | 1.41                               | 1.47 | 1.55 | 1.65 | 1.79 | 1.20                                | 1.27 | 1.34 | 1.45 | 1.58 |      |

|                 |                              |                        | 3M                        | 1.25                               | 1.32 | 1.40 | 1.50 | 1.64 | 1.15                                | 1.22 | 1.29 | 1.40 | 1.53 |      |

|                 |                              |                        | 750K                      | 1.14                               | 1.21 | 1.28 | 1.39 | 1.52 | 1.11                                | 1.18 | 1.26 | 1.36 | 1.50 |      |

|                 |                              |                        | 375K                      | 1.12                               | 1.19 | 1.26 | 1.37 | 1.55 | 1.11                                | 1.18 | 1.25 | 1.35 | 1.54 |      |

|                 |                              |                        | 187.5                     | 1.11                               | 1.18 | 1.25 | 1.36 | 1.55 | 1.10                                | 1.17 | 1.25 | 1.35 | 1.54 |      |

|                 |                              |                        | 93.75                     | 1.11                               | 1.17 | 1.25 | 1.35 | 1.49 | 1.10                                | 1.17 | 1.25 | 1.35 | 1.49 |      |

|                 |                              | HSIDIV is clock source | 8M                        | 1.40                               | 1.47 | 1.55 | 1.65 | 1.79 | 1.19                                | 1.25 | 1.33 | 1.44 | 1.57 | mA   |

|                 |                              |                        | 4M                        | 1.27                               | 1.33 | 1.41 | 1.51 | 1.65 | 1.13                                | 1.20 | 1.27 | 1.38 | 1.51 |      |

|                 |                              |                        | 2M                        | 1.17                               | 1.23 | 1.31 | 1.42 | 1.55 | 1.10                                | 1.17 | 1.24 | 1.35 | 1.48 |      |

|                 |                              |                        | 1M                        | 1.12                               | 1.19 | 1.26 | 1.37 | 1.50 | 1.08                                | 1.15 | 1.22 | 1.33 | 1.47 |      |

|                 |                              |                        | 500K                      | 1.09                               | 1.16 | 1.23 | 1.34 | 1.47 | 1.07                                | 1.14 | 1.22 | 1.32 | 1.46 |      |

|                 |                              |                        | 125K                      | 1.07                               | 1.14 | 1.21 | 1.32 | 1.46 | 1.07                                | 1.14 | 1.21 | 1.32 | 1.45 |      |

|                 |                              |                        | 62.5K                     | 1.07                               | 1.13 | 1.21 | 1.32 | 1.45 | 1.06                                | 1.13 | 1.21 | 1.32 | 1.45 |      |

|                 |                              |                        | 31.25                     | 1.40                               | 1.47 | 1.55 | 1.65 | 1.79 | 1.19                                | 1.25 | 1.33 | 1.44 | 1.57 |      |

|                 |                              |                        | LSI is clock              | 40K                                | 0.56 | 0.64 | 0.72 | 0.83 | 0.97                                | 0.56 | 0.63 | 0.72 | 0.83 | 0.97 |

**表 7.3.5-3 停机模式下的典型电流消耗<sup>(1)</sup>**

| Symbol          | Parameter                        | Conditions                                              | Typical |      |      |      |      | Unit |

|-----------------|----------------------------------|---------------------------------------------------------|---------|------|------|------|------|------|

|                 |                                  |                                                         | -40°C   | 0°C  | 25°C | 55°C | 85°C |      |

| I <sub>DD</sub> | Supply current in Stop mode      | Enter Stop mode after reset, V <sub>DD</sub> =3.3V      | 38.1    | 52.8 | 56.3 | 60.8 | 57.4 | μA   |

|                 | Supply current in Deep Stop mode | Enter Deep Stop mode after reset, V <sub>DD</sub> =3.3V | 1.32    | 1.86 | 2.02 | 2.39 | 3.65 |      |

备注 1: I/O 状态为模拟输入。

### 内置外设电流消耗

内置外设的电流消耗列于下表, 芯片的工作条件如下:

所有的 I/O 引脚都处于输入模式，并连接到一个静态电平上— $V_{DD}$  或 GND(无负载)。

所有的外设都处于关闭状态，除非特别说明。

给出的数值是通过测量电流消耗计算得出

- 关闭所有外设的时钟

- 只开启一个外设的时钟

表 7.3.5-4 内置外设的电流消耗 <sup>(1)</sup>

| Symbol   | Parameter | Bus  | Typical | Unit   |

|----------|-----------|------|---------|--------|

| $I_{DD}$ | CRC       | AHB  | 0.14    | uA/MHz |

|          | GPIOA     |      | 0.04    |        |

|          | GPIOB     |      | 0.04    |        |

|          | TIM1      | APB1 | 0.99    |        |

|          | TIM3      |      | 0.54    |        |

|          | TIM14     |      | 0.85    |        |

|          | ADC1      |      | 7.24    |        |

|          | USART1    |      | 0.19    |        |

|          | USART2    |      | 0.16    |        |

|          | I2C1      |      | 2.60    |        |

|          | COMP      |      | 5.41    |        |

|          | PWR       |      | 2.55    |        |

|          | DBG       |      | 4.28    |        |

|          | SYSCFG    |      | 1.14    |        |

备注 1.  $f_{HCLK} = 48MHz$ ,  $f_{APB1} = f_{HCLK}$ , 每个外设的预分频系数为默认值。

### 从低功耗模式唤醒的时间

下表列出的唤醒时间是在内部时钟 HSI 的唤醒阶段测量得到。唤醒时使用的时钟源依当前的操作模式而定：

停机或待机模式：时钟源是振荡器

睡眠模式：时钟源是进入睡眠模式时所使用的时钟所有的时间是使用环境温度和供电电压符合表 7.3.1 通用工作条件测量得到。

表 7.3.5-5 低功耗模式的唤醒时间

| Symbol           | Parameter                   | Conditions             | Typical | Unit |

|------------------|-----------------------------|------------------------|---------|------|

| $t_{WUSLEEP}$    | Wake up from Sleep mode     | System clock is HSIDIV | 3.3     | μs   |

| $t_{WUSTOP}$     | Wake up from Stop mode      | System clock is HSIDIV | 16.3    | μs   |

| $t_{WUDEEPSTOP}$ | Wake up from Deep Stop mode | System clock is HSIDIV | 22.6    | μs   |

### 7.3.6 外部时钟源特性

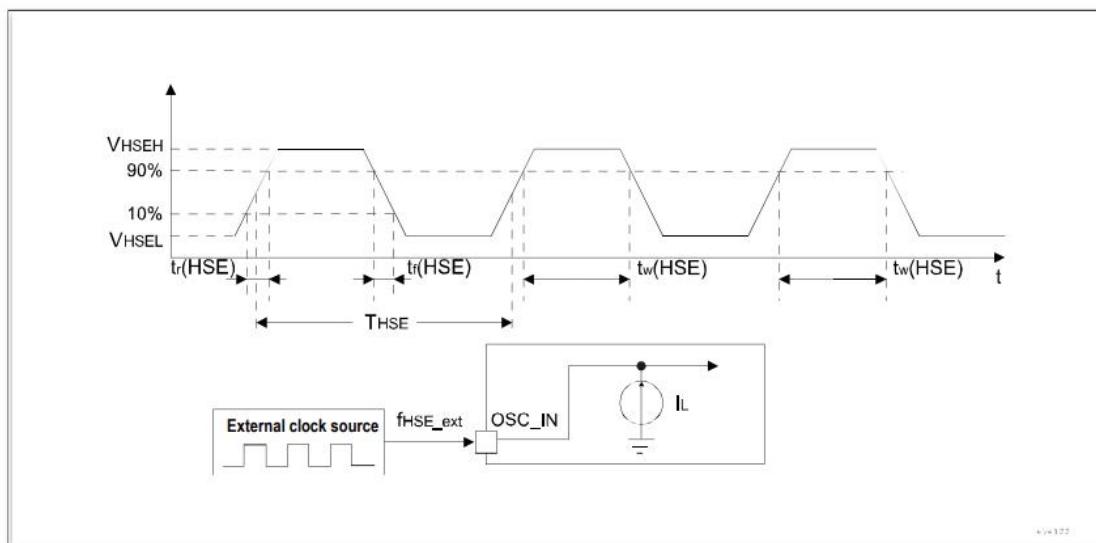

#### 来自外部振荡源产生的高速外部用户时钟

下表中给出的特性参数是使用一个高速的外部时钟源测得, 环境温度和供电电压符合通用工作条件。

表 7.3.6 高速外部用户时钟特性

| Symbol         | Parameter                                           | Condition | Min.        | Typ. | Max.        | Unit |

|----------------|-----------------------------------------------------|-----------|-------------|------|-------------|------|

| $f_{HSE\_ext}$ | User external clock source frequency <sup>(1)</sup> | -         | -           | 8    | 48          | MHz  |

| $V_{HSEH}$     | OSC_IN input high level voltage                     | -         | $0.7V_{DD}$ | -    | $V_{DD}$    | V    |

| $V_{HSEL}$     | OSC_IN input low level voltage                      | GND       | GND         | -    | $0.3V_{DD}$ | V    |

| $t_{w(HSE)}$   | OSC_IN high or low time <sup>(1)</sup>              | -         | 20          | -    | -           | ns   |

备注 1: 由设计保证, 不在生产中测试。

图 7.3.6 外部高速时钟源的交流时序图

### 7.3.7 内部时钟源特性

下表中给出的特性参数是使用环境温度和供电电压符合通用工作条件测量得到。

#### 高速内部 (HSI) 振荡器

**表 7.3.7-1 HSI 振荡器特性<sup>(1)</sup>**

| Symbol                | Parameter                        | Conditions        | Min. | Typ. | Max. | Unit |

|-----------------------|----------------------------------|-------------------|------|------|------|------|

| $f_{HSI}$             | Frequency                        | -                 | -    | 48   | -    | MHz  |

| $ACC_{HSI}^{(3)}$     | HSI oscillator deviation         | TA = 25°C         | -1   | -    | 1    | %    |

|                       |                                  | TA = 0°C ~ 85°C   | -2   | -    | 2    | %    |

|                       |                                  | TA = -20°C ~ 85°C | -2.5 | -    | 2.5  |      |

|                       |                                  | TA = -40°C ~ 85°C | -3.5 | -    | 3.5  |      |

| $T_{stab(HSI)}^{(2)}$ | HSI oscillator startup time      | -                 | -    | -    | 18   | μs   |

| $I_{DD(HSI)}^{(2)}$   | HSI oscillator power consumption | -                 | -    | 496  | -    | μA   |

备注 1.:  $V_{DD}=3.3V$ ,  $TA=-40^{\circ}C \sim 85^{\circ}C$ , 除非特别说明。

备注 2: 由设计保证, 不在生产中测试。

备注 3: 由综合评估得出。

### 低速内部(LSI) 振荡器

**表 7.3.7-2 LSI 振荡器特性<sup>(1)</sup>**

| Symbol                | Parameter                        | Conditions        | Min. | Typ. | Max. | Unit |

|-----------------------|----------------------------------|-------------------|------|------|------|------|

| $f_{LSI}$             | Frequency                        | -                 | -    | 40   | -    | KHz  |

| $ACC_{LSI}^{(3)}$     | LSI oscillator deviation         | TA = 0°C ~ 55°C   | -10  | -    | 15   | %    |

|                       |                                  | TA = -40°C ~ 85°C | -20  | -    | 20   | %    |

| $T_{stab(LSI)}^{(2)}$ | LSI oscillator startup time      | -                 | -    | -    | 50   | μs   |

| $I_{DD(LSI)}^{(2)}$   | LSI oscillator power consumption | -                 | -    | 0.3  | -    | μA   |

备注 1.  $V_{DD}=3.3V$ ,  $TA=-40^{\circ}C \sim +85^{\circ}C$ , 除非特别说明。

备注 2. 由设计保证, 不在生产中测试。

备注 3. 由综合评估得出。

### 7.3.8 存储器特性

**表 7.3.8 Flash 存储器特性**

| Symbol      | Parameter                    | Conditions | Min.   | Typ. | Max. | Unit   |

|-------------|------------------------------|------------|--------|------|------|--------|

| $t_{prog}$  | 32-bit programming time      | -          | -      | 25   | -    | μs     |

| $t_{ERASE}$ | Page (1024 bytes) erase time | -          | -      | 4    | -    | ms     |

| $t_{ME}$    | Mass erase time              | -          | -      | 8    | -    | ms     |

| $N_{END}$   | Endurance                    | -          | 100000 | -    | -    | Cycles |

| $T_{DR}$    | Data retention               | TA = 85°C  | 10     | -    | -    | Years  |

### 7.3.9 EMC 特性

敏感性测试是在产品的综合评估时抽样进行测试的。

#### 功能性 EMS (电磁敏感性)

当运行一个简单的应用程序时（通过 I/O 端口闪烁 2 个 LED），测试样品被施加 1 种电磁干扰直到产生错误，LED 闪烁指示了错误的产生。

静电放电 (ESD) (正向和负向) 施加到所有器件引脚，直到发生功能干扰。该测试符合 IEC 61000-4-2 标准。

FTB：通过一个 100 pF 的电容向  $V_{DD}$  和 GND 施加一串快速瞬变电压 (正负)，直到发生功能性干扰。该测试符合 IEC 61000-4-4 标准。

芯片复位可以使系统恢复正常操作。测试结果列于下表中。

表 7.3.9 EMS 特性

| Symbol     | Parameter                                                                                                                    | Conditions                                                                              | Level/Type |

|------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------|

| $V_{FESD}$ | Voltage limit applied to any I/O pin, resulting in malfunction                                                               | $V_{DD} = 3.3V$ , $TA = +25^{\circ}C$ , $f_{HCLK} = 48MHz$ . Conforming to IEC61000-4-2 | 2A         |

| $V_{FEFT}$ | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and GND pins to induce a functional disturbance | $V_{DD} = 3.3V$ , $TA = +25^{\circ}C$ , $f_{HCLK} = 48MHz$ . Conforming to IEC61000-4-4 | 2A         |

#### 设计可靠的软件以避免噪声的问题

在器件级进行 EMC 的评估和优化，是在典型的应用环境中进行的。应该注意的是，好的 EMC 性能与用户应用和具体的软件密切相关。因此，建议用户对软件实行 EMC 优化，并进行与 EMC 有关的认证测试。

#### 软件建议

软件的流程中必须包含程序跑飞的控制，如：

- 被破坏的程序计数器

- 意外的复位

- 关键数据被破坏（控制寄存器等）

#### 认证前的试验

很多常见的失效（意外的复位和程序计数器被破坏），可以通过人工的在 NRST 上引入一低电平或在晶振引脚上引入一个持续 1 秒的低电平而重现。

在进行 ESD 测试时，可以把超出应用要求的电压直接施加在芯片上，当检测到意外动作的地方，软件部分需要加强以防止发生不可恢复的错误。

### 7.3.10 I/O 端口特性

#### 通用输入/输出特性

除非特别说明, 下表列出的参数是按照表 7.3.1 的条件测量得到。所有的 I/O 端口都是兼容 CMOS 电平。

表 7.3.10-1 I/O 静态特性

| Symbol    | Parameter                              | Conditions        | Minimum        | Typical | Maximum        | Unit      |

|-----------|----------------------------------------|-------------------|----------------|---------|----------------|-----------|

| $V_{IL}$  | Low level input voltage                | -                 | -              | -       | $0.3 * V_{dd}$ | V         |

| $V_{IH}$  | High level input voltage               | -                 | $0.7 * V_{dd}$ | -       | -              | V         |

| $V_{hy}$  | Schmitt trigger hysteresis (1)         | -                 | $0.1 * V_{dd}$ | -       | -              | V         |

| $I_{lkg}$ | Input leakage current (2)              | -                 | -1             | -       | 1              | $\mu A$   |

| $R_{pu}$  | Weak pull-up equivalent resistor (3)   | $V_{in} = GND$    | -              | 52.7    | -              | $k\Omega$ |

| $R_{pd}$  | Weak pull-down equivalent resistor (3) | $V_{in} = V_{dd}$ | -              | 56      | -              | $k\Omega$ |

| $C_{io}$  | I/O pin capacitance                    | -                 | -              | -       | 10             | $pF$      |

备注 1: 由综合评估得出, 不在生产中测试。

备注 2: 如果在相邻引脚有反向电流倒灌, 则漏电流可能高于最大值。

备注 3: 上拉和下拉电阻是 poly 电阻。

#### 输出驱动电流

GPIO(通用输入/输出端口)可以吸收或输出多达 $\pm 20mA$  电流。

在用户应用中, I/O 脚的数目必须保证驱动电流不能超过绝对最大额定值:

- 所有 I/O 端口从  $V_{DD}$  上获取的电流总和, 加上芯片在  $V_{DD}$  上获取的最大运行电流, 不能超过绝对最大额定值  $I_{VDD}$ 。

- 所有 I/O 端口吸收并从 GND 上流出的电流总和, 加上芯片在 GND 上流出的最大运行电流, 不能超过绝对最大额定值  $I_{GND}$ 。

该芯片最多可为 2 个 8 段式共阴极 LED 数码管提供驱动, 以节省外部硬件开销。GPIOA 中最多可配置 2 个特定 IO 为灌电流模式 (最大 80mA), 用于控制数码管阴极; 最多可配置 4 个特定 IO 为恒流源模式 (可配置成 2.5/5/7.5/10mA 四档), 用于控制数码管段选。

#### 输出电压

除非特别说明, 下表列出的参数是使用环境温度和  $V_{DD}$  供电电压符合表 7.3.1 的条件测量得到。所有的 I/O 端口都是兼容 CMOS 的。

表 7.3.10-2 转出电压特性<sup>(3)</sup>

| Symbol                         | Parameter           | Conditions                                     | Typical         |                 | Unit |

|--------------------------------|---------------------|------------------------------------------------|-----------------|-----------------|------|

|                                |                     |                                                | General mode    | High Sink mode  |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 6mA, V <sub>DD</sub> =2.0V  | 0.19            | 0.06            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | 1.71            | 1.7             |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 8mA, V <sub>DD</sub> =2.0V  | 0.27            | 0.07            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | 1.58            | 1.58            |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 20mA, V <sub>DD</sub> =2.0V | V <sub>DD</sub> | 0.21            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | 0               | 0               |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 40mA, V <sub>DD</sub> =2.0V | -               | 0.47            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | -               | 0               |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 60mA, V <sub>DD</sub> =2.0V | -               | 0.87            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | -               | 0               |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 80mA, V <sub>DD</sub> =2.0V | -               | V <sub>DD</sub> | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | -               | 0               |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 6mA, V <sub>DD</sub> =3.3V  | 0.13            | 0.05            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | 3.12            | 3.12            |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 8mA, V <sub>DD</sub> =3.3V  | 0.17            | 0.07            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | 3.06            | 3.05            |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 20mA, V <sub>DD</sub> =3.3V | 0.46            | 0.16            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | 2.64            | 2.6             |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 40mA, V <sub>DD</sub> =3.3V | -               | 0.33            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | -               | 0.79            |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 60mA, V <sub>DD</sub> =3.3V | -               | 0.49            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | -               | 0               |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 80mA, V <sub>DD</sub> =3.3V | -               | 0.68            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | -               | 0               |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 6mA, V <sub>DD</sub> =5.5V  | 0.11            | 0.06            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | 5.36            | 5.36            |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 8mA, V <sub>DD</sub> =5.5V  | 0.14            | 0.07            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | 5.32            | 5.31            |      |

| V <sub>OL</sub> <sup>(2)</sup> | Output low voltage  | I <sub>IO</sub>  = 20mA, V <sub>DD</sub> =5.5V | 0.34            | 0.15            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | 5.04            | 5.02            |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 40mA, V <sub>DD</sub> =5.5V | -               | 0.29            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | -               | 4.5             |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low voltage  | I <sub>IO</sub>  = 60mA, V <sub>DD</sub> =5.5V | -               | 0.42            | V    |

| V <sub>OH</sub> <sup>(2)</sup> | Output high voltage |                                                | -               | 3.81            |      |

| <b>Symbol</b>       | <b>Parameter</b>    | <b>Conditions</b>                              | <b>Typical</b>      |                       | <b>Unit</b> |

|---------------------|---------------------|------------------------------------------------|---------------------|-----------------------|-------------|

|                     |                     |                                                | <b>General mode</b> | <b>High Sink mode</b> |             |

| V <sub>OL</sub> (1) | Output low voltage  | I <sub>IO</sub>  = 80mA, V <sub>DD</sub> =5.5V | -                   | 0.56                  | V           |

| V <sub>OH</sub> (2) | Output high voltage |                                                | -                   | 2.74                  |             |

备注 1：芯片吸收的电流  $I_{IO}$  必须始终遵循表中给出的绝对最大额定值，同时  $I_{IO}$  的总和（所有 I/O 脚和控制脚）不能超过  $I_{GND}$ 。

备注 2：芯片输出的电流  $I_{IO}$  必须始终遵循表中给出的绝对最大额定值，同时  $I_{IO}$  的总和（所有 I/O 脚和控制脚）不能超过  $I_{VDD}$ 。

备注 3：由综合评估得出。

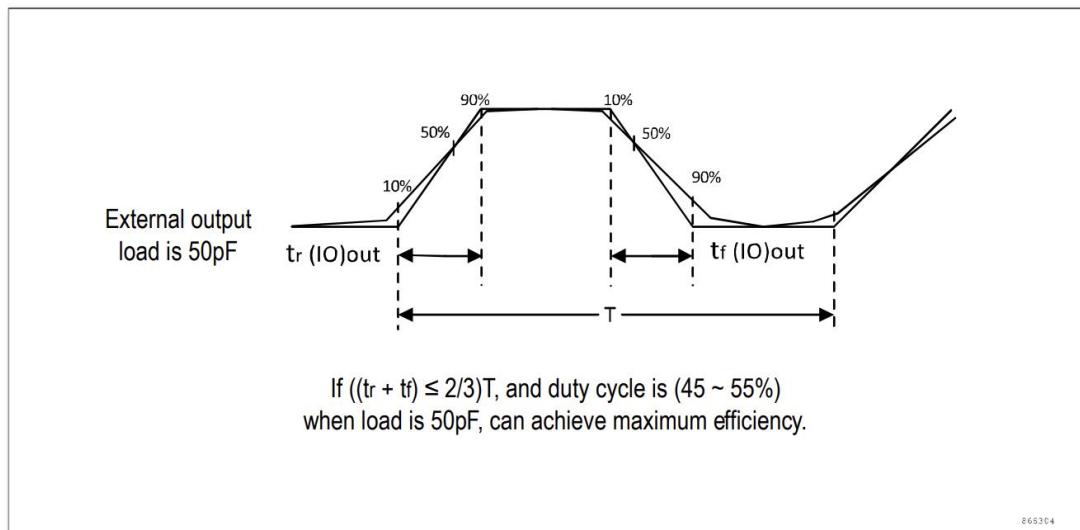

输入输出交流特性的定义和数值分别在下面的图表中给出。

除非特别说明，下表列出的参数是使用环境温度和供电电压符合表 7.3.1 的条件测量得到。

表 7.3.10-3 I/O 交流特性<sup>(1)</sup>

| <b>Symbol</b>        | <b>Parameter</b> | <b>Conditions</b>                               | <b>Typical</b> | <b>Unit</b> |

|----------------------|------------------|-------------------------------------------------|----------------|-------------|

| t <sub>(IO)out</sub> | Output fall time | C <sub>L</sub> = 50pF<br>V <sub>DD</sub> = 3.3V | 5.8            | ns          |

|                      | Output rise time |                                                 | 7.7            | ns          |

备注 1：由设计保证，不在生产中测试。

图 7.3.10 I/O 交流特性

表 7.3.10-4 恒流源模式驱动特性

| <b>Symbol</b>   | <b>Parameter</b>     | <b>Conditions</b>                                                              | <b>Minimum</b> | <b>Typical</b> | <b>Maximum</b> | <b>Unit</b> |

|-----------------|----------------------|--------------------------------------------------------------------------------|----------------|----------------|----------------|-------------|

| I <sub>OH</sub> | LEDIO Output current | V <sub>DD</sub> =2.7~5.5V, V <sub>OH</sub> =V <sub>DD</sub> ~1.0, LEDIOCR 档位 0 | -              | 2.5            | -              | mA          |

|                 |                      | V <sub>DD</sub> =2.7~5.5V, V <sub>OH</sub> =V <sub>DD</sub> ~1.0,              | -              | 5.0            | -              | mA          |

|          |                            |                                                                                                       |   |      |     |    |

|----------|----------------------------|-------------------------------------------------------------------------------------------------------|---|------|-----|----|

|          |                            | LEDIOCR 档位 1                                                                                          |   |      |     |    |

|          |                            | VDD=2.7~5.5V,VOH=VDD~1.0,<br>LEDIOCR 档位 2                                                             | - | 7.5  | -   | mA |

|          |                            | VDD=2.7~5.5V,VOH=VDD~1.0,<br>LEDIOCR 档位 3                                                             | - | 10.0 | -   | mA |

| Accuracy | Current accuracy           | VDD=5V, TA=25°C, LEDIOCR<br>档位3 (10 mA)                                                               | - | -    | TBD | -  |

| △I1      | 线性调整                       | TA= 25 °C, LEDIOCR 档位 3<br>(10 mA), VDD=5 V时电流<br>I1, VDD=4.5V 时电流I2计算<br>( I1-I2 /I1)*2              | - | -    | TBD | -  |

| △I2      | 负载调整                       | TA= 25 °C, LEDIOCR 档位 3<br>(10 mA), VDD=4.5~5.5V, 调<br>整负载到VDD-1V时电流 I1,<br>VDD-2V 时电流I2计算(I1- I2)/I1 | - | -    | TBD | -  |

| Tcoeff   | Temperature<br>coefficient | TA=-40 ~ 85 °C                                                                                        | - | -    | TBD |    |

### 7.3.11 Timer 定时器特性

下表列出的参数由设计保证。

表 7.3.11 TIMx<sup>(1)</sup> 特性

| Symbol             | Parameter                                                 | Condition           | Minimum | Maximum | Unit          |

|--------------------|-----------------------------------------------------------|---------------------|---------|---------|---------------|

| tres(TIM)          | Timer resolution                                          | -                   | 1       | -       | $t_{TIMxCLK}$ |

|                    |                                                           | $f_{TIMxCLK}=48MHz$ | 20.8    | -       | ns            |

| $f_{EXT}$          | External clock frequency<br>of channel 1 to 4             | -                   | 0       | -       | MHz           |

|                    |                                                           | $f_{TIMxCLK}=48MHz$ | 0       | 24      |               |

| Res <sub>TIM</sub> | Timer resolution                                          | -                   | -       | 16      | bit           |

| $t_{COUNTER}$      | 16-bit counter period                                     | -                   | 1       | 65536   | $t_{TIMxCLK}$ |

|                    |                                                           | $f_{TIMxCLK}=48MHz$ | 0.0208  | 1365.3  | us            |

| $t_{MAX\_COUNT}$   | Maximum possible<br>counter value (TIM_PSC<br>adjustable) | -                   | -       | 65536   | $t_{TIMxCLK}$ |

|                    |                                                           | $f_{TIMxCLK}=48MHz$ | -       | 1365.3  | us            |

|               |                             |   |   |    |     |

|---------------|-----------------------------|---|---|----|-----|

| $t_{MAX\_IN}$ | TIM maximum input frequency | - | - | 48 | MHz |

|---------------|-----------------------------|---|---|----|-----|

备注 1：设计保证，不在生产中测试。

### 7.3.12 I2C 接口特性

除非特别说明，下表列出的参数是使用环境温度， $f_{PCLK1}$  频率和  $V_{DD}$  供电电压符合表 7.3.1 的条件测量得到。

I2C 接口符合标准 I2C 通信协议，但有如下限制：SDA 和 SCL 不是“真”的开漏引脚，当配置为开漏输出时，在引出脚和  $V_{DD}$  之间的 PMOS 管被关闭，但仍然存在。

表 7.3.12 I2C 接口特性

| Symbol                       | Parameter                                              | Standard I2C <sup>(1)</sup> |                    | Fast mode I2C <sup>(1)</sup> |                    | Unit |

|------------------------------|--------------------------------------------------------|-----------------------------|--------------------|------------------------------|--------------------|------|

|                              |                                                        | Minimum                     | Maximum            | Minimum                      | Maximum            |      |

| $t_{w(SCL)}$                 | SCL clock low time                                     | $8*t_{PCLK}$                | -                  | $8*t_{PCLK}$                 | -                  | us   |

| $t_{w(SCLH)}$                | SCL clock high time                                    | $8*t_{PCLK}$                | -                  | $8*t_{PCLK}$                 | -                  | us   |

| $t_{su}(SDA)$                | SDA setup time                                         | $1*t_{PCLK}$                | -                  | $1*t_{PCLK}$                 | -                  | ns   |

| $t_h(SDA)$                   | SDA data retention time                                | $0^{(3)}$                   | $^{(4)}$           | $0^{(3)}$                    | $^{(4)}$           | ns   |

| $t_r(SDA) t_r(SCL)$          | SDA and SCL rising time                                | -                           | 1000               | 20                           | 300                | ns   |

| $t_f(SDA) t_f(SCL)$          | SDA and SCL fall time                                  | -                           | 300                | 20                           | 300                | ns   |

| $t_{vd}(DAT)$ <sup>(5)</sup> | Data valid time                                        | -                           | $7*t_{PCLK}^{(4)}$ | -                            | $7*t_{PCLK}^{(4)}$ | us   |

| $t_{vd}(ACK)$ <sup>(6)</sup> | Data valid acknowledge time                            | -                           | $7*t_{PCLK}^{(4)}$ | -                            | $7*t_{PCLK}^{(4)}$ | us   |

| $t_h(STA)$                   | Start condition hold time                              | $4*t_{PCLK}$                | -                  | $4*t_{PCLK}$                 | -                  | us   |

| $t_{su}(STA)$                | Start condition setup time                             | $8*t_{PCLK}$                | -                  | $8*t_{PCLK}$                 | -                  | us   |

| $t_{su}(STO)$                | Stop condition setup time                              | $12*t_{PCLK}$               | -                  | $12*t_{PCLK}$                | -                  | us   |

| $t_{w(STO:STA)}$             | Time from Stop condition to Start condition (bus idle) | $7*t_{PCLK}$                | -                  | $7*t_{PCLK}$                 | -                  | us   |

| $C_b$                        | Capacitive load of each bus                            | -                           | 400                | -                            | 400                | pF   |

备注 1：由设计保证，不在生产中测试。

备注 2：在 SDA 进入  $0.3V_{DD}$  至  $0.7V_{DD}$  的不确定范围之前，确保 SCL 在下降沿下降到  $0.3V_{DD}$  以下。

注意：对于无法观察 SCL 下降沿的控制器，应独立测量 SCL 从静态高电平 ( $V_{DD}$ ) 到  $0.3V_{DD}$  的转换时间来插入 SDA 转换相对于 SCL 的延迟。

备注 3： $t_{vd}(DAT)$  = 从 SCL LOW 到 SDA 输出数据信号的时间。

备注 4： $t_{vd}(ACK)$  = 从 SCL LOW 到 SDA 输出确认信号的时间。

图 7.3.12 I2C 总线交流波形和测量电路 <sup>(1)</sup>

备注 1：测量点设置于 CMOS 电平： $0.3V_{DD}$  和  $0.7V_{DD}$ 。

### 7.3.13 USART 接口特性

除非特别说明, 下表列出的参数是使用环境温度,  $f_{\text{PCLK}_x}$  频率和  $V_{\text{DD}}$  供电电压符合表 7.3.1 的条件测量得到。

表 7.3.13 USART 特性<sup>(1)</sup>

| Symbol                               | Parameter             | Conditions                            | Minimum                    | Maximum                    | Unit |

|--------------------------------------|-----------------------|---------------------------------------|----------------------------|----------------------------|------|

| $f_{\text{SCLK}}$                    | USART clock frequency | Master mode, $T_A = 25^\circ\text{C}$ | -                          | 6                          | MHz  |

| $1/t_{\text{c(SCLK)}}$               |                       | Slave mode, $T_A = 25^\circ\text{C}$  | -                          | 6                          |      |

| $t_{\text{r(SCLK)}}$                 | SCLK clock rise time  | Load capacitance: $C = 15\text{pF}$   | -                          | 6                          | ns   |

| $t_{\text{f(SCLK)}}$                 | SCLK clock fall time  | Load capacitance: $C = 15\text{pF}$   | -                          | 6                          | ns   |

| $t_{\text{W(SCLKH)}}$ <sup>(1)</sup> | SCLK high time        | -                                     | $t_{\text{c(SCLK)}}/2 - 6$ | $t_{\text{c(SCLK)}}/2 + 6$ | ns   |

| $t_{\text{W(SCLKL)}}$ <sup>(1)</sup> | SCLK low time         | -                                     | $t_{\text{c(SCLK)}}/2 - 6$ | $t_{\text{c(SCLK)}}/2 + 6$ | ns   |

|                    |                        |                                                 |   |    |    |

|--------------------|------------------------|-------------------------------------------------|---|----|----|

| $t_{su(MI)}^{(1)}$ | Data input setup       | Master mode, $f_{PCLK} = 48MHz$ , prescaler = 8 | 5 | -  | ns |

| $t_{su(SI)}^{(1)}$ | time                   | Slave mode                                      | 5 | -  | ns |

| $t_{h(MI)}^{(1)}$  | Data input hold        | Master mode, $f_{PCLK} = 48MHz$ , prescaler = 8 | 5 | -  | ns |

| $t_{h(SI)}^{(1)}$  | time                   | Slave mode                                      | 5 | -  | ns |

| $t_{v(MO)}^{(1)}$  | Data output valid time | Master mode (after enable edge)                 | - | 10 | ns |

| $t_{v(SO)}^{(1)}$  | Data output valid time | Slave mode (after enable edge)                  | - | 26 | ns |

备注 1：由设计保证，不在生产中测试。

### 7.3.14 ADC 特性

除非特别说明，下表的参数是使用符合表 7.3.1 的条件的环境温度、 $f_{PCLK2}$ 频率和  $V_{DD}$ 供电电压测量得到。

表 7.3.14 ADC 特性

| Symbol           | Parameter                                       | Conditions      | Min.                                                      | Typ. | Max.     | Unit        |

|------------------|-------------------------------------------------|-----------------|-----------------------------------------------------------|------|----------|-------------|

| $V_{DD}$         | Supply voltage                                  | -               | 2.5                                                       | 3.3  | 5.5      | V           |

| $F_{ADC}$        | ADC clock frequency                             | -               | -                                                         | -    | 16       | MHz         |

| $F_S^{(1)}$      | Sampling frequency                              | -               | -                                                         | -    | 1        | MHz         |

| $F_{TRIG}^{(1)}$ | External trigger frequency <sup>(3)</sup>       | $f_{ADC}=16MHz$ | -                                                         | -    | 1        | MHz         |

|                  |                                                 | -               | -                                                         | -    | 16       | $1/f_{ADC}$ |

| $V_{AIN}^{(2)}$  | Conversion voltage range                        | -               | 0                                                         | -    | $V_{DD}$ | V           |

| $R_{AIN}^{(1)}$  | External input impedance                        | -               | See equation 2                                            |      |          | k $\Omega$  |

| $R_{ADC}^{(1)}$  | Sampling switch resistance                      | -               | -                                                         | -    | 1.0      | k $\Omega$  |

| $C_{ADC}^{(1)}$  | Internal sample and hold capacitance            | -               | -                                                         | -    | 5        | pF          |

| $T_{STAB}^{(1)}$ | Stabilization time                              | -               | -                                                         | -    | 10       | $\mu s$     |

| $T_{LATR}^{(1)}$ | Delay between trigger and conversion start      | -               | -                                                         | -    | -        | $1/f_{ADC}$ |

| $T_S^{(1)}$      | Sampling time                                   | $f_{ADC}=16MHz$ | 0.156                                                     | -    | 15.031   | $\mu s$     |

|                  |                                                 | -               | 2.5                                                       | -    | 240.5    | $1/f_{ADC}$ |

| $T_{CONV}^{(1)}$ | Total conversion time (including sampling time) | $f_{ADC}=16MHz$ | 0.9375                                                    | -    | 15.8125  | $\mu s$     |

|                  |                                                 | -               | 15 ~ 253 (sampling $t_S$ + successive approximation 12.5) |      |          | $1/f_{ADC}$ |

| ENOB             | Effective number of bits                        | -               | -                                                         | 10.8 | -        | bit         |

备注 1：由综合评估保证，不在生产中测试。

备注 2: 由设计保证, 不在生产中测试。

备注 3: 在该系列产品中,  $V_{REF+}$  在内部连接到  $V_{DD}$ ,  $V_{REF-}$  在内部连接到 GND。

备注 4: 由设计保证, 不在生产中测试。

备注 5: 对于外部触发, 必须在时延中加上一个延迟  $1/f_{ADC}$ 。

## 8. CAP\_AFE 特征描述

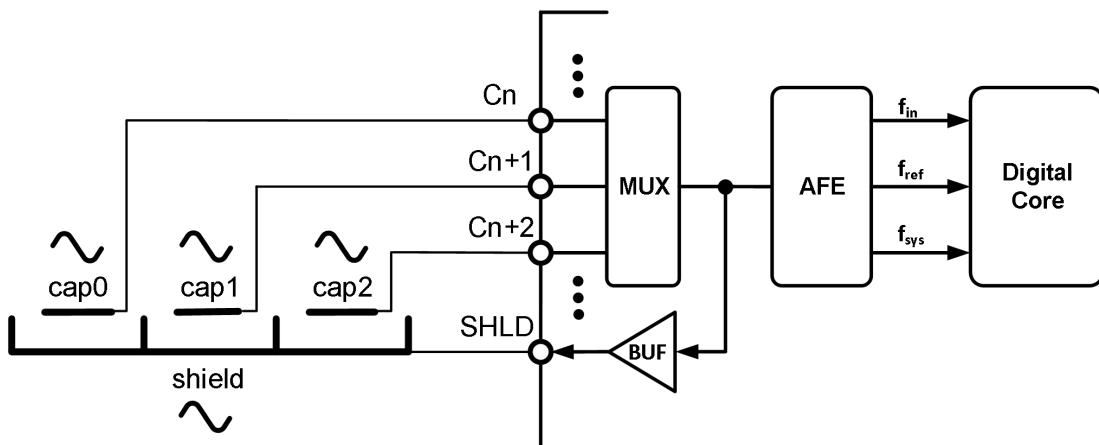

CAP\_AFE (Capacitive Analog Front End) 是集成于芯片内部的高性能电容检测子系统。它采用 System-in-Package (SiP) 架构, 包含独立的模拟前端、数字信号处理单元 (DSP) 以及专用的时钟系统。

与传统通过总线映射的外设不同, CAP\_AFE 在逻辑上是一个独立的从机设备。主控 MCU (Cortex-M0+) 通过内部互联的 I2C 接口 (映射至 PA0/PA4 引脚) 与 CAP\_AFE 通信, 实现参数配置和数据读取。

该模块的主要特性包括:

独立的时钟域: 内置 19.2MHz 高精度振荡器 ( $f_{sys}$ ), 通过可配置的分频器 ( $f_{ref}$ ,  $f_{in}$ ) 提供稳定的测量时基, 确保在 MCU 主频变化或休眠时仍能保持一致的检测性能。

硬件级 DSP: 集成专用 DSP 处理单元, 自动完成通道扫描与数据预处理, 显著降低 MCU 的 CPU 负载。

高抗扰模拟链路: 包含谐振驱动器与 SHLD 屏蔽引脚, 有效抑制环境噪声与寄生电容影响。

### 8.1 CAP-AFE 时钟系统

在 MCP1085 的系统框图中,  $f_{sys}$ 、 $f_{ref}$ 、 $f_{sensor}$  和  $f_{in}$  是 4 个重要的时钟信号。其中  $f_{sensor}$  是电容测量电路的振荡频率, 经  $FIN\_DIV$  分频后, 得到被测时钟信号  $f_{in}$ 。 $f_{sys}$  是芯片内部的系统时钟, 频率为 19.2MHz。经  $FREF\_DIV$  分频后, 得到参考时钟  $f_{ref}$ 。为了确保测量结果正确,  $f_{ref}$  和  $f_{in}$  需要满足如下条件:

$$f_{in} < \frac{f_{ref}}{4}$$

下表是时钟配置 CAP\_AFE 相关寄存器定义。

表 8.1 时钟配置寄存器定义

| 时钟        | 寄存器     | 地址   | 位            | 说明                                                                                                                                                                                                               |

|-----------|---------|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $f_{in}$  | DIV_CFG | 0x1F | FINDIV[2:0]  | 000: 分频比 $NDIV_{in}=1$<br>001: 分频比 $NDIV_{in}=2$<br>010: 分频比 $NDIV_{in}=4$<br>011: 分频比 $NDIV_{in}=8$<br>100: 分频比 $NDIV_{in}=16$<br>101: 分频比 $NDIV_{in}=32$<br>110: 分频比 $NDIV_{in}=64$<br>111: 分频比 $NDIV_{in}=64$ |

| $f_{ref}$ | DIV_CFG | 0x1F | FREFDIV[1:0] | 00: 分频比 $NDIV_{ref}=1$                                                                                                                                                                                           |

|  |  |  |  |                                                                            |

|--|--|--|--|----------------------------------------------------------------------------|

|  |  |  |  | 01: 分频比 $NDIV_{ref}=2$<br>10: 分频比 $NDIV_{ref}=4$<br>11: 分频比 $NDIV_{ref}=8$ |

|--|--|--|--|----------------------------------------------------------------------------|

时钟信号  $f_{sensor}$  与  $f_{in}$ 、 $f_{sys}$  与  $f_{ref}$  的关系如下式所示：

$$f_{in} = \frac{f_{sensor}}{NDIV_{in}} \quad (1)$$

$$f_{ref} = \frac{f_{sys}}{NDIV_{ref}} \quad (2)$$

需要注意的是， $f_{in}$  必须保证大于 100KHz。

## 8.2 电容测量

可支持多通道、多模式的电容测量。通过配置 C\_CMD 寄存器，可以选择电容的测量模式：分别为单端测量模式和双端测量模式。单端测量模式适用于一端接地的电容测量。双端测量模式适用于双端浮空的电容测量。

表 8.2 单端双端测量模式选择

| 寄存器   | 地址   | 位       | 说明                     |

|-------|------|---------|------------------------|

| C_CMD | 0x1D | OSC_SEL | 0: 单端测量模式<br>1: 双端测量模式 |

## 8.3 电容测量模式

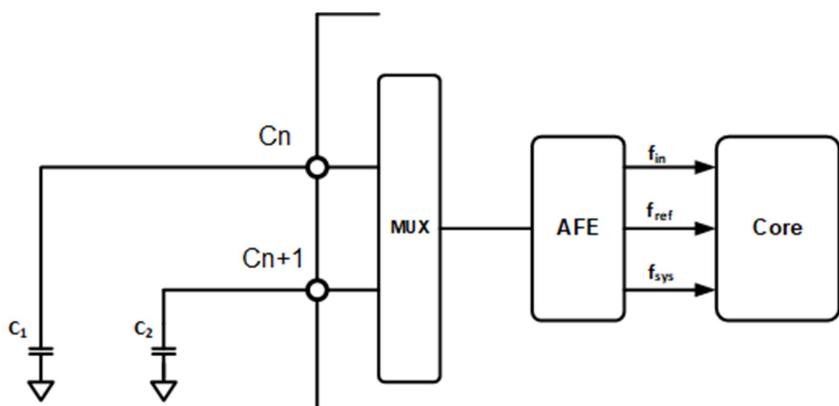

### 8.3.1 单端对地电容

测量单端对地电容，将被测电容或电极连接到芯片任意测量通道，连接方式如下图所示。需要配置 OSC\_SEL=0，并通过配置 OSC1\_CHS\_M 和 OSC1\_CHS\_L 来选择测量通道。测量通道 0 到 9 一共 10 路通道的电容数值。

图 8.3.1 测量单端电容

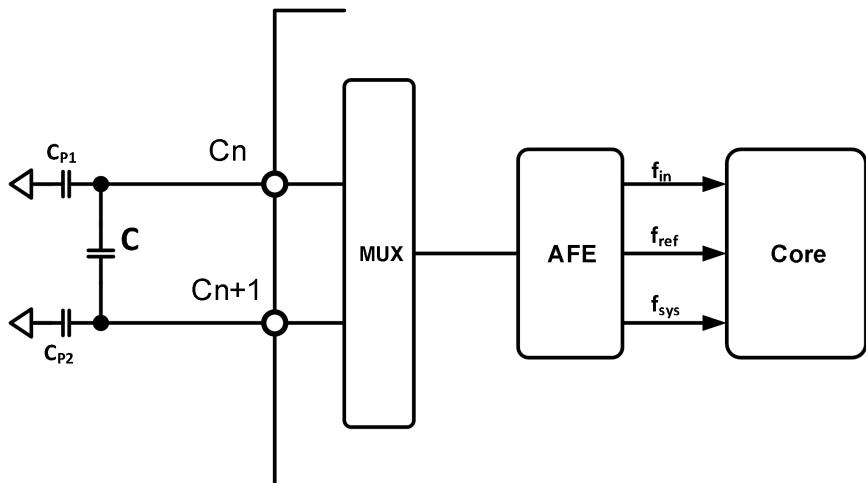

### 8.3.2 双端浮空电容

测量双端浮空电容，可以选择双端测量模式，此种方式对于地噪声不敏感，且测量速度快，适用于测量速度较快且地平面干扰较大的场合，连接方式如下图所示，其中， $C_{p1}$  和  $C_{p2}$  为寄生电容。测量需要配置  $OSC\_SEL=1$ ，并通过配置  $OSC2\_CHS$  来选择测量通道。测量通道一共 5 路，每组双端浮空电容需要占用两路单端通道。

图 8.3.2 测量双端浮空电容

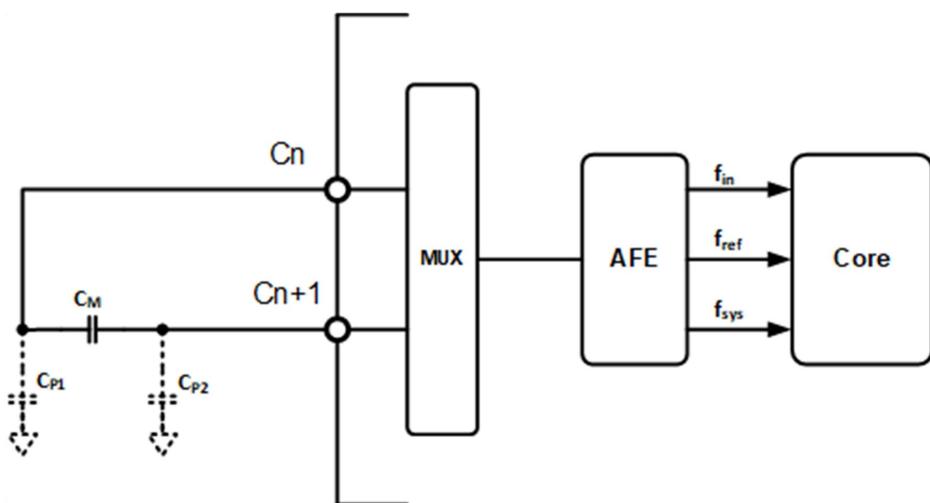

### 8.3.3 互电容

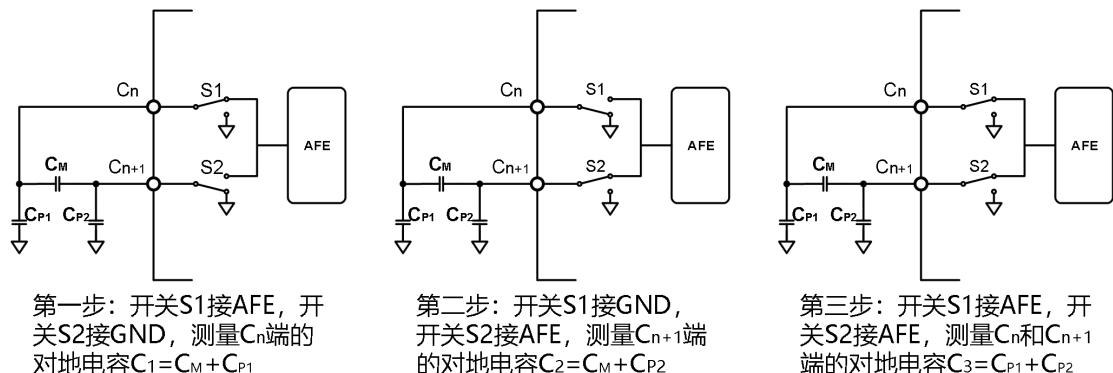

互电容可以消除通道的对地寄生电容。测量互电容，是在单端测量模式的基础上，通过内部控制逻辑和计算，得到反映互电容  $C_M$  大小的频率计数值。互电容的连接方式如下图所示，其中通道下标 n 的取值为 0、2、4、6 和 8。图中  $C_{p1}$  和  $C_{p2}$  为寄生电容。测量需要配置  $OSC\_SEL=0$ ，并通过配置  $OSC1\_CHS\_M$ 、 $OSC1\_CHS\_L$  和  $OSC1\_MCHS$  来选择测量通道。测量通道一共 5 路，每组互电容需要占用两路单端通道。

图 8.3.3-1 测量互电容

互电容测量的具体流程如下所示，分为三个步骤。第一步测出电容值  $C_1$ ，第二步测出电容值  $C_2$ ，第三步测出电容值  $C_3$ 。然后通过运算，得到互电容  $C_M = (C_1 + C_2 - C_3)/2$ 。可以看到，通过上述方法，端口的寄生电容  $C_{P1}$  和  $C_{P2}$  被减掉了。

图 8.3.3-2 测量互电容的步骤

### 8.3.4 电容测量流程

在确定被测电容类型并确定 OSC\_SEL 配置之后，需要按如下步骤执行，8.3 章节包括具体说明。

- i. 通道选择及管脚配置

- ii. 驱动强度和幅度配置

- iii. 测量及配置转换时长

- iv. 读取数据

- v. 电容计算

### 8.3.5 单端模式通道选择及端口配置

在单端模式 (OSC\_SEL=0) 下，MCP1085 共有 11 路测量通道，其中外部 10 路，对应通道 0~9，内部参比通道 1 路，对应通道 10。表 8.3.5-1 是单端模式的配置寄存器说明。

表 8.3.5-1 单端模式通道选择寄存器

| 通道及对应管脚           | 寄存器          | 地址   | 位      | 说明                           |

|-------------------|--------------|------|--------|------------------------------|

| 通道 10：内部参比电容 Cref | OSC1_CHS_MSB | 0x20 | CH_REF | 0：表示不测内部参比通道<br>1：表示测量内部参比通道 |

| 通道 9：C9           |              |      | CH9    | 0：表示不测通道 9<br>1：表示测量通道 9     |

| 通道 8：C8           |              |      | CH8    | 0：表示不测通道 8<br>1：表示测量通道 8     |

| 通道 7：C7           | OSC1_CHS_LSB | 0x21 | CH7    | 0：表示不测通道 7<br>1：表示测量通道 7     |

|          |  |  |     |                            |

|----------|--|--|-----|----------------------------|

| 通道 6: C6 |  |  | CH6 | 0: 表示不测通道 6<br>1: 表示测量通道 6 |

| 通道 5: C5 |  |  | CH5 | 0: 表示不测通道 5<br>1: 表示测量通道 5 |

| 通道 4: C4 |  |  | CH4 | 0: 表示不测通道 4<br>1: 表示测量通道 4 |

| 通道 3: C3 |  |  | CH3 | 0: 表示不测通道 3<br>1: 表示测量通道 3 |

| 通道 2: C2 |  |  | CH2 | 0: 表示不测通道 2<br>1: 表示测量通道 2 |

| 通道 1: C1 |  |  | CH1 | 0: 表示不测通道 1<br>1: 表示测量通道 1 |

| 通道 0: C0 |  |  | CH0 | 0: 表示不测通道 0<br>1: 表示测量通道 0 |

MCP1085 还支持测量通道之间的互电容，表 8.3.5-2 是互电容测量通道的分组及配置寄存器说明。

表 8.3.5-2 互电容通道选择寄存器

| 通道及对应管脚       | 寄存器       | 地址   | 位    | 说明                                           |

|---------------|-----------|------|------|----------------------------------------------|

| 通道 4: C8 和 C9 | OSC1_MCHS | 0x22 | MCH4 | 0: 表示不测通道 8-9 之间的互电容<br>1: 表示测量通道 8-9 之间的互电容 |

| 通道 3: C6 和 C7 |           |      | MCH3 | 0: 表示不测通道 6-7 之间的互电容<br>1: 表示测量通道 6-7 之间的互电容 |

| 通道 2: C4 和 C5 |           |      | MCH2 | 0: 表示不测通道 4-5 之间的互电容<br>1: 表示测量通道 4-5 之间的互电容 |

| 通道 1: C2 和 C3 |           |      | MCH1 | 0: 表示不测通道 2-3 之间的互电容<br>1: 表示测量通道 2-3 之间的互电容 |

| 通道 0: C0 和 C1 |           |      | MCH0 | 0: 表示不测通道 0-1 之间的互电容<br>1: 表示测量通道 0-1 之间的互电容 |

在配置互电容通道时，对应的 CHx 位和 MCHx 位都需要置 1。例如，选择测量互电容通道 1，需要同时设置 CH2=1、CH3=1 和 MCH1=1。芯片会自动进行测量并给出互电容  $C_M$  对应的数据。

在单端模式下，当通道不工作时，可以通过寄存器配置其管脚的连接方式，分别有 3 种模式：高阻、接地和有源屏蔽，具体配置如下表所示。

表 8.3.5-3 管脚配置寄存器

| 寄存器      | 地址   | 位       | 说明                                                                                |

|----------|------|---------|-----------------------------------------------------------------------------------|

| SHLD_CFG | 0x26 | CS[1:0] | 00: 表示电容测量端口在非测量期间为高阻状态。<br>01: 表示电容测量端口在非测量期间接地。<br>1x: 表示电容测量端口在非测量期间输出有源屏蔽信号，仅 |

|  |  |                              |

|--|--|------------------------------|

|  |  | 在 OSC_SEL=0 且 SHLD_EN=1 时有效。 |

|--|--|------------------------------|

### 8.3.6 单端模式驱动强度及幅度配置

在单端模式下，驱动强度有 9 种配置，具体配置和对应的驱动电流如下表所示。

表 8.3.6-1 单端模式驱动强度配置寄存器

| 寄存器      | 地址   | 位           | 说明                                                                                                                                                                                    |

|----------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1_CFG | 0x23 | OSC1_I[3:0] | 0000: 驱动电流为 4uA<br>0001: 驱动电流为 8uA<br>0010: 驱动电流为 16uA<br>0011: 驱动电流为 42uA<br>0100: 驱动电流为 100uA<br>0101: 驱动电流为 250uA<br>0110: 驱动电流为 500uA<br>0111: 驱动电流为 1000uA<br>1xxx: 驱动电流为 2000uA |

在单端模式下，振荡幅度有 8 种配置：当对电源噪声抑制要求较高时，幅度配置建议选择 0.2V-1.2V 幅度配置，此时驱动电路采用内部 LDO 供电；当需要大摆幅激励驱动时，配置幅度与  $V_{DD}$  电压有关，如下表后四种配置所示，此时内部 LDO 关闭，驱动电路采用  $V_{DD}$  供电。

表 8.3.6-2 单端模式振荡幅度配置寄存器

| 寄存器      | 地址   | 位           | 说明                                                                                                                                                                                                                                                                                   |

|----------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|