## 产品规格书

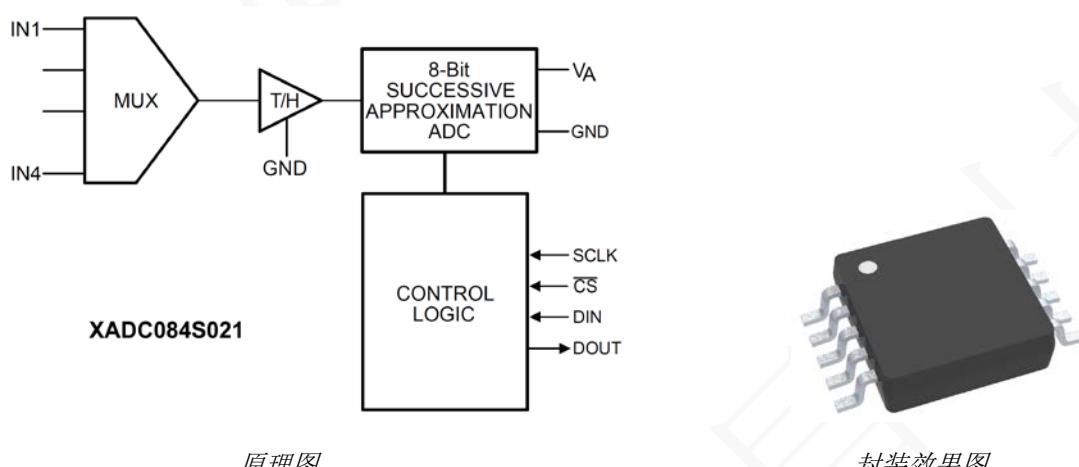

XADC084S021 是一款高速率、低功耗、4 通道、8 位 ADC (Analog-to-Digital Converter) 芯片，即模拟数字转换器。XADC084S021 的工作电压  $V_A$  范围 2.70 V - 5.25 V。XADC084S021 的性能参数涵盖了 50KSPS 至 200KSPS 的较宽转换范围，而不仅仅只在一个特定采样率下有效。XADC084S021 带有内部采样保持电路的逐次逼近寄存器架构，它可配置为在 IN1 至 IN4 输入端口接收多达四路输入信号，这些通道中每个通道的模拟输入范围为 0 至  $V_A$ 。

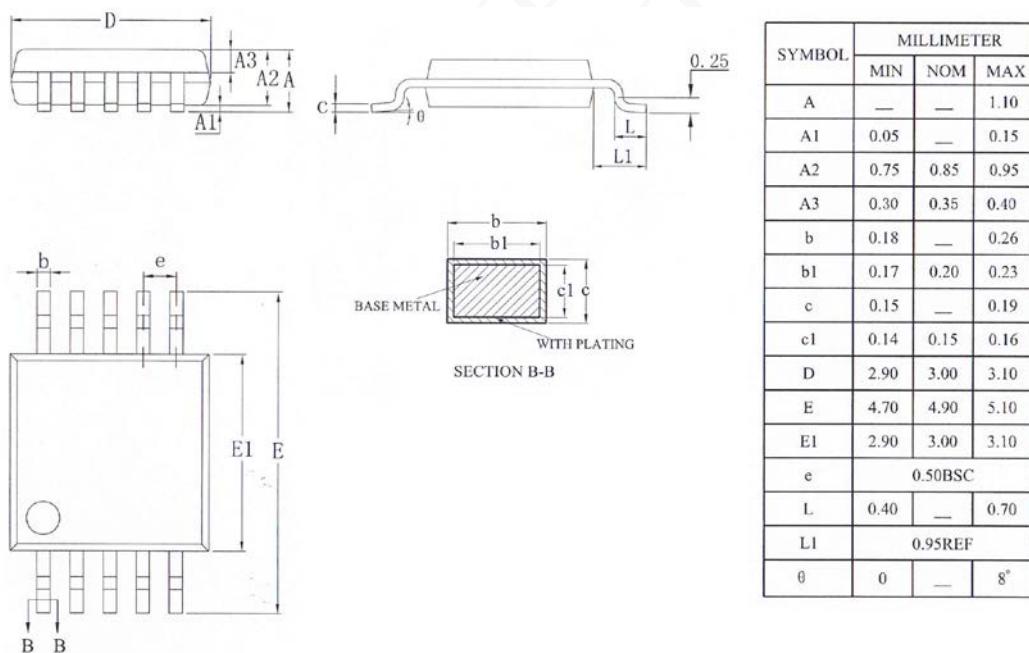

XADC084S021 采用 10 引脚 MSOP 封装，工作温度范围为 -40°C 至 85°C。

**XADC084S021 可 pin-to-pin 替代 ADC084S021。**

### 主要特征

- 电源电压范围：2.70V 至 5.25V

- 8 位分辨率

- 4 个单端输入 IN1 – IN4

- 采样率：50KSPS - 200KSPS

- 串行接口：兼容 SPI/QSPI/MICROWIR/DSP

- 10 引脚 MSOP 封装

### 应用领域

- 便携式系统

- 远程数据采集

- 仪表与控制系统

- 医疗器械

- 移动通信

原理图

封装效果图

## 1. 主要技术参数

- 电源电压范围: 2.70V 至 5.25V

- 8位分辨率, 无失码

- 微分非线性误差 DNL:  $\pm 0.4$ LSB (MAX)

- 积分非线性误差 INL: $\pm 0.4$ LSB (MAX)

- 信噪比失真 SNR:49.5dB@40kHz

- 总谐波失真 THD:-70dB@40kHz

- 串行接口: 兼容 SPI/QSPI/MICROWIRE/DSP

- 4个单端输入 IN1 – IN4

- 采样率: 50KSPS - 200KSPS

- 功耗 (典型值) :

- 0.8 mA (2.7V/200KSPS)

- 1.1 mA (3.3V/200KSPS)

- 无流水线周期延迟

- 10引脚 MSOP 封装

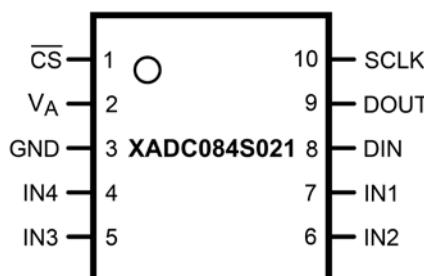

## 2. 引脚配置

引脚图

| 引脚      |     | 描述                                                                                                                           |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 序号  |                                                                                                                              |

| CS      | 1   | 片选信号, 低电平有效。                                                                                                                 |

| VA      | 2   | 模拟电源, 也用作参考电压 $V_{REF}$ 。范围是 2.70V – 5.25V。                                                                                  |

| GND     | 3   | 地信号。所有电路的接地参考点。                                                                                                              |

| IN4~IN1 | 4~7 | 模拟输入。模拟输入 1 至模拟输入 4, 4 个单端多路模拟输入通道, 通过使用控制寄存器的 ADD0 到 ADD2 位来选择要转换的模拟输入通道。所有输入通道的输入范围为 0 到 $V_A$ 。任何未使用的输入通道应连接到 GND, 以避免噪声。 |

| DIN     | 8   | 逻辑输入, 提供要写入控制寄存器的数据, 并在 SCLK 的上升沿被读入寄存器。                                                                                     |

| DOUT    | 9   | 串行数据输出, 在 SCLK 的下降沿上被输出。                                                                                                     |

| SCLK    | 10  | 串行时钟。此时钟直接控制转换和读出过程。                                                                                                         |

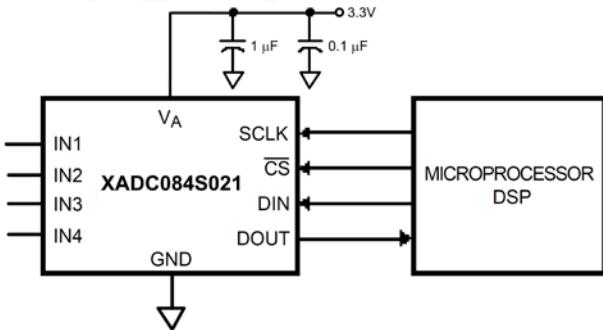

## 3. 典型连接

XADC084S021 的典型连接电路, 请参见下图。模拟电源通过靠近 XADC084S021 的电容网络旁路。XADC084S021 使用模拟电源 ( $V_A$ ) 作为其参考电压,  $V_A$  要尽可能保持没有其他信号干扰。

典型连接电路图

## 4. 控制寄存器

XADC084S021 上的控制寄存器是一个 8 位的只写寄存器。数据在 XADC084S021 的 DIN 引脚上加载，发生在 SCLK 的上升沿。数据从内部读取转换结果的同时在 DIN 线上传输。这要求每次数据传输都需要 16 个串行时钟。只有在  $\overline{CS}$  下降沿之后的前 8 个上升时钟沿提供的信息才会加载到控制寄存器中。MSB 表示数据流中的第一个位。位功能在表 I 中概述。注意，控制寄存器在上电时的默认内容是全零。

| Bit7(MSB) | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|-----------|------|------|------|------|------|------|------|

| DONTC     | ZERO | ADD2 | ADD1 | ADD0 | ONE  | ZERO | ZERO |

表 I

| Bit  | Mnemonic | Comment                           |

|------|----------|-----------------------------------|

| 7    | DONTC    | 写入控制寄存器这些位的值是 0 还是 1 是无关紧要的。      |

| 6    | ZERO     | 必须将 0 写入这个位以确保 XADC084S021 的正确操作。 |

| 5    | ADD2     | 这三位决定哪个输入通道将在下一个转换周期被采样和转换。       |

| 4    | ADD1     |                                   |

| 3    | ADD0     |                                   |

| 2    | ONE      | 必须将 1 写入这个位以确保 XADC084S021 的正确操作。 |

| 1, 0 | ZERO     | 必须将 0 写入这两位以确保 XADC084S021 的正确操作。 |

## 5. 模拟输入通道选择

开机时，默认选择是 IN4。当从掉电状态返回正常操作时，选择的 IN 将是掉电前选定的那个。下表显示了 XADC084S021 从 IN4 到 IN1 每个模拟输入对应的多路复用器地址。

| ADD2 | ADD1 | ADD0 | 模拟输入通道   |

|------|------|------|----------|

| 0    | 0    | 0    | IN4 (默认) |

| 0    | 0    | 1    | IN3      |

| 0    | 1    | 0    | IN2      |

| 0    | 1    | 1    | IN1      |

请注意，XADC084S021 与 ADC084S021 不同的是，XADC084S021 当重新开机时默认通道为 IN4，而不是 IN1。

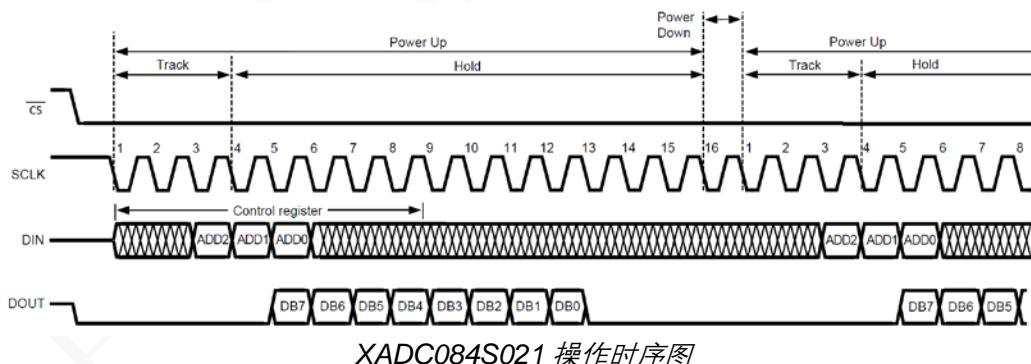

## 6. 时序图

XADC084S021 操作时序图

转换在 $\overline{CS}$ 下降沿启动，同时提供串行时钟 **SCLK** 信号。XADC084S021 完成转换并访问转换结果需要十六个串行时钟周期。数据都是 **MSB** 格式，在四个前导零后输出 8 位转换后的数据跟随四个尾随零。在 **SCLK** 的第 16 个下降沿，**DOUT** 进入三态，转换周期结束。

一旦数据传输完成 ( $\overline{CS}$  已返回高电平)，通过再次将  $\overline{CS}$  拉低即可立即启动另一个转换。

## 7. 封装示意图

## 8. 注意事项

1. 拆封的 IC、管装 IC 等必须放在干燥柜内储存，干燥柜内湿度<20% R.H。

2. 存取后都以静电包装防护袋保存元件。

3. 防静电损伤：器件为静电敏感器件，传输、装配、测试过程中应采取充分的防静电措施。

4. 用户在使用前应进行外观检查，电路底部、侧面、四周光亮方可进行焊接。如出现氧化可采去氧化手段对电路进行处理，处理完成电路必须在 12 小时内完成焊接。