# RENESAS

# RC192xx

PCIe Gen5/6 2-Input Clock Mux Family with LOS

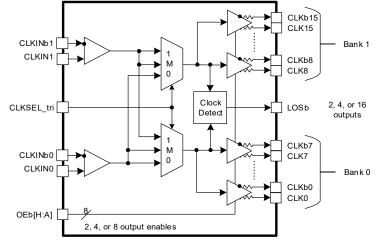

The RC192xx (RC19202, RC19204, RC19208, RC19216) are ultra-high performance clock muxes supporting PCIe Gen5 and Gen6. They provide a Loss-Of-Signal (LOS) output for system monitoring and redundancy. The devices also incorporate Power Down Tolerance (PDT), Flexible Power Sequencing (FPS), and Automatic Clock Parking (ACP) features to insure good behavior under abnormal system conditions. They can drive both source-terminated and double-terminated loads up to 400MHz. The CLKIN inputs also support either HCSL or LVDS signaling levels, making the devices ideal for LVDS to HCSL level translation. The excellent phase jitter and PNSR performance make the RC192xx well suited for network applications.

# Applications

- Cloud/High-performance Computing

- nVME Storage

- Networking

- Accelerators

# **Key Specifications**

- PCIe Gen5 additive phase jitter: 7fs RMS

- PCIe Gen6 additive phase jitter: 4fs RMS

- DB2000Q additive phase jitter: 9fs RMS

- 12kHz-20MHz additive phase jitter: 37fs RMS at 156.25MHz

- 1MHz to 400MHz operation with ACP disabled

- 25MHz to 400MHz operation with ACP enabled

# Features

- 2, 4, 8, or 16 Low-Power (LP) HCSL outputs saves up to 64 resistors

- 2:N or 2 x 1:N/2 modes (N is number of outputs)

- 85Ω or 100Ω output impedance

- Outputs drive both source-terminated and doubleterminated loads

- Open-drain LOS output

- FPS allows inputs and clocks to be applied before power is applied or power to be applied with no input clock

- ACP cleanly parks outputs in low/low state when selected input clock is lost

- Spread-spectrum tolerant

- Up to 8 output enable pins

- Selectable 4-wire Side-Band-Interface (SBI) for hardware output enable (RC19208, RC19216)

- SMBus write protection features (RC19216)

- CLKIN pins directly support HCSL or LVDS signaling levels

- 3 × 3 mm 20-VFQFPN to 6 × 6 mm 80-GQFN packages

# **PCIe Clocking Architectures**

- Common Clocked (CC)

- Independent Reference (IR) with and without spread spectrum

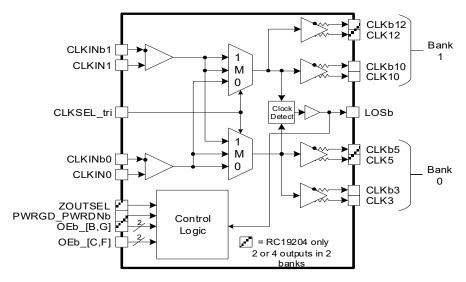

| CLKSEL_tri | 0      | 1      | М      |

|------------|--------|--------|--------|

| Bank 0     | CLKIN0 | CLKIN1 | CLKIN0 |

| Bank 1     | CLKIN0 | CLKIN1 | CLKIN1 |

# Contents

| 1. | Pin Ir | formation                                                                                                            |                                         |

|----|--------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|    | 1.1    | Signal Types                                                                                                         |                                         |

|    | 1.2    | RC19216/RC19208 Pin Information                                                                                      | nation                                  |

|    |        | 1.2.1 RC19216 Pin Assignments                                                                                        | ments                                   |

|    |        | 1.2.2 RC19216 Pin Descriptions                                                                                       | ptions                                  |

|    |        | 1.2.3 RC19208 Pin Assignments                                                                                        |                                         |

|    |        | 1.2.4 RC19208 Pin Descriptions                                                                                       |                                         |

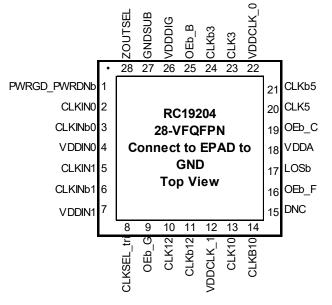

|    | 1.3    | RC19204/RC19202 Pin Information                                                                                      |                                         |

|    |        | 1.3.1 RC19204 Pin Assignments                                                                                        |                                         |

|    |        | 1.3.2 RC19204 Pin Descriptions                                                                                       |                                         |

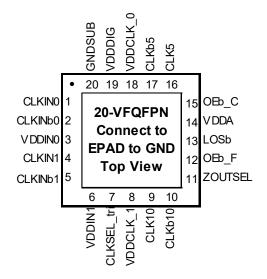

|    |        | 1.3.3 RC19202 Pin Assignments                                                                                        |                                         |

|    |        | 1.3.4 RC19202 Pin Descriptions                                                                                       |                                         |

|    | 1.4    | OEb Pin to CLK Output Mapping                                                                                        |                                         |

| 2. | Spec   | ifications                                                                                                           | 5                                       |

|    | 2.1    | Absolute Maximum Ratings                                                                                             |                                         |

|    | 2.2    | Recommended Operation Conditions                                                                                     |                                         |

|    | 2.2    | Thermal Specifications                                                                                               |                                         |

|    | 2.3    | Electrical Characteristics                                                                                           |                                         |

|    | 2.7    | 2.4.1 PCle Phase Jitter                                                                                              |                                         |

|    |        | 2.4.2 Other Phase Jitter                                                                                             |                                         |

|    |        | 2.4.2       Other Flase Sitter       24         2.4.3       Output Frequencies, Startup Time and LOS Timing       24 |                                         |

|    |        | 2.4.3       Output Prequencies, Startup Time and LOS Timing                                                          |                                         |

|    |        | 2.4.4     CER (EP-HCSE) AC/DC Output Characteristics     2       2.4.5     CLKIN AC/DC Characteristics     30        |                                         |

|    |        |                                                                                                                      |                                         |

|    |        |                                                                                                                      |                                         |

|    |        | 2.4.7 I/O Signals                                                                                                    |                                         |

|    |        | 2.4.8 Power Supply Current                                                                                           |                                         |

|    |        | 2.4.9 SMBus Electrical Characteristics                                                                               |                                         |

|    |        | 2.4.10 Side-band Interface                                                                                           |                                         |

| 3. |        | _oads                                                                                                                |                                         |

| 4. | Gene   | ral SMBus Serial Interface Information                                                                               | formation                               |

|    | 4.1    | How to Write                                                                                                         |                                         |

|    | 4.2    | How to Read                                                                                                          |                                         |

|    | 4.3    | Write Lock Functionality (RC19208, RC19216) 40                                                                       | 9208, RC19216)                          |

|    | 4.4    | SMBus Address Selection (RC19208, RC19216) 40                                                                        | C19208, RC19216)                        |

|    | 4.5    | SMBus Register Set (RC19208, RC19216) 40                                                                             | 18, RC19216)                            |

| 5. | Appli  | cations Information                                                                                                  |                                         |

|    | 5.1    | Inputs, Outputs, and Output Enable Control                                                                           | nable Control                           |

|    |        | 5.1.1 Recommendations for Unused Inputs and Outputs                                                                  |                                         |

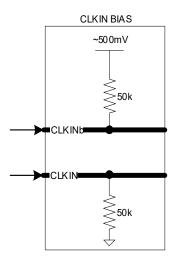

|    |        | 5.1.2 Differential CLKIN Configurations                                                                              |                                         |

|    |        | 5.1.3 Differential CLK Output Configurations                                                                         | -                                       |

|    | 5.2    | Power Down Tolerant Pins                                                                                             | 0                                       |

|    | 5.3    | Flexible Startup Sequencing                                                                                          |                                         |

|    | 5.4    | Loss of Signal and Automatic Clock Parking                                                                           |                                         |

|    | 5.5    | Output Enable Control                                                                                                |                                         |

|    | 0.0    | 5.5.1 SMBus Output Enable Bits                                                                                       |                                         |

|    |        | 5.5.2 Output Enable (OEb) Pins                                                                                       |                                         |

|    |        |                                                                                                                      | , , , , , , , , , , , , , , , , , , , , |

RENESAS

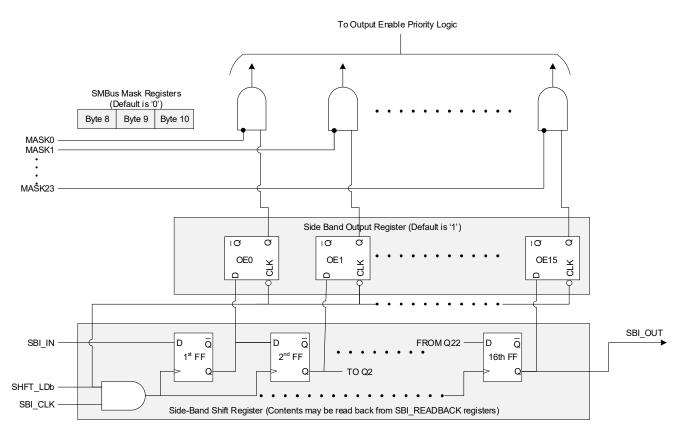

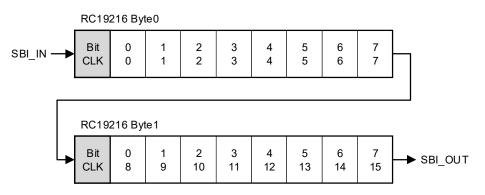

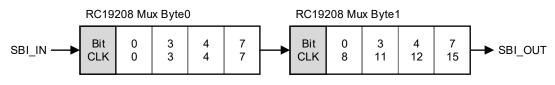

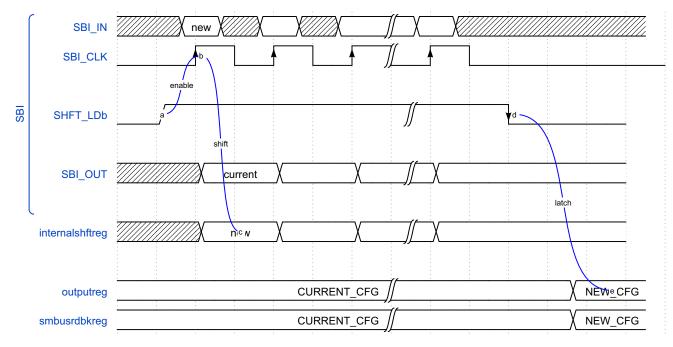

|    |       | 5.6.1      | x Clock M<br>Side-Bar<br>Output E | nd Inter | face ( | SBI) | <br> | <br>      | <br> | <br>    | <br> | <br>      | <br> |       |     | <br>56 |

|----|-------|------------|-----------------------------------|----------|--------|------|------|-----------|------|---------|------|-----------|------|-------|-----|--------|

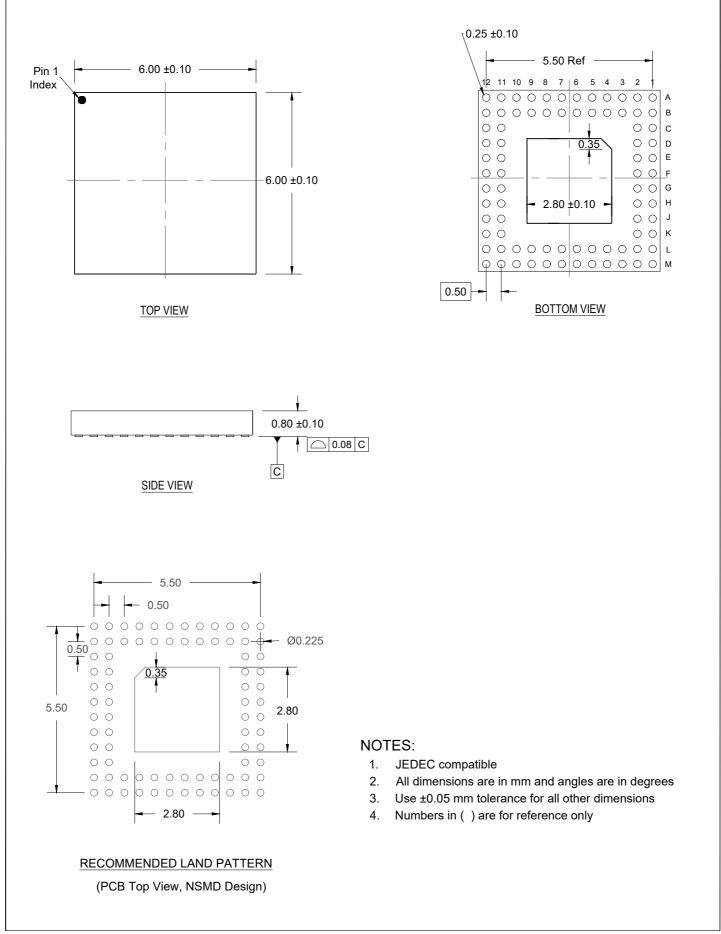

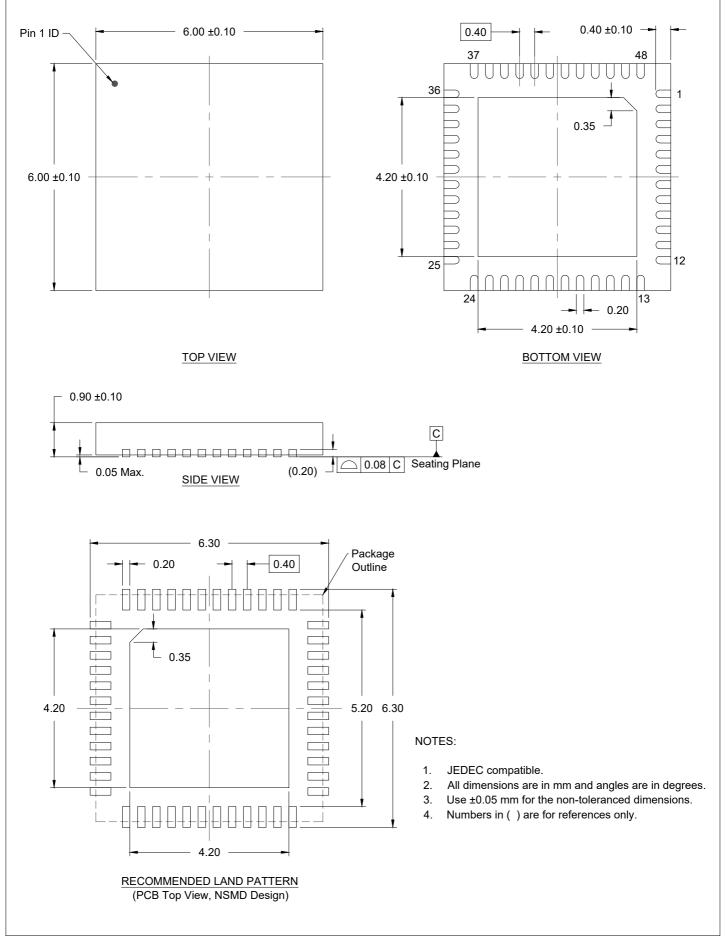

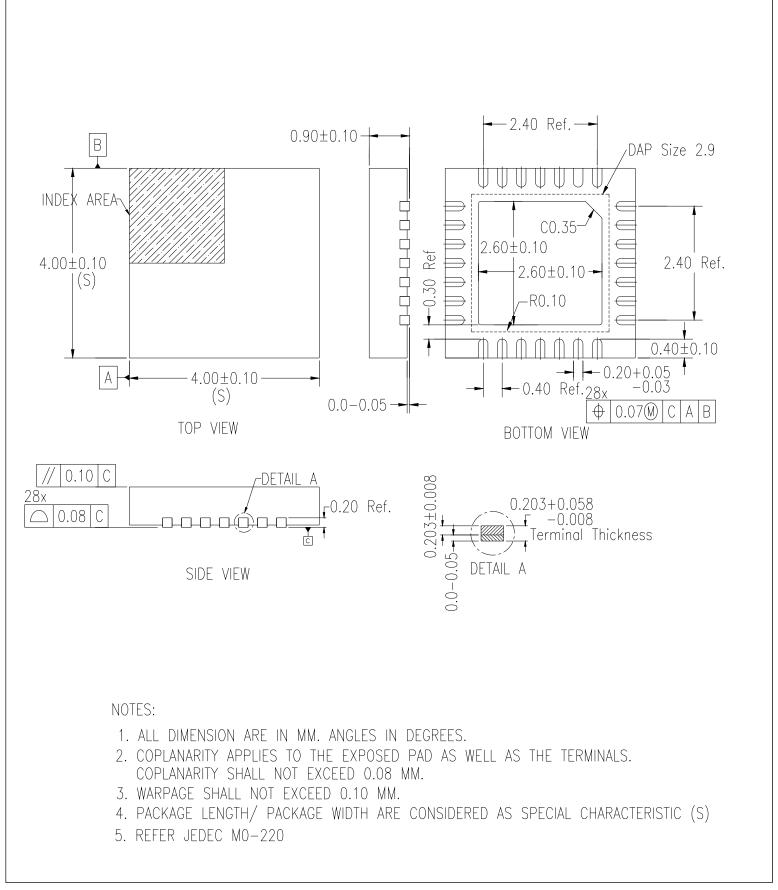

| 6. | Packa | age Outli  | ine Draw                          | ings     |        |      | <br> | <br>      | <br> | <br>    | <br> | <br>      | <br> |       |     | <br>60 |

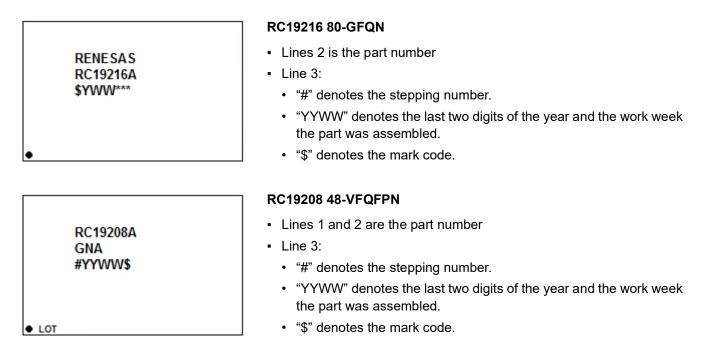

| 7. | Marki | ing Diagr  | rams                              |          |        |      | <br> | <br>      | <br> | <br>    | <br> | <br>• • • | <br> | • • • |     | <br>60 |

| 8. | Order | ring Infoi | rmation .                         |          |        |      | <br> | <br>• • • | <br> | <br>• • | <br> | <br>• • • | <br> |       | ••• | <br>61 |

| 9. | Revis | ion Histo  | ory                               |          |        |      | <br> | <br>      | <br> | <br>••• | <br> | <br>      | <br> |       |     | <br>62 |

# 1. Pin Information

# 1.1 Signal Types

| Term | Description                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------|

| I    | Input                                                                                                          |

| 0    | Input                                                                                                          |

| OD   | Open Drain Output                                                                                              |

| I/O  | Bi-Directional                                                                                                 |

| PD   | Pull-down                                                                                                      |

| PU   | Pull-up                                                                                                        |

| Z    | Tristate                                                                                                       |

| D    | Driven                                                                                                         |

| Х    | Don't care                                                                                                     |

| SE   | Single-ended                                                                                                   |

| DIF  | Differential                                                                                                   |

| PWR  | 3.3 V power                                                                                                    |

| GND  | Ground                                                                                                         |

| PDT  | Power Down Tolerant: These signals tolerate being driven when the device is powered down (VDD is not present). |

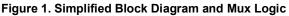

# 1.2 RC19216/RC19208 Pin Information

Figure 2. RC19216/RC19208 Block Diagram

|   | 1         | 2                 | 3      | 4          | 5      | 6                  | 7                   | 8       | 9        | 10    | 11                | 12       | _ |

|---|-----------|-------------------|--------|------------|--------|--------------------|---------------------|---------|----------|-------|-------------------|----------|---|

| Α | GNDSUB    | CLKb0             | CLK0   | CLKb1      | CLK1   | CLKb2              | CLK2                | CLKb3   | CLK3     | CLKb4 | CLK4              | CLKb5    | A |

| В | ZOUTSEL   | VDDCLK_0          | NC     | OEb_A      | NC     | OEb_B              | NC                  | SBI_ENQ | VDDCLK_0 | NC    | SADR_tri1         | CLK5     | в |

| С | VDDDIG    | NC                |        |            |        |                    |                     |         |          |       | OEb_C             | CLKb6    | с |

| D | CLKIN0    | PWRGD_P<br>WRDNb  |        |            |        |                    |                     |         |          |       | NC                | CLK6     | D |

| E | CLKINb0   | NC                |        |            |        |                    |                     |         |          |       | OEb_D_SBI<br>_CLK | CLKb7    | Е |

| F | SADR_tri0 | V DDIN0           |        |            |        | 80-G               |                     |         |          |       | VDDA              | CLK7     | F |

| G | CLKIN1    | NC                |        |            | Con    |                    | PAD to 0<br>View    | BND     |          |       | NC                | VDDCLK_0 | G |

| Н | CLKINb1   | SDATA             |        |            |        |                    |                     |         |          |       | VDDCLK_1          | LOSb     | н |

| J | SCLK      | V DDIN1           |        |            |        |                    |                     |         |          |       | NC                | CLKb8    | J |

| к | VDDCLK_1  | NC                |        |            |        |                    |                     |         |          |       | OEb_E_SBI<br>_N   | CLK8     | к |

| L | CLK15     | OEb_H_SBI<br>_OUT | NC     | CLKSEL_tri | NC     | OEb_G_SH<br>FT_LDb | VDDCLK_1            | NC      | NC       | NC    | OEb_F             | CLKb9    | L |

| Μ | CLKb15    | CLK14             | CLKb14 | CLK13      | CLKb13 | CLK12              | CLKb12              | CLK11   | CLKb11   | CLK10 | CLKb10            | CLK9     | М |

|   | 1         | 2                 | 3      | 4          | 5      | 6                  | 7<br>OEN <b>T</b> o | 8       | 9        | 10    | 11                | 12       |   |

# 1.2.1 RC19216 Pin Assignments

Figure 3. 80-GQFN – Top View

# 1.2.2 RC19216 Pin Descriptions

### Table 1. RC19216 Pin Descriptions

| Pin N | umber | Pin Name | Туре   | Description                 |

|-------|-------|----------|--------|-----------------------------|

| А     | 1     | GNDSUB   | GND    | Ground pin for substrate.   |

| А     | 2     | CLKb0    | O, DIF | Complementary clock output. |

| А     | 3     | CLK0     | O, DIF | True clock output.          |

| А     | 4     | CLKb1    | O, DIF | Complementary clock output. |

| А     | 5     | CLK1     | O, DIF | True clock output.          |

| А     | 6     | CLKb2    | O, DIF | Complementary clock output. |

| А     | 7     | CLK2     | O, DIF | True clock output.          |

| А     | 8     | CLKb3    | O, DIF | Complementary clock output. |

| Pin Nu | Pin Number Pin Name |              | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|--------|---------------------|--------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| А      | 9                   | CLK3         | O, DIF            | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| А      | 10                  | CLKb4        | O, DIF            | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| А      | 11                  | CLK4         | O, DIF            | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| А      | 12                  | CLKb5        | O, DIF            | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| В      | 1                   | ZOUTSEL      | I, SE, PD         | Input to select differential output impedance.<br>$0 = 85\Omega, 1 = 100\Omega$                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| В      | 2                   | VDDCLK_0     | PWR               | Power supply for clock output bank 0.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| В      | 3                   | NC           | NC                | No connect.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| В      | 4                   | OEb_A        | I, SE,<br>PDT, PU | Active low input for enabling output group A. See Table 5 for details.<br>1 =disable output, 0 = enable output                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| В      | 5                   | NC           | NC                | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| В      | 6                   | OEb_B        | I, SE,<br>PDT, PU | Active low input for enabling output group B. See Table 5 for details.<br>1 = disable output, 0 = enable output                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| В      | 7                   | NC           | NC                | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| В      | 8                   | SBI_ENQ      | I, SE,<br>PDT, PD | Input that selects function of pins that are multiplexed between OE and SBI<br>functionality. SMBus output enable bits and non-multiplexed OE pins remain<br>functional when SBI is enabled. This pin must be strapped to its desired state. It<br>cannot dynamically change.<br>0 = SBI is disabled. Multiplexed pins function as output enables.<br>1 = SBI is enabled. Multiplexed pins function as SBI control pins. |  |  |  |  |

| В      | 9                   | VDDCLK_0     | PWR               | Power supply for clock output bank 0.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| В      | 10                  | NC           | NC                | No connect.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| в      | 11                  | SADR_tri1    | I, SE, PD,<br>PU  | SMBus address bit. This is a tri-level input that works in conjunction with other SADR pins, if present, to decode SMBus Addresses. See the SMBus Address Selection (RC19208, RC19216) table and refer to the tri-level input thresholds in the electrical tables.                                                                                                                                                       |  |  |  |  |

| В      | 12                  | CLK5         | O, DIF            | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| С      | 1                   | VDDDIG       | PWR               | Digital power.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| С      | 2                   | NC           | NC                | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| с      | 11                  | OEb_C        | I, SE, PD,<br>PDT | Active low input for enabling output group B. See Table 5 for details.<br>0 = enable output, 1 = disable output.                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| С      | 12                  | CLKb6        | O, DIF            | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| D      | 1                   | CLKIN0       | I, DIF            | True clock input.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| D      | 2                   | PWRGD_PWRDNb | I, SE,<br>PDT, PU | Input notifies device to sample latched inputs and start up on first high assertion.<br>Low enters Power Down Mode, subsequent high assertions exit Power Down<br>Mode.                                                                                                                                                                                                                                                  |  |  |  |  |

| D      | 11                  | NC           | NC                | No connect.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| D      | 12                  | CLK6         | O, DIF            | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| E      | 1                   | CLKINb0      | I, DIF            | Complementary clock input.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| E      | 2                   | NC           | NC                | No connect.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

### Table 1. RC19216 Pin Descriptions (Cont.)

| Pin Nu | umber | Pin Name      | Туре                       | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|-------|---------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E      | 11    | OEb_D_SBI_CLK | I, SE,<br>PDT, PU<br>or PD | Active low input for enabling output group D, or the clock pin for the Side-Band<br>Interface. The function of this pin is controlled by the SBI_EN or SBI_ENQ pin.<br>Refer to the Side-band Interface section and Table 5 for details.<br>OE mode with internal pull-up:<br>0 = enable output, 1 = disable output.<br>Side-Band mode: SBI clock input with internal pull-down.                 |

| Е      | 12    | CLKb7         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                      |

| F      | 1     | SADR_tri0     | I, SE, PD,<br>PU           | SMBus address bit. This is a tri-level input that works in conjunction with other SADR pins, if present, to decode SMBus Addresses. See the SMBus Address Selection (RC19208, RC19216) table and refer to the tri-level input thresholds in the electrical tables.                                                                                                                               |

| F      | 2     | VDDIN0        | PWR                        | Power supply for clock input 0.                                                                                                                                                                                                                                                                                                                                                                  |

| F      | 11    | VDDA          | PWR                        | Power supply for analog circuitry.                                                                                                                                                                                                                                                                                                                                                               |

| F      | 12    | CLK7          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                               |

| G      | 1     | CLKIN1        | I, DIF                     | True clock input.                                                                                                                                                                                                                                                                                                                                                                                |

| G      | 2     | NC            | NC                         | No connect.                                                                                                                                                                                                                                                                                                                                                                                      |

| G      | 11    | NC            | NC                         | No connect.                                                                                                                                                                                                                                                                                                                                                                                      |

| G      | 12    | VDDCLK_0      | PWR                        | Power supply for clock output bank 0.                                                                                                                                                                                                                                                                                                                                                            |

| Н      | 1     | CLKINb1       | I, DIF                     | Complementary clock input.                                                                                                                                                                                                                                                                                                                                                                       |

| Н      | 2     | SDATA         | I/O, SE,<br>OD, PDT        | Data pin for SMBus interface.                                                                                                                                                                                                                                                                                                                                                                    |

| Н      | 11    | VDDCLK_1      | PWR                        | Power supply for clock output bank 1.                                                                                                                                                                                                                                                                                                                                                            |

| н      | 12    | LOSb          | O, OD,<br>PDT              | Output indicating Loss of Input Signal. This pin is an open drain output and requires<br>an external pull up resistor for proper functionality. A low output on this pin indicates<br>a loss of signal on the input clock.                                                                                                                                                                       |

| J      | 1     | SCLK          | I, SE,<br>PDT              | Clock pin of SMBus interface.                                                                                                                                                                                                                                                                                                                                                                    |

| J      | 2     | VDDIN1        | PWR                        | Power supply for clock input 1.                                                                                                                                                                                                                                                                                                                                                                  |

| J      | 11    | NC            | NC                         | No connect.                                                                                                                                                                                                                                                                                                                                                                                      |

| J      | 12    | CLKb8         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                      |

| К      | 1     | VDDCLK_1      | PWR                        | Power supply for clock output bank 1.                                                                                                                                                                                                                                                                                                                                                            |

| К      | 2     | NC            | NC                         | No connect.                                                                                                                                                                                                                                                                                                                                                                                      |

| к      | 11    | OEb_E_SBI_IN  | I, SE,<br>PDT, PU<br>or PD | Active low input for enabling output group E, or the data pin for the Side-Band<br>Interface. The function of this pin is controlled by the SBI_EN or SBI_ENQ pin.<br>Refer to the Side-band Interface section and Table 5 for details.<br>OE mode with internal pull-up:<br>0 = enable output, 1 = disable output.<br>Side-Band mode with internal pull-down:<br>SBI shift-register data input. |

| К      | 12    | CLK8          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                               |

| L      | 1     | CLK15         | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                               |

### Table 1. RC19216 Pin Descriptions (Cont.)

| Pin Nu | umber | Pin Name       | Туре                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|--------|-------|----------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| L      | 2     | OEb_H_SBI_OUT  | I/O, SE                    | Active low input for enabling output group H, or the SBI shift register data output.<br>The function of is this pin is controlled by the SBI_EN or SBI_ENQ pin. Refer to the<br>Side-band Interface section and Table 5 for details. <i>NOTE</i> : This pin is NOT PDT.<br>OE mode:<br>0 = enable output, 1 = disable output.<br>Side-Band Mode:<br>SBI shift register data output.                                                                                                                                      |  |  |  |  |

| L      | 3     | NC             | NC                         | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| L      | 4     | CLKSEL_tri     | I, SE, PD,<br>PU           | Input to select differential input clock 0 or differential input clock 1. This input has an internal pull-up and pull-down resistor to bias a floating pin to the mid-point.<br>0 = CLKIN0 selected for all outputs.<br>1 = CLKIN1 selected for all outputs.<br>M = CLKIN0 goes to bank 0 and CLKIN1 goes to bank 1.                                                                                                                                                                                                     |  |  |  |  |

| L      | 5     | NC             | NC                         | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| L      | 6     | OEb_G_SHFT_LDb | I, SE,<br>PDT, PU<br>or PD | Active low input for enabling output group 12 or SHFT_LDb pin for the Side-Band<br>Interface. The function of this pin is controlled by the SBI_EN or SBI_ENQ pin.<br>Refer to the Side-band Interface section and Table 5 for details.<br>OE mode with internal pull-up:<br>0 = enable output, 1 = disable output.<br>Side-Band Mode with internal pull-down:<br>0 = disable SBI shift register, 1 = enable SBI shift register.<br>A falling edge transfers SBI shift register contents to SBI output control register. |  |  |  |  |

| L      | 7     | VDDCLK_1       | PWR                        | Power supply for clock output bank 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| L      | 8     | NC             | NC                         | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| L      | 9     | NC             | NC                         | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| L      | 10    | NC             | NC                         | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| L      | 11    | OEb_F          | I, SE, PU,<br>PDT          | Active low input for enabling output group F. Refer to the Table 5 for details.<br>0 = enable output, 1 = disable output.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| L      | 12    | CLKb9          | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| М      | 1     | CLKb15         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| М      | 2     | CLK14          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| М      | 3     | CLKb14         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| М      | 4     | CLK13          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| М      | 5     | CLKb13         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| М      | 6     | CLK12          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| М      | 7     | CLKb12         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| М      | 8     | CLK11          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| М      | 9     | CLKb11         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| М      | 10    | CLK10          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| М      | 11    | CLKb10         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| М      | 12    | CLK9           | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| N/A    |       | EPAD           | GND                        | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

### Table 1. RC19216 Pin Descriptions (Cont.)

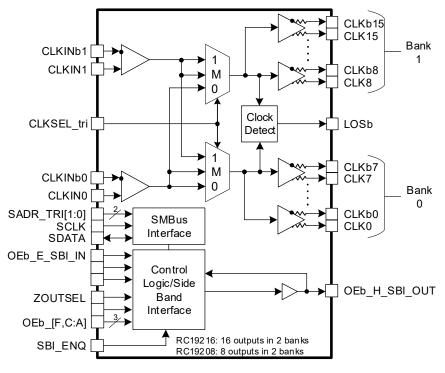

### 1.2.3 RC19208 Pin Assignments

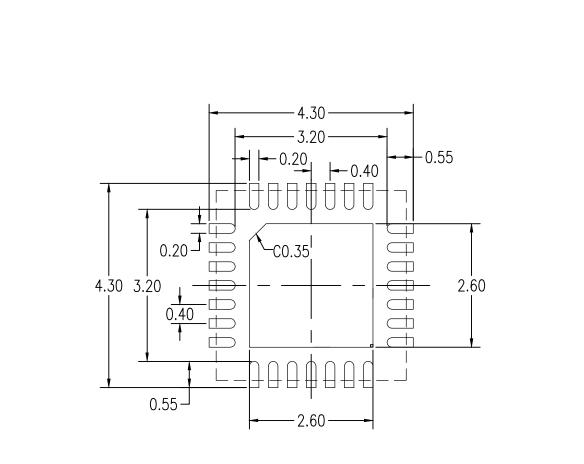

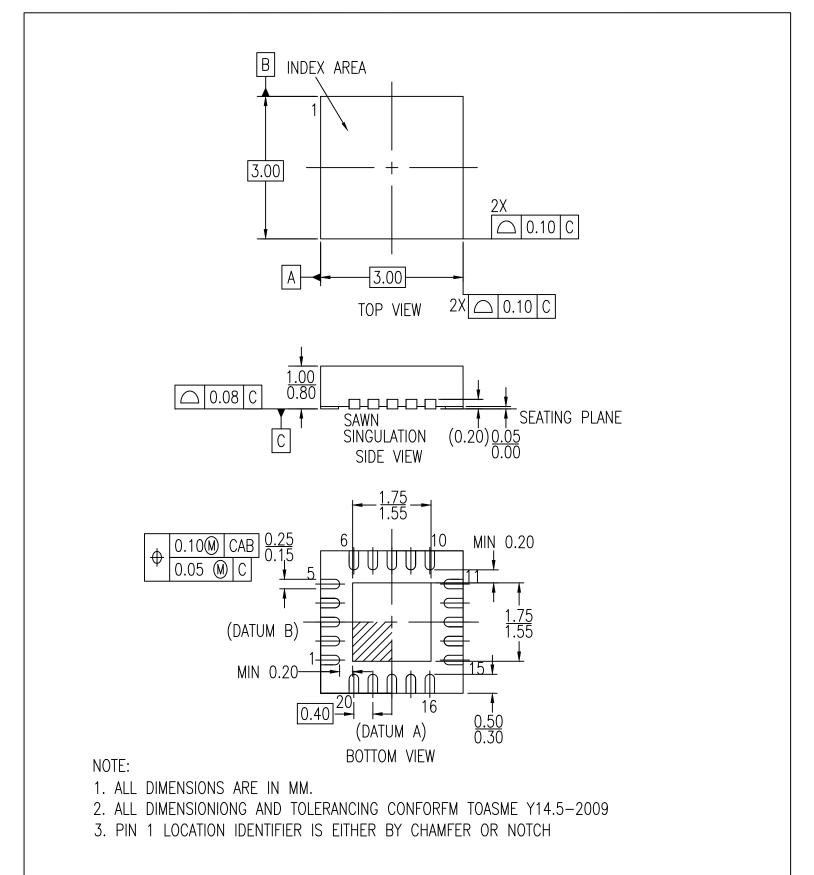

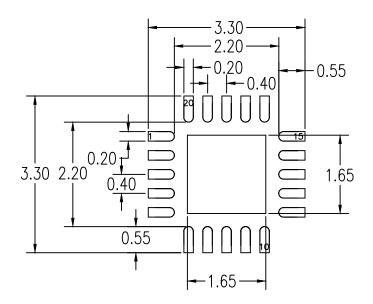

Figure 4. 48-VFQFPN – Top View

### 1.2.4 RC19208 Pin Descriptions

### Table 2. RC19208 Pin Descriptions

| Pin Number | Pin Name     | Туре              | Description                                                                                                                                                                                                                                                        |

|------------|--------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | ZOUTSEL      | I, SE, PD         | Input to select differential output impedance.<br>$0 = 85\Omega, 1 = 100\Omega$                                                                                                                                                                                    |

| 2          | VDDDIG       | PWR               | Digital power.                                                                                                                                                                                                                                                     |

| 3          | PWRGD_PWRDNb | I, SE,<br>PDT, PU | Input notifies device to sample latched inputs and start up on first high assertion.<br>Low enters Power Down Mode, subsequent high assertions exit Power Down<br>Mode.                                                                                            |

| 4          | CLKIN0       | I, DIF            | True clock input.                                                                                                                                                                                                                                                  |

| 5          | CLKINb0      | I, DIF            | Complementary clock input.                                                                                                                                                                                                                                         |

| 6          | VDDIN0       | PWR               | Power supply for clock input 0.                                                                                                                                                                                                                                    |

| 7          | SADR_tri0    | I, SE, PD,<br>PU  | SMBus address bit. This is a tri-level input that works in conjunction with other SADR pins, if present, to decode SMBus Addresses. See the SMBus Address Selection (RC19208, RC19216) table and refer to the tri-level input thresholds in the electrical tables. |

| 8          | CLKIN1       | I, DIF            | True clock input.                                                                                                                                                                                                                                                  |

| 9          | CLKINb1      | I, DIF            | Complementary clock input.                                                                                                                                                                                                                                         |

| Pin Number | Pin Name       | Туре                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|----------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10         | SDATA          | I/O, SE,<br>OD, PDT        | Data pin for SMBus interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11         | SCLK           | I, SE,<br>PDT              | Clock pin of SMBus interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12         | VDDIN1         | PWR                        | Power supply for clock input 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13         | VDDCLK_1       | PWR                        | Power supply for clock output bank 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14         | CLK15          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15         | CLKb15         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16         | OEb_H_SBI_OUT  | I/O, SE                    | Active low input for enabling output group H, or the SBI shift register data output.<br>The function of is this pin is controlled by the SBI_EN or SBI_ENQ pin. Refer to the<br>Side-band Interface section for details. <b>Note: This pin is NOT PDT.</b><br>OE mode:<br>0 = enable output, 1 = disable output.<br>Side-Band Mode:<br>SBI shift register data output.                                                                                                                                       |

| 17         | CLKSEL_tri     | I, SE, PD,<br>PU           | Input to select differential input clock 0 or differential input clock 1. This input has an internal pull-up and pull-down resistor to bias a floating pin to the mid-point.<br>0 = CLKIN0 selected for all outputs.<br>1 = CLKIN1 selected for all outputs.<br>M = CLKIN0 goes to bank 0 and CLKIN1 goes to bank 1.                                                                                                                                                                                         |

| 18         | OEb_G_SHFT_LDb | I, SE,<br>PDT, PU<br>or PD | Active low input for enabling output group 12 or SHFT_LDb pin for the Side-Band<br>Interface. The function of this pin is controlled by the SBI_EN or SBI_ENQ pin.<br>Refer to the Side-band Interface section for details.<br>OE mode with internal pull-up:<br>0 = enable output, 1 = disable output.<br>Side-Band Mode with internal pull-down:<br>0 = disable SBI shift register, 1 = enable SBI shift register.<br>A falling edge transfers SBI shift register contents to SBI output control register. |

| 19         | CLK12          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 20         | CLKb12         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21         | VDDCLK_1       | PWR                        | Power supply for clock output bank 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 22         | CLK11          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 23         | CLKb11         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 24         | OEb_F          | I, SE,<br>PDT, PU          | Active low input for enabling output group F. See the OEb_Assignment registers in Table 33 for output control details.<br>0 = enable output, 1 = disable output.                                                                                                                                                                                                                                                                                                                                             |

| 25         | OEb_E_SBI_IN   | I, SE,<br>PDT, PU<br>or PD | Active low input for enabling output group E, or the data pin for the Side-Band<br>Interface. The function of this pin is controlled by the SBI_EN or SBI_ENQ pin.<br>Refer to the Side-band Interface section for details.<br>OE mode with internal pull-up:<br>0 = enable output, 1 = disable output.<br>Side-Band mode with internal pull-down:<br>SBI shift-register data input.                                                                                                                         |

| 26         | CLK8           | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 27         | CLKb8          | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### Table 2. RC19208 Pin Descriptions (Cont.)

| Pin Number | Pin Name      | Туре                       | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|---------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28         | VDDCLK_1      | PWR                        | Power supply for clock output bank 1.                                                                                                                                                                                                                                                                                                                                                                           |

| 29         | LOSb          | O, OD,<br>PDT              | Output indicating Loss of Input Signal. This pin is an open drain output and requires<br>an external pull up resistor for proper functionality. A low output on this pin indicates<br>a loss of signal on the input clock.                                                                                                                                                                                      |

| 30         | VDDCLK_0      | PWR                        | Power supply for clock output bank 0.                                                                                                                                                                                                                                                                                                                                                                           |

| 31         | VDDA          | PWR                        | Power supply for analog circuitry.                                                                                                                                                                                                                                                                                                                                                                              |

| 32         | CLK7          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                              |

| 33         | CLKb7         | O, DIF                     | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                     |

| 34         | OEb_D_SBI_CLK | I, SE,<br>PDT, PU<br>or PD | Active low input for enabling output group D, or the clock pin for the Side-Band<br>Interface. The function of this pin is controlled by the SBI_EN or SBI_ENQ pin.<br>Refer to the Side-band Interface section for details.<br>OE mode with internal pull-up:<br>0 = enable output, 1 = disable output.<br>Side-Band mode: SBI clock input with internal pull-down.                                            |

| 35         | OEb_C         | I, SE, PU,<br>PDT          | Active low input for enabling output group C. See the OEb_Assignment registers in Table 33 for output control details.<br>0 = enable output, 1 = disable output.                                                                                                                                                                                                                                                |

| 36         | SADR_tri1     | I, SE, PD,<br>PU           | SMBus address bit. This is a tri-level input that works in conjunction with other SADR pins, if present, to decode SMBus Addresses. See the SMBus Address Selection (RC19208, RC19216) table and refer to the tri-level input thresholds in the electrical tables.                                                                                                                                              |

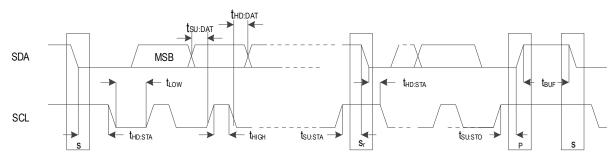

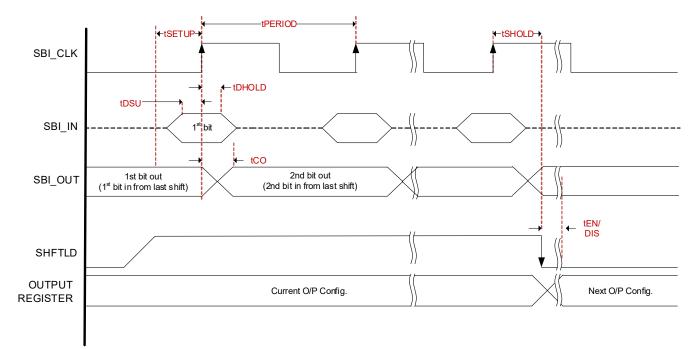

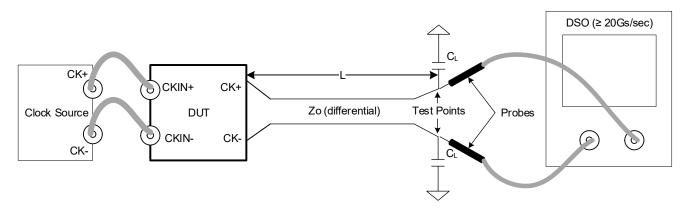

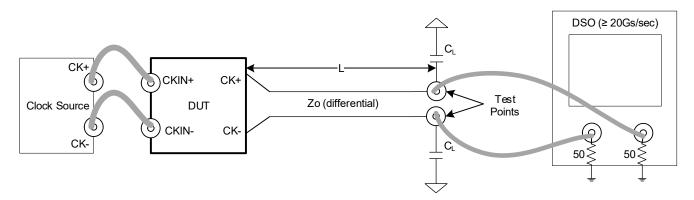

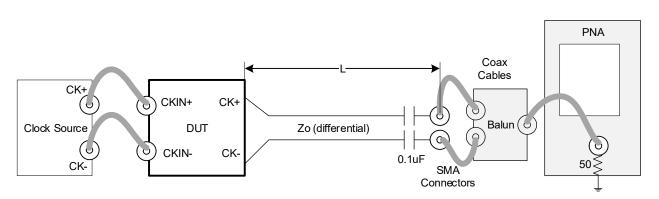

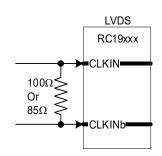

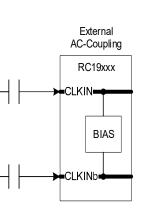

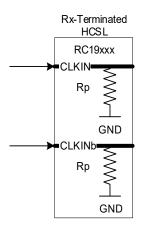

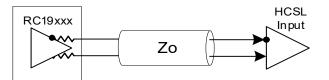

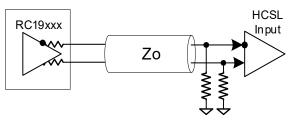

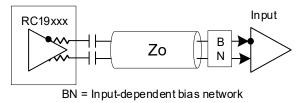

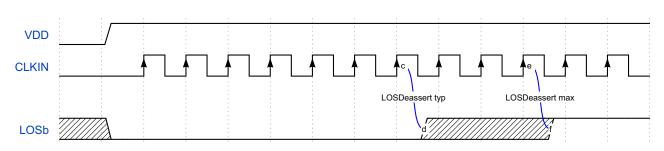

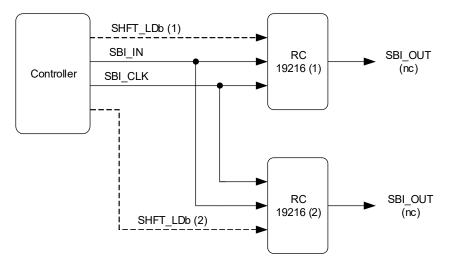

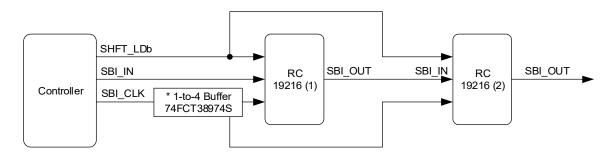

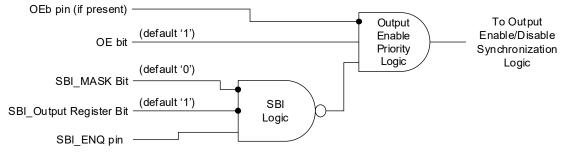

| 37         | CLK4          | O, DIF                     | True clock output.                                                                                                                                                                                                                                                                                                                                                                                              |